Original Citation:

Terms of use: Open Access

# Università degli Studi di Padova

# Padua Research Archive - Institutional Repository

Simplified on-line monitoring system of MOSFET on-resistance based on a semi-empirical model

| Availability: This version is available at: 11577/3313624 since: 2019-10-30T09:57:48Z |

|---------------------------------------------------------------------------------------|

| Publisher: Institute of Electrical and Electronics Engineers Inc.                     |

| Published version: DOI: 10.1109/APEC.2019.8721843                                     |

This article is made available under terms and conditions applicable to Open Access Guidelines, as described at http://www.unipd.it/download/file/fid/55401 (Italian only)

# "Simplified on-line monitoring system of MOSFET on-resistance based on a semi-empirical model" ABSTRACT

This work provides a solution allowing to monitor on-line the health of a power MOSFET adopted in a buck converter. In the considered application, the analysis is focused on the high-side switch, being a low-voltage power MOSFET.

The monitoring system allows estimating the on-resistance of the device by measuring both output current and voltage drop across the switch. Moreover, a semi-empirical model is considered in order to account for the dependence of on-resistance on operating temperature and gate driving voltage. The on-line implementation of such a model allows estimating on-resistance degradation in real-time with a high level of accuracy in a wide range of operating conditions. An on-line calibration procedure is also implemented in order to assess the on-resistance of fresh devices. Experimental results confirm the accuracy of the system (in conjunction with the proposed model) under different operating conditions: load current from 2A to 6A; device temperature up to  $100^{\circ}$ C and gate to source voltage ( $V_{GS}$ ) from 6V to 10.5V. In the abovementioned conditions, an accuracy  $\leq 2.6\%$  is experimentally found. Hence, the system is able to properly estimate the degradation of on-resistance due to ageing conditions.

## I. INTRODUCTION

Electronics switches in power converters are typically subjected to electrical and environmental stress, leading to potential reliability issues. A relevant parameter in analyzing semiconductor devices is the on-resistance ( $R_{on}$ ), since its value is also an indicator of the device health [1]. For example, when considering thermal or power cycling phenomena, we expect a significant increase of  $R_{on}$  due to bond wire or die-chip degradation [2, 3]. Hence, having the possibility to monitor  $R_{on}$  allows detecting in advance the failure of the device. Predictive maintenance can be then adopted, such as replacing the failing device or adopting control techniques to limit the effect of thermal/power cycling [4-6].

Different methodologies have been proposed in order to estimate the on-voltage or the on-resistance of IGBTs or Power MOSFETs. In [7] and indirect estimation of on-resistance of a power MOSFET is

implemented, based on the measurement of input and output voltages of the converter. However, the dependence on the operating temperature, gate driving voltage and output current is not accounted for. In [8, 9], dedicated circuits are developed for the direct measurement of collector-emitter voltage (of an IGBT) during the conduction phase.

This paper addresses the case of condition monitoring of low-voltage power MOSFETs, in which the onresistance is significantly affected by the semiconductor contribution and is hence related to both gate

voltage and operating temperature. To compensate this dependence a simplified semi-empirical model is

proposed. The model can be easily implemented on a microcontroller, allowing the on-line monitoring of  $R_{on}$ . Given the simplicity of the model, the calibration procedure can be also implemented on-line, rather

than considering complex off-line experiments. Being interested in monitoring the high-side switch

degradation, a differential sensing circuit is adopted to measure the drain to source voltage ( $V_{DS}$ ).

#### II. DEVICE UNDER TEST AND PROPOSED MODEL

The device under test, i.e. the high side switch, is a low-voltage trench-gate logic-level p-channel power MOSFET (STD36P4LLF6), with a breakdown voltage of above 40V and a rated drain current of 36A (at room temperature). In order to assess and model the on-resistance of the device, off-line (out of the board) experimental characterization has been performed. To this purpose, devices are placed in a thermal chamber and IV curves are measured by means of source measure units (SMUs): Keithely 2450 and 2651A. The dependence of  $R_{on}$  on both temperature and gate voltage can be described as follows:

$$R_{on} = R_0 + k \frac{T^{\alpha}}{|V_{GS} - V_T|^{\beta}} \tag{1}$$

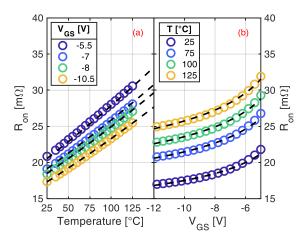

where constant k is technological parameter and  $R_0$  represents the contribution of  $R_{on}$  independent of voltage and temperature (e.g. contact resistance). Both  $R_0$  and k are parameters to be experimentally fitted. The coefficient  $\alpha$  is close to 1.5, according to the typical dependence of mobility on the temperature [10], while the coefficient  $\beta$  is found to be around 0.2. A threshold voltage  $V_T$  of -2.5V is adopted for the considered device and the temperature T is expressed in K. In Fig. 1 the dependence of  $R_{on}$  on temperature and gate

| # | $R_0$                 | k                     | α    | β     |

|---|-----------------------|-----------------------|------|-------|

|   | $[\Omega]$            | [-]                   | [-]  | [-]   |

| 1 | 2.67·10 <sup>-3</sup> | $3.74 \cdot 10^{-6}$  | 1.53 | 0.203 |

| 2 | 4.81·10 <sup>-3</sup> | $2.47 \cdot 10^{-6}$  | 1.59 | 0.226 |

| 3 | 2.93·10 <sup>-3</sup> | 5.35·10 <sup>-6</sup> | 1.47 | 0.197 |

| 4 | 2.37·10 <sup>-3</sup> | 3.54·10 <sup>-6</sup> | 1.53 | 0.206 |

Table 1: Fitting parameters obtained by means of (1) in four different samples. While  $\alpha$  and  $\beta$  coefficients are independent of the considered device,  $R_0$  and k needs to be calibrated.

voltage is reported, along with the fitting of data with (1). The list of calibration parameters is

Figure 1: On-resistance as a function of operating temperature (a) and gate voltage (b). Symbols represent experimental data. Dashed lines are obtained according to the fitting with the model reported in (1).

reported in Table 1 in the case of four different samples. The model calibration is carried out considering the following ranges for gate voltage and temperature:  $V_{GS} = [-5V, -12V]$ ;  $T = [25^{\circ}C, 125^{\circ}C]$ . The accuracy of the proposed model can be evaluated by considering the maximum and average error, between experimental and fitting data. The maximum error is always <2%, while the average error is found to be <0.4%.

## III. CONDITION MONITORING SYSTEM

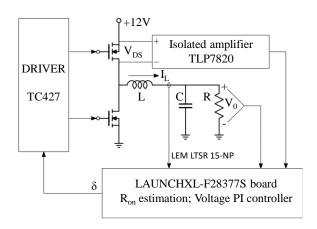

The converter considered for this application is a synchronous buck with switching frequency of 20kHz, a nominal input voltage of 12V and an output voltage of 6V. A schematic representation is reported in Fig. 2. The low-side switch is an n-MOSFET STD35NF06L. In order to monitor the on-resistance of the high-side switch, the circuit includes a current sensor (LEM LTSR 15-NP) in series to the inductor and an optically isolated voltage amplifier (TLP7820) placed between drain and source terminals of the p-MOSFET. A Texas Instruments microcontroller (TMS320F28377S) is used for both implementing the PI (proportional-integral) control of the output voltage and the real-time monitoring of R<sub>on</sub> degradation. Moreover, a type K thermocouple is fixed on the p-MOSFET package in order to estimate the temperature of the device. An electronic load (ARRAY 3723A) is connected at the output of the converter, in order to

Figure 2: Schematic representation of synchronous buck converter and of additional components for condition monitoring.

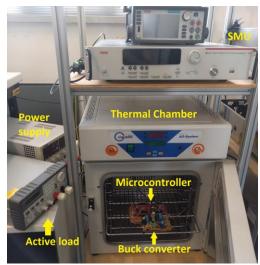

Figure 3: A picture of the experimental setup.

test the circuit under different load conditions. Fig. 3 reports a picture of the experimental setup.

#### IV. EXPERIMENTAL RESULTS

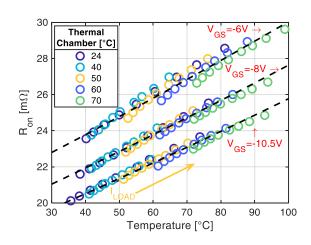

The proper functioning of the condition monitoring system is based on the calibration of the model reported in (1). This calibration must be performed with the p-MOSFET operating in the circuit application, as opposed to the activity reported in section II. The circuit is placed in a thermal chamber, in order to sweep the temperature between 24°C and 70°C. At the same time the output current is varied from 2A to 6A and different gate voltages are considered (-10.5V, -8V, -6V), overall leading to an

Figure 4: On-line monitoring of on-resistance as a function of operating temperature. The thermal chamber operates between 24°C and 70°C. Three different gate voltages are considered: -6V, -8V and -10.5V. The actual temperature is function of the load current, varied between 2A and 6A. Fitting curves (dashed lines) are also reported, with  $R_0$ = 3.424·10<sup>-3</sup> $\Omega$  and k=4.02·10<sup>-6</sup>.

operating temperature comprised between 35°C and 100°C. Fig. 4 reports R<sub>on</sub> dependence on the temperature measured by the thermocouple. The estimated R<sub>on</sub> depends on the output current, because of self-heating effects. However, R<sub>on</sub> is well described by the proposed model (see dashed lines in Fig. 4) and hence it is function of temperature and driving voltage only. Comparing the model and the experimental

data, we found out a maximum and average relative error of 2.6% and 0.7%, respectively. These values could be further reduced if a constant gate voltage was considered. Moreover, an online training algorithm has been implemented on the microcontroller in order to automatically calculate the fitting parameters.

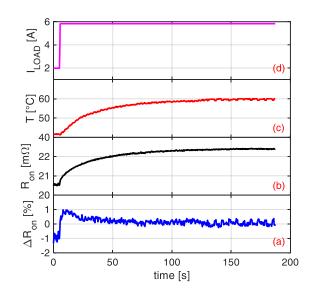

The dynamic behavior of the system is analyzed in Fig. 5. By applying an output current step, an increase of about  $2m\Omega$  is observed on the  $R_{on}$  (see Fig. 5b), because of the temperature increase (see Fig. 5c). On the other hand, the estimated  $R_{on}$  degradation, that is

Figure 5: Real-time monitoring of  $R_{on}$  degradation with respect to the expected value (a), absolute  $R_{on}$  (b), operating temperature (c) and load current (d). An output current step is considered. In spite of the significant increase of temperature and  $R_{on}$ , the estimated  $R_{on}$  degradation is very small ( $\leq 1\%$ ).

the relative change between the measured  $R_{on}$  and the value calculated with (1), is always lower than 1%.

#### V. CONCLUSIONS and FUTURE WORK

In this paper we have proposed an on-line condition monitoring system able to estimate the  $R_{on}$  degradation of a high-side switch. In order to account for the dependence of  $R_{on}$  on the temperature and gate voltage, a simplified semi-empirical model is proposed. This model is based on the calibration of two parameters: a constant resistance contribution  $R_0$  and a technological parameter k. Because of the reduced number of parameters, the calibration process can be implemented on-line. In spite of its simplicity, the accuracy of this model has been verified by means of  $R_{on}$  on-line estimation. The maximum relative error is found to be  $\leq 2.6\%$ . According to the achieved level of accuracy, a degradation in the order of 10% can be easily detected and hence predictive maintenance can be adopted. In the final paper the following work will be reported: details on the implemented circuit and on the accuracy of the adopted sensing components; description of the training algorithm adopted to calibrate the model; deeper analysis of the proposed model; experimental tests with degraded  $R_{on}$ .

## REFERENCES

- [1] S. Yang, D. Xiang, A. Bryant, P. Mawby, L. Ran, and P. Tavner, "Condition Monitoring for Device Reliability in Power Electronic Converters: A Review," *IEEE Transactions on Power Electronics*, vol. 25, no. 11, pp. 2734-2752, 2010.

- [2] M. Held, P. Jacob, G. Nicoletti, P. Scacco, and M.-H. Poech, "Fast power cycling test of IGBT modules in traction application," in *IEEE Proceedings of Second International Conference on Power Electronics and Drive Systems*, 1997.

- [3] L. Reddy GopiReddy, L. M. Tolbert, and B. Ozpineci, "Power Cycle Testing of Power Switches: A Literature Survey," *IEEE Transactions on Power Electronics*, vol. 30, no. 5, pp. 2465-2473, 2015.

- [4] P. Kumar Prasobhu, V. Raveendran, G. Buticchi, and M. Liserre, "Active thermal control of a DC/DC GaN-based converter," in *IEEE Applied Power Electronics Conference and Exposition (APEC)*, 2017, pp. 1146-1152.

- [5] H. Luo, F. Iannuzzo, K. Ma, F. Blaabjerg, W. Li, and X. He, "Active gate driving method for reliability improvement of IGBTs via junction temperature swing reduction," in *IEEE 7th International Symposium on Power Electronics for Distributed Generation Systems* (*PEDG*), 2016.

- [6] D. A. Murdock, J. E. Ramos Torres, J. J. Connors, and R. D. Lorenz, "Active Thermal Control of Power Electronic Modules," *IEEE Transactions on Industry Applications*, vol. 42, no. 2, pp. 552-558, 2006.

- [7] J. Morroni, A. Dolgov, M. Shirazi, R. Zane, and D. Maksimovic, "Online Health Monitoring in Digitally Controlled Power Converters," in *IEEE Power Electronics Specialists Conference*, 2007, pp.112-118.

- [8] P. Ghimire, A. Ruiz de Vega, S. Beczkowski, B. Rannestad, S. Munk-Nielsen, and P. Thogersen, "Improving Power Converter Reliability: Online Monitoring of High-Power IGBT Modules," *IEEE Industrial Electronics Magazine*, vol. 8, no. 3, pp. 40-50, 2014.

- [9] J. M. Anderson, R. W. Cox, and P. O'Connor, "Online Algorithm for Early Stage Fault Detection in IGBT Switches," in *IEEE International Symposium on Diagnostics for Electric Machines, Power Electronics and Drives (SDEMPED)*, 2013.

- [10] S. Takagi, A. Toriumi, M. Iwase, and H. Tango, "On the universality of inversion layer mobility in Si MOSFET's: Part I-effects of substrate impurity concentration", *IEEE Transactions on Electron Devices*, vol. 41, no. 12, pp. 2357-2362, 1994.