International Journal of Research and Innovation in Engineering Technology Volume: 01 Issue: 11

ISSN: 2394 - 4854 Pages: 14 - 26

IJRIET

# PERFORMANCE ANALYSIS OF FIVE LEVEL Z SOURCE NEUTRAL POINT CLAMPED MULTILEVEL INVERTER USING SPWM AND **SVPWM**

M.Anand<sup>1</sup>, S.Manivanan<sup>2</sup>

<sup>1</sup>PG Scholar, Department of Electrical & Electronics Engineering, Bannari Amman Institute of Technology, Erode, Tamilnadu, India <sup>2</sup>Assistant Professor, Department of Electrical & Electronics Engineering, Bannari Amman Institute of Technology, Erode, Tamilnadu, India *E-mail-ID*: <sup>1</sup>anandmeee02@gmail.com, <sup>2</sup>smani1986@gmail.com

# Abstract

The scope of this paper is to reduce the harmonic content and to boost the output voltage by introducing an emerging technique termed as Z-Source multilevel inverter. The Z-Source inverter had overcome many drawbacks in traditional inverters (Voltage source & Current source Inverters). The main advantage of Z- Source inverter is the presence of a shoot through the period (Short circuit) which plays an important role in boosting the voltage. When the number of levels in the output voltage of multilevel inverter is increased then accordingly the harmonic content is also reduced. Normally for a multilevel inverter the output voltage is restricted to the summation of all the input voltage values. To enhance this feature Z-Source is introduced with a multilevel inverter to obtain boosted voltage along with low harmonic distortion. The proposed methodology analysis the Z-Source Neutral point clamped inverter using the Space vector modulation technique with MATLAB/Simulink model and the related parameters is analyzed.

Keywords: Boosted output voltage, Neutral Point Clamped Inverter (NPCI), Reduction in harmonic content, Shoot through state, Space Vector Pulse Width Modulation Technique

# **1. INTRODUCTION**

In recent years, multilevel inverters have drawn significant attention in research and high power applications such as Flexible AC Transmission Systems (FACTS), renewable energy resources, power quality devices, etc. [1]-[4]. Such power converters have been the prime focus of power electronic researches in order to improve their performance, reliable, energy efficient at minimum cost. The important task of multilevel inverter is

producing a sinusoidal voltage waveform from DC sources.

The major advantages of multilevel inverters are:

- 1. High voltage capability with voltage limited devices

- 2. Low harmonic distortion

- 3. Reduced switching losses

- 4. Increased efficiency

- 5. Good electromagnetic compatibility

IJRIET | April 2015, Available @ http://www.ijriet.com

Among several reported topologies, diode-clamped multilevel inverter, cascaded H-bridge multilevel inverter and flying capacitor multilevel inverter are very used [2]. To control these multilevel inverters several carrier-based PWM strategies and space vector PWM (SVPWM) have been reported [11]-[12]. Some other methods such as harmonic optimization attempt to reduce or eliminate harmonic in multilevel inverters [3]. Traditional inverters are known to produce an output voltage that is lower than the DC source voltage. In order to reach boosted voltage with available switching devices Z-Source inverters were invented in 2003 [4]. This structure uses unique X-shaped inductance-capacitance (LC) impedance network that is connected between the DC link and the AC side. There are shoot-through states in Z-source inverter. These states boost voltage and LC impedance network prevent short circuit problems. Recently, new topologies of multilevel Zsource are introduced [7], [13]-[5]-[6]. These structures are used in clean energy harnessing such as photovoltaic (PV) arrays, fuel cells that have low DC voltage [6]. Some papers have attempted to introduce special structures to reduce the number of elements of multilevel Z-source inverter. In this paper, a fivelevel Z-source Neutral Point Clamped inverter is used to introduce the advantages and disadvantages of Space Vector Pulse Width Modulation Technique (SVPWM), Z-Source Inverter.

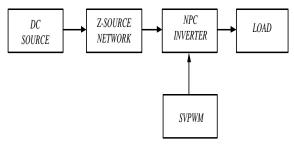

# 1.1 Block Diagram of Proposed Work

Figure: 1 Block Diagram

The DC source may be any renewable DC source like solar photovoltaic or fuel cells. The Z source network exhibits both voltage buck and voltage boost capability. The inverter that considered here is a Neutral Point Clamped Inverter (NPCI) also known

# as Diode Clamped Multilevel Inverter (DCMLI) for three level output voltage. The modulation technique adopted is Space Vector Pulse Width Modulation (SVPWM).

# 2. MULTILEVEL INVERTER

Multilevel inverter obtain a desired output voltage from several levels of input DC voltage Sources. With an increasing number of DC voltage Source, the inverter voltage output will be nearly SINUSOIDAL. In recent years, the multilevel inverters are widely used in high power applications such as large induction motor drives, UPS systems, flexible AC transmission System (FACTS)

The term multilevel began with three level converter .However the elementary concept of multilevel converter to achieve higher power by using semiconductor, switches with several lower voltage DC sources. Capacitors, batteries, and renewable energy voltage sources can be used as the multiple DC sources. The commutation of the power switches aggregates these multiple DC sources in order to achieve high voltage at the output; however the rated voltage of the power semiconductor, switches depends only upon the rating of the DC voltage sources to which they are connected.

The multilevel inverter has several outcomes over a conventional two-level converter that uses high switching frequency pulse width modulation (PWM).The attractive features of a multilevel converter can be briefly summarized as follows.

- Staircase Waveform Quality: Multilevel converters not only can generate the output voltages with very low distortion ,but also can reduce dv/dt therefore the stress Electromagnetic compatibility EMC is reduced

- Common mode (CM) voltage: Multilevel produces smaller CM voltage converter therefore the stress on the motor is reduced

- Input current: Multilevel converter can draw input current with low distortion

- Switching Frequency: MLI will operate in both fundamental and high switching frequency. Note that lower switching frequency usually

IJRIET | April 2015, Available @ http://www.ijriet.com Page:15

means lower switching loss and higher efficiency

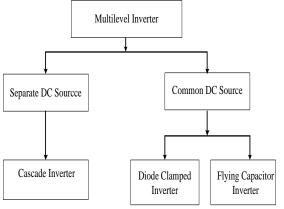

# 2.1 Classification of Multilevel Inverter Based On Source

Figure: 2 Classification of MLI

Three different topologies have been projected for multilevel converters:

- 1. Diode clamped multilevel inverter (DCMLI)

- 2. Flying capacitor multilevel inverter (FCMLI)

- 3. Cascaded multilevel inverter (CMLI)

Several modulation and control strategies have been developed or being used for multilevel converters including the following

- 1. Multilevel sinusoidal pulse width modulation (MSPWM)

- 2. Multilevel selective harmonic elimination

- 3. Space-vector modulation (SVM).

# 2.2 Diode Clamped Multilevel Inverter

The widely used multilevel topology is the diode clamped inverter, in which the diode is used as the clamping device to clamp the DC bus voltage to achieve steps in the output voltage. Each of three phases of the six level inverter shares a common DC bus, which has been subdivided by five capacitors into six levels. The voltage across each capacitor is  $V_{dc}$  and the voltage stress across each switching device is limited to  $V_{dc}$  through the clamping diodes. State condition 1 means the switch is ON and 0

means the switch ids OFF. Each phase has fi9ve complementary switch pairs such that turning on one of the switches of the pair that the other complementary switch be turned OFF. In general the voltage across each capacitor for an N level diode clamped inverter at steady state is  $V_{dc}/n-1$ . In general for a N level diode clamped inverter, for each leg 2(N-1) switching device, (N-1)\*(N-2) clamping diodes and (N-1) DC link capacitors are required

# 2.3 Flying capacitor multilevel inverter

The capacitor clamped inverter alternatively known as flying capacitor was proposed by Maynard and Foch .The flying capacitor involves series connection of capacitor clamped switching cells. The structure of this inverter is similar to that of the diode clamped inverter except that instead of using clamping diodes, the inverter uses capacitors in the place. The circuit topology has a ladder structure of DC side capacitor where the voltage on each capacitor differs from that of the next capacitor. One advantage of the flying capacitor based inverter is that it has redundancies can synthesize on output voltage .Unlike the diode clamped inverter, the flying capacitor inverter does not require all of the switches that are on be in a consecutive series

In addition to (m-1) dc link capacitors, the m-level flying capacitor multilevel inverter will require (m-1) x (m-2)/2 auxiliary capacitor per phase if the voltage rating of the capacitor is identical to that of the main switches.

# 2.4 Cascaded multilevel inverter

In single phase structure of an m-level inverter each separate dc source (SDCS) is connected to a single phase full bridge of H-bridge, inverter .Each inverter level can generate three different voltage output  $+V_{dc}$  0 and  $-V_{dc}$  by connecting the DC source to then AC output by different combination of the four switches  $S_1,S_2,S_3$  and  $S_4$ .The AC output of each of the different full bridge inverter levels are connected in series such that the synthesized voltage waveform is the sum of the inverter output. The number of output phase voltage level m in a cascade inverter is defined by m = 2s+1, where is thefore number of separate DC

sources. Multilevel cascaded inverter has been proposed for such application as static var generation, and interfaces with renewable energy sources and for battery based application. Cascaded inverter is ideal for connecting renewable energy sources with an AC grid, because of the need for separate DC sources, which is the case in application such as photovoltaic or fuel cells

# **3. Z-SOURCE INVERTER**

## 3.1 Introduction

There exist two traditional converters: voltage-source and current-source converters. The ac output voltage is limited below and cannot exceed. The dc-rail voltage has to be greater than the ac input voltage. Therefore, the V-source inverter is a buck inverter for dc-to-ac power conversion and the V-source converter is a boost rectifier for AC-to-DC power conversion An output LC filter is needed for providing a sinusoidal voltage compared with the current-source inverter, which causes additional power loss and control complexity. The dc current source can be a relatively large dc inductor fed by a voltage source such as a battery, fuel-cell stack, diode rectifier. To overcome the problems of the traditional V-source and I-source invertera new concept was developed in year 2002 by Dr. F.Z. Peng. This involves a combination of VSI and CSI to form a cross coupled network of two inductors and two capacitors, known as Impedance Network (Z-source network)

A Z-source inverter is a type of power inverter, a circuit that converts direct current to alternating current. It functions as a buck-boost inverter without making use of DC-DC Converter Bridge due to its unique circuit topology.

# 3.2 Working Principles of Z-Type Inverter

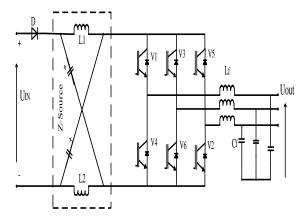

The figure presents a scheme of basic 3-phase Z-inverter. In distinction from VSI and CSI inverters, on DC side of a Z-inverter occurs a D diode and a Z-source of "X" shape, composed of two capacitors C1 and C2 and two chokes L1 and L2. The D diode prevents forbidden reversed current flow.

Figure: 3 Basic Scheme of 3 – phase Z inverter

For this reason application of Z-inverter is possible only where there is no necessity for energy return to *UIN* source, further it is even forbidden in the case of fuel cell or photo-voltaic cell. It should be marked that the same as D diode function can be served by other power electronics systems including ex. Diode rectifier or typical boost-converter".

Source Z serves as power storage and guarantees a double filtration grade at the input of the inverter, and therefore dumping current ripples and voltage pulsation in the DC circuit. Concluding, requirements for chokes and capacitors in Z-source are less restrictive than in VSI or CSI inverters. In a case where chokes L1 and L2 have very low inductance ( $\approx$ 0), the Z-source is created only from parallel connected capacitors C1 and C2. Then Z-inverter simply becomes VSI system and condensers in DC circuit are the only storage for energy and at the same point are a cell for filtration of voltage pulsation. Analogically when capacitors C1 and C2 are of low capacity ( $\approx 0$ ), the Z-source is diminished to two chokes L1 and L2 that are parallel connected, and the Z-inverter system becomes CSI system. Chokes in a DC circuit of CSI system and capacitors in a DC circuit of the VSI system must be of greater inductance and capacity (their dimensions) than in the case of Z-inverter.

Typical 3-phase VSI system can assume eight allowed (permitted) states: six active states (while the exchange of instantaneous power between the load and DC circuit) and two null states (when the load is

shorted by lower or upper group of transistors). Whereas, 3-phase Z-inverter system can assume nine permitted states that is one more than in VSI system

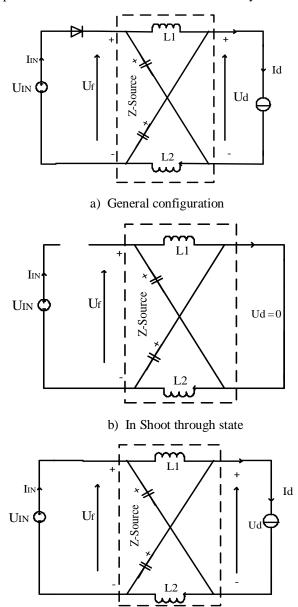

c) In non-shoot through state

#### Figure: 4 Equivalent schemes of Z-inverter

The additional ninth state is the third null state, occurring when the load is being shorted simultaneously by lower and upper group of transistors. This state, is defined as "shoot-through

#### M.Anand, S.Manivanan

state" and may be generated in seven different ways, however equivalent procedures: independently through every branch (3 procedures), simultaneously through two of the branches (3 procedures), simultaneously through all of the three branches (1 procedure). The main, unique characteristic of Zinverter is that shoot-through state permits to raise output voltage, above the supply voltage  $U_{IN}$

Figure 4 describes simple equivalent schemes of Zinverter, examined from the clap site of DC, where a source  $u_d$  shapes inverter bridge  $V_I$ - $V_6$ . In the shootthrough states (Fig.4b) a D diode is polarized reversely and does not conduct the inverter bridge input voltage  $u_d=0$ , and energy stored in capacitors  $C_I$  and  $C_2$  is transferred to the chokes  $L_I$  and  $L_2$ . In nonshoot-through" states, where every combination of the chokes  $V_I$ - $V_6$  that is allowed in VSI system is possible, the D diode conducts, and the voltage  $u_d$ increases stepwise from 0 to its maximum  $u_{d*}$ . Since Z-source is symmetric circuits, when  $C_I=C_2$  and  $L_I=L_2$  and low voltage pulsation  $U_{c1}$  and  $U_{c2}$  due to an impulse period T. It can be recorded as

$$U_{C1} = U_{C2} = U_C, u_{L1} = u_{L2} = u_L$$

(1)

Where

$U_C$  – mean value of voltage in capacitors,

*UL* – instantaneous voltage in chokes.

Considering (1) and equivalent schemes of Z-inverter (Fig.4), voltage  $u_d$  is calculated on the basis of following dependencies

(a) In shoot-through states (Fig.2b) in time  $T_Z$

$$U_L = U_C, u_{f=2} \cdot U_C, u_d = 0$$

(2)

b) In "non-shoot-through" states (Fig.2c) in time  $T_N$

$$U_L = U_{IN} - U_C$$

,

$$U_f = U_{IN}, u_d = U_C - u_L = 2 \cdot U_C - U_{IN}$$

(3)

Where

$$u_f$$

– Z-source input voltage.

If taken into consideration, that in a time period

$T = T_Z + T_{N_1}$  in steady state overage voltage in chokes  $U_L = 0$ , then on the basis of (2) and (3) we obtain

$$U_{L} = \frac{T_{Z} U_{c} + T_{N} (U_{IN} - U_{C})}{T} = 0$$

(4)

And  $U_{C} = U_{d} = U_{IN} \cdot \frac{T_{N}}{T_{N} - T_{Z}} = U_{IN} \frac{1 - D}{1 - 2 D}$

Where

$D=T_{\mathbb{Z}}/T$ -"shoot-through" coefficient, satisfying a condition D < 0.5.

Similar procedure, on the basis (3) and (4) determines the value  $u_{d*}$  of voltage  $u_d$  in "non-shoot-through" states:

$$u_{d}^{*} = U_{C} - u_{L} = U_{IN} \frac{1}{1 - 2.D}$$

(5)

Where  $l/(l-2\cdot D) = T/(T_N - T_Z) \ge l$  - peak factor, determining the value  $u_{d*}$  voltage  $U_{IN}$ .

The value  $u_{d*}$  determines output voltage amplitude  $u_{OUT}$  (max) of the Z-inverter. When applying a sinusoidal PWM algorithm the amplitude equals

$$U_{out(max)} = M \cdot \frac{u_d^*}{2} = \frac{M}{1-2D} \cdot \frac{U_{IN}}{2}$$

(6)

Where M – modulation index, of maximum value limited by inequity  $M \le l-D$ , related to time  $T_Z$  of shoot through states. As it results from the equation (6), Z-inverter output voltage amplitude  $u_{OUT(max)}$ , can be as well lower as higher than in a typical VSI system with sinusoidal PWM,

$$U_{OUT(max)} = M \cdot U_{IN}/2.1$$

#### **4. MODULATION TECHNIQUES**

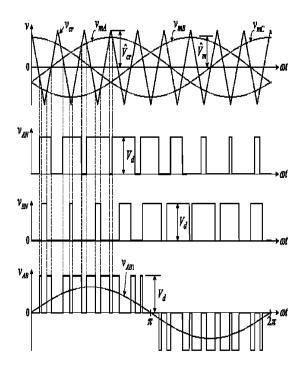

#### 4.1 Sine-Triangle Pulse Width Modulation

The principle of the sinusoidal PWM scheme for the two-level inverter is illustrated in Fig-2, where  $V_{mA}$ ,  $V_{mB}$ , and  $V_{mC}$  are the three-phase sinusoidal modulating waves and Vcr is the triangular carrier wave. The fundamental frequency component in the inverter output voltage can be controlled by amplitude modulation index,

$$ma = Vm / V_{CR}$$

(1)

Where Vm and Vcr are the peak values of the modulating and carrier waves, respectively. The amplitude modulation Index ma is usually adjusted by varying Vm while keeping  $V_{cr}$  fixed. The frequency modulation index is defined by

$$mf = fm / fcr$$

(2)

Where, fm and fcr are the frequencies of the modulating and carrier waves, respectively. The gating signals for conventional two-level inverter using SPWM can be derived as follows. The operation of switches S1 to S6 is determined by comparing the modulating waves with the carrier wave. When  $V_{mA} \ge V_{cr}$ , the upper switch S1 in inverter leg A is turned on. The lower switch S4 operates in a complementary manner and thus is switched off. The resultant inverter terminal voltage VAN, which is the voltage at the phase A terminal with respect to the negative DC-link bus 'N', is equal to the DC voltage Vd. When  $V_{mA} < V_{cr}$ , S4 is on and S1 is off, leading to

VAN = 0. Since the waveform of VAN has only two levels, Vd and 0, the inverter is known as a two level inverter.

Figure: 5 Sinusoidal Pulse Width Modulation Reference and Carrier Wave Comparison

IJRIET | April 2015, Available @ <u>http://www.ijriet.com</u> Page:19

### 4.2. Space Vector Modulation

#### A. Introduction

Space vector modulation (SVM) is an algorithm for the control of pulse width modulation (PWM).<sup>[1]</sup> It is used for the creation of alternating current (AC) waveforms; most commonly to drive 3 phase AC powered motors at varying speeds from DC using multiple class-D amplifiers. There are various variations of SVM that result in different quality and computational requirements. One active area of development is in the reduction of total harmonic distortion (THD) created by the rapid switching inherent to these algorithms.

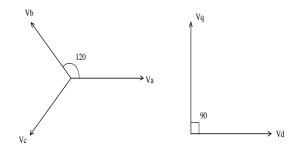

#### **B.** Space Vectors

The technique of the space vector modulation involves the concept of space vector. In any three phase machine, the stator coils are distributed in space in a symmetrical manner, i.e. each coil is placed at 120 degrees with respect to each other. In this method the five phase quantities can be transformed to their equivalent 2-phase quantity either in synchronously rotating frames or stationary reference frame.

# Figure: 6 Three Phase Quantities Transformed into Two Phase

From this 2-phase component, the reference vector magnitude can be found and used for modulating the inverter output. Let the three phase sinusoidal voltage component be,

$$V_{a}=V_{m}\sin \omega t$$

$V_{b}=V_{m}\sin(\omega t-120)$

$V_{c}=V_{m}\sin(\omega t-240)$

#### M.Anand, S.Manivanan

Equating the three phase machine quantities, we get

$$V_a + V_b + V_c = 0 \tag{1}$$

$Vd=-3/2(Vb)+3/2(Vc)=3/2Vmcos\omega t$  (2)

$Vq=Va-Vb/2-Vc/2=3/2Vmsin\omega t$ (3)

Rotating vector,

$$Vref=Vd=Vq=3/2e^{(j\omega t)}$$

(4)

From equation (4) it can be seen that space vector moves with constant angular velocity and constant amplitude. In case of non-sinusoidal quantities, the space vectors will not necessarily move with constant amplitude or constant angular velocity. The output of the inverters, which are usually used in various applications are not perfectly sinusoidal. It contains appreciable amounts of harmonics. So, the space vector of the stator voltages in these cases, if of amplitude Vdc moving in steps and not with a constant angular velocity. In space vector modulation, a reference vector of the stator voltages is generated, which is made to move in the d-q plane in small steps so that it appears to move smoothly, as in the case with a sinusoidal supply. The space vector modulation is based on the space vector representation of the voltages in d-q plane. After the transformation to the two phase quantities, the power as well as the impedance remains unchanged. In space vector modulation we try to generate a voltage reference vector at a point of time and the voltage Vref is sampled which reference vector approximately by a time sequence of five well defined switching state vector nearest to the reference vector. This is done by sampling the switching state vectors in such a way that the total volt seconds generated by these vectors over an interval Ts equals the volt seconds generated by the reference vector Ts.

### C. Design Procedure

Step I

To assume the Peak voltage value (Vm)

Time period (t)

Delta ( $\pi/2$ )

#### Step II

To Calculate the Vref Values

Va\_ref = Vm Sin ( $\omega t + \pi/2$ )

$$Vb\_ref = Vm Sin (\omega t - 2\pi/3 + \pi/2)$$

Vc\_ref = Vm Sin ( $\omega t + 2\pi/3 + \pi/2$ )

#### Step III

(i) To transfer the abc Parameters into dq Parameters

(ii) To find the magnitude and theta values from dq Parameters

Va Vb Vc  $\longrightarrow$  Vq& Vd  $\longrightarrow$  Magnitude & theta

Step IV Identification of Sectors from theta values

Theta  $\longrightarrow$  Sector Identification and ensure each sector, having angle of 60°each (theta1)

$$\beta = int [\theta/60] + 1$$

$$\gamma = rem [\theta/60] = \theta_1$$

### Step V

To find the Magnitude of Varef and VBref & Theta 1

$$V\alpha = Vm \operatorname{Cos} \left[\theta 1 * \pi/180\right]$$

$$V\beta = Vm \operatorname{Sin} \left[\theta 1 * \pi/180\right]$$

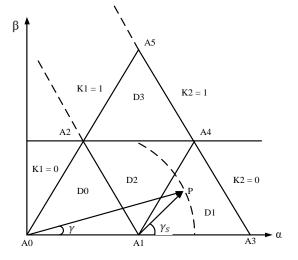

#### Step VI

Identification of Sectors by using K1 and K2 values

$$K_{1} = int \left[ \frac{V_{\alpha} + \frac{V_{\beta}}{\sqrt{3}}}{K_{2}} = int \left[ \frac{2V_{\beta}}{\sqrt{3}} \right] K_{1} \& K_{2} are integers$$

#### Step VII

To find

$$V_{\alpha i}$$

and  $V_{\beta i}$

$V_{\alpha i} = V\alpha - K_1 + 0.5K_2$

$V_{\beta i} = V\beta - K_2 h = V\beta - \frac{\sqrt{3}K_2}{2}$

$(h = \sqrt{3}/2)$

M.Anand, S.Manivanan

# Step VIII

To find the location of Reference vector P

Case I

If  $\sqrt{3} V_{\alpha i} \ge V_{\beta i}$  or  $\sqrt{3} V_{\alpha i} \le V_{\beta i}$

1. True means P is at  $\Delta 1$

2. False means P is at  $\Delta 2$

## Step IX

To find out the type of triangle (Type I or Type 2)

(i) P at  $\Delta 2$  common for type 2 triangle

$$V_{\alpha 0}^{S} = 0.5 - V_{\alpha i}$$

$$V_{\beta 0}^{S} = \frac{\sqrt{3}}{2} - V_{\beta i}$$

(ii) P at  $\Delta 1$  common for type 1 triangle

$$V_{\alpha 0}^{S} = V_{\alpha i}$$

$$V_{\beta 0}^{S} = V_{\beta i}$$

Figure: 7 Determination of Triangle

#### Step X

Triangle number calculation

For type I triangle

$$\Delta \mathbf{j} = \mathbf{K_1^2} + 2\mathbf{K_2}$$

International Journal of Research and Innovation in Engineering Technology Volume: 01 Issue: 11

ISSN: 2394 – 4854 Pages: 14 – 26

For type II triangle

$$\Delta \mathbf{j} = \mathbf{K_1^2} + 2\mathbf{K_2} + 1$$

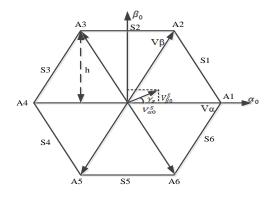

Step XI

Determination of ON time by two level SVPWM unit

Figure: 8 Space Vector Representation of Two Level Inverter

$$V\alpha = (1,0)$$

$$V\beta = (0.5, h)$$

$$V^{s} = (V^{s}_{\alpha 0} V^{s}_{\beta 0})$$

Space vector diagram for two level inverter by using this diagram the volt second balance is given by

$$V^s T_s = V_a t_a + V_b t_b$$

Time balance is given by

$$T_{\rm S} = t_a + t_b + t_0$$

In  $\alpha_0 - \beta_0$  axis

$$V_{\alpha 0}^{S} T_{S} = 1 \cdot t_{a} + 0.5 t_{b}$$

$$= t_{a} + 0.5 t_{b}$$

$$V_{\beta 0}^{S} T_{S} = h \cdot t_{b} + 0 \cdot t_{a}$$

$V\alpha = (1,0)$

= h.**t<sub>b</mark>**</sub>

Because

$$V\beta = (0.5, h)$$

M.Anand, S.Manivanan

$$V^s = (V^s_{\alpha 0} \, V^s_{\beta 0})$$

Calculation of ON time

$$V_{\alpha 0}^{S} T_{S} = t_{a} + 0.5 t_{b}$$

$$V_{\beta 0}^{S} T_{S} = h.t_{b}$$

$$t_b = \frac{V_{\beta 0}^s T_s}{h}$$

Therefore

$$t_a = V_{\alpha 0}^S T_S - 0.5 \frac{V_{\beta 0}^S T_S}{h}$$

$$=T_{s}\left\{V_{\alpha0}^{s}-\frac{V_{\beta0}^{s}T_{s}}{2h}\right\}$$

$t_0 = T_s - t_a - t_b$

Step XII

Generation of gating signals

D.Circuit Diagram of Proposed System

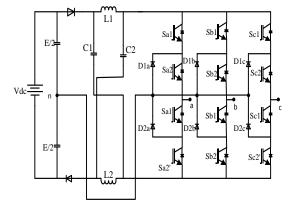

Figure: 9 Proposed Circuit Diagram of ZNPC

The circuit diagram of proposed system shows five level Z-source NPC inverter where the only difference compared with the traditional inverters is the inserted Z-source network and a passive diode D between DC supply and inverter circuitry. The twoport network is built using a split inductor and two shunt capacitors, whose X-shape structure allows switching from any phase-leg to turn ON simultaneously with the input diode D naturally reverse-biased to create a shoot through a state

without damaging the semiconductor device due to natural property of current production by inductors.

# 5. RESULTS AND DISCUSSIONS

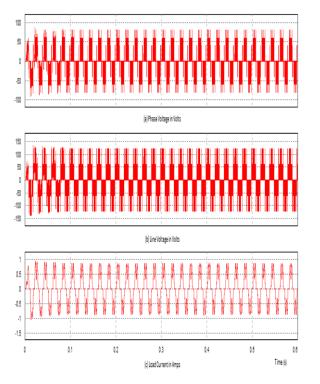

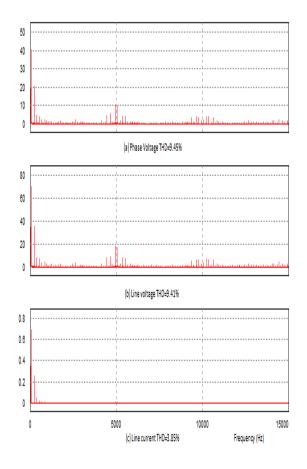

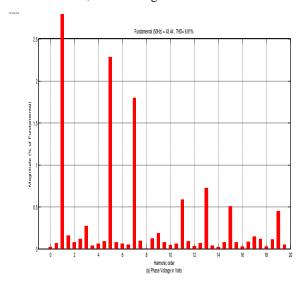

Here the Z source Neutral Point Clamped Inverter using Sinusoidal Pulse Width Modulation Technique is implemented. The performance parameters like Phase voltage, Line voltage Load current and THD are analyzed using PSIM and the results are given below.

Figure: 10 Simulated Output of Phase Voltage, Line voltage and Load Current

# Figure: 11 THD Analysis of Phase Voltage, Line voltage, Line current

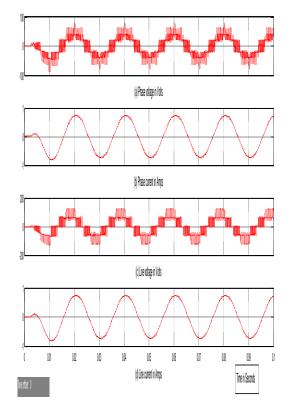

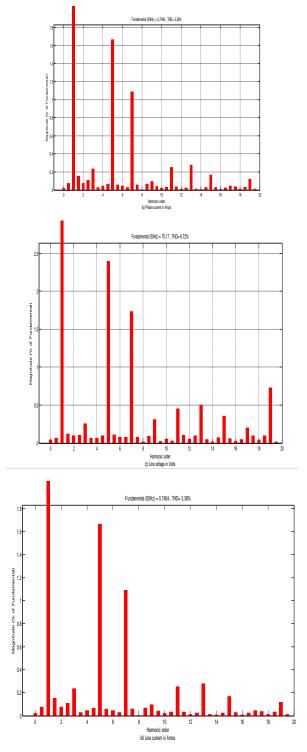

Here the Z source Neutral Point Clamped Inverter using Space Vector Pulse Width Modulation Technique is implemented. The performance parameters like Phase voltage, Line voltage Load current and THD are analyzed using MATLAB Simulink and the results are given below.

Figure: 12 Simulated Output of Phase voltage, Phase current, Line Voltage and Line current

Figure: 13 THD analysis of Phase voltage, Phase current, Line voltage and Line current

IJRIET | April 2015, Available @ <u>http://www.ijriet.com</u> Page:24

Comparison of SPWM and SVPWM techniques by analyzing various parameters.

| S.No | Performance<br>Analysis<br>Parameters | Sinusoidal<br>PWM<br>Technique | Space<br>Vector<br>PWM<br>Technique |

|------|---------------------------------------|--------------------------------|-------------------------------------|

| 1    | Phase<br>Voltage<br>Magnitude         | 62                             | 72                                  |

| 2    | Phase<br>Current<br>Magnitude         | 0.9                            | 0.72                                |

| 3    | Line Voltage                          | 107                            | 120                                 |

| 4    | Line Current                          | 0.9                            | 0.75                                |

| 5    | Phase<br>voltage THD                  | 9.45%                          | 6.81%                               |

| 6    | Phase<br>Current THD                  | 3.85%                          | 3.36%                               |

| 7    | Line Voltage<br>THD                   | 9.41%                          | 6.72%                               |

| 8    | Line Current<br>THD                   | 3.85%                          | 3.36%                               |

# Table: 1 Comparison of SPWM and SVPWM Techniques

From the above analysis, we conclude that Space Vector PWM technique is more superior than the Sinusoidal PWM technique for multilevel inverter in various industrial applications.

# 6. CONCLUSION

This paper presents the design of a Z-source NPC inverter that can perform buck-boost DC-AC energy inversion. Under special operations with respect to the partial DC-link shoot-through, which profitably appear in the operation of Z-source NPC inverter, the Z-source network shows much different operational principles and boost characteristics. Modulation wise, the proposed inverter can be controlled using Space Vector Modulation techniques with a slight

#### M.Anand, S.Manivanan

modification of three-phase references. The theoretical findings, together with the practicality of the inverter, have been analyzed using PSIM and MATLAB/Simulink model under both normal and voltage boost conditions.

# References

- Rahim, N.A.; Selvaraj, J., "Multistring Five-Level Inverter With Novel PWM Control Scheme for PV Application," Industrial Electronics, IEEE Transactions on , vol. 57, pp. 2111 – 2123, 2010.

- [2] McGrath, B.P.; Holmes, D.G.; "Multicarrier PWM Strategies for Multilevel Inverters," Industrial Electronics, IEEE Trans, Vol. 49, pp. 858-867, 2002.

- [3] Fang ZhengPeng;" Z-Source Inverter," Industry Applications, IEEE Transactions on ,Vol.39, Issue.2, pp. 504 – 510, 2003.

- Poh Chiang Loh; Feng Gao; Blaabjerg, F.; Shi Yun Charmaine Feng; Kong Ngai Jamies Soon , "Pulsewidth- Modulated Z-Source Neutral-Point-Clamped Inverter," Industry Applications, IEEE Transactions on, vol. 43, pp. 1295-1308, 2007.

- [5] Fang ZhengPeng and Yi Huang Michigan, "Z-Source Inverter for Power Conditioning and Utility Interface of Renewable Energy Sources," IEEE Trans, Vol. 23, no. 4, 2004.

- [6] Gao, F.; Loh, P.C.; Blaabjerg, F.; Teodorescu, R.; Vilathgamuwa, D.M. "Five-level Z-source diode-clamped inverter," Power Electronics, IET, vol. 3, pp. 500-510,2010.

- Banaei, M.R. Dehghanzadeh, A.R. "DVR

Based Cascaded Multilevel Z-Source

Inverter," Power and Energy (PECon), 2010

IEEE International Conference on, pp. 51-56, Nov. 29 2010-Dec. 1 2010.

- [8] Khomfoi, S.; Praisuwanna, N.; Tolbert, L.M.,"

A Hybrid Cascaded Multilevel Inverter Application for Renewable Energy Resources Including a Reconfiguration Technique"

- [9] Energy Conversion Congress and Exposition (ECCE), 2010 IEEE, pp. 3998 – 4005, 2010.

- [10] Waware, M.; Agarwal, P., "Use of Multilevel Inverter for Elimination of Harmonics in High Voltage Systems," Computer and Automation Engineering (ICCAE), 2010 The 2nd International Conference on , vol. 2, pp. 311 – 315, 2010.

- [11] Peng, F.Z.; Wei Qian; Dong Cao; "Recent Advances in Multilevel Converter/Inverter Topologies and Applications," Power Electronics Conference (IPEC), 2010 International ,pp. 492-501, 2010.

- [12] M. G. HosseiniAghdam, S. H. Fathi, G. B. Gharehpetian, "Elimination of Harmonics in a Multi-level Inverter with Unequal DC Sources Using the Homotopy Algorithm," 2007 IEEE International Symposium on Industrial Electronics(IEEE ISIE 2007), Vigo, Spain, pp.578-583, June 4-7,2007

- [13] HosseiniAghdam, M.G.; Fathi, S.H.; Gharehpetian, G.B.; "Comparison of OMTHD and OHSW harmonic Optimization Techniques in Multi-Level Voltage-Source Inverter with non-equal DC Sources," Power Electronics, 2007. ICPE '07. 7th Internatonal Conference on, pp. 587-591, 2007.

- [14] Ding Li; Feng Gao; Poh Chiang Loh; Miao Zhu; Blaabjerg, F. "Cascaded Impedance Networks for NPC Inverter," IPEC, 2010 Conference Proceedings, pp. 1176- 1180, 2010.

# A Brief Author(s) Biography

**M.Anand** completed his Bachelor Degree in the year of 2013 and finished his research in Wireless Monitoring System for Transformer with the help of zigbee module. Currently he is pursuing his Master Degree in Power Electronics and Drives, with research in Multilevel Inverter Modulated by Space Vector Modulation Technique for various Application. He has published two papers in International Journals and organized National Level Student Workshop in Industrial Automation.

**S.Manivanan** completed his Master Degree in Power Electronics and Drives in the year of 2010 and started his research in Matrix Converter. His research includes Various Configuration of Multilevel Inverter with Different types of Modulation Technique. He has presented papers in National Conferences and published 7 Papers in various International Journals. He has attended AICTE sponsored Faculty Development Program and also attended an ISTE Workshop organized by IIT Kharagpur.