## Louisiana Tech University Louisiana Tech Digital Commons

**Doctoral Dissertations**

Graduate School

Spring 1999

# A systematic integration of register allocation and instruction scheduling

Yukong Zhang Louisiana Tech University

Follow this and additional works at: https://digitalcommons.latech.edu/dissertations Part of the <u>Other Computer Sciences Commons</u>

Recommended Citation

Zhang, Yukong, "" (1999). Dissertation. 705. https://digitalcommons.latech.edu/dissertations/705

This Dissertation is brought to you for free and open access by the Graduate School at Louisiana Tech Digital Commons. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of Louisiana Tech Digital Commons. For more information, please contact digitalcommons@latech.edu.

#### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality  $6^{\circ} \times 9^{\circ}$  black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor MI 48106-1346 USA 313/761-4700 800/521-0600

# A SYSTEMATIC INTEGRATION OF REGISTER ALLOCATION AND INSTRUCTION SCHEDULING

Yukong Zhang, M.S.

A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

#### COLLEGE OF ENGINEERING AND SCIENCE LOUISIANA TECH UNIVERSITY

May 1999

#### **UMI Number: 9926395**

UMI Microform 9926395 Copyright 1999, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

#### LOUISIANA TECH UNIVERSITY

#### THE GRADUATE SCHOOL

May 17, 1999 Date

We hereby that the dissertation supervision recommend prepared under our by Yukong Zhang Scheduling entitled A Systematic Integration of Register Allocation and Instruction of fulfillment of the requirements for the Degree be accepted in partial Doctor of Philosophy

Let Unit he Supervisor of Thesis Research

Head of Department

Applied Computational Analysis and Modeling (ACAM)

Department

Recommendation concurred in:

Advisory Committee

assar

Approved:

Director of Graduate Studi

f the College

Approved:

Director of Graduate School

GS Form 13 2/97

#### ABSTRACT

In order to achieve high performance, processor architecture has become more and more complicated. As a result, compiler-time optimizations have become more and more important for the effective use of a complex processor. One of the promising compilertime optimizations is the integration of register allocation and instruction scheduling based on register-reuse chains. In the previous approach, however, the generation of register-reuse chains was not completely systematic and consequently created many unnecessary dependencies that restrict instruction scheduling.

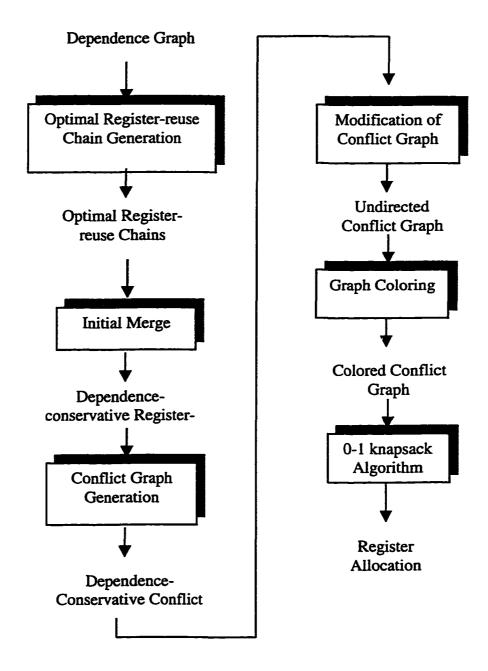

This research proposes a new register allocation technique based on a systematic generation of register-reuse chains. The first phase of the proposed technique is to generate register-reuse chains that are optimal in the sense that no additional dependencies are created. Thus, register allocation can be done without restricting instruction scheduling. For the case when the optimal register-reuse chains require more than available registers, the second phase reduces the number of required registers by merging the register-reuse chains. A heuristic is developed for the second phase in order to reduce the additional dependencies created by merging chains. The first step of the second phase is to derive a conflict graph in which each node corresponds to a register-reuse chain, while an edge represents where the corresponding two chains cannot be merged. Applying a graph-coloring algorithm to the conflict graph, the number of chains can be effectively reduced. The final step of the second phase is to reun the 0-1 knapsack

algorithm to make the number of chains exactly the same as the number of available registers. The proposed register allocation is implemented in LCC (Local C Compiler). An instruction scheduler is also implemented in LCC and then integrated with the proposed register allocator. Evaluation results show that the proposed algorithm and heuristic effectively reduce the number of necessary registers.

# **TABLE OF CONTENTS**

| ABSTRACT                        | iii |

|---------------------------------|-----|

| LIST OF FIGURES                 |     |

| ACKNOWLEDGMENTS                 | ix  |

| CHAPTER ONE                     |     |

| INTRODUCTION                    |     |

| 1.1 Statement of Problem        |     |

| 1.2 Research Objectives         |     |

| 1.3 Research Methodology        |     |

| 1.4 Outline of the Dissertation |     |

### CHAPTER TWO

| BACKGROUND                                   | 7  |

|----------------------------------------------|----|

| 2.1 Compiler Optimization Techniques         | 7  |

| 2.1.1 Data Dependence Analysis               | 7  |

| 2.1.2 Instruction Scheduling                 | 9  |

| 2.1.3 Register Allocation                    | 10 |

| 2.1.4 Live Range Analysis                    | 11 |

| 2.2 ARM7T (Advanced RISC Machines) Processor | 16 |

| 2.3 Local C Compiler (LCC)                   | 16 |

#### **CHAPTER THREE**

| DEPENDENCE ANALYSIS AND INSTRUCTION SCHEDULING | 19 |

|------------------------------------------------|----|

| 3.1 Structure of Optimizing LCC Compiler       | 19 |

| 3.2 Dependence Analysis                        |    |

| 3.2.1 True Dependence                          |    |

| 3.2.2 Anti-Dependence                          | 22 |

| 3.2.3 Output Dependence                        | 25 |

| 3.2.4 Adjustment of Dependencies               | 27 |

| 3.3 Instruction Scheduling                     |    |

#### **CHAPTER FOUR**

| REGISTER ALLOCATION                                                       | 46 |

|---------------------------------------------------------------------------|----|

| 4.1 Background                                                            |    |

| 4.2 Register Allocation Based on Register-Reuse Chains                    | 49 |

| 4.2.1 Definitions                                                         | 49 |

| 4.2.2 Previous Approach                                                   | 51 |

| 4.2.3 Possible Improvements                                               | 55 |

| 4.3 Register-Reuse Chain and Dependence Analysis                          | 57 |

| 4.3.1 Generation of Dependence Due to Register Allocation                 | 58 |

| 4.3.2 Generation of Register-Reuse Chains without Additional Dependencies | 62 |

| 4.4 Register-Reuse Chain Merging                                          | 68 |

| 4.4.1 Criterion of Chain Merging                                          | 69 |

| 4.4.2 Heuristics for Chain Merging                                        | 76 |

#### **CHAPTER FIVE**

| SYSTEMATIC MERGE OF REGISTER-REUSE CHAINS                             | 80  |

|-----------------------------------------------------------------------|-----|

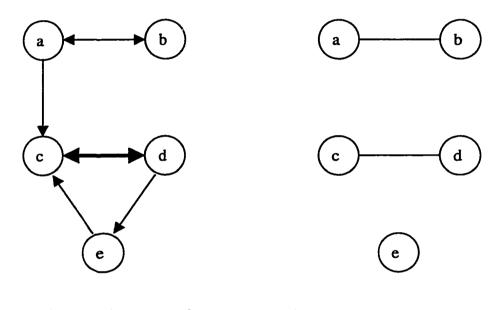

| 5.1 The Conflict Graph                                                | 80  |

| 5.2 Merging Algorithm                                                 |     |

| 5.3 Register Allocation Algorithm Based on Coloring of Conflict Graph |     |

| CHAPTER SIX                                                           |     |

| CONCLUSIONS                                                           | 112 |

| REFERENCES | <br> | <br>114 |

|------------|------|---------|

|            |      |         |

# LIST OF FIGURES

Page

Figures

|      |                                                                                    | _    |

|------|------------------------------------------------------------------------------------|------|

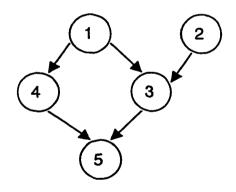

| 2.1  | An example data dependence graph                                                   |      |

| 2.2  | An example of paralleled code                                                      |      |

| 2.3  | Example for register allocation                                                    |      |

| 2.4  | Live range analysis of variables                                                   |      |

| 2.5  | Effect of instruction scheduling on register allocation                            |      |

| 2.6  | Data dependence graph                                                              |      |

| 2.7  | Structure of Local C Compiler (LCC)                                                |      |

| 3.1  | The structure of the new optimizing compiler                                       |      |

| 3.2  | A single AST and the corresponding dependence graph                                |      |

| 3.3  | Multiple ASTs and the dependence graph                                             |      |

| 3.4  | Multiple ASTs and the anti-dependence graph                                        |      |

| 3.5  | Multiple ASTs and the output dependence graph                                      |      |

| 3.6  | Adjustment of anti-dependence after register allocation                            |      |

| 3.7  | Adjustment of output dependence after register allocation                          |      |

| 3.8  | Procedure for adjustments of dependence                                            |      |

| 3.9  | A schedule example for nodes shown in Figure 3.3                                   |      |

|      | Structure of the instruction scheduler                                             |      |

|      | An example of scheduled nodes                                                      |      |

|      | A basic structure of the scheduler                                                 |      |

|      | Function for including dependent nodes in the queue                                |      |

|      | Function for including false dependent nodes in the queue                          |      |

|      | Function for inserting a node in the queue                                         |      |

|      | Function for inserting Xnode in the queue                                          |      |

|      | Function for putting a node in the queue                                           |      |

|      | Function for selecting a node from a queue                                         |      |

| 3.19 | Function for calling VLIW scheduling                                               |      |

| 4.1  | Examples of partial ordering and linear partial ordering                           |      |

| 4.2  | Register allocation example given in [8]                                           | . 52 |

| 4.3  | Creation of dependencies for register allocation                                   | . 55 |

|      | Example of dependence graph                                                        |      |

| 4.5  | Example C code and corresponding assembly code                                     | . 59 |

| 4.6  | C code and assembly code after rescheduling                                        | . 59 |

| 4.7  | Data dependence graph                                                              | . 60 |

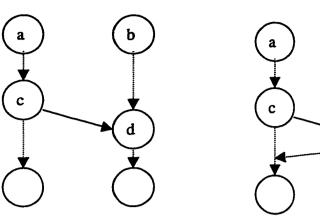

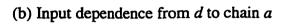

| 4.8  | An example for additional dependence forcing simultaneous execution of $c$ and $d$ | 62   |

|      | Resulting register reuse chains                                                    |      |

| 4.10 | Register reuse chain generation algorithm                                          | . 67 |

| 4.11 | Algorithm for calculation of the number of schedules                       | 71    |

|------|----------------------------------------------------------------------------|-------|

| 4.12 | An example of calculation of the number of schedules                       | 72    |

| 4.13 | Register-reuse chain merge algorithm                                       | 78    |

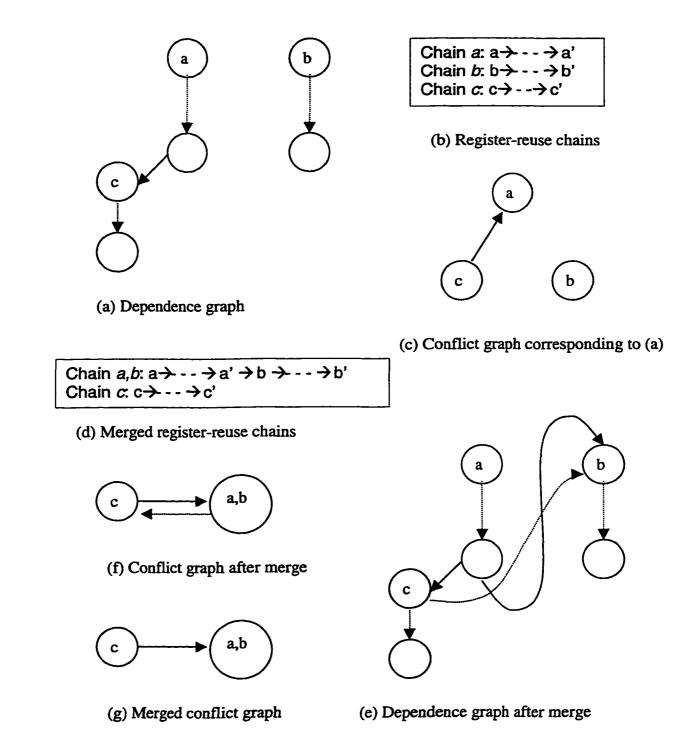

| 5.1  | Dependence graph and conflict graph                                        | 82    |

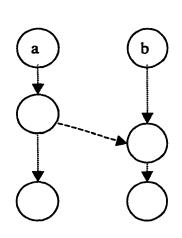

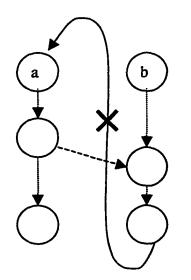

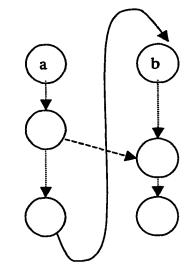

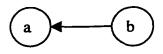

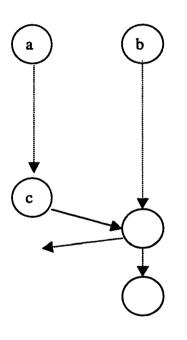

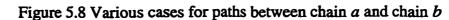

| 5.2  | No dependence between register-reuse chains                                | 85    |

| 5.3  | Unidirectional path from chain a to chain b                                | 86    |

| 5.4  | Chain b is adjacent to chain a                                             | 88    |

| 5.5  | Bidirectional path from chain a to chain b                                 |       |

| 5.6  | A path from chain a crosses a successor of chain b                         | 91    |

| 5.7  | A path from chain a crosses a successor of an intermediate node of chain b | 92    |

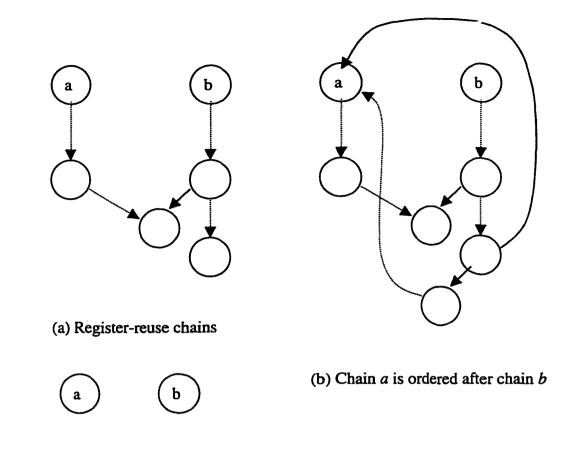

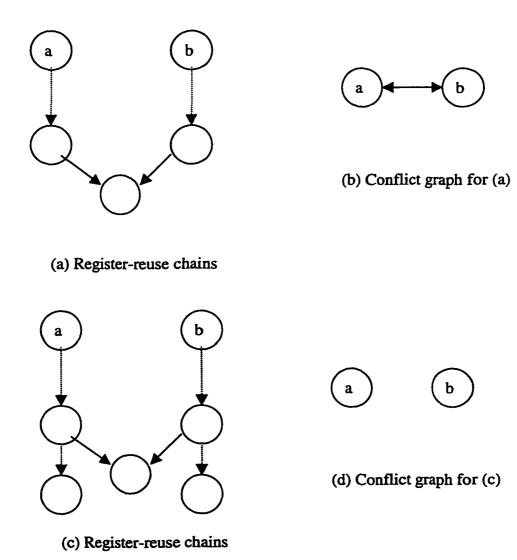

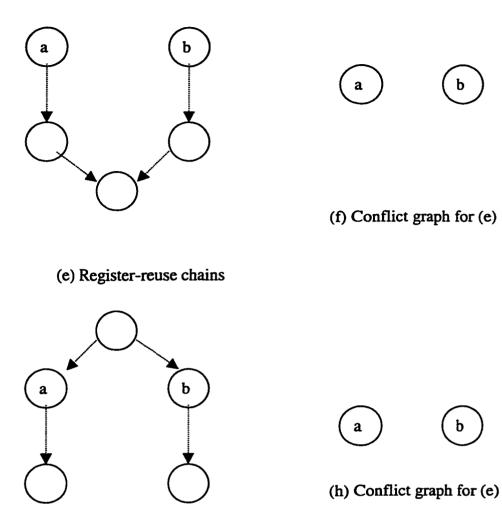

| 5.8  | Various cases for paths between chain a and chain b                        | 93    |

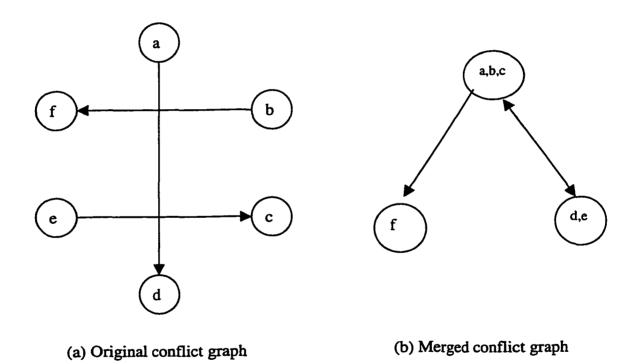

| 5.9  | Conflict graph after chain merge                                           | 97    |

| 5.10 | Merged conflict graph                                                      | 98    |

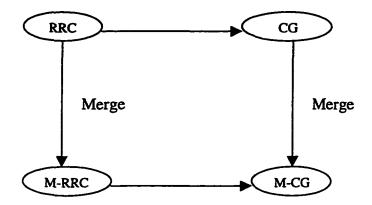

| 5.11 | Generation of merged conflict graph                                        | . 100 |

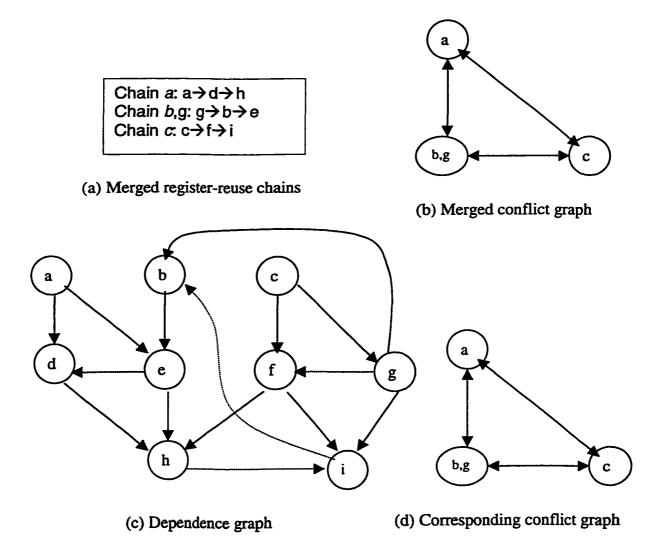

| 5.12 | Dependence-conservative register-reuse chains                              | . 101 |

| 5.13 | Chain merge based on Theorem 5.1 and Corollary 5.1                         | . 103 |

| 5.14 | Generation of the merged conflict graph                                    | . 104 |

| 5.15 | Avoidance of the case as shown in Figure 5.9                               | . 106 |

| 5.16 | Conversion of a directed conflict graph into an undirected conflict graph  | . 108 |

| 5.17 | Complete procedure for register allocation                                 | . 111 |

.

#### ACKNOWLEDGEMENTS

At this moment, the author wishes to express his gratitude to all the people who contributed to the completion of this dissertation.

First of all, I would like to express my deepest appreciation and thanks to Dr. Hyuk Jae Lee, my research advisor, for his numerous hours helping me to condense my thoughts and for his invaluable guidance to carry me through difficult times throughout my dissertation research at Louisiana Tech University.

I would like to thank Dr. Richard Greechie, Dr. Barry Kurtz, Dr. Weizhong Dai, and Dr. Raja Nassar for taking time to read my dissertation and providing me with very helpful suggestions.

I also owe a special thank to Dr. Greechie for his countless assistance throughout my study in ACAM program at Louisiana Tech University.

I wish to thank Ms. Frances Welch at College of Engineering and Science for her kindness and assistance whenever needed during my graduate study at Louisiana Tech University.

Many thanks go to my fellow students, Sanqiang Li, Xiaorong Ma, and Danny Parker for their helpful suggestions to this research and friendship.

Finally, special thanks go to my wife Xiaochun and my daughter Geran whose understanding, support, and love encourage me to complete this dissertation.

ix

#### **CHAPTER ONE**

#### INTRODUCTION

#### **1.1 Statement of Problem**

Embedded systems are application-specific systems that are designed with microprocessors. These systems are employed for applications other than general-purpose computing. Examples of these systems include cellular phones, automobile enginecontrol units, printers, fax machines, and set top-boxes etc. The major components of a typical embedded system are a programmable processor, a program ROM on which software is stored, and optionally application-specific hardware. A key characteristic of an embedded system is that the software is part of the system components. The software component of these systems is referred to as the *embedded software*, while the microprocessor is referred to as the *embedded processor* on which the software is executed.

Embedded systems have some unique characteristics compared to generalpurpose computing systems. Due to their high-volume market demand, the manufacturing of embedded systems is very cost-sensitive. Due to time-to-market requirements, a short design cycle is desirable. In addition, many applications such as cellular phones are battery-driven, so the low power consumption requirement must be met.

With recent advancements in semiconductor processing techniques, the integration of all the system components on a single chip has become possible. For a

system that is composed of hardware and software, a hardware-software co-design approach has been used by the designers of the systems [20, 40, 44]. With this design methodology, the designers first determine which part of the functionality of the systems will be implemented in hardware and which part in software. Then the designed system will be simulated and evaluated with a co-design simulator. If the simulation results do not satisfy the design requirements -- such as power consumption, cost, and real-time constraints, etc. -- the designers may repartition the hardware and software of the system and then repeat simulation and evaluation of the new design until the design requirements and specifications are satisfied.

Given a fixed size of die on which all the components of a system are integrated, a certain amount of silicon area is dedicated to the program ROM, which is used to store the embedded software. Thus the program ROM area becomes limited. It is the designer's goal to generate high-density software code in order to fit the software code within the program ROM and to reduce software code size as much as possible, because the cost of a system increases non-linearly with the die size. In addition, many applications have strict real-time performance requirements. Producing high-performance code for embedded systems is a necessity.

In addition to code size and performance, there is another important constraint for embedded systems: power consumption. Generally, there are two main factors affecting the power consumption of embedded systems. The first factor is performance of the system. It is observed that the code that is executed faster consumes less power. The other factor is related to the instruction execution order of a given application code. An optimal schedule of a sequence of instructions may reduce power consumption significantly.

Traditionally, in order to guarantee that the code size and performance requirements of embedded systems are satisfied, the software code usually is written manually in assembly languages. Although the assembly programming of small applications may be not relatively complicated, as the complexity of applications grows, manually programming in assembly languages becomes impractical, tedious, and errorprone. In addition, in order to meet short time-to-market cycle requirements, more efficient methods are desirable. Recently, most embedded software codes are written in a high-level language, such as C or C++, and use compiler technology to translate the highlevel languages into assembly code. This is because programming in the high-level languages significantly reduces the cost and time of the software development. Furthermore, relatively less effort is required to maintain the code written in high-level languages. However, the code generated by traditional compiler techniques generally cannot satisfy the code size, performance, and power consumption requirements of embedded systems at the same time. The major reason is that traditional compiler optimization techniques classically focus on the code execution speed rather than code density and power consumption. Thus the new compiler-time optimization techniques become very important for code size, performance, and power consumption of embedded systems, although the traditional compiler optimization techniques are still effective for embedded systems.

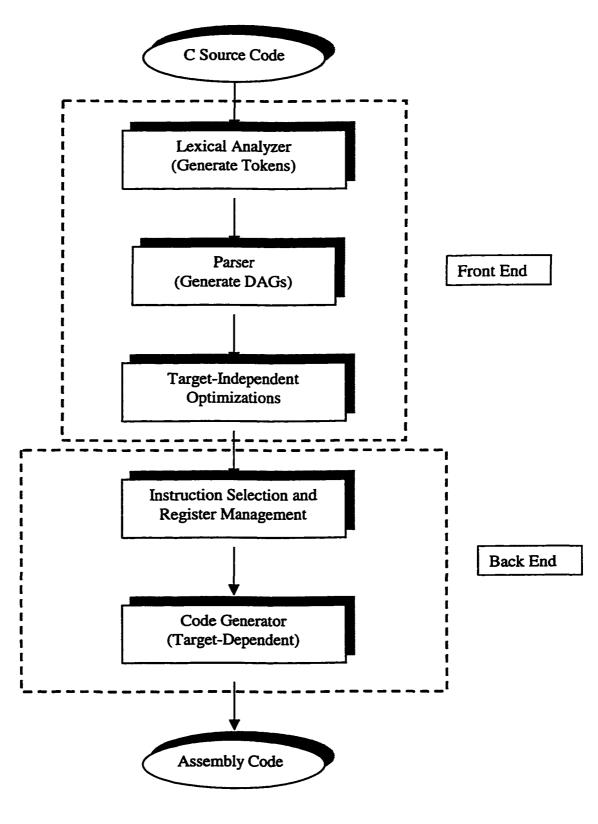

Basically, the fundamental structure of a compiler can be classified into two parts:

- The *front-end*, which takes as input a code written in high-level languages and generates an intermediate representation of the input code, which is independent of the target machine.

- The *back-end*, which generates target-machine-dependent assembly code based on the intermediate representation. In particular, two important phases are performed in the back-end: instruction scheduling and register allocation. The phase of instruction scheduling determines instruction execution order and the register allocation phase determines the registers that will be used by each instruction.

To generate high-quality code for embedded systems in terms of code density, performance, and power consumption, this research will focus on these two compiler optimization techniques: instruction scheduling and register allocation.

#### **1.2 Research Objectives**

As mentioned in the previous section, instruction scheduling determines the execution order of each of the instructions of an application code. The instructions can be scheduled in favor of our optimization goals, such as efficient use of registers and power consumption, without affecting the correctness of the code execution. Register allocation determines which registers are used for each of the instructions. Since registers are the limited temporary storage resource in a processor, which is used to store the values of variables and temporary variables of instructions, efficient use of registers is of vital importance for high-quality code generation. These two compiler optimization techniques often affect each other. If register allocation is performed first, additional dependencies between instructions are introduced due to temporary sharing of registers. It limits the flexibility of the scheduling of instructions. If instruction scheduling is

performed first, it may create a schedule that demands more registers than available. Consequently, the benefit from instruction scheduling will be limited. The objectives of this thesis can be summarized as follows:

- Design an algorithm/heuristic to integrate instruction scheduling and register allocation. This algorithm/heuristic will minimize the number of needed registers and additional constraints for instruction scheduler due to register allocation.

- Apply the algorithm/heuristic to compiler code generation for embedded systems aiming to meet requirements for code size, high performance, and power reduction.

- Evaluate the effectiveness of the proposed algorithm.

#### 1.3 Research Methodology

In this research, ARM7T (Advanced RISC Machines), one of the ARM series of processors, has been chosen as the target processor. The characteristics of ARM processors are high performance, low cost, and low power consumption. Each ARM7T instruction is 32-bit long. The Local C Compiler (LCC), originally developed by Fraser and Hanson [15], is used as the compiler frame work tool with which the compiler optimization techniques developed in this research will be incorporated. To achieve the objectives of this research, a data dependence analyzer and an instruction scheduler are developed first. A new register allocator is developed based on a systematic generation of register-reuse chains. Based on the analysis of the interaction between instruction scheduling and register allocation, an algorithm/heuristic that integrates instruction scheduling and register allocation is developed.

#### **1.4 Outline of the Dissertation**

This dissertation is divided into six chapters. Chapter 1 explains the research objectives and the methodology used to achieve these objectives. Chapter 2 gives the background related to this research including previous research on instruction scheduling and register allocation. This chapter also briefly describes ARM series architecture and LCC structure.

Chapter 3 presents the development of the data dependence analysis and instruction scheduler. Chapter 4 describes the integration algorithms of instruction scheduling and register allocation. It includes register-reuse chain generation, register-reuse chain merging, and merging criteria.

Chapter 5 presents a systematic approach to merge register-reuse chains that generated by the algorithms described in Chapter 4 when the number of chains is greater than the number of available registers.

Chapter 6 summarizes the research.

#### **CHAPTER TWO**

#### BACKGROUND

Chapter 2 provides the background on instruction scheduling and register allocation as well as the integration of both techniques. This chapter also gives a brief description of ARM architecture and Local C Compiler (LCC) structure.

#### **2.1 Compiler Optimization Techniques**

Instruction scheduling and register allocation are very important compiler optimization techniques for embedded systems. This section is intended to give background descriptions on these techniques through some simple examples. Also it will explain how we can benefit from instruction scheduling. Before going through instruction scheduling, we first describe data dependence analysis, upon which the instruction scheduling is based.

#### 2.1.1 Data Dependence Analysis

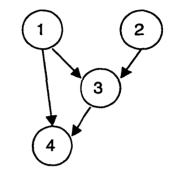

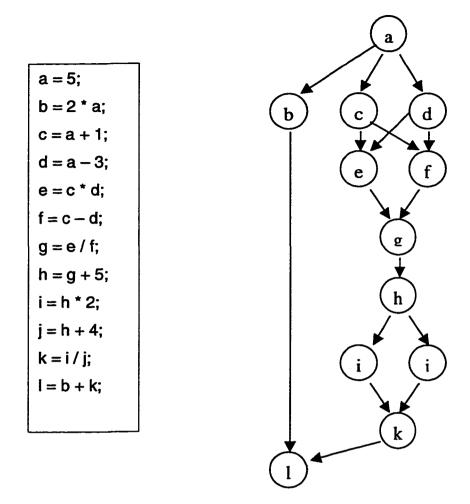

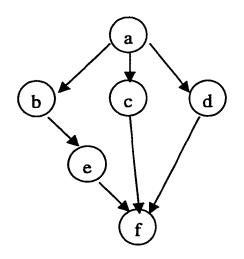

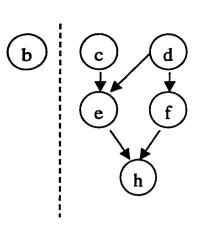

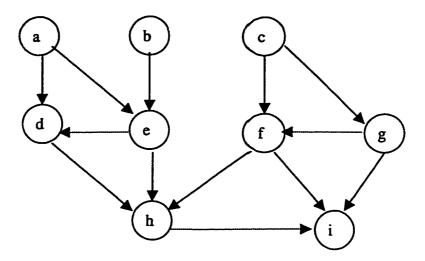

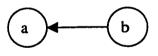

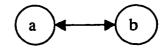

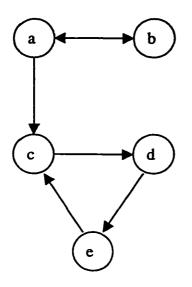

Data dependence analysis identifies the data dependence relationship between instructions and the constraints with which instruction scheduling must comply. The data dependencies between instructions fall into three categories: true dependence, antidependence, and output dependence. The alternative terminologies for these three types of data dependencies are called read-after-write (RAW), write-after-read (WAR), and write-after-write (WAW), respectively. The data dependencies between instructions can be visually expressed in directed acyclic graphs (DAGs), commonly called data dependence graphs. The following example in Figure 2.1 shows a piece of C code and its corresponding data dependence graph.

| (1) | a = 1;     |

|-----|------------|

| (2) | b = 2;     |

| (3) | c = a + b; |

| (4) | a = 5;     |

(a) Example C code

(b) Data dependence graph

#### Figure 2.1 An example of data dependence graph

In the data dependence graph shown in Figure 2.1 (b), each vertex or node of the graph represents a statement. The number in a vertex represents the statement number. Each edge represents a dependence relation between two statements. Each edge could be either one of three types of dependencies. For instance, the edge E(1, 3) represents a true data dependence (RAW) between statements 1 and 3, which indicates that statement 3 uses as input the value of variable a obtained from statement 1. The edge E(3, 4) represents an anti-dependence (WAR) between statements 3 and 4. The value of variable a in statement 3 is read as input and updated in the following statement 4. The edge E(1, 4) represents as an output dependence (WAW) between statements 1 and 4. The value of the variable a is obtained to be 1 in statement 1, and then updated to be 5 in statement 4. Whenever there is data dependence between two statements, a switch of the execution

order of these two instructions causes incorrect execution results. In other words, the execution order of two instructions must strictly comply with their data dependence relationship. Otherwise, the execution results will be wrong. For example, if we swap the execution order of statements 1 and 4, the resulting value of the variable c in statement 3 will be 7 instead of the correct value of 3.

#### 2.1.2 Instruction Scheduling

Instruction scheduling is a compiler-time process to determine the execution order of a sequence of instructions, which is performed by a scheduler (part of a compiler) based on data dependence analysis. Given a sequence of instructions, the execution order does not have to be the same as the order in which the programmer writes instructions originally. However, any execution order of instructions scheduled by the scheduler must conform to the data dependence between instructions. For example in Figure 2.1, based on data dependence analysis, it is found that there are two valid possible execution orders of four statements. They may be scheduled either in the order  $\{1, 2, 3, 4\}$  or  $\{2, 1, 3, 4\}$ . Any other execution orders will violate the data dependence in above example.

A scheduler is usually developed to schedule instructions purposely in support of the programmer's optimization goals. For example, if our optimization goal is to exploit instruction parallelism to reduce total instruction execution time, the scheduler identifies that statements 1 and 2 can be executed in parallel because there is no data dependence between these two statements in the above example. The following execution order is scheduled:

Figure 2.2 An example of paralleled code

The execution time is reduced to 3 from 4, assuming that the execution time of each statement takes one unit.

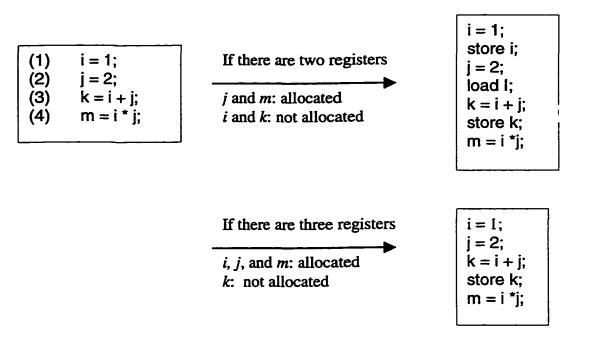

#### 2.1.3 Register Allocation

Registers are temporary storage elements in a processor. All the operations occur in registers. If a variable is not stored in a register, it is loaded from or stored in main memory whenever it is accessed. If the number of registers is less than the number of variables, the register allocator of a compiler determines which variables are stored in registers.

A register allocation example is illustrated in Figure 2.3. Assume that there are two registers available, that variables j and m are allocated in registers, and variables i and k are not allocated in registers. The left part of the figure is an example of C code and the right part is the corresponding instructions to be executed by the processor. Since variable i is not allocated in register, after the assignment instruction i = 1, the value of variable iwill be stored in main memory, so an extra store instruction is needed. When instruction k= i + j is executed, since variable i is not allocated in register, a load instruction is needed to load the value of variable i from main memory. For the same reason, the instruction store k is needed to store the value of variable k back in main memory. If there are three registers available, assuming that only variable k is not allocated in register, the corresponding instructions are shown in the lower part of the figure. Since variable k is not allocated in register, a memory access instruction is needed to store the value of variable k in main memory after instruction k = i + j is finished. As a result, the number of the instructions associated with main memory access in this case is reduced to 1 from 3 in the previous case. As a result, code size and execution time are reduced.

Figure 2.3 Example for register allocation

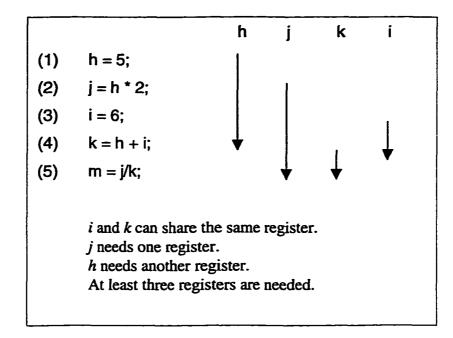

#### 2.1.4 Live Range Analysis

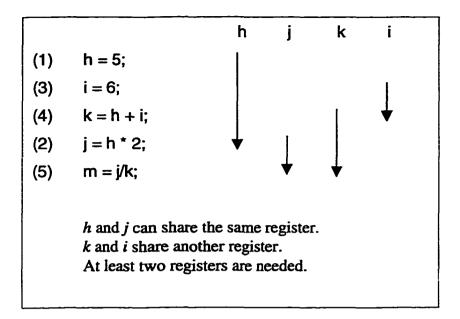

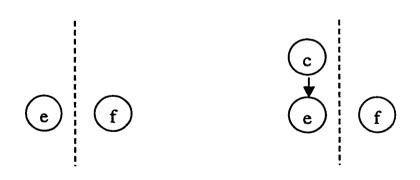

Like data dependence analysis on which instruction scheduling is based, live range analysis is the basis of register allocation. Each variable in a program has a live range. The live range of a variable is the range from its definition to its last use, that is, the range from the point where the variable becomes live to its dead point. For example in Figure 2.4, the live range of variable h is the range from statement 1 to statement 4, which is illustrated with an arrow below the variable name. If two variables have nonoverlapped live ranges, then they can share the same register. In other words, the second variable can safely reuse the register allocated to the first variable only when two variables have nonoverlapped live ranges. This is because a register is required to exclusively hold a live variable's value until that variable is "dead" once the register is allocated to that variable. Otherwise, the first variable's value stored in the register will be garbled by another variable that reuses the register allocated to the first variable. Consequently, wrong execution due to improper register allocation will result.

The minimum number of registers necessary can be obtained based on the live range analysis of a sequence of instruction. In the above example, variables i and k can share the same register because they have nonoverlapped live ranges. Variable j needs another register, and variable h needs another register. Thus at least three registers are needed in this example.

Figure 2.4 Live range analysis of variables

Obviously, the live range of a variable depends on the execution order of instructions. In other words, instruction scheduling affects register allocation. This is illustrated in Figure 2.5, which shows a different schedule for the instructions in Figure 2.4. It is easy to verify that this scheduling is a legal schedule based on the data dependence graph shown in Figure 2.5. With this schedule, variables h and j have nonoverlapped live ranges, so they can share the same register. For the same reason, variables k and i can share another register. As a result, two registers are needed, while the previous scheduling requires three registers. Thus the latter schedule saves one register compared with the original schedule.

From the above analysis, it is seen that instruction scheduling plays a very important role in the exploitation of instruction level parallelism and register allocation. In addition, instruction scheduling technique is very important to power reduction for embedded systems.

Figure 2.5 Effect of instruction scheduling on register allocation

Figure 2.6 Data dependence graph

Instruction scheduling and register allocation have been two very important optimization phases not only for the compilers targeted on embedded systems but also for other modern compilers. Traditionally, one phase is performed before another phase, which is called a phase ordering approach. In recent years it has been generally recognized that the separation between the instruction scheduling and register allocation phases leads to poor optimization for cases that are not suited to the specific phase ordering selected by the compiler [1, 31]. For instance, consider the first phase ordering approach, that is, instruction scheduling followed by register allocation. This phase ordering gives priority to instruction scheduling. It may be good for exploiting instruction-level parallelism. However, based on the previous example, it can be seen that the first schedule in Figure 2.4 stretches out some variables' live ranges compared to the second schedule in Figure 2.5. As a result, the required number of registers in the first schedule is 3, while the second schedule requires 2. If there are two registers available, one variable's value has to be spilled into main memory. Thus the first schedule relatively increases register pressure.

The second ordering approach is to perform register allocation before instruction scheduling. This approach gives priority to optimizing usage of registers, especially for the processors with a small number of registers. It may cause no spills or minimum spills. However, additional dependencies between instructions may be generated due to extra register dependencies. As a result, this generates additional constraints for instruction scheduling, thus limiting the flexibility of instruction scheduling.

It is desirable to integrate these two phases into a single phase to minimize constraints upon each other. Unfortunately, the integration of instruction scheduling and register allocation is a *NP*-Complete problem. Thus this research attempts to develop an effective heuristic algorithm for the integration problem. The register-reuse chain

generation and merging algorithms are developed primarily to minimize the constraints for instruction scheduling when optimizing of register allocation.

#### 2.2 ARM7T (Advanced RISC Machines) Processor

This research uses the ARM7T microprocessor, one of a series of ARM processors developed by Advanced RISC Machines Ltd., as the target processor. ARM designs and licenses high-performance, low-cost, power efficient RISC microprocessors and related technology. ARM intends to establish its architecture as the standard for embedded RISC processors for use in a wide range of high volume applications in the embedded, portable, and consumer multimedia markets. The application examples of ARM processors include [41]:

- Portable: digital cellular phones, pagers and personal organizers.

- Embedded: modem, hard disc drivers, printers and automotive applications.

- Consumer multimedia: sound system, games, set-top box.

ARM7T series processors are the company's most widely licensed processors.

The CPU cores of AMR7T are small, fast, low-power, 32-bit RISC processors that are primarily used in portable telecommunications. It has the ability to combine the ARM instruction set with the THUMB extension to reduce memory size and system cost. The THUMB extension delivers 32-bit RISC performance at a 16-bit system cost.

#### 2.3 Local C Compiler (LCC)

Local C Compiler (LCC) is a retargetable compiler for ANSI C, developed by Fraser and Hanson [15]. It has been used to compile production programs since 1988. As a retargetable compiler, LCC has multiple target machines. The advantages of retargetable compilers are that machine-specific compiler parts are isolated in modules that are readily applied to the user-desired target machines. For example, during the hardware-software co-design stage of an embedded system, the target architecture may be changed to achieve a better ratio of performance to cost. There is no need to rewrite the software compiler each time when some features are added or removed from the current architecture.

To be retargetable, LCC is organized into two major parts shown in Figure 2.7. The first part is called the *front end* that consists of a lexical analyzer and a parser. The lexical analyzer reads program source text and produce tokens. The parser takes a stream of tokens passed from the lexical analyzer and checks whether they conform to the syntax of the language. Then an intermediate representation of the source program, called directed acyclic graphs (DAGs), is generated. The intermediate representation generally is language-independent and target machine-independent. Within the front end, some target-independent optimizations are performed, such as common sub-expression elimination. The second part of LCC is called the *back end*. It takes as input the intermediate representation of source program, or DAGs, that are passed from the front end and translates them into target-dependent assembly code. When the target architecture is changed or a new architecture is considered, only the back end part of the compiler needs to be rewritten.

The optimization parts of LCC like instruction scheduling and register allocation originally distributed by Fraser and Hanson are primitive and simple. Based on their own needs, users can replace them and add their own optimization parts.

Figure 2.7 Structure of Local C Compiler (LCC)

#### **CHAPTER THREE**

# DEPENDENCE ANALYSIS AND INSTRUCTION SCHEDULING

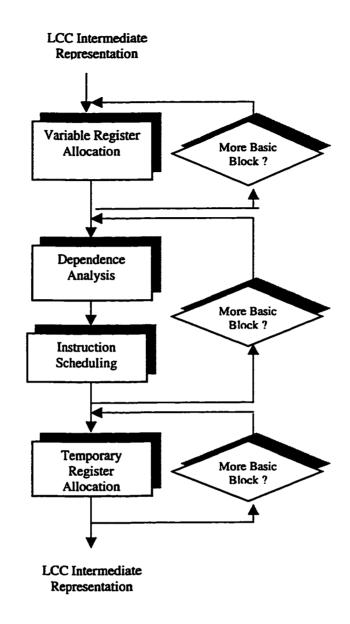

This chapter presents the dependence analysis and the instruction scheduler. In Section 1, the structure of optimizing Local C Compiler (LCC) is described. In Section 2, the data dependence analysis, the basis of the instruction scheduler, is represented. Section 3 describes the instruction scheduler developed in this research.

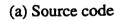

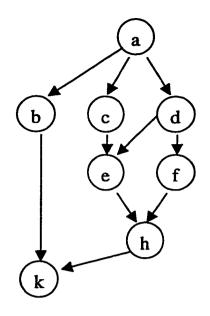

#### 3.1 Structure of Optimizing LCC Compiler

Figure 3.1 shows the overall structure of the optimizing compiler developed in this research. It consists of three main phases. In the first phase, registers are allocated to variables of a program. This register allocation is optimized by each basic block. The next phase performs instruction scheduling. Dependencies between instructions are analyzed for the correct and most efficient instruction scheduling. The dependence analysis and instruction scheduling are also performed by each basic block. The last phase is the allocation of temporary registers. For this phase, the existing LCC variable register allocator is used. The variable register allocation is the main subject of Chapter 4 and Chapter 5. Therefore, detailed explanation is given in those two chapters. In this section, the implementation of dependence analysis and instruction scheduling in the LCC is explained and issues for the increase of efficiency are discussed.

Figure 3.1 The structure of the new optimizing compiler

#### **3.2 Dependence Analysis**

#### **<u>3.2.1 True Dependence</u>**

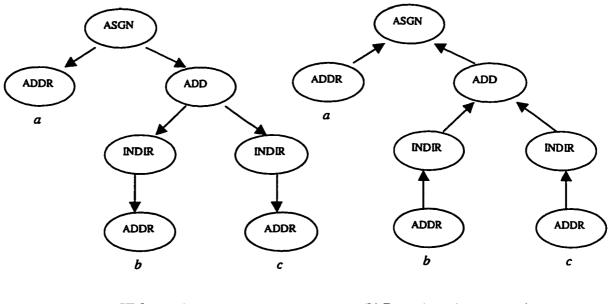

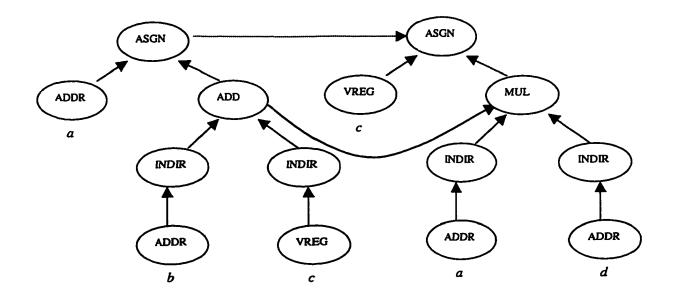

Dependence represents the relationship in which a correct computation of one node depends on the result of the computation of the dependent node. For example, consider the Abstract Syntax Tree (AST) shown in Figure 3.2 (a). All nodes depend on their kids. For example, the ASGN node depends on the computation result of ADD and the address node (ADDR a). On the other hand, the node ADD depends on its kids, INDIR (ADDR b) and INDIR (ADDR c). Figure 3.2 (b) shows the corresponding dependence graph. The arrows in this graph show the dependence relationship. The target of the arrow depends on the source of the arrow.

(a) AST for a = b + c

(b) Dependence between nodes

Figure 3.2 A single AST and the corresponding dependence graph

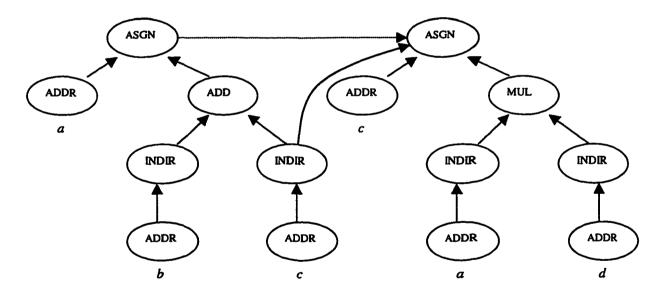

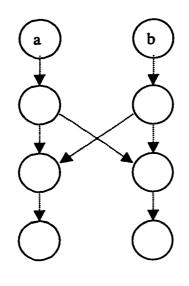

Now that the dependence graph for a single AST is explained, consider the dependence graph for multiple ASTs. Consider the ASTs shown in Figure 3.3 (a). There

21

are two ASTs, which represent statements a = c + d and e = a + d, respectively. Note that the second statement depends on the first statement. In order to represent the dependence between two statements, a new edge is created from the ASGN node of the first AST to the corresponding ADDR (a) node in the second AST. This edge is illustrated with a thick line in Figure 3.3 (b).

#### **3.2.2 Anti-Dependence**

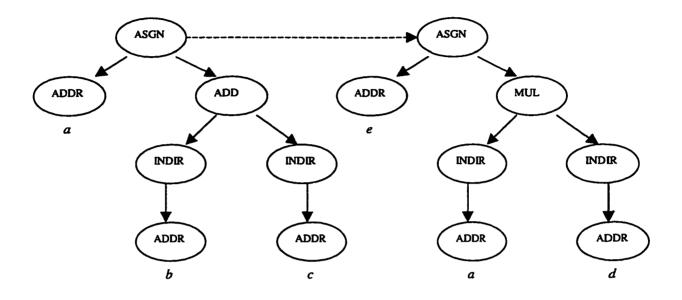

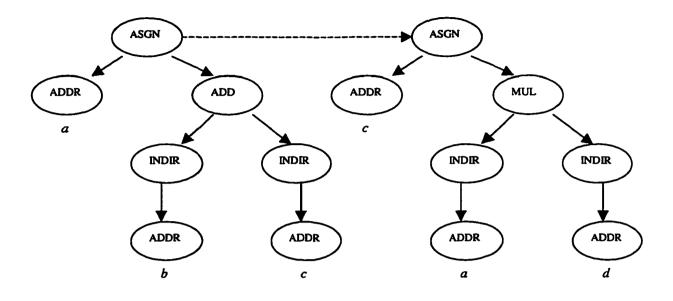

Anti-dependence represents the relationship in which one statement depends on the other statement because the statement stores a value into the same memory location as the dependent statement loading a value. If the storing statement is executed earlier, before the loading statement accesses the value, a wrong value can be loaded. Consequently, the computation result can be wrong.

Figure 3.4 (a) shows a case when anti-dependence occurs. There are two ASTs representing two statements, a = b + c and c = a \* d, respectively. Note that the second INDIR node in the first AST reads data from c, while the ASGN node in the second AST stores data into c. In this case, an edge is created from the INDIR(ADDR c) node in the first AST to the ASGN(ADDR c) node in the second AST. This edge is shown in the thick line in Figure 3.4 (b).

(a) ASTs for a = b + c and e = a \* d

(b) Dependence graph

Figure 3.3 Multiple ASTs and the dependence graph

(a) ASTs for a = b + c and c = a \* d

(b) Anti-dependence graph

Figure 3.4 Multiple ASTs and the anti-dependence graph

### 3.2.3 Output Dependence

Output dependence represents the dependent relationship in which two statements store data into the same memory location. In order to store the correct value in the location, the order of the two stores must be preserved. Figure 3.5 (a) shows the case when output dependence occurs. There are two statements, a = b + c and a = e \* d. Note that both statements store data into a. In order to prevent the reordering of the two assignments, an edge is created between the two ASGN nodes. In Figure 3.5 (b), the thick line corresponds to the output dependence.

25

(a) ASTs for a = b + c and a = e \* d

(b) Output dependence graph

Figure 3.5 Multiple ASTs and the output dependence graph

#### 3.2.4 Adjustment of Dependencies

Register allocation often changes the output assembly code depending on which variables are assigned to registers. For example, Node (ASGN (ADDR symbol)) generates STORE instruction. However, if a register is allocated to the symbol, a STORE instruction is not necessary because the value is stored in the register. Therefore, after register allocation, the code needs to be labeled again so that a new code generation rule is assigned to each node. The new rule determines whether an ASGN node needs to generate STORE instruction or not. In addition, the new rule decides whether an INDIR node needs to generate a LOAD instruction or not.

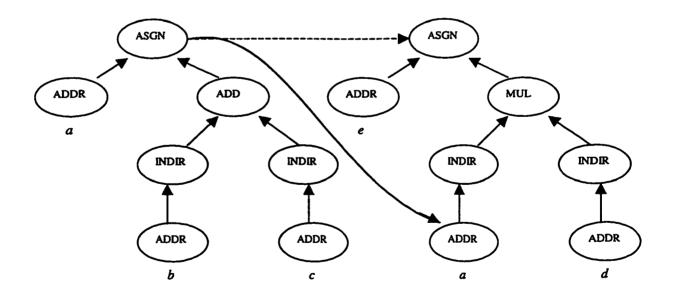

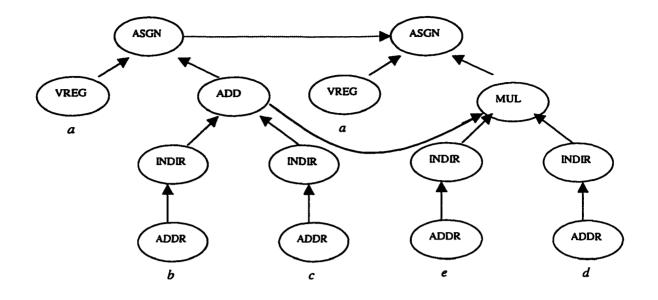

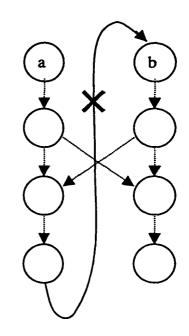

Once code generation rule is changed, dependencies need to be adjusted. Consider the example of anti-dependence shown in Figure 3.4 again. There is an anti-dependence from (INDIR (ADDR c)) in the first tree to (ASGN (ADDR c)) in the second tree. Note that node (INDIR (ADDR c)) in the first tree generates assembly instruction LOAD Rt, addr (c), and node (ASGN (ADDR c)) generates assembly instruction STORE Rt, addr (c). Here, Rt represents a temporary register, and addr(c) represents the address of variable c in main memory. The anti-dependence guarantees that instruction STORE Rt, addr(c) is scheduled later than instruction LOAD Rt, addr(c). Therefore, the correct sequence of instructions is generated.

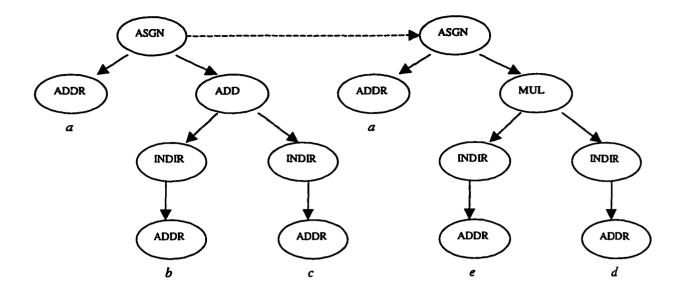

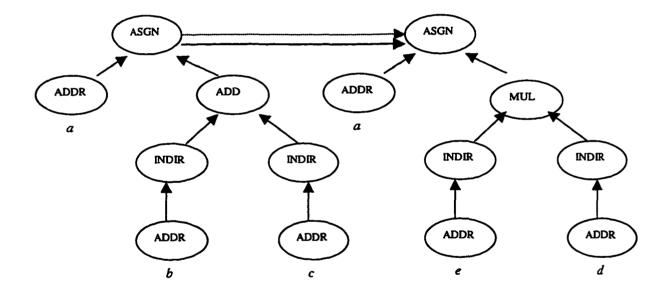

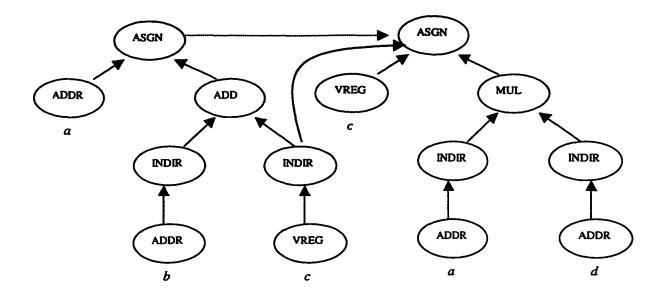

Suppose that variable c is assigned a register. Then, the tree is changed as shown in Figure 3.6 (a). Note that node (ADDR c) is changed to (VREG c) that represents a register is allocated to c. In this case, node (ASGN (VREG c)) does not generate an assembly instruction because variable c is now stored in a register. Its kid, node MUL, performs the actual assignment operation. Similarly, node (INDIR (VREG c)) does not generate an assembly instruction, and its kid, node ADD, performs the actual loading operation. Therefore, an anti-dependence needs to be adjusted such that node MUL is scheduled after node (INDIR (VREG c)). The resulting dependence graph is shown in Figure 3.6 (b). The new edge from ADD in the first tree to MUL in the second tree is created.

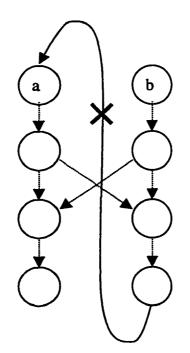

Register allocation also requires the adjustment of output dependence. Consider the dependence graph shown in Figure 3.5 again. There is output dependence from node ASGN in the first tree to node ASGN in the second tree. Suppose that a register is assigned to variable so that node (ADDR a) is changed to (VREG a). Then, the two ASGN nodes do not generate any assembly instruction. Instead, their kids, ADD and MUL, perform the assignments. Note that node MUL can be scheduled as soon as its kids are scheduled. Thus it can be scheduled earlier than node ADD in the first tree. If it happens, the resulting code stores wrong value in the register. To prevent this, the output dependence needs to be adjusted so that node MUL is scheduled later than node ADD. The corresponding dependence graph is shown in Figure 3.7.

(a) Anti-dependence graph after a register is assigned to variable c

(b) New anti-dependence from ADD in the first tree to to MUL in the second tree

Figure 3.6 Adjustment of anti-dependence after register allocation

Figure 3.7 Adjustment of output dependence after register allocation

Adjustment of input dependence is similar to that of anti-dependence. For true dependence, adjustments are in general not necessary except one corner case. Function rewriteDep() is called inside rewriteAgain() after nodes are labeled again based on register allocation. This function takes care of one corner case for the adjustment of true dependence. Then, it calls function adjustFalseDep(), shown in Figure 3.8, for the adjustment of input dependence, output dependence, and anticalls functions dependence. Function adjustFalseDep( ) three adjustAntiDep(), adjustOutputDep(), and adjustRegDep(), each of which performs adjustments for anti-dependence, output dependence, and input dependence, respectively.

Figure 3.8 Procedure for adjustments of dependence

## **3.3 Instruction Scheduling**

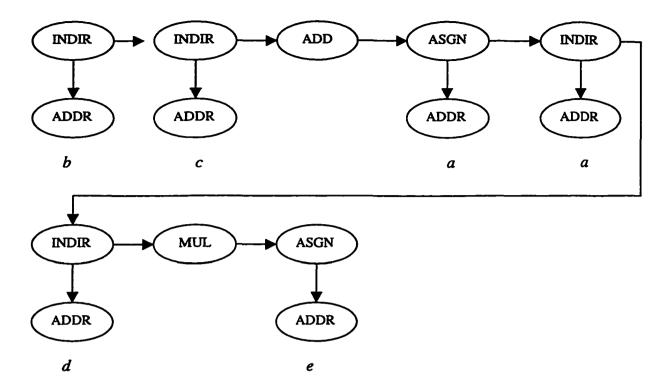

Instruction scheduling is a total (or linear) ordering of nodes in ASTs. Consider the ASTs shown in Figure 3.3 again. The dependence graph in Figure 3.3 (b) represents the partial order of the nodes, but not the total order. So the instruction scheduler transforms the dependence graph into a linked list of the nodes. Figure 3.9 shows an example of scheduled nodes. In this graph, nodes are linked in a linear order. Note, however, that all ADDR nodes are not linked in the linear list, but attached as kids of the nodes in the linear list. The reason is because the ADDR nodes do not call the LCC emitter to generate an assembly instruction. Thus, only those nodes that call the LCC emitter are included in the scheduled linked list. More details on the nodes that call the LCC emitter are illustrated in [15]

Figure 3.9 A schedule example for nodes shown in Figure 3.3

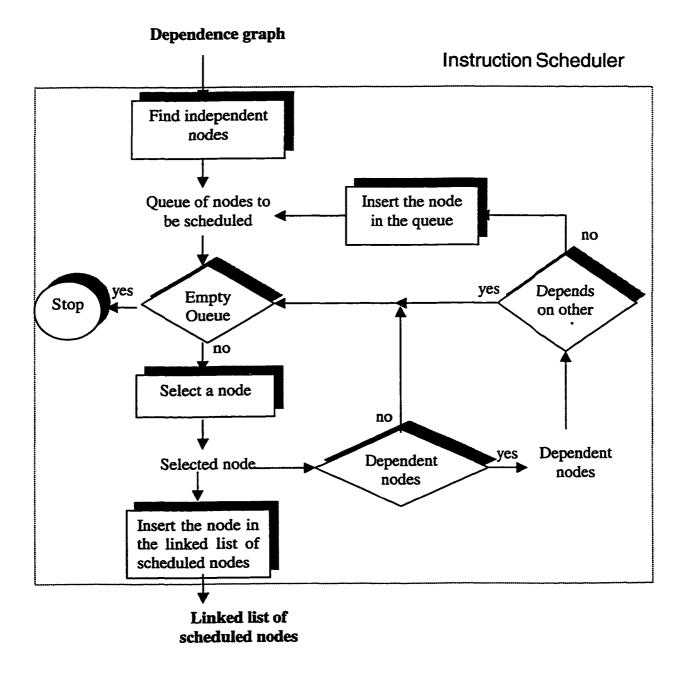

Figure 3.10 shows the structure of the instruction scheduler. The input of the scheduler is a dependence graph, and the output is the linked list of nodes in the scheduled order. The first phase of instruction scheduling is to find a set of nodes that are not dependent on any other nodes. A queue is made out of these nodes as the result of the first phase. Note that all these nodes in the queue can be scheduled next. The next phase is to select a node among the nodes in the queue and insert it into a linked list that represents the execution order of the nodes. Thus, the earlier a node is selected from the queue, the earlier the node is scheduled or executed. Once a node is selected to schedule, the next phase checks whether it has dependent nodes. If there is a dependent node, the next phase checks whether it can be scheduled next. If the node depends on any other nodes that are not scheduled at the moment, the node must be scheduled after the

dependent node is scheduled. In this case, the node cannot be inserted in the queue. Otherwise, the node is inserted in the queue, and waits for the selection phase to be inserted into the linked list. The selection and insertion phases repeat until all the nodes in the dependence graph are scheduled, and as a result the instruction queue becomes empty.

Figure 3.10 Structure of the instruction scheduler

33

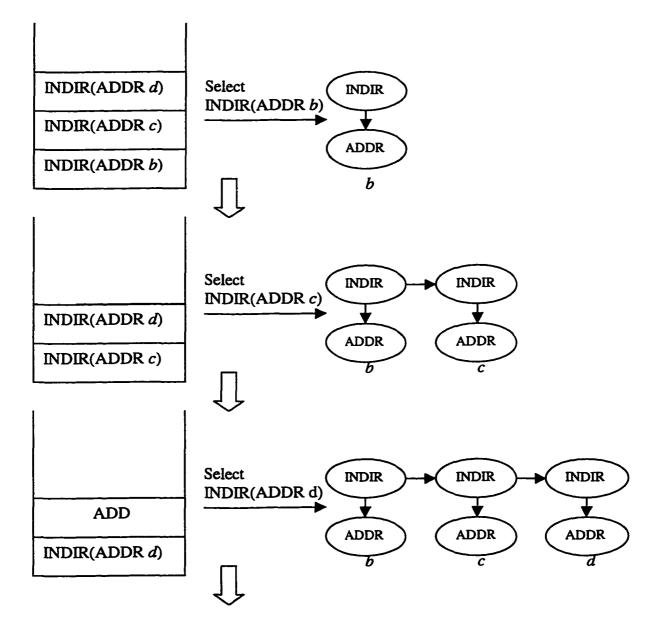

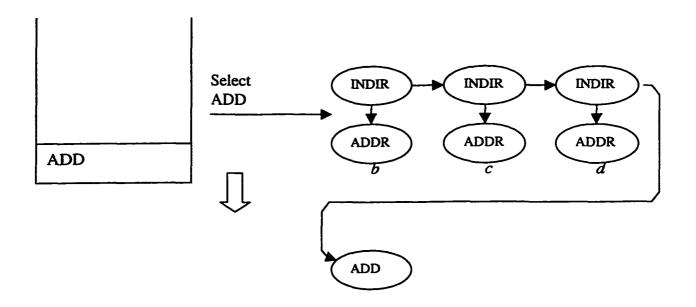

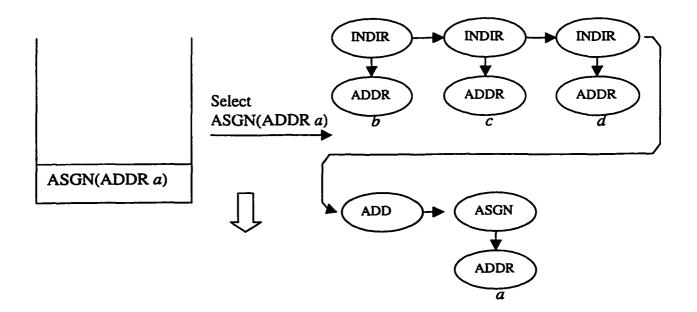

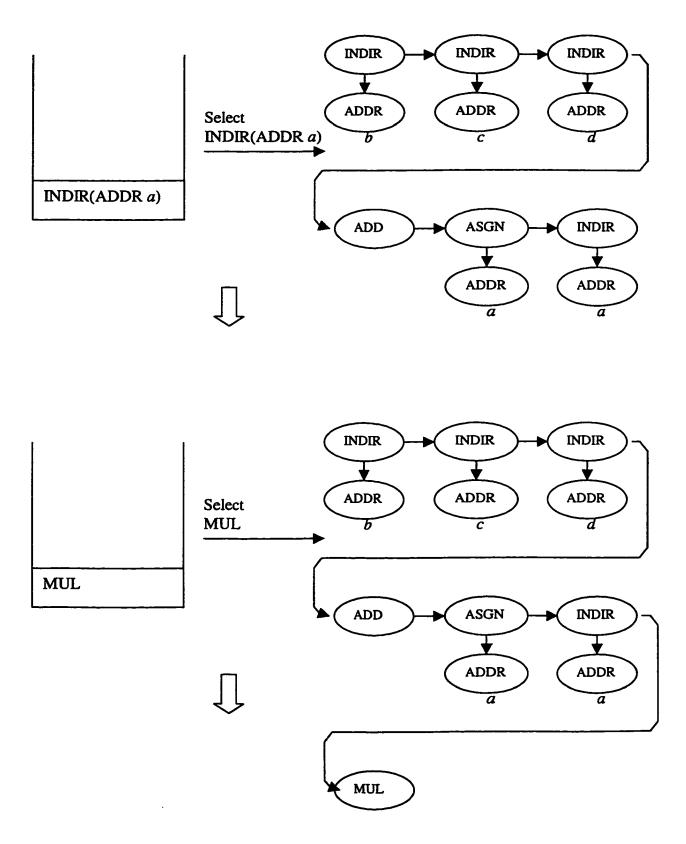

Figure 3.11 explains the steps for how the instruction scheduler generates the scheduled nodes with a given dependence graph. Refer to the dependence graph shown in Figure 3.3 (b). The first phase of the instruction scheduler finds the nodes that are independent of any other nodes. In this example, nodes (INDIR (ADDR b), (INDIR (ADDR c)), and (INDIR (ADDR d)) are independent nodes. Thus, these nodes are initially inserted in the queue. The next phase is to select one of the nodes in the queue. Depending on the constraints given to the scheduler, there are many different ways to select the node. In this example, assume that the node in the top of the queue (located at the bottom of the queue in the figure) is selected first. So (INDIR (ADDR b)) is selected first, and then inserted in the linked list of the scheduled nodes. At this stage, only one node is scheduled. In the next step, the dependent node of (INDIR (ADDR b)) is found. Node (ADD) depends on node (INDIR (ADDR b)). Then the scheduler checks whether node (ADD) depends on any other node that is not scheduled. Note that node (ADD) depends on (INDIR (ADDR c)) that is still not scheduled. This implies that node (ADD) cannot be scheduled until (INDIR (ADDR c)) is scheduled. Thus, node (ADD) cannot be inserted into the queue. Then, the queue has two nodes (INDIR (ADDR c)) and (INDIR (ADDR d)). The next step is to return to select a node from the queue. At the top of the queue is node (INDIR (ADDR c)) that is selected to schedule. So, the linked list of the scheduled nodes contains two nodes, (INDIR (ADDR b)) and (INDIR (ADDR c)). Now that (INDIR (ADDR c)) is scheduled, the scheduler checks whether its dependent node is ready to be scheduled. Node (ADD) is the dependent node of (INDIR (ADDR c)). In order for node (ADD) to be scheduled, it must be independent of any other unscheduled nodes. The only other dependent node is (INDIR (ADDR b)) that is already scheduled.

Thus, node (ADD) can be scheduled, and therefore, is inserted in the queue. Thus, the queue now includes two nodes, (INDIR d), and (ADD). The selection and insertion steps are repeated until the queue is empty. All the steps are shown in Figure 3.11.

Figure 3.11 An example of scheduled nodes

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

Figure 3.11 Continued

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

Figure 3.11 Continued

Figure 3.11 Continued

The code given in Figure 3.12 shows a rough structure of the instruction scheduler. Function initiallyIndepInstr() finds all nodes that are initially independent of any other nodes. The found nodes are inserted in the queue. Then, the body of while-statement is repeatedly executed until the queue becomes empty. The first function in the body, selectNodeInQueue() selects a node from the queue. Depending on various needs, this selected node can be different. In some cases, more than one node is selected. For space limitation, detailed explanation of this function is

omitted. The selected node is removed from the queue by function removeFromQueue(), and then inserted into the linked list of scheduled nodes. Then, function includeDepInstrInQueue() searches all dependent nodes and insert them in the queue if they are not dependent on any other unscheduled nodes. The selection (selectNodeInQueue) and insertion (includeDepInstrInQueue) repeat until the instruction queue is empty, that is, emptyInstrQueue() returns NULL.

```

mainScheduler( forest, next ) Node forest, next;

{

/* initialization */

/* find initially independent nodes and insert them in the

queue */

initiallyIndepInstr( forest );

while(!(emptyInstrQueue())) { /* repeat until the queue

is empty */

sNodes = selectNodeInQueue( p );

for( sn = sNodes; sn; sn = sn->next ) {

p = sn -> nd;

p->DFScolor = SCHEDULED;

removeFromQueue( p );

/* insert p into scheduled node list */

includeDepInstrInQueue( p );

}

}

/* reset data structure for opcode generation */

}

```

### Figure 3.12 A basic structure of the scheduler

In the insertion phase, there are three important functions, includeDepInstrInQueue(), insertInstrInQueue(), and putInstrInQueue(). Function includeDepInstrInQueue() searches all the nodes that depend on node *p*. Then, for each of the dependent nodes, insertInstrInQueue() is called. The main functionality of insertInstrInQueue() is to check whether node *p* depends on any other unscheduled nodes. If it is false, it calls putInstrInQueue() function in order to insert the node in the instruction queue. Function putInstrInQueue() puts the node in the instruction queue and updates all the data structure correspondingly.

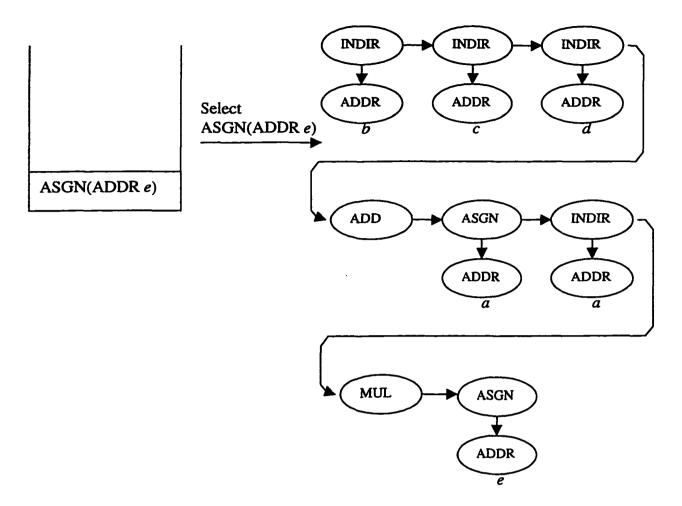

When a node in an instruction queue is selected and scheduled, its dependent nodes are searched. If a dependent node does not depend on any other nodes that are not Function scheduled. the node can be inserted in the queue. includeDepInstrInQueue(), shown in Figure 3.13, performs the search of dependent nodes. The first phase of the function is to check whether its parent node is prevented from being included in the instruction queue. In the second phase, it searches true dependent nodes that are stored in the linked list pointed by *dDependent*. In the next phase, it searches false dependent nodes bv calling function. includeFalseDepInstrInQueue().

```

includeDepInstrInQueue( p ) Node p;

{

/* prevent its parent from being included in the

instruction queue */

for( dn = p->dDependent; dn; dn = dn->next )

insertInstrInQueue( dn->nd, p );

includeFalseDepInstrInQueue( p );

}

```

Function includeFalseDepInstrInQueue() shown in Figure 3.14 searches false dependent nodes. Note that there are three different types of false dependencies: anti-dependence, output dependence, and true dependence. These dependent nodes are pointed by the fields, *d.antiTo*, *d.outputTo*, and *d.regTo*, respectively. Function insertASGNnodeInQueue() checks whether the dependent node is also dependent on any other unscheduled nodes. If it is false, then the dependent node is inserted in the instruction queue.

```

void includeFalseDepInstrInQueue( p ) Node p;

{

Node q;

if( q = p->d.outputTo ) insertASGNnodeInQueue( q, p );

if( q = p->d.antiTo ) insertASGNnodeInQueue( q, p );

if( q = p->d.regTo ) insertASGNnodeInQueue( q, p );

}

```

Figure 3.14 Function for including false dependent nodes in the queue

When includeDepInsrInQueue() finds a node to be inserted in the instruction queue, it calls function insertInstrInQueue () shown in Figure 3.15. First, this function checks whether it is an instruction node or not by evaluating x inst field. If the node is an instruction node, it can be inserted in the queue. So function insertXNodeInQueue() is called. If the node is not an instruction node, check whether the node is an ADDR node or a VREG node. If it is true, the conditions specific to the ADDR/VREG node are checked, and insert the node in the queue if the conditions If the node ADDR/VREG node, function satisfied. is not an are includeDepInsrInQueue() is recursively called to search its dependent nodes.

Figure 3.15 Function for inserting a node in the queue

Function insertXNodeInQueue(), shown in Figure 3.16, checks whether a node depends on any other nodes that are not scheduled yet. If it is not true, it calls function putInstrInQueue() to insert the node in the instruction queue. This check is performed by function isAnyOtherXKids(). If there is such a node, it is necessary to check whether it is scheduled, that is, *DFScolor = SCHEDULED*. It is also necessary to check whether the node falsely depends on any other nodes that are not scheduled yet. The examination for false dependence is performed by function isFalseDepOnNotScheduledNode(). This function checks anti-dependence, output dependence, and input dependence through register reuse. Once all these examinations are passed, function putInstrInQueue() is called. If function isAnyOtherXKids() returns NULL (that is, there is no other kids that are instruction nodes), the false dependence is the only necessary check. Thus, function isFalseDepOnNotScheduledNode() is called for the examination.

```

void insertXNodeInQueue( nd, depNode )

Node nd;

Node depNode; /* nd is dependent upon depNode */

{

Node q;

if( ( q = isAnyOtherXKids( nd, depNode )))

if ( q->x.inst && getOpIndex( q, q->x.inst )

&& q->DFScolor == SCHEDULED )

if( !isFalseDepOnNotScheduledNode( nd ) )

putInstrInQueue( nd );

else if( !isFalseDepOnNotScheduledNode( nd ))

putInstrInQueue( nd );

}

```

Figure 3.16 Function for inserting Xnode in the queue

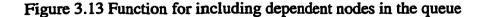

When function putInstrInQueue(), shown in Figure 3.17, is called, the first step is to check whether the node is already scheduled, or inserted in the queue. This check prevents a node from being inserted twice in the instruction queue. The second step inserts the node in the instruction queue. This step includes the establishment of new links after the insertion as well as the update of data structure. The final step checks whether it is an assembly-generating node or not. If it is true, it searches its dependent nodes by calling includeDepInstrInQueue(). In this way, the search and insertion process repeats until an assembly-generating node is inserted in the queue.

```

void putInstrInQueue( p ) Node p;

{

if( p->DFScolor == QUEUED || p->DFScolor == SCHEDULED)

return;

/* insert Node p in the instruction queue */

if( !getOpIndex( p, p->x.inst ) )

includeDepInstrInQueue( p );

}

```

Function selectNodeInQueue(), shown in Figure 3.18, is able to choose various scheduling techniques based on variable *scheduleOption*. Currently, three different scheduling techniques are implemented. The first one is to select the instruction that minimizes the hamming distance of opcode between consecutive instructions. This technique is useful for reducing power consumption due to frequent change between consecutive opcode values. The second scheduling technique is designed for VLIW architecture that can execute multiple instructions simultaneously. The third scheduling is to simply select the first instruction node in the queue.

```

void SelectedNode selectNodeInQueue()

{

switch( scheduleOption )

{

Case BIT_CHANGE_REDUCTION:

sn = callMinBitChangeOpInQueue( sn );

break;

Case VLIW:

sn = callVliwSchedule( sn );

break;

default:

sn = firstNodeInQueue( );

break;

}

}

```

Figure 3.18 Function for selecting a node from a queue

Various instruction scheduling techniques can be combined together and executed simultaneously. In order to support the combination of multiple instruction scheduling techniques, callMinBitChangeOpInQueue or callVliwSchedule() shown in Figure 3.19 supports the case when there are some nodes selected by the previous

scheduler. For example, see function callVliwSchedule(). When there is a previously selected node (that is, sn is not NULL), the function attaches the selected node by calling vliwSchedule() to the tail of the selected node list.

```

SelectedNode callVliwSchedule( sn ) SelectedNode sn;

{

if( sn ) {

SelectedNode lsn;

lsn = lastSelectedNode( sn );

lsn->next = vliwSchedule( );

}

else

sn = vliwSchedule( );

return sn;

}

```

Figure 3.19 Function for calling VLIW scheduling

# **CHAPTER FOUR**

# **REGISTER ALLOCATION**

This chapter presents an improved register allocation algorithm developed in this research. The major algorithms include register-reuse chain generation, chain merging, and the merging criteria. A discussion of the previous research on register-reuse chain in [7, 8] is also provided. For convenience of descriptions, some formal definitions related to those algorithms are given.

## 4.1 Background

As mentioned in Chapter 2, instruction scheduling and register allocation are the two major compiler optimization techniques. In most research efforts, these two techniques are studied separately [7, 8, 30, 31]. One phase is performed before the other. The resulting approaches are called phase ordering solutions. However, these two optimizations often significantly influence each other. Optimization in one phase adversely affects the optimization in the other phase. The first phase ordering approach (that is, instruction scheduling followed by register allocation) gives priority to instruction scheduling. An instruction scheduler decides the live range of a variable and consequently places significant constraints on register allocation. Therefore, even efficient instruction scheduling can degrade the overall optimization if the scheduler places too many constraints on register allocation, resulting in poor register allocation. Some variables'

values may spill in main memory. As a result, performance is lowered due to main memory access latency, and code size increases correspondingly due to extra memory access instructions generated.

On the other hand, the second approach, register allocation followed by instruction scheduling, gives priority to register allocation. Register allocation affects instruction scheduling because it often creates additional dependencies that add constraints to the scheduler. A common approach to register allocation is graph-coloring. The graph-coloring approach formulates a register allocation problem as a graph-coloring problem. Each vertex of the graph represents a variable in the program. If two variables' live ranges are overlapped, an edge exists between two vertices. The graph-coloring approach attempts to assign a color to each vertex in the graph with a minimum number of colors used, such that no two vertices between which there is an edge has the same colors. The variables with the same color can share a register.

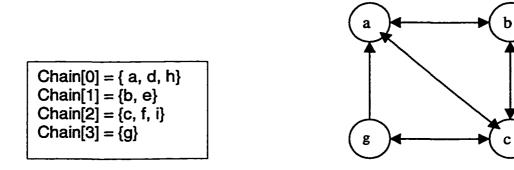

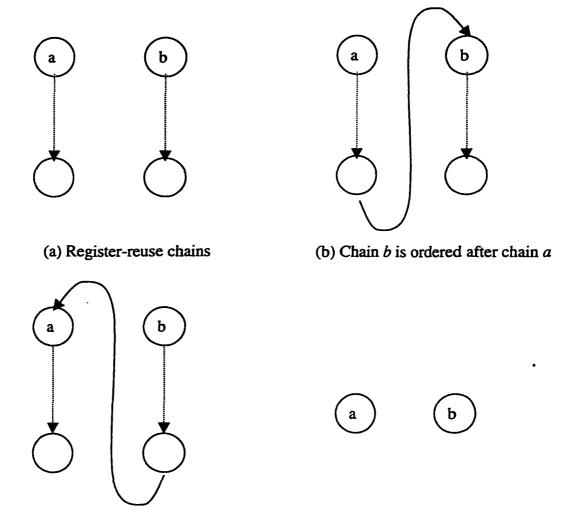

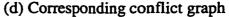

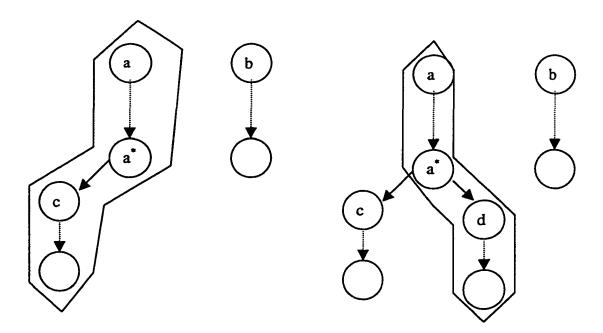

In order to develop an optimizing compiler that would be efficient for both a scheduler and a register allocator, recent research has been focused on the integration of these two techniques [7, 8]. Berson, Gupta, and Soffa make a promising contribution by proposing register allocation based on register-reuse chains [8]. A register-reuse chain is defined as an ordered set of instructions that use the same destination registers. Thus, register allocation in [8] is a procedure for decomposing a dependence graph into register-reuse chains. Each reuse chain requires a register so that the number of necessary registers is the same as the number of register-reuse chains. If the number of chains is greater than the number of registers, dependencies are added to the dependence graph that leads to the reduction of the number of register-reuse chains (see details in later sections). Since the

addition of dependencies generates additional restrictions for an instruction scheduler, efficient heuristics are proposed in [8] to reduce unnecessary restriction.

Although the main idea of the register-reuse chain approach is promising, the method proposed by [8] can still be improved. This is because it does not have a systematic approach to derive the best register-reuse chains and consequently it can result in an inappropriate selection of register-reuse chains. Another improvement is needed because the efficiency of the previous heuristic can be lowered when statements have various execution times. The previous method is optimized assuming that every statement in a program has the same execution time. However, it is often the case that different statements can have different execution times, because different statements can have different types of operations as well as different number of operations.

The register allocation technique proposed in this research follows the framework in [7,8], and improves the efficiency of the technique. The first step is to find a register allocation that is optimal in the sense that no additional dependencies are created. This optimal register allocation sometimes requires a large number of registers that is greater than the number of available registers. For this case, a heuristic is proposed to reduce the number of necessary registers while attempting to minimize the additional dependencies.

### 4.2 Register Allocation Based on Register-Reuse Chains

#### 4.2.1 Definitions

For convenience of description, some definitions that are used in the algorithms are introduced as follows:

**Definition:** A partial ordering relation P on a set S is a relation on S such that

- (1) (x, x) is  $\notin P$  for any x in S,

- (2) if  $(x, y) \in P$ , and  $x \neq y$  then (y, x) is  $\notin P$ ,

- (3) if (x, y) and  $(y, z) \in P$ , then  $(x, z) \in P$ .

Condition 3 says P is a transitive relation. Condition 1 is called the irreflective law, and Condition 2 is called the antisymmetry law. Thus, a partial ordering is an irreflective, antisymmetric, and transitive relation [10].

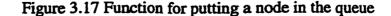

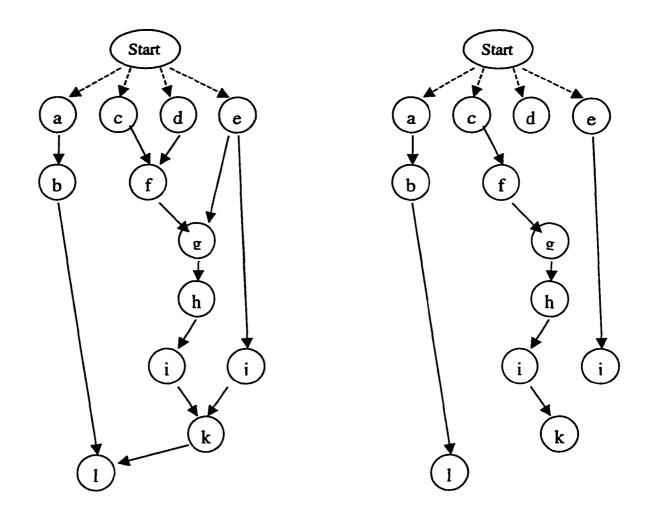

According to the above definition, a data dependence graph is a partially ordered set whose elements are the nodes of the data dependent graph. The relation between the nodes in a data dependence graph can be described as "ancestor" or "descendant" relations. It is easily seen that a data dependence graph satisfies the three conditions of a

partial ordering relation. For the example shown in 4.1 (a), there is a relation of "ancestor" between nodes a and e; that is, node a is the ancestor of node e. This relation can be obtained by applying the transitive condition (Condition 3), because the node a is

the ancestor of node c and node c is the ancestor of node e.

Figure 4.1 Examples of partial ordering and linear partial ordering.

**Definition**: A partial ordering P of a set X is *linear* if for each two elements x and y in a set X, either  $(x, y) \in P$ , or  $(y, x) \in P$ .

An example of linear partial ordering is shown in 4.1 (b) in which set  $\{a, b, c, d\}$  forms a linear ordered set because there exists a relation "ancestor" between any two nodes in the set.

**Definition**: In a partially ordered set, a subset whose elements are linearly ordered (relative to each other) is called a *chain*.

In other words, a chain is a subset of a partially ordered set and its elements are linearly ordered. Since a data dependence graph is a partially ordered set, it could be decomposed into distinct chains. For example, subsets  $\{a, e, f\}$  and  $\{b\}$  are two distinct chains in the dependence graph in Figure 4.1(a). **Definition:** A *register-reuse chain* is a chain in a data dependence graph in which all the nodes share the same register.

For example, by definition, chains  $\{a, e, f\}$  and  $\{b\}$  can be two different registerreuse chains in Figure 4.1 (a), respectively, if nodes a, e, and f share the same register and node b uses another register.

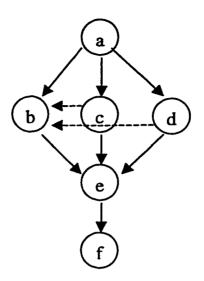

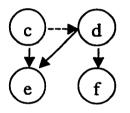

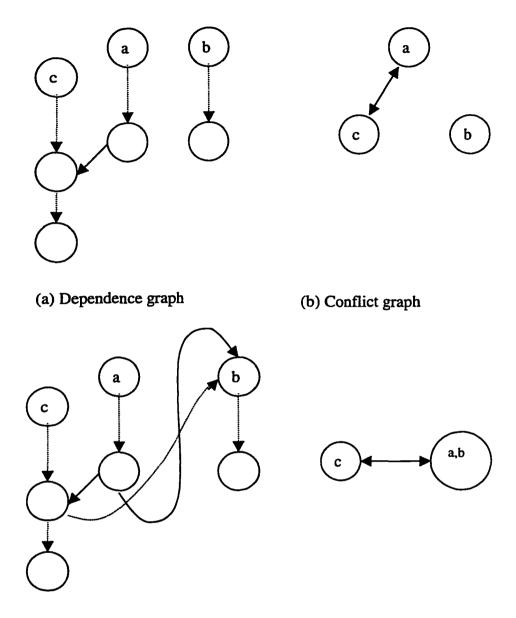

# **4.2.2 Previous Approach**

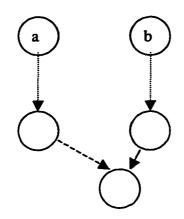

In [8], the source code shown in Figure 4.2 (a) is used to explain the register allocation based on register-reuse chains. Figure 4.2 (b) shows the corresponding dependence graph in which each node corresponds to a statement in the source code. The character in the node represents the name of the variable assigned in the statement. Figure 4.2 (c) shows the register-reuse graph derived from the dependence graph. In this graph, the nodes are the same as those in the dependence graph and an edge shows the possibility of the register-reuse; that is, the successor (destination of the edge) can reuse the register of the predecessor (source of the edge). Let E(a, b) denote the edge from node *a* to *b*. This edge represents that *b* can kill *a*; that is, *b* can reuse the register assigned to *a*. Similarly, E(c, f) represents that *f* can reuse the register for *c*. Note that *f* has another incoming edge from *d*. This means that *f* can reuse both registers for *d* and *c*. However, *f* can reuse only one register. Thus, it is necessary to decide which register *f* reuses. Removing one of the edges coming into *f* can represent this decision. For example, if *c* is chosen to be reused by *f*, then removing edge E(d, f) can represent this decision.

(b) Dependence graph

Figure 4.2 Register allocation example given in [8]

(c) Register-reuse graph

## (d) Register-reuse chains

## Figure 4.2 Continued

In general, in order to use the register-reuse graph for register allocation, a register-reuse graph needs to be transformed into another graph in which each node has at most one predecessor and one successor. Figure 4.2 (d) shows such a graph transformed from Figure 4.2 (c). By removing edges E(d, f), E(e, g), E(j, k) and E(k, l), this graph forms a set of chains in which all nodes have one predecessor and one successor at most. This graph can be used for register allocation in such a way that each chain is mapped to a

register. Thus, all statements in a chain are assigned to the same register. In this figure, a, b, and l are assigned to the same register, while c, f, g, h, i, and k are assigned to the same register. These chains in this graph are called register-reuse chains in [7, 8].

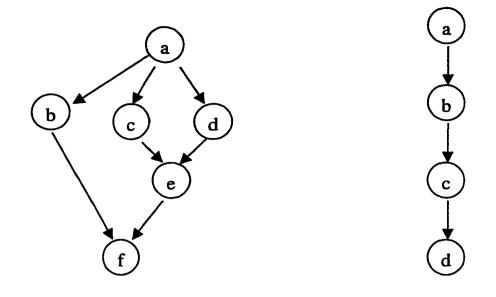

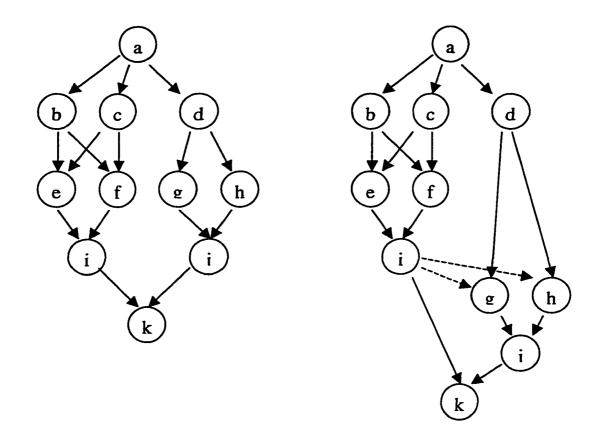

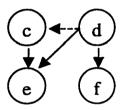

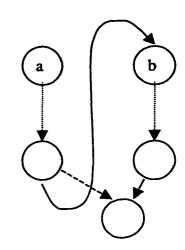

Since each chain is mapped to one register, the number of chains corresponds to the number of necessary registers. For example, the graph in Figure 4.2 (d) requires four registers. If the number of chains is greater than the number of registers, it is necessary to reduce the number of chains. In order to reduce the number of chains, [8] proposes to add dependencies in the dependence graph. For example, consider a new dependence graph as shown in Figure 4.3 (a). Five register-reuse chains are derived in [8]. Suppose that there are only four available registers. Then, [8] suggests to add dependencies from i to g and ito h as shown in Figure 4.3 (b). With the new dependencies, [8] can derive four new reuse chains. More details on the addition of dependencies can be found in [8].

There are many different ways to add dependencies. So optimization is necessary to select which additional dependencies need to be added. In [8], the criterion for the addition of new dependencies is the length of the critical path in the dependence graph. For example, the added dependencies in Figure 4.3 (b) increase the length of the critical path by one. In [8], a method is developed to add dependencies that attempt to minimize the increase of the critical path length. In addition, further optimizations are developed in [8] for the integration of instruction scheduling with the register allocation, the generation of register spill/reload instructions, and the optimization across basic blocks. Since the additional optimizations are not the interest of this research, detailed explanation is omitted.

Figure 4.3 Creation of dependencies for register allocation

### 4.2.3 Possible Improvements

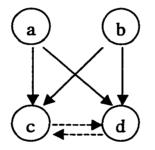

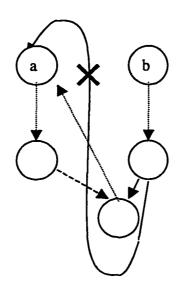

This chapter concentrates on the generation of the register-reuse graph, reuse chains, and the reduction of reuse chains. Improvements are attempted based on the following observations. In the generation of the register-reuse graph, the selection of a possible killing node can affect the efficiency of a scheduler. Recall that the killing node is the node that can reuse the register assigned to its predecessor. The previous research does not have a systematic approach to select the killing node, and consequently can degrade the efficiency of a compiler. For example, consider the following dependence graph shown in Figure 4.4.

Figure 4.4 Example of dependence graph

Suppose that b is selected to reuse the register for a. This forces that c and d must be computed no later than b. Otherwise, a is not available for the computation of c and dbecause a is already replaced by b. Assume that there are only two functional units. Since c and d cannot be executed later than b, a scheduler must force c and d to be executed immediately after the execution of a. Then, node b, e, and f must be executed sequentially due to dependencies between them. This requires 5 steps to complete the computation. Suppose that c is selected to reuse the register of a. Then, b and d need to be scheduled right after a. In the next step, c and e can be scheduled simultaneously. Finally, f is scheduled. This requires four steps to complete the computation. This example shows the importance of the selection of the initial reuse graph. In [8], dependencies are added for reducing the number of register reuse chains. In this phase, it is often the case that there is more than one choice in the selection of dependencies. [8] uses the criterion based on the increase of the length of the critical path in the dependence graph. This criterion is useful when each statement requires the same execution time. However, each statement computes different operations and therefore can have different execution times. In addition, each statement can have a different number of operations that can further differentiate the execution time of a statement. This research proposes a new criterion for the reduction of register-reuse chains. Based on the new criterion, a heuristic is proposed to reduce the register-reuse chains. The new heuristic is designed to be used efficiently for the general case when each statement can have different execution time.

#### 4.3 Register-Reuse Chain and Dependence Analysis

Register allocation is a procedure to decide which variables are stored in registers and which of them share the registers. If two variables are assigned to the same register, their live ranges must not be overlapped. If registers are allocated before instructions are scheduled, register allocation, in general, forces an ordering in the live ranges of variables, resulting in the creation of additional dependencies between instructions that access the variables. However, these additional dependencies can be avoided if the forced ordering complies with existing dependence relationship. This section investigates register allocation that does not create any additional dependencies. First, the creation of dependencies due to register allocation is studied and then an algorithm is proposed to allocate registers without the creation of additional dependencies.

# 4.3.1 Generation of Dependence Due to Register Allocation

The execution results of a given C code do not change with the schedules that comply with the data dependencies. However, when a C code is translated into assembly code, register allocation for each variable is involved and additional dependencies may be introduced by register allocation. Therefore, when instructions are scheduled, these extra dependencies due to register allocation should be taken into consideration in addition to normal data dependencies.