# Louisiana Tech University Louisiana Tech Digital Commons

Graduate School **Doctoral Dissertations**

Fall 2005

# Design and development of poly -(3 - hexylthiophene) field effect transistors

Fengliang Xue Louisiana Tech University

Follow this and additional works at: https://digitalcommons.latech.edu/dissertations

Part of the Electrical and Computer Engineering Commons

#### Recommended Citation

Xue, Fengliang, "" (2005). Dissertation. 587. https://digitalcommons.latech.edu/dissertations/587

This Dissertation is brought to you for free and open access by the Graduate School at Louisiana Tech Digital Commons. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of Louisiana Tech Digital Commons. For more information, please contact digitalcommons@latech.edu.

# DESIGN AND DEVELOPMENT OF POLY(3-HEXYLTHIOPHENE) FIELD EFFECT TRANSISTORS

by

Fengliang Xue, B.S.

A Dissertation Presented in Partial Fulfillment of the Requirement for the Degree of Doctor of Philosophy in Engineering

COLLEGE OF ENGINEERING AND SCIENCE LOUISIANA TECH UNIVERSITY

November 2005

UMI Number: 3192321

#### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

#### UMI Microform 3192321

Copyright 2006 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

### LOUISIANA TECH UNIVERSITY

#### THE GRADUATE SCHOOL

|                             |                   |          |              |               | 11/02/     | 2005      |             |             |

|-----------------------------|-------------------|----------|--------------|---------------|------------|-----------|-------------|-------------|

|                             |                   |          |              |               |            |           |             | Date        |

| We hereby                   | recommend that    | the      | dissertation | prepared      | under      | our       | superv      | ision       |

| by Fengliang Xue            |                   |          |              |               |            |           |             |             |

| entitled Design and [       | Development of Po | oly(3-he | xylthiophen  | e) Field Effe | ct Trans   | sistors   |             |             |

| be accepted in              | partial fulfillme | nt of    | the re       | quirements    | for        | the       | Degree      | of          |

| Ph.D. in Engineering        | •                 |          |              | •             |            |           |             |             |

|                             |                   |          |              |               | 1/         |           |             |             |

|                             |                   |          |              |               | $V_{i}$    | 301       |             |             |

|                             |                   |          |              | Suj           | pervisor o | of Disse  | rtation Res | earch       |

|                             |                   | _        |              | 1             | 7          |           | d of Depar  | _           |

|                             |                   |          |              | pr-           | L.D. iv    | n Eng     | neero       | ng<br>tment |

| Recommendation concur       | rad in:           |          |              |               |            |           | <b>-</b>    |             |

| Mis                         | m_                |          |              |               |            |           |             |             |

|                             |                   |          |              |               |            |           |             |             |

| - Cels                      |                   | اد A     | viaom: Comm  | aittaa        |            |           |             |             |

| Yuti )                      | LVOV              | Au       | visory Comn  | niuee         |            |           |             |             |

| (B/1)                       |                   |          |              |               |            |           |             |             |

| Approved Janu               | rchaudran         |          |              | Jum           | M          |           | pproved:    | W           |

| Director of Graduate Studie | S                 |          |              | `             | \ Dean o   | of the Gr | raduate Sch | 100         |

| Dean of the College         |                   |          |              |               |            |           |             |             |

GS Form 13 (5/03)

#### APPROVAL FOR SCHOLARLY DISSEMINATION

The author grants to the Prescott Memorial Library of Louisiana Tech University the right to reproduce, by appropriate methods, upon request, any or all portions of this Dissertation. It is understood that "proper request" consists of the agreement, on the part of the requesting party, that said reproduction is for his personal use and that subsequent reproduction will not occur without written approval of the author of this Dissertation. Further, any portions of the Dissertation used in books, papers, and other works must be appropriately referenced to this Dissertation.

Finally, the author of this Dissertation reserves the right to publish freely, in the literature, at any time, any or all portions of this Dissertation.

Date 11/09/2005

GS Form 14 (5/03)

#### ABSTRACT

Organic field effect transistors (OFETs) with poly(3-hexylthiophene) (P3HT) as the active layer are developed and studied. The device characteristics are significantly affected by source/drain contact resistance, and P3HT-SiO<sub>2</sub> interface and the traps. These results are verified by the numerical device simulations. The temperature dependence of device mobility is studied, which indicates that the carrier transport is either heat-assisted or heat-limited at different temperature ranges. The on/off ratio and threshold voltage are found to be dependent on the temperature. Hysteresis effect due to gate electric stress is investigated. The silanol groups present at the SiO<sub>2</sub> surface are thought to be the key factor, which could trap the gate-induced electrons forming immobile negative ions, and shift the device threshold voltage.

Replacing gold with modified poly(3,4-ethylenedioxythiophene)-polystyrene sulfonate (PEDOT-PSS) for the source/drain electrodes, reduces contact resistance and leads to an improved device performance. The SiO<sub>2</sub> surface is also improved. Annealing the SiO<sub>2</sub> surface prior to the deposition of the P3HT layer is found to improve the performance of the device significantly. The device mobility is increased from 0.01 to 0.026 cm<sup>2</sup>/Vs, the on/off ratio increased from 2.3×10<sup>3</sup> to 8.2×10<sup>3</sup>, and subthreshold slope decreased from 3.6 to 2 V/dec. The enhanced device performance is attributed to the possible reduction of physically adsorbed water molecules and hydroxyl groups at the SiO<sub>2</sub> surface upon annealing.

Polymer heterostructure OFETs are also developed for establishing a method to fabricate new devices and the possibility to increase the device performance. This idea stems from the conventional inorganic modulation doped field effect transistors (MODFETs) that have shown strikingly high carrier mobility. The operation of conventional MODFETs is based on the technique of "modulation doping" which provides a good means of introducing carriers into the conduction layer without the adverse effects of donors. A polymer heterojunction structure is made of P3HT and poly(9,9-dioctylfluorenyl-2,7-diyl) (PFO) and is integrated into a field effect transistor. The resulting device characteristic shows the "modulation doping" effect. To our knowledge, the modulation doping effect with a polymer heterojunction has not been reported so far. This finding opens a potential pathway to improve the OFETs' device performance.

# TABLE OF CONTENTS

| LIST OF TABLES                                      | viii |

|-----------------------------------------------------|------|

| LIST OF FIGURES                                     | ix   |

| ACKNOWLEDGEMENTS                                    | xii  |

| CHAPTER ONE INTRODUCTION                            | 1    |

| 1.1 Organic Thin Film Transistor                    | 1    |

| 1.1.1 Active Channel – Organic Semiconductor        |      |

| 1.1.1.1 Poly(3-hexylthiophene)                      |      |

| 1.1.1.2 Other organic semiconductors                |      |

| 1.1.2 Gate Dielectric – Insulator                   |      |

| 1.1.3 Electrodes – Conductor                        |      |

| 1.2 Technology Computer Assisted Design             |      |

| 1.2.1 Overview                                      |      |

| 1.2.2 Device Simulation.                            |      |

| 1.3 Dissertation Objectives                         |      |

| 1.4 Organization of this Dissertation               |      |

| CHAPTER TWO THEORETICAL BACKGROUND                  | 13   |

| 2.1 Charge Transport in Polymeric Semiconductors    | 13   |

| 2.1.1 Overview                                      | 13   |

| 2.1.2 Hopping                                       | 16   |

| 2.1.3 Field Dependent Mobility                      | 16   |

| 2.1.4 Multiple Trapping and Release                 | 16   |

| 2.2 Operation of Polymeric Field Effect Transistors | 17   |

| 2.2.1 Energy Band Diagrams                          | 18   |

| 2.2.2 Current-Voltage Characteristics               | 19   |

| 2.2.3 Contact Resistance Effects                    | 22   |

| 2.2.4 Trapping Effects                              | 24   |

| 2.2.5 Gate Bias-Dependence Mobility                 | 26   |

| CHAPTER THREE FABRICATION AND CHARACTERIZATION      | 27   |

| 3.1 Introduction                                                | 27                   |

|-----------------------------------------------------------------|----------------------|

| 3.2 Inkjet Printing                                             | 27                   |

| 3.2.1 Introduction                                              |                      |

| 3.2.2 Suitable Inks                                             | 28                   |

| 3.2.3 Coffee-Drop Effect                                        | 29                   |

| 3.2.4 Microdrop Inkjet Printing System                          |                      |

| 3.3 Spin Coating                                                |                      |

| 3.4 Device Characterization                                     |                      |

| 3.4.1 Keithley Probe Station                                    | 33                   |

| 3.4.2 Required Measurements                                     |                      |

| 3.4.3 Guidelines for OFET Characterization                      | 34                   |

| CHAPTER FOUR POLY (3-HEXYLTHIOPHENE) FET                        | 36                   |

| 4.1 Introduction                                                | 36                   |

| 4.2 Device Fabrication                                          | 37                   |

| 4.3 Results and Discussion                                      | 38                   |

| 4.3.1 Device Characteristics                                    | 38                   |

| 4.3.2 Gate Voltage Dependent Mobility                           | 43                   |

| 4.3.3 Temperature Dependence of Mobility                        | 44                   |

| 4.3.4 Hysteresis                                                | 47                   |

| 4.4 Summary                                                     | 50                   |

| CHAPTER FIVE MODELING AND SIMULATION OF P3HT FET                | 51                   |

| 5.1 Introduction                                                | 51                   |

| 5.2 Description of the Models                                   | 52                   |

| 5.3 Device Structure                                            |                      |

| 5.4 Results and Discussion                                      | 55                   |

| 5.4.1 Channel Formation                                         | 56                   |

| 5.4.2 Simulation with Trapping Effect                           | 58                   |

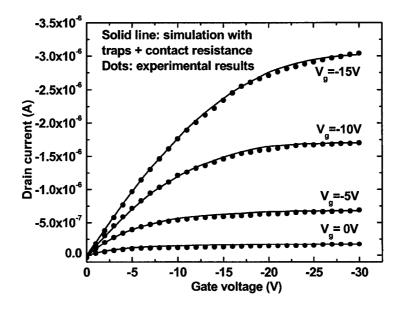

| 5.4.3 Simulation with Traps Coupled with Contact Resistance     | 59                   |

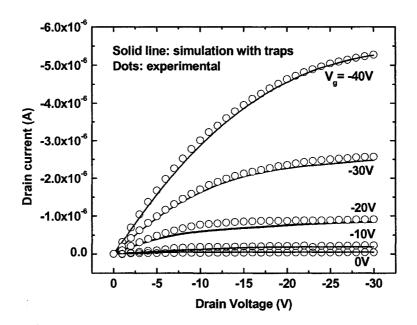

| 5.4.4 Simulations on Devices with Low Contact Resistance Effect | 61                   |

| 5.5 Summary                                                     | 62                   |

| CHAPTER SIX P3HT FET WITH ENHANCED PERFORMANCE                  | 63                   |

| 6.1 Introduction                                                | 63                   |

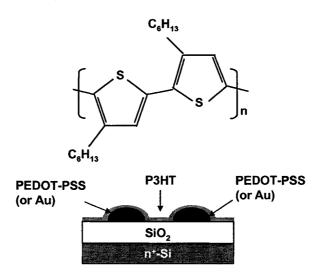

| 6.2 Improving S/D Contact                                       | 64                   |

| 6.2.1 Experiments                                               |                      |

| 6.2.2 Results and Discussion                                    | 64                   |

| 6.3 Improving the P3HT-SiO <sub>2</sub> Interface               | 64<br>66             |

|                                                                 | 64<br>66<br>75       |

| 6.3.1 Experiments                                               | 64<br>66<br>75       |

| 6.3.1 Experiments                                               | 64<br>66<br>75<br>75 |

| CHAPTER SEVEN POLYMER MODULATION DOPED FET         | 79  |

|----------------------------------------------------|-----|

| 7.1 Introduction                                   | 79  |

| 7.2 Polymer Heterostructure                        |     |

| 7.3 Device Fabrication                             |     |

| 7.4 Results and Discussion                         |     |

| 7.5 Summary                                        |     |

| CHAPTER EIGHT CONCLUSIONS AND FUTURE WORK          | 89  |

| 8.1 Conclusions                                    | 89  |

| 8.2 Future Work                                    |     |

| 8.2.1 Side Effects of Solvents                     |     |

| 8.2.2 Leakage Current                              | 92  |

| 8.2.3 Polymer Modulation Doped OFET                |     |

| 8.2.4 Treatments of Gate Silicon Oxide             |     |

| 8.2.5 Inkjet Printing Technique                    |     |

| 8.2.6 Other Issues                                 |     |

| APPENDIX A TAURUS-DEVICE INPUT SIMULATION COMMANDS | 96  |

| REFERENCES                                         | 105 |

## LIST OF TABLES

| Table 5-1 Basic material parameters used in simulation                   | .55 |

|--------------------------------------------------------------------------|-----|

| Table 6-1 Extracted parameters using conventional MOSFET equations with  |     |

| and without considering the parasitic series resistance ('corrected'     |     |

| represents extraction taking into account parasitic series resistance)   | .70 |

| Table 6-2 Comparison of device parameterss between devices with annealed |     |

| and non-annealed SiO <sub>2</sub>                                        | .78 |

# LIST OF FIGURES

| Figure 1-1 | A schematic structure of a typical OFET                                             | 2   |

|------------|-------------------------------------------------------------------------------------|-----|

| Figure 1-2 | Packing orientation of P3HT films relative to substrate with (a) 95%                |     |

| _          | and (b) 81% regionegularity, as determined by X-ray diffraction [7]                 | 4   |

|            | A typical TCAD flow [42]                                                            | 9   |

| Figure 2-1 | (a) The molecular structure of polyacetylene. The alternating single                |     |

|            | and double bonds indicate that the polymer is conjugated.                           |     |

|            | (b) Schematic representation of the electronic bonds in                             |     |

|            | polyacetylene [44]                                                                  | 14  |

| Figure 2-2 | Charge transport mechanisms in solids: (a) band transport in a crystal              |     |

|            | structure, such as, silicon and (b) hopping transport in an amorphous               |     |

|            | structure such as conjugated polymer [44].                                          | 15  |

| Figure 2-3 | Schematic structures of a TFT with (a) bottom-contact and                           |     |

|            | (b) top-contact configuration                                                       | 18  |

| Figure 2-4 | Energy gap diagram of a MIS structure with p-type semiconductor                     |     |

|            | under (a) lat band condition, (b) accumulation, and (c) depletion.                  |     |

|            | LUMO and HOMO apply for organic semiconductors                                      | 19  |

| _          | Channel formation in a TFT                                                          | 20  |

| Figure 2-6 | The effect of immobile negative ions on the electric field at the                   |     |

|            | SiO <sub>2</sub> surface, (a) ions enhance the gate electric field and              |     |

|            | (b) ions compensate the gate electric field. The length of the arrows               |     |

|            | schematically represents the amplitude of the electric field                        | 26  |

| Figure 3-1 | Schematic representation of a drop-on-demand ink-jet printing                       |     |

|            | system [63]                                                                         | 28  |

|            | The Microdrop Dispensing System                                                     | 30  |

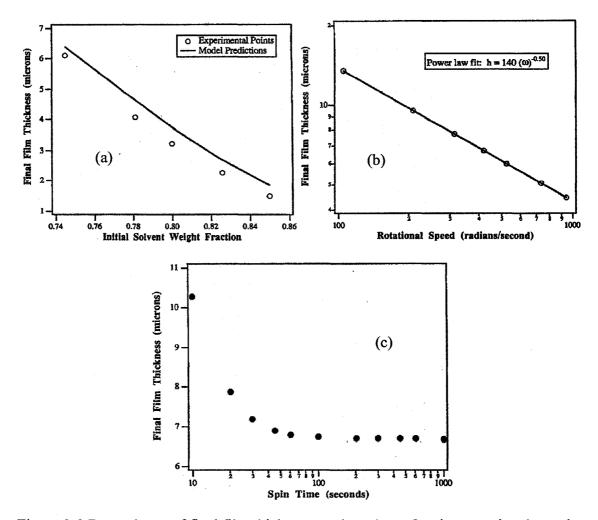

| Figure 3-3 | Dependence of final film thickness on the solvent fraction, rotational              |     |

|            | speed, and spin time (Du Pont PI2525 polyimide was used) [68]                       | 32  |

|            | Photograph of Keithley probe station                                                | 33  |

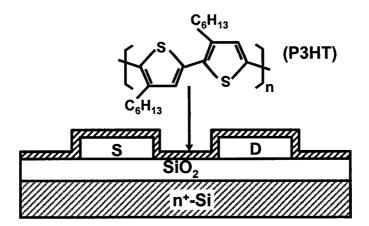

| Figure 4-1 | Schematic cross section of P3HT FET structure, along with                           | 2.5 |

| T' 40      | the molecular structure of P3HT                                                     | 37  |

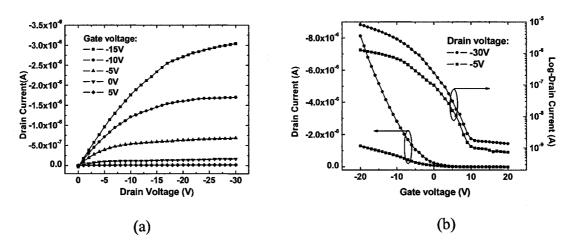

| Figure 4-2 | Output (a) and transfer (b) characteristics of poly(3-hexylthiophene)               | 20  |

|            | FETs                                                                                | 38  |

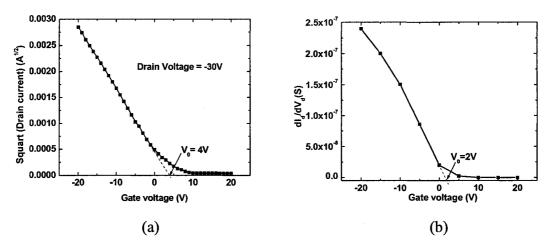

| Figure 4-3 | (a) $I_d^{1/2}$ vs. $V_g$ in the saturation regime and (b) $dI_d/dV_d$ vs. $V_g$ in |     |

|            | the linear regime                                                                   | 40  |

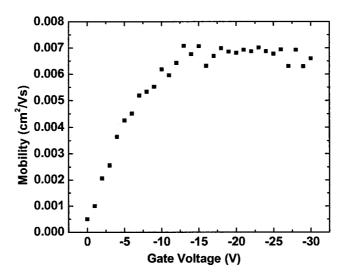

| Figure 4-4 | Figure 4-4 Mobility versus the gate voltage in P3HT FETs without                    |     |

|            | considering the contact resistance                                                  | 41  |

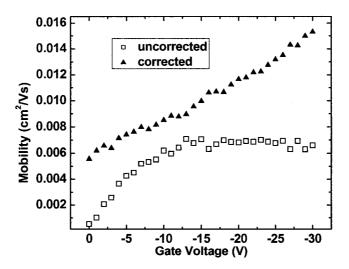

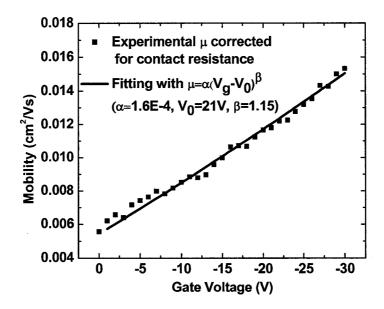

| _          | Mobility versus gate voltage corrected for the contact series resistance            |     |

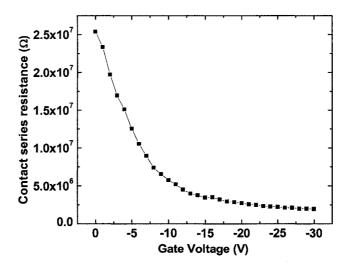

| Figure 4-6 | Contact series resistance as a function of the gate voltage                         | 43  |

| Figure 4-7  | Mobility versus gate voltage                                                                   | 44  |

|-------------|------------------------------------------------------------------------------------------------|-----|

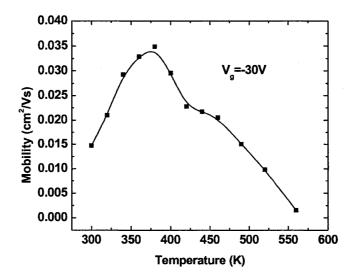

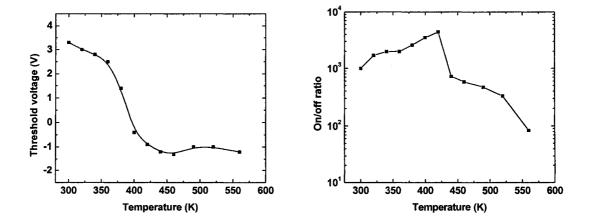

| Figure 4-8  | Mobility versus the operation temperature                                                      | 4   |

|             | (a) Threshold voltage and (b) on/off ratio versus temperature in the                           |     |

|             | linear region $(V_d = -3V)$ .                                                                  | 46  |

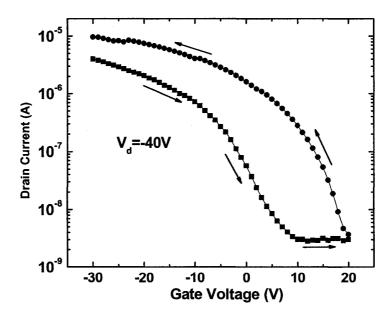

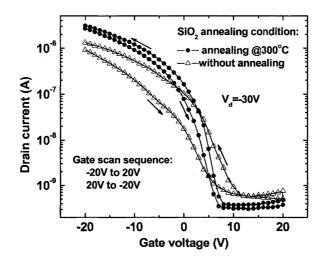

| Figure 4-10 | Hysteresis behavior in a P3HT FET. Arrows represent the                                        |     |

|             | gate voltage scan directions                                                                   | 47  |

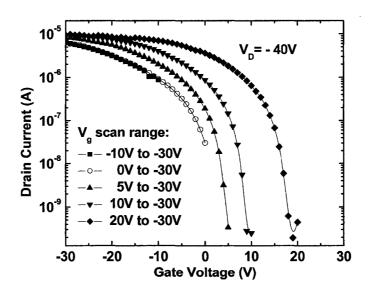

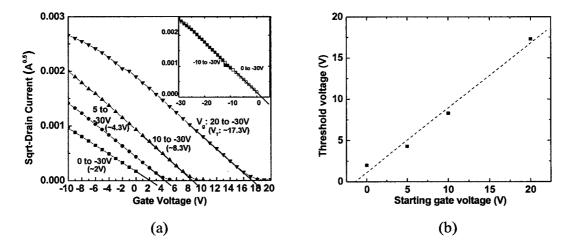

| Figure 4-11 | Transfer characteristics of a P3HT FET starting with various sweep                             |     |

|             | gate voltages                                                                                  | 48  |

| Figure 4-12 | (a) Square root of drain current versus gate voltage of the P3HT FET                           |     |

|             | under various gate sweep conditions and (b) threshold voltage versus                           |     |

|             |                                                                                                | 49  |

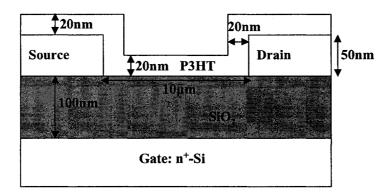

| Figure 5-1  | Schematic representation of the P3HT OFET structure                                            | 54  |

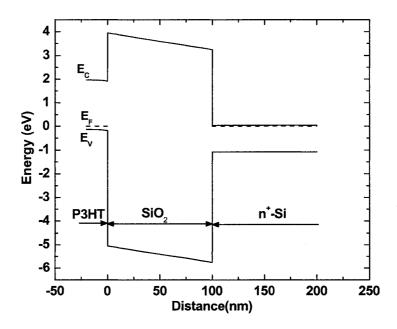

| Figure 5-2  | Energy level diagram of the MIS (n <sup>+</sup> -Si-SiO2-P3HT) structure under                 |     |

|             | 1                                                                                              | 56  |

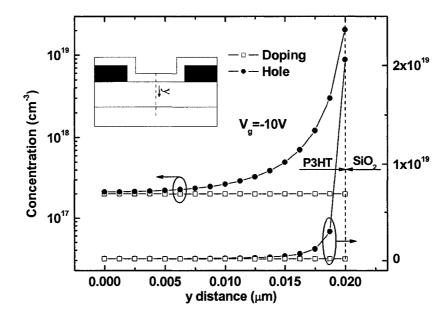

| Figure 5-3  | Hole concentration profile in the channel along the direction normal                           |     |

|             | to P3HT-SiO <sub>2</sub> interface. The inset shows the cut line at the center of              |     |

|             | the channel. P3HT surface is the starting point                                                | 57  |

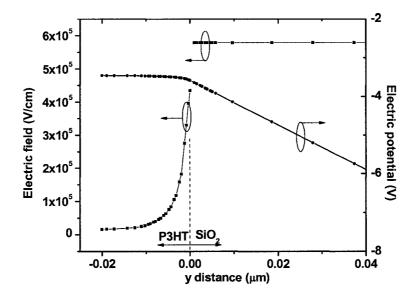

| Figure 5-4  | Electric field and potential profile in P3HT channel and part of SiO <sub>2</sub> ,            |     |

|             | cut line was chosen at the center of the device. P3HT surface is the                           | 50  |

| T).         | starting point                                                                                 | 58  |

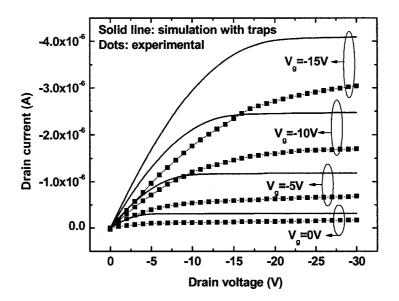

| Figure 5-5  | Output characteristics of OFETs including bulk traps of 6×10 <sup>17</sup> cm <sup>-3</sup>    | 50  |

| F: 5.6      | $(E_t=0.5eV).$                                                                                 | 59  |

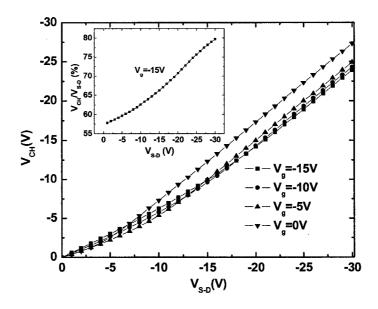

| Figure 5-6  | Effective channel voltage as a function of the applied S-D voltage with                        |     |

|             | the effect of the contact resistance. The inset shows the percentage of $\frac{1}{2}$          | 60  |

| Figure 5 7  | channel voltage as a part of the total source-drain voltage at V <sub>g</sub> =-15V            | 60  |

| Figure 5-7  | Output characteristics of OFETs including bulk traps and contact                               | 60  |

| Figure 5 9  | resistance Simulation results of OFETs with low contact resistance effect                      | 00  |

| Figure 5-8  | including only traps model                                                                     | 61  |

| Figure 6-1  | Schematic diagram of P3HT field effect transistor with inkjet printed                          | 01  |

| riguie 0-1  | PEDOT-PSS or gold as S/D electrodes. The chemical structure of P3HT                            |     |

|             | is also shown                                                                                  | 65  |

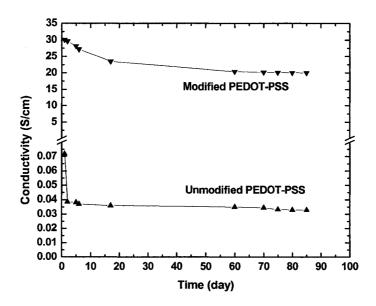

| Figure 6-2  | The variations of conductivities of the modified and unmodified                                | 05  |

| 1 iguic 0-2 | PEDOT- PSS as a function of time in air at room temperature                                    | 66  |

| Figure 6-3  | The variation of resistance of a modified PEDOT-PSS resistor as a                              | 00  |

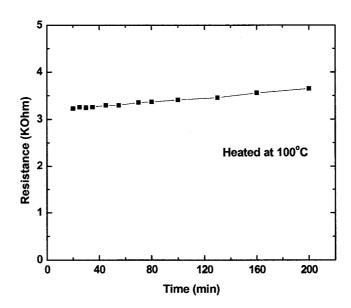

| 1 15410 0 5 | function of time. The resistor washeated at 100°C in the air                                   | .67 |

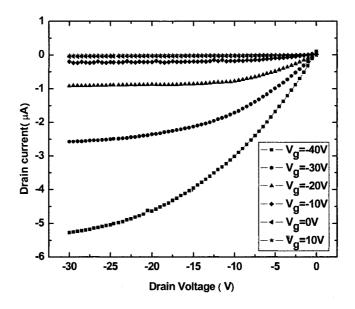

| Figure 6-4  | Output characteristic of P3HT TFT with modified PEDOT-PSS S/D                                  |     |

| 1.80.10     | electrodes                                                                                     | 68  |

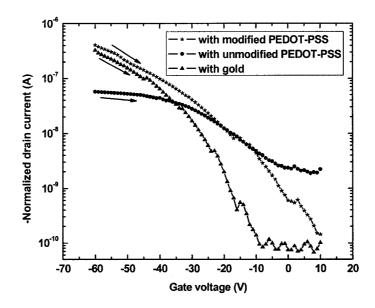

| Figure 6-5  | Normalized output characteristics of P3HT TFTs in the saturation                               |     |

|             | regimes. Arrows represent the sweep direction of gate voltages                                 | 69  |

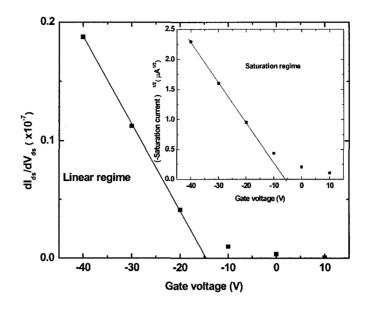

| Figure 6-6  | Plot of dI <sub>DS</sub> /dV <sub>DS</sub> as a function of gate voltage in the linear regime. |     |

|             | The inset shows the square root of saturation current as a function of                         |     |

|             | gate voltage                                                                                   | 70  |

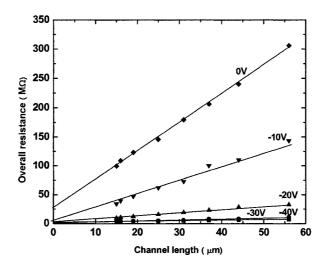

| Figure 6-7  |                                                                                                |     |

| •           | voltages from 0 to -40V for the devices with modified PEDOT-PSS                                | 72  |

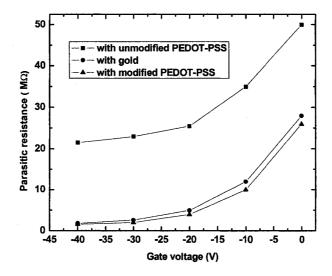

| Figure 6-8  | Parasitic series resistance as a function of gate voltage for the devices with modified PEDOT-PSS, gold, and unmodified PEDOT-PSS        | 72 |

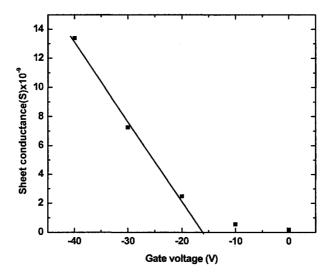

|-------------|------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 6-9  | Sheet conductance of the active channel region as a function of gate                                                                     |    |

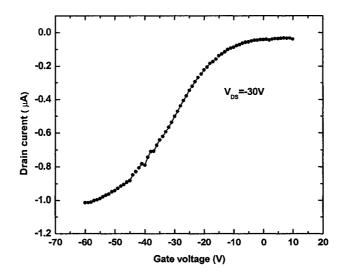

| Figure 6-10 |                                                                                                                                          | /3 |

|             | unmodified PEDOT-PSS source/drain electrodes at $V_{DS}$ =-30V. The                                                                      |    |

|             | drain current appears to saturate at high negative gate voltage                                                                          | 75 |

| Figure 6-11 | Transfer characteristics of P3HT FETs with annealed and                                                                                  |    |

|             | non-annealed SiO <sub>2</sub>                                                                                                            | 77 |

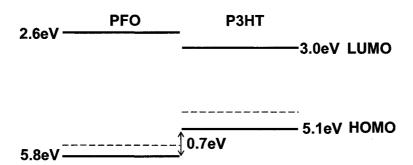

| Figure 7-1  | Energy level schematic diagram of PFO and P3HT before contact                                                                            | 81 |

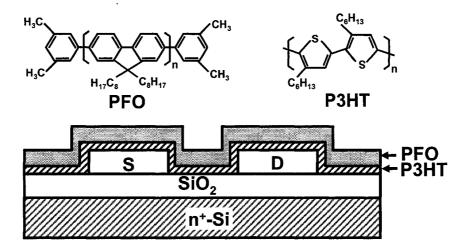

| Figure 7-2  | A schematic cross-section of a fabricated quantum-well polymer field effect transistor (SiO <sub>2</sub> : 100nm, P3HT: 20nm, PFO: 40nm, |    |

|             | S/D: 500Å gold/30Å titanium, channel length: 10µm, and channel                                                                           |    |

|             | width: 500µm). The molecular structures of PFO and P3HT are also                                                                         |    |

|             | shown                                                                                                                                    | 83 |

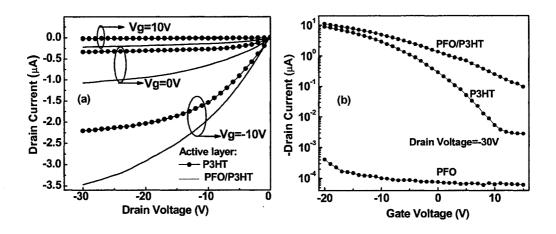

| Figure 7-3  | (a) Output characteristics and (b) transfer characteristics of the P3HT-                                                                 |    |

|             | only and the PFO/P3HT FETs. For comparison, the transfer                                                                                 |    |

|             | characteristics of a PFO FET in the same device configuration are                                                                        |    |

|             | shown in (b)                                                                                                                             | 84 |

| Figure 7-4  | Schematic energy band diagrams of PFO and P3HT after contact in                                                                          |    |

|             | the thermal equilibrium. The inset shows the confined holes                                                                              | 85 |

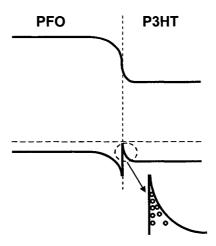

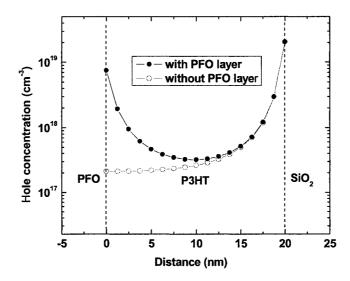

| Figure 7-5  | Simulated hole concentration profile in the P3HT layer with and                                                                          |    |

|             | without PFO layer in contact with it (at $V_g=-10V$ ). The cut line is                                                                   |    |

|             | chosen at the center of the device.                                                                                                      | 86 |

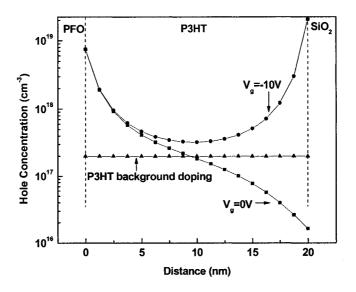

| Figure 7-6  | Simulated hole concentration profile in the P3HT layer in the                                                                            |    |

|             | P3HT-PFO heterojunction at different gate biases. The cut line                                                                           |    |

|             | is chosen at the center of the device                                                                                                    | 87 |

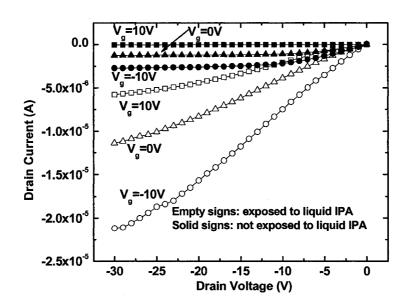

| Figure 8-1  | P3HT device characteristics showing the side effect of isopropyl                                                                         |    |

|             | alcohol                                                                                                                                  | 91 |

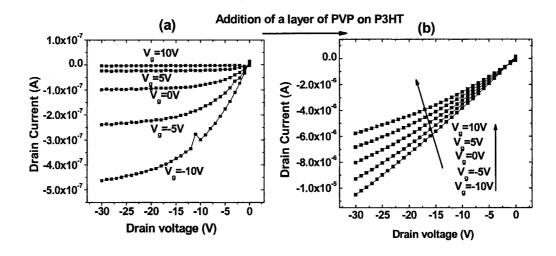

| Figure 8-2  | P3HT device characteristics showing the effect of PVP cast from                                                                          |    |

|             | isopropyl alcohol solution (a) without PVP layer and (b) with PVP                                                                        |    |

|             | layer on P3HT                                                                                                                            | 92 |

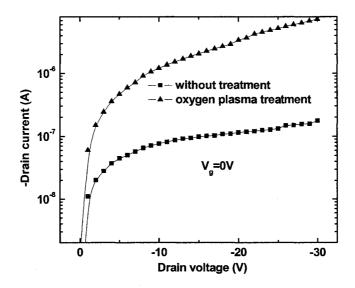

| Figure 8-3  | P3HT FFT drain leakage current at V=0V                                                                                                   | 93 |

#### **ACKNOWLEDGEMENTS**

I am very grateful to my thesis advisor, Dr. Yi Su, for his attention, kindness, guidance and support throughout these years at Louisiana Tech University. I am also grateful to Dr. Kody Varahramyan, my co-advisor, for his support and insightful direction in my research. Deep gratitude is also for Dr. Chester Wilson, Dr. Yuri Lvov, and Mr. Ji Fang, for their advice and serving on the advisory committee for this dissertation.

I am indebted to many people at the Institute for Micromanufactruing for their technical supports. Special thanks are extended to Dr. Alfred Gunasekaran for proofreading this dissertation.

I would like to thank Dr. Bala Ramachandran and the College of Engineering and Science for extending my graduate assistantship to the fourth year.

I am fortunate to have worked with a wonderful group of graduate students, and I would like to thank all of them for their mental and emotional support and helpful discussions and advice. They are Zhengchun Liu, Rajneek Kumar Khillan, Razat Nohria, Rohit Dikshit, Jie Liu, Merugu Kapil, Neha Goel, and Ganga Parthasarathi.

I am blessed I met my wife here. She makes my life magnificent and valuable. I thank my parent-in-laws for their unreserved support. My parents are my unending support. Without their love and encouragement, anything I have achieved today is impossible. I hope that I am living a life they are proud of.

xii

#### CHAPTER ONE

#### INTRODUCTION

#### 1.1 Organic Thin Film Transistor

Organic electronics have attracted tremendous research efforts over the last twenty years. It offers several advantages over the traditional inorganic semiconductor technologies for low cost, easy processing, good compatibility with a variety of substrates including flexible plastics and low temperature processing with little or no vacuum process involved. The interests in organic electronics are mostly driven by the demand for low cost, large area, flexible and lightweight devices. Organic light emitting diodes (OLEDs) and organic field effect transistors (OFETs) are two mainstream technologies in this area. OLED technology is now being commercialized, and there is a tremendous market for such devices. OLEDs have already been used in small displays in cellular phones, digital cameras, handheld computer games, and other consumer devices [1]. Meanwhile, OFET has also received considerable attention, although on a reduced scale. Since the first organic field effect transistor was reported in 1986 [2], there has been a very impressive progress both in the development of new fabrication techniques and the materials performance. OFETs have been demonstrated in applications, such as electronic paper, sensors, and memory devices including radio-frequency identifications tags [3-4]. Although they are not intended to replace conventional inorganic counterparts due to the upper limit of the switching speed, they have a great potential for a wide variety of applications, such as electronic newspapers, low-end smart tags, and large-area drive circuits for flexible displays [5].

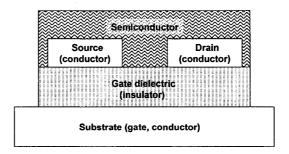

A field effect transistor (FET) with organic material as the semiconductor is normally called organic FET. An organic FET consists of materials ranging from conductors and semiconductors, to insulators. A typical device structure is shown in Figure 1-1. Here, the gate electrode, insulated from the semiconductor by an insulator, is used to control the current flow between the source and drain electrodes. A transistor is called p-channel device if the major charge carrier is hole, and on the contrary n-channel device when the major charge carrier is electron.

Figure 1-1 A schematic structure of a typical OFET.

#### 1.1.1 Active Channel – Organic Semiconductor

One important feature that makes organic semiconductor attractive is the possibility for them to be deposited from solution for low-cost manufacturing. However, only a small number of soluble p-type organic semiconductors have been reported to show high performance, and a very few n-type organic semiconductors are soluble with reasonably high mobility. In order to build transistors with high mobility from solutions,

the materials should be soluble, and it should be possible to create large-area uniform films, in which the semiconducting molecules are desired to be well-ordered. The  $\pi$ -stacking between these molecules forms the conducting path for charge carriers to hop from one molecule to another molecule. However, with highly ordered materials it is usually difficult to form uniform films due to their high crystallinity. In contrast, polymers can easily form uniform films, but it is more difficult to obtain polymer films with high ordering. The polymer that gets around these two limitations is the regionegular poly (3-hexylthiophene) [6]. Therefore in our work, P3HT was selected for field effect transistor to demonstrate our strategies for improving OFET's performance.

#### 1.1.1.1 Poly(3-hexylthiophene)

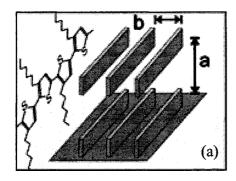

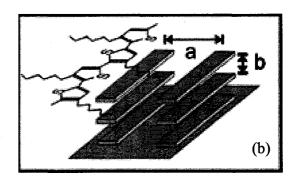

Poly(3-hexylthiophene) (P3HT) has been of particular interest due to its self-organizing properties to form a microcrystalline structure in films. Self-organization in P3HT results in a lamellar structure with two-dimensional conjugated sheets formed by interchain stacking [7]. Differences in the regioregularity in P3HT samples have been found to cause markedly different orientations relative to the substrate. As shown in Figure 1-2, the lamellae can adopt two different orientations: parallel and perpendicular to the substrate, the mobilities of which differ by more than a factor of 100. In samples with high regioregularity (96%) and low molecular weight, the preferential orientation of ordered domains is with the (100)-axis normal to the film and the (010)-axis in the plane of the film (Figure 1-2a). Here (100)-axis is with the lamella layer structure ("a" in Figure 1-2a) and (010)-axis is with  $\pi$ - $\pi$  interchain stacking ("b" in Figure 1-2a). In contrast, in samples with low regioregularity (81%) and high molecular weight, the crystallites are

preferentially oriented with the (100)-axis ("a" in Figure 1-2b) in the plane and the (010)-axis ("b" in Figure 1-2b) normal to the film.

Charge modulation spectroscopy (CMS) has been used to study the charge carriers present in region-regular P3HT [8]. It was demonstrated that the CMS spectra of charge carriers in high-mobility region-regular P3HT FET's are independent of charge density, modulation frequency, and temperature. This was the evidence for the presence of a single, intrinsic charge carrier that was identified as a singly charged polaron.

Figure 1-2 Packing orientation of P3HT films relative to substrate with (a) 95% and (b) 81% regioregularity, as determined by X-ray diffraction [7].

P3HT can be dissolved in a variety of solvents, such as chloroform, chlorobenzene, tetrahydrofuran, p-xylene and toluene, etc. It has been noted that the field-effect mobility can vary significantly with different solvents [9]. The mobility as high as 0.2 cm<sup>2</sup>/Vs has been reported with P3HT film cast from chloroform solution and the SiO<sub>2</sub> gate dielectric covered with a hydrophobic self-assembly monolayer [10]. It was recently found that the dependence of mobility on the solvents could be related to the boiling points of the solvents [11]. Low boiling and rapid evaporation limit time for crystallization during spin coating process resulting in lower field effect mobility. Solution processes, such as drop casting, contact printing, Langmuir-Blodgett deposition,

dip coating, spin coating, and inkjet printing can be used to deposit P3HT films [12] [13] [14] [15]. One drawback of P3HT is that it is sensitive to moisture and oxygen when it is exposed to air, leading to the degradation of the device performance [16].

#### 1.1.1.2 Other organic semiconductors

Examples of other organic semiconductors include p-type materials such as Cuphthalocyanine [17], tetracene [18], phthalocyanine [19],  $\alpha$ -sexithiophene [20], pentacene [21],  $\alpha$ - $\omega$ -dihexyl-sexithiophene [22], poly[2-methoxy-5(2'-ethyl-hexyloxy)-1,4-phenylene vinylene] (MEH-PPV) [23], poly(9-9'-dioctyl-fluorene-co-bithiophene) [24], and dihexyl-anthradithiophene [25], etc., and n-type materials such as C<sub>60</sub> [26], TCNQ [27], F<sub>16</sub>CuPc [28], and NTCDA [29]. It should be noted that most of the work to date has focused on p-type materials. The disproportionate development of p-type OFETs vs. ntype should be due to the inherent instability of n-type organic materials that react with water and oxygen under operating conditions, thus offering unstable devices [30]. Two methods have been proposed to improve the stability of n-type organic semiconductors in air. One is achieved by carefully tuning the electron affinity of n-type materials, since the stability of n-type doped materials depends strongly on the value of the overpotential associated with the chemical processes. The other is accomplished by kinetically inhibiting the undesired redox processes. For example, the incorporation of hydrophobic functionalities into the chemical structure of the organic semiconductor could thwart the penetration of water [30].

#### 1.1.2 Gate Dielectric - Insulator

As compared to the extensive research efforts on organic semiconductors, there has not been much research on dielectric materials so far, even though they are extremely

crucial for high-performance and reliable organic devices. The basic requirements for such dielectric materials are their ability to form thin, pinhole-free films with a high breakdown voltage and good long-term stability. Additionally, the dielectric material should be compatible with organic semiconductors. For instance, the dielectric films must have low surface trapping density, low surface roughness, low impurity concentration and must not degrade the performance of ordered organic semiconducting films [6]. Silicon dioxide has been the most extensively used dielectric material so far, since it possesses most of the desired features and it offers a simple fabrication process for organic devices that are built on the silicon substrate. However, the natural hydroxyl groups present at the SiO<sub>2</sub> surface acted as surface traps reducing the hole mobility and quenching n-channel FET activity of organic semiconductors that do not have sufficiently large electron affinities [31] [32]. Pre-treatment of the Si-SiO<sub>2</sub> substrate with silylating agents replacing the hydroxyl groups with non-polar alkyl group has resulted in hole mobility of as high as 0.1cm<sup>2</sup>/Vs [31] and ambipolar activity [32] in P3HT FETs. A number of organic dielectric materials have also been found to give reasonable transistor performance. Examples are poly(methyl methacrylate) [33], poly(vinylphenol) [34], and polyimide [35]. From reliability and manufacturing yield considerations, a minimum dielectric layer thickness of 1000Å or more is necessary for large-area electronics [30]. Thicker dielectric layers are more suitable for large area applications since they suppress the formation of pinholes and the problems with step coverage. In this sense, a higher dielectric constant gate insulator is the more appropriate solution for low operationvoltage OFETs [36]. However, exceptional examples are known to exist. For example, recently, thin (2.3-5.5nm) self-assembled organic dielectric multilayers were integrated into OFET structures to achieve sub-1V operating characteristics [37]. It was claimed that these thin dielectrics were smooth, nanostructurally well defined, strongly adherent, thermally stable, virtually pinhole-free, and with excellent insulating properties.

#### 1.1.3 Electrodes – Conductor

Besides the organic semiconductor and gate dielectric, the conductor material, as the third component in an OFET's structure, has decisive impacts on the device electrical characteristics. The heavily doped silicon substrate is commonly used as the gate electrode for a simple fabrication process. Gate contact normally would affect the operation voltage of the OFET, but not at a significant level since organic devices normally operate at high voltages. For the source and drain electrodes, specific requirements need to be met. They have to be energetically well-matched with the organic semiconductor layer so that ohmic contact can be formed to allow efficient charge injection. For p-channel OFETs, charge carriers are holes. They are injected from or onto the highest occupied molecular orbital (HOMO) levels of the organic semiconductors. High work function conductors are usually preferred for an efficient injection due to a low injection barrier. On the other hand, n-channel OFETs, charge carriers are electrons. Conductors with low work function are normally required to achieve efficient injection of electrons from the lowest unoccupied molecular orbital (LUMO) levels of the organic semiconductors. Among those contact metals that have been employed in organic electronic devices, gold is the most frequently used one. It was found to form ohmic contact with many p-type organic semiconductors, resulting in good device performance. For n-type FET, electrode materials are usually metals of low work function, such as Ca, and Mg. However, they are very reactive in air and require a vacuum or inert environment for device preparation. Since the inkjet printing emerged as a direct writing method for metallization, conducting polymers, such as PEDOT-PSS, have become promising electrode materials to achieve low-cost and high-performance devices [38]. Metals, such as gold [39] and silver [40], have also been deposited by printing for source/drain (S/D) electrodes giving good OFET performance.

#### 1.2 Technology Computer Assisted Design

#### 1.2.1 Overview

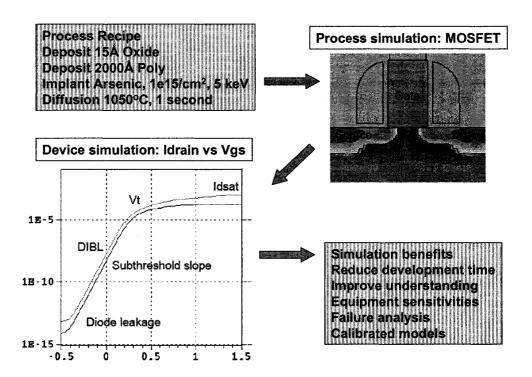

Technology Computer Aided Design, or TCAD, is the term used to describe a wide range of modeling and analysis activities that comprises detailed simulation of fabrication processes, electrical performance of single or multiple device and extraction of discrete parameters for equivalent circuit models. Numerical simulation of semiconductor device fabrication and operation is significant to the design and manufacturing of integrated circuits because it provides insights into complex phenomena that cannot be obtained through experimentation or simple analytical models. Simulation tools also provide a controlled and repeatable numerical experiment which can yield information that cannot be measured with present equipment. For the simulation tools to be useful in a practical environment, they should be physically accurate, computationally robust, and usable by those other than the software developers [41]. TCAD has been widely used by IC manufacturers during technology development. The software examples are SUPREM, PISCES, PROPHET, ATHENA, ATLAS, TSUPREM4, MEDICI, TAURUS, DIOS, and DESSIS, etc. Figure 1-3 shows schematically a typical TCAD flow. Starting from a process recipe and knowledge of the layout, a structure is created via process simulation. This structure is fed directly into the device simulator,

which produces I-V or C-V curves. One important benefit from simulation is a better understanding of how devices really operate. The simulation allows one to see inside the devices. For example, one can see how the electric field, and charge carriers distribute in the device structure; one can visualize where depletion regions are located. Apart from the flow information as shown in Figure 1-3, device simulation can also be performed without process simulation. In this case, doping profiles can be specified as Gaussian functions, which is suitable for many applications. This approach is very fast compared to process simulation. Another TCAD application is associated with the concept of inverse modeling. One starts with known device characteristics, and then searches for a structure that reproduces these curves.

Figure 1-3 A typical TCAD flow [42].

However, examples can always be found where the simulation results do not match experimental results. The differences could arise from the insufficient physics for new materials, inaccuracies in metrology especially for gate length and oxide thickness, improper use of software tools such as models, and missing process details such as temperature ramp [42].

#### 1.2.2 Device Simulation

Device simulation is usually done by employing the drift-diffusion (DD) model for electron transport. The equations for the flow of electrons and holes were given by Shockley consisting of three partial differential equations (PDEs) including electron and hole-current continuity equations and Poisson's equation [41]. Besides the DD model, there exists a density gradient (DG) model, which is an extension to the DD equations. It applies a quantum potential correction in the current density expression and is capable of calculating confined carrier concentrations and other quantum effects such as tunneling. Some of its advantages over other quantum models include the ability to handle complex geometries and to be readily applied in 1D, 2D and 3D [43].

#### 1.3 Dissertation Objectives

The objective of this project is to present the previously discussed strategies to improve organic field effect transistors. First, poly(3-hexylthiophene) OFETs are fabricated and characterized based on a solution process. Then we will use TCAD simulations to gain better understanding of our devices and to identify the key factors that could limit the device performance. After that our device improvement strategies will be demonstrated. Based on our understanding of the inorganic and organic semiconductors and the gate insulated FETs, we will present polymer heterojunction modulation doped

field effect transistors, which could offer an alternative pathway for improving OFET's performance.

#### 1.4 Organization of this Dissertation

Chapter One introduces organic field effect transistor as an ensemble of three components, namely, conductor, semiconductor and insulator. Related work that has been done and special requirements on these three components are briefly addressed in order to highlight the issues that could lead to high-performance OFETs. Then TCAD is introduced, highlighting the importance of the numerical simulation on the design and the understanding of the semiconductor devices. Finally, the objectives of our work are described.

Chapter Two covers the theoretical background that has been applied in this work. The conducting mechanisms of the organic semiconductors are introduced, followed by the operation principles of the OFETs. The conducting mechanisms include hopping transport, multiple trapping and release models, and field-dependent mobility. In the operation principles of the OFETs, we focus on the energy band diagrams, electric characteristics, contact resistance effects, trapping effects and gate bias dependent mobility.

Chapter Three introduces the fabrication and characterization techniques. Two solution processes, i.e. spin coating and inkjet printing, as well as the device characterization technique are emphasized.

Fabrication and analysis of poly(3-hexylthiophene) field effect transistors are given in Chapter Four. Device characteristics are investigated considering contact

resistance effect, gate voltage dependence of mobility, temperature dependence of mobility. The hysteresis effect of the fabricated devices is also explored.

In Chapter Five, we simulate the P3HT FET using 2-D Taurus-Device simulator in order to gain better understanding of device operation. The simulation is carried out based on drift-diffusion model. Traps and contact resistance are modeled.

With the knowledge of the fundamental issues that could affect P3HT device characteristics and performance, our strategies to improve P3HT device are demonstrated in Chapter Six, including improving S/D contact and semiconductor-insulator interface.

In Chapter Seven, instead of a single P3HT layer as the active channel, a polymer heterojunction involving P3HT is utilized as the channel material. The polymer heterojunction FETs show "modulation doping" effect analogous to that in conventional inorganic modulation doped field effect transistor (MODFET).

We will conclude our work in Chapter Eight and high-light some issues that should be done in the future.

#### **CHAPTER TWO**

#### THEORETICAL BACKGROUND

#### 2.1 Charge Transport in Polymeric Semiconductors

#### 2.1.1 Overview

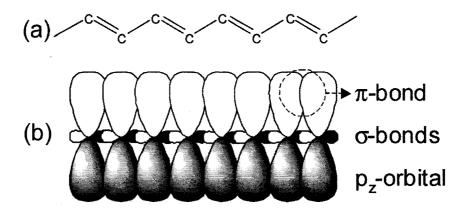

The main element of conjugated polymers is the carbon atom, which has four electrons in the outer electronic level. The orbitals of these electrons could mix to create four equivalent degenerate orbitals called  $sp^3$  hybrid orbitals around the carbon atom. These  $sp^3$  hybrid orbitals arrange in a tetrahedral configuration. If only three chemical bonds are formed, three  $sp^2$  hybridized orbitals will be created at an angle of  $120^\circ$  with each other in a plane. These bonds are called  $\sigma$ -bonds, associated with highly localized electrons in the plane of the molecule. The one remaining free electron per carbon atom is located in the  $p_z$  orbital, which is normal to the  $sp^2$  plane. The  $p_z$  orbitals on the adjacent carbon atoms overlap to form  $\pi$ -bonds. A schematic representation of this hybridization is illustrated in Figure 2-1, for the simplest conjugated polymer polyacetylene [44]. Molecules with  $\sigma$ - and  $\pi$ -bonds are schematically represented by single and double alternating chemical bonds between the carbon atoms. They are called conjugated molecules. Due to the  $\pi$ -bonds, a delocalized electron density distributes above and below the plane of the molecule. It is the nature of these delocalized  $\pi$ -electrons that provide conjugated polymers interesting electrical and optical properties [44].

Figure 2-1 (a) The molecular structure of polyacetylene. The alternating single and double bonds indicate that the polymer is conjugated. (b) Schematic representation of the electronic bonds in polyacetylene [44].

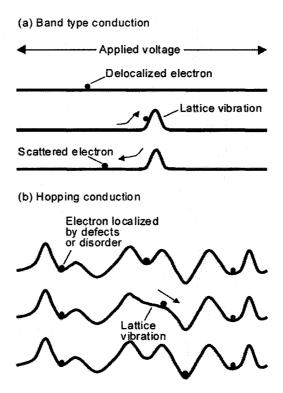

There exist significant differences between the 3-dimensional crystal lattice of most inorganic semiconductors and the amorphous structure of conjugated polymers. Inorganic semiconductor crystalline lattices are characterized by long range order and strongly coupled atoms. Long-range delocalized energy bands are separated by a forbidden energy gap. Charge carriers added to the semiconductor can travel in these energy bands with a relatively large mean free path. The restrictive factor for this band transport is the scattering of the charge carriers due to thermal lattice vibrations, as illustrated by Figure 2-2a, where straight line represents a free carrier delocalized and moving freely in a perfect crystal [44]. Since lattice vibrations increases with increasing temperature, the mobility of the charge carriers decreases with increasing temperature. On the other hand, in conjugated polymers, the polymer chains are weakly bound by Van der Waals forces. These polymers generally have narrow energy bands. They can easily be disrupted by disorder. Although electric charge is delocalized along the  $\pi$ -conjugated segments of the polymer backbone, the length of such perfectly conjugated segments is generally limited to around several nm. These conjugated segments are separated by

chemical defects, such as a non-conjugated sp<sup>3</sup> hybridized carbon atom on the polymer backbone, or by structural defects, such as, chain kinks or twists out of coplanarity. Due to the disorder, the semiconductor can not be considered simply as having two delocalized energy bands separated by an energy gap. Instead, the charge transport sites, the segments of the main polymer chain, have a Gaussian distribution of energies [44]. The motion of the carriers in the amorphous conjugated polymers is thought to be via hopping process. The lattice vibrations are essential for a carrier to move from one site to another. The mobility normally increases with increasing temperature. The charge transport in these amorphous material system is schematically illustrated in Figure 2-2b.

Figure 2-2 Charge transport mechanisms in solids: (a) band transport in a crystal structure, such as, silicon and (b) hopping transport in an amorphous structure such as conjugated polymer [44].

#### 2.1.2 Hopping

As mentioned above, due to the disorder and localization of charges, the transport of charge carriers in polymeric semiconductors occurs by hopping between localized states. The transport is assisted by phonons, thus the mobility increases with increasing temperature. Several models have been developed for the hopping transport. In most cases, the temperature dependence of the mobility follows

$$\mu = \mu_0 \exp[-(T_0 / T)^{1/\alpha}]$$

(2-1)

where  $\alpha$  is an integer ranging from 1 to 4 [2].

#### 2.1.3 Field Dependent Mobility

In organic materials, the mobility generally becomes field dependent at high electric field, i.e., larger than  $\sim 10^5$  V/cm. This effect is generally explained as follows: the coulombic potential near the localized levels could be modified by the applied electric field in a way that the tunnel transfer rate is increased between sites. The field dependence of the mobility is expressed by

$$\mu(E) = \mu(0) \exp(\frac{q}{kT} \beta \sqrt{E})$$

(2-2)

$$\beta = (q / \pi \varepsilon \varepsilon_0)^{1/2} \tag{2-3}$$

where  $\mu(0)$  is the mobility at zero electric field,  $\beta$  the Poole-Frenkel factor determined by Equation 2-3, E the magnitude of the electric field,  $\epsilon$  permittivity of the semiconductor, and q electron charge [45].

#### 2.1.4 Multiple Trapping and Release

Multiple trapping and release (MTR) model has been used to explain gate voltage dependent mobility in amorphous silicon. This model assumes that charge transport takes

place in extended states, and most of the carriers injected into the semiconductor are trapped in states localized in the band gap. Then by a thermally activated process, the trapped carriers are released to the extended states. The trapped-controlled drift mobility related to the mobility in the delocalized band can be expressed by Equation 2-4 [45] [46]

$$\mu_D = \mu_0 \lambda \exp(-\frac{E_t}{kT}) \tag{2-4}$$

where  $\mu_D$  and  $\mu_0$  are effective drift mobility and the mobility in the delocalized band, respectively,  $E_t$  is the distance between the trap level and the delocalized band edge. In the case of single level of trapping states,  $\lambda$  is the ratio of the density of states at the delocalized band edge and the density of traps.

#### 2.2 Operation of Polymeric Field Effect Transistors

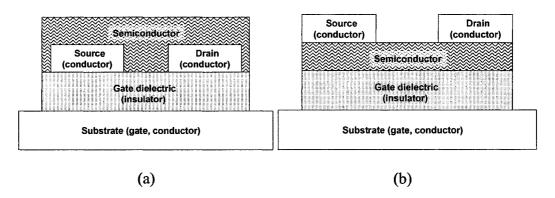

Figure 2-3 shows schematic diagrams of thin film transistors (TFTs) based on bottom-contact and top-contact structure, respectively. Both structures have been widely used in organic field effect transistor with their own advantages. The operation mode of a TFT is different from that of a conventional metal-insulator-semiconductor field effect transistor (MISFET). The operation of a conventional MISFET is through a minority-carrier channel which forms in the strong inversion regime. The source and drain regions are oppositely doped as compared to the semiconductor channel. At zero gate voltage, structure from source to drain actually consists of two back-to-back p-n junctions, thus giving extremely low off-currents. In the TFT, source and drain electrodes have low contact resistance. The low source-drain current at zero gate voltage is simple due to the low conductivity of the semiconductor. Field-enhanced current occurs through majority-carrier injection in the accumulation layer. Organic (or polymer) field effect transistors

share the common features with the TFTs, in that, it also operates in the accumulation regime and not in the inversion region, and the low off currents are only guaranteed by the low conductivity of the organic semiconductors.

Figure 2-3 Schematic structures of a TFT with (a) bottom-contact and (b) top-contact configuration.

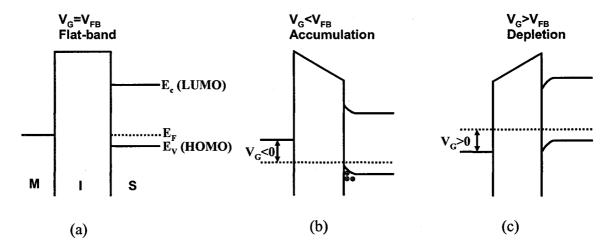

#### 2.2.1 Energy Band Diagrams

The energy band diagrams of a p-type MISFET at different operation conditions are schematically shown in Figure 2-4. Due to the work function potential difference between the semiconductor and the metal, a gate voltage is applied so that the Fermi levels of metal and semiconductor align, then no band bending will occur in the semiconductor as shown in Figure 2-4a. This gate voltage is called the flat band voltage  $V_{FB}$

$$V_{FB} = \phi_{ms} = \phi_m - (\chi + \frac{E_g}{2q} + \phi_b)$$

(2-5)

Here,  $\phi_m$  is the metal work function,  $\chi$  the electron affinity,  $E_g$  the semiconductor bandgap, q the electron charge, and  $\phi_b$  the potential between the Fermi level and the intrinsic Fermi level  $E_i$ . If the work function of metal is similar to the Fermi level of semiconductor, the flat band voltage will be close to 0. Here we are not considering the

will induce charges at the semiconductor-insulator interface. This causes band bending-up as shown in Figure 2-4b, indicating accumulation of holes at the interface. Under this condition, the p-channel transistor is turned on. When a positive gate voltage (or gate voltage higher than the flat band voltage) is applied, the mobile holes are depleted from the semiconductor-insulator interface due to the electric field, causing band bending down in the p-type semiconductor illustrated by Figure 2-4c.

Figure 2-4 Energy gap diagram of a MIS structure with p-type semiconductor under (a) flat band condition, (b) accumulation, and (c) depletion. LUMO and HOMO apply for organic semiconductors.

#### 2.2.2 Current-Voltage Characteristics

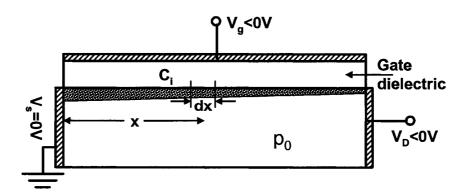

The drain current  $I_d$  up to the saturation point was predicted by a model derived by Borkan and Weimer [47]. An incremental section of length dx of a TFT, at an arbitrary distance x from the source, is shown in Figure 2-5, where the source is grounded, and the gate and drain are negatively biased. The charge at position x induced by gate is  $C_i(V_g-V_x)$  per unit area, where  $C_i$  is the gate capacitance per unit area of the insulator,  $V_g$  is the gate potential, and  $V_x$  is the potential of the dx section relative to the source. The

potential  $V_x$  changes continuously along the semiconducting channel from zero at the source to  $V_d$  at the drain. If the initial free carrier concentration in the semiconductor is  $p_0$  (p type) per unit area of surface, then the total conducting charge per unit area in the semiconductor is  $p_0q + C_i(V_g-V_x)$ . Then at low drain voltage, the current  $I_d$  is given by Equation 2-6[48]

$$I_{d} = w\mu [p_{0}q + C_{i}(V_{g} - V_{x})] \frac{dV_{x}}{dx}$$

(2-6)

where w is the width of the TFT,  $\mu$  is the carrier mobility, and  $dV_x$  is the potential difference across the dx section. Having  $V_T = -p_0 q/C_i$ , Equation 2-6 becomes

$$I_d \int_0^L dx = C_i w \mu \int_0^{V_d} [(V_g - V_T) - V_x] dV_x$$

(2-7)

where L is the channel length, the distance from the source to drain. By integration, Equation 2-7 becomes

$$I_d = \frac{Cw\mu}{L} [(V_g - V_T)V_d - \frac{V_d^2}{2}]$$

(2-8)

$V_T$  represents the applied gate voltage required for the onset of the conduction. If  $V_T$  is positive, the TFT is thought to operate in the enhancement mode, whereas the device is said to operate in the depletion mode if  $V_T$  is negative.

Figure 2-5 Channel formation in a TFT.

Equation 2-8 indicates that for a given Vg, the current increases with drain voltage and reaches a maximum value when  $V_d=V_g-V_T$ . At a low drain voltage and a large negative gate voltage, the quadratic term in Equation 2-8 could be ignored, and then Equation 2-8 could be simplified to

$$I_d = \frac{Cw\mu}{L} (V_g - V_T) V_d \tag{2-9}$$

Under this condition, there will be a uniform accumulated charge density throughout the channel. However, as the drain bias becomes increasingly negative, the voltage drop across the insulator and semiconductor will be a function of a position along the channel [49]. The accumulation charge density decreases along the channel from the source to the drain, as shown in Figure 2-5. When drain voltage reaches V<sub>g</sub>-V<sub>T</sub>, charge accumulation disappears near the drain, resulting in the so-called "pinch-off" of the channel. Then the TFT starts with a saturation region, where drain current remains substantially constant with increasing drain voltage. The saturation current is given by

$$I_{dsat} = \mu \frac{w}{2L} C_i (V_g - V_T)^2$$

(2-10)

Equation 2-10 is obtained by simply substituting in Equation 2-8 with  $V_d$ =Vg- $V_T$ . From the I-V characteristics, two important technological parameters viz. the channel conductance  $g_d$  and transconductance  $g_m$  can be determined. The channel conductance is obtained in the linear regime expressed by

$$g_d = \left| \frac{\partial I_d}{\partial V_d} \right|_{V_g = cons \tan t} = \frac{w}{L} \mu C_i (V_g - V_T)$$

(2-11)

The transconductance in the linear and saturation regimes are given by Equations 2-12 and 2-13, respectively,

$$g_{m} = \left| \frac{\partial I_{d}}{\partial V_{g}} \right|_{V_{c} = const} = \frac{w}{L} \mu C_{i} V_{d}$$

(2-12)

$$g_{m} = \frac{w}{L} \mu C_{i} (V_{g} - V_{0})$$

(2-13)

Another significant technological parameter is mobility, which is normally taken as a measure of device performance. Higher mobility is preferred. For simplicity, mobility value can be derived from Equation 2-10 by plotting  $I_D^{1/2}$  against  $V_G$  in the saturation regime. The x-intercept of the curve determines the threshold voltage. In the linear operation region, the mobility estimated using Equation 2-12 is usually gate-dependent, which is due to a nonlinear  $V_g \sim I_d$  relationship at low drain voltage. As addressed afterwards, this nonlinearity could be attributed to the source/drain contacts and the trapping effects in the organic field effect transistors.

## 2.2.3 Contact Resistance Effects

Source/drain contact resistance in OFETs have been investigated and found to strongly affect the overall device performance [50][51][52]. In the metal-organic semiconductor system, a large contact resistance normally arises from a Schottky contact between them. This non-ohmic contact is dependent on the gate electric field [53], resulting in the nonlinearity of  $V_g \sim I_d$  as mentioned above. By matching the energy levels between electrode and semiconductor, an ohmic contact could be reached. However, at the transition area between organic semiconductor and source/drain electrodes, the organic semiconductor could be poorly ordered forming a low-mobility region, resulting in a significant contact resistance. Accounting for the parasitic series resistance at source and drain  $R_p$ , Equation 2-9 could be improved to [51]

$$I_{d} = \frac{w}{L} C_{i} \mu (V_{g} - V_{T}) (V_{d} - I_{d} R_{p})$$

$$= \frac{(w/L) C_{i} \mu (V_{g} - V_{0}) V_{d}}{1 + (w/L) C_{i} R_{p} (V_{g} - V_{0})}$$

(2-13)

Since  $R_p$  can not be directly measured, estimating mobility from Equation 2-13 seems to be complicated. Nevertheless,  $R_p$  could be removed by some numerical manipulations [51]. First, we calculate the drain conductance  $g_d$  (Equation 2-14) and transconductance  $g_m$  (Equation 2-15) at low drain voltage

$$g_{d} = \frac{\partial I_{d}}{\partial V_{d}} = \frac{I_{d}}{V_{d}} = \frac{(w/L)C_{i}\mu(V_{g} - V_{T})}{1 + (w/L)C_{i}\mu R_{p}(V_{g} - V_{T})}$$

(2-14)

$$g_{m} = \frac{\partial I_{d}}{\partial V_{g}} = \frac{(w/L)C_{i}\mu V_{d}}{\left[1 + (w/L)C_{i}\mu R_{p}(V_{g} - V_{T})\right]^{2}}$$

(2-15)

To eliminate the parasitic resistance, Equation 2-14 is divided by the square root of Equation 2-15 giving the following equation [51]

$$\frac{g_d}{\sqrt{g_m}} \sqrt{\frac{L V_d}{W C_i}} = \sqrt{\mu} (V_g - V_T)$$

(2-16)

Therefore Equation 2-16 could be used to estimate field effect mobility, which is corrected for contact resistance and therefore it could describe the carrier mobility in organic semiconductor channel more accurately. The parasitic contact resistance could be derived from Equation 2-14 and has the following form

$$R_{p} = \frac{1}{g_{d}} - \frac{L}{w\mu C_{i}(V_{g} - V_{T})}$$

(2-17)

Parasitic contact resistance could also be estimated by channel length series method, in which a set of devices with various channel lengths are characterized at low drain voltage [54] [55]. For each device at each gate voltage, the linear portion of I<sub>d</sub>-V<sub>d</sub>,

is used to find total source-to-drain resistance  $R_{total}$ , which is then plotted as a function of channel length. The extrapolated resistance corresponding to zero channel length gives parasitic contact resistance  $R_p$ . Then channel conductance  $R_{ch}$  can be obtained by subtracting  $R_p$  from the  $R_{total}$ . The mobility threshold voltage can be derived from the linear fit of sheet channel conductance as a function of gate voltage, with the slope and x-intercept of fitted line giving the intrinsic mobility and threshold voltage, respectively.

## 2.2.4 Trapping Effects

As described earlier in section 2.1 in this chapter, for the amorphous semiconductors, especially polymeric semiconductors, the material system is featured with a disordered structure having a significant density of defects that could trap carrier charges. The device behaviors of the OFETs, like the amorphous silicon TFTs [48], have been successfully explained by the trapping effects [56] [57] [58]. Proposed by Horowitz et al., [57], the trapping effect on the OFETs is divided into three regions.

(1) Region 1 extends from V=0 to  $V=V_1$ .  $V_1$  corresponds to the surface potential where all traps are filled. The free and trapped carrier distribution can be approximated by the Boltzman distribution

$$n_f = N_v \exp(-\frac{E_v - E_F - qV}{kT}) = n_{f0} \exp\frac{qV}{kT}$$

(2-18)

$$n_t = N_t \exp(-\frac{E_t - E_F - qV}{kT}) = n_{t0} \exp(\frac{qV}{kT})$$

(2-19)

where  $n_{f0}$  and  $n_{t0}$  are the bulk free and trapped carrier density. Bulk free/trap carrier-density ratio is introduced and expressed by

$$\theta_0 = \frac{n_{f0}}{n_{f0} + n_{t0}} \tag{2-20}$$

Taking into account the trapping effects, Equation 2-10 could be rewritten as

$$I_{dsat} = \theta_0 \mu_0 \frac{w}{2L} C_i (V_g - V_T)^2$$

(2-21)

where  $\mu_0$  could represent the intrinsic mobility of organic semiconductor.

- (2) Region 2 extends from  $V_1$  to  $V_2$ , where  $n_t$  is equal to  $n_f$ . This region corresponds to the so-called subthreshold regimes. The saturation current varies exponentially with the gate voltage.

- (3) Region 3 extends beyond  $V_2$ . The free-carrier concentration is higher than the trapped carrier density. Therefore the total carrier concentration can be taken as the free carrier concentration resulting in  $\theta_0$  approximating 1. Then the intrinsic field effect mobility is approximately equal to the experimentally determined mobility.

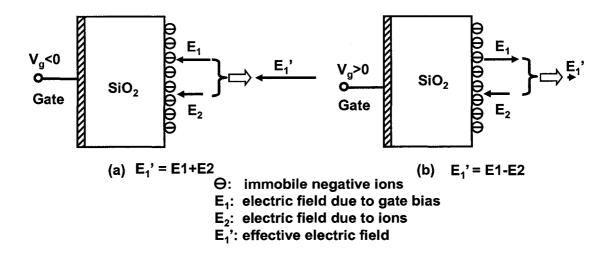

Besides the above mentioned bulk traps that are associated with the organic semiconductor itself, interface traps at the insulator-semiconductor interface due to the defects on the insulator should not be neglected. The interface trapping effect could be significant due to the fact that the most of the charge transport occurs in one or two monolayers near the insulator-semiconductor interface. Recent reports [59] [60] suggested that the thermally grown  $SiO_2$  surface carries SiOH silanol groups of a concentration up to  $(3-7) \times 10^{13}$  cm<sup>-2</sup>, which greatly exceeds the typical carrier concentration of  $10^{13}$  cm<sup>-2</sup>. These SiOH groups could trap induced electrons creating immobile  $SiO^-$  ions ( $SiOH + e^- \rightarrow SiO^- + 1/2H_2$ ), which compensate or enhance gate electric field depending on the polarity of gate voltage, as illustrated in Figure 2-6, where  $\Theta$  represents the immobile negative ions,  $E_1$  gate electric field,  $E_2$  the field due to the negative ions,  $E_1$ ' the effective gate electric field. One can see that, for a negative gate

voltage, the effective electric field is enhanced by the negative ions, and vice versa for positive gate voltage.

Figure 2-6 The effect of immobile negative ions on the electric field at the  $SiO_2$  surface, (a) ions enhance the gate electric field and (b) ions compensate the gate electric field. The length of the arrows schematically represents the amplitude of the electric field.

## 2.2.5 Gate Bias-Dependence Mobility

As mentioned above in the section 2.2.4, the gate voltage dependent mobility is associated with the trapping effect. The gate voltage dependence of mobility simply comes from its dependence on mobile carrier density. Varying the gate voltage tunes the ratio between the densities of free carriers and trapped charge carriers, resulting in changing effective mobility. The gate dependence of mobility can be described by an empirical equation [61]

$$\mu = \alpha (V_g - V_0)^{\beta} \tag{2-22}$$

where  $\alpha$  and  $\beta$  are fitting constants,  $V_g$  the gate voltage and  $V_0$  the fitting threshold voltage.

## CHAPTER THREE

## FABRICATION AND CHARACTERIZATION

## **METHODS**

## 3.1 Introduction

In this work, several micro-fabrication processes and characterization techniques were used. They include metallization processes, such as thermal evaporation, sputtering, e-beam deposition, lithography, lift-off, etc.; polymer deposition processes, such as spin coating and inkjet printing; film characterization techniques such as atomic force microscope (AFM), scanning electron microscopy (SEM), Alpha step profilometer, Fourier transform infrared spectroscopy (FTIR), ellipsometer, roughness step tester (RST), etc.; device characterization system, such as Keithley probe station. Inkjet printing, spin coating, and device characterization techniques are most frequently used and thus are highlighted as follows.

## 3.2 Inkjet Printing

## 3.2.1 Introduction

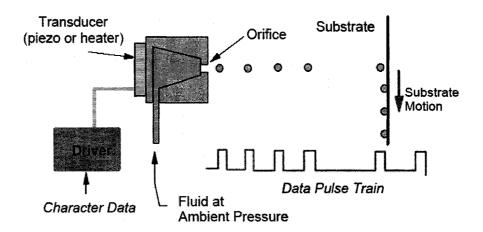

Inkjet printers may operate in either continuous or drop-on-demand (DOD) mode. In continuous-mode inkjet printing, the ink is pumped through a nozzle to form a liquid jet. It is mostly used for high-speed graphical applications. In our work, drop-on-demand

mode is used. In a DOD inkjet printer, an acoustic pulse ejects ink droplets from a reservoir through a nozzle. The pulse can be generated either thermally or piezoelectrically (Figure 3-1). In a thermal DOD inkjet printer, ink is heated locally to form a rapidly expanding vapor bubble that ejects an ink droplet. Thermal DOD usually uses water as a solvent and may therefore impose restriction on the type of polymers that can be printed using this technique. Piezoelectric DOD inkjet printing, on the other hand, relies on the deformation of some piezoelectric material to cause a sudden volume change and hence generate an acoustic pulse. Piezo-electric DOD is suitable to a variety of solvents [62].

Figure 3-1 Schematic representation of a drop-on-demand ink-jet printing system [63].

## 3.2.2 Suitable Inks

The key part of inkjet printing technology is the ink. It must have specific physical properties particularly for the viscosity and surface tension. The viscosity should be suitably low, typically less than 20mPas. The polymer solution should therefore be sufficiently dilute. The surface tension is responsible for the spheroidal shape of the

liquid drop from the nozzle. Finally, the wetting behavior of fluid and nozzle material is of importance, as wetting of nozzle outlet face results in spray formation.

## 3.2.3 Coffee-Drop Effect

A serious problem with inkjet printing is the "coffee-drop effect": after evaporation of a printed solution droplet, most of the solute is accumulated as a ring that marks the original contact line [64]. This effect was explained by the pinning of the contact line of the droplet in combination with increased evaporation at the edges. However, to pin the contact line, liquid evaporated at the edges must be replenished by liquid from the interior. The resulting outward flow can carry virtually all the dispersed material to the edge [65] [66]. This "coffee-drop effect" could be overcome by the use of solvent mixtures to make polymer solutions, in which one solvent has a high boiling point and a low solubility for the polymer, and the other solvent has a low boiling point and a high solubility for the polymer. The dissolving potential of the solvent gradually decreases during evaporation and the polymer precipitates before a ring is formed. This method has been applied by Tekin et al., to avoid ring formation [67].

# 3.2.4 Microdrop Inkjet Printing System

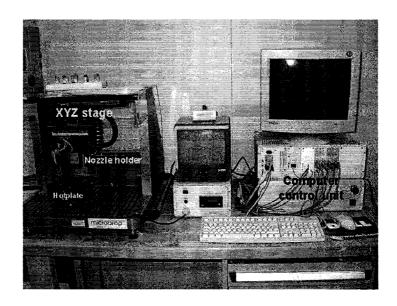

All printing experiments are performed on a drop-on-demand (DOD) Microdrop Dispensing System (Microdrop GmbH, Germany, Figure 3-2). A printer head nozzle with an internal diameter of 50 µm and a 4 ml ink reservoir is used for our work. The printer is capable of simultaneously accommodating four printer head nozzles. The nozzle is driven by a voltage pulse signal, whose amplitude, pulse width, and frequency are determined by the printing program.

An MD-P-705 positioning system controls the movements of the nozzle in a XYZ station. The positioning accuracy is  $\pm 10~\mu m$ . The repetition accuracy is  $\pm 3~\mu m$ . The minimum step width of movement is  $1~\mu m$  in X, Y and Z directions.

The substrate holder is a hotplate which is controlled by a PID (Proportional, Integral, and Derivative) regulator. The substrate holder can be heated up to 150 °C. A microscope connected with a monitor is used to accurately position printer head in order for the ejected droplets falling at the desired locations on the substrate.

Figure 3-2 The Microdrop Dispensing System.

## 3.3 Spin Coating

Spin coating is a commonly used process in microfabrication to deliver solid films from solutions. Uniform film with desired thickness is achieved by controlling solution properties and spin coating parameters. A spin-coating process can be divided into three stages. Full knowledge of each stage is helpful for the formation of films with desired properties. The three stages are deposition and spin up, spin off, and film drying [68].

The first stage is the deposition and spin up [68]. At this stage, a liquid solution is first applied over the substrate. Next, the substrate is accelerated to its final rotational speed. At this stage, the majority of the liquid is sloughed from the substrate due to the overwhelming force of the centrifugal acceleration. Conversion to a thin, nearly uniform film takes place within the first second or two of spinning.