# Louisiana Tech University Louisiana Tech Digital Commons

**Doctoral Dissertations**

Graduate School

Spring 2000

# Bulk micromachining of silicon for MOEMS prototype

Sung-Dong Suh

Follow this and additional works at: https://digitalcommons.latech.edu/dissertations

# **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality  $6^* \times 9^*$  black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA

BULK MICROMACHINING OF SILICON

#### FOR MOEMS PROTOTYPE

by

SUNG-DONG SUH, B.S., M.S.

A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree PhD in Engineering

# COLLEGE OF ENGINEERING LOUISIANA TECH UNIVERSITY

MAY 2000

UMI Number: 9964411

Copyright 2000 by Suh, Sung-Dong

All rights reserved.

# UMI®

#### UMI Microform 9964411

Copyright 2000 by Bell & Howell Information and Learning Company. All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> Bell & Howell Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

#### LOUISIANA TECH UNIVERSITY

#### THE GRADUATE SCHOOL

|                                    | _                     | May           | r 1, 2000 | ··             |

|------------------------------------|-----------------------|---------------|-----------|----------------|

|                                    |                       |               | Date      |                |

| We hereby recommend that           | the dissertation      | prepared      | under o   | ur supervision |

| bySung-Dong, Suh                   |                       |               |           |                |

| entitled Bulk Micromachining of Si | licon for MOEMS Pr    | rototype      |           |                |

|                                    |                       |               |           |                |

| be accepted in partial fulfillme   | ent of the requ       | uirements     | for the   | Degree of      |

|                                    | k                     | ing           | the       |                |

|                                    | Supervisor of Dissert |               |           |                |

|                                    | - Ray                 | 1 the         | ling      |                |

|                                    | Head of Departmen     | The           |           | •              |

|                                    | Department            | an an         | quicen    | 7              |

| Recomment from concurrent in:      |                       |               |           |                |

| AML )                              |                       |               |           |                |

| pluar J. Al Sume                   | -                     |               |           |                |

| Trentury Cui                       | Advisory Comr         | nittee        |           |                |

| INC                                |                       |               |           |                |

| Approved:                          | Approved              | :<br>Imili    | m. Am     | othu           |

| Director of Graduate Studies       | Director of the       | he Graduate S |           |                |

| Astie Quice                        |                       |               |           | ·              |

| Dean of the College                |                       |               |           |                |

GS Form 13 2/97

~

#### ABSTRACT

In this dissertation, the optical application of silicon micromachining technology was investigated in order to create the threedimensional microstructures that can be used as the components for the MOEMS prototype. These microstructures were designed and fabricated by utilizing corner compensation techniques and silicon bulk micromachining technologies. The fabricated microstructures are silicon mirror arrays that have a 1250 µm etch depth and through-holes across the OE-MCM substrate that has sixteen-fan-out OCDN on front side and a 1mm thickness.

Guided-wave OCDN on MCMs are designed and fabricated to meet the high-speed clocking requirements of next-generation digital systems through a realization of superior network bandwidth, low power consumption, and large fan-out capabilities.

Two fabricated components were assembled to build the MOEMS prototype. From the fiber-to-waveguide butt coupler, the light signal is launched on the waveguide core, and the signal travels and splits along the waveguide. Then, the light signals reflect at the micromachined silicon mirrors which are located in the sixteen fan-out nodes. This device was characterized by measuring the excess loss at the sixteen fan-out nodes at the wavelengths of 1310 nm and 1550 nm. The results show low loss signal propagation and signal uniformity.

# TABLE OF CONTENTS

| ABSTRACT                                           | iii |

|----------------------------------------------------|-----|

| LIST OF TABLES                                     | vi  |

| LIST OF FIGURES                                    | vii |

| ACKNOWLEDGEMENTS                                   | ix  |

| CHAPTER 1. INTRODUCTION                            | 1   |

| Background                                         | 1   |

| Silicon Micromachining                             | 1   |

| MEMS                                               | 2   |

| Optical Application of Silicon Bulk Micromachining | 3   |

| OE-MCM                                             | 9   |

| Research Objective                                 | 10  |

| Outline of the Document                            | 10  |

| CHAPTER 2. BULK MICROMACHINING OF SILICON          | 12  |

| Mask Layer Design for Mirrors                      | 13  |

| Mask Layer Design for Through-Holes                | 21  |

| Fabrication of 45° Mirror                          | 26  |

| CHAPTER 3. INTEGRATED OPTIC WAVEGUIDE              | 30  |

| Planar Waveguide                                   | 31  |

| Channel Waveguide                                  | 35  |

| Channel Waveguide Type                             | 35  |

| Radiation Bending Loss                             | 36  |

| Y-Branching Waveguide                              | 45  |

| Directional Coupler                                | 49  |

| Fiber-to-Waveguide Couplers                           | 52 |

|-------------------------------------------------------|----|

| Butt Coupling                                         | 52 |

| Grating Couplers                                      | 54 |

| Test Results and Characterizations                    | 56 |

| CHAPTER 4. PROTOTYPE FABRICATION AND CHARACTERIZATION | 58 |

| Prototype Fabrication and Procedures                  | 58 |

| Base Clean                                            | 61 |

| Oxidation                                             | 61 |

| Photoresist Spin Coating                              | 63 |

| Alignment, Exposure and Development                   | 66 |

| Hard Bake and Back Side Protection                    | 66 |

| Isotropic Etching                                     | 68 |

| Anisotropic Wet Etching of Silicon                    | 69 |

| Through-Hole                                          | 71 |

| Measurement Results and Characterizations             |    |

| CHAPTER 5. CONCLUSIONS AND RECOMMENDATIONS            | 77 |

| Conclusion                                            | 77 |

| Future Research                                       |    |

| BIBLIOGRAPHY                                          | 80 |

# LIST OF TABLES

| 1.1 | Microsensors                                            | 4  |

|-----|---------------------------------------------------------|----|

| 3.1 | Cutoff Thickness                                        | 34 |

| 3.2 | Effective Refractive Index                              | 34 |

| 3.3 | Total Excess Losses for 1-to-16 Splitter Test Structure | 56 |

| 4.1 | Oxide Thickness                                         | 63 |

| 4.2 | Photoresist Thickness vs RPM                            | 65 |

| 4.3 | HMDS/PR Spin RPM and Times                              | 65 |

| 4.4 | Etch Rate of Silicon Mirror                             | 71 |

| 4.5 | Etch Rate of the MCM Substrate                          | 72 |

| 4.6 | Dimensions for Mask Opening Squares on MCM Substrate    | 73 |

| 4.7 | Excess Losses at 1-to-16 Fan-Out                        | 74 |

|     |                                                         |    |

.

## LIST OF FIGURES

| 1-1  | Front Side of the OE-MCM Substrate                  | 6  |

|------|-----------------------------------------------------|----|

| 1-2  | Micromachined Mirror Array                          | 7  |

| 1-3  | MOEMS Prototype after Assembly                      | 8  |

| 1-4  | Silica Glass Waveguide Layers                       | 8  |

| 2-1  | Diagrams for Mirrors                                | 13 |

| 2-2  | Mask Layer for Test Structures                      | 15 |

| 2-3  | Corner Compensation Structure                       | 16 |

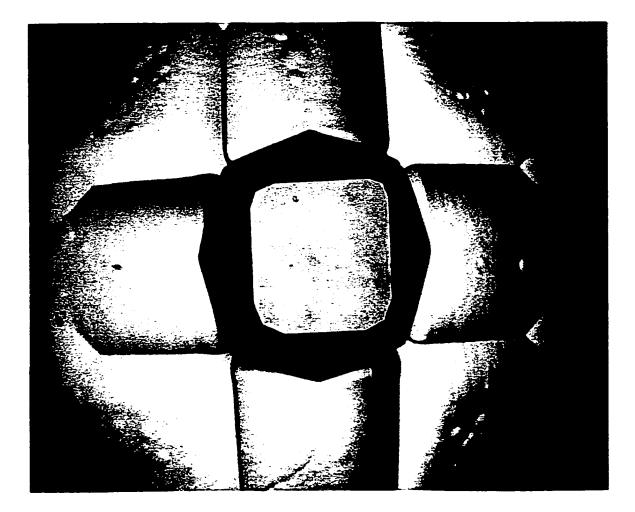

| 2-4  | Fabricated Mirror                                   | 18 |

| 2-5  | Corner Compensation Design                          | 19 |

| 2-6  | Mask Layer for Symmetric Sixteen Mirrors            | 20 |

| 2-7  | Micromachined Silicon Substrate                     | 21 |

| 2-8  | Geometry of an Etched Pit                           | 22 |

| 2-9  | Mask Layer for Through-Holes                        |    |

| 2-10 | Mask Layer for Sixteen Through-Holes                | 25 |

| 2-11 | Geometry of Off Axis Silicon Wafer                  | 26 |

| 2-12 | Location of 45° Mirror                              |    |

| 2-13 | Direction of Incident Beam to 45° Mirror            | 28 |

| 2-14 | 45° Mirror During Bulk Micromachining               | 29 |

| 3-1  | Silica Glass Waveguide Structure                    | 31 |

| 3-2  | Three Layer Waveguide                               | 32 |

| 3-3  | Graphical Solution of the Guidance Condition        | 34 |

| 3-4  | Various Types of Channel Waveguides                 | 35 |

| 3-5  | Bending Section of the Waveguide                    | 37 |

| 3-6  | Radiation Aperture for Fields on a Curved Waveguide | 40 |

| 3-7  | Attenuation as a Function of Bending Radius         | 43 |

| 3-8  | New Bending Section Design                          | 44 |

| 3-9  | Y-Branching Waveguide                               | 45 |

| 3-10 | Characteristic Modes of a Symmetric Y-Junction      | 46 |

| 3-11 | Excitation of a Y-Junction at the Left End       | <b>48</b> |

|------|--------------------------------------------------|-----------|

| 3-12 | Directional Coupler                              | 50        |

| 3-13 | Fiber-to-Channel Waveguide Using Silicon Grooves | 53        |

| 3-14 | Grating Coupler                                  | 54        |

| 3-15 | Sixteen Fan-Out OCDN Prototype Input Coupling    | 57        |

| 4-1  | Fabrication Process of Silicon Mirror            | <b>58</b> |

| 4-2  | Fabrication Process of Through-Holes             | 60        |

| 4-3  | After Development                                | 67        |

| 4-4  | Anisotropic Etching System                       | 70        |

| 4-5  | Fabrication of Through-Holes                     | 72        |

| 4-6  | Beam Reflectivity of Silicon Mirror              | 75        |

| 4-7  | Assembled OE-MCM Prototype                       | 76        |

| 5-1  | Excess Losses at Sixteen Fan-Out Nodes           | 78        |

#### ACKNOWLEDGEMENTS

I wish to express my sincere appreciation to my advisor Dr. Koh for his continued guidance and support during this research. Sincere appreciation is also expressed to Dr. Joseph T. Boyd, professor of the electrical engineering at the University of Cincinnati for providing me the research facilities such as a clean room and a wet etching station, and advice. I also appreciate Dr. Kody Varahramyan, the academic director and professor of electrical engineering for his advice and support while I have been at Louisiana Tech University. In addition, I appreciate my advisory committee members, Dr. Mike McShane, assistant professor of biomedical engineering; Dr. Tianhong Cui, assistant professor of IfM; Dr. Meng Tao, assistant professor of electrical engineering for their helpful advice. In addition, I would like to express appreciation to Daniel Saddler for his useful advice about technical skills. Also I thanks to Ron Fleeniken, technical staff at the University of Cincinnati, for making the optical masks and sputtering of the aluminum.

I also wish to express special thanks to my parents for their assistance and support during my education. I would like to extend my appreciation to Heather Daigle and Song Jehoon for editing and correcting this dissertation.

ix

# CHAPTER 1

#### INTRODUCTION

#### **Background**

#### Silicon Micromachining

Silicon micromachining is the process of creating microstructures in silicon by means of photolithography and chemical or physical etch. There are three technologies in micromachining: bulk micromachining, surface micromachining, and LIGA process.

Bulk micromachining, used to selectively remove silicon from substrates, has been applied in the fabrication of micromachined sensors, actuators, and microstructures [1]. Since the silicon can be micromachined precisely by anisotropic etchants, whose etching rates depend on the crystal orientation, bulk micromachining utilizes the etching selectivity between {111} planes and {100} or {110} planes [2-4]. There are two types of bulk micromachining techniques depending on the state of the etchants: chemical wet etching and dry micromachining. In dry micromachining, chemically active species collide with the substrate. This collision removes the substrate ion, atom or molecule. It even produces delicate microstructures, but it requires an expensive facility. Dry micromachining is particularly amenable to single-wafer processing, and for practical reasons etching depth is usually limited to depths of less than 20  $\mu$ m [5]. Therefore, traditional bulk micromachining (wet chemical etching) is preferred for the fabrication of thick and high aspect ratio microstructures.

Surface micromachining is the fabrication process of the micromechanical structures by deposition and etching of thin structural and sacrificial films. There are several advantages and trade-offs between surface micromachining and bulk micromachining technologies. Compared to the bulk micromachining technique, the surface micromachining method does not have enlargement effects so the improvement of device density is expected. The increased throughput reduces the cost of individual devices and makes the development of merged integrated sensor/microelectronic systems economically feasible [6]. In addition, the optical applications of the surface micromachining have been reported recently [7]. However, the biggest disadvantage of surface micromachining is that it is limited to thin films.

A variety of high aspect ratio microstructures can be fabricated by using the LIGA process that utilizes a combination of surface micromachining and metal electroplating. The fabrication method of the LIGA process for micro-optical elements has been presented by many researchers [8,9].

#### <u>MEMS</u>

The most important goal of micromachining technologies is the ability to create higher performance with smaller and more functional measurement, instrumentation, and control systems. These systems may include sensors, actuators, and electronics or a combination of them, implemented using batch fabrication technologies typically used in integrated circuits [10-12].

Micro-electro-mechanical-systems (MEMS) are integrated micro-scale devices or systems that utilize both electrical and mechanical components. Two main categories of MEMS are sensors and actuators. Both of these are special types of tranducers, which are devices that convert one physical quantity to another. Therefore, the sensor is considered to be a device that converts a physical quantity to an electric signal, and the actuator is considered to be a device that converts an electric signal to a physical quantity. In Table 1-1, types of sensors are listed. Electrostatic actuators such as comb drives and micromotors, piezoelectric actuators, thermal actuators, hydraulic actuators and microstimulators, are all considered actuators.

#### **Optical Applications of Silicon Bulk Micromachining**

When MEMS technology is applied to optics, it can extend the functionality of optical devices and miniaturize the optical systems. The miniaturization and integration of optical and optoelectronic systems can improve the performance of these systems with a reduction in size and cost, very similar to IC fabrication technology in the recent technological revolution. Since micro-optical elements such as mirrors and actuators can be monolithically integrated on the same substrate using a batch process, micromachining technology brings many opportunities for the application of optoelectronic systems [13-16].

| Sensor Types            | Examples                                                                                       |  |

|-------------------------|------------------------------------------------------------------------------------------------|--|

| Thermal Sensors         | Thermocouples                                                                                  |  |

|                         | Thermoresistors                                                                                |  |

|                         | Thermal flow-rate sensors                                                                      |  |

|                         | Photodiodes                                                                                    |  |

|                         | Phototransistors<br>Charge coupled devices (CCDs)<br>Pyroelectric sensors<br>Integrated Optics |  |

| Radiation Sensors       | Charge coupled devices (CCDs)                                                                  |  |

|                         | Pyroelectric sensors                                                                           |  |

|                         | Integrated Optics                                                                              |  |

|                         | ISFETsensors                                                                                   |  |

| <b>Chemical Sensors</b> | Enzyme-based biosensors                                                                        |  |

|                         | Microelectrods for neurophysiology                                                             |  |

|                         | Piezoresistors                                                                                 |  |

|                         | Piezoelectric sensors                                                                          |  |

|                         | Capacitive sensors                                                                             |  |

| Mechanical Sensors      | Optical sensors                                                                                |  |

|                         | Resonant sensors                                                                               |  |

|                         | Accelerometers                                                                                 |  |

|                         | Pressure sensors                                                                               |  |

### Table 1-1. Microsensors

\* Available from internet: http://www.dbanks.demon.co.uk/ueng/

The basis for the MEMS technologies is micromachining, which involves the fabrication of mechanical structures in the micron to millimeter range. Wet chemical anisotropic etching of silicon is one of the key technologies of silicon micromachining, and it is also referred to as "bulk micromachining" since significant amounts of silicon are removed from a substrate in this technology [1,17].

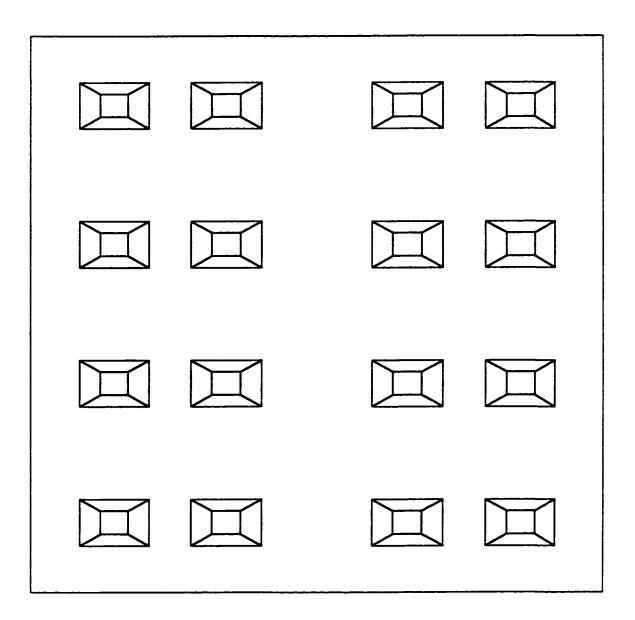

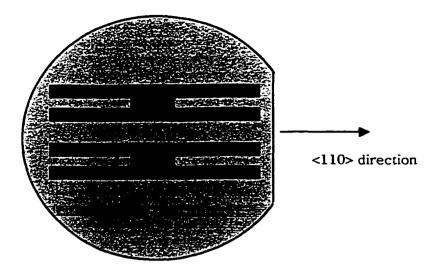

Wet chemical anisotropic etching was used to create the microstructures in this dissertation. Two different microstructures were fabricated. These are the silicon micromachined mirror array and the through holes across the optoelectronic multichip module (OE-MCM). The silicon mirror array, which has a convex structure, is used for optical signal distribution. The fast etching planes determine the shape of the silicon micromachined mirrors. The through-hole is a concave structure, and its final form after etching is determined by the slow etching planes [17-21].

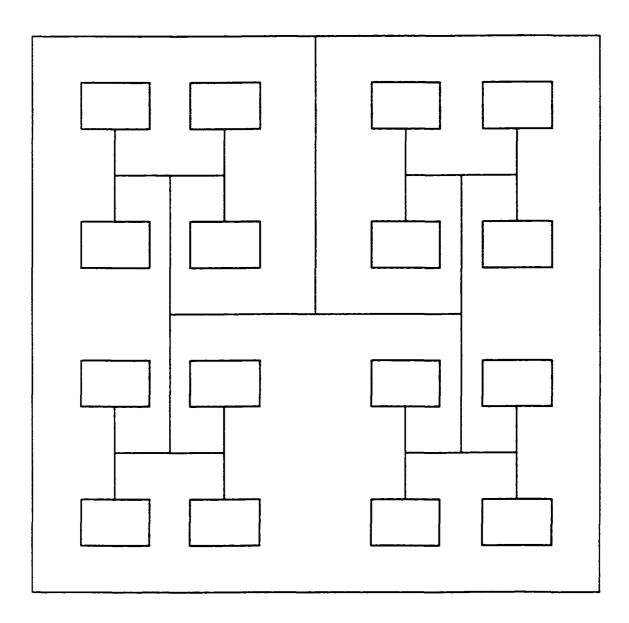

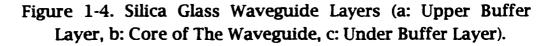

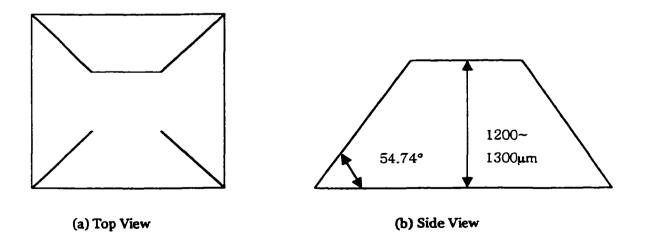

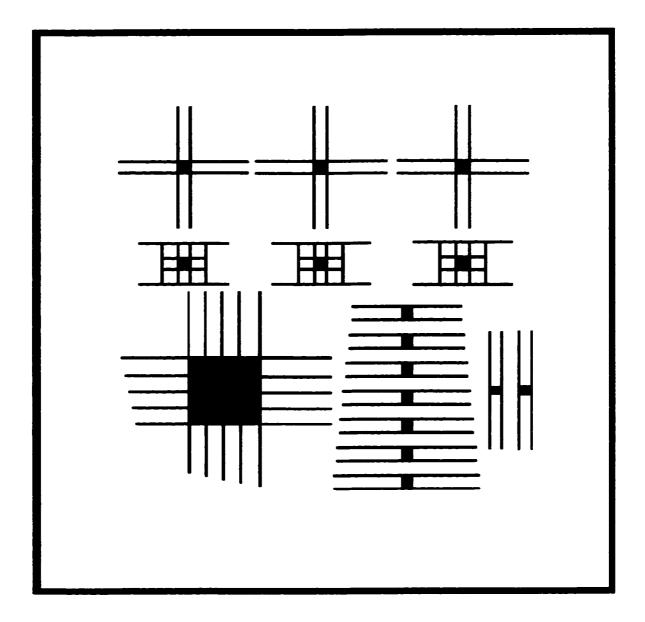

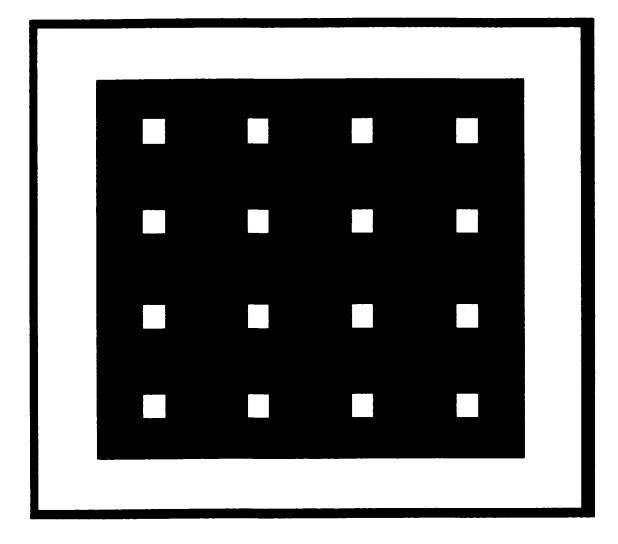

There is an optical waveguide network on the MCM substrate. Figure 1-1 shows the optical waveguide network and the locations of input/output (I/O) couplers on the front side of the MCM substrate. The optical waveguide network is composed of bending sections and branches such as Y-splitters, even though it looks like it consists of all straight lines in Figure 1-1. The back side of the substrate is patterned with oxide openings at the same location of the I/O pads on the front, but the openings for bulk micromachining have larger dimensions than those on the front side. The through-holes are formed by etching both sides simultaneously to accommodate the silicon mirror array. Figure 1-2 shows a diagram of the micromachined silicon mirror array.

Figure 1-1. Front Side of The OE-MCM Substrate

Figure 1-2. Micromachined Mirror Array

Figure 1-3. MOEMS Prototype after Assembly.

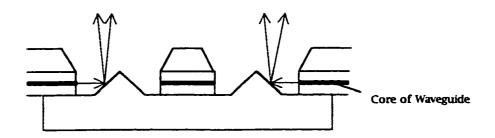

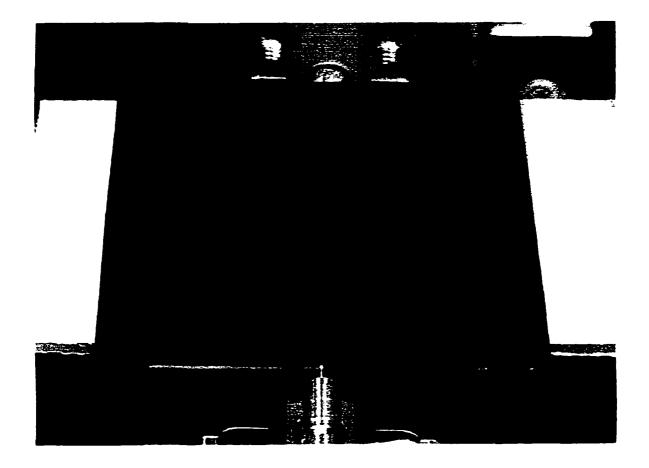

The micromachined silicon mirror array and the through-holes across the OE-MCM are combined and used for I/O couplers on the OE-MCM [22-25]. Figure 1-3 shows a side view of the micro-opto-electro-mechanical-systems (MOEMS) prototype after assembly. The beam comes from the core of the waveguide, and reflects at the mirror's surface, and then goes to the detector.

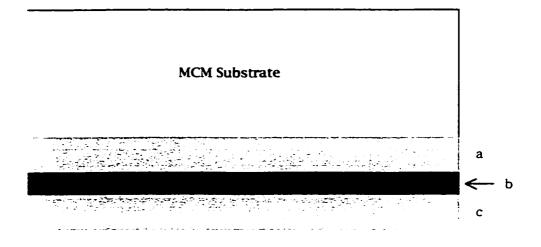

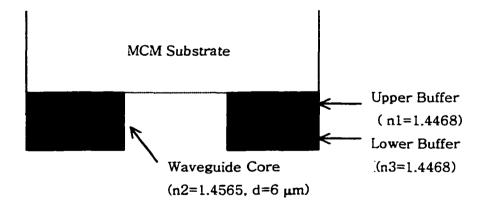

The optical waveguides are composed of symmetric, three layers, and the structure of the layers is shown in Figure 1-4. The photonic integrated circuits (PIC) for the optical clock distribution network (OCDN) have been designed by considering the following requirements: PIC sizes determined by the minimum bending rules, waveguide and coupling excess losses, and distribution of equivalent powers at the clock fan-out nodes.

#### <u>OE-MCM</u>

The multichip module (MCM) is a new packaging approach in which multiple bare chips are mounted and interconnected on a substrate. Some of the problems such as propagation delay, packaging, and power dissipation can be solved by using MCM technology [26-28]. But other problems such as electromagnetic interference, number of chip I/O pads, and maximum interconnection density remain even in the MCM environment for high speed digital applications. Optical interconnects are a potential solution to these problems [29-33]. There are two types of optical interconnections: guided-wave type and free-space type. The guided-wave type is superior to the free-space type in coupling efficiency, compactness and mechanical stability [34,35]. In this project, high silica glass guided-waves are used as optical interconnections for the global signal distribution [36,37].

#### **Research Objectives**

The objective of this research is to build a MOEMS prototype by using bulk micromachining technologies. The fabricated MOEMS prototype is a guided-wave optoelectronic clock distribution network on MCMs, which utilizes silica glass waveguides and micromachined silicon microstructures.

The micromachined microstructures include a silicon mirror array and the through-holes across the MCM substrates. Since these microstructures require very deep etch depths ( $1000 - 1300 \mu m$ ), the design of a mask layer that prevents the corner undercutting is the main objective. These micromachined silicon microstructures are used as optical I/O couplers on the OE-MCM.

The optical waveguides are used for optical interconnection within the MCM. The optical waveguide networks contain many components, such as bending sections and branching waveguides. Therefore, the investigation of these waveguide components is also an objective of this research.

#### **Outline of the Documents**

Chapter 2 presents the mask layer designs for high mirrors that need corner compensation techniques, and for deep through-holes. The fabrication method of the 45° mirror is also introduced. Chapter 3 describes the waveguide network on MCM substrate, including the bending loss theory and branching components. In Chapter 4 experimental procedures for the fabrication of the silicon mirror array and throughholes across MCM substrate are explained in detail. The measured experimental data, assembled structure, excess loss measurements and characterizations are also covered. Finally, Chapter 5 contains conclusions and recommendations for future work.

#### **CHAPTER 2**

#### BULK MICROMACHINING OF SILICON

Silicon micromachining technology has been used to create threedimensional microstructures on silicon substrate in order to form Vgrooves for optical fiber alignment and construct micro-optical elements such as mirrors and through-holes. Through-holes and tall mirrors are fabricated to build MOEMS through this dissertation. And Tetramethylammonium hydroxide (TMAH) is chosen as an etchant for bulk micromachining. Since TMAH is an organic material, it is a potentially ICcompatible etching agent as well as a nontoxic material. Some potential drawbacks of TMAH are high undercutting ratios, surface roughness on the (100) plane, and limited published results [38-40]. Another popular etchant is an aqueous solution of potassium hydrixide (KOH) with concentration ranging from 10 to 50%. However, the selectivity over silicon dioxide is less than 500 at various concentrations, which is not quite enough for masking during long etches [6].

In this chapter, the mask layer design of microstructures and the 45° mirror fabrication method are explained, and wafer preparation, fabrication procedures and results are covered in chapter 4.

#### Mask Layer Design for Mirrors

It is known that there is corner undercutting at the convex corner in the anisotropic etching of (100) oriented silicon wafers [2,4,41,42]. There are two methods that can be used to correct for corner undercutting [43]. The first one is the addition of compensation patterns to the mask corners, and the second one is the tilting of the mask side with respect to the wafer flat by a small angle.

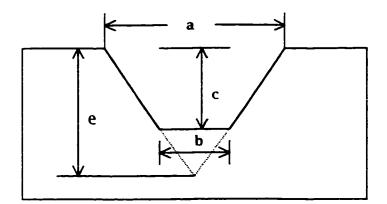

Since the second method is not the efficient way for a given facility with limited functionalities, the first method is chosen to fabricate the mirrors that have mesa structures, and it can be used for guiding the optical signal. Figure 2-1 shows the desired shape of mirror. The required etch depth is 1200 ~ 1300  $\mu$ m, and N-type, 3-inch, 2mm thick wafers are used to create these particularly tall structures.

Figure 2-1. Diagrams for Mirrors

Many types of corner compensation design have been presented. All of the different compensation structures were created based on the fastetching planes [17]. Several methods to compensate corner undercutting have been presented by many researchers. M.M. Abu-Zeid added rectangles to the corner of the square mask pattern and Xian-Ping Wu and Wen H. Ko used triangles, and H. Sandmaier and H.L Offerins attached <110> oriented beams and <110> oriented squares to make the sharp corners [43-47]. But these designs were devised only to use a specific etchant (usually KOH), not for other etchants. Since different etchants show different characteristics such as different lateral etch ratio, their designs could not be adopted directly for our bulk micromachining, which uses TMAH as an etchant. Therefore, a mask that has several test structures was prepared for obtaining the information required to design a corner compensation structure. Figure 2-2 shows the mask layer with different structures. Using the below test structures, the silicon wafer etched at 70°C. This experiment shows the high lateral etch ratio and relatively slow etch rate into the <100> direction. After several experiments, we concluded that 85°C is an optimum etching temperature for our mirror fabrication, considering both surface quality and etch rate. At this particular temperature, the etch rate is  $25 \sim 27 \,\mu$ m/hr and the lateral etch ratio is 6.8 ~ 7.2.

It has been reported that the main beveling planes at undercut corners are all {212} planes, whether KOH or hydrazine or EPW solutions are used as etchant [44]. That means the fastest etching planes do not depend on the etchant but on the atomic density. Therefore, the lateral etch ratio and target etch depth can be the main design parameters

Figure 2-2. Mask Layer for Test Structures

Figure 2-3. Corner Compensation Structure

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

٠

regardless of the etchants used. The first designed corner compensation structure is showed in Figure 2-3. In this design, square patterns are added to the mask corners to correct the corner undercutting. The corner compensation structure is based on M. M. Abu-Zeid's model [43].

But the above model did not work exactly for our case because of the alignment error and imperfect flatness of the silicon wafer. The maximum attainable etching depth was 400  $\mu$ m with this mask layer design for our case, because of the each mirror's location in the silicon mirror array. Figure 2-4 shows the photograph (by using stereo microscope) of the fabricated mirror. It shows the top plane in mesa structure, and it shows the hillocks on the (100) plane. This is one of the disadvantages of TMAH. Since TMAH produces smooth side the {111} planes that are used as mirrors, the quality of (100) surface has nothing to do with the mirror usages.

To obtain the 1200 ~ 1300  $\mu$ m height mirror, the design shown in Figure 2-3 was changed. Simply speaking, the length of the beam should be longer to get the target etch depth. But, the wafer has a limited area for the 16-mask opening with 8 beams each to be located. Therefore, 4 beams per mask opening were removed to prevent the overlapping of beams due to each mirror's location for the alignment with the through-holes. To simplify the design, the width of the beam was changed to narrow and the beam length was decided to have value of around lateral ratio times target etch depth. Figure 2-5 shows the corner compensation structure for the mirror that is supposed to be used in the dissertation. Four beams are attached to the squares.

Figure 2-4. Fabricated Mirror

Stopping the etching process properly before the corner structures start to collapse is one of hardest jobs in mirror fabrication. Thus to easily find the stopping point of etching, the left side of the arms are designed longer than the right hand side arms. The etching process is stopped when the short-arm side of the corner structure begins to collapse. Since only one side plane of the four side planes in the mirror structure is used for the guiding optical signal, this design pattern was possible.

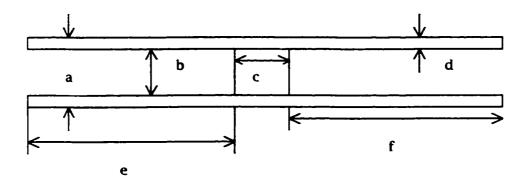

a. 1800 μm b. 1100 μm c. 975 μm d. 350 μm e. 9315 μm f. 8615 μm

Figure 2-5. Corner Compensation Design

Figure 2-6. Mask Layer for Symmetric Sixteen Mirrors

#### Mask Design for Through-Holes

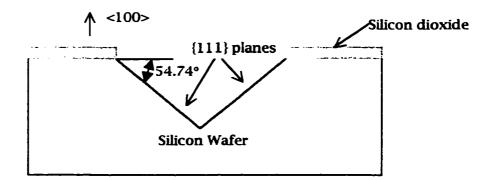

As opposed to a convex structure such as a mirror structure, a through-hole is a concave structure. The forms resulting from concave structures are dominated by slowly etching planes [17]. Since silicon belongs to the diamond cubic crystal structure, the (111) plane has a very high atomic packing density, and (100), (110) planes have low atomic packing densities. Therefore, micromachined structures are bounded by high atomic density planes. Figure 2-7 shows the {111} planes after micromachining of silicon.

Figure 2-7. Micromachined Silicon Substrate

In the above figure, a mask opening is aligned to the <110> direction, and 54.74° has come from the following simple vector algebra:

$$\theta = COS^{-1} \left[ \frac{(111) \bullet (100)}{|(111)| \times |(100)|} \right] = COS^{-1} \left( \frac{1}{\sqrt{3} \times 1} \right) = 54.74^{\circ}$$

where  $\theta$  is the angle between (111) plane and (100) plane.

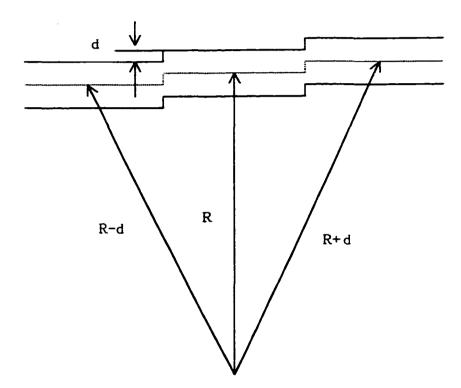

If the silicon substrate is immersed in an anisotropic etchant such as TMAH, etching will proceed in the <100> direction until the etch front hits the {111} planes, intersecting the (100) plane at the edge of mask opening, and the etching will stop as in Figure 2-7 [41]. In bulk micromachining, the required area on the silicon wafer surface is larger than actual device size because of the anisotropic wet chemical etching characteristics. The diagram in Figure 2-8 explains this characteristc.

Figure 2-8. Geometry of an Etched Pit

In Figure 2-8, a is the mask opening, b is the width after some amount of etching, c is the etching depth after some amount of etching, and e is the etching depth when the etching ceases. The etch depth to oxide opening ratio is 0.707. And the relation between a, b and c can be driven as follows:

$$\frac{c}{(a-b)} = \frac{\tan \theta}{2} \quad \text{where } \theta \text{ is } 54.74^{\circ} \text{ .}$$

$$a - b = \frac{2c}{\tan \theta} = \sqrt{2}c$$

$$\frac{c}{a} = \frac{c}{b + \sqrt{2}c} \qquad \qquad \frac{c}{a} = 0.707, \text{ if } b = 0$$

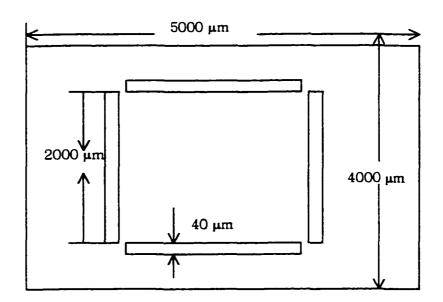

From the above equations, we know the enlargement effect of bulk micromachining. Therefore, the width of the oxide opening should be 1.414 times larger than the actual device feature size. With this concept, a mask layer for back side opening squares was designed, and special alignment marks were used for minimizing the alignment error. Because the front side of the substrate is covered with silica glass, it is hard to see the alignment mark on front side of the substrate even though the IR aligner is used for the back side lithography. Figure 2-9 shows the dimensions and shape of the mask layer design.

Figure 2-9. Mask Layer for Through-Holes

Figure 2-10. Mask Layer for Sixteen Through-Holes

## Fabrication of 45° Mirrors

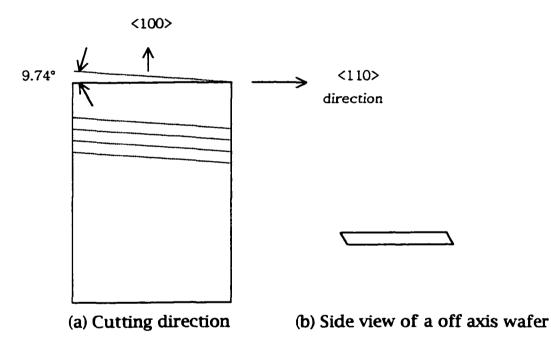

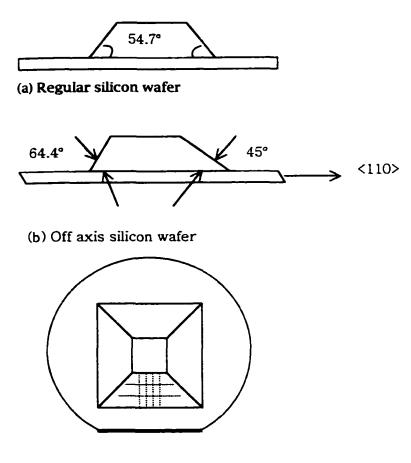

In integrated optic devices, the purpose of the mirror is to change the direction of the guided beam. Compared to the 54.74° mirror, the 45° mirror provides more accuracy in guiding the beam. There are two methods to fabricate the 45° mirror. One is to reveal the {110} planes on (100) silicon wafer, and the other is to use a 9.7° off axis (100) silicon wafer [48,49]. In our project, the second method was used to create the 45° mirror. Figure 2-11 shows the geometry of the off axis (100) silicon wafer.

Figure 2-11. Geometry of Off Axis Silicon Wafer

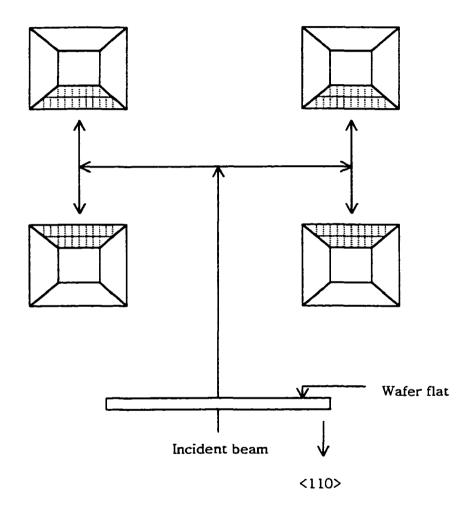

The dot lines, which are slanted 9.7° to <110>, indicate the wafer cutting direction. From the above figure, the front surface can be easily recognized by investigating the edge side. Since there is no mark on the silicon surface, determining which one is the front side is very important for designing the 45° mirror. Figurer 2-12 shows the angle of mirror plane with (100) surface.

(c) Top view

Figure 2-12. Location of 45° Mirror

The hatched region on the above figure is the plane that has a 45° to the (100) surface. The opposite side has a 64°. The figure shown below displays the necessary location of the 45° mirrors and the direction of the incident beam.

Figure 2-13. Direction of Incident Beam to 45° Mirrors

To achieve the desired location of the 45° mirrors, the wafer should be cut and flipped over parallel to the flat, and each piece of wafer should be bonded to the pyrex glass. Figure 2-14 shows the 45° mirror on the topside and 64° mirror on the bottom. It also shows the attatched corner compensation beams, which are slanted.

Figure 2-14. 45° Mirror During Bulk Micromachining

# CHAPTER 3

## INTEGRATED OPTIC WAVEGUIDE

To distribute the global signal within the multi chip module (MCM), guided-waves using a silica glass optical waveguide were designed, fabricated and characterized. The single-mode, step-index, buried-type silica glass waveguide networks were designed by utilizing H-tree network configuration and 3 dB Y-branching beam splitters to minimize the propagation losses and clock skew [50-53]. The Y-branching for 3 dB coupling has been selected due to its polarization and wavelength insensitive characteristics.

The silica glass optical waveguide networks are deposited on the silicon wafers using flame hydrolysis deposition (FHD) processes. The photonic integrated circuits are composed of three layer silica glasses and the waveguide is designed to be symmetric, single-mode, step-index, and buried type. The waveguide is formed, using silica glass layers with the varying refractive indices, by differing impurity doping levels in the silica glass. The channel waveguide has been formed using the reactive ion etching (RIE) process. The cross-sectional dimension of the waveguide is 6  $\mu$ m by 6  $\mu$ m, and the I/O coupling sidewall has been designed to be 1200  $\mu$ m by 1200  $\mu$ m to accommodate the silicon mirror arrays. The fabricated optical waveguide network is characterized by measuring the excess losses at the wavelength of 1550 nm.

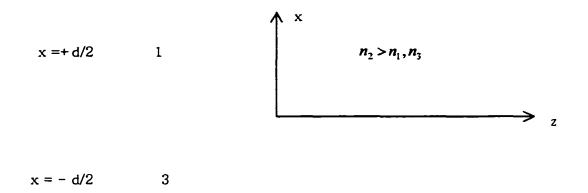

## <u>Planar Waveguide</u>

The channel waveguide, which is symmetric, and has a single-mode, was used as an optical interconnection within the MCM. Channel optical waveguides differ from planar waveguides in that they have additional transverse direction field confinement. But the investigation of planar waveguide theories is necessary to understand the wave propagation phenomena. In this section, cutoff frequency and cutoff thickness of the waveguide core at different wavelengths are calculated based on the planar waveguide theories. The design parameters and structures are shown in Figure 3-1.

Figure 3-1. Silica Glass Waveguide Substrate

The space between waveguides shows the I/O coupling side wall and reveals that the core diameter is 6  $\mu$ m. This waveguide network is used at the wavelength 1550 nm. Using the above parameters and a guidance condition for a symmetric waveguide, propagation mode is found graphically.

$$\tan(\frac{k_{2x}d}{2}) = \frac{\alpha_x}{k_{2x}} \tag{3-1}$$

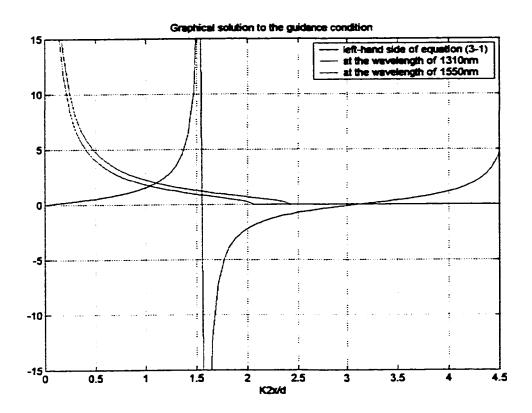

where  $k_{2x} = \sqrt{\omega^2 \mu_0 \varepsilon_2 - k_z^2}$ , d is a diameter of the core, and  $\alpha_x$  is decay coefficient. The above guidance condition was drived under the assumption: (1) z is the direction of propagation, (2) the waveguide core is located between x = -d/2 and x = d/2, and (3) there is no field variation along the y direction. Figure 3-3 shows the graphical solution to the above equation.

Figure 3-2. Three Layer Waveguide.

Figure 3-3. Graphical Solution of the Guidance Condition

The intersection point in Figure 3-4 represents the allowed solution. According to the graphical solution, only one mode is propagating in the optical waveguide network at two different wavelengths. But Figure 3-3 shows that the plot of the right-hand side of the equation (3-1) at 1310 nm wavelength is placed to right of the plot at 1550 nm. This means increasing frequency can introduce more propagating modes. Tables 3-1 and 3-2 show the cutoff thickness of core and the effective refractive index at two wavelengths for given refractive indices (n1 and n2) and core diameter (d).

| Table | 3-1. | Cutoff | Thickness |

|-------|------|--------|-----------|

|-------|------|--------|-----------|

| wavelength      | nl     | n2     | Cutoff thickness |  |

|-----------------|--------|--------|------------------|--|

| 1.31 µm         | 1.4468 | 1.4565 | 3.9031 µm        |  |

| 1.55 μ <b>m</b> | 1.4468 | 1.4565 | 4.6182 µm        |  |

Table 3-2. Effective Refractive Index

| wavelength |        | -2     | Effective        |  |

|------------|--------|--------|------------------|--|

|            | nl     | n2     | Refractive Index |  |

| 1.31 µm    | 1.4468 | 1.4565 | 1.4545           |  |

| 1.55 µm    | 1.4468 | 1.4565 | 1.4540           |  |

# Channel Waveguide

Channel waveguides have additional confinement in the transverse direction, so they give the desirable device characteristics. Channel waveguides are used in many active and passive devices of integrated optics, including lasers, modulators, switches and directional couplers [54].

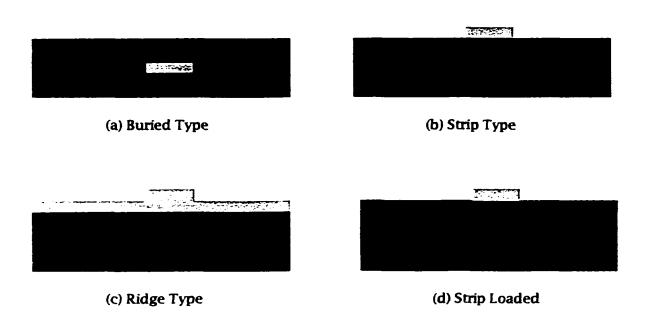

# Channel Waveguide Types

Generally, there are four types of channel waveguides. Figure 3-4 shows channel waveguide structures.

The analysis of a channel waveguide is generally a complicated problem, and different approaches are used for each type. Since the analysis of the channel waveguide requires solutions of partial differential equations, powerful computers are necessary to obtain numerical solutions such as finite element (FE), finite difference (FD), method of lines (MoL) [55]. Although numerical methods are required to obtain the solutions, there are several approximations such as effective index method and Marcatili's method [56,57].

#### Radiation Bending Loss

When guided wave optoelectronic interconnections are designed on a single chip or multichip to make the signal distribution, sometimes bending sections are required. In this region, power loss happens because there is a change in propagation. In this section, the theory of bending loss and a new design for the bending section are introduced. Many bending loss theories and improved structures have been presented [58,59]. In this section, we followed Donald Lee's approach.

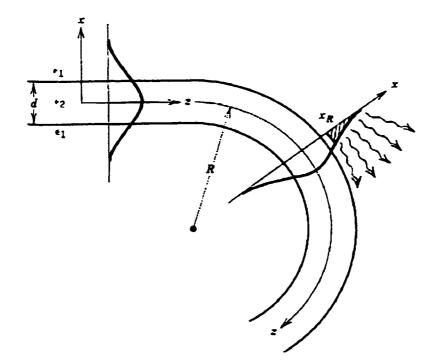

Changes in propagation direction within a waveguide cause a portion of the power to be radiated away from the guiding layer. Figure 3-5 shows the bending section of the waveguide. If the phase velocity  $(V_p = \omega/k_z)$  is measured along the axis of the bend under the approximation of  $\mathbf{R} \rightarrow \infty$ , this would be equal to the tangential velocity at R from the center of the curvature.

Figure 3-5. Bending Section of the Waveguide [58]

$$\frac{\omega}{k_z} = R \frac{d\theta}{dt} \tag{3-2}$$

In the upper buffer layer, the above equation changed as follows:

$$\frac{\omega}{k_1} = (x_r + R)\frac{d\theta}{dt}$$

(3-3)

where  $k_1 = \omega \sqrt{\mu_0 \varepsilon_1}$

By combining the equation (3-2) and (3-3),  $x_r$  is given in terms of the waveguide parameters by

$$x_r = \left(\frac{k_z - k_1}{k_1}\right) R \tag{3-4}$$

As the guided mode enters the bending section, the portion of the evanescent tail beyond x, cannot travel as fast as the guided mode and so it splits away from the guide and radiates into upper buffer layer. If we assume that the rate of loss of total power contained in the waveguide at z is proportional to the power contained in the mode at that point, then

$$\frac{-dP(z)}{dz} = \alpha P(z) \tag{3-5}$$

where P(z) is the total power contained in the mode at any point z along the bend,  $\alpha$  is the proportionality constant.

The above equation has the solution

$$P(z) = P(0)e^{-\alpha z}$$

(3-6)

and  $\alpha$  is identified as the exponential decay constant. To compute the attenuation, equation (3-6) is solved for  $\alpha$ .

$$\alpha = \frac{dP(z)/dz}{P(z)}$$

(3-7)

If the amount of power lost between the z and  $z + \Delta z$  is defined as  $P_L$ , then for small  $\Delta z$ ,  $\alpha$  is approximated as

$$\alpha \cong \frac{P_L(z)}{\Delta z P(z)}$$

(3-9)

And the quantity  $\frac{P_L}{\Delta z}$  can be obtained following way:

$$\frac{P_L}{\Delta z} = \frac{power \ contained \ in \ tail \ at \ z}{dis \tan ce \ for \ power \ in \ tail \ to \ radiate \ away}$$

(3-10)

$\Delta z$  can be estimated by treating the portion of the waveguide field beyond  $x = x_r$ , radiating aperture as shown in figure 3-6.

Figure 3-6. Radiation Aperture for Fields on a Curved Waveguide [58]

In upper buffer layer, the dispersion relationship is

$$k_x^2 + k_z^2 = k_1^2 \tag{3-11}$$

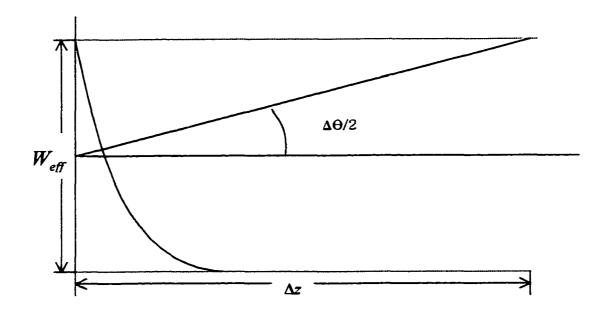

If  $k_x \ll k_1$ , the corresponding angular spread  $\Delta \Theta$  is given by

$$\tan\frac{\Delta\theta}{2} \cong \frac{\Delta\theta}{2} = \frac{k_x}{k_1} = \frac{\alpha_x\lambda_1}{2\pi}$$

therefore,

$$\Delta z \cong \frac{\pi W_{\text{eff}}}{\alpha_x \lambda_1} = \frac{\pi}{\alpha_x^2 \lambda_1}$$

(3-12)

Since the field at the aperature varies as  $e^{-\alpha_r x}$ , the aperature width can be approximated as  $W_{eff} \cong \frac{1}{\alpha_r}$ .

To find the exponential decay constant,  $P_L$  (amount of power lost between the arbitrary planes z and  $z + \Delta z$ ) and P (z) (total power contained at any point z along the bend) should be derived. The power radiated away per unit length along z is

$$P_L = \frac{1}{2} \operatorname{Re} \int_{x_r}^{\infty} (\vec{E} \times \vec{H}^*) \cdot \hat{z} \, dx \tag{3-13}$$

And the total power is

$$P = \frac{1}{2} \operatorname{Re} \int_{-\infty}^{\infty} (\vec{E} \times \vec{H}^{*}) \cdot \hat{z} \, dx \qquad (3-14)$$

For the fundamental mode on the symmetric slab waveguide,

$$\frac{1}{2}\operatorname{Re}(\bar{E}\times\bar{H}^{*})\cdot\hat{z} = \frac{k_{z}}{2\omega\mu_{0}}\left|E_{y}\right|^{2}$$

(3-15)

Using an equation (3-15),  $P_L$  and P expressed as follow.

$$P_{L} = \frac{k_{z}}{a\omega\mu_{0}\alpha_{x}} |A|^{2} \cos^{2}(k_{2x}d/2)e^{\alpha_{x}(d-2x_{r})}$$

(3-16)

$$P = \frac{k_z}{4\omega\mu_0} |A|^2 (d+2/\alpha_x)$$

(3-17)

where A is the amplitude coefficient. Therefore  $\alpha$  is expressed as

$$\alpha = \frac{\alpha_x^2 \lambda_1}{\pi(\alpha_x d + 2)} \cos^2(k_{2x} d/2) e^{\alpha_x d} \exp[-2\alpha_x (k_z - k_1) R/k_1]$$

(3-17)

The above equation can be written as the functional form

$$\alpha = C_1 e^{-C_2 R} \tag{3-18}$$

where  $C_1$  and  $C_2$  are independent of radius R. When only a single-mode is guided, the propagation constant  $k_2$  can be approximated as follows.

$$k_{z} = \left(k_{1}^{2} + \alpha_{x}^{2}\right)^{1/2} = k_{1}\left(1 + \alpha_{x}^{2}/k_{1}^{2}\right)^{1/2} \cong k_{1} + \frac{1}{2}\frac{\alpha_{x}^{2}}{k_{1}}$$

(3-19)

In this case,  $C_1$  and  $C_2$  are expressed as

$$C_{1} = \alpha_{x}^{2} / k_{1}$$

$$C_{2} = \alpha_{x}^{3} / k_{1}^{2}$$

The quantity  $\alpha_x$  can be obtained in terms of the waveguide parameters.

$$\alpha_r d = \sqrt{v^2 + 1} - 1 \tag{3-20}$$

where v is the frequency parameter that is related to the normalized film thickness.

$$v = k_1 d \left( \frac{n_2^2}{n_1^2} - 1 \right)$$

(3-21)

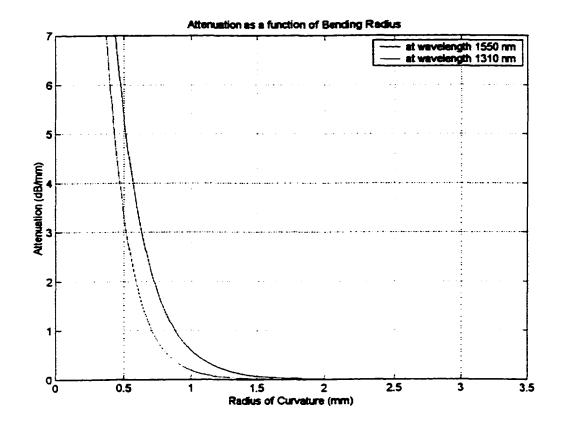

Figure 3-7 shows the attenuation as a function of bending radius at two different wavelengths. From the figure 3-7, it is noted that radiation loss increases exponentially with decreasing bending radius. In integrated optic devices there are limited available spaces, so a bending radius cannot be increased beyond a specific point to further reduce the radiation loss. To solve this problem, a new bending design was suggested. Figure 3-8 shows the bending section of the waveguide, which consists of many segments [59].

Figure 3-7. Attenuation as a Function of Bending Radius

·

Figure 3-8. New Bending Section Design

#### **Y-Branching Waveguide**

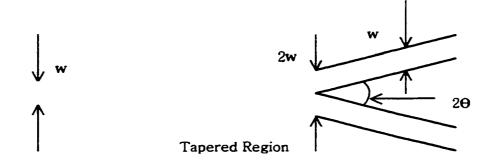

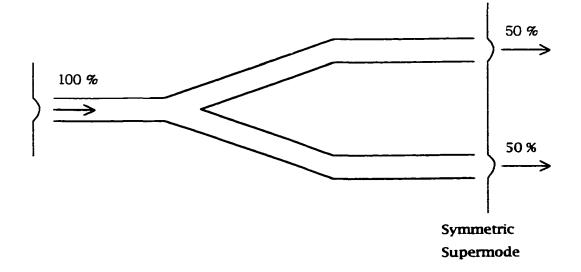

A single-mode Y-branching waveguide is used as a power divider or combiner [60-64]. Figure 3-9 shows the structure of the Y-branching waveguide.

Figure 3-9. Y-Branching Waveguide Structure.

A Y-junction consists of a single-mode input guide that is gradually separated by a tapered region into two similar single-mode ouput guides. When light is incident from the one-waveguide end, the gradual taper of the waveguide width causes the light to spread with most of the power staying in the lowest-order mode of the waveguide. As this light is incident on the two-waveguide section, the incident light is divided and equal amounts of power propagate in the two branches with some scattering loss at the junction [61].

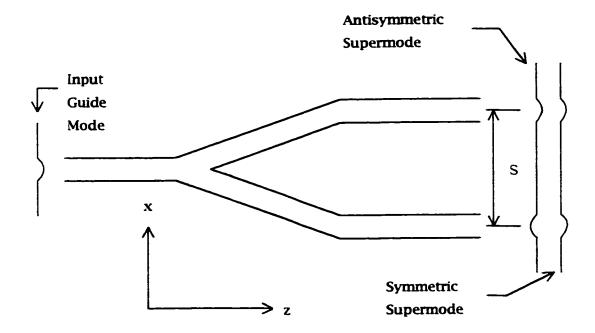

Since the operation of this device is complicated, it is useful to see the characteristic modes of the entire structure at each end [62].

45

Figure 3-10. Characteristic Modes of a Symmetric Y-Junction [62]

The left side of the structure consists of one single-mode guide that supports a characteristic mode with a transverse field distribution

$$E_L(\mathbf{x}, \mathbf{y}) = E(\mathbf{x}, \mathbf{y}) \tag{3-22}$$

The right end of the device consists of two similar single-moded guides separated by a distance S. The transverse field patterns are

$$E_{RU}(x,y) = E(x - S/2, y)$$

and  $E_{RL}(x,y) = E(x + S/2, y)$  (3-23)

where  $E_{RU}$  and  $E_{LU}$  are transverse patterns of the upper and lower guides. The combined structure at the right hand end can be thought of as

a composite guide that supports its own characteristic modes, known as supermodes. Since the structure is symmetric, we shall assume that the supermodes are symmetric and anti-symmetric field patterns. These patterns are labeled  $E_{RS}$  and  $E_{RA}$ . Therefore, at the right-hand end of the device, we assume that the combined structure can support two guided supermodes of the form:

$$E_{RS}(x, y) = E_{RU} + E_{RL}$$

$$E_{RA}(x, y) = E_{RU} - E_{RL}$$

(3-24)

Figure 3-10 shows the response to an input to the single guide at the left end. At some reference point near the input, the transverse field can be taken as

$$E_m = a_m E_L(\mathbf{x}, \mathbf{y}) \tag{3-25}$$

where  $a_{in}$  is the input mode amplitude. According to the theory of local normal mode, the single input gradually converts into the symmetric supermode in the tapered region. Because the taper itself is symmetric, no anti-symmetric modes can be excited. At some reference point near the output, the transverse field can be written as

$$E_{out}(x, y) = a_{out} E_{RS}(x, y)$$

(3-26)

Figure 3-11. Excitation of a Y-Junction at the Left End [62]

Assuming 100% efficiency, the field amplitude can be calculated. The input power is given by

$$P_{in} = (\beta / 2\omega \mu_0) a_{in}^2 \langle E, E \rangle$$

(3-27)

where  $\beta$  is propagation constant and  $\langle E, E \rangle = \int_{\infty}^{\infty} E^2 dx$ . While the output power is

$$P_{out} = (\beta / 2\omega \mu_0) a_{out}^2 \langle E_{RS}, E_{RS} \rangle$$

(3-28)

If the two output guides are sufficiently far apart, equation (3-28) can be approximately written as follows:

$$P_{out} = (\beta / 2\omega\mu_0) a_{out}^2 \{ \langle E_{RU}, E_{RU} \rangle + \langle E_{RL}, E_{RL} \rangle \}$$

=  $2(\beta / 2\omega\mu_0) a_{out}^2 \langle E, E \rangle$  (3-29)

where we have assumed that  $\langle E_{RU}, E_{RU} \rangle \approx 0$ . From equation (3-27) and (3-29),

$$a_{out} = \frac{a_{in}}{\sqrt{2}} \tag{3-30}$$

Equation (3-26) can be reexpressed as

$$E_{out}(x, y) = (a_{in} / \sqrt{2}) E_{RU}(x, y) + (a_{in} / \sqrt{2}) E_{RL}(x, y)$$

(3-31)

The equation implies that the Y-junction divides the input equally between the two output guides. The derivation of equation (3-31) follows Richard Syms and John Cozens's book. The operation as a power combiner was described by these researchers [62,65].

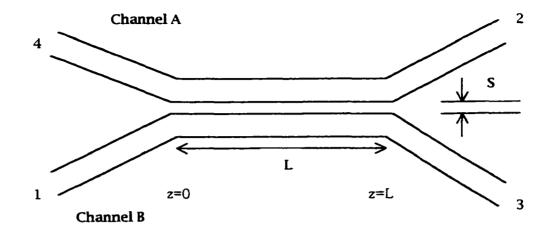

# **Directional Coupler**

Directional coupler is a fundamental element in optical integrated circuits (OIC) and forms the basis of many distribution networks [66-68]. Figure 3-12 shows the typical four-port directional coupler.

Figure 3-12. Directional Coupler

The coupling of light between two channel waveguides A and B occurs when light propagates as long as the separation between two channels is small. By using coupled mode theory, output powers at port 2 and port 3 can be expressed as [58]

$$P_{A} = P_{m} \frac{|C_{BA}|^{2}}{S^{2}} \sin^{2}(Sz)$$

(3-32)

$$P_{B} = P_{in} \left[ \left( \frac{\Delta k}{2S} \right)^{2} \sin^{2}(Sz) + \cos^{2}(Sz) \right]$$

(3-33)

where C,  $P_A$ ,  $P_B$ ,  $P_m$  and S are the coupling efficiency, output power at port 2, output power at port 3, input power and the separation between two identical channel waveguides, respectively.

$\Delta k$  and S are given as

$$\Delta k = k_{zA} - k_{zB}$$

$$S = \sqrt{\left(\frac{\Delta k}{2}\right)^2 + C_{BA}C_{AB}}$$

Under phase-matched conditions ( $\Delta k = 0$  and  $C_{AB} = C_{BA} = C$ ),

$$P_{A}(z) = P_{in} \sin^{2}(Cz)$$

(3-34)

$$P_B(z) = P_m \cos^2(Cz)$$

(3-35)

Equations (3-34 &3-35) indicate that the length  $L_{dc}$  required for total power transfer under phase-matched condition. From equation (3-34)

$$\sin(CL_{dc}) = 1$$

$$L_{dc} = \frac{\pi}{2C}$$

(3-36)

Light will completely couple from one waveguide to the other at integral multiples of  $L_{dc}$ . For making 3 dB couplers, coupling length is adjusted as follows:

$$L_{1dB} = \frac{\pi}{4C} \tag{3-37}$$

For non-phase-matched condition ( $\Delta k \neq 0$ ), complete power transfer cannot occur.

The maximum power transfer to channel A occurs when  $Sz = \frac{\pi}{2}$ .

$$P_{A_{-\text{consx}}} = P_{in} \frac{|C_{BA}|^2}{C_{AB}C_{BA} + \Delta k^2 / 4}$$

(3-38)

From the above equation, we know that power transferred to channel A depends on phase mismatch ( $\Delta k$ ). The appreciable power transfer requires that [38]

$$|\Delta k| < 2\sqrt{C_{AB}C_{BA}} \tag{3-39}$$

#### Fiber-to-Waveguide Couplers

One of the key elements of an integrated optic system is the coupler that transfers the optical waves between a fiber and a waveguide of the OIC [69]. The coupling efficiency depends on the overlap integral between the field profile of the incident wave and the modal profile of the guided mode [70]. In this section, the discussion of butt coupling, and grating couplers is presented.

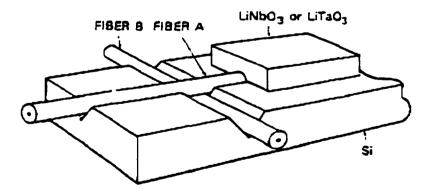

## Butt Coupling

Butt coupling is the process of forming the junction between entirely different guides. The fiber may be directly butted in contact with the waveguide, without any interfacing device, in an end-on alignment [69]. Fiber-to-waveguide butt coupling has a high efficiency coupling, if the numerical aperture, the field profile, and fiber-to-waveguide alignment are matched. Since both optical fiber core and channel waveguide core have the dimensions around few micro-range, it is very difficult to align them.

The silicon V-groove technique has been introduced to align a channel waveguide with a single-mode optical fiber [71]. Sheem and Giallorenzi showed the alignment between 3  $\mu$ m channel waveguide core and 4.5  $\mu$ m fiber core using two-dimensional groove pattern on a silicon wafer. Figure 3-13 shows the schematic diagram of the alignment.

Figure 3-13. Fiber-to-Channel Waveguide Using Silicon Grooves [71]

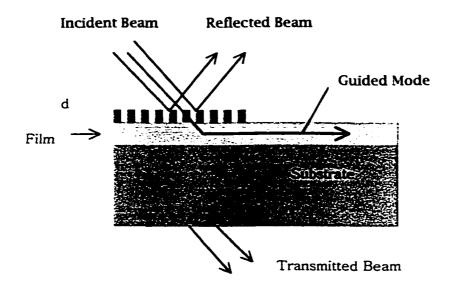

## **Grating Coupler**

Figure 3-14. Grating Coupler

The structure of the grating coupler is shown in figure 3-14. The grating coupler produces a phase matching between a particular waveguide mode and unguided optical beams which is incident at an oblique angle to the surface of the waveguide [69]. The operation of the grating coupler is understood on the basis of the coupled mode theory. But there is an additional aspect because of its periodic nature. Therefore, the propagation wave vectors in the grating have the form [72]

$$\beta_{gr} = \beta_0 + \frac{2\pi\nu}{d} \tag{3-40}$$

where and  $\nu = 0, \pm 1, \pm 2, \pm 3,..., d$  is the periodicity of the grating. The fundamental factor  $\beta_0$  is approximately equal to the propagation in the

guide. The phase matching condition between grating-waveguide region and the air is given by [72]

$$k_a \sin \theta = \beta_{gr} \tag{3-41}$$

where  $k_a$  is the wavevector in air and  $\theta$  is the incidence angle.

The main advantage of the grating coupler is that it can be the integral part of the waveguide structure, however its coupling efficiency is not as good as the prism coupler because of the transmitted beams.

# **Test Results and Characterizations**

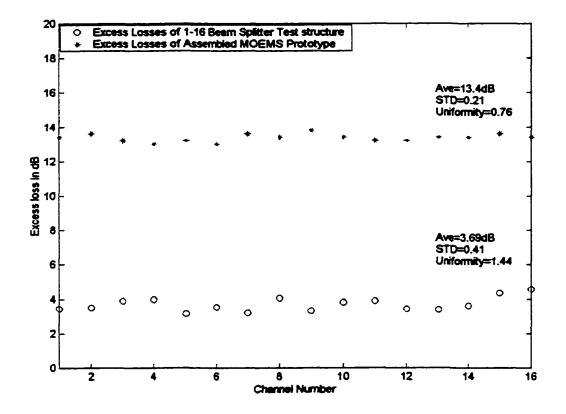

The actual power available to the detector is determined by the source power and the losses throughout the distribution system [25]. In this system, the power is required to be split equally and transferred to sixteen-fan-out. Input coupling to sixteen-fan-out OCDN is shown in Figure 3-15. Table 3-3 shows the optical power loss and signal uniformity. The test structures with one-to-sixteen beam splitters have shown a positive results with an average excess loss of 3.69 dB and signal uniformity of 1.44 dB at the wavelength of 1550 nm.

Table 3-3 Total Excess Losses for 1-to-16 Splitter Test Structure.

| Channels  | 1     | 2     | 3       | 4     | 5     | 6          | 7     |

|-----------|-------|-------|---------|-------|-------|------------|-------|

| Power(dB) | -3.44 | -3.49 | -3.89   | -3.96 | -3.13 | -3.52      | -3.20 |

| Channels  | 8     | 9     | 10      | 11    | 12    | 13         | 14    |

| Power(dB) | -4.05 | -3.30 | -3.79   | -3.88 | -3.41 | -3.38      | -3.61 |

| Channels  | 15    | 16    | Average |       | STD   | Uniformity |       |

| Power(dB) | -4.35 | -4.57 | -3.69   |       | 0.41  | 1.44       |       |

\* The signal wavelength is 1550 nm and the total excess losses include losses from fiber to-waveguide coupling, waveguide propagation, waveguide bending, Y-branch, and waveguide-to-fiber coupling.

Figure 3-15. Sixteen Fan-Out OCDN Prototype Input Coupling

# **CHAPTER 4**

## **PROTOTYPE FABRICATION AND**

# **CHARACTERIZATION**

## **Prototype Fabrication and Procedures**

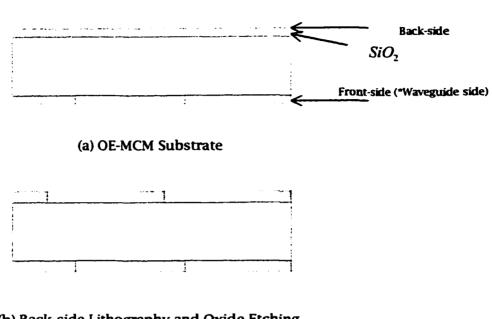

In this section, the procedures of the fabrication process are described. Figure 4-1 and Figure 4-2 show the overall fabrication procedures for mirrors and through-holes. The difference between the fabrications of these two microstructures is a lithography process.

(b) Oxidation

58

(c) Spin Coating, Exposure and Development

(d) Oxide Etch and Photoresist Removal

(e) Silicon Etching on Back Side& Front Side Oxide Removal

(f) Aluminum Coating

Fig 4-1. Fabrication Process of Silicon Mirror

(b) Back-side Lithography and Oxide Etching

(c) Bulk Micromachining

# Figure 4-2. Fabrication Process of Through-Holes

\*Detailed waveguide layers are shown in figure 1-4.

Based on the schematic diagrams shown above, each procedure is described here along with skillful tips.

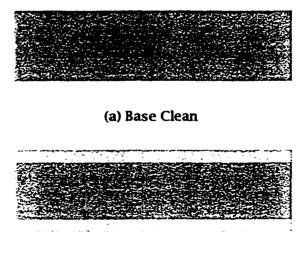

### **Base Clean**

The purpose of this procedure is to remove all the organic dirt from the surface of the silicon wafers prior to processing. To prepare the base cleaning solution, ammonium hydroxide ( $NH_4OH 27\%$  aqueous solution) and deionized water (DI  $H_2O$ ) are mixed in a beaker. Then slowly, the solution is heated on a hot plate to between 75°C and 80°C, and then the beaker is removed from the hot plate, and hydrogen peroxide ( $H_2O_2$  30% aqueous solution) is added. The solution will bubble after 1~2 minutes when it is ready for use. After submerging the wafers into the solution for 15 minutes, the beaker containing the solution and wafers is placed under running DI H<sub>2</sub>O for 3 minutes. During the base cleaning, contaminants tend to float to the top of the solution; therefore, during the DI H<sub>2</sub>O rinse, it is important to flush the water in the beaker several times without allowing the wafers to break the surface of the liquid.

# **Oxidation**

To mask the regions we do not want attacked by anisotropic (wet) silicon etchant when the microstructures are formed, we need to grow a silicon dioxide layer on our silicon substrate. There are two main chemical mechanisms for the growth of oxide by this process. If the oxide grows in the presence of molecular oxygen, a high-quality oxide would be generated, but fairly slowly:

$Si + O_2 \rightarrow SiO_2$

If we bubble the oxygen through water (in our case at a flow rate of 0.3 L/min. at ~ 99°C) we can increase the rate of growth. We then form oxide via the following reaction, with hydrogen as a by-product:

$Si + H_2O \rightarrow SiO_2 + H_2$

This so-called wet oxide is typically not as high quality as that grown by dry oxide as far as adhesion and other properties are concerned. However, it is generated at a much faster rate. Since the etching time required for creating the mirrors is more than 40 hours, enough thick oxide layers were grown on the silicon surface. Using a quartz-tube oxidation furnace, oxide was grown on both sides of the wafers. Typically, there is a 'flat zone' from 10 - 16" somewhere along the length of the furnace where the temperature remains approximately constant. With the help of the push rod, a quartz boat where wafers are loaded is inserted into this region of the furnace very slowly to prevent sudden thermal shock. The procedure for growing the oxide is to use 30 minutes of dry oxidation, 15 hours of wet oxidation, and 30 minutes of dry oxidation in order to obtain good quality oxides at the surface and silicon interface and still grow the oxide in an efficient manner. The oxide thickness was measured by using a Gaertner ellipsometer.

|        | Oxide Layer Thickness (µm) |           |  |

|--------|----------------------------|-----------|--|

| Wafers | Front Side                 | Back Side |  |

| 1      | 1.69                       | 1.69      |  |

| 2      | 1.72                       | 1.73      |  |

| 3      | 1.71                       | 1.73      |  |

| 4      | 1.72                       | 1.72      |  |

| 5      | 1.73                       | 1.73      |  |

Table 4-1. Oxide Thickness

#### Photoresist Spin Coating

In order to perform optical lithography (transferring layered patterns across the wafer to mask certain regions), we must employ a material that changes its solubility when exposed to this type of radiation. Photoresists (PRs) are organic, polymer-based molecules that either become more or less susceptible to dissolution in a developing solution when exposed to radiation (meaning any portion of the material exposed to UV radiation would be dissolved away by the developer, in our case S-351). This allows us to generate patterns by selectively removing or leaving parts of the PR layer on top of the substrate. The photoresist employed was a micro-positive S 1800 series photoresist manufactured by Shipley. S 1800 series are sensitive to light in the UV range and were used to protect the silicon dioxide mask layer from the buffered oxide etching (BOE or BHF) solution when it was used for opening a window in order to form the microstructures in the next step.

Before doing the photoresist spin coating, there is a preparation step for increasing the adhesion of the photoresist. It is a dehydration bake. The wafers are baked in the oven at  $200^{\circ}C$  for 30 minutes and then cooled down at room temperature. After this step, the wafers are ready for a spin coating. If the photoresist is stored in the refrigerator, it is necessary for it to warm up to room temperature. HMDS (hexa-ethyl dislazane) was used as an adhesion promoter, and a micro-positive S 1800 series photoresist was used for spin coating. The table below relates specific S 1800 series products to corresponding film thickness at 3000 to 6000 rpm. The standard product name is derived from the coating thickness at 4000 rpm spin speed.

For this project, 3-inch thick silicon wafers were used. Because of the heavy weight, a high enough rpm could not be reached to obtain the thin layer of photoresist. Therefore, S 1805 photoresist was chosen, and spinning time was increased to obtain uniformly covered thin film. Table 4-3 shows the photoresist spin coating speed and times for 3 inch-thick silicon wafers.

Next, the photoresist was hardened by soft baking so sticking or smearing would not occur during the mask-wafer alignment necessary for exposure. This was done in an oven at 90°C for about 30 minutes.

|         | Micro-Positive 1800 Series Photoresist |         |         |         |  |  |

|---------|----------------------------------------|---------|---------|---------|--|--|

| Product | Photoresist Thickness (µm)             |         |         |         |  |  |

| Type    | 3000 rpm                               | 4000rpm | 5000rpm | 6000rpm |  |  |

| 1805    | 0.54                                   | 0.46    | 0.41    | 0.36    |  |  |

| 1811    | 1.23                                   | 1.06    | 0.93    | 0.83    |  |  |

| 1813    | 1.51                                   | 1.28    | 1.14    | 1.02    |  |  |

| 1815    | 1.78                                   | 1.53    | 1.34    | 1.22    |  |  |

| 1818    | 2.10                                   | 1.82    | 1.59    | 1.45    |  |  |

| 1822    | 2.58                                   | 2.20    | 1.95    | 1.77    |  |  |

# Table 4-2. Photoresist Thickness vs RPM

# Table 4-3. HMDS/PR Spin RPM and Times

|        | HMDS             |      | Photoresist |          |

|--------|------------------|------|-------------|----------|

| Cycle  | Spin Speed (rpm) |      | Time        | e (secs) |

| Spread | 10               | 400  | 10          | 400      |

| Spin   | 60               | 1200 | 60          | 1200     |

.

#### Alignment, Exposure and Development

Alignment is the most important of all the steps because we can not fabricate the precise microstructures if the alignment error is too big. During the soft bake, the aligner must be warmed up to stabilize the UV (ultra violet) light. Once the soft bake is finished, the wafers are cooled down at room temperature, and a mask and a wafer are loaded into the chamber. Then a wafer edge is aligned to the alignment marks on the mask. The exposures take place in the spectral output range of 350 – 450 nm for nine and half seconds. The next procedure is development of S 1805 photoresist. Its purpose is to remove the area of the photoresist film exposed to UV light from the wafers. The preparation and procedures are as follows:

- a. Mix 5 parts of DI water with Shipley 351 developer.

- b. Immerse the wafer into the developer solution for 1 minute.

- c. Rinse the wafer under running DI water for 1 minute.

- d. Blow dry with filtered nitrogen.

After this step, inspection with a microscope is required. If any mistakes are found, every step after the oxidation should be repeated. Figure 4-3 shows the patterns after development.

### Hard Bake and Back Side Protection

After the lithography, a hard bake is necessary to harden the photoresist and to remove the solvent to make it etch resistant. The hard bake procedure is the same as the soft bake procedure, except for the temperature setting.

Figure 4-3. After Development

The hard bake is done at  $105^{\circ}C \pm 5^{\circ}C$ . Now, the wafers are ready for oxide etching, but sometimes photoresist stripping can occur during this process if the wafer is not dry enough or clean enough [3]. Since this project requires a long wet anisotropic etching, the back sides of the wafers should be protected perfectly. In addition, back side spin coating is not desirable because the vacuum pressure between a wafer and a chuck may cause damages on the front side (patterned side) of the wafer. The other problem is protecting the edge. Since the edge side of the wafer is rough compared to the polished surface, the oxide growth rate is low, and this condition makes it hard to cover the edge with photoresist. To solve these problems, the method used to protect an edge and back side of the wafer is as follows:

- a. Prepare 4-inch glass wafers and AZ photoresist.

- b. Spread photoresist on the glass wafer.

- c. Put the silicon wafer on the glass wafer.

- d. Bake at  $60^{\circ}C$  for 12 hours.

#### **Isotropic Etching**

One of the most frequently encountered photolithographic processes in monolithic integrated-circuit fabrication is the selective etching of thermally grown  $SiO_2$  on silicon substrates. Wet chemical etching using HF or buffered HF is the most popular means for accomplishing this process. SiO<sub>2</sub> is readily attacked by room temperature HF, while silicon is not. It is therefore possible to selectively remove  $SiO_2$ with HF solutions. As supplied by the manufacturers of electronic grade chemicals, the HF concentration is 49% aqueous solution. This is too strong a concentration for a controlled pattern definition. The HF can be diluted to 5 to 10% with DI water for a more controlled etch. Diluted HF loses its acidity during the etched process and must be replaced frequently. A more common etchant contains a buffering agent like ammonium fluoride  $(NH_4F)$ , which helps maintain a constant acid-base ratio. In this project, the silicon dioxide was etched in BOE (Buffered Oxide Etching) solution. Since the measured oxide thickness with the ellipsometer was 1.8 µm, etching time was 18 minutes.

The etchant of the BOE is a mixture of 6 parts of  $NH_4F$  and one part of HF (49% aqueous solution). One interesting fact is that silicon is hydrophobic and silicon dioxide is hydrophilic. So the end point of etching can be easily seen. It is recommended, however, to check the etch result under the microscope because there may be little residual oxide spots. After this step, the photoresist is stripped using acetone, and the wafers are base cleaned to remove any organic dirt.

## Anisotropic Wet Chemical Etching of Silicon

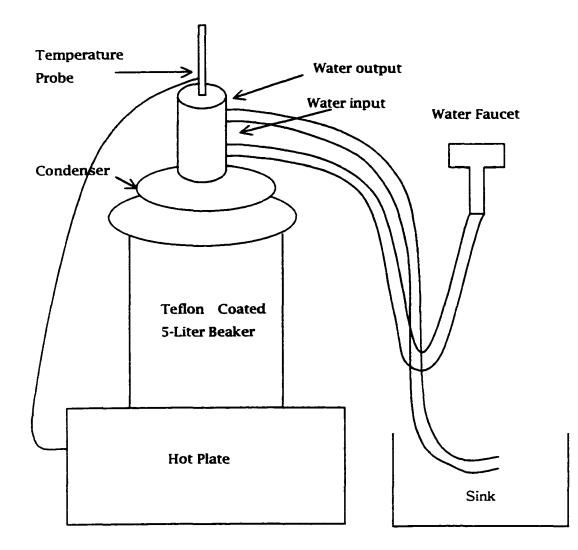

Anisotropic wet chemical etching requires careful attention. Even though TMAH etchant is a nontoxic material, it is very harmful to skin. To obtain the best results, careful measurements of the etch rate and temperature control of the etchant are required. Figure 4-4 shows the etching system for the bulk micromachining of silicon.

Etching of the silicon wafer is processed at different temperatures to measure the etch rate and investigate the surface quality. Since the target etch depth is  $1200 \sim 1300 \mu$ m, both a higher etch rate and a good surface quality are needed to obtain the best reults. Table 4-4 shows the etch rate of silicon at various temperatures. The data reveals that the etch rate increases as the temperature increases. The surface quality, however, degrades at 90°C or higher. Thus it is concluded that 85°C is the optimum temperature for the etching process. After finishing the wet etching process, the residual oxide thicknesses of the wafers are measured. Only 0.3  $\mu$ m is etched in TMAH, and this value is negligible compared to the 1250  $\mu$ m silicon etch. So, the oxide layer on the silicon wafer acts as a good mask layer for the TMAH etching process.

Figure 4-4 Anisotropic Etching System

| Temperature (°C) | Etch Rate (µm/hr) |  |  |

|------------------|-------------------|--|--|

| 70               | 14.3              |  |  |

| 75               | 17.0              |  |  |

| 80               | 19.8              |  |  |

| 85               | 25.6              |  |  |

| 90               | 35.5              |  |  |

| 95               | 45.5              |  |  |

#### Table 4-4 Etch Rate of Silicon Mirror

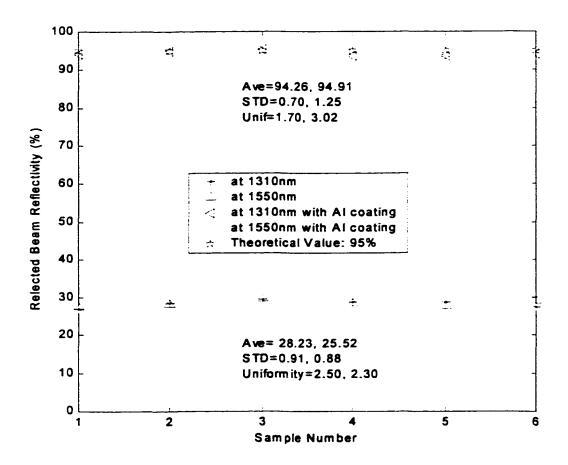

The final step after anisotropic wet etching is a base clean of the silicon wafers to remove any organic etchant. This process is described in previous pages, and the residual oxide is removed by using BOE. After all fabrication steps, the aluminum is coated by using a sputtering machine to increase the reflectivity. The reflectivity of the silicon micromachined mirror array was 30%, but it was increased to 94% after the aluminum coating. This is shown at figure 4-6.

# Through-Holes

The process of making through-holes on MCM substrate is very similar to the process of mirror fabrication steps. The only difference is the lithography process. Infrared (IR) aligner is used for back side alignment and exposure. In this process, etching takes place on both the front side and back side simultaneously. However, there is a slight etch rate difference between the front side and the back side of the MCM substrate.

| Table 4-5. Etch | Rate of | the MCM | Substrate |

|-----------------|---------|---------|-----------|

|-----------------|---------|---------|-----------|

|                  | Etch Rate per Hour (µm/hr) |           |  |

|------------------|----------------------------|-----------|--|

| Temperature (°C) | Front Side                 | Back Side |  |

| 85               | 19.28                      | 22.15     |  |

| 90               | 23.8                       | 27.3      |  |

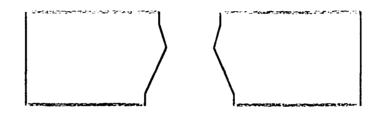

In Figure 4-5, (a) shows the substrate when the through-hole has just been created, and (b) shows the through-hole after the complete etching process.

(a) When through-hole is created

(b) After Complete Etching

Figure 4-5 Fabrication of Through-Hole

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

From Table 4-5 and Figure 4-5, it is shown that the back side of the substrate has a faster etch rate. This is because the back side opening has larger areas that interact with etchant. The dimensions of the openings are shown in table 4-6.

Table 4-6. Dimensions for Opening Squares on MCM Substrate

|            | Size of Opening Squares |  |  |

|------------|-------------------------|--|--|

| Front Side | 1200 μm × 1200 μm       |  |  |

| Back Side  | 5000 μm × 4000 μm       |  |  |

# Measurement Results and Characterizations

Bulk micromachining of silicon using a TMAH provided good etching selectivity and a well-controlled etch rate. Only 0.3  $\mu$ m of the silicon dioxide layer was etched away during more than 40 hours of etching at 85°C. When this value is compared to the 1250  $\mu$ m etch of silicon, it is negligible, and the selectivity is more than 4000. With a determined etch rate and etch selectivity of the TMAH etchant, deep and high quality silicon micromachined structures were fabricated. One interesting fact is that the fabricated structure shows the shape of a table cloth on the corner intersections, even though there is no under cutting. The fabricated silicon mirror prototypes have uniform and repeatable beam guiding performances at the wavelength of 1550 nm. Figure 4-6 shows the beam reflectivity of the silicon micromachined mirror. Aluminum was coated on the silicon mirror arrays to improve the I/O coupling efficiencies of the mirror arrays. Also, Figure 4-6 gives the comparison of the silicon mirror array reflectivity before and after the aluminum coating. It shows that the reflectivity increased from 30% to 94% after the aluminum coating.

Micromachined silicon mirrors array substrate and the sixteen-fanout optical clock distribution network (OCDN) with through-holes were assembled to build an MOEMS prototype. Figure 4-7 shows the assembled OE-MCM prototype and displays the laser beams of 635 nm wavelength at the sixteen fan-out nodes. This OE-MCM has a silicon mirror substrate underneath the optical waveguide layers, which are on the top surface of OE-MCM substrate. The laser signals are coupled into the OE-MCM by using the fiber-to-waveguide butt coupler. In addition, the total excess loss of sixteen-fan-out OE-MCM protype was measured at the wavelength of 1550 nm. Table 4-7 shows the total excess loss for assembled sixteen-fan-out OCDN signal propagation. The total loss includes fiber-to-waveguide coupling, waveguide propagation, waveguide bending, Y-branch, and through-hole output coupling losses. In this situation, the through-hole output coupling loss includes the losses due to mirror reflectivity, and waveguide-to-mirror coupling efficiencies associated with mirror size. The through-hole output coupling losses also include separation between waveguide end-facet and micromachined silicon mirrors.

| Channels  | 1     | 2     | 3       | 4     | 5     | 6          | 7     |

|-----------|-------|-------|---------|-------|-------|------------|-------|

| Power(dB) | -13.4 | -13.6 | -13.2   | -13.0 | -13.2 | -13.0      | -13.6 |

| Channels  | 8     | 9     | 10      | 11    | 12    | 13         | 14    |

| Power(dB) | -13.4 | -13.8 | -13.4   | -13.2 | -13.2 | -13.6      | -13.4 |

| Channels  | 15    | 16    | Average |       | STD   | Uniformity |       |

| Power(dB) | -13.6 | -13.4 | -13.4   |       | 0.21  | 0.         | 76    |

Table 4-7 Excess Losses at 1-to-16 Fan-Out

Figure 4-6. Beam Reflectivity of Silicon Mirror