Technische Universität Dresden

## Advanced Connection Allocation Techniques in Circuit Switching Network on Chip

#### Yong Chen

Born in Anhui, China, 10 June 1989

von der Fakultät Elektrotechnik und Informationstechnik der Technischen Universität Dresden

zur Erlangung des akademischen Grades

#### Doktoringenieur

(Dr.-Ing.)

genehmigte Dissertation

| Vorsitzender: | Prof. DrIng. Christian G. Mayr   |

|---------------|----------------------------------|

| Gutachter:    | Prof. DrIng. Gerhard P. Fettweis |

|               | Prof. DrIng. Holger Blume        |

|               | Prof. Dr. Ing. Ralf Lehnert      |

| Tag der Einreichung:  | 29.06.2017 |

|-----------------------|------------|

| Tag der Verteidigung: | 08.09.2017 |

### Abstract

With the advancement of semiconductor technology, the System on Chip (SoC) is becoming more and more complex, so the on-chip communication has become a bottleneck of SoC Design. Since the traditional bus system is inefficient and not scalable, the Network-On-Chip (NoC) has emerged as the promising communication mechanism for complex SoCs. As some systems have specific performance requirements, such as a minimum throughput (for real-time streaming data) or bounded latency (for interrupts, process synchronization, etc), communication with Guaranteed Service (GS) support becomes crucial for predictable SoC architectures. Circuit Switching (CS) is a popular approach to support GS, which firstly has to allocate an exclusively connection (circuit) between the source and destination nodes, and then the data packets are delivered over this connection. However, it is inefficient and inflexible because the resource is occupied by single connection during its whole lifetime, which can block other communications. Hence, two extensions of CS have been proposed to share resources: i) Time-Division Multiplexing (TDM), in which the available link capacity is split into multiple time slots to be shared by different flows in TDM scheme; and ii) Space-Division-Multiplexing (SDM), in which only a subset (sub-channel) of the link wires is exclusively allocated to a specific connection, while the remaining wires of the link can be used by other flows.

The connection allocation is critical for CS, since the data delivery can start only after the associated connection is allocated. In this thesis, we propose a dedicated hardware connection allocator to solve the dynamic connection allocation problem for CS NoCs, which has to i) allocate a contention-free path between source-destination pairs and ii) allocate appropriate portions of link bandwidth (appropriate number of time slots and subsets) along the path. The dedicated connection allocator, called NoCManager, solves the connection allocation problem by employing a trellis-search based shortest path algorithm. The trellis search can explore all possible paths between source node and destination. Moreover, it shall find the requested path in a fixed low latency and can guarantee the path optimality in terms of path length if the path is available.

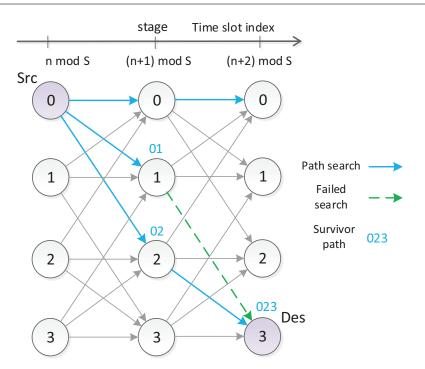

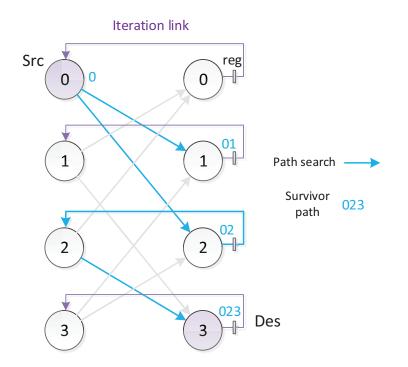

In this thesis, two different trellis graphs, *Forward-Backtrack trellis* and *Register-Exchange trellis* are proposed. The Forward-Backtrack trellis completes the path search in two steps: forward search and backtracking. Firstly, the forward search begins at source node that traverses the network to find the free path. When destination node is reached, the backtrack starts from destination to select the survivor path and collect the associated path parameters. However, Register-Exchange trellis saves the entire survivor path sequences during forward search. Consequently, the backtracking step can be omitted, and thus the

allocation time is halved compared to forward-backtrack approaches. Moreover, each trellis graph consists of three categories, *unfolded structure*, *folded structure* and *bidirectional structure*. The unfolded structure can provide high allocation speed while folded structure is more efficient from a hardware point of view. The bidirectional structure starts the search at two sides, source node and destination node simultaneously, so the allocation speed is 2 times faster than previous unidirectional search. Furthermore, in order to address the scalability issue of previous centralized systems, the partitioned architecture (i.e. spatial partitioning technique) is proposed to divide the large system into multiple smaller differentiated logical partitions served by local NoCManagers. This partitioning technique keeps the request load of the manager and manager-node communication overhead moderate. Inside each partition, the path search problem is solved by a local manager with trellis-search algorithm. To establish a path that crosses partitions, the managers communicate with each other in distributed manner to converge the global path.

In order to further enhance the path diversity and resource utilization, we adopt the combined TDM and SDM technique. In combined TDM-SDM approach, each SDM subchannel is split into multiple time slots so that can be shared by multiple flows. Hence, the number of sub-channels can be kept moderate to reduce router complexity, while still providing higher path diversity than TDM scheme. In order to investigate and optimize TDM-SDM partitioning strategy, we studied the influence of different TDM-SDM link partitioning strategies on success rate and path length that allowed us to find the optimal solution. The dedicated connection allocator using the trellis-search algorithm is employed for TDM, SDM and TDM-SDM CS.

In the end, we present the router architecture that combines the circuit-switching network (for GS communication) and packet-switching network (for best-effort communication).

## Acknowledgment

This thesis comprises of the results generated during my work at the Vodafone Chair Mobile Communications Systems at Technische Universität Dresden between 2013 and 2017.

First of all I would like to thank my supervisor Prof. Gerhard Fettweis for giving me the opportunity to join his group and inspiring me with his invaluable guidance. I cannot be any less grateful to have Prof. Blume as my co-supervisor whose guidance and mentoring had made this journey possible. I also thank my group leader Dr. Emil Matus. Emil is a very good person. He teaches me how to do research, and helps me go through the difficult times. Additionally, I am grateful to my colleagues, Sadia Moriam, Seungseok Nam and Mohammed Radi, for reviewing the thesis.

I would like to thank all colleagues from the chair. I would like to thank Friedrich, Sebastian, Wen, Stefan, Robert, Mattis, Amanda, Song, Zou and Zhang for all the joys and fun shared with me.

Finally, I am grateful to my parents, and my wife Aihong, for their faith in me. Your support, encouragement and unwavering love made me able to finish the thesis.

Yong Chen Dresden, Germany, June 2017

## Contents

| $\mathbf{A}$ | bstra           | $\mathbf{ct}$                                  | III  |

|--------------|-----------------|------------------------------------------------|------|

| Li           | st of           | Symbols                                        | XI   |

| Li           | st of           | Abbreviations                                  | XI   |

| Li           | st of           | Figures                                        | XIII |

| Li           | st of           | Tables                                         | XIX  |

| 1            | $\mathbf{Intr}$ | oduction                                       | 1    |

|              | 1.1             | Overview of on-chip interconnection solutions  | 1    |

|              | 1.2             | Network on Chip                                | 3    |

|              | 1.3             | Guaranteed Service in NoCs                     | 5    |

|              |                 | 1.3.1 Circuit Switching NoCs                   | 6    |

|              | 1.4             | Scope and Outline of this Work                 | 6    |

| <b>2</b>     | Con             | nection Allocation in CS NoCs                  | 9    |

|              | 2.1             | Connection allocation problem                  | 9    |

|              | 2.2             | Related work                                   | 10   |

|              |                 | 2.2.1 Distributed allocation techniques        | 11   |

|              |                 | 2.2.2 Centralized allocation techniques        | 12   |

|              | 2.3             | Trellis Search based Allocation approach       | 13   |

| 3            | Cen             | tralized Connection Allocation for TDM CS NoCs | 15   |

|              | 3.1             | Introduction of TDM CS                         | 15   |

|              |                 | 3.1.1 Connection allocation in TDM CS          | 17   |

| 3.2 | System | n Model     |                                                                           | 17 |

|-----|--------|-------------|---------------------------------------------------------------------------|----|

| 3.3 | Conne  | ection Alle | ocator Architecture                                                       | 20 |

|     | 3.3.1  | Formaliz    | zing The Trellis Graph Structure                                          | 20 |

|     |        | 3.3.1.1     | General Model                                                             | 21 |

|     |        | 3.3.1.2     | Path Search Model Simplification                                          | 25 |

|     | 3.3.2  | Forward     | -Backtrack Trellis Path Search                                            | 25 |

|     |        | 3.3.2.1     | Unfolded Trellis Search                                                   | 29 |

|     |        | 3.3.2.2     | Folded Trellis Search                                                     | 29 |

|     |        | 3.3.2.3     | Bidirectional Trellis Search                                              | 31 |

|     | 3.3.3  | Forward     | -Backtrack Trellis Path Search Implementation                             | 31 |

|     |        | 3.3.3.1     | Unfolded Trellis Implementation                                           | 32 |

|     |        | 3.3.3.2     | Bidirectional Trellis Implementation                                      | 34 |

|     |        | 3.3.3.3     | Folded Trellis Implementation                                             | 34 |

| 3.4 | Perfor | mance Ev    | valuation of Forward-Backtrack trellis                                    | 35 |

|     | 3.4.1  | Synthes     | is Results                                                                | 35 |

|     | 3.4.2  | Simulati    | ion Results                                                               | 38 |

|     |        | 3.4.2.1     | Comparison with centralized exhaustive path-search $\ . \ .$ .            | 39 |

|     |        | 3.4.2.2     | Comparison with distributed parallel probe search $\ . \ . \ .$           | 41 |

|     |        | 3.4.2.3     | Influence of splitting the link into different time slots on success rate | 45 |

|     |        | 3.4.2.4     | Influence of allowing different hops of detours on success                |    |

|     |        |             | rate                                                                      | 45 |

| 3.5 | Regist | er-Excha    | nge Trellis Search                                                        | 47 |

|     | 3.5.1  | Register    | -Exchange Trellis Path Search Algorithm                                   | 47 |

|     |        | 3.5.1.1     | Unfolded Register-Exchange Trellis Path Search                            | 47 |

|     |        | 3.5.1.2     | Folded Register-Exchange Trellis Path Search                              | 49 |

|     | 3.5.2  | Trellis F   | Path Search Implementation                                                | 49 |

|     | 3.5.3  | Perform     | ance Evaluation                                                           | 51 |

|     |        | 3.5.3.1     | Synthesis Results                                                         | 51 |

|     |        | 3.5.3.2     | Simulation Results                                                        | 53 |

| 3.6 | Single | Layer Tr    | ellis                                                                     | 56 |

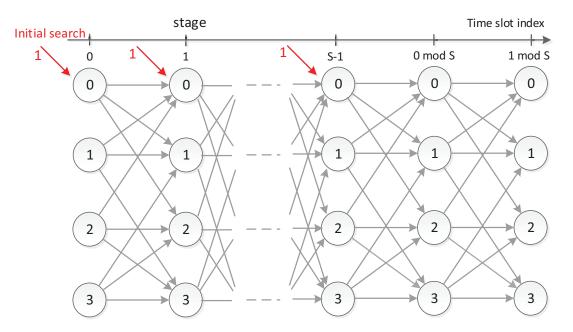

|     | 3.6.1  | Single-la   | yer Trellis Path Search Algorithm                                         | 57 |

|   |     | 3.6.2  | Single-la | yer Trellis Path Search Implementation                                        | 59        |

|---|-----|--------|-----------|-------------------------------------------------------------------------------|-----------|

|   |     | 3.6.3  | Synthesi  | s Results                                                                     | 59        |

|   | 3.7 | Partit | ioned Tre | llis Architecture                                                             | 61        |

|   |     | 3.7.1  | Partition | ned TESSA search algorithm                                                    | 63        |

|   |     | 3.7.2  | NoCM a    | rchitecture                                                                   | 64        |

|   |     |        | 3.7.2.1   | Control signals                                                               | 64        |

|   |     |        | 3.7.2.2   | Control trellis path search in each partition $\ldots \ldots \ldots$          | 65        |

|   |     |        | 3.7.2.3   | Ensuring that the destination is activated only once by one request           | 67        |

|   |     | 3.7.3  | Perform   | ance Evaluation                                                               | 67        |

|   |     |        | 3.7.3.1   | Synthesis Results                                                             | 67        |

|   |     |        | 3.7.3.2   | Simulation Results                                                            | 68        |

|   |     |        | 3.7.3.3   | Suggestion on how to partition the system                                     | 70        |

|   | 3.8 | Summ   | ary       |                                                                               | 72        |

| 4 | C   |        | d Como    | ation Allocation for Combined TDM CDM CC No.Co                                | 75        |

| 4 | 4.1 |        |           | SDM CS                                                                        | <b>75</b> |

|   | 4.1 | 4.1.1  |           | ed TDM and SDM CS                                                             | 75<br>76  |

|   |     | 4.1.1  |           |                                                                               |           |

|   | 4.2 |        |           | ion allocation in combined TDM and SDM CS                                     |           |

|   |     | v      |           |                                                                               |           |

|   | 4.3 |        |           | cator Architecture                                                            | 78<br>70  |

|   |     |        |           | zing The Trellis Graph Structure         Lath Second Algorithm                | 79<br>70  |

|   |     | 4.3.2  |           | Path Search Algorithm        Unidimentional Trailie Dath Second               | 79<br>70  |

|   |     |        | 4.3.2.1   | Unidirectional Trellis Path Search                                            | 79<br>81  |

|   |     | 199    | 4.3.2.2   | Bidirectional Trellis Path Search                                             | 81        |

|   | 4 4 | 4.3.3  |           | Path Search Implementation                                                    | 81        |

|   | 4.4 |        |           |                                                                               | 82        |

|   |     | 4.4.1  |           | s Results                                                                     | 83        |

|   |     | 4.4.2  |           | on Results                                                                    | 84        |

|   |     |        | 4.4.2.1   | Influence of different link partitioning on success rate                      | 85        |

|   |     |        | 4.4.2.2   | Evaluation of different link partitioning under certain<br>background traffic | 87        |

|   | 4.5 | Summ   | ary       |                                                                               | 89        |

| <b>5</b> | Router Design |                  |                         |      |  |  |

|----------|---------------|------------------|-------------------------|------|--|--|

|          | 5.1           | 5.1 System Model |                         |      |  |  |

|          | 5.2           | Propo            | sed Router Architecture | . 93 |  |  |

|          |               | 5.2.1            | Router architecture     | . 93 |  |  |

|          |               | 5.2.2            | Packet-switching Part   | . 94 |  |  |

|          |               | 5.2.3            | Circuit-switching Part  | . 95 |  |  |

|          | 5.3           | Synthe           | esis Results            | . 96 |  |  |

|          | 5.4           | Summ             | ary                     | . 96 |  |  |

| 6        | Con           | clusio           | ns and Future Work      | 99   |  |  |

| Bi       | bliog         | graphy           |                         | 101  |  |  |

# List of Symbols

| $\mathbf{S}$ | Slot table size                                                 |

|--------------|-----------------------------------------------------------------|

| $\mathbf{T}$ | the total link capacity                                         |

| $\mathbf{t}$ | a specific time slot                                            |

| $\mathbf{R}$ | required bandwidth                                              |

| Н            | route time over single hop                                      |

| m            | the path length from source to destination                      |

| В            | branch metric                                                   |

| a            | the available slots of the branch                               |

| r            | the number of requested slots                                   |

| W            | the weight of the branch                                        |

| Р            | path metric                                                     |

| $S_j$        | the set of states that have transitions to state $j$            |

| 1            | the distance between source and destination                     |

| d            | the number of allowed detours                                   |

| Μ            | the number of routers of the whole network                      |

| Ν            | the side length of the network, hence the network is $N\cdot N$ |

| $T_{eff}$    | the effective time                                              |

| E            | the error rate                                                  |

| С            | the number of sub-channels                                      |

# List of Abbreviations

| ATM      | Asynchronous Transfer Mode                        |

|----------|---------------------------------------------------|

| Ans      | Answer signal                                     |

| Ack      | Acknowledgment                                    |

| AT       | Area.Time product                                 |

| AT/S     | Area.Time/Success Rate measure                    |

| BE       | Best Effort                                       |

| bk       | background traffic                                |

| CS       | Circuit Switching                                 |

| Des      | destination                                       |

| DSS      | Detect-Select-Shift                               |

| DS       | Detect-Select                                     |

| EoP      | End-Of-Packet                                     |

| FB TESSA | Forward-Backtrack TrElliS-Search based Allocation |

| GS       | Guaranteed Services                               |

| HAGAR    | HArdware Graph ARray                              |

| HPU      | Header Parsing Unit                               |

| IP       | Intellectual Property                             |

| Ν        | Node                                              |

| NoC      | Network-on-Chip                                   |

| NoCM     | NoCManager                                        |

| NI       | Network Interface                                 |

| PE       | Processing Element                                |

| RE TESSA | Register-Exchange TrElliS-Search based Allocation |

| R        | Router                                            |

| SDM      | Space-Division-Multiplexing                       |

| SoC      | System on Chip                                    |

| Src      | source                                            |

| TDM      | Time-Division Multiplexing                        |

| TESSA    | TrElliS-Search based Allocation                   |

| 2D       | 2 dimension                                       |

# List of Figures

| 1.1   | Interconnection solutions.                                                                                                                                                                                                                                           | 2   |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.2   | Circuit Switching network. Each flow has its own dedicated point-to-point connection to transfer data. Src: source node, Des: destination node                                                                                                                       | 5   |

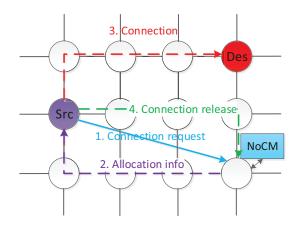

| 1.3   | General operating procedure of Circuit Switching                                                                                                                                                                                                                     | 6   |

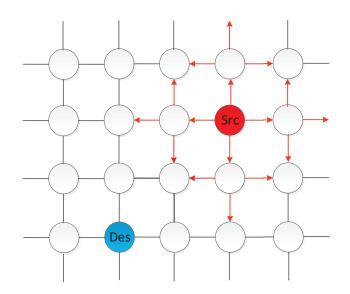

| 2.1   | Src tries to find a contention-free path to the Des. As the detour is allowed, during the path search, at each node there are up to 4 directions to go. Src: source node, Des: destination node                                                                      | 10  |

| 3.1   | The classification tree of TESSA structures                                                                                                                                                                                                                          | 16  |

| 3.2   | Contention-free TDM CS routing                                                                                                                                                                                                                                       | 17  |

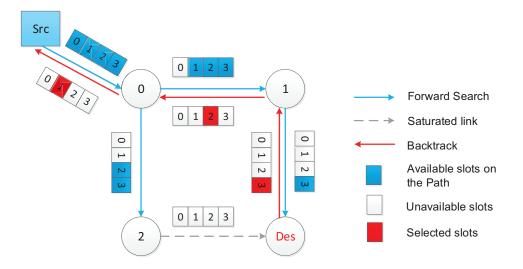

| 3.3   | A connection allocation example for TDM CS. Src: source node, Des: des-<br>tination node                                                                                                                                                                             | 18  |

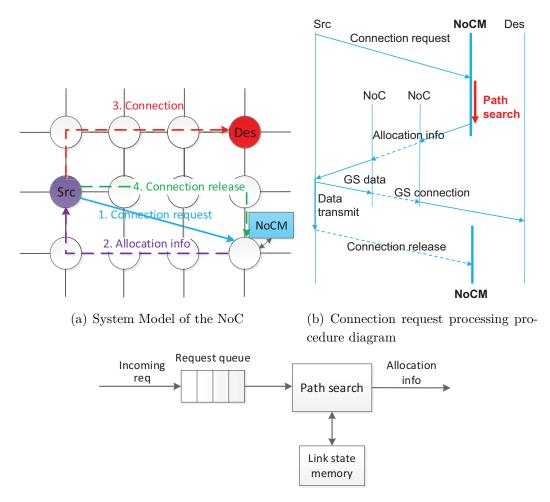

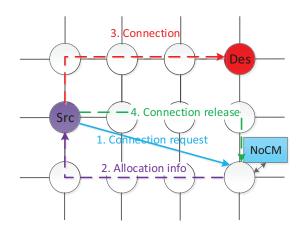

| 3.4   | Proposed System model of the NoCManager based NoC platform. Src: source node, Des: destination node                                                                                                                                                                  | 19  |

| 3.5   | Block diagram of the NoCManager                                                                                                                                                                                                                                      | 20  |

| 3.6   | Network graph represented by trellis graph                                                                                                                                                                                                                           | 22  |

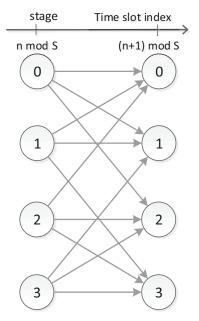

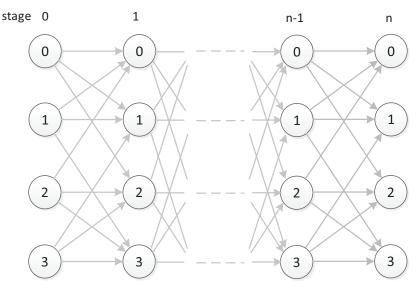

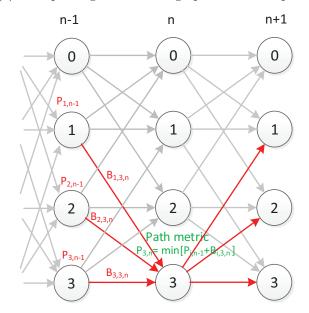

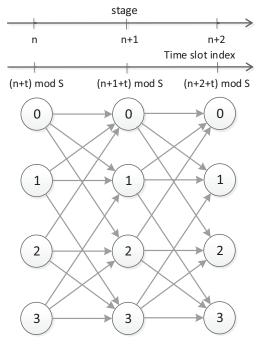

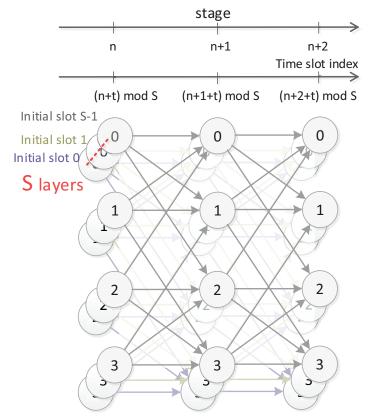

| 3.7   | Multiple stages trellis graph                                                                                                                                                                                                                                        | 23  |

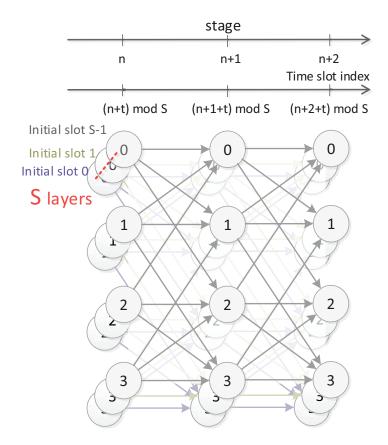

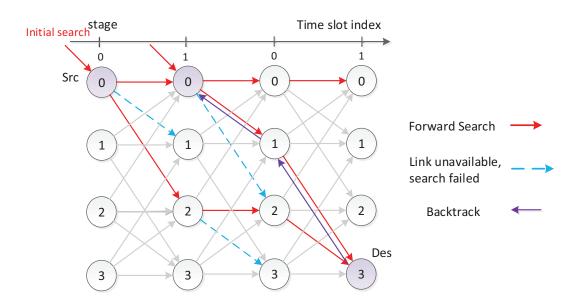

| 3.8   | Each slot at the initial stage has its own layer of trellis                                                                                                                                                                                                          | 26  |

| 3.9   | Each slot searches its own path in parallel                                                                                                                                                                                                                          | 27  |

| 3.10  | Communication bandwidth split over multiple paths. Src: source node, Des: destination node.                                                                                                                                                                          | 27  |

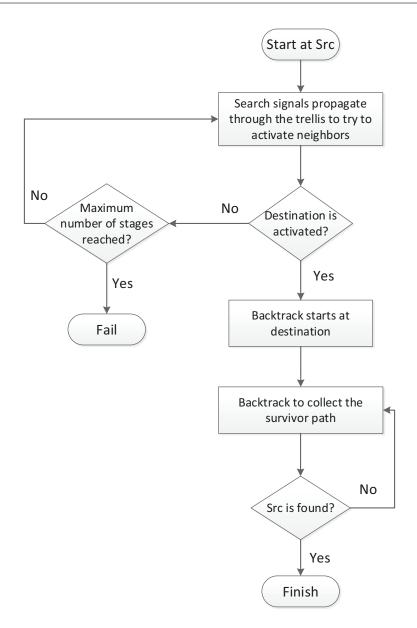

| 3.11  | The flow chart of the path search in trellis                                                                                                                                                                                                                         | 28  |

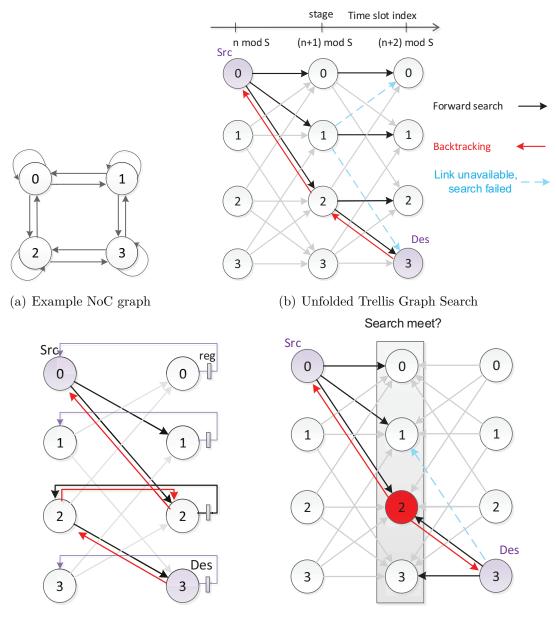

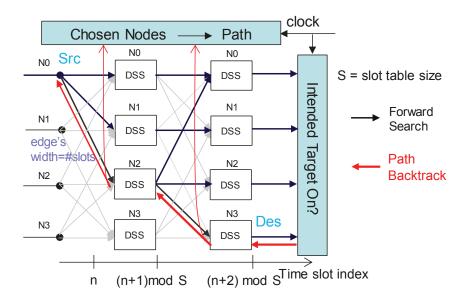

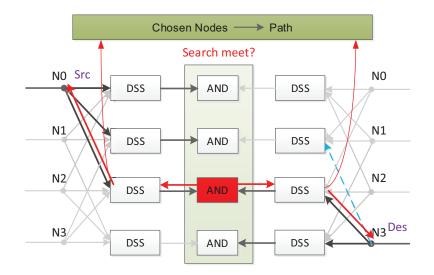

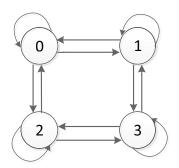

| 3.12  | a)2x2 2D-mesh example NoC; b)schematic structure of the unfolded trellis<br>Search for the example NoC; c)schematic structure of the folded trellis<br>Search; d)schematic structure of the bidirectional trellis Search. Src: source<br>node, Des: destination node | 30  |

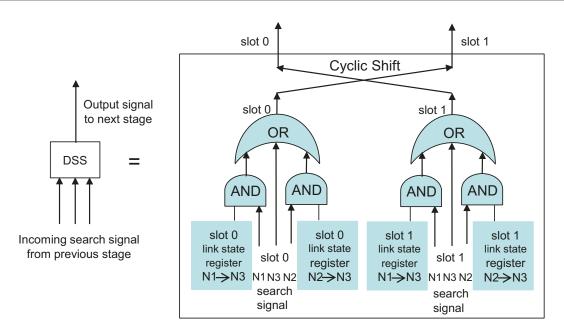

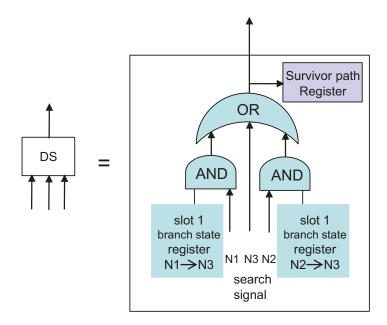

| 3 1 3 | Implementation details of an example DSS unit of node 3                                                                                                                                                                                                              | 30  |

| 3.13  | Implementation details of an example DSS unit of node 3                                                                                                                                                                                                              | -32 |

| 3.14 | Implementation schematic of the unfolded trellis for the example NoC                                                                              | 33 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.15 | Implementation schematic of the bidirectional trellis for the example NoC .                                                                       | 33 |

| 3.16 | Implementation schematic of the folded trellis for the example NoC $\ . \ . \ .$                                                                  | 34 |

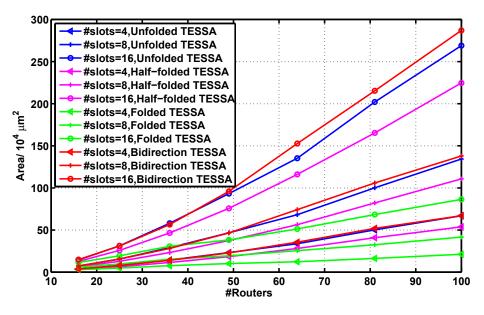

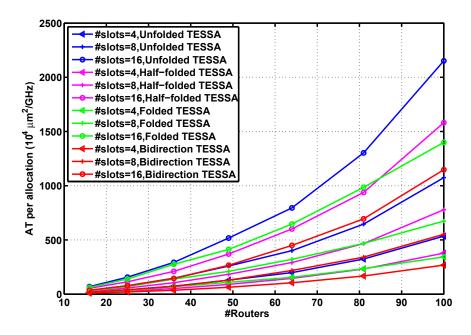

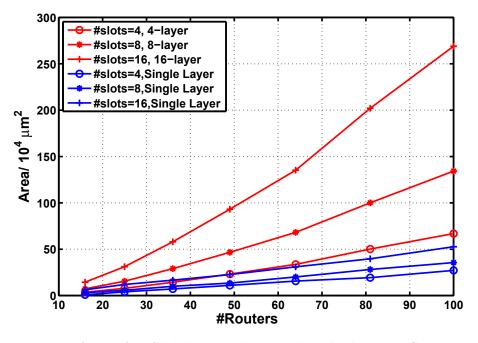

| 3.17 | Area of different TESSA in different size NoC with different slot table size                                                                      | 36 |

| 3.18 | Average AT complexity per allocation of different TESSA in different size<br>NoC with different slot table size                                   | 37 |

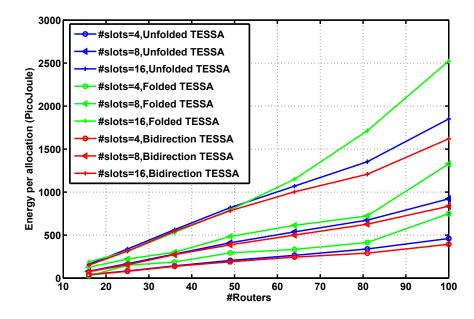

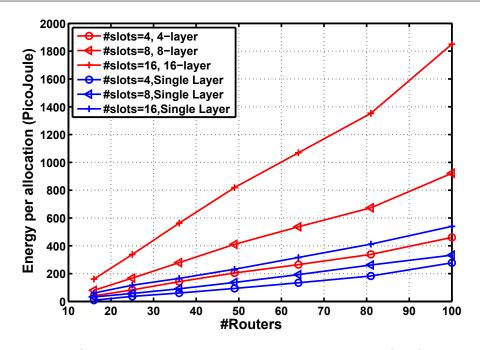

| 3.19 | Average Energy consumption per allocation of different TESSA in different size NoC with different slot table size                                 | 37 |

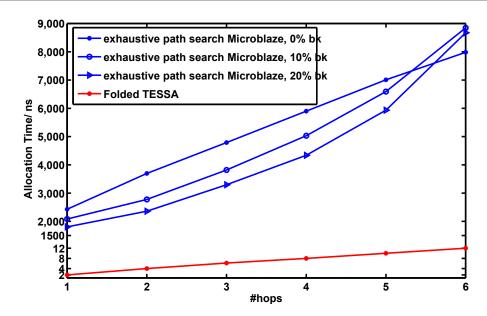

| 3.20 | Allocation speed compared to Microblaze software-based approach[SNG12] with different background in 4x4 NoC with slot table size of 16            | 39 |

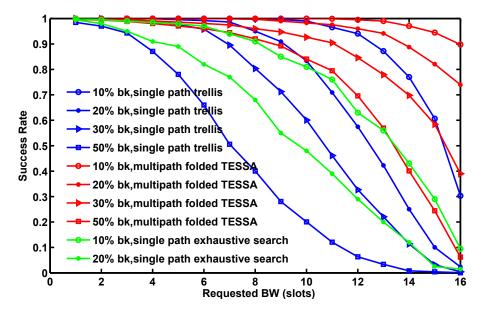

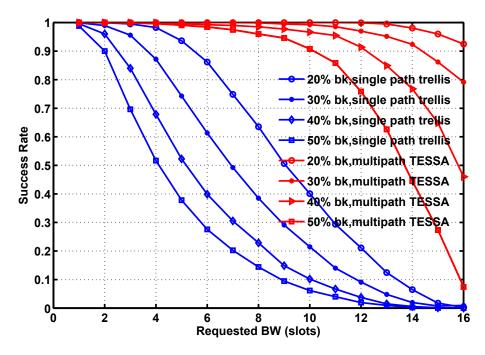

| 3.21 | Success Rate compared to single path solutions in 4x4 NoC with different background traffic with Slot Table Size of 16                            | 40 |

| 3.22 | Success Rate compared to single path approach in 8x8 NoC with different background traffic with Slot Table Size of 16                             | 41 |

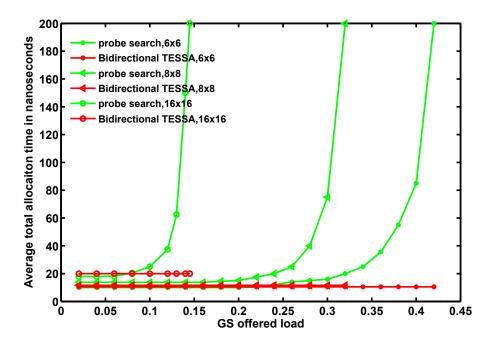

| 3.23 | Allocation speed of bidirectional TESSA compared to probe search in different networks with different GS offered load with Slot Table Size of 16. | 42 |

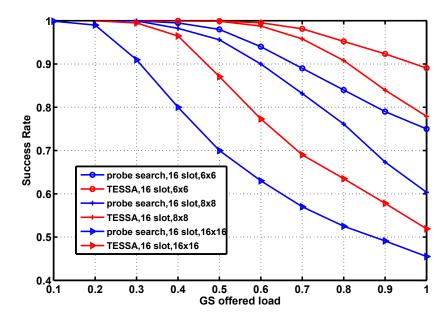

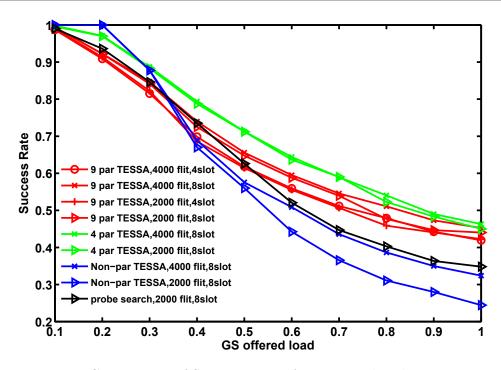

| 3.24 | Success Rate of Bidirectional TESSA compared to probe search in different networks. Each connection delivers 200 flits.                           | 43 |

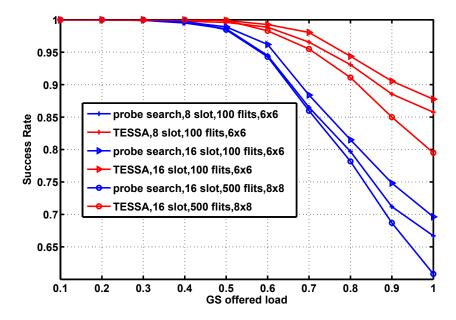

| 3.25 | Success Rate compared to probe search in 6x6 and 8x8 mesh networks with 8 or 16 slot table size. Each connection delivers 100 or 500 flits        | 44 |

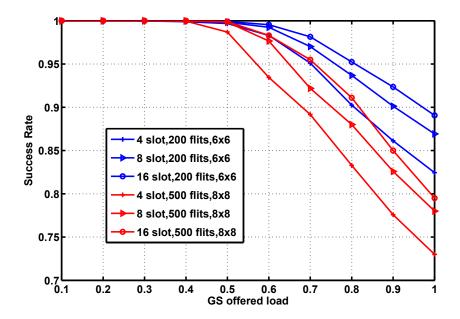

| 3.26 | Success Rate influence of split link into different slots in 6x6 and 8x8 net-<br>works. Each connection delivers 200 or 500 flits                 | 45 |

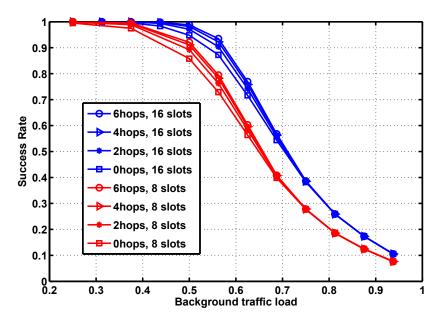

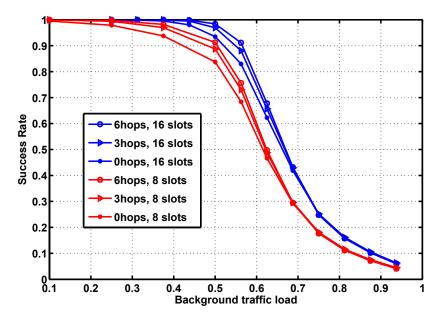

| 3.27 | Success rate under different hops of allowed detours in 6x6 network with 8 or 16 slot table size                                                  | 46 |

| 3.28 | Success rate under different hops of allowed detours in 8x8 network with 8 or 16 slot table size                                                  | 46 |

| 3.29 | 2x2 2D-mesh example NoC.                                                                                                                          | 47 |

| 3.30 | Unfolded RE trellis path search. The survivor path is read directly from destination node without backtrack.                                      | 48 |

| 3.31 | The folded RE trellis search graph of the example NoC                                                                                             | 48 |

| 3.32 | Block diagram of single state.                                                                                                                    | 49 |

| 3.33 | Implementation schematic of the folded RE trellis                                                                                                 | 50 |

| 3.34 | Area of folded FB and folded RE NoCManagers in different size NoCs with different slot table sizes.                                               | 51 |

| 3.35 | Average AT complexity per allocation of RE and FB NoCManagers in different size NoCs with different slot table sizes                                                                                                                                                                                                                                                                                                                                                                           | 52 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

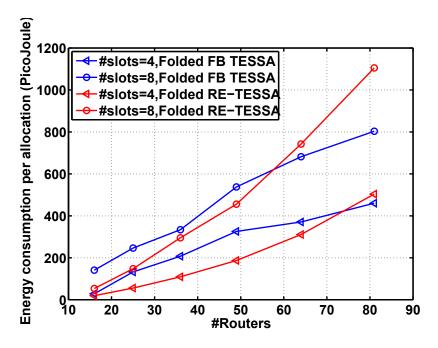

| 3.36 | Average Energy consumption per allocation of RE and FB NoCManagers<br>in different size NoCs with different slot table sizes                                                                                                                                                                                                                                                                                                                                                                   | 52 |

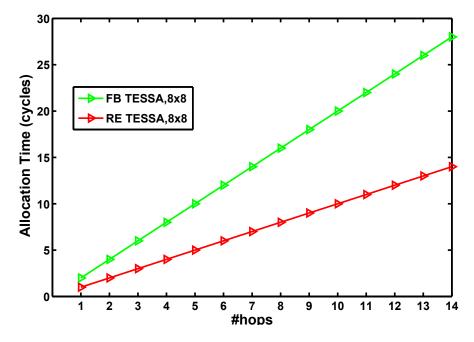

| 3.37 | Allocation speed comparison between RE TESSA and FB TESSA                                                                                                                                                                                                                                                                                                                                                                                                                                      | 53 |

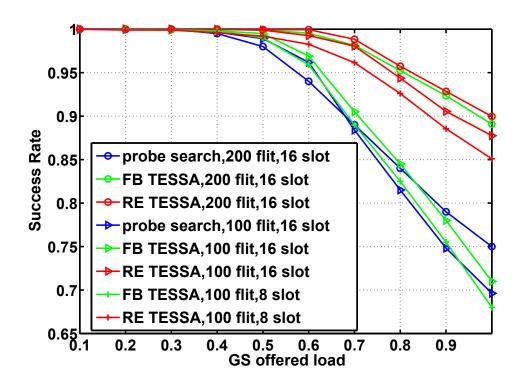

| 3.38 | Success Rate compared to FB TESSA and probe search in 6x6 network with Slot Table Size of 16 and 8. Each connection delivers 100 or 200 flits.                                                                                                                                                                                                                                                                                                                                                 | 54 |

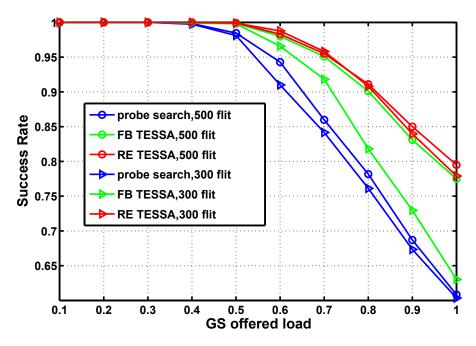

| 3.39 | Success Rate compared to FB TESSA and probe search in 8x8 network with Slot Table Size of 16. Each connection delivers 300 or 500 flits                                                                                                                                                                                                                                                                                                                                                        | 55 |

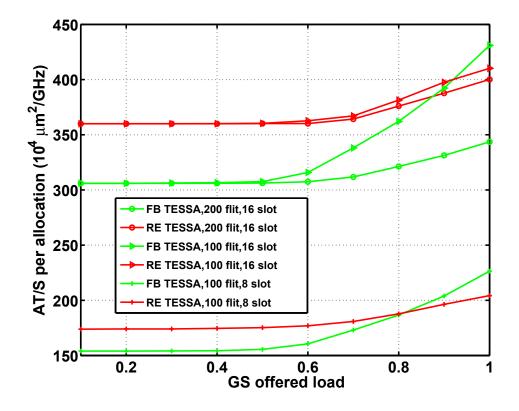

| 3.40 | Average Area. Time/Success Rate (per allocation) in 6x6 network with Slot<br>Table Size of 16 and 8. Each connection delivers 100 or 200 flits                                                                                                                                                                                                                                                                                                                                                 | 56 |

| 3.41 | 2x2 example NoC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 57 |

| 3.42 | Multiple-layer trellis of the example NoC. Each slot at the initial stage has its own layer.                                                                                                                                                                                                                                                                                                                                                                                                   | 57 |

| 3.43 | General schematic structure of the single-layer approach. The slot table size<br>is S, so there are S-1 additional stages. The first S stages are associated<br>with S time slots, which can launch S initial searches simultaneously at the<br>source node                                                                                                                                                                                                                                    | 58 |

| 3 44 | Single-layer path search example.                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 59 |

|      | The implementation schematic of node 3 at stage 1, so the associated time                                                                                                                                                                                                                                                                                                                                                                                                                      | 00 |

| 0.10 | slot is slot 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 60 |

| 3.46 | Area of unfolded single layer and multi-layer NoCManagers in different size<br>NoCs with different slot table sizes.                                                                                                                                                                                                                                                                                                                                                                           | 60 |

| 3.47 | Average Energy consumption per allocation of unfolded single layer and<br>multi-layer NoCManagers in different size NoCs with different slot table                                                                                                                                                                                                                                                                                                                                             |    |

|      | sizes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 61 |

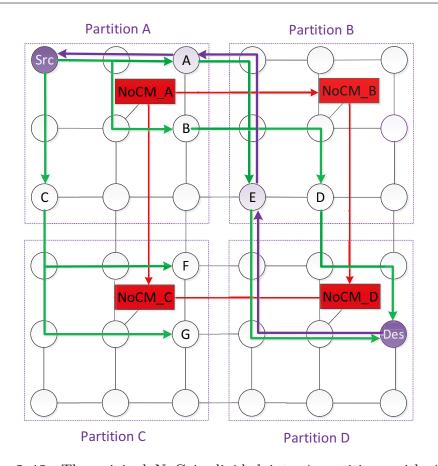

| 3.48 | The original NoC is divided into 4 partitions with 4 dedicated NoCMs.<br>The green arrow: forward search, purple arrow: backtrack, and the red arrow: communication among NoCMs. The border nodes A and E are backtracked as survivor path. The cross-partition search is along $NoCM\_A \rightarrow (NoCM\_B, NoCM\_C) \rightarrow NoCM\_D$ . The path search inside each partition is done as forward-backtrack trellis search, while cross-partition search among NoCMs is as probe search. | 62 |

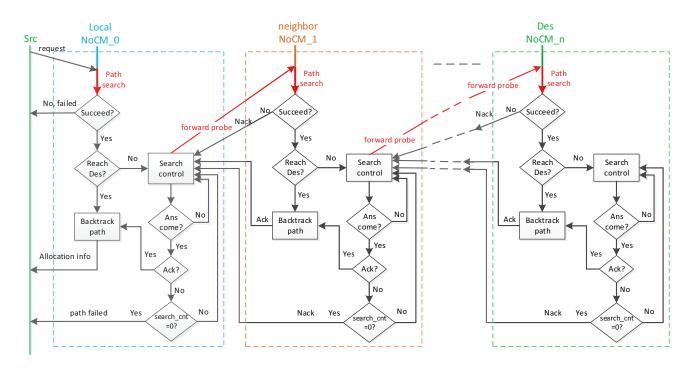

| 3 /0 | The probe search among NoCMs. Each node represents a NoCM.                                                                                                                                                                                                                                                                                                                                                                                                                                     | 64 |

|      | Block diagram of the NoCManager                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65 |

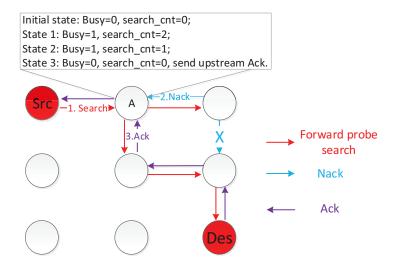

|      | At the beginning, NoCM A is free. At state 1, probe search comes, NoCM                                                                                                                                                                                                                                                                                                                                                                                                                         | 00 |

| 0.01 | A becomes busy. At state 2, Nack comes. At state 3, Ack comes                                                                                                                                                                                                                                                                                                                                                                                                                                  | 66 |

| 3.52       | The search procedure of partitioned TESSA                                                                                                                                                                                            | 66 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

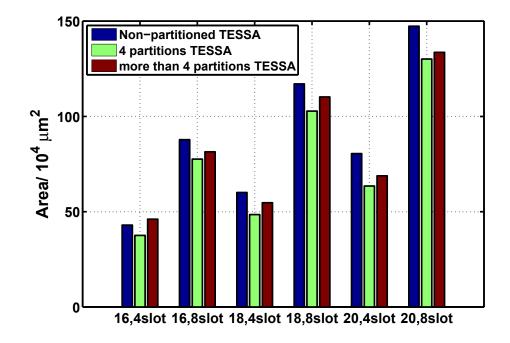

| 3.53       | Total area of non-partitioned and partitioned NoCMs in different size NoC with different slot table size. The x-axis label '16, 4slot' indicates 16x16 mesh with 4 slots.                                                            | 68 |

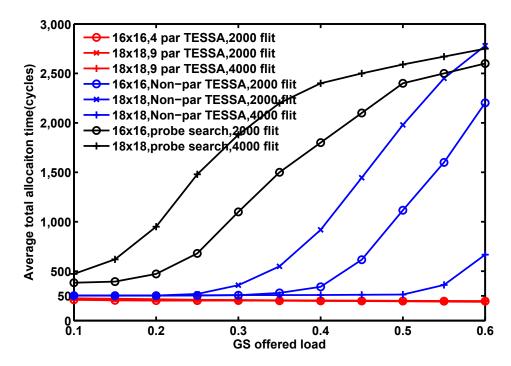

| 3.54       | Comparison of allocation speed of partitioned and non-partitioned TESSA and probe search in different network with Slot Table Size of 8                                                                                              | 69 |

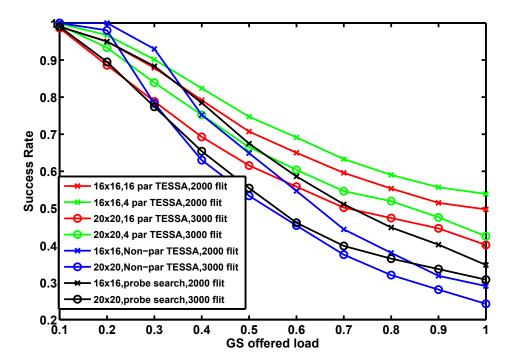

| 3.55       | Comparison of Success Rate of partitioned and non-partitioned TESSA and probe search in 16x16 and 20x20 networks with Slot Table Size of 8. $$ .                                                                                     | 70 |

| 3.56       | Comparison of Success Rate of partitioned and non-partitioned TESSA and probe search in 18x18 network with Slot Table Size of 4 or 8. $\ldots$ .                                                                                     | 71 |

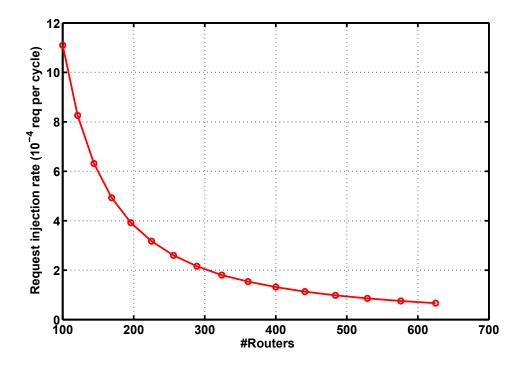

| 3.57       | The boundary of request injection rate under the NoCM's capacity in different NoC sizes.                                                                                                                                             | 72 |

| 4.1        | Connection allocation in TDM CS and SDM CS.                                                                                                                                                                                          | 76 |

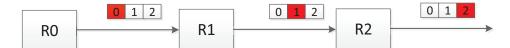

| 4.2        | Combined TDM-SDM routers with each link split into 2 sub-channels and 3 time slots. Along the path, if time slot 1 is reserved at a sub-channel in router R1, slot 2 at any of the two sub-channels can be reserved in R2            | 77 |

| 4.3        | System Model of the NoCManager based NoC platform. Src: source node,<br>Des: destination node.                                                                                                                                       | 78 |

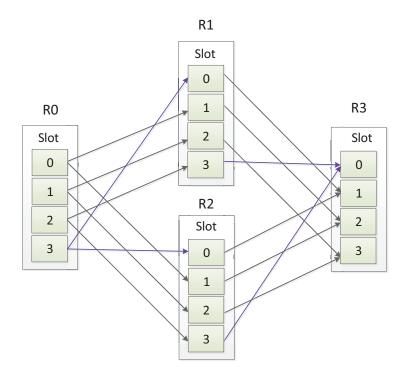

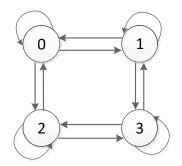

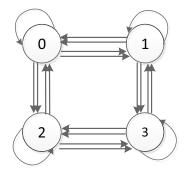

| 4.4        | Example NoC graph. Each link has two sub-channels. A node can reach itself (curve arrow)                                                                                                                                             | 78 |

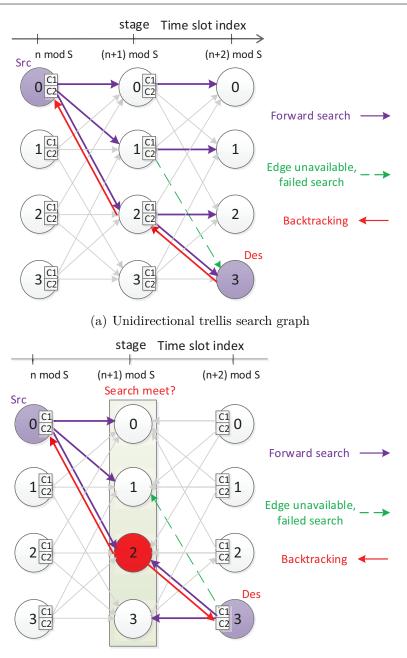

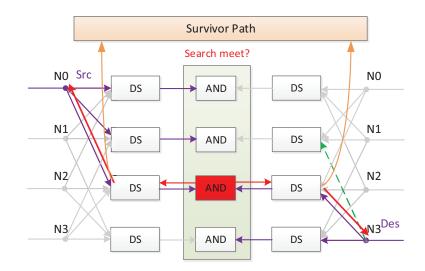

| 4.5        | The example NoC can be represented by trellis. Assume each link has 2 sub-<br>channels (C1 and C2). The green dotted arrow indicates the search of this<br>edge failed because it is not available at the moment (already occupied). |    |

| 16         | Src: source node, Des: destination node                                                                                                                                                                                              |    |

| 4.6<br>4.7 | Implementation schematic of the bidirectional trends graph                                                                                                                                                                           | 81 |

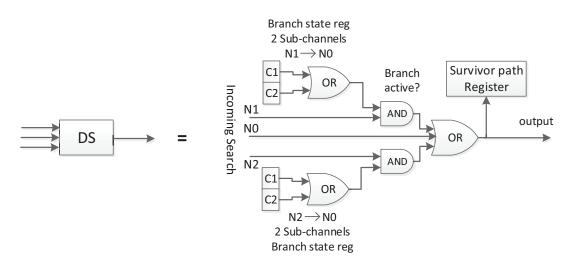

| 1.1        | node 0                                                                                                                                                                                                                               | 82 |

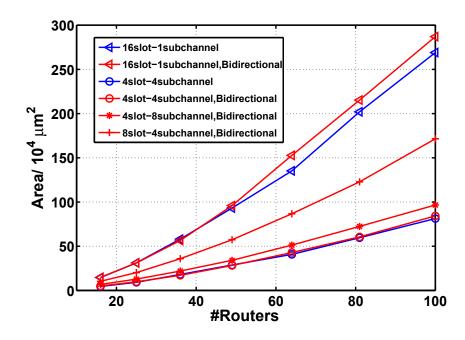

| 4.8        | Area of (unidirectional) TESSA and Bidirectional TESSA NoCManagers with different link partitioning for different NoC sizes                                                                                                          | 83 |

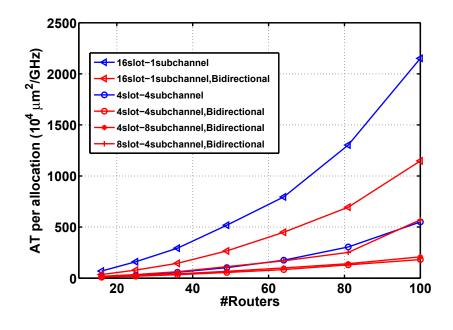

| 4.9        | Average AT complexity per allocation of two different NoCManagers with different link partitioning for different NoC sizes                                                                                                           | 84 |

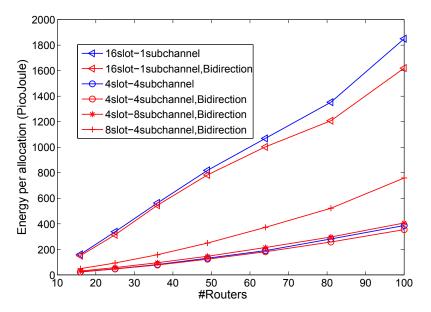

| 4.10       | Average energy consumption per allocation of two different NoCManagers with different link partitioning for different NoC sizes                                                                                                      | 84 |

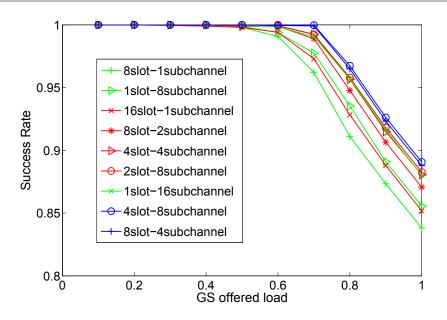

| 4.11       | Influence of different link partitioning on success rate in $6x6$ mesh                                                                                                                                                               | 86 |

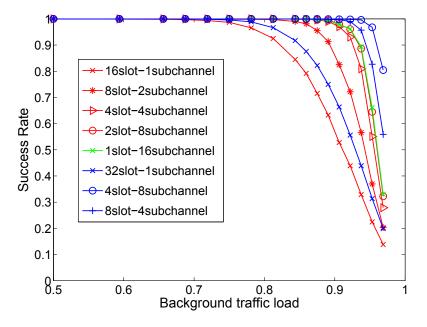

| 4.12       | Influence of different link partitioning on success rate under background traffic.                                                                                                                                                   | 86 |

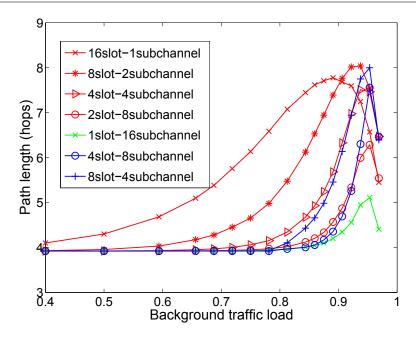

| 4.13 | Influence of different link partitioning on average path length under back-<br>ground traffic                                                                                                                           | 88 |

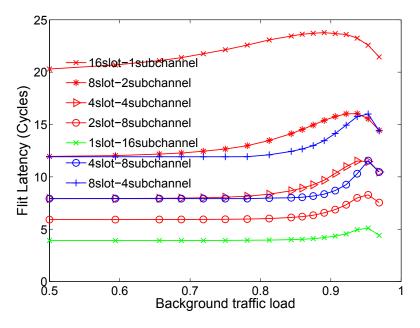

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.14 | Influence of different link partitioning on average delivery latency under background traffic.                                                                                                                          | 88 |

| 5.1  | System Model of the NoCManager based NoC platform                                                                                                                                                                       | 92 |

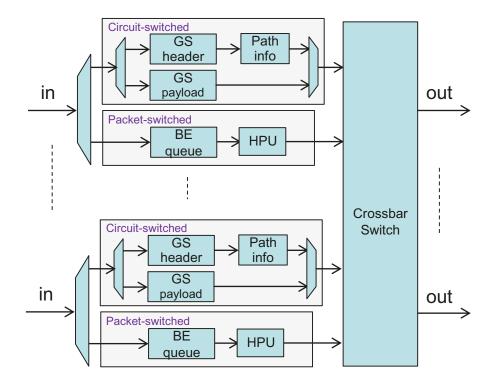

| 5.2  | The proposed router architecture                                                                                                                                                                                        | 93 |

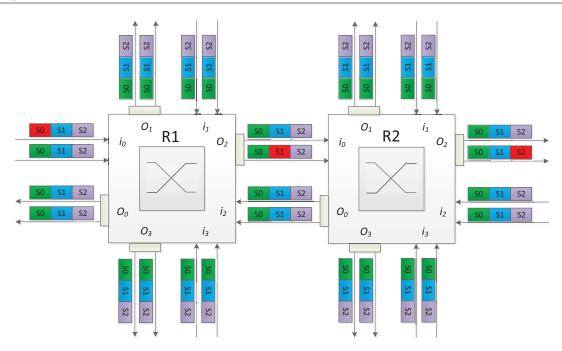

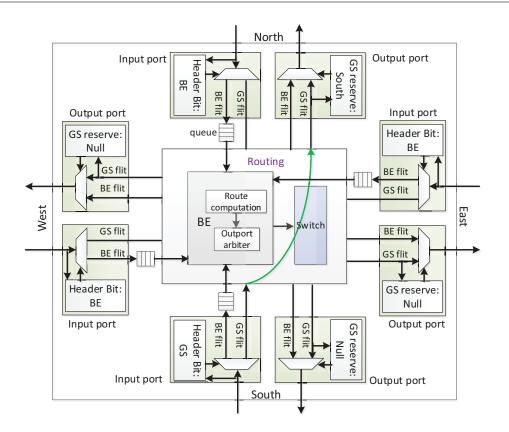

| 5.3  | Block diagram of the proposed combined BE-GS router with 4 ports. As<br>an example a GS connection (green arrow) from port south to north is<br>established and the GS flits from south to north are directly forwarded | 94 |

| 5.4  | GS flits.                                                                                                                                                                                                               | 94 |

# List of Tables

| 1.1 | The interconnections advantages and disadvantages                  | 3  |

|-----|--------------------------------------------------------------------|----|

| 1.2 | Comparison between Circuit Switching vs. Packet Switching networks | 5  |

| 3.1 | The comparison of different TESSA structures.                      | 38 |

| 3.2 | The usage of control signals                                       | 64 |

| 5.1 | The control signals of GS phit                                     | 95 |

| 5.2 | Resource Consumption of the Proposed Router with 65 nm technology  | 96 |

XXII

## Chapter 1

## Introduction

Due to the advances of semiconductor technology, the transistor size is decreasing while the die size is increasing. As a result, nowadays, a single chip can contain billions of transistors, so more devices and Intellectual Property (IP) cores can be integrated on a single chip. Consequently, the on-chip interconnection (communication) problem, i.e. how to connect the on-chip modules, is becoming a critical issue for complex System on Chip (SoC) design [WL03].

#### **1.1** Overview of on-chip interconnection solutions

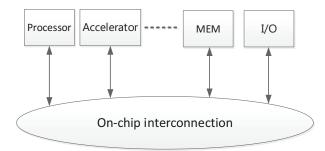

The on-chip interconnection is used to connect the modules of the on-chip system, to connect e.g. processors, memories, and peripherals. A typical interconnection diagram is illustrated in Fig. 1.1a.

The **bus** is a widely used interconnect, which is simple and cost effective with hardware complexity O(n) and performance scalable typically for a small number of nodes. All the modules on a chip are connected to a shared bus, while only one master module can access it at a time, as depicted in Fig. 1.1b. The data sent from a module is broadcasted to all the other modules. This induces a contention among competing modules resolved through arbitration, to determine who gains access to the bus at a time. The problem of the bus-based system is the lack of scalability. When the number of the connected modules increases, the average bandwidth per module decreases while the contention rate increases, which reduces the operating frequency.

In order to enable simultaneous communications among multiple modules, the **crossbar switch** is proposed, as depicted in Fig. 1.1c. In crossbar, every module is connected to every other modules. The communication bandwidth is enhanced since multiple communications can be supported simultaneously as long as they occur between different modules. Though crossbar can provide low latency and high throughput, it is expensive.

(a) On-chip interconnection diagram

Figure 1.1: Interconnection solutions.

The hardware complexity of crossbar scales with  $O(n^2)$ , where n is the number of the connected modules. Hence, it is good for small number of modules, but too expensive for large system.

In order to address the aforementioned problems, the advanced interconnection solution, **Network-On-Chips (NoC)** is proposed [DT04, BDM02, GHKM11]. The NoC borrows

|                   | Bus  | Crossbar | NoC     |

|-------------------|------|----------|---------|

| scaling           | 10   | 10-100   | 10 +    |

| wire cost         | low  | high     | average |

| logic/buff cost   | low  | high     | average |

| throughput        | low  | highest  | high    |

| energy efficiency | poor | average  | good    |

| energy efficiency | poor | average  | good    |

Table 1.1: The interconnections advantages and disadvantages

ideas from large-scale communication networks, e.g. Internet or Asynchronous Transfer Mode (ATM) network, to create a scalable on-chip communication network. The Processing Element (PE), or module, is connected to a router via Network Interface (NI). Data transfer in point-to-point communication is controlled and relayed by routers. Hence, the long wires between a source node and a destination are avoided, and the data packet may take multiple hops through the network to reach the destination. The popular NoC topology, a mesh, is depicted in Fig. 1.1d. Since each router just needs to connect the adjacent routers, the wire length is short. Concurrent communications is possible as long as they are delivered over different links. Since a mesh has a regular structure and equal-length links, it is easy to layout. Moreover, it has high path diversity so that there are many alternate paths possible from one node to another. Therefore, the NoC can provide large communication bandwidth, low wiring complexity and good scalability. The advantages and disadvantages of the aforementioned interconnections is shown in table 1.1 [Ste12].

#### 1.2 Network on Chip

There is some terminology for NoC, which is:

- 1. **Router** connects fixed number of input links to fixed number of output links, which forwards the incoming packet to the specific output according to predefined routing policy.

- 2. Network Interface (NI) connects the PE to network and decouples communication.

- 3. Link is a bundle of wires that carries communication/data signals between two adjacent routers.

- 4. Channel is a single logical connection between two adjacent routers.

- 5. Network node is a logical abstraction of a router within a network.

- 6. Traffic flow is a sequence of packets from a source node to a destination.

- 7. Message is the transfer entity from the network's clients to the network.

- 8. **Packet**: A single message can be split into one or more packets, which represents transport element of network.

- 9. Flit i.e. FLow control unIT, is the elementary data unit of the flow control mechanism. Each packet is split into one or more fixed-size flits.

- 10. Phit is the physical digit, which is the data transmitted per link per cycle.

The basic characteristics of NoC are:

- 1. **Topology**: The network topology is the pattern in which network nodes are connected via links, i.e. the arrangement of these nodes and links. A good topology should meet the bandwidth and throughput requirements of the system at a minimum cost. The path diversity of a topology also determines the performance under adversarial traffic and fault tolerance. The most popular network topology is the mesh, which has regular structure and equal-length links, so it is easy to layout, as shown in Fig. 1.1d.

- 2. Routing is the process of selecting a path for traffic from source node to destination node. Once a topology is selected, the routing algorithm determines the system throughput. A good routing algorithm should be deadlock-free, can balance traffic load, and typically keep the path lengths as short as possible.

- 3. Flow control dictates which messages get access to particular network resources over time. It manages the allocation of channel bandwidth and buffer capacity to packets along the path from source to destination. A good flow control can minimize packets delivery latency, and can avoid resource conflicts and buffer overflow.

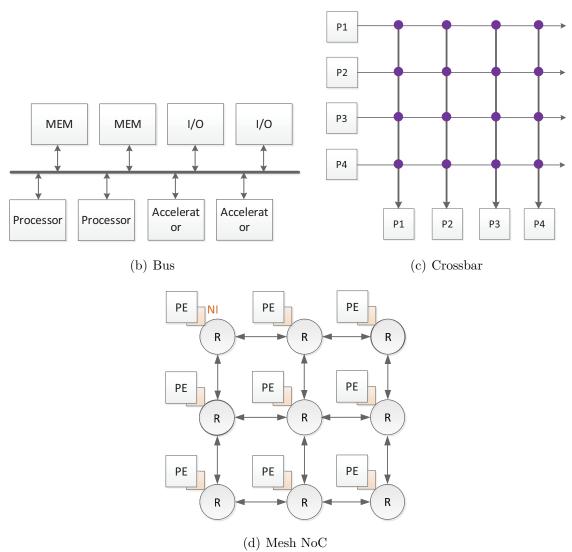

- 4. Switching model: Generally speaking, the NoC can be grouped into two categories: packet switching and circuit switching networks. In packet switching networks, the communication resources, e.g. link and buffers, are allocated at each node for each packet. When a packet reaches a node, the resources are allocated. When the packet leaves, the resources are released. In contrast, circuit switching networks allocate exclusively channels to form a circuit (connection) from source node to destination, and then the data packets are delivered over this connection, as depicted in Fig. 1.2. The comparison between Circuit Switching and Packet Switching networks is listed in table 1.2.

- 5. Service class: The traffic can be divided into two broad categories: guaranteed service classes and best efforts (BE) classes. The guaranteed service classes provide some minimum level of performance, such as a guaranteed loss rate, throughput, latency, and jitter. In contrast, the network provides no hard guarantees for best-effort classes.

| Circuit Switching            | Packet Switching                                                                                                                       |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| Connection oriented          | Connectionless                                                                                                                         |  |

| Yes                          | No                                                                                                                                     |  |

| Resources are allocated      |                                                                                                                                        |  |

| before data transfer.        | Not required.                                                                                                                          |  |

| High                         | Unreliable                                                                                                                             |  |

| Fixed                        | Dynamic                                                                                                                                |  |

| Connection Allocation delay. | Packet transmission delay.                                                                                                             |  |

| Low                          | Unpredictable                                                                                                                          |  |

| Inflexible                   | Flexible                                                                                                                               |  |

|                              | Connection oriented<br>Yes<br>Resources are allocated<br>before data transfer.<br>High<br>Fixed<br>Connection Allocation delay.<br>Low |  |

Table 1.2: Comparison between Circuit Switching vs. Packet Switching networks

Figure 1.2: Circuit Switching network. Each flow has its own dedicated pointto-point connection to transfer data. Src: source node, Des: destination node.

#### 1.3 Guaranteed Service in NoCs

In modern complex SoCs, many applications have specific requirements of the performance, such as a minimum throughput (for real-time streaming data), bounded latency (for interrupts, process synchronization, etc). Therefore, providing Guaranteed Services (GSs), e.g. to guarantee bounded latency, minimum bandwidth and low (or no) data loss, is crucial for predictable SoC architectures[SMG14]. In general, there are two popular approaches to provide GS in NoCs: i) the connection-less approach employing priority scheduling in packet switching networks and ii) the connection-oriented method based on Circuit Switching (CS) network. Priority scheduling assigns higher priority to the latency-sensitive flows, as in e.g. QNoC[BCGK04], artNoC[SLB07] and Quota-setting NoC[CTSM13]. This approach however suffers from reduced determinism and predictability due to the contention of multiple flows on shared resources. In contrast, the CS allocates exclusive channels to form a circuit (connection) to the particular flow, so it can provide hard GS, e.g. used in MANGO[BS05]. After the connection is established, the requested

Figure 1.3: General operating procedure of Circuit Switching.

bandwidth (link capacity) and bounded/constant end-to-end latency are guaranteed. In order to achieve hard GS, in this thesis, we focus on CS approach only.

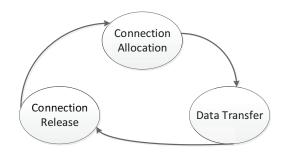

#### 1.3.1 Circuit Switching NoCs

The general operating procedure of CS comprises three phases: connection allocation (setup), data transfer and connection release, as depicted in Fig. 1.3. In CS, when a source node wants to send data to a destination, a connection between the source node and destination should be allocated first. Thereafter, the data packets are delivered over this connection. When the data transfer is finished, the connection will be released.

In CS, since the resource is exclusively occupied during the entire lifetime of a connection, it may lead to inefficiencies and in-flexibilities for the system due to the blocking of other traffic flows. Hence, there are two extensions to share the resource (links) among multiple flows: 1) Time-Division Multiplexing (TDM) CS and 2) Space-Division-Multiplexing (SDM) CS.

In TDM CS, the link capacity is split into multiple time slots, and the link is allocated exclusively to a flow only in specific time slots, while the other time slots can be used by other flows, used in e.g. Nostrum[MNTJ04], AEthereal[GDR05, GH10], parallel probe NoC[LJL14b].

In SDM CS[LJL15, EJ13, LMV<sup>+</sup>08, RRRM08], the link wires are physically split into subsets (sub-channels), and only subset of the link wires is exclusively allocated to a given connection, while the remaining wires of the link can be used by other flows.

#### 1.4 Scope and Outline of this Work

CS is frequently adopted for providing GSs in NoCs. In order to share the resource (links), two extensions have been proposed: TDM CS and SDM CS. Since the data can be transferred only after the connection is allocated, the connection allocation is critical to CS NoCs. In this thesis, we focus on the connection allocation problem, which has to i) allocate a contention-free path between source-destination pairs and ii) allocate appropriate portions of link bandwidth (appropriate number of time slots and subsets) along the path.

The dissertation is structured as follows.

- In Chapter 2, we first explain what is the problem of connection allocation in CS NoCs, and then present the overview of related work. At the end, we present the scheme of our allocation approach which is a dedicated allocator (i.e. NoCManager) based centralized allocation technique.

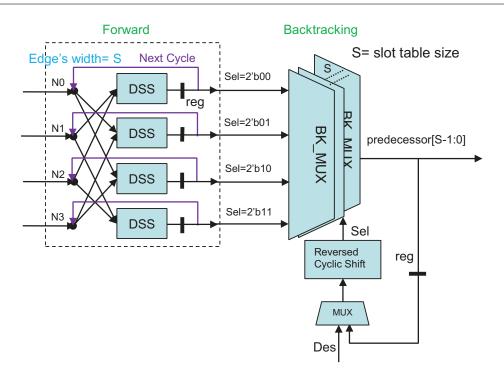

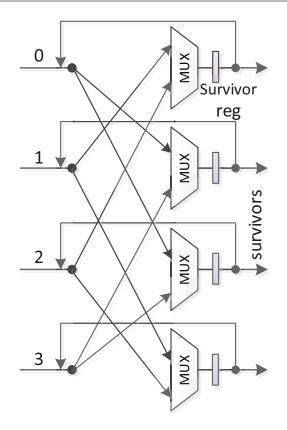

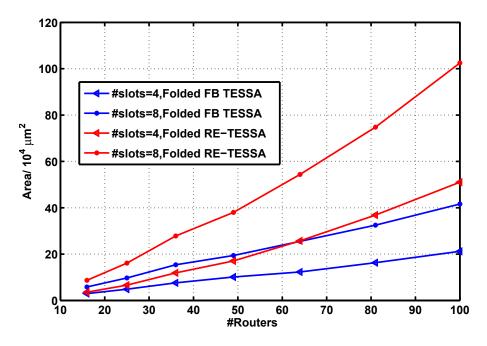

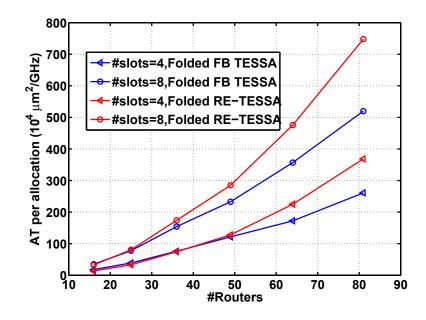

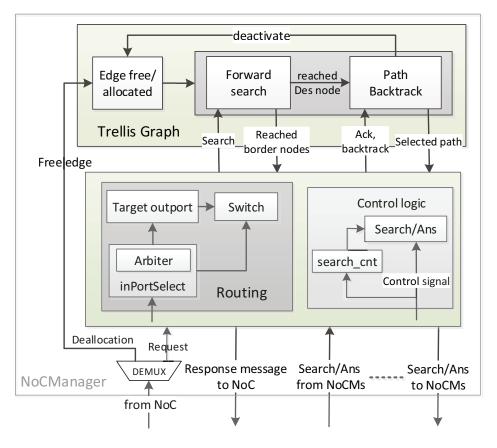

- Chapter 3 starts by describing the problem of the TDM CS connection allocation, and then presents the architecture of the dedicated allocation unit, NoC-Manager, which employs the dynamic programming to solve the connection allocation problem as a trellis path search algorithm, which can solve the shortest path search problem efficiently. The trellis graph consists of two categories: Forward-Backtrack trellis[CMF16a, CMF16b] and Register-Exchange trellis[CMF17d]. In Forward-Backtrack trellis, the path search is divided into two steps: forward search to try to reach the destination, and backtrack from destination to select the survivor path. However, in Register-Exchange trellis, we only need to do forward search and the backtrack step can be omitted. As soon as the forward search is finished, we can get the survivor path from the destination node immediately. And thereby compared to Forward-Backtrack approach, the search time is halved. Moreover, in both approaches, the trellis search can be further grouped into three categories, unfolded structure[CMF16a], folded structure[CMF16b] and bidirectional structure. The unfolded structure constructs the trellis graph as multiple stages to represent multi-hop traversal through the network, but the folded structure only implements one stage and reuses this stage to do path search. The folded structure is more efficient for area but the cost for clock cycles is increased to complete single allocation, as one cycle for traversing single stage. The bidirectional structure starts the search at two sides, source node and target node simultaneously, so compared to the traditional search that starts only at the source node, the path search time is halved. The synthesis results of area, Area. Time product and energy consumption per allocation of different trellis structures are presented and compared. The allocation time and allocation success rate of trellis search are compared to previous centralized and distributed allocation approaches. Finally, in order to address the scalability issue, the partitioning structure [CMF17a] that divides the large system into multiple partitions with multiple local managers is proposed.

- Chapter 4 starts by giving introduction of the SDM CS. In SDM CS, since there is no time slot scheduling constraint, and any free sub-channel at the next hop can be allocated, it can provide higher path diversity than TDM CS. However, the area cost of SDM switch scales as quadratic with the number of the sub-channels.

Moreover, the number of sub-channels is limited by the number of wires, so it cannot be increased arbitrarily. Hence, we present the combined TDM and SDM CS technique[CMF17c], in which each sub-channel is further split into time slots. The trellis path search based NoCManager is employed for the connection allocation of combined TDM and SDM CS. We also studied the influence of different link partitioning strategies with fixed link wires, i.e. the effect of splitting the link into different number of time slots and sub-channels, on allocation success rate and average path length.

- In Chapter 5, we present the router architecture [CMF17b] that combines the circuitswitching network (for GS communication) and packet-switching network (for BE communication).

- Finally, we draw conclusions and provide some future research directions in Chapter 6.

## Chapter 2

## Connection Allocation in CS NoCs

This section first explains what is the problem of the connection allocation in CS NoCs, and then presents the overview of known methods and approaches (related work). Finally, we introduce the idea of our allocation approach that bases on a centralized dedicated allocator (i.e. NoCManager).

#### 2.1 Connection allocation problem

Some real-time applications have strict time requirements that the data delivery across the NoC must be in time, so it would be preferred to reserve dedicated transfer resources for the communication i.e. perform connection allocation. In CS, the connection allocation has to i) allocate a contention-free path from source node to destination node and ii) allocate appropriate portions of link bandwidth (appropriate number of time slots in TDM CS and subsets in SDM CS) along the path. Assume the total link capacity is T, and the link is split into p portions (number of slots/channels). If an application requires R bandwidth, then  $R \div (\frac{T}{p}) = \left\lceil \frac{R \cdot p}{T} \right\rceil$  slots/channels will be assigned to it. If the path length from source to destination is m hops, and it takes time of H to route over single hop, then the packet delivery latency through NoC will be  $m \cdot H$ .

The connection allocation is critical to circuit switching since the data transfer relies on the allocated connections. If the connection allocation fails, the data transfer cannot be started at all. If we allocate a short path, we can reduce delivery latency, energy consumption and resource utilization.

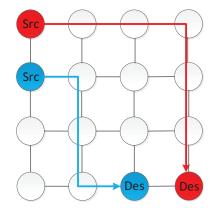

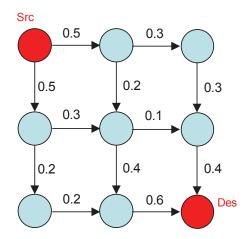

In order to minimize the packet delivery latency and resource cost, usually the goal is to select the shortest path out among all contention-free paths from source to destination. This path search problem has exponential complexity with the path length, and the exact complexity function depends on the network topology, more particularly, on the path diversity and length parameters [Ste12]. For a mesh network, if a detour is allowed, at each hop there are up to 4 directions to go, as shown in Fig. 2.1. Assume l is the distance

Figure 2.1: Src tries to find a contention-free path to the Des. As the detour is allowed, during the path search, at each node there are up to 4 directions to go. Src: source node, Des: destination node.

(i.e. the hop count) between source and destination, d is the number of allowed detours, then the rough complexity function would be  $O(4^{l+d})$ , where 4 is the path diversity and (l+d) is the length components.

#### 2.2 Related work

The allocation techniques can be grouped into two categories: i) static (design-time) allocation and ii) dynamic (run-time) allocation.

The static allocation [LJ08, SBSK12, KS14, SKS13, SG11a, MGK14] is done at the design (compile) time of the system, and usually complicated allocation algorithms are adopted. The communication patterns and connection requirements are assumed already known at design time, and the allocation cannot be changed according to the dynamic applications' requirements during run time. Moreover, since the static allocation cannot use the knowledge of real-time network communication traffics, the resource utilization is usually sub-optimal. Consequently, they are not well suitable for dynamic systems.

In the dynamic connection allocation techniques, the connections are allocated at runtime according to the real-time applications' requirements based on real-time network states. It can be further divided into two categories: i) centralized [SNG12, MMB07, MBD+05, WF08, WF11, SG11b, PMM15, HCG07, HG07] and ii) distributed allocation [LJL14b, GDR05, LJL12, LL12a, LL12b, LL11, Hei14].

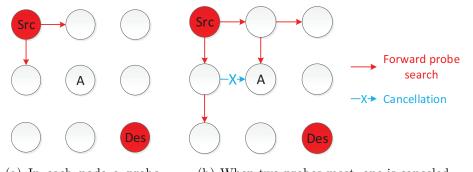

#### 2.2.1 Distributed allocation techniques

In a distributed allocation, typically the source node sends a setup signal for searching a path that traverses through the NoC to try to reach the destination node. The search signal can be delivered over a dedicated setup network or normal NoC based on some routing algorithms. The resource is reserved by the search signal hop by hop. When the search signal reaches the destination, it means the search succeeds and an acknowledgment signal is sent back to the source node. When the source node receives the acknowledgment, the connection is established successfully, and the data transfer starts. The distributed allocation has good scalability, but the problem of distributed allocation is the lack of the global knowledge, e.g. if there are several concurrent requests, the corresponding searches might block each other, especially under heavy traffic load and high connection request rate. When the failure of the allocation occurs, an additional mechanism is needed to tear down the failed partial setup path. Moreover, since the setup search operates at relatively low clock frequency of the network (compared to the high speed central manager), the setup latency is increased. Furthermore, usually the distributed approaches are constrained to search minimal path, which limits the path diversity.

In [LL12a, LL12b, LL11], when a node needs a connection to another node in the network, it sends a best-effort setup packet, which is routed to the destination based on XY deterministic routing algorithm and reserves a channel in each crossed router along the path. When the setup packet reaches its destination, an ACK packet is generated. Upon reception of the ACK, the source then starts transferring data. The problem of this approach is because of the unpredictable contention of best-effort packets, the setup latency is not guaranteed. Moreover, the XY deterministic routing can only search one fixed path between source node and destination node without exploring other possible paths, which seriously limits the success probability of the connection setup.

In parallel probe search [LJL14b, LJL12, Sha15], the source node sends a setup packet for searching path that traverses through the NoC along all minimal paths to try to reach target node. It is a flood-based algorithm which eliminates redundant incoming paths. The probe search in [LJL12] is proposed for basic CS without link sharing. The probe search in [LJL14b] is an extended version for TDM CS with a double time-wheel technique used to make backtrack efficient and to guarantee the setup delay. In this approach, several trials for success might be needed due to the fact that this method investigates single slot at a time. For instance, if the link is split into S time slots, it has to search S times in the worst case to find the path or to determine the path is not available. Furthermore, this approach enables single-slot allocation, but the problem of multi-slot allocation was not addressed in recent work. Moreover, since the search packets have to flood through the NoC to route via relatively complex routers, it would cost more energy than dedicated centralized systems.

Virtual-channel based distributed allocation is proposed in [Hei14], which provides different levels of throughput and latency guarantees for point-to-point connections. The weighted round-robin scheduling is used for arbitration. Different Service Levels for communication are assigned for different applications based on their requirements. End-to-end connections from one node to another are reserved as a chain of virtual channels. This method can provide high throughput, but since each flow requires exclusive virtual channels, the cost of the area is high. Furthermore, the low setup latency is not guaranteed.

#### 2.2.2 Centralized allocation techniques

In a centralized system, a central manager is responsible for connection allocation. Since the central manager has the global knowledge of the system, it could achieve global optimal results. The centralized system typically is based on software solution. The authors in [SNG12] e.g. utilize Microblaze processor while an ARM processor is employed in [SBSK12, MMB07]. Software solutions provide excellent flexibility, however, they might suffer from relatively long allocation time. For instance, single path exhaustive path-search in [SNG12] tries to add links to the current path if the link provides sufficient slots and is closer to destination. If all links of current node fail, it rolls back to the previous node and tries to search another direction. Due to sequential investigation of a single link at a time, and allocation of all required slots on a single path, thousands of processor cycles are required for single allocation.

In order to increase the allocation speed, HArdware Graph ARray (HAGAR) approaches [WF08, WF11] proposed a dedicated hardware connection allocator, which can speedup the allocation by two orders of magnitude against software methods. In HAGAR, the connection allocation problem is solved as a shortest path problem in a graph representation of the NoC. However, HAGAR is employed for basic CS, and does not support link sharing techniques such as TDM and SDM. In paper [PMM15], a centralized hardware unit that uses breadth-first path searching algorithm was proposed with excellent performance. But it is restricted to search of minimal paths, which only considers links that make the distance to the destination shorter, so it cannot detour when there is no available minimal path. Moreover, in both HAGAR and breadth-first search approaches, the path search is divided into two steps:

- Forward search i.e. firstly, the forward search begins at source node that traverses the network to find the path.

- Backtracking i.e. secondly, when destination node is reached, the backtrack starts from destination to collect the associated survivor path parameters.

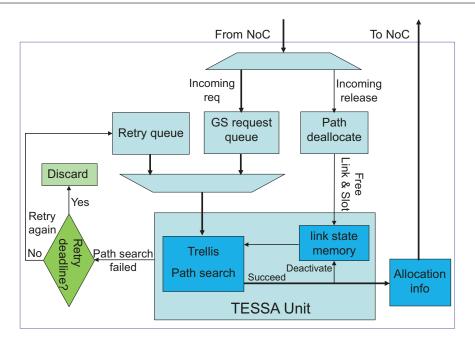

Though the centralized system has the advantages of global knowledge and high performance, as the network grows and the allocation request rate at the central unit increases, the central unit might be the bottleneck due to the drawbacks of centralism in computation and communication. The motivation of this work is to address this problem by a dedicated allocator for connection allocation employing novel trellis-search based Allocation algorithm for TDM and SDM CS NoCs. The Register-Exchange technique is adopted to merge the forward search and backtrack into single step to enhance the allocation speed, and the partitioning structure is proposed to enhance the scalability of centralized system.

#### 2.3 Trellis Search based Allocation approach

In this thesis, we propose a dynamic allocation method using a dedicated centralized hardware unit called 'NoCManager', which solves the problem of connection allocation by employing a trellis-search based shortest path algorithm. We call this as TrElliS Search based Allocation (TESSA) approach. The aforementioned shortest path search problem has exponential complexity with the length of the paths. However, the path search problem can be efficiently solved by the dynamic programming optimization approach that transforms the complex problem into a sequence of simpler problems and solved stage by stage, with linear computation complexity [BHM77, Lou95]. Moreover, the dynamic programming optimized path search problem can be efficiently solved by trellis search approach [LKFF12]. The trellis search can explore all possible paths between two given nodes within a guaranteed low latency, and can ensure the found path is the contentionfree shortest path. The details of trellis search for TDM CS is presented in chapter 3 and the trellis search for SDM CS is presented in chapter 4.

# Chapter 3

# Centralized Connection Allocation for TDM CS NoCs

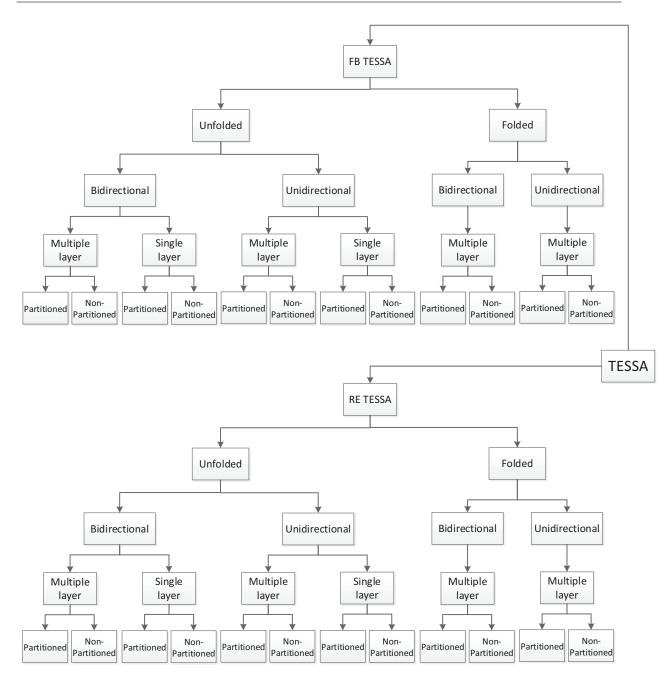

This section presents the trellis path search algorithm for TDM CS connection allocation. In this thesis, we proposed two different approaches, Forward-Backtrack (FB) trellis[CMF16a, CMF16b] and Register-Exchange (RE) trellis[CMF17d]. The Register-Exchange technique saves the entire path information during the forward search, and thus compared to forward-backtrack approaches where a backward phase is required to build the path after the forward search, here the allocation time is reduced by half. Moreover, in both approaches, the trellis graph consists of three categories, unfolded structure[CMF16a], folded structure[CMF16b] and bidirectional structure [CMMF]. The bidirectional unfolded structure can provide high allocation speed while folded structure is more efficient in terms of hardware, which will be suitable for different scenarios depending on different requirements. Furthermore, the single-layer approach is proposed, which only needs to implement one layer of the trellis graph, and all slots can be searched simultaneously in the single layer. Compared to previous approaches in which multiple layers of the trellis have to be implemented, the consumption of hardware resource is reduced dramatically. Finally, the partitioning structure [CMF17a] is proposed to address the scalability issue. The different categories of TESSA structures are shown in Fig. 3.1.

# 3.1 Introduction of TDM CS

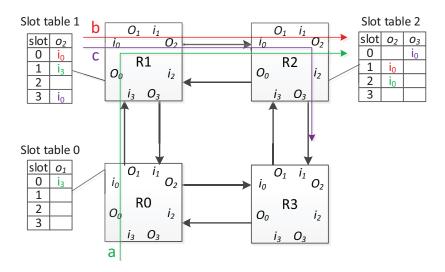

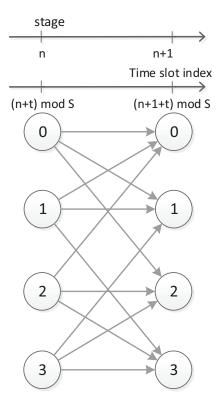

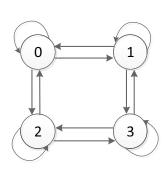

In TDM CS NoCs [YZSZ14], the link capacity is split into multiple time slots to be shared by multiple flows. The allocation information is stored in a slot allocation table of particular router with one table for each shared resource (a link). The allocation tables are synchronized such that a flow with slot t allocated at a specific router, gets slot  $(t + 1) \mod S$  at the next hop at neighbor router, where S is the number of slots in the slot table [GEEK11]. Fig. 3.2 illustrates TDM routing with a router network and

Figure 3.1: The classification tree of TESSA structures.