# TECHNISCHE UNIVERSITÄT DRESDEN FAKULTÄT INFORMATIK

INSTITUT FÜR TECHNISCHE INFORMATIK PROFESSUR FÜR RECHNERARCHITEKTUR

# Routing on the Channel Dependency Graph: A New Approach to Deadlock-Free, Destination-Based, High-Performance Routing for Lossless Interconnection Networks

Dissertation zur Erlangung des akademischen Grades

# Doktor rerum naturalium (Dr. rer. nat.)

vorgelegt von

Name: Domke Vorname: Jens

geboren am: 12.09.1984 in: Bad Muskau

Tag der Einreichung: 30.03.2017 Tag der Verteidigung: 16.06.2017

Gutachter: Prof. Dr. rer. nat. Wolfgang E. Nagel, TU Dresden, Germany

Professor Tor Skeie, PhD, University of Oslo, Norway

Multicast loops are bad since the same multicast packet will go around and around, inevitably creating a black hole that will destroy the Earth in a fiery conflagration.

— OpenSM Source Code

## **Abstract**

In the pursuit for ever-increasing compute power, and with Moore's law slowly coming to an end, high-performance computing started to scale-out to larger systems. Alongside the increasing system size, the interconnection network is growing to accommodate and connect tens of thousands of compute nodes. These networks have a large influence on total cost, application performance, energy consumption, and overall system efficiency of the supercomputer. Unfortunately, state-of-the-art routing algorithms, which define the packet paths through the network, do not utilize this important resource efficiently. Topology-aware routing algorithms become increasingly inapplicable, due to irregular topologies, which either are irregular by design, or most often a result of hardware failures. Exchanging faulty network components potentially requires whole system downtime further increasing the cost of the failure. This management approach becomes more and more impractical due to the scale of today's networks and the accompanying steady decrease of the mean time between failures. Alternative methods of operating and maintaining these high-performance interconnects, both in terms of hardware- and software-management, are necessary to mitigate negative effects experienced by scientific applications executed on the supercomputer. However, existing topology-agnostic routing algorithms either suffer from poor load balancing or are not bounded in the number of virtual channels needed to resolve deadlocks in the routing tables.

Using the fail-in-place strategy, a well-established method for storage systems to repair only critical component failures, is a feasible solution for current and future HPC interconnects as well as other large-scale installations such as data center networks. Although, an appropriate combination of topology and routing algorithm is required to minimize the throughput degradation for the entire system. This thesis contributes a network simulation toolchain to facilitate the process of finding a suitable combination, either during system design or while it is in operation. On top of this foundation, a key contribution is a novel scheduling-aware routing, which reduces fault-induced throughput degradation while improving overall network utilization. The scheduling-aware routing performs frequent property preserving routing updates to optimize the path balancing for simultaneously running batch jobs. The increased deployment of lossless interconnection networks, in conjunction with fail-in-place modes of operation and topology-agnostic, scheduling-aware routing algorithms, necessitates new solutions to solve the routing-deadlock problem. Therefore, this thesis further advances the state-of-the-art by introducing a novel concept of routing on the channel dependency graph, which allows the design of an universally applicable destination-based routing capable of optimizing the path balancing without exceeding a given number of virtual channels, which are a common hardware limitation. This disruptive innovation enables implicit deadlock-avoidance during path calculation, instead of solving both problems separately as all previous solutions.

# **Contents**

| Li | st of | Figures | 5                                                    | xi   |

|----|-------|---------|------------------------------------------------------|------|

| Li | st of | Tables  |                                                      | xiii |

| Li | st of | Algorit | hms                                                  | χV   |

| Li | st of | Abbrev  | viations and Symbols                                 | xvii |

| 1  | Intr  | oductio | on                                                   | 1    |

|    | 1.1   | Motiva  | ation                                                | . 1  |

|    | 1.2   | Contri  | butions                                              | . 4  |

|    | 1.3   | Thesis  | Gorganization                                        | . 5  |

| 2  | Rela  | ated W  | ork                                                  | 7    |

|    | 2.1   | State-o | of-the-Art for High-Performance Interconnect Designs | . 7  |

|    |       | 2.1.1   | Resiliency of Networks, Topologies, and Routings     | . 7  |

|    |       | 2.1.2   | HPC Routing Strategies and Network Management        | . 8  |

|    |       | 2.1.3   | Simulation Frameworks for Network Analyses           | . 9  |

|    | 2.2   | State-o | of-the-Art for Deadlock-free Routing Approaches      | 10   |

|    |       | 2.2.1   | Topology-aware Routing Algorithms                    | 12   |

|    |       | 2.2.2   | Topology-agnostic Routing Algorithms                 | . 12 |

| 3  | Bac   | kgroun  | d, Assumptions, and Definitions                      | 15   |

|    | 3.1   | Interco | onnection Networks and Routing Algorithms            | 15   |

|    |       | 3.1.1   | Network-related Definitions                          | 15   |

|    |       | 3.1.2   | Routing-related Definitions                          | . 17 |

|    |       | 3.1.3   | Topology and Routing Metrics                         | 19   |

|    | 3.2   | Comm    | non Network Topologies and Production HPC Systems    | 21   |

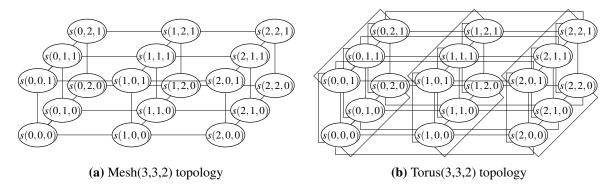

|    |       | 3.2.1   | Meshes and Tori                                      | 22   |

|    |       | 3.2.2   | Fat-Trees and eXtended Generalized Fat-Trees         |      |

|    |       | 3.2.3   | Kautz Graph                                          | 24   |

|    |       | 3.2.4   | Dragonfly Topologies                                 | 24   |

|    |       | 3 2 5   | Random Topologies                                    | 26   |

|   |       | 3.2.6    | Real-world HPC Systems                             | 26 |

|---|-------|----------|----------------------------------------------------|----|

|   | 3.3   | Selecti  | on of Routing Algorithms for HPC                   | 28 |

|   |       | 3.3.1    | MinHop Routing                                     | 28 |

|   |       | 3.3.2    | Single-Source Shortest-Path Routing (SSSP)         | 28 |

|   |       | 3.3.3    | Dimension Order Routing (DOR)                      | 29 |

|   |       | 3.3.4    | Up*/Down* and Down*/Up* Routing                    | 29 |

|   |       | 3.3.5    | Fat-Tree Routing                                   | 29 |

|   |       | 3.3.6    | Layered Shortest Path Routing (LASH)               | 31 |

|   |       | 3.3.7    | Torus-2QoS Routing                                 | 31 |

|   |       | 3.3.8    | Deadlock-Free SSSP Routing (DFSSSP)                | 32 |

| 4 | Fail- | -in-Plac | ce High-Performance Networks                       | 33 |

|   | 4.1   | Failure  | es Analysis for Real HPC Systems                   | 33 |

|   | 4.2   | Buildi   | ng Blocks for Fail-in-Place Networks               | 36 |

|   |       | 4.2.1    | Resilient Topologies                               | 36 |

|   |       | 4.2.2    | Resilient Routing Algorithms                       | 36 |

|   |       | 4.2.3    | Resiliency Metrics                                 | 37 |

|   | 4.3   | Interco  | onnect Simulation Framework                        | 40 |

|   |       | 4.3.1    | Toolchain Overview                                 | 40 |

|   |       | 4.3.2    | InfiniBand Model in OMNeT++                        | 41 |

|   |       | 4.3.3    | Traffic Injection                                  | 42 |

|   |       | 4.3.4    | Simulator Improvements                             | 43 |

|   | 4.4   | Simula   | ation Results                                      | 44 |

|   |       | 4.4.1    | Initial Usability Study                            | 44 |

|   |       | 4.4.2    | Influence of Link Faults on Small Topologies       | 46 |

|   |       | 4.4.3    | Influence of Link Faults on Large Topologies       | 50 |

|   |       | 4.4.4    | Case Study of the TSUBAME2 Supercomuter            | 52 |

|   |       | 4.4.5    | Case Study of the Deimos HPC System                | 54 |

| 5 | Utili | ization  | Improvement through SAR                            | 57 |

|   | 5.1   | Conce    | ptual Design of SAR for shared HPC Environments    | 57 |

|   | 5.2   | Examp    | ble Implementation of the Scheduling-Aware Routing | 62 |

|   |       | 5.2.1    | Hardware and Software Building Blocks              | 62 |

|   |       | 5.2.2    | Scheduling-Aware Routing Optimization              | 65 |

|   |       | 5.2.3    | Property Preserving Network Update for InfiniBand  | 67 |

|   | 5.3   | Evalua   | tion                                               | 71 |

|   |       | 5.3.1    | Current Limitations and Problems                   | 72 |

|   |       | 5.3.2    | Theoretical Evaluation of Network Metrics          | 72 |

|   |       | 533      | Practical Evaluation on a Production System        | 77 |

| 6  | Rou   | iting or | the Channel Dependency Graph                    | 81  |  |

|----|-------|----------|-------------------------------------------------|-----|--|

|    | 6.1   | Limita   | ations of Multi-Step Routing Approaches         | 81  |  |

|    | 6.2   | Nue R    | outing                                          | 84  |  |

|    |       | 6.2.1    | Complete Channel Dependency Graph               | 84  |  |

|    |       | 6.2.2    | Escape Paths for the Static Nue Routing         | 85  |  |

|    |       | 6.2.3    | Choosing Root Node for the Spanning Tree        | 87  |  |

|    |       | 6.2.4    | Dijkstra's Algorithm for the complete CDG       | 89  |  |

|    |       | 6.2.5    | Nue Routing Function                            | 91  |  |

|    |       | 6.2.6    | Optimizations for Nue Routing                   | 92  |  |

|    |       | 6.2.7    | Correctness, Completeness & Complexity          | 99  |  |

|    | 6.3   | Evalua   | ation of Nue Routing                            | 102 |  |

|    |       | 6.3.1    | Path Length and Edge Forwarding Index           | 103 |  |

|    |       | 6.3.2    | Throughput for Regular and Irregular Topologies | 104 |  |

|    |       | 6.3.3    | Runtime and Practical Considerations            | 107 |  |

| 7  | Sun   | nmary,   | Conclusion, and Future Work                     | 109 |  |

| Bi | bliog | raphy    |                                                 | 113 |  |

# List of Figures

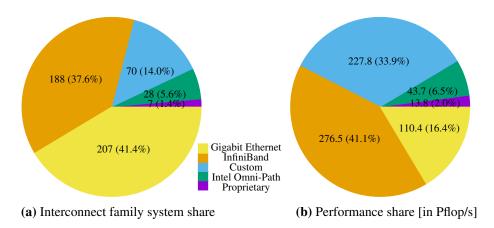

| 1.1 | Interconnect technology statistics of the TOP500 list of November 2016                                | 2  |

|-----|-------------------------------------------------------------------------------------------------------|----|

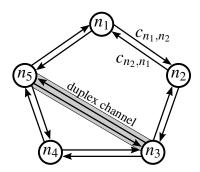

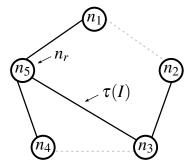

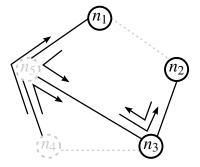

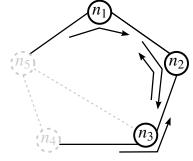

| 3.1 | 5-node interconnection network $I = G(N,C)$                                                           | 16 |

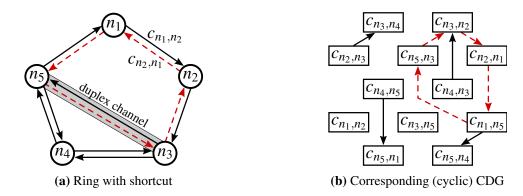

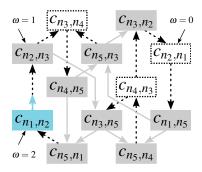

| 3.2 | Using a shortest-path, counter-clockwise routing for network <i>I</i> induces the channel             |    |

|     | dependency graph $D$                                                                                  | 18 |

| 3.3 | Example visualization of a 3-dimensional mesh and torus topology without terminals                    | 22 |

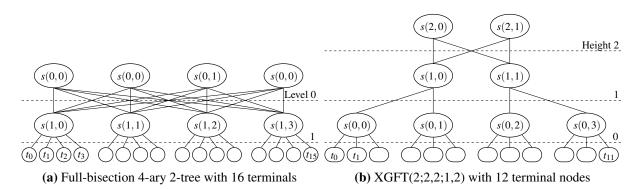

| 3.4 | Example visualization of a <i>k</i> -ary <i>n</i> -tree topology and an extended generalized fat-tree |    |

|     | topology                                                                                              | 23 |

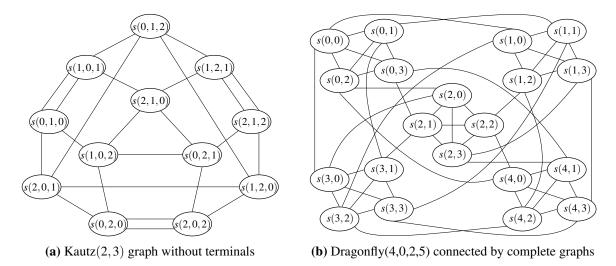

| 3.5 | Example visualization of a Kautz graph and a dragonfly topology                                       | 24 |

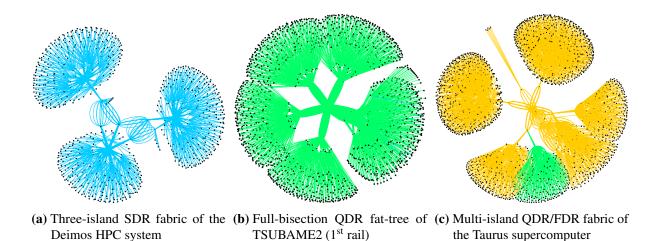

| 3.6 | Topology configurations of three real-world supercomputers                                            | 27 |

|     |                                                                                                       |    |

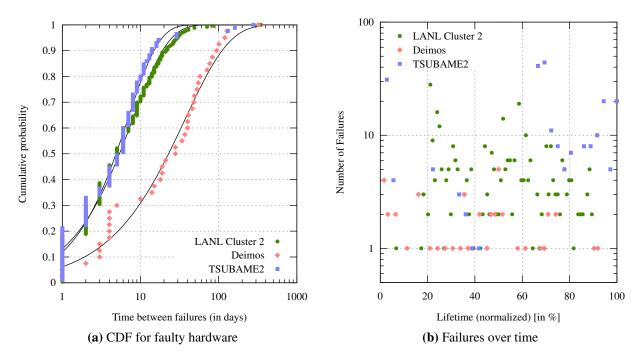

| 4.1 | Network-related hardware failures of three HPC systems                                                | 34 |

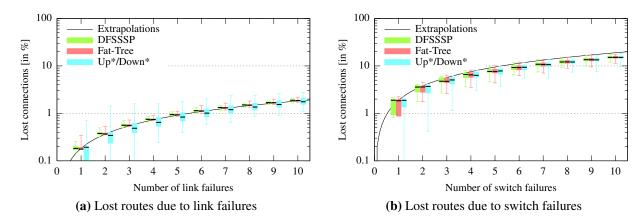

| 4.2 | Whisker plot for lost connections while removing links or switches from a 10-ary 3-tree               |    |

|     | without performing a rerouting                                                                        | 39 |

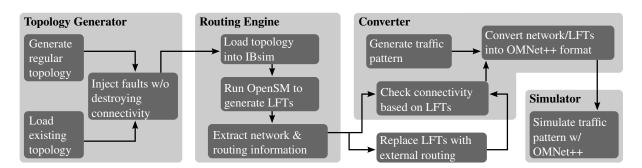

| 4.3 | Toolchain to evaluate the network throughput of a fail-in-place network                               | 41 |

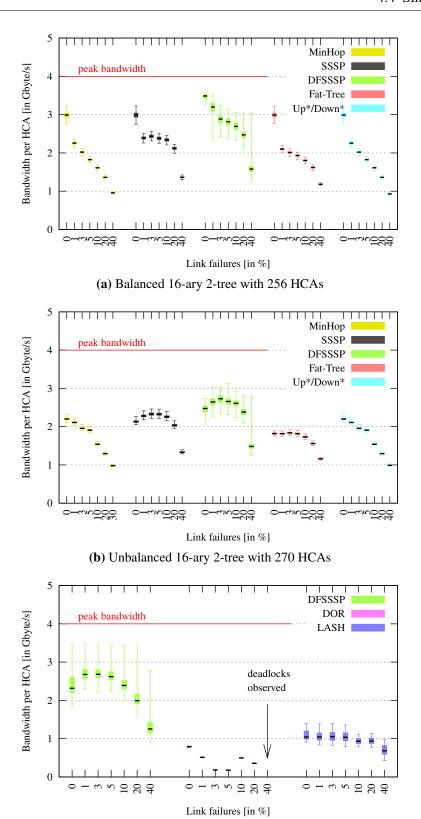

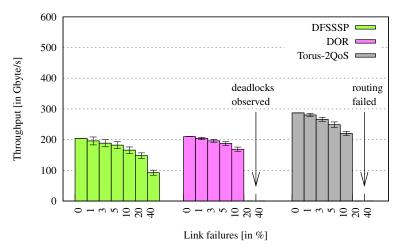

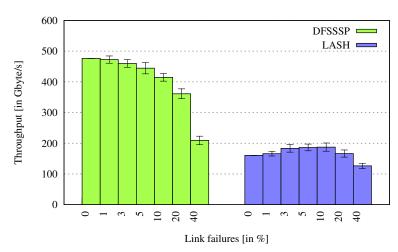

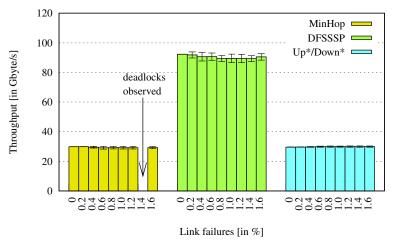

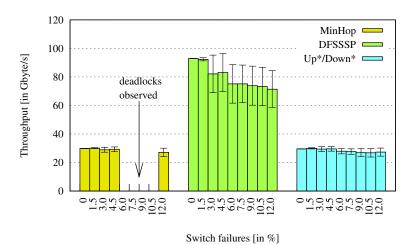

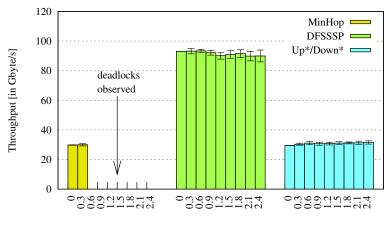

| 4.4 | Whisker plots of consumption bandwidth for uniform random injection                                   | 47 |

| 4.5 | Histograms for exchange patterns with error bars, showing mean value and the 95%                      |    |

|     | confidence interval for ten seeds                                                                     | 49 |

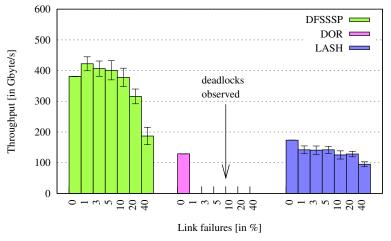

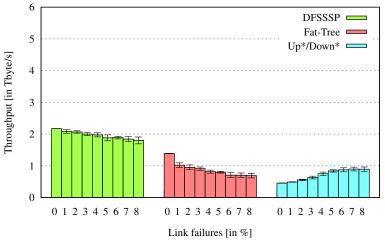

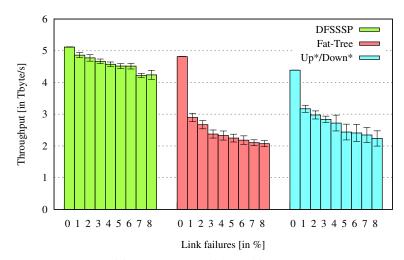

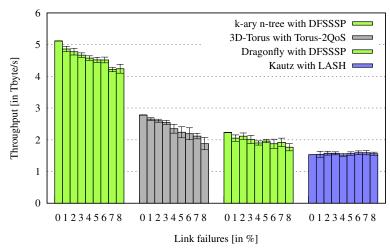

| 4.6 | Histograms for exchange patterns executed on networks with up to 8% link failures                     | 51 |

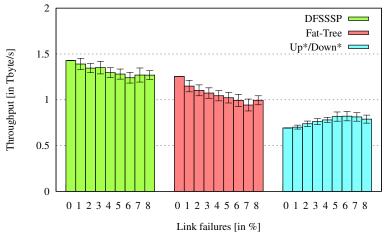

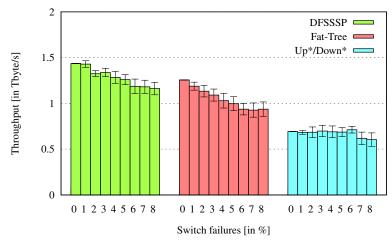

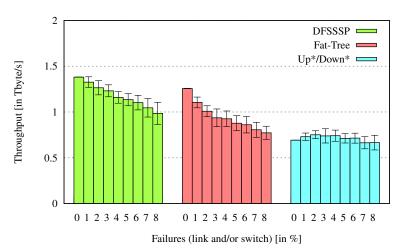

| 4.7 | Histograms for exchange patterns for different failure types using DFSSSP, fat-tree and               |    |

|     | Up*/Down* routing on TSUBAME2                                                                         | 53 |

| 4.8 | Histograms for exchange patterns for different failure types using MinHop, DFSSSP and                 |    |

|     | Up*/Down* routing on Deimos                                                                           | 55 |

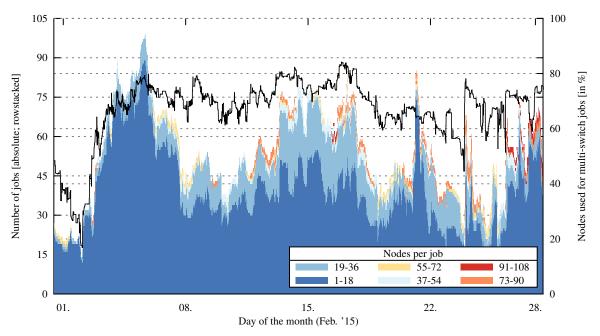

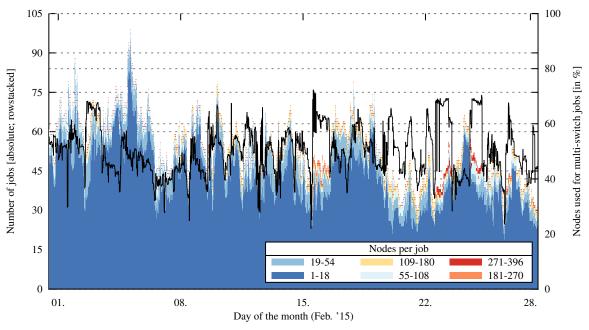

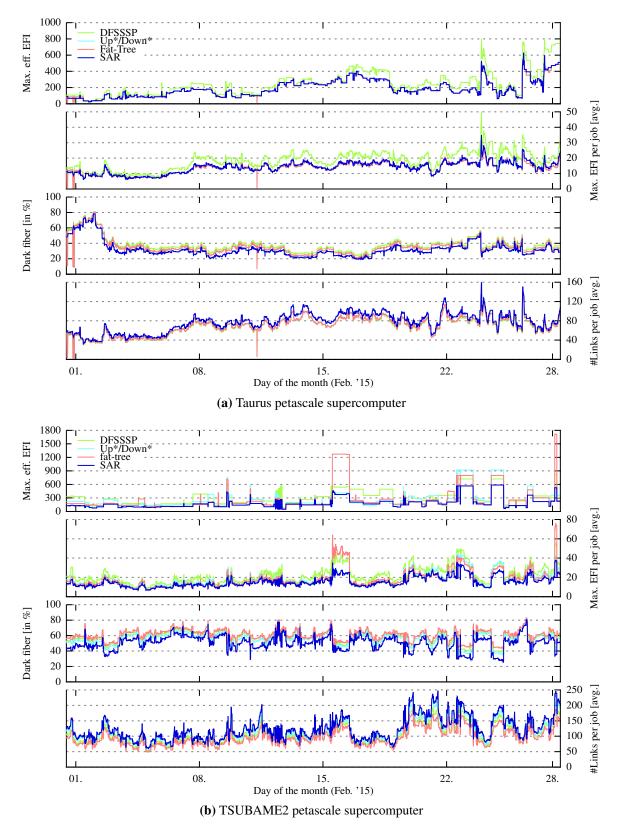

| 5.1 | Batch job history of two petascale HPC systems for one month of operation                             | 58 |

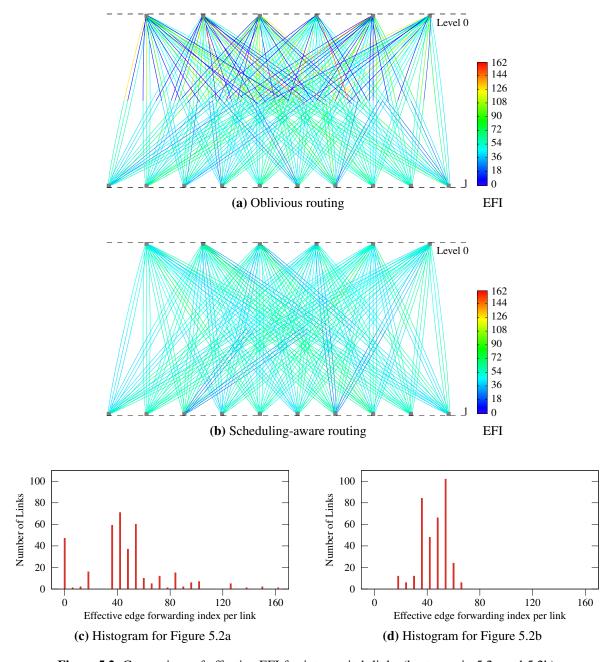

| 5.2 | Comparison of effective EFI for inter-switch links: Oblivious routing vs. scheduling-aware            |    |

|     | routing for three equal-sized batch jobs on a 2-level fat-tree                                        | 60 |

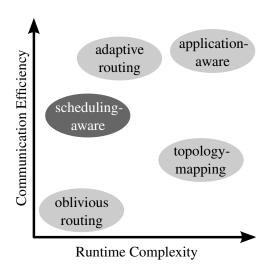

| 5.3 | Qualitative comparison of different routing and network optimizations for supercomputers              | 61 |

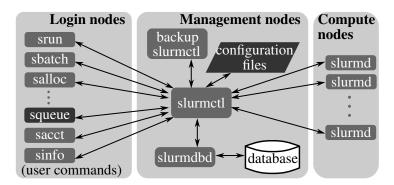

| 5.4 | SLURM architecture                                                                                    | 63 |

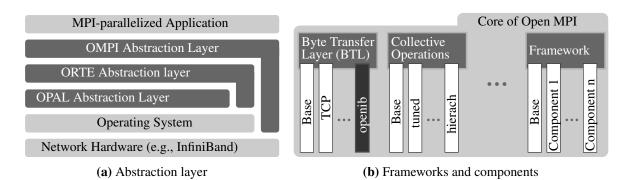

| 5.5 | Open MPI's modular component architecture establishes a message passing interface                     |    |

|     | between application and hardware to enable inter-process communication                                | 64 |

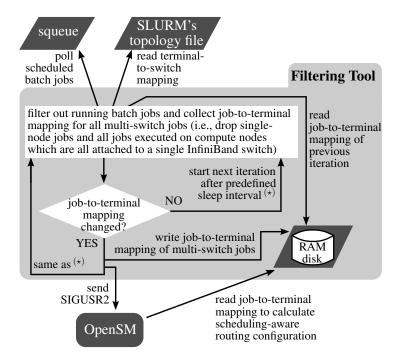

| 5.6 | Flowchart of a filtering tool                                                                         | 65 |

|     |                                                                                                       |    |

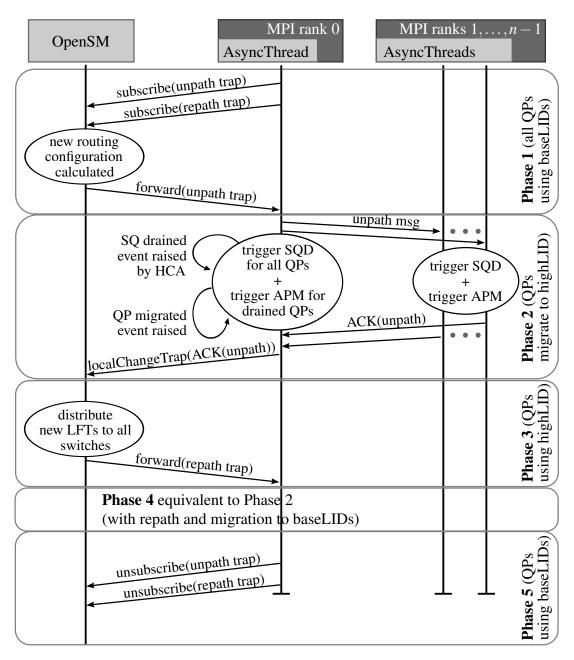

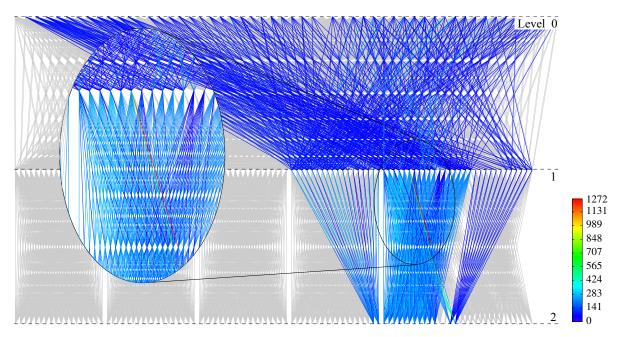

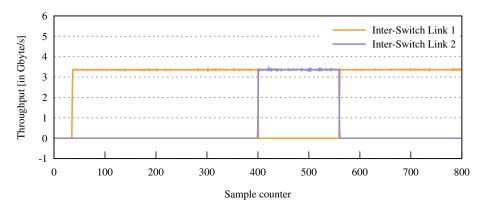

| 5.7  | Sequence diagram of a five-phase update protocol to achieve property preserving network                    |

|------|------------------------------------------------------------------------------------------------------------|

|      | updates of InfiniBand networks                                                                             |

| 5.8  | Replay of job history (Figure 5.1) for two HPC systems                                                     |

| 5.9  | Heat map of the EFIs for inter-switch links of TSUBAME2 for the 200-node batch job on                      |

|      | day 16 of Feb. '15; Used routing algorithm: fat-tree                                                       |

| 5.10 | Heat map of the effective EFIs for inter-switch links of TSUBAME2 for the 200-node                         |

|      | batch job on day 16 of Feb. '15; Used routing algorithm: SAR                                               |

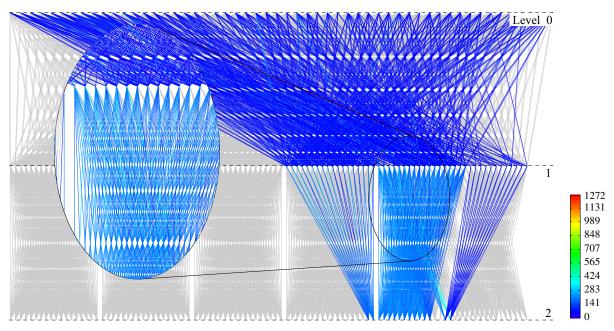

| 5.11 | Histograms of effective EFI for inter-switch links: Fat-tree routing vs. scheduling-aware                  |

|      | routing for the 200-node batch job on TSUBAME2                                                             |

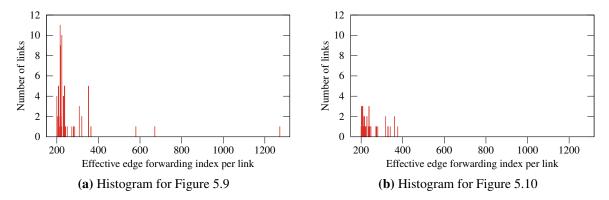

| 5.12 | Runtime measurement for MPI_Alltoall (with 1 MiByte in each send buffer) on 28                             |

|      | compute nodes using three different routing approaches                                                     |

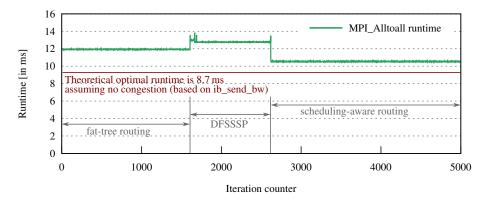

| 5.13 | Visualization of the network update protocol (without QP draining) and path migration                      |

|      | between two inter-switch links on a testbed during high MPI load                                           |

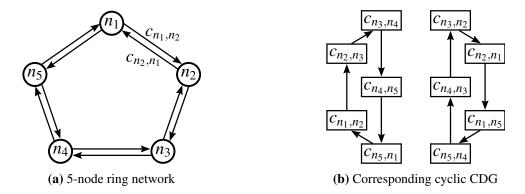

| 6.1  | Using a shortest-path routing for 5-node ring network $I$ induces the CDG $D$ 82                           |

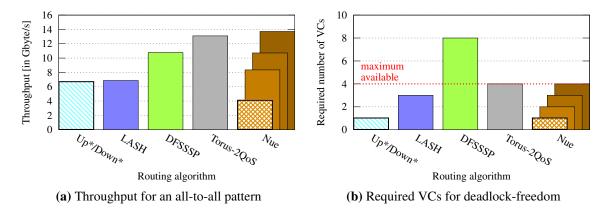

| 6.2  | Simulated throughput for an all-to-all operation and required VCs for deadlock-freedom                     |

|      | for different routing algorithms                                                                           |

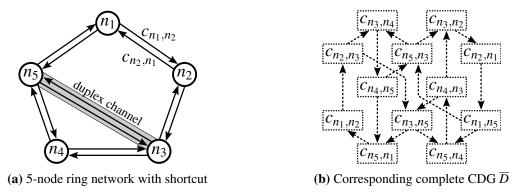

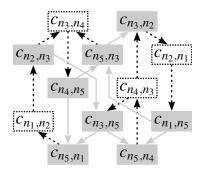

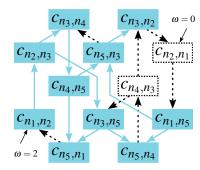

| 6.3  | Complete CDG $\overline{D}$ for the 5-ring network with shortcut; All channels are in unused state . 84    |

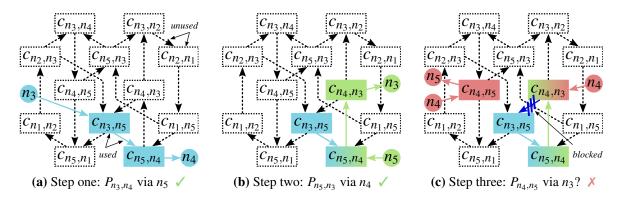

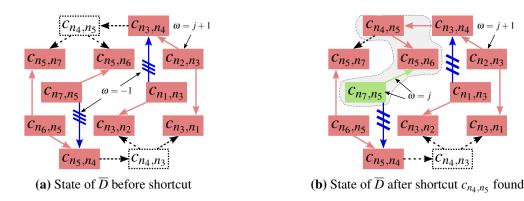

| 6.4  | Sketching the process of finding paths between network nodes within the complete CDG $\overline{D}$        |

|      | while avoiding to close any cycles in the induced CDG $D$                                                  |

| 6.5  | Acyclic escape paths $D^{\tau}$ for the 5-node ring network with shortcut                                  |

| 6.6  | Arrows show the initial channel dependencies of the escape paths for the node set $N_i^d$ =                |

|      | $\{n_1, n_2, n_3\}$ and root node $n_5$ or root node $n_2$ , respectively                                  |

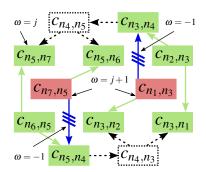

| 6.7  | State change of $\overline{D}$ after five steps with Algorithm 6.2, starting from $c_{n_1,n_2}$            |

| 6.8  | Impasse of Algorithm $6.2$ to reach $n_4$ based on previously placed routing restrictions for              |

|      | channels dependencies $(c_{n_1,n_3},c_{n_3,n_4})$ and $(c_{n_7,n_5},c_{n_5,n_4})$                          |

| 6.9  | States of the channel dependency graph $\overline{D}$ , of the subnetwork $I^*$ of Figure 6.8a, shown . 98 |

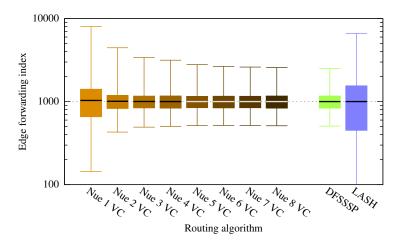

| 6.10 | Averaged edge forwarding index metrics for 1,000 random topologies with 125 switches, 1,000                |

|      | terminals, and 1,000 switch-to-switch channels                                                             |

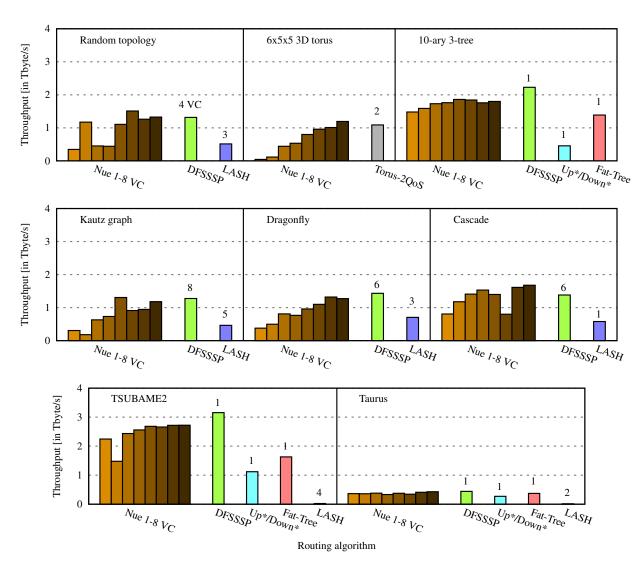

| 6.11 | Simulated throughput for an all-to-all operation on five standard and three real-world                     |

|      | topologies, as configured according to Table 6.1                                                           |

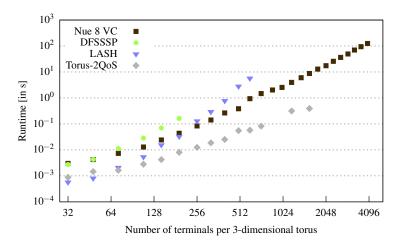

| 6.12 | Runtime comparison of deadlock-free routings for 3-dimensional tori (without channel                       |

|      | redundancy) of various topology sizes with 1% injected link failures                                       |

# **List of Tables**

| 2.1 | Qualitative comparison of existing topology-aware and topology-agnostic routing algorithms for supercomputers                                          | 14  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Vertex-connectivity for the investigated network topologies of Sections 3.2.1–3.2.4 (except for random and Cascade)                                    | 25  |

| 4.1 | Comparison of network-related hardware and software failures, MTBF/MTTR, and annual failure rates for three production supercomputers                  | 34  |

| 4.2 | Topology configurations for a balanced (and unbalanced) number of HCAs with link redundancy $r_{C'}$ to allow a fair comparison between topology types | 45  |

| 4.3 | Usability of topology and routing combinations for networks listed in Table 4.2                                                                        | 45  |

| 4.4 | Intercept [in Gbyte/s], slope, and $R^2$ for balanced topologies of Table 4.2 for best performing routing algorithm                                    | 50  |

| 4.5 | Intercept [in Gbyte/s], slope, and $R^2$ for the large topology/routing combination shown in Figure 4.6c                                               | 52  |

| 4.6 | Intercept, slope, and $R^2$ for TSUBAME2 and Deimos shown in Figure 4.7c and Figure 4.8c                                                               | 56  |

| 5.1 | Improvements by the scheduling-aware routing compared to DFSSSP, fat-tree, and Up*/Down* routing for the Taurus HPC system                             | 75  |

| 5.2 | Improvements by the scheduling-aware routing compared to DFSSSP, fat-tree, and Up*/Down* routing for the TSUBAME2 HPC system                           | 75  |

| 6.1 | Topology configurations, with link redundancy $r_{C'}$ , used for throughput simulation results visualized in Figure 6.11                              | 105 |

# List of Algorithms

| 3.1 | SSSP: Global balancing of routes with single-source shortest-path routing                     | 28 |

|-----|-----------------------------------------------------------------------------------------------|----|

| 3.2 | Fat-Tree: Setting LFTs towards all compute nodes                                              | 30 |

| 3.3 | Fat-Tree: Assign-down-going-port-by-ascending                                                 | 30 |

| 3.4 | Fat-Tree: Assign-up-going-port-by-descending                                                  | 30 |

| 3.5 | LASH: Deadlock-free path calculation by layered shortest path routing                         | 31 |

| 3.6 | DFSSSP: Search cycles in the CDGs and remove potential deadlocks                              | 32 |

| 5.1 | Scheduling-aware DFSSSP routing                                                               | 67 |

| 6.1 | Convex subgraph for node set $N^d$ of an unweighted graph $G(N,C)$                            | 89 |

| 6.2 | Modified Dijkstra's algorithm within the complete CDG $\overline{D}$                          | 90 |

| 6.3 | Nue routing calculates all paths within a network $I = G(N, C)$ for a given number of virtual |    |

|     | channels $k \geq 1$                                                                           | 91 |

| 6.4 | Search for cyclic <i>used</i> subgraphs in the complete CDG $\overline{D}$                    | 94 |

| 6.5 | Local backtracking finds paths into islands                                                   | 96 |

| 6.6 | Finding shortcuts through island nodes                                                        | 98 |

# List of Abbreviations and Symbols

ACK Acknowledgement signal to acknowledge the receipt of data

API Application programming interface

APM Automatic path migration

BFS Breadth-first search

BGP Border Gateway Protocol

BTL Byte transfer layer of Open MPI

CDG Channel dependency graph

CEE Converged enhanced Ethernet

DDR Double data rate – 5 Gb/s per lane (or 20 Gb/s for 4x link width)

DFS Depth-first search

DFSSSP Deadlock-free single-source shortest-path routing

DOR Dimension order routing

EDR Enhanced data rate – 25 Gb/s per lane (or 100 Gb/s for 4x link width)

EFI Edge forwarding index

FDR Fourteen data rate – 14 Gb/s per lane (or 56 Gb/s for 4x link width)

HCA Host channel adapter (InfiniBand's network interface card)

HPC High-performance computing

IB InfiniBand

IBTA InfiniBand Trade Association

LASH Layered shortest path routing

LFT Linear forwarding tables

LID Local identifier

LMC LID mask control

MAD Management datagram packet of InfiniBand

MCA Modular component architecture

MPI Message Passing Interface

MTBF Mean time between failure

MTTR Mean time to repair

MTU Message transfer unit

MUD Multiple Up\*/Down\* routing

NIC Network interface card

NoC Network-on-Chip

PCI Peripheral Component Interconnect

QDR Quad data rate – 10 Gb/s per lane (or 40 Gb/s for 4x link width)

QP Queue pair

RC Reliable connection

SAR Scheduling-aware routing

SDN Software defined network

SDR Single data rate -2.5 Gb/s per lane (or 10 Gb/s for 4x link width)

SLURM Simple Linux Utility for Resource Management

SQ Send queue

SQD Send queue draining

SSSP Single-source shortest-path routing

UC Unreliable connection

VC Virtual channel

VL Virtual lanes (InfiniBand's virtual channel)

xviii

| WR                      | Work request                                                                                        |

|-------------------------|-----------------------------------------------------------------------------------------------------|

| XGFT                    | eXtended Generalized Fat-Tree                                                                       |

| χ                       | Network state, i.e., the entirety of all forwarding tables of all switches                          |

| Δ                       | Maximum degree of the interconnection network, i.e., maximal switch radix                           |

| $\gamma(I,R)$           | Edge forwarding index of the network $I$ as defined by the routing $R$                              |

| $\gamma^e(I,R,J)$       | Edge forwarding index of the network $I$ as defined by the routing $R$ and jobs set $J$             |

| $\gamma_{R,J}^e(c)$     | Effective edge forwarding index of a channel $c \in C$ w.r.t job set $J$                            |

| $\gamma_R(c)$           | Edge forwarding index of a channel $c \in C$ defined by the routing $R$                             |

| κ/λ                     | Vertex-/edge-connectivity for a graph or network                                                    |

| ${}^{s}P_{n_{u},n_{v}}$ | Shortest path between two network nodes $n_u, n_v \in N$                                            |

| $\omega(\cdot)$         | Function assigning a unique identifier to a cycle-free subgraph of $\overline{D}_i$                 |

| $\overline{D}_i$        | Complete channel dependency graph $G(C_i, \overline{E}_i)$ of the <i>i</i> -th virtual layer $L_i$  |

| $\overline{E}_i$        | Set of edges $(\subseteq C_i \times C_i)$ of the complete channel dependency graph $\overline{D}_i$ |

| au(I)                   | Spanning tree of network $I$                                                                        |

| $	heta_{R,J}$           | Dark fiber percentage of unused channels for intra-job routes as induced by the routing R           |

| $	ilde{c}$              | Virtual channel of a network channel $c \in C$                                                      |

| C                       | Set of network channels or links                                                                    |

| c                       | Network link or channel of the channel set <i>C</i>                                                 |

| $C^*$                   | Set of switch-to-switch channels                                                                    |

| $C_i$                   | Set of network channels of the $i$ -th virtual layer $L_i$                                          |

| $C_L$                   | Set of faulty switch-to-switch channels                                                             |

| $C_B(n)$                | Betweenness centrality value of a network node $n \in N$                                            |

| $D_i^	au$               | Escape paths defining a cycle-free subgraph of $\overline{D}_i$                                     |

| h                       | Path length                                                                                         |

| $H_i$                   | Convex Subgraph $G(N_i^H, C_i^H)$ for a set $N_i^d \subseteq N$ of network nodes                    |

|                         |                                                                                                     |

$H_i$

- $h_R$  Routing-induced path length or routing-based hop count between two nodes

- I Interconnection network with I := G(N, C)

- J Set of batch jobs running simultaneously on a supercomputer

- k Maximum number of supported virtual channels (except when used for k-ary n-trees)

- N Set of network nodes composed of switches and terminals, i.e.,  $N = S \cup T$

- *n* Network node of the node set *N*

- $N_i^d$  Set of destination nodes being routed with the *i*-th virtual layer  $L_i$

- $N_i$  Set of network nodes belonging to the same batch job  $j \in J$

- $P_{n_u,n_v}$  Path between two network nodes  $n_u, n_v \in N$

- Q Queue data structure used within algorithms

- *R* Routing function

- $R^*$  Perfectly balanced routing function (with respect to the edge forwarding index)

- $R^2$  Coefficient of determination for a linear regression

- $r_{C'}$  Link redundancy for the augmented network I' := G(N, C')

- Set of switches in the network (subset of N)

- T Set of terminal nodes (subset of N)

- $u_s$  Sequence of atomic updates applied to forwarding tables

# 1 Introduction

Ensuring efficient communication within a supercomputer is an important task to enable progress of other scientific fields. High-speed lossless interconnection networks, such as InfiniBand, are the de facto standard for the fastest computers in the world, see Section 1.1. This thesis advances the state-of-the-art, as listed in Section 1.2, by introducing new concepts for operating these networks, both in terms of hardware and software. Section 1.3 provides the list of preceding articles published by the author of this thesis, and outlines the high-level structure and content of the following chapters.

#### 1.1 Motivation

With Moore's law slowly coming to an end, many information technology domains started to scale-out. A global trend visible from small many-core systems-on-chip, such as the 256-core Kalray MPPA-256 chip [Din+13] or the 1024-core Epiphany-V developed by Adapteva [Olo16], over large-scale data centers or data wearhouses [Mic15], to the world's most powerful supercomputers, such as the 40,960-node Sunway TaihuLight system hosting more than 10 million compute cores [Don16]. All these systems, and many more (e.g., wireless sensor networks, the Internet with the emerging Internet-of-Things, etc.), have one common property: the requirement for a network connecting the individual devices. The network, connecting these compute nodes, machines, or appliances, plays a crucial role for successful operation.

For high-performance computing (HPC) systems, it can be expected that the number of network endpoints will grow significantly [KBB08; Luc+14] which emphasizes the role of the interconnection network as one of the most critical components in a supercomputer even more. These HPC networks, as well as other previously mentioned networks, are largely controlled by routing algorithms which determine how to forward packets. Routing algorithms have to balance multiple, partially conflicting, requirements. For example, they shall provide the best forwarding strategy to guarantee a certain quality of service (throughput, latency, etc.), which is an NP-hard problem in general, while minimizing the runtime of the routing in order to quickly react to failures of network components.

Most supercomputers listed in the TOP500 list of November 2016 [Str+16], 84.6% to be precise, rely on standardized and off-the-shelf interconnection network components. The deployed interconnection technologies are either different high-speed versions of Ethernet [IEE16] (207 systems), different speeds of InfiniBand [Inf15] (188 systems), or Intel's 100 Gbit/s Omni-Path technology [Bir+15] (28 systems), see Figure 1.1a. Both, the system share and performance share shown in Figure 1.1 are adjusted to include the current No. 1 system, the Chinese 93 Pflop/s Sunway TaihuLight supercomputer, in the InfiniBand (IB)

**Figure 1.1:** Interconnect technology statistics of the TOP500 list of November 2016; Ethernet distribution: 1x 100G, 178x 10G, 28x 1G; InfiniBand distribution: 15x EDR, 149x FDR, 24x QDR; Shares adjusted for IB-based Sunway TaihuLight (No. 1)

shares, since it utilizes Mellanox's EDR InfiniBand switch chips and host channel adapters [Don16]. Otherwise, these numbers would unfairly belittle the significance of the InfiniBand for the performance of the top-tier supercomputers. Besides Ethernet or InfiniBand interconnects, a subset of HPC systems make use of either custom or proprietary interconnects, such as Cray's Gemini interconnect used in Titan [ARK10] (No. 3) or the Tofu interconnect of the K computer [Aji+12a] (No. 7).

To meet the vast data transfer demands of supercomputers in terms of low latency and high bandwidth, these network architectures increasingly embrace functions that enable a tighter interaction between networking hardware and programming models. The best examples are Remote Direct Memory Access (RDMA) in combination with a kernel bypass, and lossless Layer 2 networking, all tailored for these demands. The former enables the programmer to directly instruct the network interface to read and write remote memory without having to issue a kernel call to the operating system. While the latter enables the reliable transport within the network which is needed for RDMA. Such advanced features have been prevalent in the high-speed networking area, such as InfiniBand [SWM03] or Cray's Cascade [Faa+12], but also find their way into Ethernet, which was recently extended with Priority Flow Control at Layer 2 to support RDMA [Inf10; Zhu+15].

Unfortunately, as network topologies grow, failures of switches and connectors or cables become common. As opposed to network endpoints, the wiring complexity and infrastructural demands of cabling, e.g., arrangement of cable trays, make maintaining complex networks challenging and expensive. Thus, network structures are often kept in place over years and multiple generations of machines while other components such as CPU or main memory are upgraded. Today, many networks are based on the concept of over-provisioning the hardware, such as installing spare cables in the cable trays or having an inventory of spare parts. Alternatively, they are operated in a deferred repair mode, in which a failed component will not be replaced instantaneously but within a reasonable time frame, such as a business day.

Fail-in-place strategies are common in storage systems when maintenance costs exceed maintenance

benefits, such as in large-scale data centers with millions of hard drives. For example, Microsoft owned more than one million servers in 2015 [Mic15], i.e., even an optimistic failure rate of 1% per year and two hypothetically hard drives per server would result in a mean time between failure of 26 minutes. Instead of replacing the hard drives of a server, the storage system, such as IBM's Flipstone [Ban+08], uses RAID arrays for reliability and a software approach to disable failed hard drives and to migrate the data, until a critical component failure disables the entire server. Hence, a fail-in-place approach for interconnection networks could be similarly beneficial, if supported by the correct combination of network topology and applied routing algorithm.

Routing algorithms for HPC systems have been the topic of many studies ranging from topology-specific routing algorithms [Rod+09; Zah12] through general deadlock-free algorithms [DS87; Sch+91], more advanced deadlock-free algorithms balancing the routes [DHN11], to advanced path-caching for quick failover [VSR15]. A good overview is provided by Flich et al. [Fli+12]. Many advanced approaches for application-specific [Pal+06; Kin+09] or topology-specific [Sub+12; Pri+13b; Jok+15] routing and mapping assume idealized conditions such as a regular topology without faulty components, isolated bulk-synchronous applications communicating in synchronized phases, and the absence of system noise. Unfortunately, these assumptions are rarely true in practice. Presumably, integrating additional information about the current state of the supercomputer, such as state of the batch system (i.e., the current job mix) or application demands, can help guiding the network manager in assigning optimized routes on-demand which potentially increases utilization and achievable throughput.

Due to the previously addressed hardware failures and these on-demand software adjustments, topology-aware routing algorithms become increasingly inapplicable in modern supercomputers. Hence, avoiding deadlock situations [CES71; DT03], a requirement for lossless Layer 2 networking, becomes much harder to achieve. A network deadlock arises when a group of packets cannot be forwarded because of unavailable resources, such as buffers or channels, and the group is circularly depended on each other, which disables parts or the entire network. Topology-aware routings usually avoid deadlocks algorithmically for many regular topologies, e.g., by restricting the routing to use only a subset of all available channel dependencies, as it is implemented by dimension-order routing (DOR) [RR10]. In contrast, many topology-agnostic routing technique for HPC and on-chip networks (NoC) use virtual channels to break deadlocks [SLT02; BM06; Shi+09; DHN11]. Yet, all these concepts have limitations:

- (1) Topology-aware routing algorithms usually assume perfect topologies and often do not support switch or link failures, see Chapter 4 of this thesis,

- (2) Cycle-avoiding routing algorithms often cannot balance routes across the available links and thus limit global achievable throughput [SRD00a], and

- (3) Routing algorithms based on virtual channel isolation fail when the required number of virtual channels is not available [Fli+12].

### 1.2 Contributions

This thesis contributes to multiple frontiers of the design and operation of interconnection networks of modern and future HPC systems, as well as proposes a novel approach to solve the deadlock-free routing problem of these networks, which will greatly influence the next generation of routing algorithms.

Historical failure data of three production HPC systems allows this thesis an analysis that subsequently enables a realistic performance model for a wide range of HPC networks. Initial connectivity simulations reveal that it is insufficient to consider fault properties of the topology or to consider the resiliency of the routing algorithm in isolation. For fail-in-place networks, both these properties and the combination of topology and routing must meet requirements. The developed flit-level simulation toolchain for InfiniBand networks determines the achievable throughput accurately. An exhaustive study, using the simulator for several real-world topologies and two real HPC systems, shows that the choice of the routing algorithm influences the number of disconnected paths in case of a failure and the quality of service after a reinitialization of the network with missing links or switches. Depending on the underlying topology and routing method, a low number of failing links already reduces the overall throughput by up to 30% (e.g., for small-scale fat-trees), or an HPC system can be operated in fail-in-place mode with almost zero performance degradation, respectively. Overall, the study reveals that fail-in-place network designs can be accomplished with an appropriate combination of topology and routing algorithm, while assuming that a performance degradation up to a predefined threshold is tolerable. Changing the used routing method of the two investigated HPC systems would not only increase their network throughput by up to 2.1x or 3.1x for the fault-free network, respectively, but also increase their fail-in-place characteristics.

The influence of the degrading fail-in-place interconnect on the achievable application throughput can be further reduced by optimizing the routing algorithm to exploit the knowledge about the momentary resource allocation in the supercomputer. The developed scheduling-aware routing (SAR), an enhancement of one of the most appropriate routings for fail-in-place networks, frequently reconfigures the switches' routing tables for intra-job communication of concurrently running applications. This low-overhead routing algorithm is already deployed on a production petascale supercomputer for over one year and improves the system's utilization and its amount of scientific output. Two newly introduced metrics, the effective edge forwarding index and the dark fiber percentage, show the effectiveness of SAR in comparison to the state-of the-art oblivious routing mechanisms for HPC systems, using simulations with historical resource allocations of two InfiniBand-based supercomputers. The former metric measures the well-established edge forwarding index with respect to the running applications, both within and between allocations, to estimate a theoretical upper bound for the worst-case network congestion. The latter metric, the dark fiber percentage, quantifies the utilization of the network. Unfortunately, some network architectures, such as InfiniBand, rely on in-order packet delivery, i.e., a prerequisite for unobstructed operation, which can be compromised by frequent reconfigurations. Hence, the formalism of per-packet consistent updates is extended for in-order delivery and deadlock-freedom, and a new network update protocol is introduced to achieve the required consistency for InfiniBand hardware.

Even more important than preventing deadlocks during the reconfiguration of the network is the deadlock-avoidance while a single network configuration is active. A thought experiment visualizes the limitations of state-of-the-art multi-step routing approaches, i.e., the impossibility to achieve deadlock-freedom for shortest-path routing with limited amount of supported virtual channels on arbitrary or faulty topologies. Consequently, a novel routing approach is developed based on the concept of routing within the complete channel dependency graph that overcomes all limitations (1) – (3) mentioned in Section 1.1. Hence, this routing, called Nue, is capable of distributing the paths across the network to increase the throughput, while reliably avoiding deadlocks. Flit-level simulations with the developed toolchain show that the destination-based Nue routing works on any arbitrary topology, especially fail-in-place networks, with all possible numbers of available virtual channels, including network technologies without support for virtual channels. The conducted complexity analysis, as well as runtime measurements with an implementation of Nue in the InfiniBand subnet manager, demonstrate Nue's competitiveness and broad applicability for InfiniBand and other network architectures.

## 1.3 Thesis Organization

This thesis, especially Chapters 4-6, focuses on flow-oblivious, static, destination-based, unicast routing for supercomputers, and is based on the following three peer-reviewed publications which have been reformatted and/or partially rewritten, and the author's contributions are as follows:

- J. Domke, T. Hoefler, and S. Matsuoka. "Fail-in-Place Network Design: Interaction between Topology, Routing Algorithm and Failures". In: *Proceedings of the IEEE/ACM International Conference for High Performance Computing, Networking, Storage and Analysis (SC14)*. SC '14. New Orleans, LA, USA: IEEE Press, Nov. 2014, pp. 597–608. ISBN: 978-1-4799-5500-8. DOI: 10.1109/SC.2014.54

- The author of this thesis is the main contributor to this publication. In particular, he performed the analysis of failure data, and designed and implemented the simulation framework. Subsequent simulations, analysis of the results, and preparation of the manuscript were done by the author.

- J. Domke and T. Hoefler. "Scheduling-Aware Routing for Supercomputers". In: *Proceedings of the International Conference for High Performance Computing, Networking, Storage and Analysis*. SC '16. Piscataway, NJ, USA: IEEE Press, 2016, 13:1–13:12. ISBN: 978-1-4673-8815-3. URL: http://dl.acm.org/citation.cfm?id=3014904.3014922

- The author is the main contributor to this publication. Besides identifying the disadvantages of the current state-of-the-art HPC routing methods, he was responsible for algorithm and protocol design (including their implementations) to overcome the challenges. The tasks of benchmarking existing systems and conducting wide-ranging simulations with subsequent data analysis, as well as drafting the publication, were carried out by the author.

• J. Domke, T. Hoefler, and S. Matsuoka. "Routing on the Dependency Graph: A New Approach to Deadlock-Free High-Performance Routing". In: *Proceedings of the 25th ACM International Symposium on High-Performance Parallel and Distributed Computing*. HPDC '16. New York, NY, USA: ACM, 2016, pp. 3–14. ISBN: 978-1-4503-4314-5. DOI: 10.1145/2907294.2907313

The author is the main contributor to this published work. Both, the new conceptual approach for solving the deadlock problem and its model implementation, were contributed by the author. Additionally, he analyzed the results of the executed simulations, proved mathematical correctness and characteristics of the routing function, and prepared the manuscript for publication.

The remaining chapters comprise the following: Chapter 2 reviews the state-of-the-art with respect to network simulation frameworks and routing algorithms. Especially, fault-tolerant and deadlock-free routing algorithms are of interest. Chapter 3 lays the groundwork for the following chapters by providing network-related and routing-related definitions, by introducing numerous network topologies, and by illustrating the inner workings of various routing algorithms, which will be used for later comparisons. Thereafter, the three Chapters 4, 5, and 6, outline the main contributions in the field of high-speed interconnects by: (1) showing that fail-in-place network operation is feasible and the corresponding throughput degradation manageable, (2) improving the utilization and communication efficiency through scheduling-aware routing, and (3) developing an invariably working deadlock-free routing algorithm. In conclusion, Chapter 7 summarizes the thesis and provides the prospects for future work.

## 2 Related Work

The following two sections review the related work, relevant to this thesis, in the research domain of high-performance interconnection networks. Section 2.1 outlines state-of-the-art interconnection architectures, topologies commonly used in HPC systems, management and resiliency considerations, as well as simulation frameworks to analyze the effectiveness of the interconnect. Subsequently, Section 2.2 gives a summary of the state-of-the-art deterministic routing algorithms tailored for the application in supercomputers or for the usage in related network architectures, such as Network-on-Chip. Especially, the algorithm's characteristics with respect to achievable latency, throughput, and deadlock-freedom, as well as applicability to current real-world architectures, are of interest. The Table 2.1, provided at the end of Section 2.2, summarizes the attributes of a subset of these algorithms. Readers unfamiliar with the basics of HPC interconnects and routing algorithms are encouraged to review Section 3.1 prior to continuing with this section.

## 2.1 State-of-the-Art for High-Performance Interconnect Designs

The interconnection networks of the supercomputers in the TOP500 list of November 2016 are essentially dominated by seven different network architectures, e.g., InfiniBand, Gigabit Ethernet, and Intel's Omni-Path, comprising a total of 423 systems. The remaining systems are connected by either IBM's interconnect for the Blue Gene systems [Adi+05; Che+12], Cray's 3-dimensional tori-based Gemini networks and more recent Aries networks [ARK10; Alv+12], the TH Express interconnect used in MilkyWay 2 systems [Pan+14], or Fujitsu's Tofu interconnect [Aji+12a]. Hence, the prevalent topologies used by these supercomputers are fat-trees [PV97] (occasionally deployed as dual-rail fat-tree [Hat11] or tapered fat-tree [Leó+16]), 5-dimensional or 6-dimensional tori in case of Blue Gene systems or Tofu-based systems, respectively, and dragonfly topologies in case of Aries-based HPC systems. Due to the scale of these production systems, in terms of compute node count, fault-free and regular topologies are an exception rather than the norm [SG10], because both network and compute hardware fails frequently.

#### 2.1.1 Resiliency of Networks, Topologies, and Routings

Resiliency of network topologies has been studied extensively in the past. Xu et al. [Xu10] analyzed numerous interconnection topologies, such as De Bruijn graphs, Kautz graphs, meshes, and butterfly networks. However, an analysis of routing algorithms has been done based on edge forwarding index, but not based on actual performance delivered for a traffic pattern. Another comprehensive survey of network

fault tolerance was performed by Adams et al. [AAS87]. The authors describe methods to increase fault tolerance through hardware modification of existing topologies, such as adding additional links, ports, or switches. Other attempts to enhance the fault tolerance properties of the network have been performed analytically. One example is the multi-switch fault-tolerant modified four tree network which aims to improve the single-switch fault-tolerant four tree network [SB02]. Another example is the attempt to solve the problem heuristically with genetic algorithms [Szl06].

Co-design strategies have been proposed, such as the F10 network [Liu+13], where the interconnection topology is optimized for the routing algorithm and vice versa. This includes an increase in alternative paths using an AB Fat-Tree instead of an ordinary fat-tree and includes enhanced fault recovery properties through local rerouting. The routing algorithm for F10, besides optimizing for global load balancing, manages the failure detection and propagates this information to a subset of the nearest neighbors of the failure. This subset is smaller for F10 than in an ordinary fat-tree allowing for fast recovery and therefore decreases the potential for the packet loss.

Okorafor et al. [OL05] proposed a fault-tolerant routing algorithm for an optical interconnect, which assumes a fail-in-place 3-dimensional mesh topology and enhances the throughput. The IBM Intelligent Bricks project [Fle+06] investigates the feasibility of building fail-in-place storage systems and includes considerations about the performance loss in the network due to failed bricks. The throughput degradation in the 6x6x6 3-dimensional torus is simulated up to 60% failed bricks. However, no other routing algorithm besides the IceCube mesh routing has been tested.

Fault-tolerant topology-aware routing algorithms have been developed and studied in the past, especially for meshes and tori topologies and in the field of Network-on-Chip, e.g., [Suh+95; DYL02; RFR09; Man+11; AA13], but the usability of these algorithms for other topologies has not been tested. Flich et al. [Fli+12] performed a survey of topology-agnostic routing algorithms and compared them not only analytically, but also evaluated their performance with a flit-level simulator, which realizes its message forwarding based on the smallest logical unit of network information, called flit, required for flow control [DT03, 12.1]. The simulations have been conducted on small 2-dimensional mesh and tori networks, up to a size of 16x8. Additionally to these regular topologies, faulty meshes and tori with an injected number of link failures of 1%, 3%, and 5% were investigated.

### 2.1.2 HPC Routing Strategies and Network Management

The state-of-the-art routing method for supercomputers is static and flow-oblivious routing, where the packet route is uniquely defined by the source-destination pair, e.g., [Aji+12b; Inf15], but a few alternatives, such as adaptive routing strategies [Ari+10; Alv+12; Bir+15], exist. Switches of adaptive routed networks are capable of adjusting the path towards a destination dynamically in response to changing local or global conditions, such as link load [DT03, p. 189]. Research has shown that oblivious routing can result in local congestion, which increases application runtime, when the routes and communication pattern does not match properly [HSL08]. Yet, its simplicity and practicality makes it the most-used

routing mechanism, for example, in all InfiniBand and Ethernet networks, which combined provide  $\approx 58\%$  performance of all systems in the TOP500 list. The objective of these flow-oblivious routings, such as Up\*/Down\* [Sch+91] and fat-tree routing [Zah+10], or the deadlock-free single-source shortest-path routing algorithm (DFSSSP) [DHN11], is to distribute the routes evenly across the interconnection network. However, this static and global balancing approach is only effective when the system is used by a single parallel application.

Optimizing communication performance for multi-user HPC system has been studied in the past resulting in many different approaches. Mellanox's proprietary traffic-aware routing, short TARA [Mel16], monitors active applications and the network port counters, and attempts path adjustments when congestion is identified. However, TARA is a reactive optimization and depends on the time to collect and analyze all port counters. Furthermore, TARA's ability to enforce property preserving network updates of the forwarding rules is unknown, hence out-of-order packet delivery might be possible.

Application-aware routings, e.g., [ZL92; Kin+09], have been developed, but require detailed knowledge about traffic patterns and injection rates of each application. Additionally, this optimization approach has no notion of a timely behavior of the applications, and might assign too few links to each applications assuming they communicate simultaneously.

Optimizing the job-to-node assignment via the batch system, while considering the network topology [YCM06; HS11; BDM15], is feasible for regular networks, but assumes an idealized routing or ignores it completely. Performing a routing-aware job-to-node mapping [ATB14] by the batch job scheduler has been proposed as alternative. However, the computational complexity to solve the mapping problem is usually infeasible for an online scheduling of batch jobs, or fast and imprecise heuristics need to be used. In addition, this job-to-node mapping might increase the system's fragmentation, or it is hindered by the logical separation of the system through batch queues.

Changing the forwarding rules of the entire supercomputer, either in reaction to a hardware failure or due to desired optimizations, can violate certain network properties, such as in-order delivery. Multiple network update protocols, tackling these problems, have been developed in the past, but the solutions are usually specific to certain technologies and their properties, such as for the broader gateway protocol (BGP) [Fra+07; RZC11] or for software-defined networking (SDN) [Rei+12; McC+15], to name but a few. Yet, no property preserving network update protocol tailored to the conditions and requirements found in lossless InfiniBand fabrics exists, which is the focus network architecture of this thesis.

#### 2.1.3 Simulation Frameworks for Network Analyses

Academia developed various discrete event simulation frameworks to model network protocols or to design and gauge network architectures, such as ns-3 [YHZ09], OMNeT++ [VH08], and ROSS [CBP00], to name but a few. Subsequently, researchers utilize these frameworks to construct modules for individual architectures or degrees of accuracy. For example, a flit-level accurate simulation model for InfiniBand [Ope07], developed by Mellanox and based on OMNeT++, is used to analyze and improve congestion control in IB

networks [Rei+11]. Similarly, Yebenes et al. [Yeb+13] tried to implement an efficient packet-level IB simulator for very large topologies used in exascale supercomputers based on OMNeT++, but only showed results for 28x28 meshes and tori. Alternatively, less accurate, but highly efficient packet-level simulations are enabled by the CODES network and storage simulator (based on ROSS) [Cop+11]. Multiple regular topologies, such as (multi-rail) fat-trees using adaptive and deterministic routings [Liu+15; Wol+17], Slim Flies [BH14; Wol+16], or tori [Mub+14] with millions of compute nodes, have been studied using the CODES simulator. Furthermore, many scientists implemented their own simulator, e.g., cycle-accurate interconnection simulator for Network-on-Chip, called BookSim [Jia+13], or the IB simulator used by Sancho et al. [San+02].

The OMNEST framework, a non-commercial version of OMNeT++, is used by Denzel et al. [Den+08; BRM12] to design a parallel network simulator, interfacing with Dimemas and Paraver, which is able to read and replay communication traces of MPI applications. Despite being a flit-level simulator, their Venus toolchain is not tailored to a specific interconnection technology, such as InfiniBand. Both, the simulated regular topologies with up to  $\approx$ 4,000 compute nodes, i.e., 2/3-dimensional mesh/torus, hierarchical full mesh, and a fat-tree, and the used forwarding rules for these networks are generated by tools comprised in the Venus toolchain. Multiple routing strategies, such as random routing, source routing, and distributed routing, have been implemented.

Chen et al. [Che+16] compares state-of-the-art and emerging topologies, e.g., single-rail 3-level fat-trees, Mellanox's Dragonfly+, and Hewlett Packard's HyperX topology [Ahn+09], etc. These network topologies are validated by means of synthetic workloads, such as nearest neighbor and all-to-all traffic patterns, and realistic application communication patterns collected for selected mini-apps. Despite assuming different routing strategies (deterministic shortest-path routing, random routing, and adaptive and Valiant-like [DT03], the authors ignored the influence of network component failures.

Jain et al. [Jai+16] evaluates the achievable performance of multi-application workloads simultaneously running on a 5-dimensional torus, dragonfly, and fa-tree topology, respectively. The authors combined the CODES framework with BigSim [Zhe+05], which allows the simulations to relay the exact communication pattern of the individual applications, as well as to model their time spend in computation phases. The implemented adaptive routing algorithms have been tailored for the specific topologies, which prevents comparisons. Furthermore, limiting the analysis to certain applications only, and limiting the switch radix to 13 ports for the torus, while allowing the fat-tree to utilize a radix of 72, might not result in generally valid conclusions with respect to the available design space for interconnection networks.

## 2.2 State-of-the-Art for Deadlock-free Routing Approaches

As outlined in Chapter 1, avoiding deadlocks in the interconnection network, induced by the routing algorithm, is one of the most crucial property of these algorithms or the underlying topology, respectively. However, not all routing algorithms, such as MinHop [Mel13] or the single-source shortest-path routing [HSL09], take deadlocks into consideration. Therefore, methods for deadlock prevention, avoidance,

and recovery for networks have been studied extensively in the past, classifiable into four categories:

- 1. Solving deadlocks through architecture features,

- 2. Analytical deadlock-prevention, either through appropriate topology design or routing,

- 3. Deadlock-preventing routings using virtual channels, and

- 4. Alternative solutions, usually inapplicable to existing architectures.

For example, for routing algorithms which basically ignore the problem, the interconnection architecture defines a packet lifetime, e.g., InfiniBand [Inf15, 12.9.8.4], as a fall back for categories 1. Clearly, the disadvantage of this approach is that it only resolves a single deadlock, which might form again and again, and decreases the achievable throughput. Furthermore, it complicates the design of networking hardware, such as switches and routes, which have to monitor and enforce packet lifetimes.

Representative routings of category 2 are essentially derivatives of Up\*/Down\* routing [Sch+91], which prohibit certain turns within the topology to avoid the creation of a routing deadlock. Alternatively, the correct combination of chosen topology and (usually) deadlock-prone routing, such as any loop-free routing on binary trees or dimension order routing on n-dimensional meshes [RR10], ensures deadlockfree transmission in the network. However, prohibiting turns, and therefore restricting the number of possible routes, increases path lengths, hence latency, and overloads nodes resulting in diminished throughput [SRD04]. The algorithms of the third category are relying on virtual channels [DS87] or virtual layers [Lys+06], respectively, and are assigning paths (partially or fully) to different virtual channels to create an acyclic and routing-induced channel dependency graph. While overcoming the path length and throughput constraints of the previous category, this approach requires more complex switch and router designs [San+02], and is potentially unbound in the number of required virtual channels [DHN11; Fli+12] to achieve deadlock-freedom. However, current interconnection hardware only supports a limited number of virtual channels (VCs). For instance, obtainable InfiniBand network components maximally support eight VCs for data traffic, called virtual lanes, while the InfiniBand standard caps the theoretically supported number to 15 data VCs and one VC for subnet management traffic [Inf15, 7.6]. The following Sections 2.2.1 and 2.2.2, as well as Table 2.1, review and summarize a subset of the wide variety of (deadlock-free) deterministic topology-aware and topology-agnostic routing algorithms, respectively.

Category 4 comprises multiple different approaches to enforce deadlock-freedom within the interconnection network. Examples are the "controller principle" [Tou80], where a global entity oversees all network components, and controls packet injection/consumption rates and the forwarding of individual packets to avoid forming a deadlock. Obviously, this approach is unsuitable for modern large-scale interconnects, as well as the latency requirements in high-performance computing. Other approaches for deadlock-freedom are usually inapplicable due to missing features of state-of-the-art network architectures, such as "destination renaming" [LFD01] which easily exceeds the available memory to store forwarding tables in the switches, or "bubble flow control" [Pue+99; WCP13] which aims at controlling the filling level of port buffers to ensure that at least on packet can be forwarded at any given time.

#### 2.2.1 Topology-aware Routing Algorithms

Many of the proposed topologies for supercomputers and other interconnected systems come with a fitting (deadlock-free) topology-aware deterministic routing. For example, Zahavi et al. [Zah10] proposed D-Mod-K routing for parallel port fat-trees. Kim et al. [KBD07] suggested dimension-order routing as a possibility for flattened butterfly NoC topologies. The randomized partially-minimal routing has been tailored for 3-dimensional meshes [RL08] to improve the worst-case throughput, but requires 2 virtual channels for deadlock-freedom. The three topology-aware routings investigated in this thesis, i.e., dimension-order routing (DOR) [RR10] for meshes, Torus-2QoS routing [Mel13], and fat-tree routing [Zah+10], will be explained further in Section 3.3. Generally, the disadvantage of topology-aware routings is their limited fault-tolerance, and therefore limited applicability to large-scale networks, where a number of faults impedes the algorithm's ability to identify the remaining graph as supported topology. However, most these algorithms calculate the deadlock-free forwarding rules for the network faster in comparison to topology-agnostic algorithms, while providing highly optimized routing for low latency and high message throughput.

#### 2.2.2 Topology-agnostic Routing Algorithms

A well-known example for algorithms avoiding to create cycles in the channel dependency graph (CDG) is the Up\*/Down\* routing [Sch+91]. Up\*/Down\* prohibits a route to use an "up" direction after a "down" directions. This approach does not necessarily use shortest paths or load-balances routes efficiently. Indeed, the root often becomes a bottleneck in practice. The algorithms UD\_DFS routing [SRD00a], L-turn routing [Koi+01] and segment-based routing (SR) [Mej+06] are based on Up\*/Down\* and try to reduce or balance the routing restrictions to increase the path balancing across the network. For network technologies where the next channel in each routing step is chosen based on the source and destination node the Multiple Up\*/Down\* routing (MUD) [LS01; Fli+02] can increase the path balancing. For similar network technologies without virtual channel support the Tree-turn routing [ZC12] or FX routing [SRD00b] can be used. For example, Tree-turn adds two more directions to the four directions used by L-turn routing, which reduces the number of prohibited turns further to increase the balancing.

Another set of algorithms breaks cycles in the channel dependency graph with virtual channels. The destination-based routing algorithms DFSSSP [DHN11] and LASH [SLT02] operate similarly in terms of breaking the cycles, i.e., searching for cycles in the CDG and moving individual paths to other virtual layers. Unfortunately, both algorithms might suffer from a limited number of available virtual channels, therefore LASH-TOR [Ske+04] enhanced LASH routing to use Up\*/Down\* in the last virtual layer if the routes in this layer form a cycle which cannot be resolved. This can result in multiple outgoing ports at a switch for a single destination, hence LASH-TOR is not a destination-based routing in the general case, and therefore inapplicable to most network architectures, especially InfiniBand.

Kinsy et al. [Kin+09] proposed two application-aware routings, called bandwidth-sensitive oblivious routing (with minimal routes) or BSOR(M). BSOR operates within the CDG to calculate the routes, while

randomly deleting edges from the CDG to form an acyclic channel dependency graph. The algorithm solves a multi-commodity flow problem, based on the demands of the application, with a mixed-integer linear programming algorithm for small networks. For large networks, BSOR uses Dijkstra's algorithm as a heuristic on a weighted and acyclic channel dependency graph for each source/destination pair to balance the application traffic. In contrast, BSORM routing calculates the routes within the network and breaks cycles afterwards, resembling the method of DFSSSP and LASH. BSOR(M) is designed for network technologies with forwarding based on source and destination, and therefore are inapplicable to InfiniBand for example. The same holds for smart routing [CKR96]. The approach of smart routing is to calculate the shortest paths and investigate the routing-induced channel dependency graph for cycles, while storing which path induced which edge in the CDG. A cycle search in the CDG subsequently cuts the edges of a cycle which minimizes the average path length after recalculating the paths inducing this edge. While smart routing can be used for technologies without virtual channels, the computational cost, which is  $\mathcal{O}((\#\text{switch})^9)$ , is to high for a practical use in large-scale networks.

**Table 2.1:** Qualitative comparison of existing topology-aware and topology-agnostic routing algorithms for supercomputers; Highlighted in red: limitations and shortcomings

| <b>t</b>                     | 37                   | T       | 1                     | j<br>= -<br>-<br>-                                     | 1.1        | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |                                     |

|------------------------------|----------------------|---------|-----------------------|--------------------------------------------------------|------------|-----------------------------------------|-------------------------------------|

| Routing                      | Network Topology     | Latency | Ihroughput            | Deadlock-Freedom                                       | #VC needed | Fault-Tolerant                          | Time Complexity"                    |

|                              |                      |         | top                   | topology-aware                                         |            |                                         |                                     |

| DOR                          | meshes               | +       | +                     | yes                                                    | 1          | no                                      | N/A                                 |

| Torus-2QoS                   | 2D/3D meshes/tori    | +       | ++                    | yes                                                    | ≥ 2        | limited                                 | N/A                                 |

| Fat-Tree                     | k-ary n-trees/XGFTs  | +       | ++                    | yes                                                    | 1          | limited                                 | N/A                                 |

|                              |                      |         | topc                  | topology-agnostic                                      |            |                                         |                                     |

| MinHop                       | arbitrary            | +       | +                     | no                                                     | Ľ          | yes                                     | $\mathscr{O}( N \cdot C )$          |

| Up*/Down*                    | arbitrary            | 1       | 1                     | yes                                                    | 1          | yes                                     | $\mathscr{O}( N \cdot C )$          |

| MUD                          | arbitrary            | ı       | ı                     | yes                                                    | $\geq 2$   | yes                                     | $\mathscr{O}( N \cdot C )$          |

| SSSP                         | arbitrary            | +       | +                     | no                                                     | 1          | yes                                     | $\mathcal{O}( N ^2 \cdot \log  N )$ |

| DFSSSP                       | arbitrary            | +       | +                     | yes*                                                   | \times 1   | yes                                     | $\mathcal{O}( N ^2 \cdot \log  N )$ |

| L-turn                       | arbitrary            | i.      | 1                     | yes                                                    | 1          | yes                                     | $\mathcal{O}( N ^3)$                |

| LASH                         | arbitrary            | +       | 1                     | yes*                                                   | ≥ 1        | yes                                     | $\mathcal{O}( N ^3)$                |

| LASH-TOR                     | arbitrary $^\dagger$ | 1       | 1                     | yes                                                    | $\geq 1$   | yes                                     | $\mathcal{O}( N ^3)$                |

| SR                           | arbitrary            | 1       | 1                     | yes                                                    | 1          | yes                                     | $\mathcal{O}( N ^3)$                |

| Smart                        | arbitrary            | i.      | +                     | yes                                                    | 1          | yes                                     | $\mathcal{O}( N ^9)$                |

| BSOR(M)                      | arbitrary $^\dagger$ | +       | ++‡                   | yes                                                    | ≥ 1        | yes                                     | N/A                                 |

|                              |                      | ve      | rsatile, topology-agr | versatile, topology-agnostic, high-performance routing | ng         |                                         |                                     |

| Novel approach <sup>\$</sup> | arbitrary            | -/+     | +/++                  | yes                                                    | <u>~</u>   | yes                                     | $\leq \mathcal{O}( N ^3)$           |

Inapplicable to current interconnection hardware, such as Infini Band, because destination-based routing criterion might be violated.

<sup>‡</sup>Requires knowledge about the bandwidth demands of the application(s) to optimize the forwarding rules.

<sup>\*</sup>Can require more virtual channels than there are available and hence renders the algorithm unusable to calculate deadlock-free routes.

<sup>\$</sup>This approach will be the subject of Chapter 6 and can be further tuned by applying the knowledge gained in Chapter 5, as outlined in the conclusion of this thesis #Time complexity to calculate all source-destination paths for the entire network I = G(N, C) consisting of |N| nodes interconnected by |C| links [DHN11; Fli+12].

# 3 Background, Assumptions, and Definitions

This chapter formalizes network-related terms, which will be used throughout the thesis to accurately design, enhance, and compare network topologies and routing algorithms. Section 3.1 defines the terms interconnection network, path, and routing function and introduces common metrics. Subsequently, Section 3.2 gives an overview of a subset of network topologies, which have been proposed for the usage in HPC systems. Furthermore, a number of modern real-world installations and their topologies will be presented. The basis operating principles of a selection of routing algorithms will be given in Section 3.3. These algorithms are used throughout the world in production supercomputers and therefore serve as reliable baselines for later comparisons.

## 3.1 Interconnection Networks and Routing Algorithms

First, and foremost, an exact characterization of the network is needed when working on network topology design, as described in Section 3.1.1. This graph-based specification, see Definition 3.1, builds the basis for subsequent terms, such as path or route and derived routing functions.

#### 3.1.1 Network-related Definitions

Within the scope of interconnection networks for high-performance computers [DYL02], the assumption is that a network is a multigraph where each pair of network devices is connected by one or more full-duplex channels (or links). These full-duplex links can be simultaneously used in opposing directions without interference or throughput degradation. Furthermore, the link capacity, i.e., the maximum achievable throughput, in the network is assumed to be uniform and constant over time.

**Definition 3.1** (Interconnection Network). An interconnection network I := G(N,C) is a connected multigraph with the node set N and multiset C of directed (multi-)channels. Nodes  $n_x \in N$  are called a terminal, if and only if there exists exactly one  $n_y$  with  $(n_y, n_x) \in C$ , otherwise  $n_x$  is called a switch. Furthermore, let  $C^* \subseteq C$  be the largest possible subset, with  $\forall c_{n_x,n_y} \in C^* : n_x, n_y$  being switches  $\in N$ , denoting the set of inter-switch links of network I.

If exact device information is required, e.g., for figures, then ordered pairs  $(n_x, n_y)$ , or  $c_{n_x, n_y}$  for short, are used, otherwise a simpler  $c_i$  notation denotes channels. In the following, S is used to denote the set of switches and the set T is used for terminals, hence  $N = S \cup T$  with  $S \cap T = \emptyset$ . Figure 3.1 shows an example network consisting of five switches and no terminal nodes. For a more precise delimitation, terminals

**Figure 3.1:** 5-node interconnection network I = G(N, C);  $N = S \cup T$  with |S| = 5, |T| = 0; Full-duplex channels C allow bi-directional, simultaneous, non-interfering transmission

can be further subdivided into *compute nodes*, executing scientific applications in the supercomputer, and *supplementary nodes*, responsible for storage, administration, etc. Nodes in the network communicate via *messages* of arbitrary length, which are transferred as a payload of one or more *network packets* from a sending node to a receiving node. The packet routes, see Definition 3.2, for all nodes to all other nodes are defined by a routing function, see Definition 3.4, within the multigraph representing the network. While the mathematical concept of cyclic paths is valid, for the remainder of the thesis the absence of cycles, or so called *routing loops* [SKC14, pp. 230-231], is required, see Definitions 3.2 and 3.4. Otherwise, since network switches or routers commonly cannot distinguish between the first or additional passes of a packet, a packet might be trapped in an infinite forwarding cycle through the network.