Technische Universität Dresden

## Characterization and Evaluation of a 6.5-kV Silicon Carbide Bipolar Diode Module

## Felipe Alejandro Hernán Filsecker Diez

Von der Fakultät Elektrotechnik und Informationstechnik der Technischen Universität Dresden

zur Erlangung des akademischen Grades eines

## Doktoringenieurs

(Dr.-Ing.)

genehmigte Dissertation

Vorsitzender: Jun. Prof. Dr.-Ing. Kambiz Jamshidi

Gutachter: Prof. Dr.-Ing. Steffen Bernet

Tag der Einreichung: 29.02.2016

Prof. Dr.-Ing. Andreas Lindemann Tag der Verteidigung: 07.12.2016

Faculty of Electrical and Computer Engineering Institute of Power Engineering, Chair of Power Electronics

# CHARACTERIZATION AND EVALUATION OF A 6.5-KV SILICON CARBIDE BIPOLAR DIODE MODULE

Felipe Filsecker

DISSERTATION

Referee Prof. Dr.-Ing. Steffen Bernet

# CONTENTS

| No | omen                                    | clature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5                                                                           |

|----|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Ac | rony                                    | ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9                                                                           |

| AŁ | ostrac                                  | ot in the second s | 11                                                                          |

| 1  | Intro                                   | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13                                                                          |

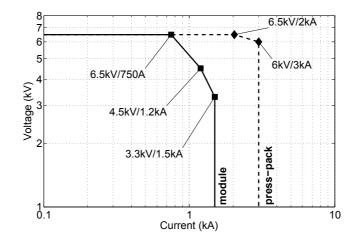

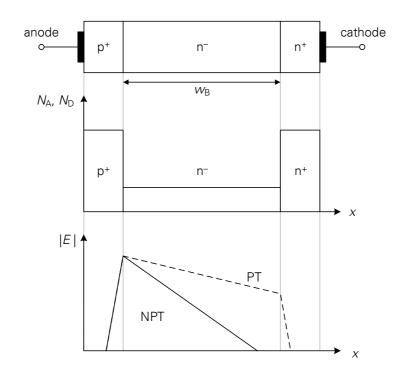

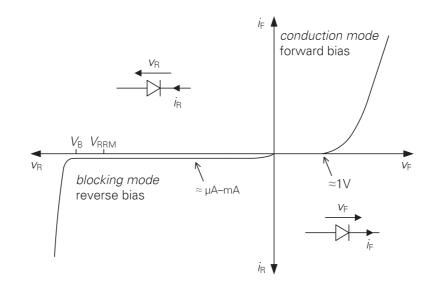

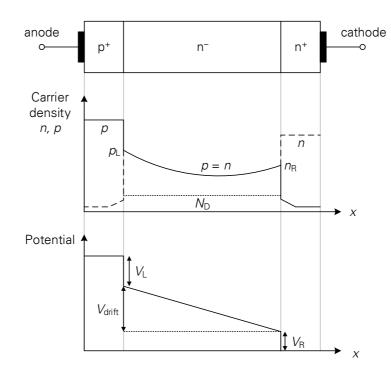

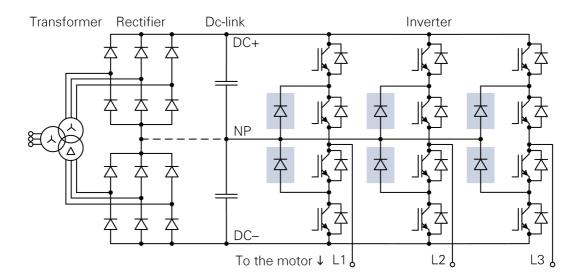

| 2  | State<br>2.1<br>2.2                     | Silicon carbide diodes and medium-voltage modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>15</b><br>16<br>20<br>23<br>25<br>25<br>27<br>34                         |

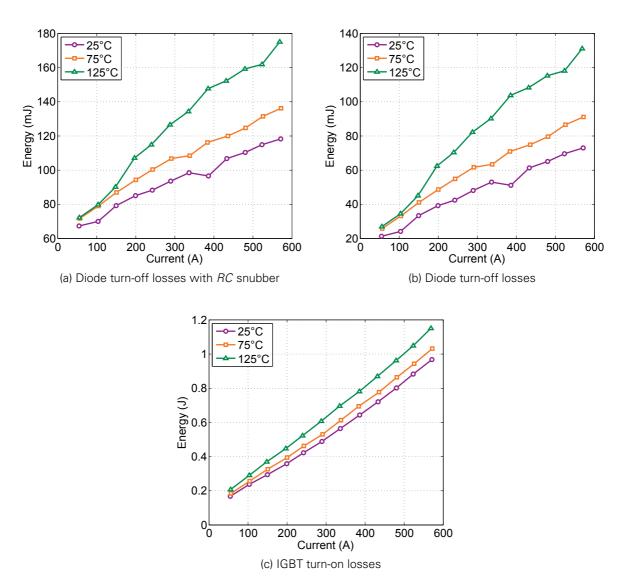

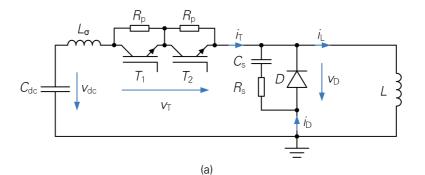

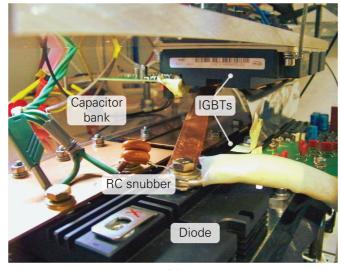

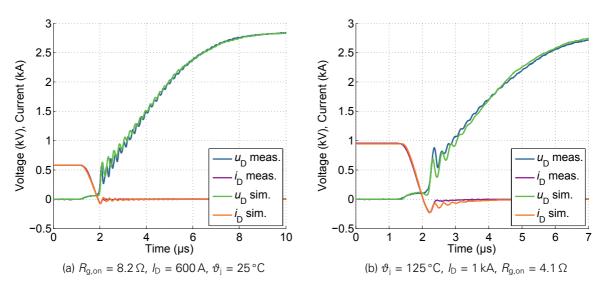

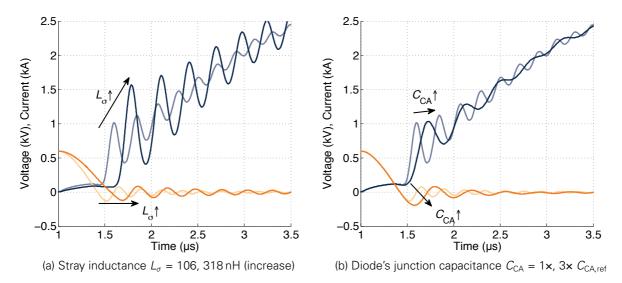

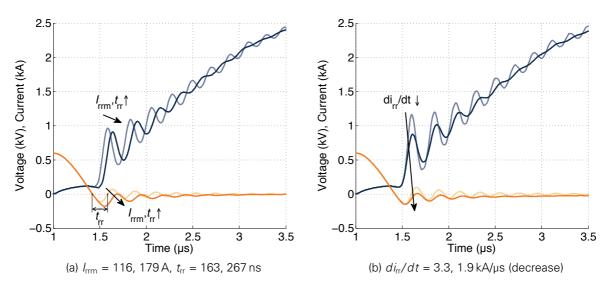

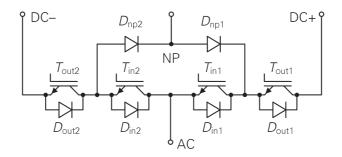

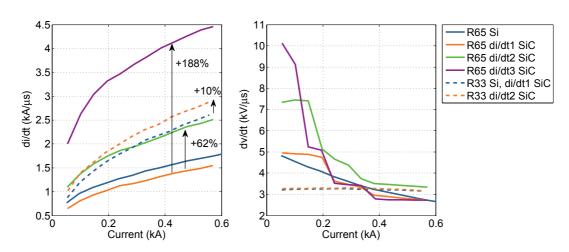

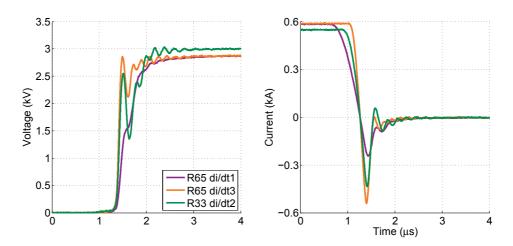

| 3  | Chai<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5 | IntroductionExperimental setup3.2.1Switching behaviour3.2.2Static behaviourExperimental results: static behaviourExperimental results: switching behaviour3.4.1Definitions and adjustments3.4.2Switching behaviour with a 6.5-kV IGBT3.4.3Switching behaviour with two 3.3-kV IGBTs in series3.5.1Diode current rating calculation3.5.2Static behaviour                                                                                                                                                                                                                                                                                                                                              | <b>37</b><br>39<br>40<br>42<br>43<br>46<br>49<br>59<br>64<br>64<br>65<br>66 |

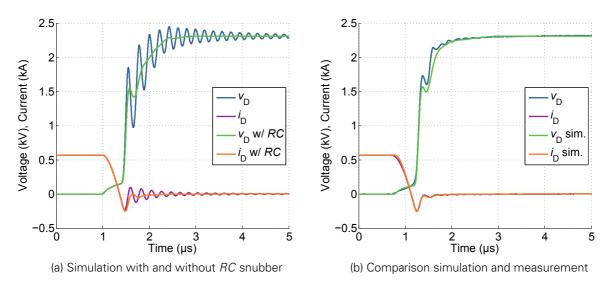

|    | 3.6                                     | <ul> <li>3.5.4 Summary</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 70<br>71<br>72<br>73<br>76                                                  |

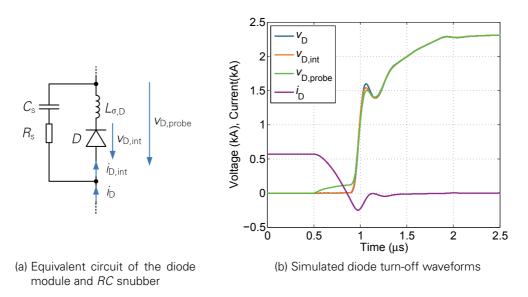

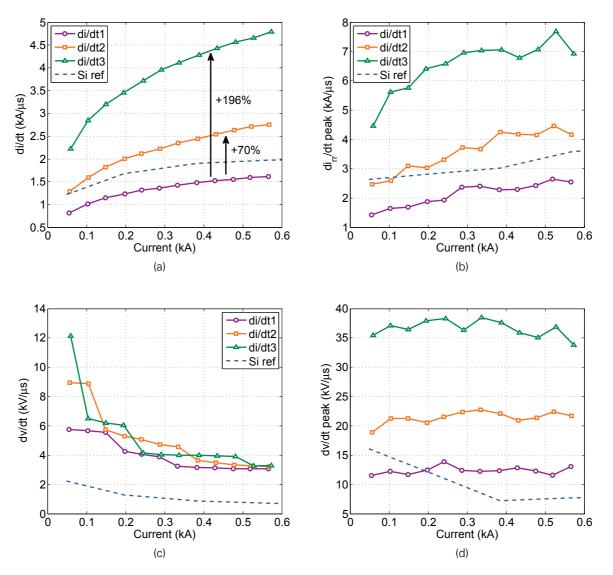

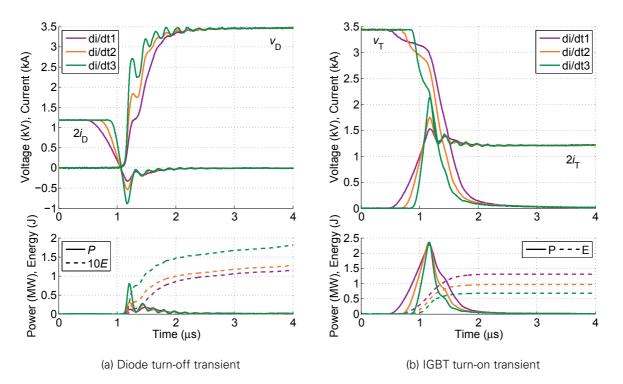

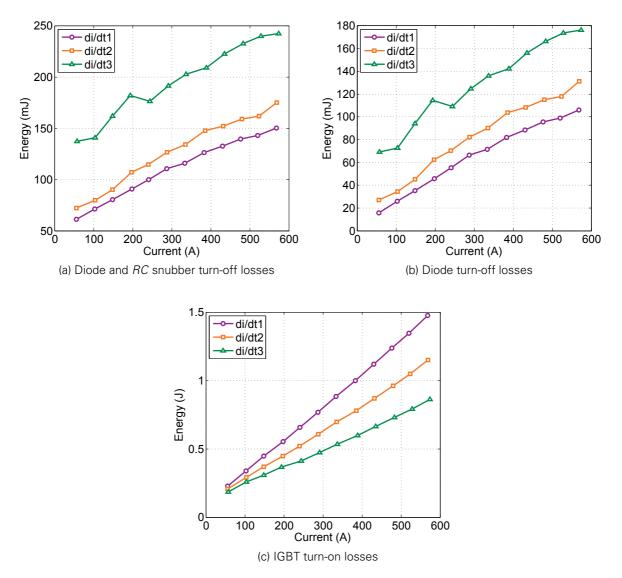

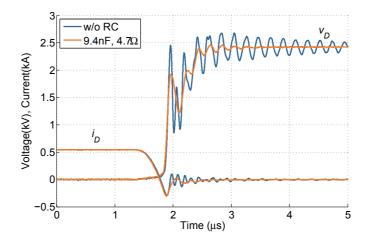

|   | 3.7 | 3.6.4<br>3.6.5 | Damping the oscillations with an RC snubber                   | 79  |

|---|-----|----------------|---------------------------------------------------------------|-----|

|   | 3.7 | Summ           | Idi y                                                         | 00  |

| 4 | Con | npariso        | n at converter level                                          | 83  |

|   | 4.1 | Introd         | uction                                                        | 83  |

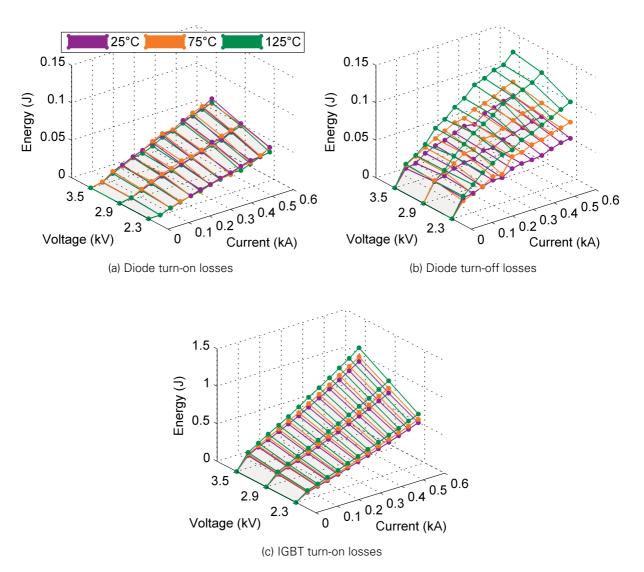

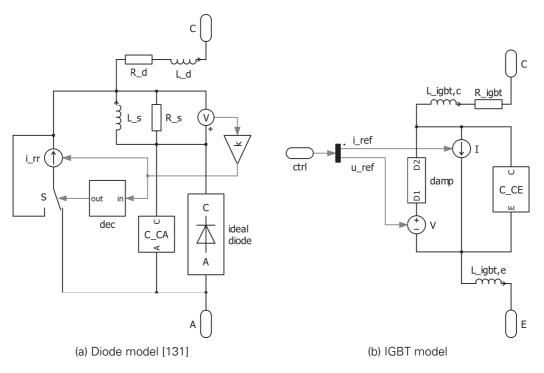

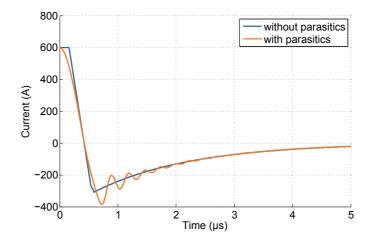

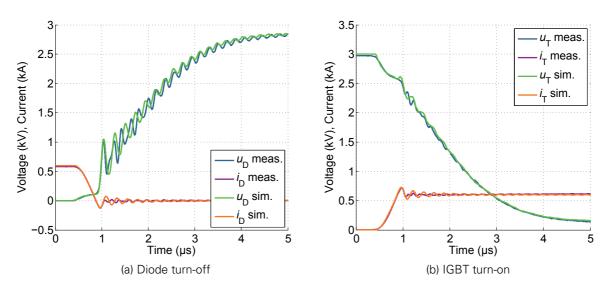

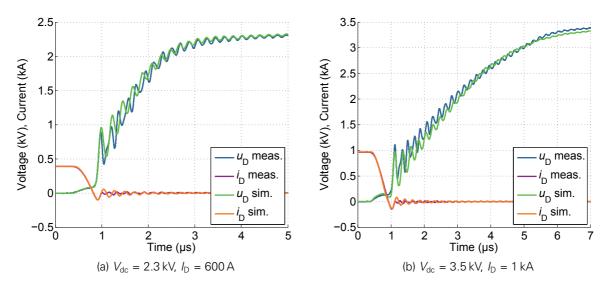

|   | 4.2 | Power          | device modelling                                              | 84  |

|   | 4.3 | Deterr         | mination of maximum converter power rating                    | 87  |

|   | 4.4 | Analys         | sis                                                           | 88  |

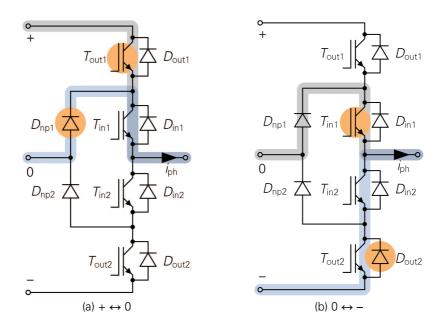

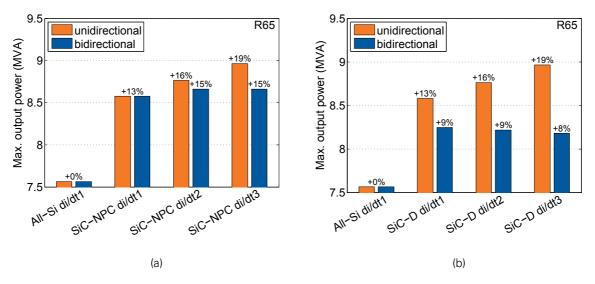

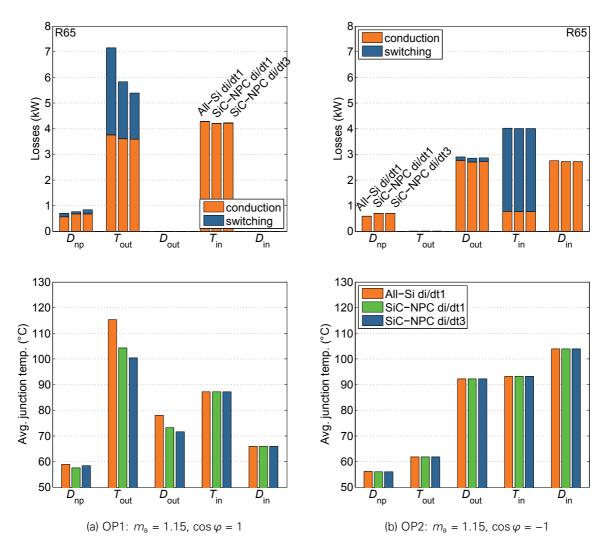

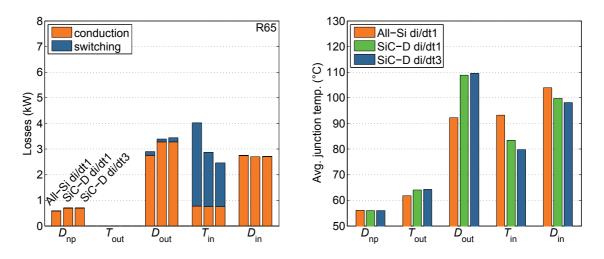

|   |     | 4.4.1          | SiC diode as NP diode with 6.5-kV IGBTs (R65 SiC-NPC)         | 89  |

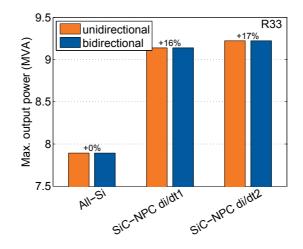

|   |     | 4.4.2          | SiC diode as antiparallel diode with 6.5-kV IGBTs (R65 SiC-D) | 91  |

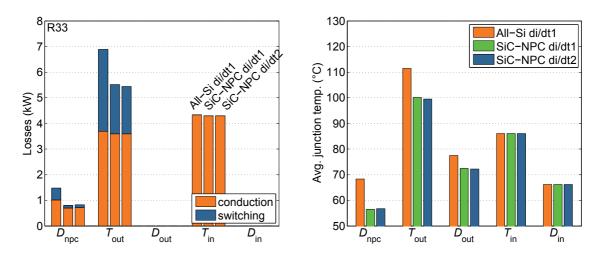

|   |     | 4.4.3          | SiC NP diode with 3.3-kV Si IGBTs (R33 SiC-NPC)               | 93  |

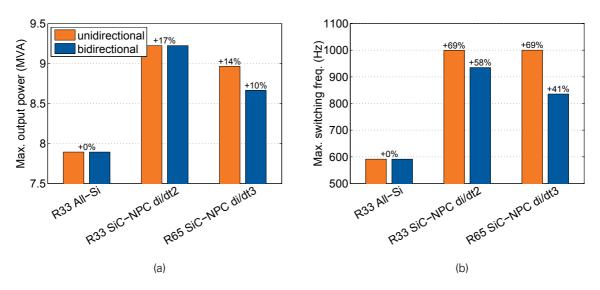

|   |     | 4.4.4          | Best semiconductor device configurations                      | 94  |

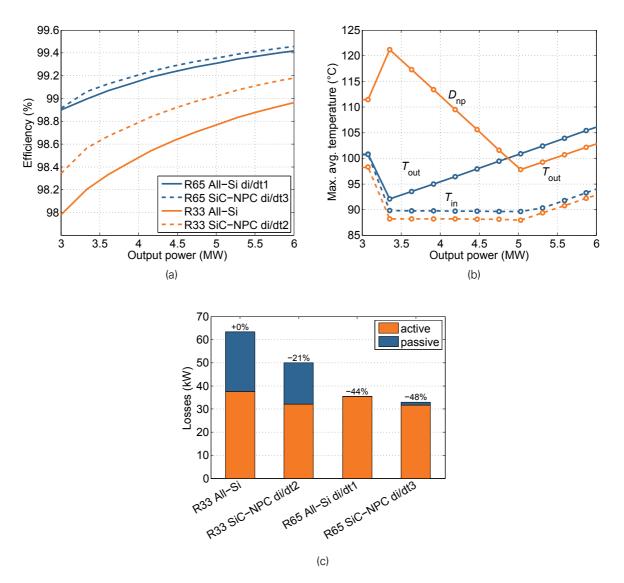

|   |     | 4.4.5          | Efficiency                                                    | 95  |

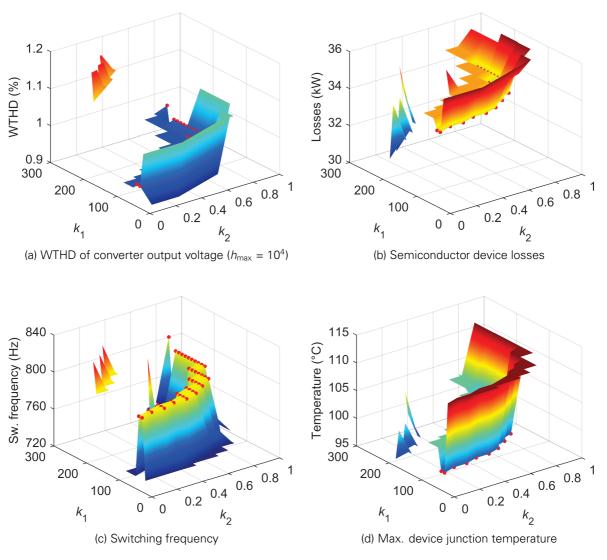

|   | 4.5 | Increa         | sed efficiency through model predictive control               | 96  |

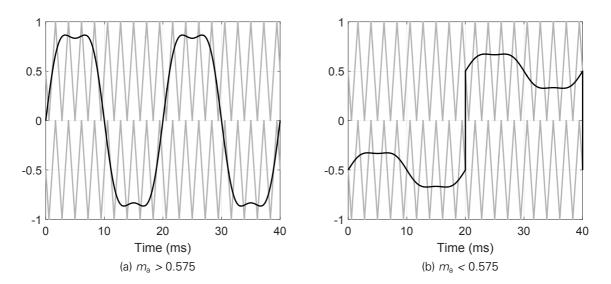

|   |     | 4.5.1          | MPC algorithm and models                                      | 97  |

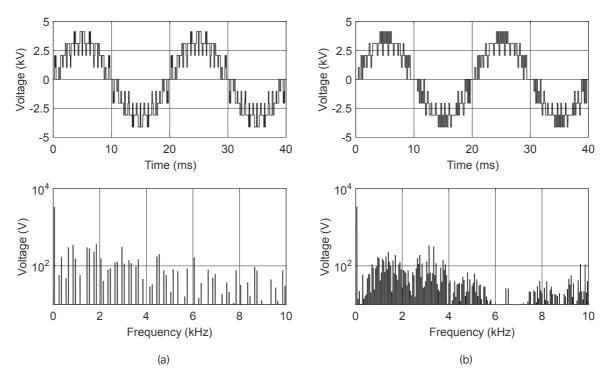

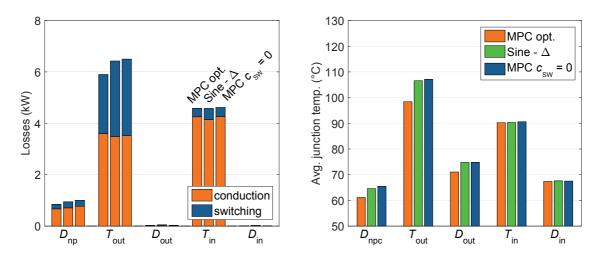

|   |     | 4.5.2          | Simulation results                                            | 98  |

|   | 4.6 | Summ           | nary                                                          | 102 |

| 5 | Con | clusior        | 1                                                             | 105 |

# NOMENCLATURE

A Area of the device

| C                                                                                                                                 | Cost function                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C <sub>C</sub> A                                                                                                                  | Diode's cathode-anode capacitance                                                                                                                                                                                                                                                                                                                                                          |

| C <sub>C</sub> A,ref                                                                                                              | Diode's reference cathode-anode capacitance                                                                                                                                                                                                                                                                                                                                                |

| C <sub>dc</sub>                                                                                                                   | DC-link capacitance                                                                                                                                                                                                                                                                                                                                                                        |

| C <sub>j</sub>                                                                                                                    | Junction capacitance                                                                                                                                                                                                                                                                                                                                                                       |

| C <sub>s</sub>                                                                                                                    | <i>RC</i> snubber capacitance                                                                                                                                                                                                                                                                                                                                                              |

| C <sub>sw</sub>                                                                                                                   | Cost factor that evaluates the switching events in the MPC algorithm                                                                                                                                                                                                                                                                                                                       |

| D                                                                                                                                 | Diode symbol in the equivalent circuits                                                                                                                                                                                                                                                                                                                                                    |

| D <sub>in</sub>                                                                                                                   | Inner diodes in an NPC converter                                                                                                                                                                                                                                                                                                                                                           |

| D <sub>np</sub>                                                                                                                   | Neutral point diodes in an NPC converter                                                                                                                                                                                                                                                                                                                                                   |

| D <sub>out</sub>                                                                                                                  | Outer diodes in an NPC converter                                                                                                                                                                                                                                                                                                                                                           |

| di <sub>rr</sub> /dt                                                                                                              | Diode's reverse recovery current change rate after I <sub>rrm</sub>                                                                                                                                                                                                                                                                                                                        |

| E<br>E <sub>C</sub><br>E <sub>D,int,off</sub><br>E <sub>D,int,on</sub><br>E <sub>D,off</sub><br>E <sub>g</sub><br>E <sub>sw</sub> | Electric field<br>Critical electric field strength<br>Stored energy in the snubber capacitor <i>C</i> <sub>s</sub><br>Turn-off losses in the diode itself (no additional <i>RC</i> snubber losses)<br>Turn-on losses in the diode itself (no additional <i>RC</i> snubber losses)<br>Turn-off losses in the diode (including <i>RC</i> snubber if present)<br>Band gap<br>Switching losses |

| f <sub>c</sub>                                                                                                                    | Cut-off frequency                                                                                                                                                                                                                                                                                                                                                                          |

| f <sub>r</sub>                                                                                                                    | Resonant frequency in <i>RLC</i> circuit                                                                                                                                                                                                                                                                                                                                                   |

| f <sub>s</sub>                                                                                                                    | Sampling frequency of the MPC algorithm                                                                                                                                                                                                                                                                                                                                                    |

| f <sub>sw</sub>                                                                                                                   | Switching frequency (carrier signal frequency in PWM)                                                                                                                                                                                                                                                                                                                                      |

| G                                                                                                                                 | Time-continuous transfer function                                                                                                                                                                                                                                                                                                                                                          |

| h                                                                                                                                 | Harmonic of order <i>h</i>                                                                                                                                                                                                                                                                                                                                                                 |

| h <sub>max</sub>                                                                                                                  | Maximum harmonic order considered for the WTHD calculation                                                                                                                                                                                                                                                                                                                                 |

| I <sub>D</sub>                                                                                                                    | Diode current                                                                                                                                                                                                                                                                                                                                                                              |

| i <sub>D</sub><br>i <sub>D,int</sub><br>i <sub>E</sub><br>i <sub>H</sub><br>i <sub>L</sub><br>i <sub>L</sub><br>i <sub>L</sub><br>i <sub>L</sub><br>i <sub>L</sub><br>i <sub>D</sub><br>i <sub>T</sub><br>i <sub>s</sub><br>i <sub>T</sub> | Diode current (time dependent)<br>Diode current excluding the <i>RC</i> snubber current (time dependent)<br>Electron recombination current<br>Diode forward current<br>Hole recombination current<br>Load current (space vector)<br>Load current<br>Load current (time dependent)<br>Converter output current (rms value)<br>Phase current<br>Reference current in the MPC algorithm (space vector)<br>Diode's reverse recovery current maximum value<br><i>RC</i> snubber current (time dependent)<br>IGBT current (time dependent) |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $J_{F}$                                                                                                                                                                                                                                    | Diode forward current density                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| k                                                                                                                                                                                                                                          | Current sampling instance in the MPC algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| k <sub>B</sub>                                                                                                                                                                                                                             | Boltzmann constant (1.38066×10 <sup>-23</sup> J/K)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| k <sub>drift</sub>                                                                                                                                                                                                                         | Proportionality constant relating V <sub>drift</sub> and J <sub>F</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| L                                                                                                                                                                                                                                          | Load inductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| L <sub>σ</sub>                                                                                                                                                                                                                             | Stray inductance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| L <sub>σ,D</sub>                                                                                                                                                                                                                           | Stray inductance inside the diode module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| m                                                                                                                                                                                                                                          | Number of switching states in a converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| m <sub>a</sub>                                                                                                                                                                                                                             | Modulation index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| N                                                                                                                                                                                                                                          | Time horizon in model predictive control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| n                                                                                                                                                                                                                                          | Electron density                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| N <sub>D</sub>                                                                                                                                                                                                                             | Donor doping density                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| n <sub>i</sub>                                                                                                                                                                                                                             | Intrinsic carrier density                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| n <sub>R</sub>                                                                                                                                                                                                                             | Electron density near the nn <sup>+</sup> junction in a PiN diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Ρ                                                                                                                                                                                                                                          | Average hole density                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| p                                                                                                                                                                                                                                          | Hole density                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P <sub>L</sub>                                                                                                                                                                                                                             | Hole density near the p <sup>+</sup> n junction in a PiN diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P <sub>tot,sc</sub>                                                                                                                                                                                                                        | Total semiconductor device losses (conduction and switching)                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P <sub>cond</sub>                                                                                                                                                                                                                          | Conduction losses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| q                                                                                                                                                                                                                                          | Elementary charge (1.60218×10 <sup>19</sup> As)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Q                                                                                                                                                                                                                                          | Charge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Q <sub>F</sub>                                                                                                                                                                                                                             | Stored charge of the PiN diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| R                                                                                                                                                                                                                                          | Load resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| R <sub>ho</sub>                                                                                                                                                                                                                            | High-ohmic resistance for the estimation of $C_j$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| R <sub>g,on</sub>                                                                                                                                                                                                                          | IGBT's gate drive unit turn-on resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| R <sub>p</sub>                                                                                                                                                                                                                             | Parallel resistance for static voltage balancing of series-connected IGBTs                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| R <sub>s</sub>                                                                                                                                                                                                                             | <i>RC</i> snubber resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| R <sub>th,ch</sub>                                                                                                                                                                                                                         | Thermal resistance, case to heat sink                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| R <sub>th,ha</sub>                                                                                                                                                                                                                         | Thermal resistance, heat sink to ambient                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| R <sub>th,jc</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Thermal resistance, junction to case                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R <sub>th,jh</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Thermal resistance, junction to heat sink                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Laplace variable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| S <sub>C</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Converter power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IGBT symbol in the equivalent circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| T <sub>in</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Inner IGBTs in an NPC converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| T <sub>out</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Outer IGBTs in an NPC converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| t <sub>rr</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Diode's reverse recovery current duration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>B</sub><br>V <sub>C</sub><br>V <sub>D</sub> ,int<br>V <sub>D</sub> ,int<br>V <sub>dc</sub><br>V <sub>dc</sub><br>V <sub>dc</sub><br>V <sub>dc</sub><br>V <sub>dc</sub><br>V <sub>drift</sub><br>V <sub>F</sub><br>V <sub>F</sub><br>V <sub>j</sub><br>V <sub>L</sub><br>V <sub>out</sub><br>V <sub>R</sub><br>V <sub>R</sub> RM<br>V <sub>T</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Breakdown voltage<br>Voltage of the snubber capacitor (time-dependent)<br>Converter output voltage (space vector)<br>Diode's anode-cathode voltage<br>Diode's anode-cathode internal voltage in the device simulation model (time dependent)<br>Diode's anode-cathode voltage (time dependent)<br>DC-link voltage<br>DC-link voltage (time dependent)<br>Diode's anode-cathode voltage at the module terminals, including internal stray induct-<br>ance (time dependent)<br>Drift zone voltage<br>Diode forward voltage<br>Diode forward voltage (time dependent)<br>Junction voltage<br>Voltage of the p <sup>+</sup> n junction in a PiN diode<br>Converter output phase voltage<br>Voltage of the nn <sup>+</sup> junction in a PiN diode<br>Reverse repetitive maximum voltage<br>IGBT collector-emitter voltage |

| W <sub>B</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Width of the lightly doped, middle region in a PiN diode (base)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| W <sub>SCR</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Width of the space charge region                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| $egin{aligned} \epsilon_0 \ \epsilon_{ m r} \ \mu_{ m n} \ \mu_{ m p} \ arphi \ arphi_{ m H} \ arphi_{ m d} \ arphi_{ m h} \ arphi_{ m j} \ arphi_{ m j} \ arphi_{ m j} \ arphi_{ m j,max} \ arkappa \ arphi \ $ | Vacuum permittivity (8.854 $\times$ 10 <sup>-12</sup> F/m)<br>Relative permittivity<br>Electron mobility<br>Hole mobility<br>Phase angle between the fundamental components of voltage and current<br>Carrier lifetime at high-level injection<br>Temperature<br>Heat sink temperature<br>Junction temperature<br>Maximum junction temperature<br>Damping factor in <i>RLC</i> circuit                                                                                                                                                                                                                                                                                                                                                                                                                                |

## ACRONYMS

- 3L three level

- AMB active metal brazing

- BJT bipolar junction transistor

- BPD basal plane dislocation

- DBC direct bonded copper

- EMI electromagnetic interference

- ESL equivalent series inductance

- ESR equivalent series resistance

- FEM finite element method

- GDU gate drive unit

- IEGT injection-enhanced gate transistor

- IGBT insulated-gate bipolar transistor

- IGBT3 third generation IGBT

- IGCT integrated gate-commutated thyristor

- JBS junction barrier Schottky

- JFET junction gate field-effect transistor

- JTE junction termination extension

- MOSFET metal-oxide-semiconductor field-effect transistor

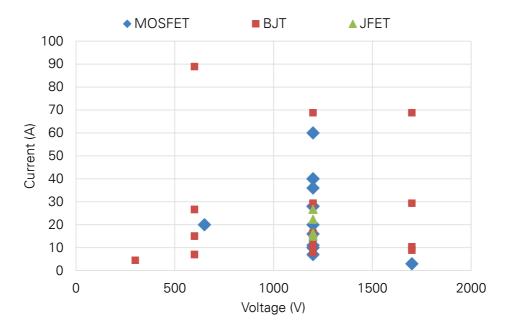

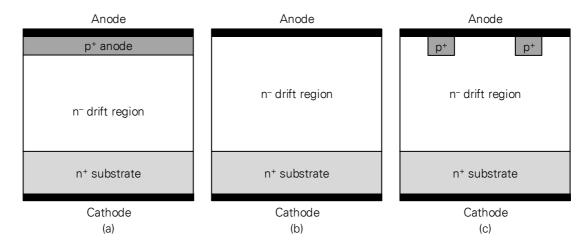

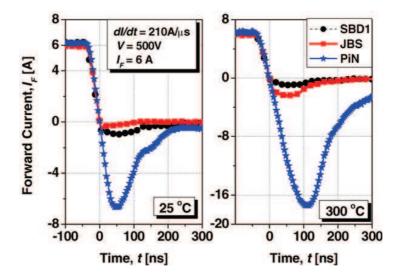

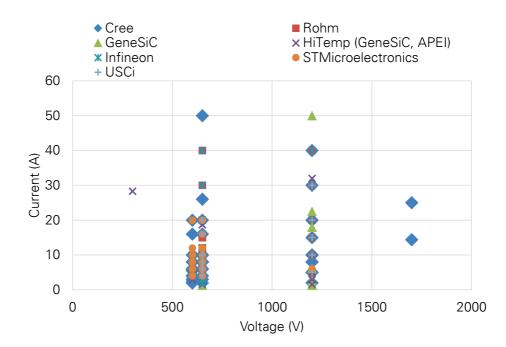

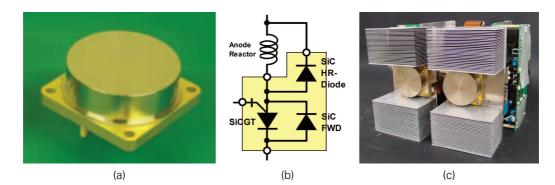

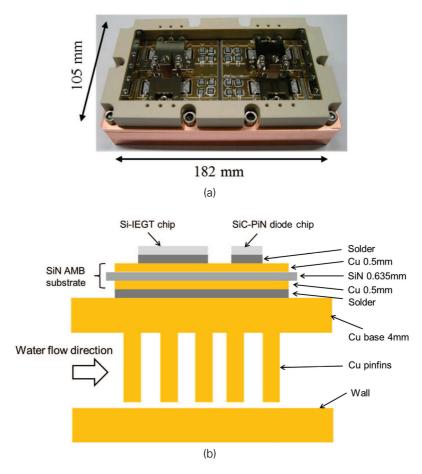

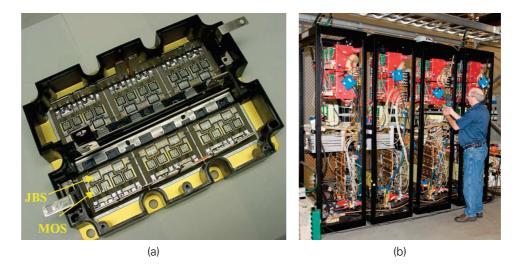

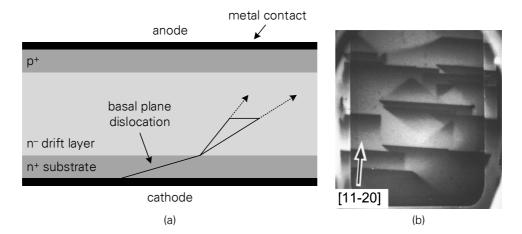

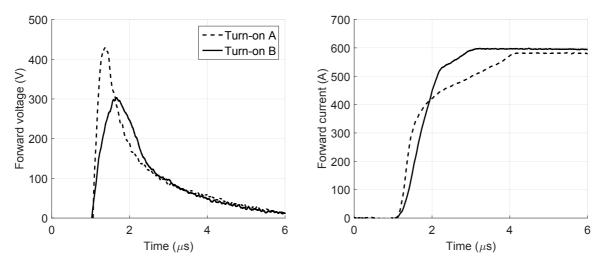

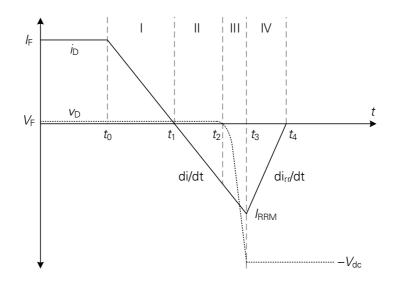

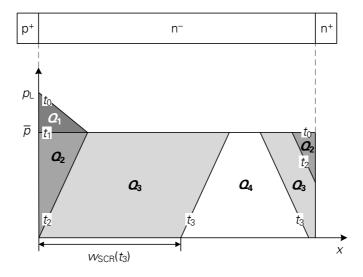

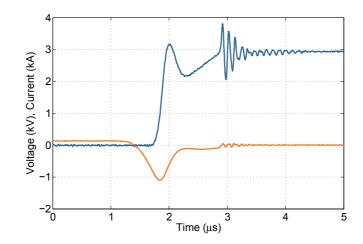

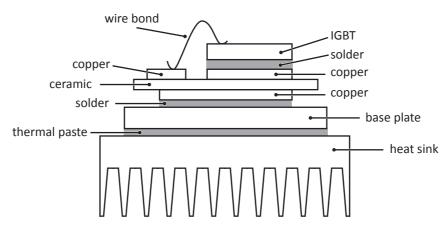

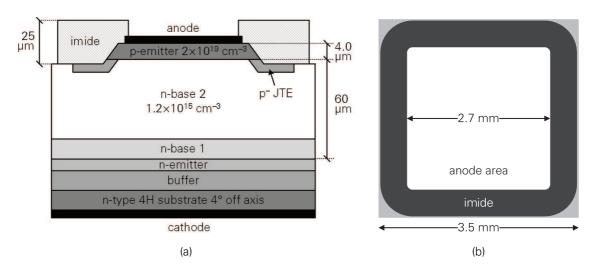

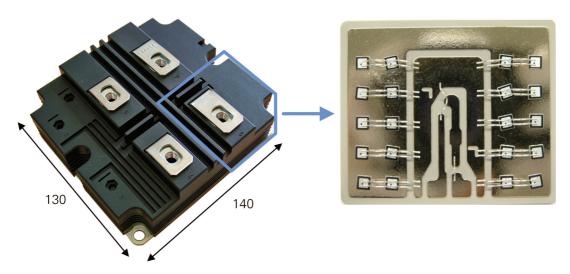

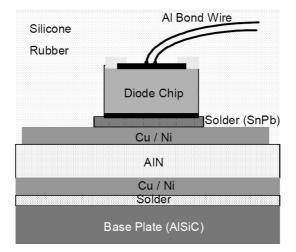

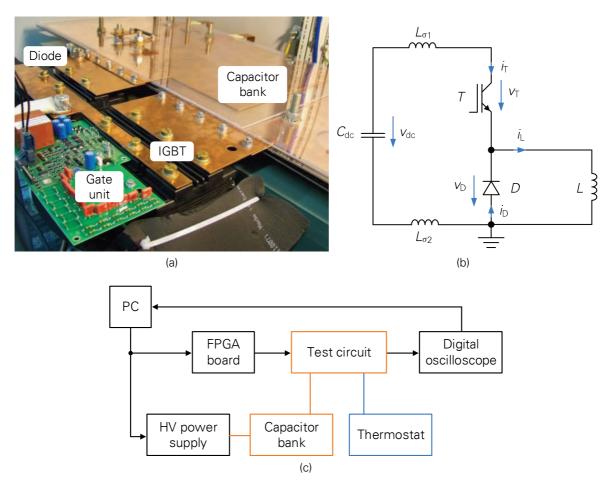

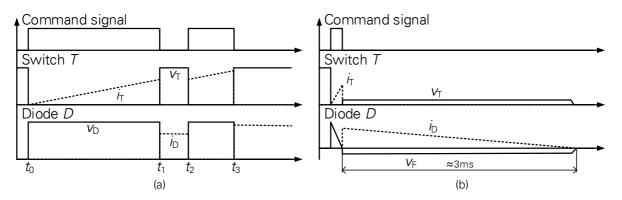

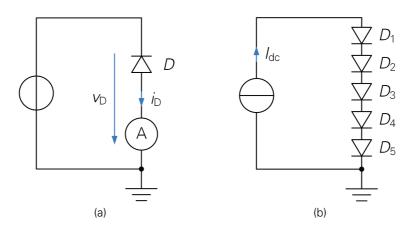

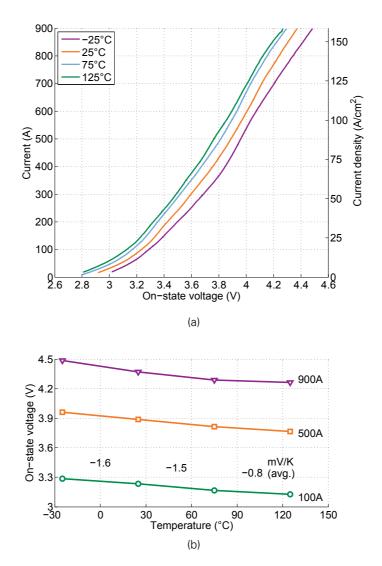

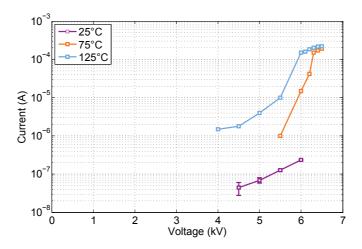

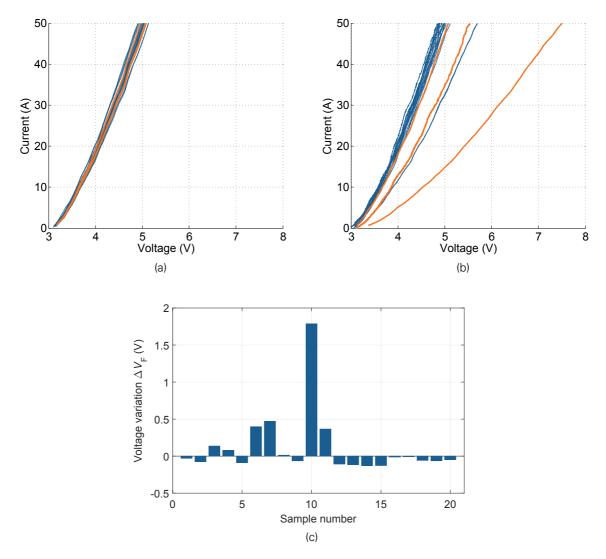

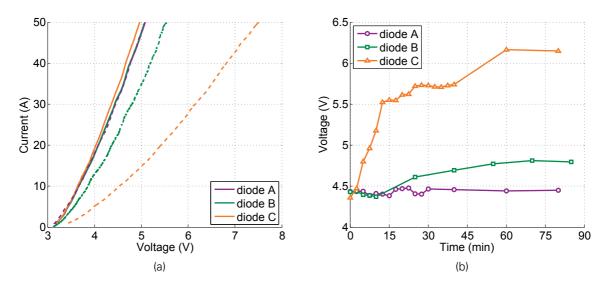

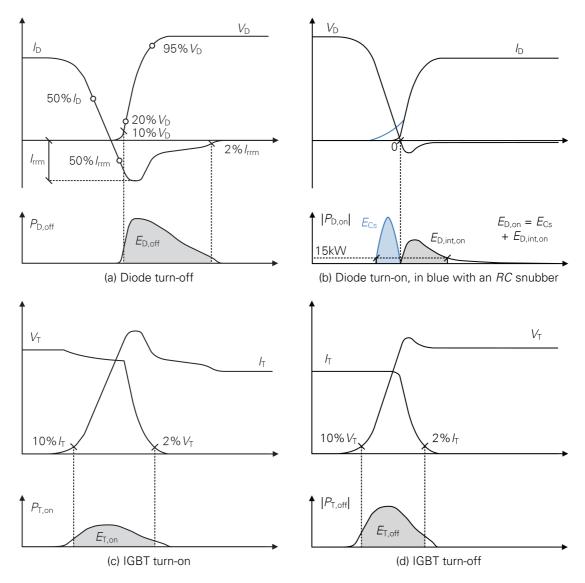

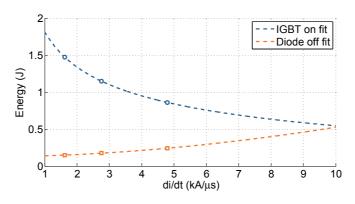

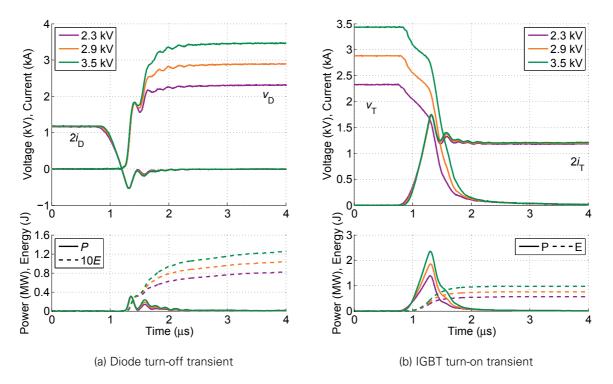

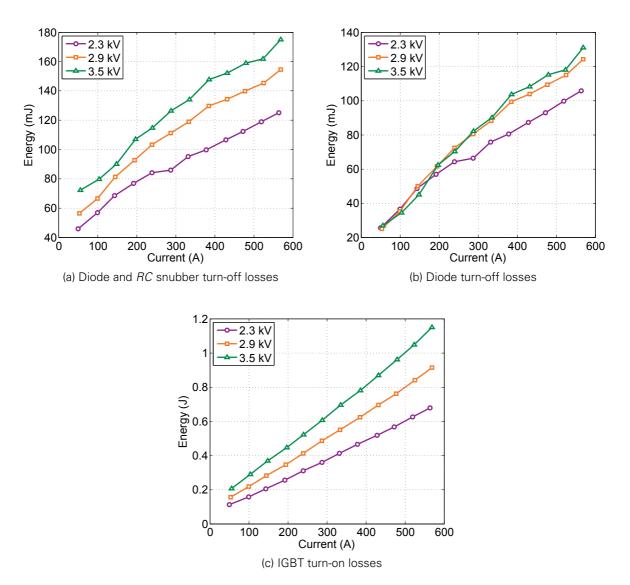

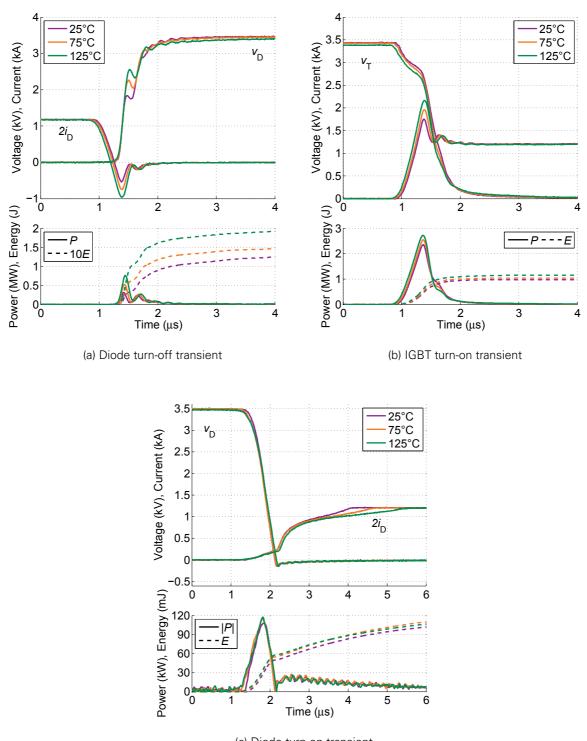

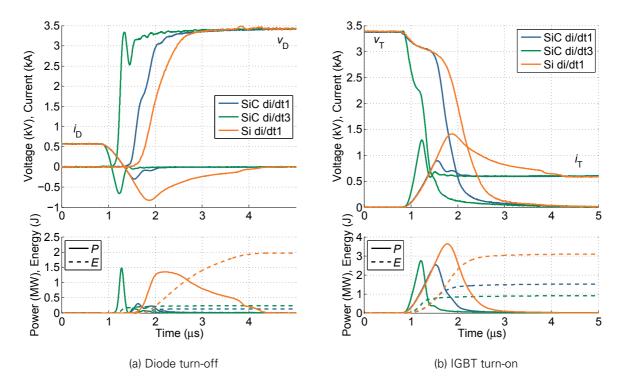

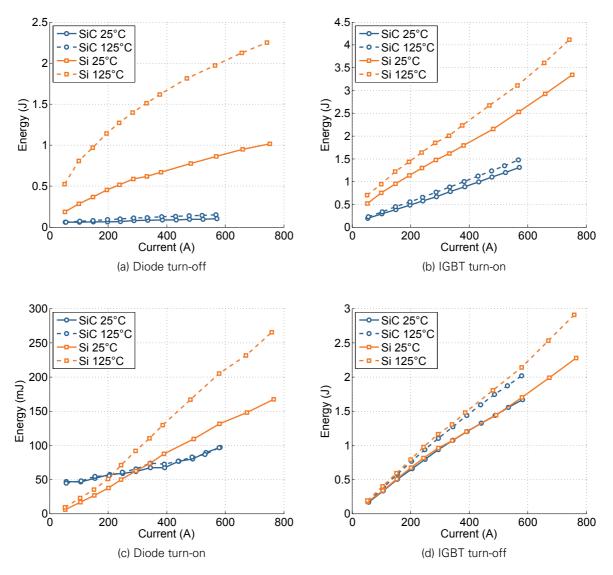

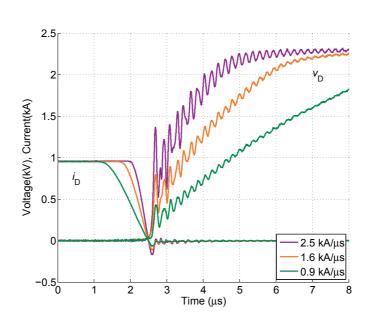

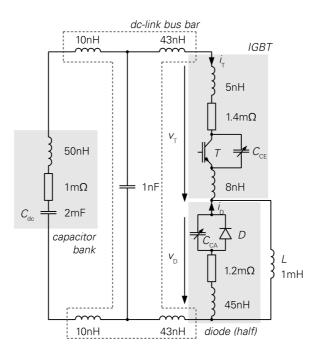

- MPC model predictive control