# Hardware Error Detection Using AN-Codes

#### Dissertation

zur Erlangung des akademischen Grades Doktoringenieur (Dr.-Ing.)

vorgelegt an der TECHNISCHEN UNIVERSITÄT DRESDEN FAKULTÄT INFORMATIK

eingereicht von

Dipl.-Inf. Ute Schiffel

geboren am 08.07. 1980 in Sebnitz

Gutachter: Prof. Christof Fetzer, PhD,

Technische Universität Dresden

Prof. Dr. Wolfgang Ehrenberger,

Hochschule Fulda

Datum der Verteidigung: 20. Mai 2011

Dresden, den 10.06.2011

# **Abstract**

Due to the continuously decreasing feature sizes and the increasing complexity of integrated circuits, commercial off-the-shelf (COTS) hardware is becoming less and less reliable. However, dedicated reliable hardware is expensive and usually slower than commodity hardware. Thus, economic pressure will most likely result in the usage of unreliable COTS hardware in safety-critical systems.

The usage of unreliable, COTS hardware in safety-critical systems results in the need for software-implemented solutions for handling execution errors caused by this unreliable hardware. In this thesis, we provide techniques for detecting hardware errors that disturb the execution of a program. The detection provided facilitates handling of these errors, for example, by retry or graceful degradation.

We realize the error detection by transforming unsafe programs that are not guaranteed to detect execution errors into safe programs that detect execution errors with a high probability. Therefore, we use arithmetic AN-, ANB-, ANBD-, and ANBDmem-codes. These codes detect errors that modify data during storage or transport *and* errors that disturb computations as well. Furthermore, the error detection provided is independent of the hardware used.

We present the following novel encoding approaches:

- Software Encoded Processing (SEP) that transforms an unsafe binary into a safe execution at runtime by applying an ANB-code, and

- Compiler Encoded Processing (CEP) that applies encoding at compile time and provides different levels of safety by using different arithmetic codes.

In contrast to existing encoding solutions, SEP and CEP allow to encode applications whose data and control flow is not completely predictable at compile time.

For encoding, SEP and CEP use our set of encoded operations also presented in this thesis. To the best of our knowledge, we are the first ones that present the encoding of a complete RISC instruction set including boolean and bitwise logical operations, casts, unaligned loads and stores, shifts and arithmetic operations.

Our evaluations show that encoding with SEP and CEP significantly reduces the amount of erroneous output caused by hardware errors. Furthermore, our evaluations show that, in contrast to replication-based approaches for detecting errors, arithmetic encoding facilitates the detection of permanent hardware errors. This increased reliability does not come for free. However, unexpectedly the runtime costs for the different arithmetic codes supported by CEP compared to redundancy increase only *linearly*, while the gained safety increases *exponentially*.

# Für Arthur 💢

Es weht der Wind ein Blatt vom Baum, von vielen Blättern eines.

Das eine Blatt, man merkt es kaum, denn eines ist ja keines.

Doch dieses eine Blatt allein, war Teil von unsrem Leben.

Drum wird uns dieses Blatt allein, für immer, immer fehlen.

Hermann Hesse

# **Acknowledgments**

Over the last years many people helped me to complete this thesis. Now, it is time to thank them for their support.

My advisor Christof Fetzer always believed in encoding – even when I did not. He was always open for discussions and an endless source of ideas. His constant request: "You could publish at conference XYZ." ensured a steady progress of my work. Thank you.

My colleagues at the chair for Systems Engineering at TU Dresden provided a friendly and enjoyable working environment. They were always open for discussing ideas, problems and gave lots of feedback on paper drafts and presentations. I especially thank, Martin Süßkraut whose ideas and suggestions considerably helped to improve the Encoding Compiler and this thesis, which he proof-read from the first to the very last page, André Schmitt who transformed my ideas for the ANB-encoding Compiler into a compiler pass during his diploma thesis, Thomas Knauth who implemented the list- and tree-based version management, Gert Pfeifer who had always time for me: either for just listening or for explaining some interesting P2P or DNS technique, Andrey Brito on whom I could count on to drop by on these long evenings before a paper deadline, Martin Nowack who proof-read the short version of this thesis, and Claudia Einer and Karina Wauer who helped me to survive in an otherwise women-free work environment.

Special thanks go to my husband Stephan. He endlessly discussed problems and possible solutions with me, he proof-read this thesis, and supported me wherever he could.

Und zu guter Letzt: Danke meine lieben Eltern, daß Ihr mich immer unterstützt und gefördert habt und auch heute noch für Stephan und mich da seid und alle unsere Vorhaben mit Ratschlägen und Hilfe begleitet.

# **Contents**

| Co | Contents |                      |                                                                               |      |  |

|----|----------|----------------------|-------------------------------------------------------------------------------|------|--|

| 1. | Intro    | oduction             |                                                                               | 1    |  |

| 2. | Relia    | ability of Hardward  | e                                                                             | 7    |  |

|    | 2.1.     | Terminology          |                                                                               | . 7  |  |

|    | 2.2.     | Causes and Effect    | ts of Hardware Errors                                                         | . 8  |  |

|    |          | 2.2.1. Causes for    | Increasing Unreliability of Hardware                                          | . 8  |  |

|    |          | 2.2.2. (Un)Reliab    | bility of Hardware                                                            | . 11 |  |

|    | 2.3.     | Impact of Hardwa     | are Errors                                                                    | . 14 |  |

|    | 2.4.     | Conclusions from     | the State of Hardware Reliability                                             | . 15 |  |

|    | 2.5.     | Software-level Syr   | mptoms of Hardware Errors                                                     | . 16 |  |

| 3. | Arit     | nmetic Codes         |                                                                               | 19   |  |

|    | 3.1.     | Berger Code          |                                                                               | . 21 |  |

|    | 3.2.     | Residue Codes .      |                                                                               | . 23 |  |

|    | 3.3.     | AN-Codes             |                                                                               | . 26 |  |

|    |          | 3.3.1. Error Corn    | recting AN-Codes                                                              | . 29 |  |

|    |          | 3.3.2. Systematic    | c AN-Codes                                                                    | . 30 |  |

|    |          | 3.3.3. $ gAN _M$ C   | Code                                                                          | . 31 |  |

|    |          | 3.3.4. Conclusion    | ns for AN-Codes                                                               | . 33 |  |

|    | 3.4.     | ANB-Codes            |                                                                               | . 33 |  |

|    | 3.5.     | ANBD-Codes           |                                                                               | . 35 |  |

|    | 3.6.     | Comparison of the    | e Codes                                                                       | . 36 |  |

| 4. | Enc      | oding an Instruction | on Set                                                                        | 39   |  |

|    | 4.1.     | Implementation o     | of Encoding and Decoding                                                      | . 40 |  |

|    |          | 4.1.1. Provided I    | $Functions \dots \dots$ | . 41 |  |

|    |          | 4.1.2. Encoding      |                                                                               | . 42 |  |

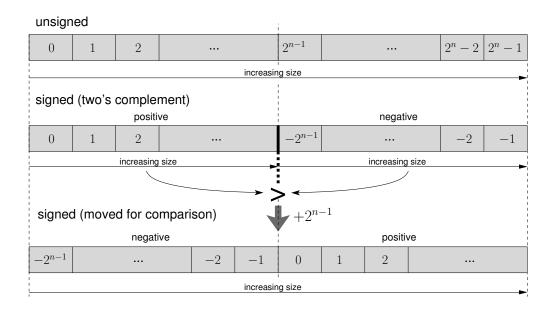

|    |          | 4.1.3. Conversion    | n: Signed Encoded $\leftrightarrows$ Unsigned Encoded                         | . 44 |  |

|    |          | 4.1.4. Decoding      |                                                                               | . 46 |  |

|    | 4.2.     | Encoded Operation    | ons                                                                           | . 46 |  |

|    |          | 4.2.1. Encoded B     | Base Operations                                                               | . 47 |  |

|    |          | 4.2.2. Encodable     | e Replacement Operations                                                      | . 74 |  |

|    |          | 4.2.3. Floating P    | Point Operations                                                              | . 79 |  |

|    | 4.3.     | Encoded Constan      | its                                                                           | . 80 |  |

x Contents

|    | 4.4. | Calls to External Libraries                                          |

|----|------|----------------------------------------------------------------------|

|    | 4.5. | Encoded Data and Control Flow                                        |

|    | 4.6. | Encoding Dynamic Memory Access                                       |

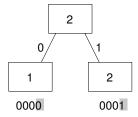

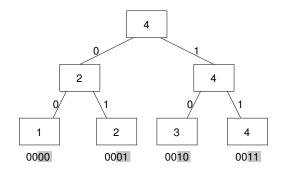

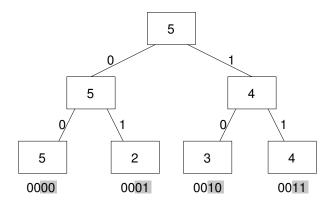

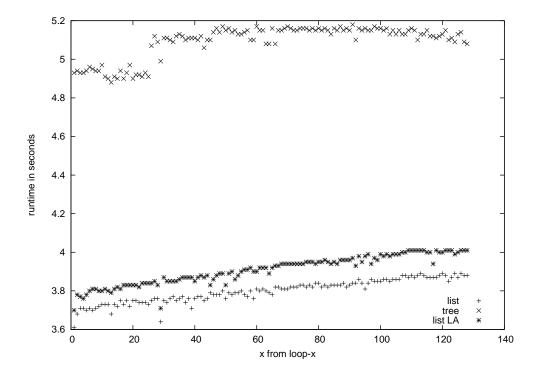

|    | 4.7. | Version Management                                                   |

|    |      | 4.7.1. The List                                                      |

|    |      | 4.7.2. The Tree                                                      |

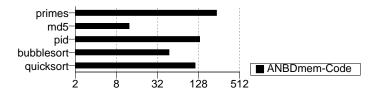

|    |      | 4.7.3. Performance Evaluation                                        |

|    | 4.8. | Outlook:                                                             |

|    |      | Application of Encoded Basic Building Blocks 90                      |

| 5. | Cho  | ice of Encoding Parameters 93                                        |

|    | 5.1. | Choice of A                                                          |

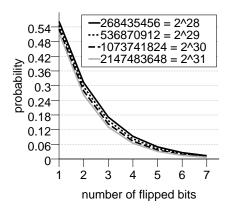

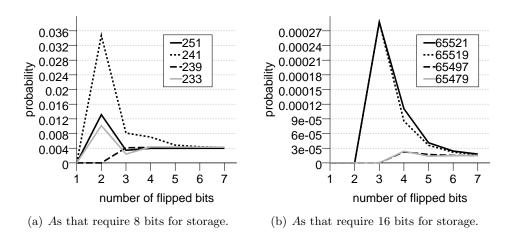

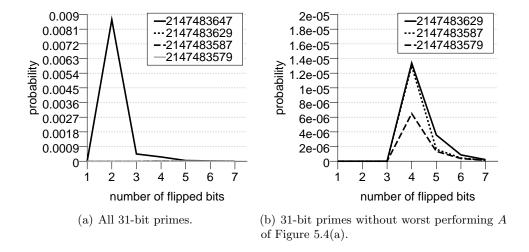

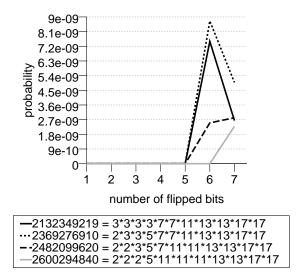

|    |      | 5.1.1. How $A$ Influences the Probability of Detecting Errors 94     |

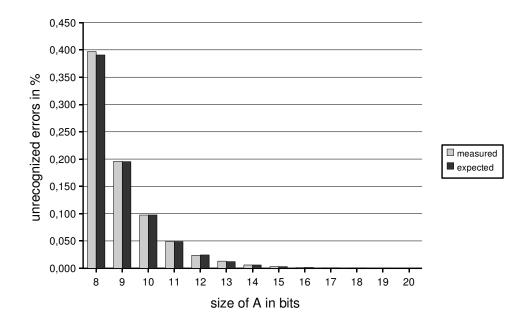

|    |      | 5.1.2. Practical Evaluation: How Many Errors Are Undetectable? 96    |

|    | 5.2. | Choice of the Signatures                                             |

|    | 5.3. | Version                                                              |

|    | 5.4. | Conclusion                                                           |

| 6. | The  | Vital Coded Processor (VCP) 105                                      |

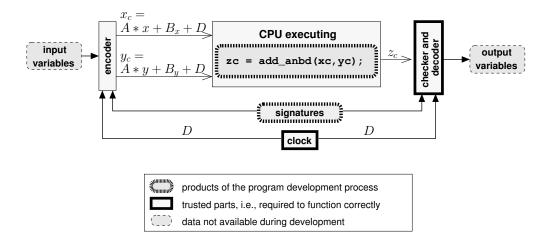

|    | 6.1. | System Overview                                                      |

|    | 6.2. | Workflow                                                             |

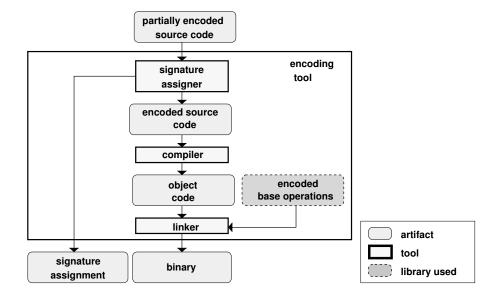

|    | 6.3. | Program Encoding                                                     |

|    | 6.4. | Discussion of VCP                                                    |

| 7. | Soft | ware Encoded Processing (SEP) 111                                    |

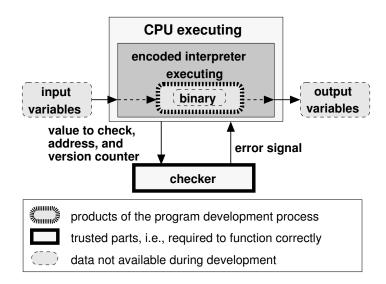

|    | 7.1. | System Overview                                                      |

|    | 7.2. | Workflow                                                             |

|    | 7.3. | Program Encoding                                                     |

|    |      | 7.3.1. Critical Combinations of Error Symptoms                       |

|    |      | 7.3.2. Encoding of the Process Image and the Instruction Pointer 115 |

|    |      | 7.3.3. Encoded Program Execution                                     |

|    |      | 7.3.4. Encoding of Control Flow Instructions                         |

|    |      | 7.3.5. Input and Output                                              |

|    |      | 7.3.6. Code Checking                                                 |

|    | 7.4. | Evaluation                                                           |

|    |      | 7.4.1. Error Detection Capabilities                                  |

|    |      | 7.4.2. Runtime Overhead                                              |

|    | 7.5. | Summary of SEP                                                       |

| 8. | Con  | npiler Encoded Processing (CEP) 129                                  |

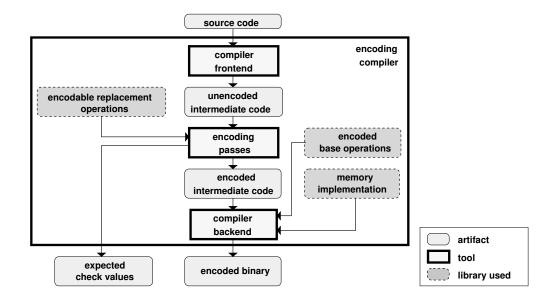

|    | 8.1. | System Overview                                                      |

|    | 8.2. | Workflow                                                             |

|    | 8.3. |                                                                      |

|    |      | 8.3.1. LLVM Bitcode                                                  |

|    |      |                                                                      |

Contents xi

|    |        | 8.3.2.  | Preparations for Encoding                          |

|----|--------|---------|----------------------------------------------------|

|    |        | 8.3.3.  | Encoding                                           |

|    | 8.4.   | Check   | ing the Correctness of the Execution               |

|    | 8.5.   | Evalua  | ation                                              |

|    |        | 8.5.1.  | Benchmarks Used                                    |

|    |        | 8.5.2.  | Other Error Detection Approaches Evaluated 156     |

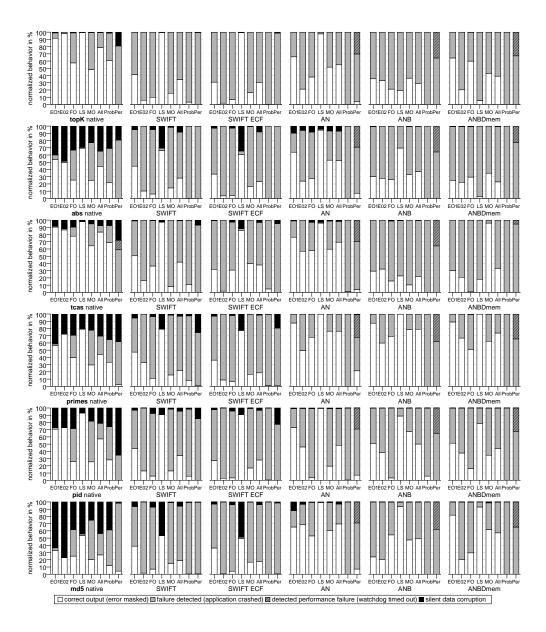

|    |        | 8.5.3.  | Error Detection Capabilities                       |

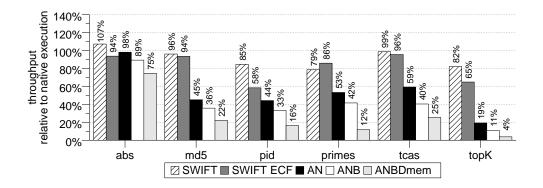

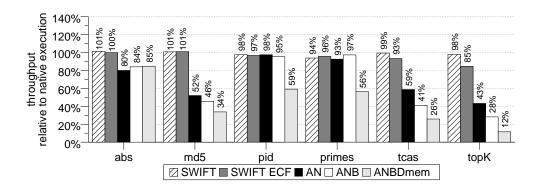

|    |        | 8.5.4.  | Runtime Overhead                                   |

|    |        | 8.5.5.  | Costs vs Gains                                     |

|    | 8.6.   | Summ    | ary of CEP                                         |

| 9. | Sym    | ptom-k  | pased Error Injection Tools 171                    |

|    | 9.1.   | Relate  | d Work                                             |

|    |        | 9.1.1.  | Error Injectors                                    |

|    |        | 9.1.2.  | Error Injectors Used in Recent Research Papers 174 |

|    |        | 9.1.3.  | Slicing                                            |

|    |        | 9.1.4.  | Design Decisions Derived                           |

|    | 9.2.   | FITgr   | ind                                                |

|    |        | 9.2.1.  | Design and Implementation                          |

|    |        | 9.2.2.  | Results                                            |

|    | 9.3.   | EIS .   |                                                    |

|    |        | 9.3.1.  | Error Injection                                    |

|    |        | 9.3.2.  | Debugging with Forward Slicing                     |

|    | 9.4.   | Conclu  | asion                                              |

| 10 | . Rela | ted We  | ork 191                                            |

|    | 10.1.  | Classif | fying Error Handling Approaches                    |

|    | 10.2.  | Reliab  | le Hardware                                        |

|    |        | 10.2.1. | Error Avoidance                                    |

|    |        | 10.2.2. | Error Detection                                    |

|    |        | 10.2.3. | Summary                                            |

|    | 10.3.  | Handl   | ing of Hardware Errors in Software                 |

|    |        | 10.3.1. | Error Avoidance                                    |

|    |        | 10.3.2. | Error Detection                                    |

|    |        | 10.3.3. | Error Correcting Software                          |

|    |        | 10.3.4. | Summary                                            |

|    | 10.4.  | Appro   | aches Combining Hardware and Software 211          |

|    |        | 10.4.1. | Error Detection                                    |

|    |        | 10.4.2. | Summary                                            |

|    | 10.5.  | Conclu  | asion                                              |

| xii | Contents |

|-----|----------|

| 11. Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 215   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 11.1. Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 215 |

| 11.2. Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 216 |

| 11.3. Publications, Proposals, and Filed Patents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 217 |

| A. Detection of Over- and Underflows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| by Choice of A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 219   |

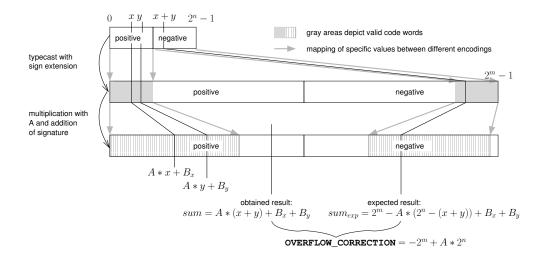

| A.1. Detecting Overflows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 219 |

| A.1.1. Lower Bound for $A \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 220 |

| A.1.2. Upper Bound for $A 	cdots . 	cd$ | . 220 |

| A.1.3. Interval of Available As                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| A.1.4. Condition for Code Invalidation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 222 |

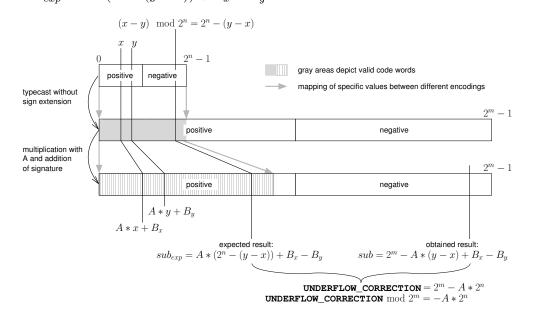

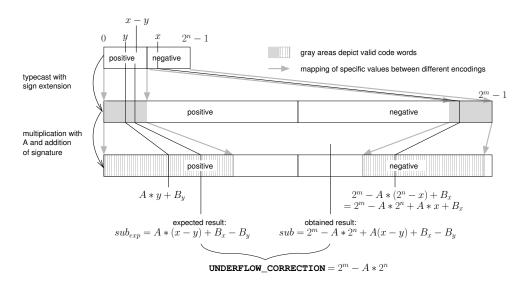

| A.2. Detecting Underflows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 223 |

| A.3. Practical Aspects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 223 |

| Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 225   |

| Bibliography                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 229   |

# 1. Introduction

"Dependability is the ability to deliver service that can justifiably be trusted." [ALRL04] When building dependable systems, we have to consider what can go wrong in the system. Computing systems contain many sources for failures:

- Erroneous hardware might execute the software incorrectly.

- Software contains bugs and security vulnerabilities with high probability. These can lead to erroneous behavior when the software is executed.

- Users and operators of the system may make mistakes.

For building dependable systems, we have to deal with all these possible failures either by preventing them by removing their causes or by tolerating them. In a dependable computing system, we have to ensure that the software is executed correctly by the hardware, that the correct software is executed, that users and operators use the software correctly, and that the software itself is correct.

This thesis focuses on ensuring that software is executed correctly. We present mechanisms that enable the user to detect if software was executed correctly or not. Being able to detect an incorrect execution, the user can react to the problem by, for example, using checkpointing and re-execution. However, tolerating the execution errors detected by our approaches is not part of this thesis. This thesis presents only mechanisms for detecting execution errors.

Nobody questions that software contains bugs. But is today's hardware unreliable? Many people assume that hardware executes software correctly. Most often, we think a software error is the culprit of a failing system. This assumption will change in the future. It is already wrong for highly dependable systems that require smaller failure rates. In the future, the share of failures that are caused by faulty hardware will increase. See Chapter 2 for a detailed discussion of hardware reliability.

While hardware reliability has improved dramatically over the last decades, the decreasing feature sizes<sup>1</sup> of integrated circuits and their growing design complexity lead to less reliable hardware in the future. According to Baumann [Bau05] the failure rate of hardware even with additional error mitigation mechanisms still ranges from 50–200 FIT<sup>2</sup>. Without the often expensive mitigation, the rate increases to over 50,000 FIT per chip.

A failure rate of 50,000 FIT means that a failure should be expected every 2 years for a chip running 24 hours a day, 7 days a week. For large scale server applications using hundreds of chips a failure rate of 50,000 FIT results in several

Focus of this thesis

<sup>&</sup>lt;sup>1</sup>Feature size means the size of the elements on a chip.

$<sup>^2</sup>$ FIT denotes failure in time. 1 FIT equals 1 failure in  $10^9$  device hours.

failing chips per week [Bau05]. Thus, this error rate bears an unacceptable economic risk for high-volume cost-critical systems. For nuclear plants even 200 FIT is much too high considering the tremendous consequences such a failure might have. 200 FIT means approximately one failure every 500 years for one continuously working chip. Currently Germany has 17 active nuclear plants. Even if each had only one safety-critical chip, that results in approximately one possibly fatal failure in one of these chips every 29 years. To summarize, the required failure rate for a single system depends on the number of such systems used and the criticality of these systems. For many systems, the currently provided hardware failure rates of commodity hardware are too high. Thus, we need additional means to ensure the correct execution of software by hardware.

Hardwareimplemented reliability Critical and, in particular, safety-critical systems in the past have been mainly built using custom hardware that provides better error detection and masking than common hardware. For example, custom reliable hardware is radiation hardened to prevent environment induced execution errors. Another approach is simple redundancy where two or more processors execute the same code and check each other.

Recent research developing safety-critical hardware tries to implement more sophisticated redundancy. These approaches seem very promising, especially with respect to runtime costs. However, to the best of our knowledge, none of the currently commercially available commodity systems use any of these new solutions that we shortly discuss in Section 10.2 of our *Related Work* Chapter.

Economics of reliability

In contrast to commodity hardware, the market for custom reliable hardware is comparatively small. Additionally, development costs for custom reliable hardware are high. Hence, custom reliable hardware is more expensive than commodity hardware. In contrast to that, the average selling price per computational device has decreased from 200\$ to 5-10\$ [Dec05]. In the future, economic pressure will necessitate the use of unreliable but cheap commodity hardware even in critical systems. This results in the need for mechanisms that facilitate to build reliable systems based on unreliable hardware. Thus, software-implemented mechanisms are required.

These mechanisms would also facilitate mixed-mode systems, which allow to consolidate hardware. *Mixed-mode systems* execute both safety-critical and non-critical applications on the same possibly unreliable commodity hardware. With the gained flexibility, hardware utilization can be improved ensuring optimal capacity utilization. Mixed-mode systems allow to use one powerful processor instead of several small ones, which are specifically adapted to the criticality of their tasks. The costs for this one commodity processor and its setup costs will be less than the costs of several custom processors and their installation. For these systems, the usage of custom reliable hardware would be especially uneconomic because running non-critical applications on expensive custom reliable hardware is a waste of resources.

For using commodity hardware in dependable systems, we have to handle their wide spectrum of possible failures. Commodity hardware exhibits not only fail-stop but also arbitrary value failures, which are more difficult to detect and to mask. A system that exhibits arbitrary value failures might produce arbitrary erroneous output. This deviation from the expected behavior of a software is also known as *silent data corruption*. In contrast to crash failures (fail-stop), these failures are especially difficult to handle because they are not easy to detect.

Thus, techniques are required that facilitate building reliable systems using unreliable hardware. Therefore, it is required to extend the limited failure detection capabilities of commodity hardware with the help of software. This thesis presents several approaches that prevent silent data corruptions without the need for custom hardware. The presented approaches realize failure virtualization by turning harder to handle value failures into crash failures. Whenever an execution error is detected that might result in a silent data corruption, the execution is aborted. As Powell shows in [Pow95], under certain conditions more reliable systems can be build if the used protocols can assume a crash failure model instead of an arbitrary failure model. For the arbitrary failure model usually more redundancy is required. This increases the probability that any of the redundant parts fails. Additionally, the fail-stop model facilitates the usage of less complex algorithms to manage the redundancy that is used to tolerate hardware errors. This reduces the risk of bugs in these algorithms.

When implementing hardware error detection in software, one will need more CPU cycles to execute an application. In comparison to using custom reliable hardware, one can however use commodity hardware. Commodity hardware is typically faster and less expensive than custom reliable hardware because its development is faster progressing and less time and money consuming. The larger market of commodity hardware further decreases its cost. Furthermore, in many systems, only a few application components are critical and only these components need to be protected by additional error detection. These mixed-mode systems can be economically realized using commodity hardware and software-implemented hardware error detection. In summary, the flexibility gained by using a software-based approach allows

- 1. to reduce the hardware cost, and

- 2. to bound the performance impact of the software-based error detection by focusing on the critical application components.

The error detection approaches presented in this thesis are based on *arithmetic codes*, which we introduce in Chapter 3. They facilitate software-implemented end-to-end hardware error detection, i. e., cover all components that might cause a data corruption. In particular, arithmetic codes cover

- errors that modify data stored in memory or

- data transported on a bus and

- errors that disturb computations implemented by logical circuits, e.g., address computations or computations done in an arithmetic logical unit.

The detection provided is end-to-end because after encoding data, errors disturbing its transportation, its storage, and its processing are detectable. For an ideal implementation of arithmetic codes no windows of vulnerability exist. This is much harder to achieve with hardware-implemented error detection mechanisms.

Softwareimplemented reliability

Arithmetic codes

For example, if parities combined with redundant execution are used, data is vulnerable for unnoticeable modifications after its redundant computation and before its parity for storage is computed. Removing these windows of vulnerability is difficult.

An application that is protected from undetected execution errors by an arithmetic code is called (arithmetically) encoded. We will in this thesis present different ways to arithmetically encode programs written in C. The error detection capabilities of arithmetically encoded applications are largely decoupled from the error detection capabilities of the hardware used. They only depend on the chosen arithmetic code and its parameters. This eases hardware replacement in critical systems because less requirements are posed on the hardware used.

From the broad variety of known arithmetic codes (see Chapter 3), we chose the AN-codes because they are the most useful for software implementation. The other codes are either

- not suitable for software implementation because only a hardware implementation can provide their full detection capabilities, or

- they are less powerful because they do only support a restricted set of recognizable errors or of operations that conserve the code.

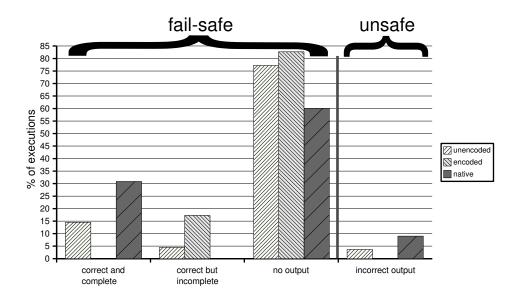

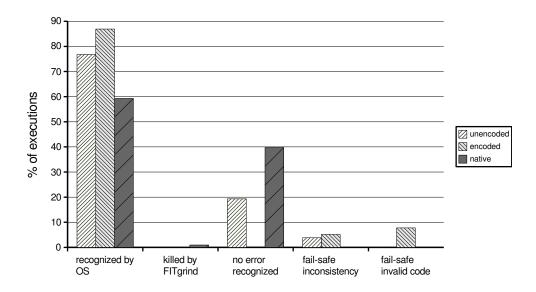

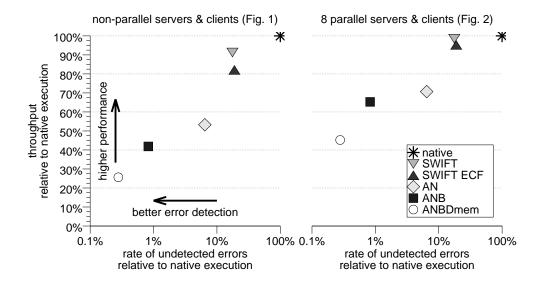

Our error detection implementations support different AN-codes with different error detection capabilities. Thereby different safety levels are provided to systems engineers. Our experiments show that AN-codes decrease the rate of silently corrupted output immensely compared to unprotected applications. Depending on the AN-code used, this reduction ranges from one to three orders of magnitude. Furthermore, the detection capabilities of AN-codes are also better than that of software-implemented redundancy – especially when permanent hardware errors are considered. Our experiments also show that a higher detection capability always comes at the cost of an increased runtime overhead. Increased safety as increased security does not come for free. This is true for different AN-codes compared to each other as well as for AN-codes compared to software-implemented redundancy. In Chapter 8 we will show the following: When choosing a detection mechanism with higher detection rate, the performance degradation is *linear*. However, the gain, i.e., reduction of the rate of undetected silent corruptions, grows exponentially. Thus, the different safety levels that we provide enable systems engineers to balance the error detection capabilities and the runtime overheads of the error detection.

Thesis structure

The thesis is structured in the following way: Chapter 2 discusses the evolution of reliability of hardware in the future and the impact that unreliable hardware has on computing systems. Furthermore, we introduce the failure model of hardware that we assumed in the development of the error detection mechanisms. Chapter 3 describes arithmetic codes in general and some specific codes. To encode an application it is required to use operations that are capable of handling encoded values. These – so-called *encoded operations* – preserve the code in an error-free execution. An erroneous execution with high probability results in invalid code words. Chapter 4 presents our encoded versions of the operations required to encode programs. Since the error detection capabilities of an encoded

program do not only depend on the arithmetic code used, but also on the code parameters, we discuss their selection in Chapter 5. Using the encoded operations described in Chapter 4 encoding an application can be done at different levels of abstraction and different points in the application's life cycle. Chapters 6, 7, and 8 present three different approaches to encode an application. While Chapter 6 introduces the Vital Coded Processor that was first described by Forin in [For89], Chapter 7 describes our newly developed Software Encoded Processing (SEP) and Chapter 8 presents our Compiler Encoded Processing (CEP). For evaluating hardware error detection mechanisms error injection is a common tool. Since none of the available error injectors fulfilled our needs, we developed our own injection tools. Chapter 9 describes the reasons for doing so and the tools' design and implementation. The thesis is concluded with a review of related work in Chapter 10 and a conclusion in Chapter 11.

Our contributions to the research community are:

Contributions

The set of encoded instructions: For encoding whole applications, we need a code-conserving version for all instructions that we encounter in an application. This encoded version of an operation takes encoded input values and produces encoded output values if no error disturbs the execution. In Chapter 4 we describe how we encode instructions that will be encountered during encoding applications. To reduce the manual work of encoding, we only encoded a small number of arithmetic operations by hand. These encoded base operations are described in Section 4.2.1. For more complex operations such as type casting or shifting, we developed our own encodable C-implementations – the replacement operations. These are described in Section 4.2.2. All occurrences of such operations are replaced with their encodable version before the actual encoding is done. Thus, they are encoded automatically afterwards. The remaining sections of Chapter 4 describe the encoding of instructions implementing control flow and memory access. To the best of our knowledge, we are the first ones presenting a complete set of encoded instructions that facilitates complete encoding of applications implemented in ANSI C.

Support of dynamic memory for ANB- and ANBD-encoding Forin introduced in [For89] AN-encoding with signatures (ANB-codes) and timestamps (ANBD-codes). His implementation – the Vital Coded Processor – is introduced in Chapter 6. One of its main drawbacks is that it does not support dynamically accessed memory for which the access pattern is not known at compile time. In Section 4.6 we present our approach to support dynamically accessed memory using our newly developed dynamic signatures.

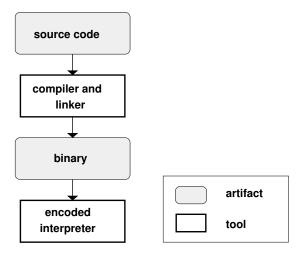

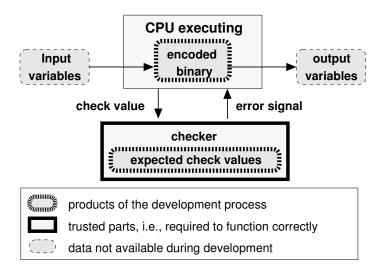

**Software Encoded Processing (SEP)** Chapter 7 describes Software Encoded Processing that protects binaries during execution from undetected silent data corruption through hardware errors. Therefore, we developed an encoded interpreter that executes the binaries using solely encoded operations. Error injections confirmed the error detection capabilities of this approach.

Compiler Encoded Processing (CEP) The encoded execution of binaries using an encoded interpreter is expensive in terms of runtime overhead. It can be expected that for safety-critical applications the source code is available since the source code of critical components is anyhow required to be able to fix bugs or modify their behavior. Thus, we developed the Encoding Compiler that we present in Chapter 8. In contrast to SEP, the Encoding Compiler supports different safety-levels by using different AN-codes. Furthermore, the runtime overhead induced by the resulting encoded applications is far less than for applications executed using SEP.

Comparison of duplicated execution and different AN-codes For comparing the different AN-codes to duplicated execution we implemented a simple software-based double modular redundancy and a signature-based control flow checking. We compared the error detection capabilities and runtime overhead of the different AN-codes, double modular redundancy, and double modular redundancy with additional control flow checking. Our experiments have shown that safety can be adapted to the required needs by choosing an appropriate safety-level – implemented for example by one of the AN-codes. However, the higher the obtained error detection capabilities are, the higher are also the runtime costs in terms of execution time. For details see Section 8.5.

Symptom-based error injector with debugging support For evaluating our error detection mechanisms, we used symptom-based error injection. Since we were not able to obtain a sufficient error injector that implemented the error model described in Section 2.5, we implemented our own injectors: FITgrind and EIS. They are described in Chapter 9. Their injection can be applied to arbitrary applications. Hence, we can compare the error detection capabilities of different error detection mechanisms and also of applications that are not protected by additional mechanisms at all. The applications analyzed can be exposed to different symptoms of hardware failures. Furthermore, the error injector EIS allows to debug error detection mechanisms by providing traces of the data flow that was influenced by an injected error. This helps to find weaknesses in our error detection mechanisms and was also not available in any other error injection tool.

# 2. Reliability of Hardware

After introducing some basic terminology, this chapter first motivates why hardware is expected to become less reliable in the future. Secondly, the chapter motivates why we should take care of unreliable hardware. Therefore, we represent studies and reports that demonstrate the impact of hardware errors on safety and security of systems and the economical impacts undetected errors had. Afterwards we introduce the symptom-based error model that we assume for all our further developments. This error model describes the symptoms unreliable hardware can cause at the level of software during the execution of an application. Hence, it is hardware independent and enables us to develop and test our hardware error detection independent of a specific hardware.

#### 2.1. Terminology

For describing the reliability of systems – in this chapter mainly hardware systems – we use the terminology introduced in [ALRL04]. The most important terms are explained in the following.

A *failure* occurs when a system's behavior deviates from its expected correct behavior. For example, if for the system memory not the same word is read from an address as was written to that address before.

Failure

An *error* is the deviation in a system's state from the expected correct version of the system's state. An error might lead to a failure if it gets *activated*. If an error does not result in a failure, it is said to be *masked*. In our memory example, a flipped bit is an error. If that bit is read, the error is activated. If that bit is overwritten with other valid data, the error is masked.

A fault is the cause for an error. A fault might be activated. In that case it leads to an error. In our memory example, the fault is, for example, the vulnerability of the memory to radiation induced bitflips.

Fault

Permanent faults are continuous in time. For hardware they are either caused by irreversible physical changes or by a faulty design. Permanent faults cause so-called hard or permanent errors. These errors are repeatable under the same conditions. For example, if a memory cell has a bit that is stuck at 1, every data item written into that cell will be modified accordingly.

The presence of *transient faults* is bounded in time. If an operation disturbed by a transient fault is repeated, the result will be most likely correct. An example for a transient fault is noise on the power supply.

An *intermittent fault* occurs, than vanishes, and than reappears again. Unstable or marginal hardware is prone to intermittent faults, for example, a transistor

that is going to break down – one time it is working correctly and the next time not.

Transient and intermittent faults cause *soft errors*. These are temporary malfunctions in a circuit [Lau06]. The *soft error rate (SER)* is the frequency of occurrence of soft errors.

#### 2.2. Causes and Effects of Hardware Errors

According to Siewiorek et. al. [SCK04] hardware reliability has been increasing with every new generation. However, in the future the decreasing feature size of hardware will not lead to more reliable but to less reliable hardware [SG99]. Logical building blocks as well as memory will become more errorprone. While the decreasing size of the elements of processors and the growing design complexity of processors increase the performance achieved, they decrease reliability. Hence, the rate of hardware failures will increase.

In the following, we will first present the reasons for increasing unreliability of hardware and, second, discuss how unreliable hardware currently is and in the future will become.

#### 2.2.1. Causes for Increasing Unreliability of Hardware

Effects of decreasing feature size

Higher variability in feature properties

The decreasing feature sizes of hardware lead to higher variability in the electrical properties of hardware. Today's CPUs have a variation in operating frequency of about 30% which is dealt with by using die binning, i.e., testing the resulting chips to find their appropriate operating frequency. However, the variability will increase further with decreasing feature sizes because of the following reasons [Bor05]:

dopant variation The threshold voltage of transistors is controlled by dopants inserted into the transistor channels. The smaller the transistors become, the less dopants are inserted. Thus, variations in the amount of dopants have a greater impact onto the electrical properties of the transistors. So, the uncontrollable variability of the production process leads to unpredictable properties of transistors.

**subwavelength lithography** Nowadays, the wavelength of the light used in lithography is bigger than the produced structures. That makes the structures unpredictable rough and uneven resulting in variations in the electrical properties of the produced transistors.

varying heat flux How much heat is produced highly depends on the functionality of a building block and thus varies across the die. Since the transistor's electrical properties are influenced by heat, transistors will have varying properties. Varying heat flux has a higher impact on smaller transistors than on larger ones.

Increasing variability will make processor designs, at least as done today, more and more unpredictable. It will not only increase the amount of hardware building blocks that fail altogether, but increased variability will also lead to more building blocks that are marginally functional. These are susceptible to soft errors and have a higher probability to fail altogether during the hardware's lifetime [CCL<sup>+</sup>08].

Decreased feature sizes and increased system sizes also lead to increased soft error rates. The problem of soft errors caused by radiation is known since the 1950s of the previous century. For example, soft errors were observed at locations near nuclear bomb test sites. Since then soft errors are continuously researched and tried to make hardware less susceptible to them [ZCM<sup>+</sup>96]. Borkar expects the SER (soft error rate) to increase exponentially with every new technology generation [Bor05].

Increasing soft error rate

One main cause for soft errors is radiation that causes energetic particles to travel through processors. These particles are responsible for inducing soft errors by for example changing the state of a transistor. Soft errors can be caused by three different kinds of radiation [Bau05]:

Alpha particles are emitted by impurities in the packaging materials of chips that are undergoing radioactive decay. Examples are uranium and thorium impurities. While emitted alpha particles travel through the processor, they transfer part of their kinetic energy into the surrounding material. Thereby, they can induce state changes [Bau05].

Since the discovery of the effect of impurities, they were reduced immensely. However, it is not possible to exclude impurities that emit energetic particles completely. Thus, alpha-particle-induced soft errors have to be considered when building reliable systems [KHP04].

**High-energy cosmic radiation** reacts with the Earth's atmosphere. This reactions emit cascades of secondary particles – mostly high-energy neutrons – that can also induce soft errors. The rate of these soft errors depends on altitude and geographical location.

According to Baumann [Bau05] high-energy neutrons have a higher potential to cause soft errors than alpha particles. Furthermore, it is difficult to protect from neutrons by shielding. Only thick layers of concrete reduce their impact [Bau05].

**Low-energy cosmic radiation** results in low-energy neutrons – so-called thermal neutrons. Boron is used as a dopant to control the threshold voltage of transistors. Low-energy neutrons can cause soft errors when encountering a specific boron isotope.

According to Baumann [Bau05] these soft errors can be easily prevented because the concerned boron isotope can be avoided easily. However, Wilkinson et. al. [WBB<sup>+</sup>05] reported that many integrated circuits still contain the concerned boron isotope.

Note that low- and high-energy neutrons are not exclusively caused by cosmic radiation. For example, cancer-radiotherapy equipment also emits low-energy

neutrons.

Decreased feature sizes result in decreased supply voltages. Thus, less energy, that is, less radiation, is required for causing a state change. The measurements presented by Constantinescu [Con03] indeed show a higher SER for memories operated at a lower supply voltage. Karnik et. al. [KHP04] observed that the error rate grows faster than the supply voltage decreases: "The SER increases by 2x when the voltage is reduced from 1.2V to 0.8V. Over the range of measurements, the SER increases by 18 percent for every 10 percent reduction in the supply voltage." Thus, in the future not only hardware operated under extreme conditions will be susceptible to soft errors. Commodity hardware under normal conditions will also be prone to radiation induced soft errors.

Furthermore, the increased system size leads to increased error rates for systems. Smaller transistors are less likely hit by an energetic particle and indeed the error rates per bit of memory are decreasing [Con03, DHW09]. However, the number of transistors per system follows Moore's Law and grows exponentially over time. Thus, the increased number of transistors increases the probability that any of them is hit by an energetic particle. Constantinescu from Intel [Con03] has shown that the SER of SRAM and DRAM increases linearly with their size. Dixit et.al. [DHW09] (working with Sun Microsystems) also confirm higher SERs for microprocessors with more memory. Dixit et.al. also state that the decreased SER per bit in RAM is partly caused by a change in design and not only by the reduced feature size. The new design was more lithography friendly and the resulting memories thus less susceptible. Memories in logical circuits such as registers have a less regular and thus less lithography friendly structure. Indeed, starting with the 90nm generation Dixit et.al. observed a higher SER for memories used in logical circuits than for SRAM.

There are various other causes for soft errors whose impact is also increased by decreasing feature sizes because they always go hand in hand with decreasing supply voltages:

- noise on the power supply

- charge sharing

- crosstalk and crosstalk-induced delays

- electromagnetic interference

- electrostatic discharge

Changing error model

Technology changes such as the feature size reduction do not only affect error rates observed, but also the kind of induced errors. For a long time single bitflips were a well-established error model. But with decreasing feature size multiple bitflips become more probable [DHW09].

Higher impact of physical effects

Furthermore, the reduced feature size increases the impact of physical effects such as the Miller and the skin effect. Thereby SER is also increased. The Miller effect means that the simultaneous switching of both terminals of a capacitor will modify the effective capacitance between the terminals. Thus, it can significantly affect on-chip delays [SK99]. According to the skin effect signals mostly propagate along the surface of wires at high frequencies. Because of the skin effect the resistance of wires varies with the signal frequency [Wal00].

Smaller features are also less reliable because decreased feature sizes increase the effects of transistor aging. While today these effects are factored in during design, this will not be possible anymore in the future [Bor05]. The amount of transistors that are either permanently broken or exhibit a borderline behavior will increase.

Increasing hard error rate

Possible causes for hard errors whose impact is increased by decreasing feature size are [BSO05]:

- *Electromigration* is the transport of material caused by the gradual movement of the ions in a conductor. It eventually results in highly resistive interconnects or contacts and leads to open circuits.

- Gate oxide breakdown is caused by the progressive build-up of defects inside the gate oxide of a transistor. Eventually these defects line up and constitute a conductive path across the dielectric.

- As we will detail later smaller structures are more difficult to handle during manufacturing. Hence, during chip fabrication with smaller feature sizes more hard errors are introduced.

A further type of hard errors are design errors. Due to the increasing complexity of processors, it becomes more and more difficult to ensure their correctness [WA01]. Design errors are even worse than hard errors caused by randomly failing circuits because they are not detectable with a redundant execution that uses the same circuit.

Design errors