**Retrospective Theses and Dissertations**

1976

# A Simulator for the Motorola M6800 Microprocessor

Carolyn Elizabeth Jordan University of Central Florida

Find similar works at: https://stars.library.ucf.edu/rtd University of Central Florida Libraries http://library.ucf.edu

This Masters Thesis (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Retrospective Theses and Dissertations by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS Citation**

Jordan, Carolyn Elizabeth, "A Simulator for the Motorola M6800 Microprocessor" (1976). *Retrospective Theses and Dissertations*. 224.

https://stars.library.ucf.edu/rtd/224

## A SIMULATOR FOR THE MOTOROLA M6800 MICROPROCESSOR

BY

CAROLYN ELIZABETH JORDAN

B.S., Florida Technological University, 1974

#### RESEARCH REPORT

Submitted in partial fulfillment of the requirements for the degree of Master of Science in the Graduate Studies Program of the College of Engineering of Florida Technological University

Orlando, Florida 1976

## A SIMULATOR FOR THE MOTOROLA M6800 MICROPROCESSOR

by

Carolyn E. Jordan

## ABSTRACT

The Motorola Company has developed a microprocessor called the M6800 Microprocessor. While the microprocessor is being configured, it is general practice to develop the software at the same time. This is where simulation of the proposed hardware operation can become very important to the success of the design effort. The simulator duplicates the microprocessor execution of machine language instructions on another computer.

The simulator discussed in this paper is denoted the SIM6800. The purpose of this paper is to describe the structure, coding, and execution of the SIM6800 simulator. A User's Guide and sample program have been included.

Director of Research Report

# TABLE OF CONTENTS

| I.    | INTRODUCTION                                                  |

|-------|---------------------------------------------------------------|

| II.   | CHAPTER 1                                                     |

|       | SIM6800 Structure                                             |

| III.  | CHAPTER 2                                                     |

|       | SIM6800 Coding                                                |

| IV.   | CONCLUSIONS AND SUGGESTIONS FOR FUTURE WORK 19                |

| v.    | APPENDIX A                                                    |

|       | SIM6800 User's Guide for the Motorola<br>M6800 Microprocessor |

| VI.   | APPENDIX B                                                    |

|       | Sample Output from the SIM6800<br>Simulator Program           |

| VII.  | APPENDIX C                                                    |

|       | Computer Listing of the SIM6800<br>Simulator Program          |

| VIII. | BIBLIOGRAPHY                                                  |

#### INTRODUCTION

A microprocessor is fundamentally no different from any other computer in that the five major subsystems are present, including: the ALU (arithmetic logic unit), the CPU (control function), input, output, and memory. A microprocessor is constructed by putting the ALU and the CPU into one or a small number of integrated circuit chips. The Motorola Company has developed a processor of this type called the M6800 Microprocessor.

While the microprocessor hardware is being configured, it is general practice to develop the software at the same time. This is where simulation of the proposed hardware operation can become very important to the success of a design effort. A simulator program facilitates overall checkout and error elimination from programs written for the microprocessor. The simulator duplicates the microprocessor execution of machine language instructions on another computer. Although the simulator program does not match the microprocessor's real time operating speeds, a count is kept of elapsed time cycles in simulated execution which can be used to estimate program execution times. The simulator program discussed in this paper was designed and written to operate in a time-sharing mode. Choosing the time-sharing mode over the batch mode allows the user to

have complete interactive control over the program being tested. The user gives appropriate commands to the simulator, resulting in execution of all or any part of the program being tested. This flexibility of user control would be difficult to obtain using only the microprocessor hardware.

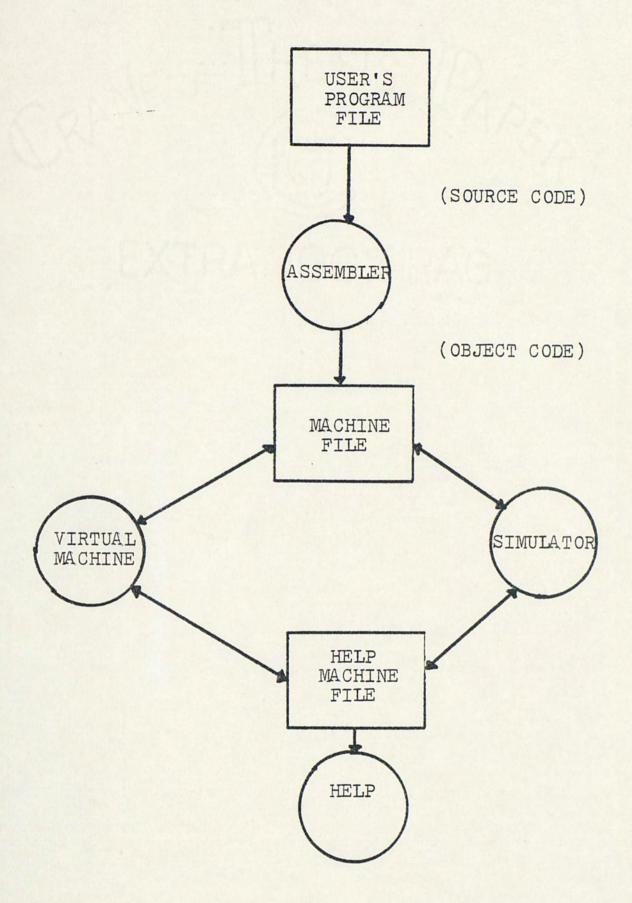

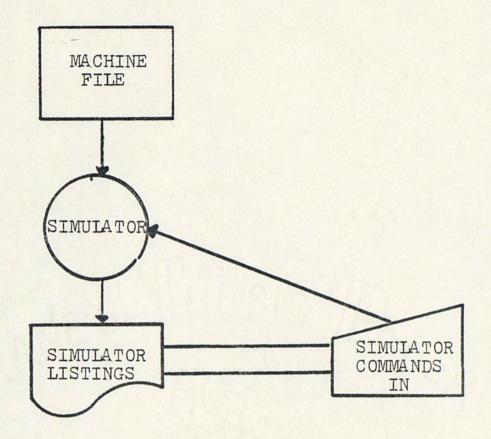

The simulator is only part of the overall software support aids for the Motorola M6800 (Figures 1 and 2). The microprocessor users begin by writing a program in the assembler language for the computer. The assembler language program serves as input to a Cross-assembler, an assembler resident on a computer other than the computer for which it generates the machine code. The machine code from the Cross-assembler is then used as input to the simulator program. The simulator duplicates the execution of the machine language. The output from the simulator is a computer activity listing which the user can review to determine if the assembler language program has executed correctly with the intended results.

The original purpose of the simulator was to allow parallel work on the microprocessor software and hardware. The configuration of the microprocessor hardware allows only one user at a time. However, the host computer containing the simulator is usually large enough to support several terminals allowing several users of the simulator software at once. With this increased access to the

Fig. 1.--FILE INTERCONNECT SCHEME FOR SOFTWARE SUPPORT

Fig. 2. -- SIMULATOR, A BLOCK DIAGRAM

simulator, the use of the simulator can later be expanded to general debugging of all microprocessor software.

The simulator discussed in this paper, denoted the SIM6800, was written in IBM PL/1-F for the IBM 360-75 computer. PL/1 lends itself to this type of programming application due to the structural format of the language, the character string and bit string manipulation abilities, and the access methods to the machine's bits and addresses. The simulator program can be executed in a minimum core partition of 120K-bytes under time-sharing.

The purpose of this report is to describe the structure, coding, and execution of the SIM6800 simulator. A User's Guide and sample program have been included to allow any individual to use the SIM6800 simulator with ease.

#### CHAPTER 1

#### SIM6800 STRUCTURE

The input to the simulator is the result of several previous steps in the software support scheme. The user written assembler language program (Figure 3), the assembled program (Figure 4), and the object code file, named EXAMPLE 1 (Figure 5) have all been generated prior to the execution of the simulator.

SIM6800 itself is a single program written in PL/1.

All subprocedures are contained internally to the main program, but the simulator does require three files for it to execute. These three files are:

- 1. Object code file (OBJ)

- 2. Machine operation table (MOT)

- 3. Simulator commands

The name of the OBJ file is supplied by the user when dialog to SIM6800 is initiated through an interactive terminal. The procedure call for establishing communication is as follows:

# exec sim6800(example1)

This statement moves the object file EXAMPLE 1 into simulated memory. Each line of the object code symbolically represents each line of the assembler program and is divided into two components:

```

100 NAM ITEMI

110 OPT MEM DIRECTS THE ASSEMBLER TO SAVE

120 * AN OBJECT PROGRAM.

130 *

140 * ADDITION OF TWO EIGHT-BYTE

150 * BINARY-CODED-DECIMAL NUMBERS.

160 *

190 ORG $1000

200 LDA B #8

210 LDA #P LOADS INDEX REGISTER

220 *

WITH THE ADDRESS OF THE

230 *

MOST SIGNIFICANT BYTE

240 *

OF P

250 CLC

260 NEXT LDA A 7, X

270 ADC A 15,X

280

DAA

290

STA A 23, X

300

DEX

DEC B

310

320 BNE NEXT

LOOPS BACK FOR NEXT

330 *

BYTE IF ADDITION NOT COMPLETED.

400 NOP

410 BRA *-1

500 * ALLOCATE A DATA AREA IN READ-WRITE

510 * MEMORY FOR THE NUMBERS TO BE ADDED

520 * (P AND Q) AND FOR THE SUM (RES)

530 ORG $0100

540 P RMB 8

550 Q RMB 8

560 RES RMB 8

END

610

MON

```

| 00010<br>00020<br>00030<br>00040                                                                                                                                                                           |                                                                              |                         |                        | * REVIS                                       | NOIS                                   | 1.0                | ITEM2<br>)<br>MEM<br>SYMBOLS                                                                                                           |                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------|------------------------|-----------------------------------------------|----------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00060<br>00070<br>00080                                                                                                                                                                                    |                                                                              |                         |                        |                                               |                                        |                    | TWO-MULTI<br>D-DECIMAL                                                                                                                 | PLE-PRECISION<br>NUMBERS.                                                                                                                              |

| 00090                                                                                                                                                                                                      |                                                                              | 0008                    |                        | NB<br>*                                       | EQU                                    |                    | 8                                                                                                                                      | SPECIFIES 8-BYTE<br>OPERANDS                                                                                                                           |

| 0110<br>00120<br>00130<br>00140<br>00150<br>00160<br>00170<br>00180<br>00190<br>00210<br>00220<br>00230<br>00250<br>00260<br>00270<br>00280<br>00290<br>00310<br>00320<br>00330<br>00350<br>00350<br>00360 | 1000<br>1002<br>1005<br>1006<br>1008<br>100A<br>100B<br>100D<br>100E<br>100F | FE 0C A6 A9 19 A7 09 5A | 0100<br>07<br>0F<br>17 | * TEST  *  *  *  *  *  *  *  *  *  *  *  *  * | ORGALDX LDX STRPBRA CARG               | B A A A B IN ESUBE | \$1000<br>#NB<br>ADDR<br>NB-1,X<br>2*NB-1,X<br>3*NB-1,X<br>NEXT<br>PROGRAM<br>ROUTINE 'B<br>\$1100<br>#\$13F<br>#P<br>ADDR<br>BCD<br>* | LOADS DATA ADDR START LOOP  END OF BCD SUBROUTINE  CD' INITIALIZE STACK POINTER LOADS ADDRESS OF P  DO BCD ADDITION END OF MAIN PROG IN READ-WRITE MEM |

| 00370<br>00380<br>00390<br>00400<br>00410<br>00420<br>00430                                                                                                                                                |                                                                              |                         |                        | ADDR                                          | RMB<br>RMB<br>RMB<br>RMB<br>RMB<br>RMB |                    | IE SUBROUT 2 IE MAIN PRO NB NB NB NB                                                                                                   |                                                                                                                                                        |

Fig. 4.--ASSEMBLED PROGRAM

```

4364 001 <u>0</u>

4365 032 254

4361 189 4096

4358 255

256

4355 206 258

4352 142 319

4096 198 8

4098 254 256

4101 012 0

4102 166

4104 169 15

4106 025 0

4107 167 23

4109 009 0

4110 090 0

4111 038 245

4113 057 0

```

## Component

## PL/1 Variable Names

1. Instructional address

BYTE1

2. Operands

BYTE2

The second file, MOT, is automatically moved into a storage structure called MOT. The MOT file remains the same for all programs being tested. This file contains information needed to decode and execute the object code. There are 197 entries in the MOT file and each entry contains the following categories:

| MOM | D'n+m |

|-----|-------|

| TOM | Entry |

## PL/1 Variable Names

OP

1. Operator number

2. Mnemonic code MNEMONIC

3. Address mode ADDR\_MODE

4. Time TIME

5. Bytes BYTES

6. MOT number MOT\_NO

7. Address accumulator ADDR\_ACC

Once these first two files are set up, SIM6800 will print the following header:

SIMULATOR FOR THE MOTOROLA M6800 MICROPROCESSOR

WRITTEN FOR THE IBM360

VERSION 1 1976

The simulator acknowledges a request for a command by printing a "?". At this time the user creates the third file by entering a simulator command after every prompt. The simulator commands now available are:

## MNEMONIC MEANING

DM Display memory

DR Display register

EX Exit simulator

HR Set header count

RN Run

SM Set memory

SR Set register

A complete explanation of these commands may be found in Appendix A.

The SIM6800 has 72 executable instructions. These instructions assemble into 1 to 3 bytes of object code. The length of the instruction depends on the particular instruction and on the type of addressing used. The length of the instruction is the value of BYTES in the MOT file.

SIM6800 has two 8-bit data registers where arithmetic calculations are performed. These are equivalent to Accumulator A and Accumulator B in the M6800 processor chip. The corresponding PL/1 variable names are ACCA and ACCB, respectively.

SIM6800 has seven types of addressing, as follows:

- 1. Inherent addressing

- 2. Relative addressing

- 3. Immediate addressing

- 4. Accumulator addressing

- 5. Indexed addressing

- 6. Extended addressing

- 7. Direct addressing

The addressing mode used is coded 1 through 7 and this code is entered in the MOT variable ADDR\_MODE. If either Accumulator A or Accumulator B is needed in the addressing, an "A" or a "B" is placed in MOT entry ADDR\_ACC.

SIM6800 uses a 16-bit register called the Index

Register (IX), again, corresponding to a hardware register

on the M6800 chip. This register is needed for instructions

that use the indexed addressing mode. The use of IX allows

the current instruction or data address to be computed

during execution of the program and allows additional

flexibility over the strict use of fixed addresses predetermined by the assembler.

The SIM6800 simulated memory is a two dimensional array, denoted M(5000,2). The size of memory is 10,000 8-bit memory locations. The design of M as a 2-dimensional array is based on the format of the object code for the M6800 hardware. The maximum length of a coded instruction is 3 bytes. The first byte is the memory address which will be the array M subscript. Therefore, only two dimensions of array M are needed to store the last two bytes of the instructions.

The memory location of the current instruction about to be executed is assigned to the program counter variable,

PC. That memory location is also assigned to the instruction address, IA. Once the length of the instruction has been determined, PC is incremented by that length. This new value of PC is the memory location of the next instruction to be executed.

Like most microprocessors, the Motorola M6800 is not designed to handle the conventional subroutine returnaddress storage scheme. Rather, the M6800 uses a hardware "push-down stack." The stack consists of any number of locations in memory providing for temporary storage and retrieval of successive bytes of information. Usually, the stacks will be one single block of successive memory locations but there could conceivably be several stacks, each consisting of a block of successive memory locations. Associated with the stack is a 16-bit stack pointer called SP. When a subroutine is called, the current contents of PC (return address) are stored on the stack at location SP. The stack pointer SP is then decremented by 2. When a return from subroutine occurs, the current contents at stack location SP (entry address) is assigned to PC. The stack pointer SP is incremented by 2.

The Condition Code Register, CC, is a 6-bit register containing information on the status of the program being run. The 6 bits in CC are:

| Bit No. | Condition Code     |

|---------|--------------------|

| 0       | C (Carry-borrow)   |

| 1       | V (Overflow)       |

| 2       | Z (Zero)           |

| 3       | N (Negative)       |

| 4       | I (Interrupt Mask) |

| 5       | H (Half-carry)     |

The CC can be set by any of a number of instructions. The value to which CC is set depends on the result of the last instruction executed. If, for example, the subtraction of two numbers results in a negative number, the N bit would be turned on (set to "1"). The value of the CC register can be used to control branching within a program, and is useful in implementing data comparison operations and similar program functions.

#### CHAPTER 2

## SIM6800 CODING

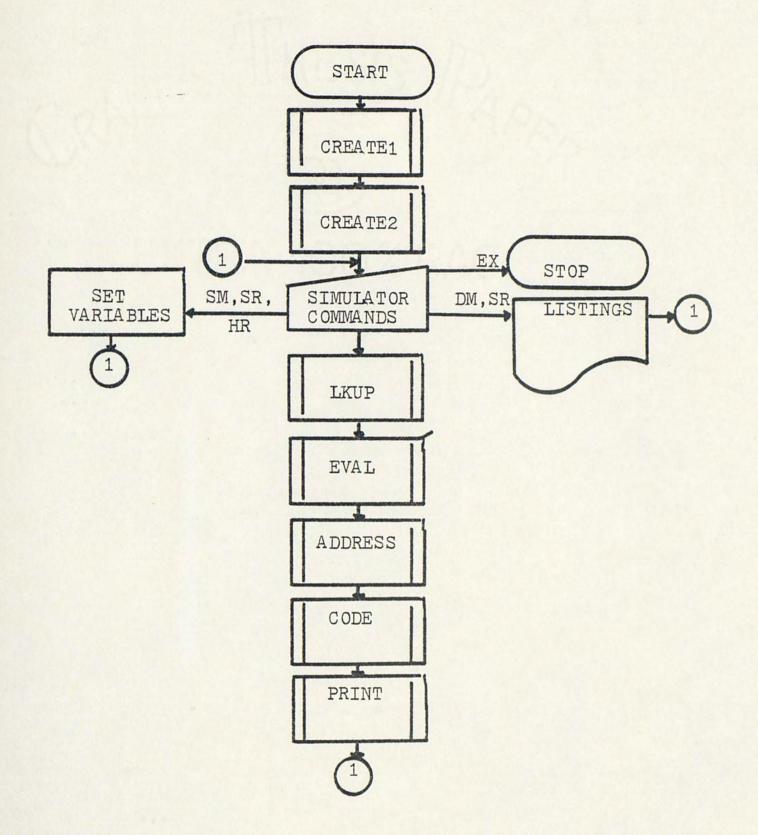

The simulator program is divided into 10 subprocedures contained within a main procedure. Each subprocedure performs one step in the decoding of the object code. This modular approach aids in debugging and future modification to the simulator. Figure 6 is an overall flowchart of the SIM6800.

When the simulator is executed, the first two subprocedures CREATE1 and CREATE2 are called. Their function is to load the OBJ and MOT files already discussed. Before executing any further, the simulator prompts the user for a command. The user-supplied commands EX, SM, SR, DM, DR, and HR either set variable values or end execution of the simulator. The RN command causes all of the subprocedures to be executed.

A brief, functional description of each of these subprocedures follows.

#### LKUP

BYTE1 of the object code identifying the instruction should match with an entry in the MOT file if the instruction is valid. If the match is found, all entries in the MOT file structure are filled in. At this point, the simulator should have information available to it

Fig. 6.--SIM6800 FLOWCHART

concerning the instruction abbreviation (MNEMONIC), the type of address used (ADDR\_MODE), and number of execution cycles needed (TIME), length of the instruction (BYTES), the instruction number from 1 to 72 (MOT\_NO), and whether or not an accumulator is needed in the addressing (ADDR\_MODE). If a match is not found, Error #301 will be printed on the terminal to flag the problem (see Appendix A for a list of error codes and corrective actions).

## ADDRESS

The variable ADDR\_MODE in the MOT file determines which of the seven types of addressing is required. The address of the instruction operands is calculated in this subprocedure to be used in another procedure. If the calculated address exceeds the bounds of simulated memory, Error #313 will be printed (see Appendix A).

#### EVAL

The operation number OP from the OBJ file determines what type of operation the instruction is to perform (e.g. ADD). Using the address generated by ADDRESS, the operands needed in the operation are obtained and the instruction can then be completely evaluated.

#### CODE

The results of the operation identified in EVAL are now tested. The CC bits are set to a specific value based on the particular instruction. The Boolean formulae used to test the results are the same as those used by Motorola

in the hardware operation.

# PRINT

After each instruction is evaluated, the values of the simulated machine registers are printed along with the register abbreviation as a header.

#### CONCLUSIONS AND SUGGESTIONS FOR FUTURE WORK

The SIM6800 shows how a simulator can be used to verify a microprocessor program without the use of the microprocessor hardware. The PL/1 simulator program was written with "ease of use" in mind and was written for a wide range of users, from the less experienced to the experienced. The SIM6800 also shows execution of the programs in various amounts of detail as required by the user. Two additional concepts, MACRO commands and HELP files are suggested as future work to the SIM6800. The following is an overall description of these concepts.

### MACRO COMMANDS

A user defined simulator command(s) is called a MACRO.

MACRO commands allow the user to create a string of commands or redefine existing commands. Suppose the user repeatedly enters:

RN 7

DM 0102 8

DM 010A 8

DM 0112 8

To avoid repetition, the user could define a MACRO command named XY by typing

? XY(RN 7.DM 0102 8.DM 010A 8.DM 0112 8)

A MACRO command is executed in the same way as an existing command.

?XY

Once the MACRO concept has been implemented, it can be expanded to include MACROs with variable parameters and MACROs with multiple variable parameters.

Commands would then be needed to give the user control over MACRO commands. These would be:

| MACRO Command | Meaning                      |

|---------------|------------------------------|

| MD            | Delete MACRO                 |

| MIL           | List MACRO                   |

| MR            | Read MACRO from machine file |

| MS            | Save MACRO in machine file   |

## HELP FILES

Once the entire M6800 software and hardware have been assembled, a HELP system should be created. The HELP system provides up-to-date information on improvements and new developments of the M6800 microprocessor system. The users enter a request for assistance and a search is made through the HELP file for the desired information. The HELP file is a set of messages, each divided into three sections:

- 1. the message number

- 2. the message description

- 3. the message text

The amount of detail to be printed with the HELP message is specified by format control commands. With the added

feature of format control, the user could print all messages added within the last month, all simulator messages, all HELP messages, or any combination of messages desired.

The inclusion of MACROs and HELP files will round out user control and interface with SIM6800.

# APPENDIX A

SIM6800 USER'S GUIDE

FOR THE MOTOROLA M6800 MICROPROCESSOR

### EXECUTING THE SIM6800 SIMULATOR

The SIM6800 simulator is designed to be used in a time-sharing mode. Since every computer installation has its own form of time-sharing, procedures may vary. The sample problem included in this appendix and Appendix B was executed on an IBM2741 terminal to an IBM360/75 computer operating under OS/360. To execute the SIM6800 simulator, the user logs on the computer and types in:

exec sim6800(example1)

(EXAMPLE1 is the file containing the object code of the program being simulated.)

## SIMULATOR COMMANDS

The following is a list of the currently available M6800 simulator commands:

| MNEMONIC | MEANING           |

|----------|-------------------|

| DM       | Display memory    |

| DR       | Display registers |

| EX       | Exit simulator    |

| HR       | Set header count  |

| RN       | Run               |

| SM       | Set memory        |

| SR       | Set registers     |

The exact format and explanation of each of these commands are found on the following pages. There are several basic directives which must be observed when executing SIM6800.

- 1. Insert at least one blank between operands in the command.

- Hexidecimal values must contain four positions.

Leading zeros must be added if needed.

- Real number values must not contain a decimal point.

- 4. All operands listed in the command format must be included.

5. All memory locations (addresses) must be hexidecimal and other operands must be integers (unless otherwise stated).

### DM--DISPLAY MEMORY

Format

DM a n

Display n memory positions starting at memory address a.

The DM command can be used to display n memory locations containing data values or n memory locations containing the object code of the program being simulated.

## DR--DISPLAY REGISTERS

Format

DR

The DR command causes the value of the registers to be printed.

The codes for the registers to be displayed are:

IA -- Instruction address

OC -- Operation code

EA -- Effective address

P -- Program counter

X -- Index register

A -- Accumulator A

B -- Accumulator B

C -- Condition codes

S -- Stack pointer

T -- Time

Note: This simulator command has no operands.

## EX--EXIT FROM SIMULATOR

Format

EX

The EX command causes all simulation to stop. The only file saved is the machine program file.

After entering the EX command, the user will return to an idle state under TSO.

Note: This simulator has no operands.

# HR--SET HEADER COUNT

Format

HR n

The HR command controls the number of times the header line will be printed. The header will print every n lines of output.

### RN--RUN n INSTRUCTIONS

Format

RN n

The RN command causes the simulator to execute the next n instructions of the machine program file.

Simulation (execution) continues until:

- 1. n instructions have been executed

- 2. an error occurs.

SM--SET MEMORY (CHANGE MEMORY)

Format

sm a n  $v_1$   $v_2 \cdot \cdot \cdot v_n$

Starting at memory address a, set n memory positions with the values  $v_1,\ v_2,\ \dots\ v_n.$

The SM command can be used to enter data before execution or can be used to modify the actual machine program file.

# SR--SET REGISTERS

Format

SR r v

The SR command sets register r to the value v.

The codes for the r operand with corresponding v input bases are:

|   | <u>r</u>        |             |

|---|-----------------|-------------|

| P | Program counter | Hexidecimal |

| X | Index register  | Hexidecimal |

| A | Accumulator A   | Integer     |

| В | Accumulator B   | Integer     |

| C | Condition codes | Bit-string* |

| s | Stack pointer   | Hexidecimal |

| T | Time            | Integer     |

<sup>\*</sup> To turn all condition codes "on" enter '1111111'B.

To turn all condition codes "off" enter '000000'B.

# ERROR MESSAGES

| Error Number | <u>Description</u>            |

|--------------|-------------------------------|

| 301          | **** ERROR 301 AAAA           |

|              | Undefined simulator command.  |

| 302          | **** ERROR 302 AAAA           |

|              | Possible syntax error in      |

|              | simulator command.            |

|              |                               |

| 306          | **** ERROR 306 AAAA           |

|              | The operand in the simulator  |

|              | command caused a register     |

|              | overflow.                     |

|              |                               |

| 313          | **** ERROR 313 NNNN           |

|              | The calculated address beyond |

|              | bounds of memory.             |

AAAA -- The simulator address which caused the error.

NNNN -- A numeric field.

# APPENDIX B

SAMPLE OUTPUT FROM THE SIM6800 SIMULATOR PROGRAM

The M6800 program being tested is one designed to add the following two 8-byte binary coded decimal numbers:

1357902468097531

# +9258147036741852

0616049504839383 (result)

The object code exists in a file named "EXAMPLE1". The simulator was started by the statement:

exec sim6800(example1)

The SR command was used to initialize the program counter with the hexidecimal value 1100. This is the address in memory of the first instruction.

The SM command was used to enter the data values to be added.

A repetition of the RN and DM commands were used to execute the instructions and to display the results.

# SIMULATOR FOR THE MOTO DLA M6800 MICROPROCESSOR WRITTEN FOR THE IBM 360 VERSION 1 1976

?

| dm 0102 8<br>13 57                                                                        | 90 24                                                     | 68 9                                                                | 75                         | 31                                        |                                                     |                                                      |                        |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------|----------------------------|-------------------------------------------|-----------------------------------------------------|------------------------------------------------------|------------------------|

| dm 010a 8<br>92 58                                                                        | 14 70                                                     | 36 74                                                               | 13                         | 52                                        |                                                     |                                                      |                        |

| dm 0112 8<br>0 0-<br>?<br>rn 7                                                            | 0 0                                                       | 0 0                                                                 | 0                          | 83                                        |                                                     |                                                      |                        |

| IA CC<br>1006 LDA<br>1008 ADC<br>100A DAA<br>100B STA<br>100D DEX<br>100E DEC<br>100F BNE | A 0110 10<br>100A 10<br>A 0118 10<br>100D 10<br>B 100E 10 | X<br>08 0101<br>0A 0101<br>0B 0101<br>0D 0101<br>0E 0100<br>0F 0100 | 93<br>93<br>93<br>93<br>93 | 3<br>7<br>7<br>7<br>7<br>7<br>7<br>6<br>6 | C<br>000000<br>00N0V0<br>00N000<br>00N000<br>000000 | S<br>013D<br>013D<br>013D<br>013D<br>013D<br>013D    | T 688 76 76 82 86      |

| ?<br>dm 0102 3<br>13 57<br>?                                                              | 90 24                                                     | 83 9                                                                | 75                         | 31                                        |                                                     |                                                      |                        |

| dm 010a 8<br>92 58                                                                        | 14 . 70                                                   | 36 74                                                               | 13.                        | 52                                        |                                                     |                                                      |                        |

| dm 0112 8<br>0 0<br>?<br>rn 7                                                             | 0 0                                                       | 0 0                                                                 | 93                         | 83                                        |                                                     |                                                      |                        |

| IA OC<br>1006 LDA<br>1008 ADC<br>100A DAA<br>100R STA<br>100D DEX<br>100E DEC<br>100F BNE | A 010F 10<br>100A 10<br>A 0117 10<br>100D 10<br>B 100E 10 | X<br>08 0100<br>0A 0100<br>0B 0100<br>0D 0100<br>0E 00FF<br>0F 00FF | 83<br>83<br>83<br>83       | 8 6 6 6 6 6 5 5                           | C<br>000000<br>000000<br>000000<br>000000<br>000000 | 013D<br>013D<br>013D<br>013D<br>013D<br>013D<br>013D | T 91 96 95 104 100 114 |

| ?<br>dm 0102 8<br>13 57                                                                   | 90 24                                                     | 63 9                                                                | 75                         | 31                                        |                                                     |                                                      |                        |

| ?<br>dm 010a 8<br>92 53                                                                   | 14 70                                                     | 36 7h                                                               | 13                         | 52                                        |                                                     |                                                      |                        |

| ?<br>dm 0112 8<br>0 0                                                                     | 0 0                                                       | ი ვვ                                                                | 93                         | 83                                        |                                                     |                                                      |                        |

| dm   010a   3   92   58   14   70   36   74   18   52   7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | dm<br>?        | 0102 8<br>13 57                                                |   | 90                                   | 24                                                       | 68  | 39                                           | 75                          | 31  |           |                                                |                                              |                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------------------------------------|---|--------------------------------------|----------------------------------------------------------|-----|----------------------------------------------|-----------------------------|-----|-----------|------------------------------------------------|----------------------------------------------|----------------------------------------|

| dm   0112   3   7   7   7   7   7   7   7   7   7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | dm             |                                                                |   | 14                                   | 70                                                       | 36  | 74                                           | 13                          | 52  |           |                                                |                                              |                                        |

| 1006                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | dm<br>?        | 0 0                                                            |   | 4                                    | 95                                                       | 4   | 83                                           | 93                          | 83  |           |                                                |                                              |                                        |

| dm 0102 8     13 57 90 24 68 9 75 31 ? dm 010a 8     92 58 14 70 36 74 18 52 ? dm 0112 8     0 16 4 95 4 83 93 93 ? rn 7  IA OC EA P X A B C S T 1008 LDA A 0102 1008 00FB 13 1 H00000 013D 231 1003 ACC A 010A 100A 00F3 106 1 00N000 015D 236 100A DAA 100A 100B 00FB 6 1 000000 013D 238 100B STA A 0112 100D 00FB 6 1 000000 013D 238 100D DEX 100D 100E 00FA 6 1 000000 013D 244 100F DEC B 100F 100F 00FA 6 0 000Z0C 013D 244 100F BEC B 100F 100F 00FA 6 0 000Z0C 013D 250 100F BHE 1010 1011 00FA 6 0 000Z0C 013D 254 ? dm 010a 8     S2 58 14 70 36 74 18 52 ? dm 0112 0 6 15 4 95 4 83 93 33 ? | 101010         | 106 LDA<br>108 ADC<br>10A DAA<br>10B STA<br>10D DEX<br>10E DEC | A | 0103<br>0108<br>1004<br>0113<br>1008 | 3 1008<br>3 1008<br>4 1008<br>5 1008<br>5 1008<br>5 1008 | 3   | 00FC<br>00FC<br>00FC<br>00FC<br>00FB<br>00FB | 57<br>116<br>16<br>15<br>16 | 3   | 2 2 2 2 1 | 00000C<br>H0000C<br>H0000C<br>H0000C<br>H0000C | 013D<br>013D<br>013D<br>013D<br>013D<br>013D | 203<br>208<br>210<br>216<br>220        |

| 92 58 14 70 36 74 18 52  ? dm 0112 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | dm<br>?        | 1.3 57                                                         |   | 90                                   | 24                                                       | 68  | 9                                            | 75                          | 31  |           |                                                |                                              |                                        |

| dm 01112 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |                                                                |   | 14                                   | 70                                                       | 36  | 71;                                          | 18                          | 52  |           |                                                |                                              |                                        |

| 1008 LDA A 0102 1008 00FB 13 1 H0000C 013D 231 1003 ADC A 010A 100A 00FB 106 1 00N000 015D 236 100A DAA 100A 100B 00FB 6 1 0000CC 015D 238 100B STA A 0112 100D 00FB 6 1 0000CC 013D 244 100D DEX 100D 100E 00FA 6 1 0000CC 013D 248 100F DEC B 100F 100F 00FA 6 0 000Z0C 013D 250 100F BNE 1010 1011 00FA 6 0 000Z0C 013D 254 ?  dm 0102 8                                                                                                                                                                                                                                                              | dr             | 0 16                                                           |   | l <sub>t</sub>                       | 95                                                       | 4   | 83                                           | 93                          | 03  |           |                                                |                                              |                                        |

| dm 0102 8<br>13 57 90 24 68 9 75 31<br>?<br>dm 010a 8<br>52 58 14 70 36 74 18 52<br>?<br>dm 0112 8<br>6 15 4 95 4 83 93 83<br>?                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10 10 10 10 10 | DOS LDA<br>DOS ADC<br>DOA DAA<br>DOB STA<br>DOD DEX<br>DOF DEC | A | 0102<br>0104<br>1004<br>0112<br>1001 | 2 1008<br>A 1008<br>A 1008<br>2 1008<br>D 1008<br>E 1008 | 3 0 | 00FB<br>00FB<br>00FB<br>00FA<br>00FA         | 13<br>105<br>6<br>6<br>6    | В   | 1 1 1 1 0 | H0000C<br>00N000<br>00000C<br>00000C<br>00000C | 013D<br>013D<br>013D<br>013D<br>013D<br>013D | 231<br>235<br>238<br>244<br>248<br>250 |

| dm 010a 8<br>\$2 58 14 70 36 74 18 52<br>?<br>dm 0112 8<br>6 15 4 95 4 83 93 83<br>?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | dr             |                                                                |   | 90                                   | 2 lụ                                                     | 68  | ; g                                          | 75                          | 31  |           |                                                |                                              |                                        |

| ? dm 0112 8 6 15 4 95 4 83 · 93 83 ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | dn             |                                                                |   | 14                                   | 70                                                       | 36  | 74                                           | 10                          | -52 |           |                                                |                                              |                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | dr<br>?        | 0112 8 6 15                                                    |   |                                      |                                                          |     | 83                                           | 93                          | 33  |           |                                                |                                              |                                        |

READY

# APPENDIX C

COMPUTER LISTING OF THE SIM6800 SIMULATOR PROGRAM

```

OPTIONS (MAIN);

OCL 1 MOT (200),

OCL 1 MOT (200),

2 MOP FIXED BIN,

2 MODR MODE FIXED BIN,

2 TIME FIXED BIN,

2 MOT MO FIXED BIN,

OCL (1:5700,2) FIXED BIN;

OCL (5,00,0) FIXED BIN;

OCL (1:5700,2) FIXED

2

345678901234567

PRINT: PROC;

IF $HC=1 THEN DO;

PUT SKIP;

COL(1),A(2).COL(7),A(2).COL(15).A(2).COL(21).A(1).

COL(27),A(1).COL(35).A(1).COL(41).A(1).COL(47),A(1).

COL(53),A(1).COL(60).A(1));

PUT SKIP;

END;

CC_CHAR=:000000:

IF H THEN SUBSTR(CC_CHAR.2.1)=:I:;

IF N THEN SUBSTR(CC_CHAR.3.1)=:N:;

IF I THEN SUBSTR(CC_CHAR.3.1)=:V:;

IF V THEN SUBSTR(CC_CHAR.3.1)=:V:;

IF V THEN SUBSTR(CC_CHAR.3.1)=:V:;

IF C THEN SUBSTR(CC_CHAR.3.1)=:V:;

IF C THEN SUBSTR(CC_CHAR.3.1)=:V:;

CONVERT(UNSPEC(FA)).

CONVERT(UNSPEC(FA)).

3133435

36799135791

EVAL: PROC:

DCL LBL2(72) LABEL;

LBL2(19) = E19;

LBL2(20) = E20;

LBL2(20) = E50;

LBL2(20) = E50;

LBL2(20) = E20;

555666778889

LBL2(37) = £37;

LBL2(38) = £38;

LBL2(39) = £39;

LBL2(40) = £40;

LBL2(41) = £41;

LBL2(44) = £44;

LBL2(44) = £44;

LBL2(44) = £44;

LBL2(45) = £45;

LBL2(46) = £46;

LBL2(55) = £556

LBL2(56) = £557

LBL2(57) = £597

LBL2(57) = £661

LBL2(59) = £661

LBL2(61) = £661

LBL2(62) = £663

LBL2(63) = £699

LBL2(64) = £699

```

```

LAL2(65) = E65;

LBL2(66) = E66;

LBL2(67) = E67;

LBL2(68) = E68;

LBL2(69) = E69;

LBL2(70) = E70;

LBL2(71) = E71;

LBL2(72) = E99;

90048260489012334678

139

140

141

142

143

144

145

146

147

148

/* ABA */

X=ACCA: Y=ACCB;

ACCA=ACCA+ACCB;

XY=ACCA:

XY=ACCA:

CALL CODE (X,Y,XY,4,4,4,4,4,4,4,4);

RETURN;

El:

/* ADC */

IF MOT (MM) ADDR MODE >4 THEN ADDR=M(ADDR,2);

IF ACC_CODE THEN DO: X=ACCA+BIN(C);

Y=(ADDR);

ACCA=ACCA+ADDR+BIN(C);

Y=(ACCA);

END:

ELSE DO: X=(ACCB): Y=(ADDR):

ACCB=ACCB+ADDR+BIN(C):

XY=(ACCB):

END;

SACC_CODE=ACC'CODE;

CALL CODE(X,Y,XY,4,4,4,4,6,H,N,Z,V,C,ACCX);

RETURN;

/* ADD */

IF MOT(MM).ADDR_MODE >4 THEN ADDR=M(ADDR+2);

IF ACC_CODE THEN DO; X=ACCA; Y=ADDR;

ACCA=ACCA+ADDR; XY=ACCA;

END;

ELSE DO: X=ACCB: Y=ADDR;

ACCB=ACCB+ADDR; XY=ACCB;

1689

1693

1775

1779

183

E3:

CALL CODE (X.Y.XY.4.4.4.4.6.H.N.Z.V.C.ACCX);

IF ACC_CODE THEN DO: ACCA=DEC( BIT(ACCA) & BIT(M(ADDR+2)));

XY=ACCA: END:

ACCB=DEC( BIT(ACCB) & BIT(M(ADDR+2)));

XY=ACCB: END:

ACCB=DEC( BIT(ACCB) & BIT(M(ADDR+2)));

XY=ACCB: END:

CALL CODE(X,Y,XY+1+4+4+2,1,+++N+Z,V+C+ACCX);

RETURN;

/* ASL */

IF ADDR=0 THEN DO: IF ACC_CODE THEN REL=ACCA:

ELSE REL=ACCB;

END:

ELSE REL=M(ADDR.2);

BS=BIT(REL);

C=SUBSTR(BS.8.1);

SUBSTR(BS.8.7)=SUBSTR(BS.9.7);

SUBSTR(BS.15.1)='0'B;

REL=DEC(GS);

XY=REL; CALL CODE(X.Y.XY.1.4.4.1.1.H.N.Z.V.C.ACCX);

V=(N&-C); (¬N&C);

IF ADDR=0 THEN DO; IF ACC_CODE THEN ACCA=REL;

ELSE ACCB=REL;

```

```

ELSE M(ADOR . 2) = REL;

RETURN;

E6: /* ASR */

IF ADDR=0 THEN DO; IF ACC_CODE THEN REL=ACCA:

ELSE REL=ACCB;

END:

ELSE REL=M(ADDR.2);

BS=BIT(HEL);

I=SUBSTR(BS.8.1); C=SUBSTR(BS.15.1);

SUBSTR(BS.8.7)=SUBSTR(BS.9.7);

SUBSTR(BS.8.7)=I;

I='0'B;

REL=DEC(BS);

XY=REL; CALL CODE(X.Y.XY.1.4.4.1.1.H.N.Z.V.C.ACCX);

V=(N&-C) | (-N&C);

IF ADDR=0 THEN DO; IF ACC_CODE THEN ACCA=REL;

ELSE ACCB=REL;

END:

ELSE M(ADDR,2) =REL;

RETURN;

243

E7: /* BCC */

IF -C THEN PC=PC+2+ADDR;

RETURN;

246

247

248

EA: /* ACS */

IF C THEN PC=PC+2+ADDR;

RETURN;

249

E9: /* BEQ */

IF Z THEN PC=PC+2+ADDR:

RETURN;

253

E10: /* RGE */

IF (NEV) | (-N&-V) THEN PC=PC+2+ADDR:

RETURN:

255

Ell: /+ AGT */

IF (-Z) & (N&V) | (-N&-V) THEN PC=PC+2+ADDR;

RETURN;

258

259

260

E12: /* BHI */

IF (-C) & (-Z) THEN PC=PC+Z+ADDR;

RETURN;

261

262

263

264

265

E13: /* RIT */

IF ACC_CODE THEN XY=RIN( BIT(ACCA) & BIT(M(ADDR.2)) );

CALL CODE(X,Y,XY,1,4.4.2.1.H.N,Z,V,C.4CCX);

RETURN;

266

267

268

E14: /* BLE */

IF (Z) | (N&-V) | (-N&V) THEN PC=PC+2+ADDR:

RETURN:

269

270

271

E15: /* ALS */

IF (C) | (Z) THEN PC=PC+2+ADDR;

RETURN;

272

E16: /* ALT */

IF (N&-V) ! (-N&V) THEN PC=PC+2+ADDR:

RETURN:

275

276

277

E17: /* RMI */

IF N THEN PC=PC+2+ADOR;

RETURN;

278

279

280

E18: /* RNE */

IF -Z THEN PC=SPC+2+ADDR:

RETURN:

281

282

283

E19: /* APL */

IF -N THEN PC=PC+2+ADDR;

RETURN;

E20: /* ARA */

PC=PC+2+400R;

RETURN;

284

285

```

```

MAIN: PROC OPTIONS (MAIN) :

E21: /* ASR */

PC=PC+2:

SP=SP-2:

PC=PC+ADDR:

RETURN:

286

287

288

289

290

291

292

E22: /* BVC */

IF -V THEN PC=PC+2+ADDR:

RETURN;

293

294

295

E23: /* BVS */

IF V THEN PC=PC+2+ADDR:

RETURN:

E24: /* CRA */

REL=4CCA-4CCB:

X=ACCA; Y=ACCB; XY=REL;

CALL CODE(X,Y,XY,1,4,4,5,5,H,N,Z,V,C,4CCX);

RETURN;

296

297

300

301

E25: / CLC */

C=:0'8:

RETURN:

302

303

E27: /* CLR */

IF ADDR=0 THEN DO:

30459135601

IF ACC CODE THEN DO; ACCA=0: XY=ACCA; END; ELSE DO; ACCB=0; XY=ACCB; END;

END;

ELSE DO; M(ADDR-2) = 0; XY=M(ADDR-2); END;

CALL CODE(X+Y+XY+1+2+3+2+2+H+N+Z+V+C+ACCX);

RETURN;

E28: / CLV ./

322

323

RETURN:

E29: /* CMP */

IF ACC_CODE THEN REL=ACCA;

ELSE REL=ACCB;

X=REL: Y=ADDR!

REL=REL-ADDR:

XY=REL: CALL CODE(X.Y.XY.1.4.4.5.5.H.N.Z.V.C.ACCX):

IF REL<0 THEN N='1'R:

IF REL=0 THEN Z='1'B:

RETURN;

33344468923

E30: /* COM */

IF ADDR=0 THEN DO: IF ACC_CODE THEN DO: ACCA=DEC(-BIT(ACCA));

XY=ACCA: END:

ELSE DO: ACCB=DEC(-BIT(ACCB));

XY=ACCB: END:

END:

ELSE DO: M(ADDR+2) = DEC(\BIT(M(ADDR+2))): END;

CALL CODE(X,Y,XY+1,4+4+2+3,H,N+Z,Y+C+ACCX):

RETURN;

354

355

356

357

359

E32: /* DAA */

CALL CODE(X,Y,XY,1,4,4,2,7,H,N,Z,V,C,ACCX):

IF $ACC_CODE THEN ACCA=ACCX:

ELSE ACCB=ACCX:

360

361

363

364

E34: /* DES */

SP=SP-1;

RETURN;

365

366

E36: /* EOR */

IF ACC CODE THEN DO:

ACCA=DEC((RIT(ACCA)&-BIT(M(ADDR.2))) | (-BIT(ACCA)&BIT(M(ADDR.2))));

XY=ACCA; END;

ELSE DO:

ACCB=DEC((BIT(ACCB)&-BIT(M(ADDR.2))) | (-BIT(ACCB)&BIT(M(ADDR.2))));

XY=ACCB; END;

367

368

369

377

3773

```

```

CALL CODE (X.Y.XY.1.4.4.2.1, H.N.Z.V.C.ACCX) ; RETURN;

E37: /* INC */

IF ADDR ==0 THEN DO; X=M(ADDR.2); M(ADDR.2) = M(ADDR.2) +1;

XY=M(ADDR.2); END;

ELSE DO; IF ACC_CODE THEN DO; X=ACCA; ACCA=ACCA-1;

XY=ACCA; END;

ELSE DO; X=ACCB; ACCB=ACCB+1;

XY=ACCR; END;

378

3792

384

388

399

399

401

END;

CALL CODE (X+Y+XY+1+4+4+1+1+++N+Z+V+C+ACCX);

IF X=127 THEN V='1'B; ELSE V='0'B;

RETURN;

E38: /* INS */

SP=SP+1;

RETURN;

402

403

404

405

E40: /* JUMP */

PC=ADDR;

RETURN;

408

419

E33: /* DEC */

IF ADDR == 0 THEN DO;

X=8IT(M(ADDR.2));

M(ADDR.2)=M(ADDR.2)-1;

XY=8IT(M(ADDR.2));

G0 T0 E333;

END;

IF ACC_CODE THEN DO; X=(A)

111234567012367892

14111112222222223

X=(ACCA);

ACCA=ACCA-1;

XY=(ACCA);

END:

ELSE DO: X=(ACCB): ACCB=ACCB-1:

XY=(ACCB):

XY=(ACCH);

END;

END;

CALL CODE(X+Y+XY+1+4+4+1+1+H+N+Z+V+C+ACCX);

IF BIN(X)>80 THEN V=+1+8; ELSE V=+0+8;

RETURN;

433

434

435

436

E41: /* JSR */

EA=SP-1;

M(SP,2)=PC;

SP=SP-2;

PC=ADDR;

RETURN;

437

438

439

440

441

442

443

444

453

454

E42: /* LDA */

IF MOT(MM).ADDR MODE >4 THEN ADDR=M(ADDR.2);

IF ACC_CODE THEN DO: ACCA=ADDR: XY=(ACCA); END:

ELSE DO: ACCB=ADDR: XY=(ACCB); END:

CALL CODE(X,Y,XY,1,4,4,4,2,1,++,N,Z,V,C,ACCX);

RETURN;

45567890

E43: /* LDS */

IF MOT(MM).ADDR_MODE >4 THEN ADDR=M(ADDR.2);

SP=ADDR;

XY=(SP);

CALL CODE(X.Y.XY.1.4.4.2.1.H.N.Z.V.C.ACCX);

RETURN;

E44: /* LDX */

IF MOT(MM) .4DDR_MODE >4 THEN DO: ADDR=M(ADDR,2);

461

463

465

465

466

468

END:

[X=ADDR:

XY=(IX):

CALL CODE(X+Y+XY+1+4+4+2+1+H+N+Z+V+C+ACCX):

RETURN:

```

```

E45: /* LSR */

IF ADDR=0 THEN DO: IF ACC_CODE THEN REL=ACCA:

ELSE REL=ACCB:

4477456778901348901

44776778901348901

END:

ELSE REL=M(ADDR, 2);

RS=RIT(REL);

C=SUBSTR(BS, 15, 1);

SUBSTR(BS, 8, 7) = SUBSTR(BS, 9, 7);

SUBSTR(BS, 8, 1) = *0 * R;

REL=DEC(BS);

XY=REL; CALL CODE(X, Y, XY, 1, 2, 4, 1, 1, H, N, Z, V, C, ACCX);

V=(N& -C) | (-N&C);

IF ADDR=0 THEN DO; IF ACC_CODE THEN ACCA=REL;

ELSE ACCB=REL;

END:

ELSE M(ADDR.2) =REL:

RETURN:

E46: /* NEG */

IF ACC_CODE THEN DO: X=ACCA: ACCA=0-4CCA: XY=ACCA: END: ELSE DO: X=ACCB: ABBB=0-4CCB: XY=ACCB: END:

2348035691258

444455555555555

519

E47: /* NOP */

E49: /* PSH */

IF ACC_CODE THEN M(SP.2) = ACCB;

ELSE M(SP.2) = ACCB;

531

533

533

534

535

SP=SP-1;

E50: /* PUL */

SP=SP+1:

IF ACC_CODE THEN ACCA=M(SP+2):

ELSE ACCB=M(SP+2):

536

E51: /* ROL */

IF ADDR=0 THEN DO; IF ACC_CODE THEN REL=ACCA;

ELSE REL=ACCB;

1-205-67-89-01-205-457-803-45

44444444555555555566666

END:

ELSE REL=M(ADDR.2);

RS=BIT(REL);

I=C;

C=SUBSTR(BS.8.1);

SUBSTR(BS.8.7)=SUBSTR(BS.9.7);

SUBSTR(BS.15.1)=I;

I='0'B;

REL=DEC(BS);

XY=REL; CALL CODE(X.Y.XY.1.4.4.1.1.H.N.Z.V.C.4CCX);

V=(N&-C) | (¬N&C);

IF ADDR=0 THEN DO; IF ACC_CODE THEN ACCA=REL;

ELSE ACCB=REL;

END:

ELSE M(ADDR.2) =REL;

RETURN:

E52: /* ROR */

IF ADDR=0 THEN DO: IF ACC_CODE THEN REL=ACCA;

ELSE REL=ACCB;

5667

570

571

572

END:

ELSE PEL=M(ADDR.2);

```

```

BS=BIT(REL);

I=SUBSTR(BS.15,1);

SUBSTR(BS.8,7)=SUBSTR(BS.8,7);

SUBSTR(BS.8,1)=C;

C=I;

I=:0,9;

REL=DEC(BS);

XY=REL; CALL CODE(X.Y.XY.1.4,4,1.1.H.N.Z.V.C.ACCX);

V=(N&-C) | (¬N&C);

IF ADDR=0 THEN DO; IF ACC_CODE THEN ACCA=REL;

ELSE ACCB=REL;

END:

ELSE M(ADDR.2) =REL;

RETURN;

E54: /* RTS */

SP#SP+2:

PC=M(SP+2);

E4=SP:

RETURN:

591

592

593

594

E55: /* SBA */

ACCA=ACCA-ACCB:

RETURN:

595

596

E56: /* SBC */

IF MOT(MM).ADDR_MODE >4 THEN ADDR=M(ADDR.2):

IF ACC_CODE THEN ACC4=ACC4-ADDR-C;

ELSE ACC8=ACC8-ADDR-C;

597

598

599

601

E57: /* SEC */

C=:1'8:

RETURN:

603

604

E59: /* SEV */

V=*1*B:

RETURN:

605

606

E60: /* STA */

IF ACC_CODE THEN DO: M(ADDP, 2) =ACCA:

XY=(ACCA);

6078611124567

END:

ELSE DO: M(ADDR.2)=ACCB;

XY=(ACCB);

CALL CODE (X,Y,XY,1,4,4,4,2,1,H,N,Z,V,C,ACCX);

RETURN:

E61: /* STS */

M(ADDR,2)=SP:

XY=SP: CALL CODE(X,Y,XY.1,4.4.2,1,H.N.Z.V.C.ACCX):

RETURN:

618

622

623

E63: /* SUB */

IF MOT(MM).ADDR MODE > 4 THEN ADDR=M(ADDR,2);

IF ACC_CODE THEN ACCA=ACCA-ADDR;

ELSE ACCB=ACCB-ADDR;

626

627

628

631

RETURNI

E65: /* TAB */

ACCB=ACCA;

XY=ACCB; CALL CODE(X,Y,XY,1,4,4,2,1,+H,N,Z,V,C,ACCX);

RETURN;

632

633

E66: /* TAP */

BS=RIT(ACCA);

CC=SUBSTR(BS:10:6):

N=SUBSTR(CC:1:1): I=SUBSTR(CC:2:1): N=SUBSTR(CC:3:1):

Z=SUBSTR(CC:4:1): V=SUBSTR(CC:5:1): C=SUBSTR(CC:6:1):

RETURN:

636

637

638

641

644

E67: /* TBA */

ACCA=ACCB;

XY=ACCA; CALL CODE(X,Y,XY,1,4,4,2,1,H,N,Z,V,C,ACCX);

RETURN;

645

646

```

```

E68: /* TPA */

CC=H || I || N || Z || V || C;

SUBSTR(BS:8:2)=:11:9;

SUBSTR(BS:10:6)=CC;

ACCA=DEC(BS);

RETURN;

649

650

651

653

6558

6558

6666

6662

E69: /* TST */

IF ADDR=0 THEN DO: IF ACC_CODE THEN XY=ACCA:

ELSE XY=ACCB;

ELSE XY=ACC

ELSE XY=M(ADDR+2);

CALL CODE(X,Y,XY+1,4+4+2+2+H+N+Z+V+C+ACCX);

RETURN;

E70: /* TSX */

IX=SP+1;

RETURN;

663

664

E71: /* TXS */

SP=[X-1;

RETURN;

665

666

E99: RETURN:

ADDRESS: POOC:

OCL ONE FIXED AIN. XX BIT(15);

OCL LAL1(7) LAREL;

LAL1(1)=A1;

LBL1(2)=A2;

LAL1(3)=A3;

LBL1(4)=A4;

LBL1(5)=A5;

LBL1(6)=A6;

LBL1(7)=A7;

IF (MOT(MM).ADDR_ACC='A') THEN ACC_CODE='1'R;

ELSE IF (MOT(MM).ADDR_ACC='B') THEN ACC_CODE='0'B;

GO TO LBL1(MOT(MM).ADDR_MODE);

669

6671

6671

6673

6676

6677

6679

6683

/* INHERENT */

EA=$PC:

RETURN:

684

685

/* RELATIVE */

EA=$PC+1;

IF RYTE2>=240 THEN BYTE2=(255-BYTE2+1) * (-1);

ADDR=BYTE2;

RETURN;

686

689

690

/* [MMEDIATE */

IF MOT(MM).MOT_NO = 31 |

MOT(MM).MOT_NO = 43 |

MOT(MM).MOT_NO = 44 THEN EA=$PC+2;

ELSE EA=$PC+1;

ADDR=BYTE2;

RETURN;

691

43:

693

693

694

/* ACCUMULATOR */

EA=$PC;

AODR=0;

RETURN;

696

697

/* INDEXED */

EA=BYTE2+IX;

ADDR=BYTE2+IX;

RETURN;

699

A5:

700

/* EXTENDED */

ADDR=8Y1E2;

EA=ADDR+1;

RETURN;

702

703

/* DIRECT */

ADDR=RYTE2;

EA=ADDR+1;

RETURN;

705

706

708

END ADDRESS:

```

```

LKUP: PROC;

00 MM=1 BY 1 TO 197;

IF M(PC.1)=MOT(MM).OP THEN GO TO LK1;

END;

709

710

711

713

714

LK1:

END LKUP!

CODE: PROC(XX.YY.XYXY.C1.C2.C3.C4.C5,H.N.Z.V.C.ACCX);

OCL (H.N.Z.V.C) BIT(1);

OCL (C1.C2.C3.C4.C5) FIXED BIN;

OCL (X.Y.XY) BIT(15) INIT( (15) '0'8);

OCL (XX.YY.XYXY.ACCX.L0.UP) FIXED BIN;

OCL (BITUP.BITLO) BIT(15);

OCL (LBL3(4).LBL4(4).LBL5(4).LBL6(5).LBL7(5)) LABEL;

715

716

717

718

719

720

721

LBL3(1) = CC2! LBL4(1) = CC3: LBL5(1) = CC4: LBL6(1) = CC5: LBL7(1) = CC6: LBL3(2) = HC1: LBL4(2) = NC1: LBL5(2) = ZC1: LBL6(2) = VC1: LBL7(2) = CC1: LBL3(3) = HS: LBL4(3) = NS: LBL5(3) = ZS: LBL6(3) = VS: LBL7(3) = CS: LBL3(4) = HP: LBL4(4) = NP: LBL5(4) = ZP: LBL6(4) = VP: LBL7(4) = CP: LBL3(4) = HP: LBL4(4) = NP: LBL5(4) = ZP: LBL6(5) = VP2: LBL7(5) = CP2: LBL3(4) = HP: LBL4(4) = NP: LBL5(4) = ZP: LBL6(5) = VP2: LBL7(5) = CP2: LBL3(4) = LB

722

727

732

737

742

UP=XX/10; BITUP=BIT(UP);

L0=XX-FLOOR(XX/10)*10; BITLO=BIT(LO);

SUBSTR(X,8.8)=SUBSTR(BITUP+12.4); UP=YY/10; BITUP=BIT(UP);

L0=YY-FLOOR(YY/10)*10; BITLO=BIT(LO);

SUBSTR(Y,8.4)=SUBSTR(BITUP+12.4); If SUBSTR(BITLO+12.4);

IF C5<=5 THEN O0;

UP=XYXY/10; BITUP=BIT(UP);

L0=XYXY-FLOOR(XYXY/10)*10; BITLO=BIT(LO);

SUBSTR(XY,8.8)=SUBSTR(BITUP+12.4); If SUBSTR(BITLO+12.4);

END;

ELSE DO;

UP=BIN(SUBSTR(X,8.4)) + BIN(SUBSTR(Y,8.4));

L0=BIN(SUBSTR(X,8.4)) + BIN(SUBSTR(Y,8.4));

IF L0>=16 THEN DO; L0=L0-16; UP=UP+1; END;

BITUP=BIT(UP); BITLO=BIT(LO);

SUBSTR(XY,8.8)=SUBSTR(BITUP+12.4); If SUBSTR(BITLO+12.4);

ENO;

IF C5=6 THEN C5=4;

IF C5<7 THEN GO TO CC1;

L0=BIN(SUBSTR(XY,8.4));

IF L0>=16 THEN DO; L0=L0-6;

UP=BIN(SUBSTR(XY,8.4));

IF L0>=16 THEN DO; L0=L0-16; UP=UP+1; END;

IF L0>=16 THEN DO; L0=L0-16; UP=UP+1; END;

IF UP>BIN(SUBSTR(XY,8.4));

IF L0>=16 THEN DO; L0=L0-16; UP=UP+1; END;

IF UP>BIN(SUBSTR(XY,8.4));

IF L0>=16 THEN DO; L0=L0-16; UP=UP+1; END;

IF UP>BIN(SUBSTR(XY,8.4));

IF UP>BIN(SUBSTR(XY,8.4));

IF UP>BIN(SUBSTR(XY,8.4));

IF UP>BIN(SUBSTR(XY,8.4));

IF UP>BIN(SUBSTR(XY,8.4));

IF UP>BITLO=BIT(LO);

XY='00000000'B !! SUBSTR(BITUP+12.4) !! SUBSTR(BITLO+12.4)!;

ACCX=BIN(SUBSTR(BITUP+12.4))*10 + BIN(SUBSTR(BITLO+12.4));

C5=1;

CC1: GO TO L9L3(C1);

798

799

801

803

804

807

807

811

815

CC4:

816

817

819

821

```

```

VP2: V=( SUBSTR(X+8+1) & ¬SUBSTR(Y+8+1) & ¬SUBSTR(XY+8+1));

CC5: GO TO LALT(CA);

CCL: C=+0+9; GO TO CC6;

CS: C=+1+8; GO TO CC6;

CP: C=( SUBSTR(X+8+1) & SUBSTR(Y+8+1));

( SUBSTR(X+8+1) & SUBSTR(XY+8+1));

( TOURSTR(X+8+1) & SUBSTR(XY+8+1));

GO TO CC6;

CP2: C=(¬SUBSTR(X+8+1) & SUBSTR(XY+8+1));

( SUBSTR(X+8+1) & SUBSTR(X+8+1));

( SUBSTR(X+8+1) & SUBSTR(X+8+1));

( SUBSTR(X+8+1) & SUBSTR(XY+8+1));

( SUBSTR(X+8+1) & SUBSTR(XY+8+1));

( SUBSTR(X+8+1) & SUBSTR(XY+8+1));

CC6: RETURN;

END COOE;

823

CONVERT: PROC(A) RETURNS(CHAR(16) VAR);

OCL A ARIT(*), HEXREP CHAR(16) VAR INIT(''),

HEX_DIGITS CHAR(16) INIT('0123456789ARCDEF') STATIC,

TABLE(0:15) CHAR(1) DEF HEX_DIGITS*DIGIT FIXED BIN(4);

LP: DO K=1 BY 1 TO LENGTH(A)/4;

OIGIT=SUBSTR(A,4*K-3,4);

HEXREP=HEXREP||TABLE(DIGIT);

END LP;

RETURN(HEXREP);

END CONVERT;

836

837

838

840

841

CON: PROC(CHAREP) RETURNS(FIXED BIN(15));

DCL CHAREP CHAR(4);

DCL BITS FIXED BIN;

DCL DIGIT CHAR(15) INIT(*123456789AB;

BITS=0;

OO II=1 BY 1 TO 4;

K=INDEX (DIGIT.SUBSTR(CHAREP,II.1));

BITS=BITS+(K) * (16 * * (4-II));

END;

RETURN(BITS);

END CON;

844456789012

8484456789012

INIT( 123456789ABCDEF 1) 1

SIM: PROC:

IA=PC:

CALL EVAL:

CALL EVAL:

IF ERR THEN RETURN:

ADOR=0:

SHC=SHC+1:

IF SHC+HC THEN SHC=1:

CALL PRINT:

RETURN:

END SIM;

855557901345

888888888888

CREATEL: PROC!

00 MM=1 BY 1 TO 197:

GET FILE(DSM) EDIT(MOT(MM))

(COL(1),F(3),COL(5),A(3),COL(9),F(1),COL(11),F(1),COL(13),F(1),

COL(15),F(2),COL(18),A(1));

ENO:

RETURN:

ENO CREATEL:

866

868

CREATE: PROC:

ON ENOFILE(DSO) GO TO INEND:

OO WHILE('1'8):

GET FILE(DSO) LIST(NN.N1.N2):

M(NN.1)=N1:

4(NN.2)=N2:

END:

INEND: RETURN:

END CREATE2:

8773

8776

8778

8778

878

881

ON ERROR BEGIN;

PUT SKIP;

PUT EDIT('**** ERROR 302 ', Y0,

'POSSIBLE SYNTAX ERROR IN SIMULATOR COMMAND')

(COL(1), A(15), COL(17), A(2), SKIP, COL(1), A);

PUT SKIP;

GO TO MSTRT;

884

886

GO TO WSINE

STRT:

```

```

PUT EDIT('SIMULATOR FOR THE MOTOROLA M6800 MICROPROCESSOR',

'WRITTEN FOR THE IBM 360',

'VERSION 1 1976')

(COL(5), A+SKIP, COL(15), A+SKIP, COL(15), A);

PUT SKIP;

890

891

MINT: CALL CREATEL:

MINT: CALL CREATE1:

CALL CREATE2:

MSTRT:

PUT SKIP:

PUT EDIT('?') (COL (1) , A (1)):

PUT SKIP:

PUT SKIP:

PUT SKIP:

PUT SKIP:

PUT SKIP:

READ FILE (SYSIN) INTO (BUFFER):

ZO=VERIFY (BUFFER, ''):

BUFFER=SUBSTR (BUFFER, ''):

BUFFER=SUBSTR (BUFFER, ZO):

ZO=INDEX (COMMAND, YO):

IF ZO=O THEN DO:

PUT SKIP:

PUT EDIT('**** ERROR 301 '.YO,

'UNDEFINED SIMULATOR COMMAND')

(COL (1) , A (15) , COL (17) , A (2) , SKIP , COL (1) , A):

PUT SKIP:

GO TO MSTRT:

ZO=(ZO+) | MA:

LBL3(Z) = MS:

LBL

894

895

896

897

898

9090112344567890

99999999999

Z2. (M(Z3.2) 00 Z3=71 TO 70));

/* DISPLAY MEMORY */

Z0=VERIFY (BUFFER.: '):

BUFFER=SUBSTR (BUFFER.Z0):

GET STRING (BUFFER) EDIT (CHAREP) (A (4)):

Z0=INDEX (BUFFER,'):

RUFFER=SUBSTR (BUFFEP.Z0):

GET STRING (BUFFER) LIST (Z2):

Z1=CON (CHAREP):

Z2=Z2-Z1-1:

Z0=MOD (Z2-12):

IF Z0=0 THEN Z0=Z2/12:

ELSE Z0=Z2/12+1:

PUT EDIT ((M(Z3-2) DO Z3=Z1 TO Z2)) ((Z0) (12 F(5) .SKIP)):

GO TO MSTRI:

930

15M

9333456789123

M3: /* SET REGISTERS */

Z0=vERIFY(BUFFER.'');

BUFFER=SUBSTR(BUFFER.Z0);

GET STRING(AUFFER) EDIT(Y1)(A(1));

Z0=INDEX(BUFFER.'');

BUFFER=SUBSTR(BUFFER.Z0);

Z0=vERIFY(BUFFER.Z0);

Z0=vERIFY(BUFFER.Z0);

Z0=INDEX(REGISTER.Y1);

IF Z0=4 THEN GO TO M3_2;

IF Z0=4 THEN GO TO M3_3;

M3_1: GET STRING(BUFFER) EDIT(CHAREP)(A(4));

IF Z0=1 THEN PC=CON(CHAREP);

IF Z0=3 THEN SP=CON(CHAREP);

IF PC>5000 | SP>5000 | IX>5000 THEN DO;

PUT SKIP;

944

945

```

```

PUT EDIT( **** ERROR 306 *.Y1,

'THE OPERANO IN THE SIMULATOR COMMAND *.

'CAUSED A REGISTER OVERFLOW!)

(COL(1), A(15), COL(17), A(1), SKIP, COL(1), A, SKIP, COL(1), A);

PUT SKIP;

GO TO MSTRT;

END;

GO TO MSTRT;

IF Z0=5 THEN ACCA=Z1;

IF Z0=5 THEN ACCB=Z1;

IF Z0=7 THEN T=Z1;

GO TO MSTRT;

966

967

969

970

971

971

977

977

9778

979

980

983

986

M3_3: GET STRING(BUFFER) EDIT(CC)(B(6));

H=SUBSTR(CC.1.1); I=SUBSTR(CC.2.1); N=SUBSTR(CC.3.1);

Z=SUBSTR(CC.4.1); V=SUBSTR(CC.5.1); C=SUBSTR(CC.6.1);

GO TO MSTRT;

/* RUN */

GET STRING(RUFFER) LIST(Z1);

DO ZZ=1 BY 1 TO Z1;

CALL SIM;

IF ERR THEN GO TO MSTRT;

END;

GO TO MSTRT;

987

M4:

988

989

990

990

993

/* SET HEADER COUNT */

GET STRING(BUFFER) LIST(Z1);

HC=Z1;

$HC=0;

GO TO MSTRT;

994

M5:

995

996

997

/* DISPLAY REGISTERS */

CALL PRINT:

GO TO MSTRT;

999

M6:

999

M7: /* EXIT */

1000

```

# **BIBLIOGRAPHY**

- Cohen, Leo J. Operating System Analysis and Design.

Rochelle Park, N.J.: Hayden Book Company, Inc., 1970.

- M6800 Microprocessor Programming Manual. Motorola Semiconductor Products, Inc., 1975.

- Ogdin, Jerry L. "Microprocessors: The Inevitable Technology." Modern Data 8 (January 1975): 42-47.

- O'Malley, John. <u>The Digital Computer.</u> New York: Holt, Rinehart, and Winston, Inc., 1972.

- Struble, George. <u>Assembler Language Programming: The IBM System/360.</u> Reading, Massachusetts: Addison-Wesley Publishing Company, 1971.