Electronic Theses and Dissertations, 2004-2019

2019

# Leveraging the Intrinsic Switching Behaviors of Spintronic Devices for Digital and Neuromorphic Circuits

Steven Pyle University of Central Florida

Part of the Computer Engineering Commons

Find similar works at: https://stars.library.ucf.edu/etd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### STARS Citation

Pyle, Steven, "Leveraging the Intrinsic Switching Behaviors of Spintronic Devices for Digital and Neuromorphic Circuits" (2019). *Electronic Theses and Dissertations, 2004-2019.* 6292. https://stars.library.ucf.edu/etd/6292

# LEVERAGING THE INTRINSIC SWITCHING BEHAVIORS OF SPINTRONIC DEVICES FOR DIGITAL AND NEUROMORPHIC CIRCUITS

by

#### STEVEN D. PYLE M.S. University of Central Florida 2015

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering in the College of Engineering and Computer Science at the University of Central Florida

Orlando, Florida

Spring Term 2019

Major Professor: Ronald F. DeMara

© 2019 Steven D. Pyle

#### **ABSTRACT**

With semiconductor technology scaling approaching atomic limits, novel approaches utilizing new memory and computation elements are sought in order to realize increased density, enhanced functionality, and new computational paradigms. Spintronic devices offer intriguing avenues to improve digital circuits by leveraging *non-volatility* to reduce static power dissipation and vertical integration for increased density. Novel hybrid spintronic-CMOS digital circuits are developed herein that illustrate enhanced functionality at reduced static power consumption and area cost. The developed spin-CMOS D Flip-Flop offers improved power-gating strategies by achieving instant store/restore capabilities while using 10 fewer transistors than typical CMOS-only implementations. The spin-CMOS Muller C-Element developed herein improves asynchronous pipelines by reducing the area overhead while adding enhanced functionality such as instant data store/restore and delay-element-free bundled data asynchronous pipelines.

Spintronic devices also provide improved scaling for neuromorphic circuits by enabling compact and low power neuron and non-volatile synapse implementations while enabling new neuromorphic paradigms leveraging the stochastic behavior of spintronic devices to realize stochastic spiking neurons, which are more akin to biological neurons and commensurate with theories from computational neuroscience and probabilistic learning rules. Spintronic-based Probabilistic Activation Function circuits are utilized herein to provide a compact and low-power neuron for Binarized Neural Networks. Two implementations of stochastic spiking neurons with alternative speed, power, and area benefits are realized. Finally, a comprehensive neuromorphic architecture comprising stochastic spiking neurons, low-precision synapses with *Probabilistic*

Hebbian Plasticity, and a novel non-volatile homeostasis mechanism is realized for subthreshold ultra-low-power unsupervised learning with robustness to process variations. Along with several case studies, implications for future spintronic digital and neuromorphic circuits are presented.

#### ACKNOWLEDGMENTS

Life is a funny thing. In a universe compelled towards maximizing entropy, life seems to boldly run up stream. The life of each individual is more peculiar still, for by no will of their own they are given a will and thrust into reality and consciousness, expected to make something useful out of it. Most people find their meaning traveling down the path well worn, changing things little, but making the most of it where they can. Some people are lucky enough to meet the right people at the right time who give them the tools to forge new paths into a bigger world of possibilities then they ever thought was possible. I consider myself ridiculously lucky and eternally grateful for the people that chance, fate, God, or what-have-you graciously brought into my life at just the right times to elicit the immense personal growth that made this dissertation, and my future, possible.

I want to specifically thank my parents, who gave me the freedom and support to explore any direction my heart desired. I must thank Dr. Ronald F. DeMara and the shear seconds of coincidence that lead me to his class, for his unrelenting willfulness to teach, inspire, discuss, include, help, support, and take-the-kid-gloves-off was so much of what I needed that I will never be able to fully express my gratefulness for that man. I want to thank Dr. Deliang Fan, who's research and classwork on neuromorphic architectures helped to lay the bedrock for much of this dissertation. I want to thank Dr. Pamela Douglas, who introduced me to the circuits and large-scale behaviors of the brain and encouraged me in my exploration of bold new paths. I want to thank Drs. Reza Abdolvand, Mingjie Lin, and Vikram Kapoor for their kind words, encouragement, and support on my dissertation committee. I want to thank Ramtin Zand, Soheil Salehi, Arman Roohi, and Navid Khoshavi for the endless hours of quality conversation that undoubtable shaped myself

and my work. Finally, I must thank Orlando Arias, who was always able to help me debug what stack exchange could not.

# **TABLE OF CONTENTS**

| LIST OF FIGURES                                     | xii |

|-----------------------------------------------------|-----|

| LIST OF TABLES                                      | xvi |

| CHAPTER ONE: INTRODUCTION                           | 1   |

| Need for Spintronic Circuits                        | 1   |

| Spintronic Technology                               | 2   |

| Spintronic Approaches for Digital Circuits          | 5   |

| Spintronic Approaches for Neuromorphic Circuits     | 5   |

| Contributions of the Dissertation                   | 8   |

| CHAPTER TWO: PREVIOUS WORKS                         | 11  |

| Previous Spintronic Approaches for Digital Circuits | 11  |

| Previous Approaches for Neuromorphic Circuits       | 14  |

| Probabilistic Bits                                  | 17  |

| Spin-Hall Effect Probabilistic Bit                  | 18  |

| Embedded Probabilistic Bit                          | 19  |

| CHAPTER THREE: HYBRID SPIN-CMOS DIGITAL CIRCUITS    | 21  |

| Domain Wall Coupled Spin Transfer Torque Device     | 22  |

| Compact Instant Store/Restore D Flip-Flop           | 23  |

| Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 28 |

| Spintronic Muller C-Element                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29 |

| Overview of Asynchronous Pipelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30 |

| Proposed Spintronic Muller C-Element Designs                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 33 |

| Spintronic Muller C-Element Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 34 |

| Asynchronous Pipeline Simulation and Results                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 39 |

| Discussion  Spintronic Muller C-Element  Overview of Asynchronous Pipelines  Proposed Spintronic Muller C-Element Designs  Spintronic Muller C-Element Results  Asynchronous Pipeline Simulation and Results  Discussion  Summary  CHAPTER FOUR: BINARIZED DEEP NEURAL NETWORKS WITH STOCHASTIC SPINTRONIC NEURONS  Background  Binary Neural Networks  Recent Work on Binary Neural Network Hardware Acceleration  Accelerator Design  Pseudo-Crossbar Array  Probabilistic Activation Function Circuit | 42 |

| Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 43 |

| CHAPTER FOUR: BINARIZED DEEP NEURAL NETWORKS WITH STOCHASTIC                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| SPINTRONIC NEURONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 44 |

| Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 46 |

| Binary Neural Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 46 |

| Recent Work on Binary Neural Network Hardware Acceleration                                                                                                                                                                                                                                                                                                                                                                                                                                               | 48 |

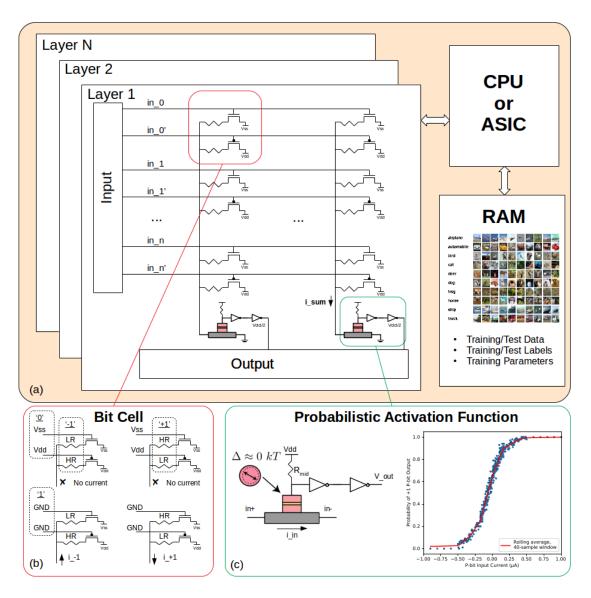

| Accelerator Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50 |

| Pseudo-Crossbar Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 51 |

| Probabilistic Activation Function Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 53 |

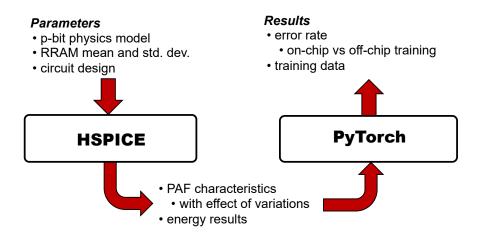

| Simulation Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 54 |

| HSPICE Simulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54 |

| PyTorch Simulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 55 |

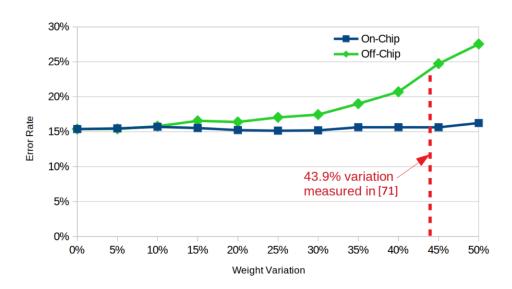

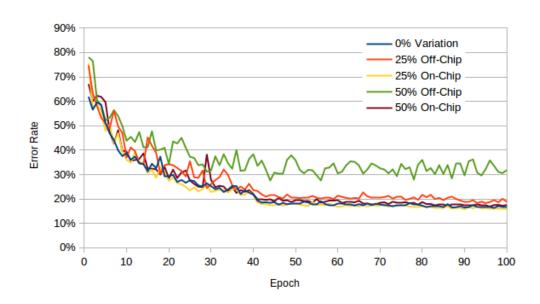

| On-Chip vs Off-Chip Training                                           | 56               |

|------------------------------------------------------------------------|------------------|

| Results                                                                | 57               |

| Summary                                                                | 58               |

| CHAPTER FIVE: SPINTRONIC STOCHASTIC SPIKING NEURONS                    | 60               |

| Spintronic Stochastic Spiking Neuron                                   | 60               |

| Second Order Synapse                                                   | 61               |

| Results                                                                | 63               |

| Discussion                                                             | 68               |

| Subthreshold Spintronic Stochastic Spiking Neuron                      | 71               |

| Circuit Overview                                                       | 71               |

| Results                                                                | 76               |

| Summary                                                                | 80               |

| CHAPTER SIX: NEURAL SAMPLING CORE                                      | 82               |

| Previous Work on Stochastic Spiking Neural Network Hardware with Unsup | ervised Learning |

|                                                                        | 84               |

| Neural Sampling Theory                                                 | 86               |

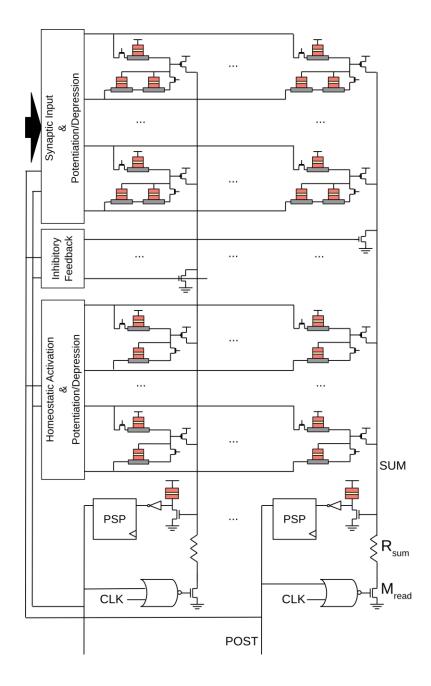

| Circuits of the Neural Sampling Core                                   | 86               |

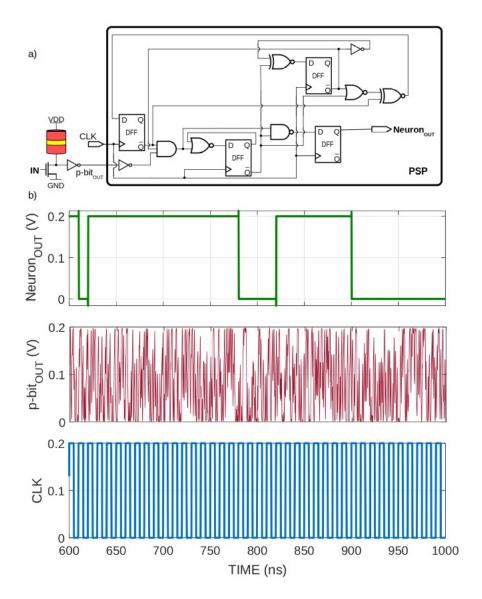

| Stochastic Spiking Neuron with Digital Post-Synaptic Potentials        | 87               |

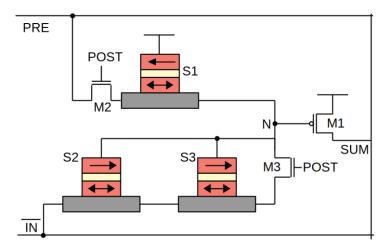

| Hybrid Synanse with Probabilistic Hebbian Plasticity                   | 88               |

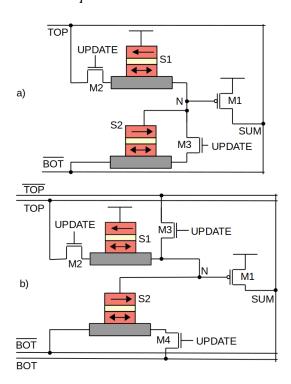

| Non-Volatile Homeostasis Mechanism                           | 91  |

|--------------------------------------------------------------|-----|

| Inhibition Mechanism                                         | 93  |

| Architectural Discussion                                     | 93  |

| Simulation Framework                                         | 97  |

| Stochastic Spiking Neuron Circuit Simulation Results         | 97  |

| Synapse Simulation Results                                   | 100 |

| Update Phase                                                 | 103 |

| Architecture Results                                         | 104 |

| Unsupervised Learning                                        | 104 |

| Noise Analysis                                               | 108 |

| Power Analysis                                               | 110 |

| Summary                                                      | 111 |

| CHAPTER 7: CONCLUSION                                        | 112 |

| Summary of the Developed Circuits and Techniques             | 112 |

| Complementary Switching in Hybrid Spin-CMOS Digital Circuits | 113 |

| Stochastic Switching for Neuromorphic Circuits               | 114 |

| Lessons Learned and Limitations                              | 116 |

| Future Work                                                  | 118 |

| APPENDIX: COPYRIGHT PERMISSIONS                              | 119 |

| REFERENCES 12 |

|---------------|

|---------------|

# **LIST OF FIGURES**

| Figure 1: Illustration of the MTJ stack, high resistance state, and low resistance state          |

|---------------------------------------------------------------------------------------------------|

| Figure 2: Typical neuromorphic crossbar architecture with synapses and neurons                    |

| Figure 3: Taxonomy of spintronic technologies and architectures with their associated             |

| characteristics                                                                                   |

| Figure 4: p-bit device schematic and equivalent READ circuit: (a) The gray layer represents a     |

| heavy metal (HM) exhibiting the Spin Hall Effect (SHE) that injects a spin current into an        |

| adjacent "free layer" of a Magnetic Tunnel Junction. The free layer is a circular magnet with no  |

| preferred easy axis (EB=0 kT) that fluctuates in the z-x plane in the presence of thermal noise.  |

| The MTJ is connected to an average resistance R0 creating a fluctuating voltage that is amplified |

| by two inverters. (b) The circuit equivalent READ circuit is also shown                           |

| Figure 5: Embedded p-bit circuit                                                                  |

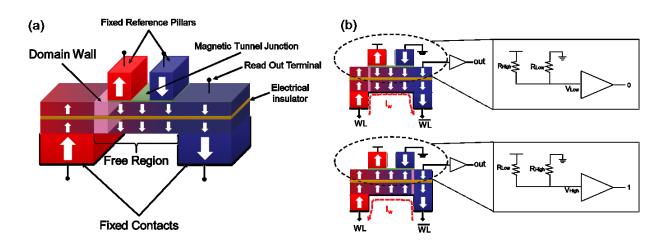

| Figure 6 (a): Domain Wall Coupled Spin Transfer Torque Device; (b): Low and High states 22        |

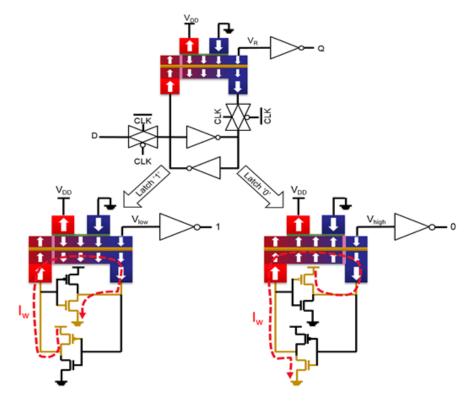

| Figure 7: The compact hybrid spin-CMOS D F/F circuit with non-volatile input latching 25          |

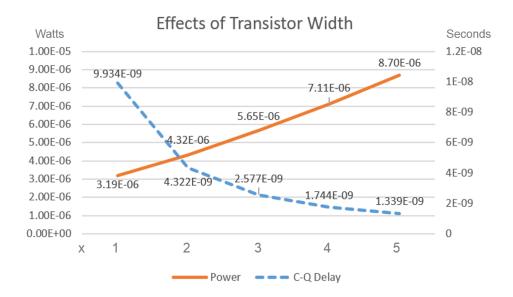

| Figure 8: The effects of transistor width on power and C-Q delay of the compact hybrid Spin-      |

| CMOS D F/F                                                                                        |

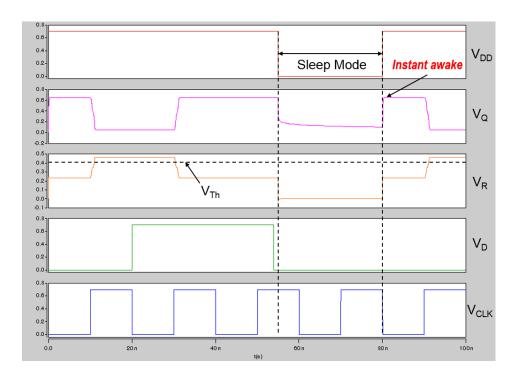

| Figure 9: Simulated waveforms of the compact hybrid spin-CMOS D F/F                               |

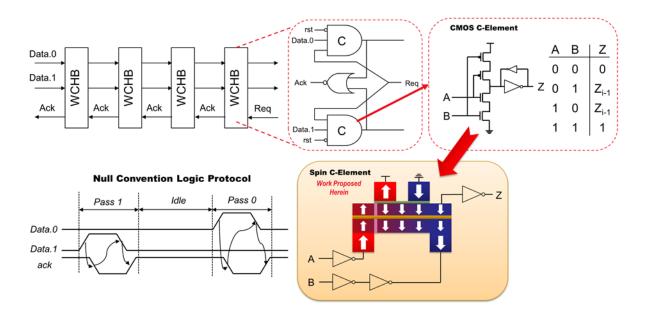

| Figure 10: Null Convention Logic, Weak Conditioned Half Buffer, Muller C-Element gate,            |

| CMOS implementation, and the proposed implementation. © 2018 IEEE                                 |

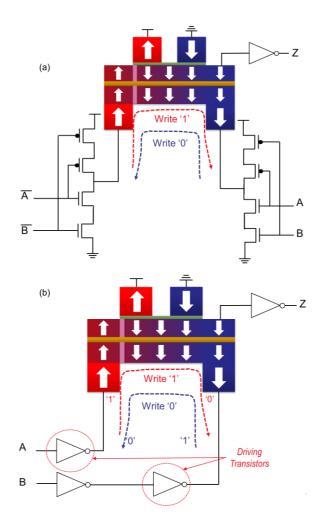

| Figure 11: Two Spintronic Muller C-Element Designs. © 2018 IEEE                                   |

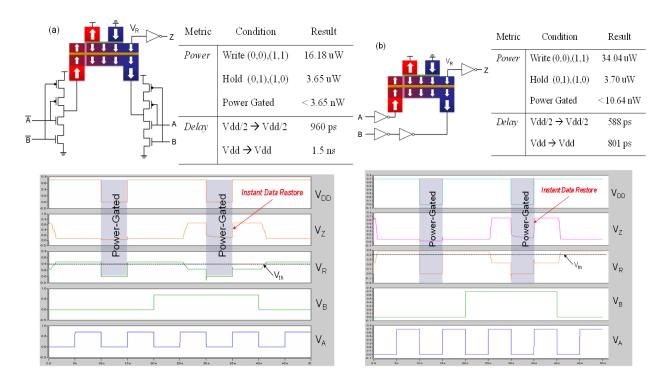

| Figure 12: Spintronic C-Element designs, functional verification, and performance metrics 36          |

|-------------------------------------------------------------------------------------------------------|

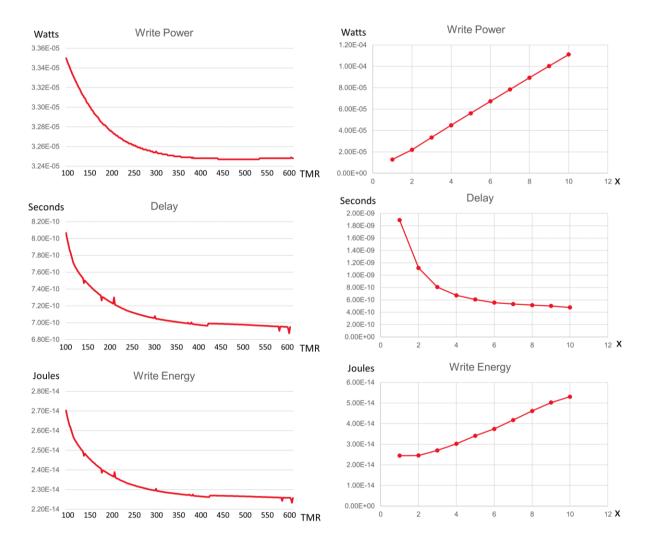

| Figure 13: Left side – relation of performance characteristics to TMR. Right side – relation of       |

| performance characteristics to driving transistor width (nMOS width = Fw and pMOS with =              |

| 2Fw where $F$ is the minimum feature size). © 2018 IEEE                                               |

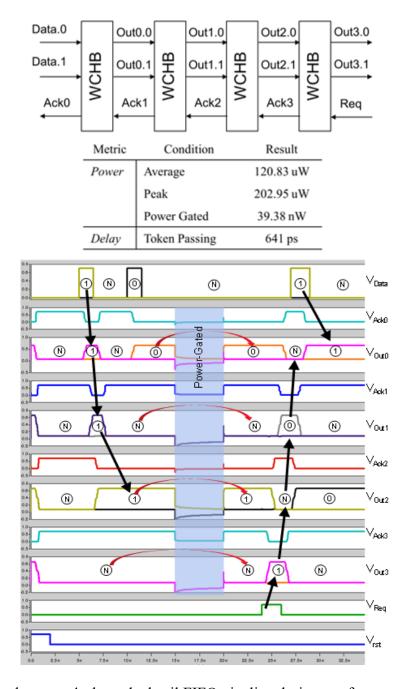

| Figure 14: Asynchronous 4-phase dual-rail FIFO pipeline design, performance characteristics,          |

| and functional verification showing instant on/off after power gating. © 2018 IEEE 40                 |

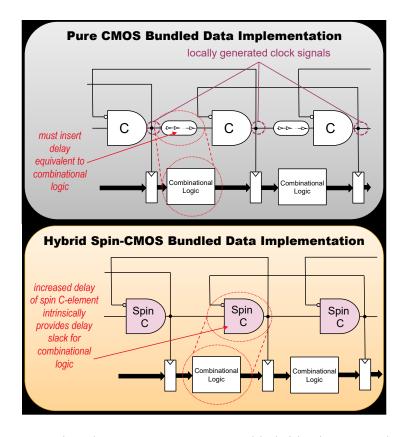

| Figure 15: Comparison between pure CMOS and hybrid spin-CMOS bundled data                             |

| implementations. © 2018 IEEE. 42                                                                      |

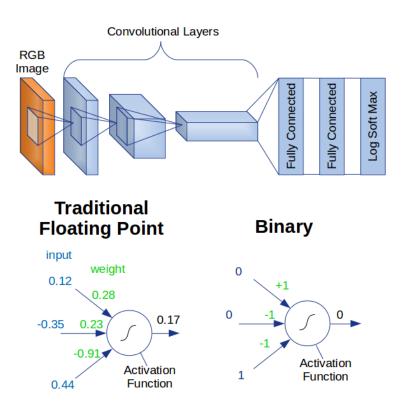

| Figure 16: Convolutional DNN structure along with representative neurons for both floating-           |

| point and binary representations. © 2019 IEEE                                                         |

| Figure 17: Neuromorphic accelerator proposed in this Chapter. © 2019 IEEE                             |

| Figure 18: Simulation Framework for Stochastic Binarized Deep Neural Network Accelerator. 54          |

| Figure 19: Effect of weight variations for on-chip vs off-chip training. © 2019 IEEE 57               |

| Figure 20: Error rate per epoch for a selection of off-chip and on-chip test cases. © 2019 IEEE.      |

|                                                                                                       |

| Figure 21: The Spintronic Stochastic Spiking Neuron circuit with Spin-Hall driven p-bit 61            |

| Figure 22: Second-order neuromorphic synapse used herein                                              |

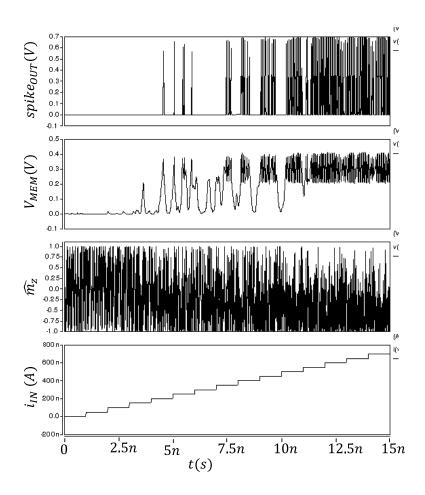

| Figure 23: Stochastic Spiking Neuron simulation graphs illustrating, from the bottom up, <i>iIN</i> , |

| mz, VMEM, and spikeOUT65                                                                              |

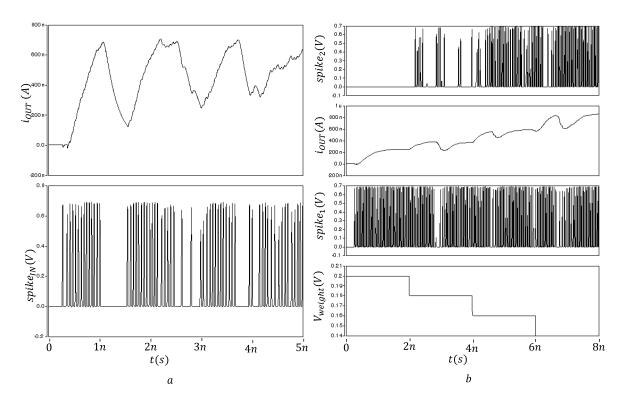

| Figure 24: Simulation transients of Stochastic Spiking Neuron with Neuromorphic Synapse 67            |

| Figure 25: Simulation transients of S3N with Neuromorphic Synapse implementing Perceptron        |

|--------------------------------------------------------------------------------------------------|

| functionality. 68                                                                                |

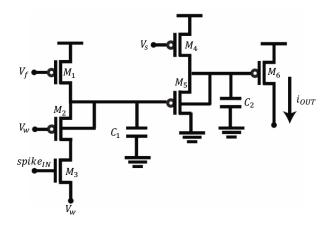

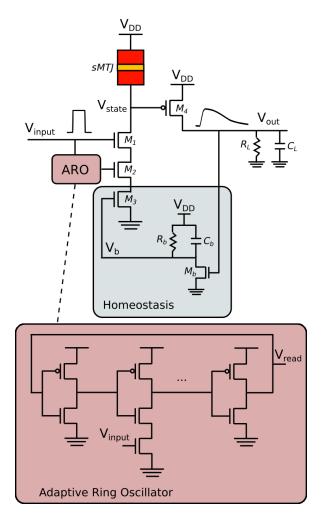

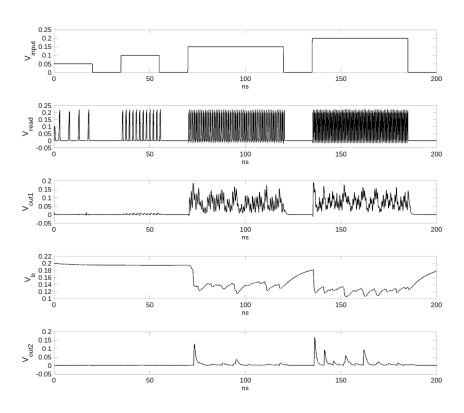

| Figure 26: The Subthreshold Spintronic Stochastic Spiking Neuron circuit                         |

| Figure 27: Operational waveforms of the Subthreshold Spintronic Stochastic Spiking neuron 78     |

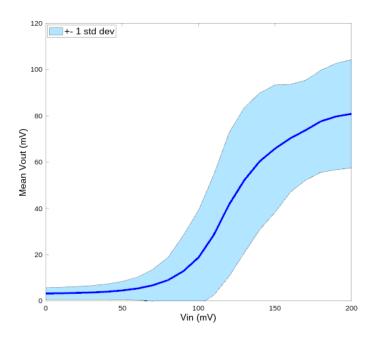

| Figure 28: Mean output voltage of the S4N versus input voltage including process variation 79    |

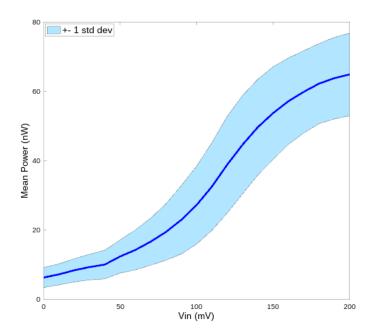

| Figure 29: Mean power of the S4N versus input voltage including process variation                |

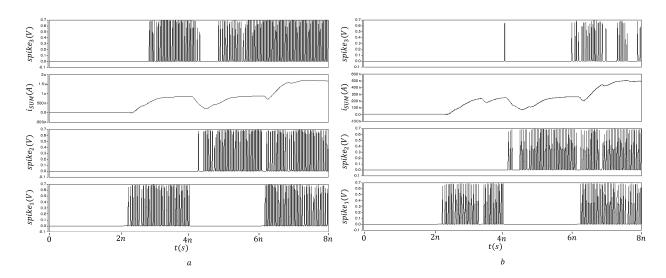

| Figure 30: The stochastic spiking neuron circuit and associated waveforms. © 2019 IEEE 88        |

| Figure 31: The three-bit hybrid spin-CMOS synapse. © 2019 IEEE                                   |

| Figure 32: Two alternative implementations for the homeostatic synapse. © 2019 IEEE 92           |

| Figure 33: An architectural overview of the Neural Sampling Core. © 2019 IEEE                    |

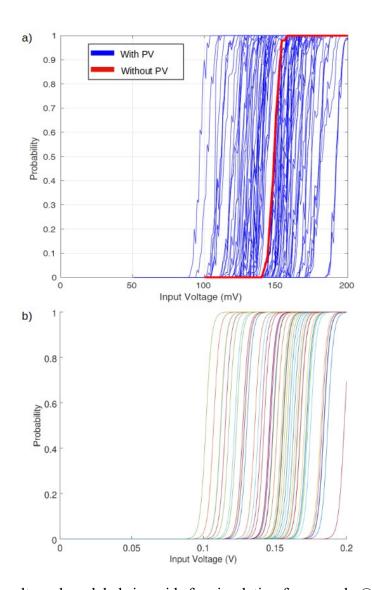

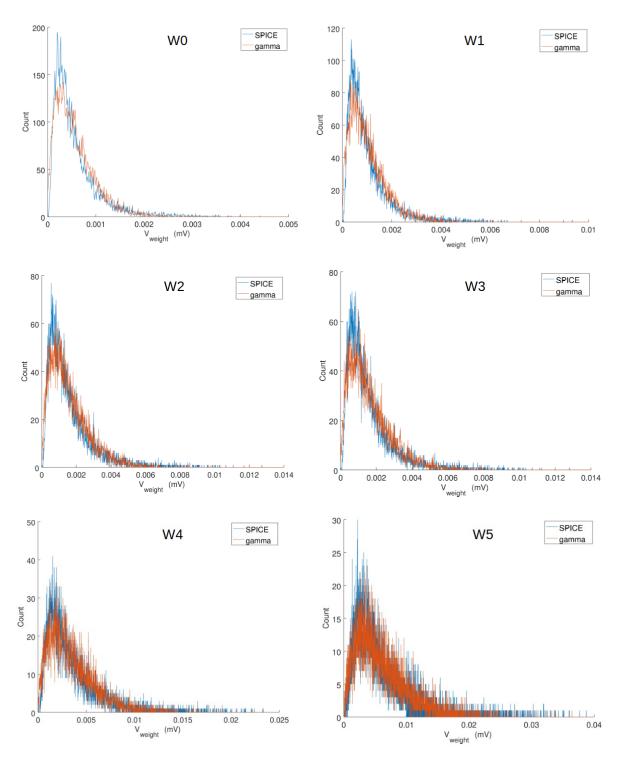

| Figure 34: SPICE results and modeled sigmoids for simulation framework. © 2019 IEEE 99           |

| Figure 35: Synapse weight distributions for SPICE simulations and fitted gamma parameters.       |

| © 2019 IEEE. 102                                                                                 |

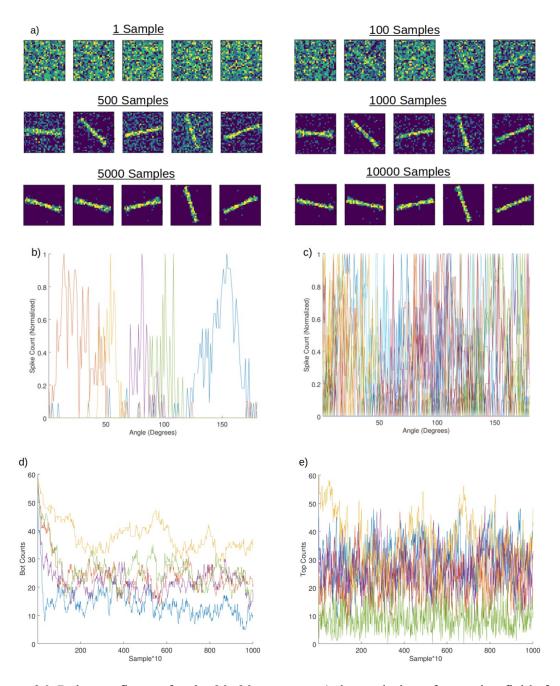

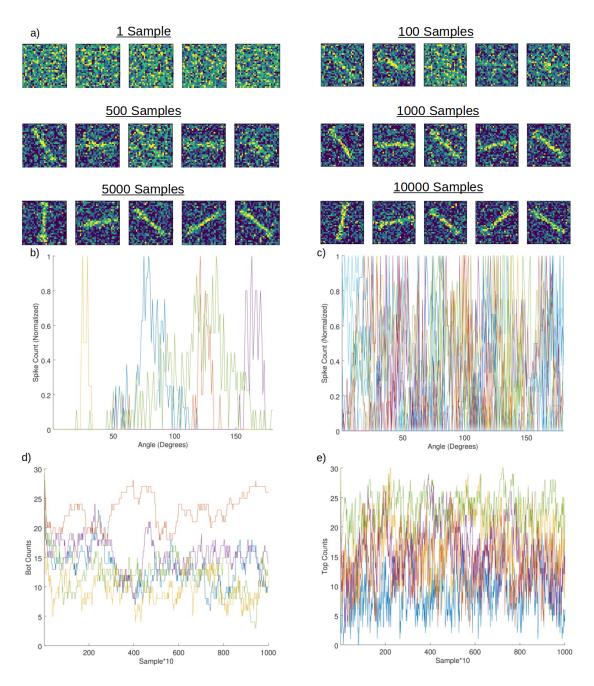

| Figure 36: Relevant figures for the 30x30 test case. a) the evolution of receptive fields for a  |

| random selection of five output neurons. b) the tuning curves for a random selection five output |

| neurons. c) the tuning curves for all 50 output neurons. d) the temporal evolution of the number |

| of homeostatic synapses with potentiated long-term SHE-MTJs (bot) for a random selection of      |

| five output neurons. e) the temporal evolution of the number of homeostatic synapses with        |

| potentiated short-term SHE-MTJs (top) for a random selection of five output neurons. © 2019      |

| IEEE 106                                                                                         |

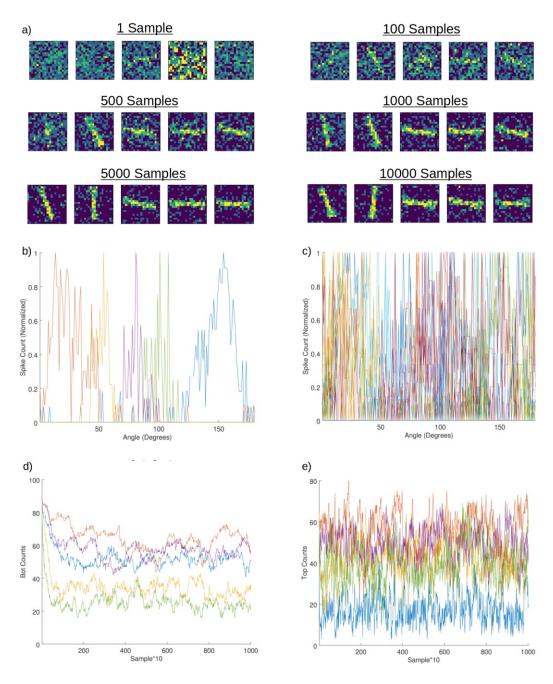

| Figure 37: Relevant figures for the 20x20 test case. a) the evolution of receptive fields for a      |

|------------------------------------------------------------------------------------------------------|

| random selection of five output neurons. b) the tuning curves for a random selection five output     |

| neurons. c) the tuning curves for all 50 output neurons. d) the temporal evolution of the number     |

| of homeostatic synapses with potentiated long-term SHE-MTJs (bot) for a random selection of          |

| five output neurons. e) the temporal evolution of the number of homeostatic synapses with            |

| potentiated short-term SHE-MTJs (top) for a random selection of five output neurons. © 2019          |

| IEEE                                                                                                 |

| Figure 38: Relevant figures for the 30x30 test case with noise. a) the evolution of receptive fields |

| for a random selection of five output neurons. b) the tuning curves for a random selection five      |

| output neurons. c) the tuning curves for all 50 output neurons. d) the temporal evolution of the     |

| number of homeostatic synapses with potentiated long-term SHE-MTJs (bot) for a random                |

| selection of five output neurons. e) the temporal evolution of the number of homeostatic             |

| synapses with potentiated short-term SHE-MTJs (top) for a random selection of five output            |

| neurons. © 2019 IEEE                                                                                 |

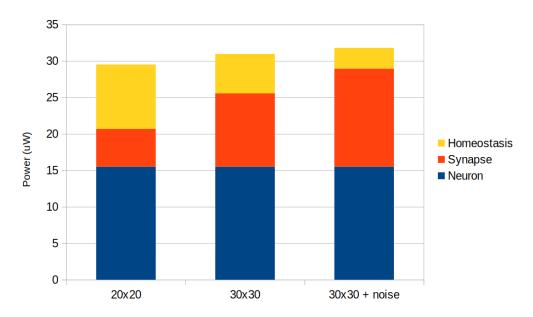

| Figure 39: Average power consumption for each component of the NSC for each test case 111            |

# LIST OF TABLES

| Table 1: Comparison of Hybrid Spin-CMOS Digital Circuits.                             | 13    |

|---------------------------------------------------------------------------------------|-------|

| Table 2: Comparison of Stochastic Spiking Neuron Approaches                           | 17    |

| Table 3: Simulation parameters used for the compact hybrid spin-CMOS D F/F            | 26    |

| Table 4: Neuron attributes of recent BNN approaches. © 2019 IEEE.                     | 50    |

| Table 5: S3N and Second-Order Synapse Simulation Parameters.                          | 64    |

| Table 6: Circuit Parameters for the Subthreshold Spintronic Stochastic Spiking Neuron | 76    |

| Table 7: Comparison to Previous Spintronic Stochastic Spiking Neuromorphic Hardware.  |       |

| © 2019 IEEE                                                                           | 85    |

| Table 8: Synapse Weights for MTJ States. © 2019 IEEE.                                 | 90    |

| Table 9: Synapse Fitting Parameters. © 2019 IEEE.                                     | 101   |

| Table 10: Homeostatic Synapse Fitting Parameters. © 2019 IEEE.                        | 101   |

| Table 11: SHE-MTJ Switching Probability During Events. © 2019 IEEE                    | . 104 |

#### **CHAPTER ONE: INTRODUCTION**

Scalable, energy-efficient, and enhanced functionality over CMOS technology are all desirable characteristics for future computational devices. Emerging spintronic devices achieve greater functionality through nonvolatility and improved scalability via Back End of Line (BEoL) compatibility, which enables vertical integration [1]. By utilizing these features, enhancements to contemporary computational architectures can be realized, such as area-efficient digital circuits with instant store/restore functionality for aggressive power gating, while new neuromorphic computational architectures can leverage the dense arrays of non-volatile memory, and the intrinsic properties of spintronic devices can be used to realize entirely new computational paradigms at even greater energy efficiency [2, 3]. This Chapter introduces the need for spintronic architectures, provides an overview of current spintronic approaches for digital and neuromorphic circuits, and delineates the contributions of this Dissertation.

#### **Need for Spintronic Circuits**

The Moore's Law scaling of CMOS devices has enabled the proliferation of computational technology in every facet of the information processing revolution since the 1960s. However, the fundamental limitations of CMOS scaling has necessitated the semiconductor industry to formally acknowledge that transistors will stop shrinking by the early 2020s, as emphasized by the chairman of the road-mapping organization [4]. Means for continuing Moore's Law or enhancing the capabilities achievable with current integration densities could be through the development of new

nanodevices. Among promising devices, the 2015 International Technology Roadmap for Semiconductors (ITRS) identifies nanomagnetic, or spintronic, devices as capable post-CMOS candidates [5].

Spintronic devices have the potential to operate at frequencies above 1 GHz and at energies approaching 1aJ [6]. Thus, they provide a direction for a scalable universal memory technology, which is in contrast to today's current memory systems that are segmented between SRAM for high speed/high area, DRAM for moderate speed/low area, and Flash or magnetic platters for very low speed/very low area data storage. Additionally, the features of spintronic devices enable new classes of circuits that, in contrast with CMOS, intrinsically hold their state without any external power signals. This feature can provide novel circuit and architectural strategies leveraging powergating for reduced energy consumption and heat generation, as well as the development of new computational strategies beyond typical von-Neumann approaches, such as neuromorphic circuits, where the improved integration density of high-speed non-volatile devices can decrease area overheads for the memory-intensive nature of neural network paradigms, while the stochastic switching properties of the devices enable the implementation of stochastic behaviors found in biological neural networks and probabilistic unsupervised learning rules using a minimal number of discrete binary memory devices [2, 7, 8].

#### Spintronic Technology

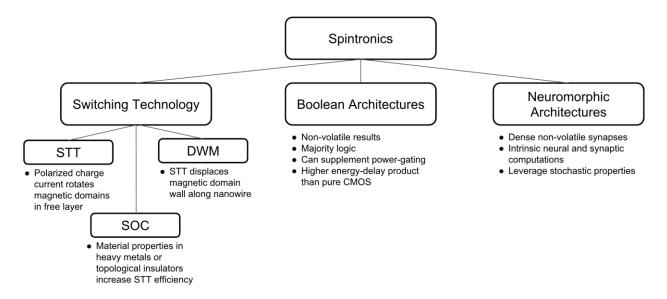

In this Section, the spintronic switching mechanisms outlined in Figure 3 are delineated.

To begin, almost all currently-commercializable spintronic devices utilize a Magnetic Tunnel Junction (MTJ) for switching, reading the magnetic state, or both, and the MTJ is realized with a material stack of a thin insulating oxide, which is typically MgO, sandwiched between two Ferromagnets (FM) [1, 9-25].

Figure 1: Illustration of the MTJ stack, high resistance state, and low resistance state.

As shown in Figure 1, one FM is deemed the fixed layer since it is engineered such that its magnetic orientation will not change, and the other FM is called the free layer since its magnetic orientation will rotate according to the principles of the specific device it is a part of. The MTJ acts as a mechanism to read the state of magnetic orientation of a FM since the resistance across the MTJ is based on the relative magnetic orientations of the fixed- and free-layer FMs in the stack. If the two FMs are parallel (P), then the MTJ has its lowest resistance, and if they are anti-parallel (AP), then the MTJ has its highest resistance. The relative resistance ratio between the P and AP states is called the Tunneling Magnetoresistance (TMR) ratio. MTJs will be used throughout the dissertation to interface between spin-states and electrical circuits.

One of the primary mechanisms by which the free-layer of an MTJ can be switched is with Spin Transfer Torque (STT) [26, 27]. STT operates by injecting a spin-polarized charge current into the free-layer. If electrons of one spin orientation meet an electron of differing orientation,

then a net magnetic torque is applied, which is STT. MTJs can be utilized to polarize the spin of electrons through its fixed-layer before passing into the free-layer much like how a polarizer only allows photons of a particular polarization to pass through it [28]. Other physical phenomena, such as Spin Orbit Coupling discussed later, are also able to inject spin-polarized currents into free layers to switch the magnetic state. STT will be used throughout this dissertation as a mechanism to switch the magnetic state of a free layer.

Domain Wall Motion (DWM) is a phenomena whereby two regions with opposing magnetic orientations in the same FM wire have a region between the two called the domain wall [29, 30]. By applying STT to the domain wall it will move in the direction of the electron flow, which allows charge current-based manipulation of a magnetic region in a continuous fashion as opposed to the discrete nature of mono-domain FMs used in typical STT-MTJs. DWM will be used in Chapter 3 to realize novel hybrid spin-CMOS digital circuits.

Spin Orbit Coupling (SOC) effects such as the Spin Hall Effect (SHE) are mechanisms by which particular materials cause electrons of one spin orientation to flow opposite to those of opposite spin orientation [31-38]. The SHE is a bulk phenomena found in heavy metals such as Pt or beta-W and works by passing a charge current through the material, and due to SOC electrons with opposing spins are pushed to opposite sides of the heavy metal, which provides a mechanism for injecting spin current into FMs interfaced with the material. SOC effects can be engineered to realize very high efficiency spin injection and as such has been at the forefront of the latest in spintronic device research. SOC will be used in Chapters 4, 5, and 6 to realize neuromorphic synapses and neurons.

#### Spintronic Approaches for Digital Circuits

Spintronic devices can be beneficial for standard digital circuits since they can reduce the overheads by reducing the number of devices needed while migrating some circuitry to BEoL, alleviating area overheads. The current-based switching of the devices also affords the straightforward implementation of majority logic gates, which can reduce total gate counts in some circuits [17]. Furthermore, the non-volatility of the devices allows for replacement of in-circuit memory structures, such as SRAM, with spintronic devices that can be readily power-gated when not being used to conserve static power consumption. Two novel hybrid spin-cmos circuits are developed in Chapter 3 that utilize the overhead-reduction and non-volatility capabilities of spintronic devices to improve both synchronous and asynchronous Von-Neumann architectures.

#### Spintronic Approaches for Neuromorphic Circuits

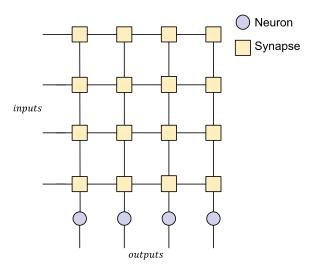

The dense, non-volatile, resistive, and stochastic switching properties of spintronic devices can all be utilized for neuromorphic architectures. Neuromorphic architectures are a paradigm shift away from Von-Neumann architectures that focuses on combining computation and memory elements within neural network computational schemes. The primary components of neuromorphic architectures are the synapses, which modulate the strength of input signals, effectively implementing a multiplication between the synaptic weight and the input signal, and the neurons, which implement some form of non-linearity applied to the summation of presynaptic input signals multiplied by the connecting synaptic weights. The synapses and neurons are typically organized into a crossbar configuration as shown in Figure 2.

Figure 2: Typical neuromorphic crossbar architecture with synapses and neurons.

There are a variety of neural network algorithms that can be used to develop neuromorphic architectures such as standard Deep Neural Networks (DNNs) that use continuous valued weights and neuron activations [39], Binarized Neural Networks (BNNs) that use binary neuron activations and synaptic weights [40], and Spiking Neural Networks (SNNs) that attempt to mimic the spiking behavior found in biological neurons, use discrete binary spike events to represent the outputs of neurons and can have either discrete, continuous, or binary synaptic weights [3, 41-43].

Spintronic devices can be utilized to implement both the synapse and neuron components of neuromorphic architectures. The resistive nature of spintronic devices lends themselves to naturally implement synaptic weighting of input signals in an analog fashion in crossbar arrays for parallel computation of all input signals and synapses to be applied to the input of the neuron. Additional benefits are realized by the vertical integration of spintronic devices, reducing the area overheads of synapses, which make up the majority of neuromorphic architecture footprints. Also,

the non-volatility of spintronic devices mitigates static power consumption within the crossbar array. SNNs also receive additional benefits from the utilization of spintronic devices because they can leverage the intrinsic stochastic switching behavior of spintronic devices to realize efficient probabilistic update rules with binary or low-bit synapses for hardware-efficient neuromorphic architectures with unsupervised learning, as shown in Chapter 6. For neuron circuits, spintronic devices can naturally implement sigmoidal Probabilistic Activation Functions (PAFs), which can be implemented with resistive crossbar arrays for compact low-power neuron designs as developed in Chapter 4. Spintronic devices also pave a way towards more biologically-mimetic stochastic spiking neuron behaviors that realize powerful Bayesian computations as prescribed from several works in computational neuroscience [44-46]. Such stochastically spiking neurons typically require expensive overheads to be realized with deterministic CMOS circuits, but by leveraging the intrinsic stochasticity of spintronic devices to implement such stochastic spiking behaviors, compact low-power circuits can be realized, as developed in Chapters 5 and 6.

Figure 3: Taxonomy of spintronic technologies and architectures with their associated characteristics.

#### Contributions of the Dissertation

The primary contributions of this dissertation are detailed below.

Hybrid Spin-CMOS circuits for area reduction and enhanced functionality in Von-Neumann architectures: The direct integration of spintronic devices in traditional CMOS circuits achieves reductions in device counts as well as enhanced functionality due to the non-volatility imparted into the circuits, such as instant store and restore capabilities for aggressive power-gating schemes. As CMOS devices have been scaled, static power consumption has increased to a significant proportion of the total power consumption, prompting chip architects to utilize power-gating schemes whereby the power supplies to idle circuits are shut off to reduce static power consumption. However, due to the volatility of typical SRAM memory used in digital circuits, the

data needs to be migrated to either non-volatile storage or non-power-gated circuits prior to turning the supply off, and then the data needs to be restored from storage after power is resupplied before the circuit can resume operation. The work presented in Chapter 3 demonstrates how to utilize spintronic devices to impart edge-triggered flip-flops and Muller C-elements with instant store and restore capabilities while reducing device counts.

Stochastic neurons in area- and power-efficient circuits: Stochastic neuron circuits can be beneficial for both BNN and SNN architectures. The binarization of DNNs requires neurons that provide a non-linearity to a wide-ranging input, which can be either a deterministic sign function, or a sigmoidal Probabilistic Activation Function. Chapter 4 introduces a spintronic Probabilistic Activation Function that has reduced power and area overheads compared to the deterministic approach. A ubiquitous behavior found in biological neural networks is the stochasticity of the firing rate, which arises from the stochastic opening and closing of the ion channels that drive spiking behavior and is determined to be an important component of theoretical computational frameworks developed in computational neuroscience, such as Neural Sampling. Most spiking neuron circuits utilize a simple Leaky Integrate and Fire (LIF) model that does not accurately model the stochastic spiking found in-vivo and is incompatible with Neural Sampling. The works presented in Chapter 5 detail two approaches that utilize the stochastic behaviors of spintronic devices to realize compact, high-speed, and low-energy stochastic spiking neuron circuits with a spike rate determined by the input signal, which can be utilized for neuromorphic architectures implementing computational models that leverage stochastic spiking neurons.

Comprehensive hardware and algorithm co-design for process variation resilient and lowpower neuromorphic architecture: The design of robust, hardware-efficient, and low-power neuromorphic architectures with unsupervised learning requires an integration of knowledge from device physics, low-power circuits, and computational neuroscience to realize a holistic deviceaware circuit, architecture, and algorithm co-design. Several emerging devices are promising for advancing neuromorphic architectures in part due to their non-volatility and stochastic switching behaviors, of which spintronic devices have the advantage of nearly unlimited write endurance. Typical approaches to neuromorphic architectures using spintronic devices attempt to impose ideal algorithmic constraints, such as exponential Spike-Timing Dependent Plasticity learning rules onto non-ideal circuits in an ad-hoc fashion, requiring precise parameter tuning that would be challenging when considering the effects of process variations, especially at subthreshold voltages. The Neural Sampling Core developed in Chapter 6 leverages the intrinsic properties of spintronic devices and subthreshold CMOS under the effects of process variation to design ultra-low-power neuron, synapse, and homeostasis circuits that are hardware-efficient and implement principles from Neural Sampling, while utilizing the stochastic switching properties of spintronic devices to realize a new unsupervised learning rule called *Probabilistic Hebbian Plasticity* that is shown to be robust under various forms of parameter and circuit variations, input sizes, and input noise.

#### **CHAPTER TWO: PREVIOUS WORKS**

This Chapter starts by introducing previous approaches for implementing spintronic devices in standard digital circuits to reduce static power consumption through power-gating, due to the non-volatile nature of spintronic devices. Then, previous approaches utilizing emerging devices for compact and low-power neuromorphic circuits, such as neurons and synapses, are detailed.

#### Previous Spintronic Approaches for Digital Circuits

The non-volatile, high-speed, high write-endurance, and BEoL properties of spintronic devices offers the ability to improve digital circuits, particularly by ameliorating the ever-growing static power consumption overhead of highly scaled CMOS circuits through power-gating. In this Section, several approaches for utilizing spintronic devices to imbue D F/F and Muller C-Element circuits with low-overhead non-volatile storage for standby power reduction are delineated. A direct comparison between the works can be found in Table 1.

D F/F circuits, which are the primary intra- and inter-computation memory elements in standard synchronous architectures, are an ideal candidate for the non-volatile, high-speed, and high-endurance properties of spintronic devices since non-volatility within these circuits can allow entire portions of the overall architecture to be power-gated without loss of data. Several works have used these properties to develop such non-volatile D F/Fs, which are listed in Table 1. In particular, Ryu et al. [47] utilized a master-slave D F/F configuration in which the slave latch is

connected to a sensing circuit containing two MTJs, which also includes associated write circuitry. Prior to power-gating, a write-enable signal is sent to the write circuitry, which then writes the state of the D F/F into the MTJs in a complementary fashion. Once power is restored to the circuit, a sense-enable signal is sent to the sensing circuitry, which senses the data in the MTJs and loads that data into the D F/F. Suzuki et al. [48] used a master-slave D F/F configuration with a DWM device-based non-volatile storage cell with associated store and recall circuitry. Prior to power-gating a store signal is sent to the non-volatile storage cell, causing the state of the D F/F to be written to the DWM device, and once power has been restored, a recall signal causes the data in the DWM device to be sensed and loaded into the slave latch of the D F/F. Both of these non-volatile D F/F circuit designs require significant circuitry overhead as well as additional signaling wires and timing overheads to store and restore the data to and from non-volatile storage prior and after power-gating. Thus, the work presented in [8] and Chapter 3 removes these overheads, allowing very compact circuits with instant store and restore capabilities without any additional signaling wires or timing overheads.

The asynchronous counterpart to the D F/F for synchronous architectures is the Muller C-Element, which is involved with storing inter-computational data and is critical for performing asynchronous handshaking protocols in lieu of a global clock signal [49]. Therefore, several works have targeted the Muller C-Element for integration with spintronic devices to imbue asynchronous architectures with non-volatility for power-gating capabilities, as listed in Table 1. Zianbetov et al. [50] developed a hybrid spin-CMOS Muller C-Element with body biasing and a silicon-on-insulator design. Their design typically operates in an ordinary CMOS-only fashion for high speed,

with a propagation delay of just 32 ps, and it can then backup the state data to non-volatile MTJ cells prior to powering the circuit down for power-gating. The metrics listed in Table 1 compare only the backup delay and power instead of the standard CMOS-only high-speed operation in order to compare the non-volatile operation of the design with the intrinsically non-volatile operation of the design proposed herein. Storing data in spintronic devices can also increase radiation-induced soft error immunity. For instance, Onizawai et al. proposed their design to address Single Event Upsets using the resilience of MTJs [51]. Their design lacks the CMOS-only high speed operation of Zianbetov et al. as their focus was to improve reliability, and as such, needed to write to the non-volatile cells every operation.

Table 1: Comparison of Hybrid Spin-CMOS Digital Circuits.

| Ref.          | ef. Circuit Device Count I |          | Delay    | Power    |

|---------------|----------------------------|----------|----------|----------|

| [47]          | D F/F                      | 56T + 2S | 203.3 ps | N/A      |

| [48]          | D F/F                      | 27T + 1S | 62.2 ps  | 12.7 uW  |

| [8]<br>Herein | D F/F                      | 10T + 1S | ~1-10 ns | ~3-9 uW  |

| [51]          | Muller C-Element           | 38T + 2S | 1.05 ns  | 263.8 uW |

| [50]          | Muller C-Element           | 17T + 2S | 1 ns     | 50 uW    |

| [2]<br>Herein | Muller C-Element           | 8T + IS  | 801 ps   | 34.04 uW |

#### Previous Approaches for Neuromorphic Circuits

Spintronic devices have been utilized to realize high-speed, low-power, and compact neuromorphic circuits including neurons and synapses, of which we review a recent selection in this Section. Although spintronics have been utilized to realize both deterministic and stochastic neuromorphic circuits, since the works developed in this dissertation focus on the stochastic approach for its potential power and area savings as well as biological plausibility and compatibility with theories from computational neuroscience. Where appropriate, spintronic approaches are also compared to standard CMOS and alternative emerging technologies, such as memristor in order to demonstrate the benefits of spintronics for stochastic circuit implementations.

The implementation of stochastic neuron circuits requires a circuit to take an input signal, which is typically voltage or current, and compute a probability of spiking based on that signal. Most approaches utilize a sigmoidal spiking probability, which is commensurate with the behavior of emerging device switching probabilities as well as biological behavior and computational neuroscience theories [42, 44, 45, 52]. Implementing stochastic neuron circuits in standard digital CMOS designs is not very natural due to the determinism inherent in the designs, and requires a Pseudo-Random Number Generator (PRNG) and the associated power, area, and timing overheads, such as in [53]. Emerging devices can implement a sigmoidal probability of switching much more naturally through their stochastic switching properties. Wijesinghe et al. [54] utilized the stochastic filament formation behavior of amorphous silicon-based metal filament formation memristor devices to realize a compact stochastic spiking neuron that operates with a three-phase

approach. The first phase is the write phase where a voltage is applied to the memristor, representing the input signal corresponding to the previous synaptic weighted summation computation, to the device for a period of time, which may or may not switch based on the input voltage. After the write phase, the read phase senses the state of the memristor, and if the device switched during the write phase, a spike signal is generated. After the read phase, the device is reset with a voltage pulse with an amplitude and duration chosen such that the device is reset with a very high probability. Spintronic approaches to designing stochastically spiking neural circuits utilize the thermally-driven random magnetic excitations found in nanomagnets to switch the device probabilistically based on the applied input signal [42, 43, 52]. Previous approaches using both MTJs and SHE-MTJs have a similar three-phase approach to the memristor design previously described. The first phase is considered the write phase, where a current pulse is applied to the MTJ or the SHE layer of the SHE-MTJ with a current pulse equivalent to the input strength for a pre-defined pulse duration, and the device may or may not have switched. After the write phase, the device is sensed, and if it was switched, an output spike is generated. Once the read phase is complete, the MTJ or SHE-MTJ must be reset with a strong current pulse to reset the state of the device prior to the next write phase. Of all the previous memristor and spintronic stochastic spiking neuron approaches, they require the write-read-reset phases, which introduces additional time and power overheads. In Chapters 5 and 6, spintronic stochastic spiking neuron circuits are developed that leverage the properties of a novel spintronic device to realize intrinsically spiking hardware that does not need any additional read or reset phase overheads.

In addition to stochastic spiking neuron circuits, emerging devices have been utilized for implementing stochastically switching synapses for realizing either binary or multi-bit synapses with probabilistic update rules for compact and low-power unsupervised learning algorithms in hardware. Suri et al. [55] fabricated a SNN chip with conductive-bridge RAM (CBRAM) binary synapses with probabilistic unsupervised learning rules that were capable of realizing auditory and visual pattern extraction. Bill et al. [56] showed that compound memristive synapses using 1-100 devices with unsupervised probabilistic learning rules is capable of recognizing handwritten digits with diminishing returns on the number of devices in each synapse, showing that high precision is not required. Zhang et al. demonstrated a similar scheme with compound MTJ synapses consisting of 1 to 9 MTJs and showed that with probabilistic unsupervised learning rules, the network can learn to recognize handwritten digits with respectable accuracies and some robustness to process variation. Srinivasan et al. [42, 57] demonstrated two approaches to using SHE-MTJs as synapses with probabilistic unsupervised learning rules resembling exponential Spike-Timing-Dependent-Plasticity (STDP) curves; one showed that single SHE-MTJs are capable of achieving respectable accuracies for handwritten digits and a stochastic spiking neuron, and the other showed that two SHE-MTJs per synapse, each with slightly different circuity, could realize long-term and shortterm memory, which reduces the total energy required to train the network. In Chapter 6, a lowprecision subthreshold hybrid spin-CMOS synapse using three SHE-MTJs and a new probabilistic unsupervised learning rule called *Probabilistic Hebbian Plasticity* is developed to realize an ultralow power synapse that is robust to process variations.

Table 2: Comparison of Stochastic Spiking Neuron Approaches

|                            | [53]            | [54]                                  | [42, 43, 52]               | S3N<br>Herein                 | S4N<br>Herein                 |

|----------------------------|-----------------|---------------------------------------|----------------------------|-------------------------------|-------------------------------|

| Technology                 | CMOS            | Hybrid<br>CMOS/Memristor              | Hybrid Spin-<br>CMOS       | Hybrid Spin-<br>CMOS          | Hybrid Spin-<br>CMOS          |

| Source of Stochasticity    | PRNG            | Memristor<br>Switching<br>Probability | Thermal Energy             | Thermal Energy                | Thermal Energy                |

| Spike<br>Implementation    | Event<br>Signal | Write-Read-Reset<br>Cycle             | Write-Read-Reset<br>Cycle, | Intrinsic Circuit<br>Behavior | Intrinsic Circuit<br>Behavior |

| Spike Time-<br>Scale Order | 1 ms            | 10 ns                                 | 1 ns                       | 10 ps                         | 1-10 ns                       |

| Energy per spike           | ~10 pJ          | ~1-10 pJ                              | ∼1 nJ                      | ~1 nJ                         | ~10-100 aJ                    |

| Normalized Device Count    | >10x            | ~1x                                   | ~0.5×                      | 1×                            | 2x                            |

#### Probabilistic Bits

An important family of spintronic approaches to leveraging thermally-driven true random behavior in circuits, which are used extensively in Chapters 4, 5, and 6, are called Probabilistic Bits (p-bit) [58]. P-bit circuits come in a couple different flavors that center around a spintronic device with a very low energy barrier free layer as will be described subsequently. Although these specific devices have not been demonstrated comprehensively yet, the field of probabilistic spintronics is an active area of research with very promising experimental results demonstrating the utilization of stochastic nanomagnets as a tunable random number generator [59].

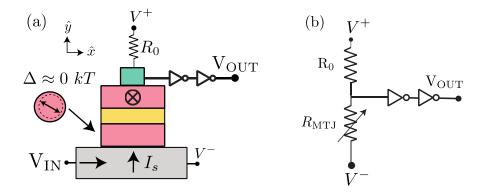

#### Spin-Hall Effect Probabilistic Bit

The SHE-driven p-bit, shown in Figure 4a, combines a heavy metal (HM) exhibiting SHE and an MTJ whose free layer magnetization is modulated by the SHE layer. Unlike standard experiments combining the HM with an MTJ that utilizes ferromagnets with energy barriers of the order of 40 to 60 kT [58, 60-62], the p-bit uses an unstable ferromagnet, with an energy barrier of 0 to 1 kT, which can be obtained by either reducing the volume of a stable magnet [63] or by using circular magnets that effectively have no barrier in the absence of a geometrically preferred easy axis [64]. In the absence of any SHE current, the magnetization fluctuates with average  $\langle m_z \rangle = 0$  and the inverter chain amplifies this signal to produce rail-to-rail voltage swings between 0 and VDD. An input current into the SHE layer generates a spin current that influences the magnetization of the circular magnet, which effectively biases the probability that the output is 0 or VDD. The SHE-driven p-bit is utilized in Chapters 4 and 5 to provide intrinsic thermally-generated stochasticity for various stochastic neuron implementations.

Figure 4: p-bit device schematic and equivalent READ circuit: (a) The gray layer represents a heavy metal (HM) exhibiting the Spin Hall Effect (SHE) that injects a spin current into an adjacent "free layer" of a Magnetic Tunnel Junction. The free layer is a circular magnet with no preferred easy axis (EB=0 kT) that fluctuates in the z-x plane in the presence of thermal noise. The MTJ is connected to an average resistance R0 creating a fluctuating voltage that is amplified by two inverters. (b) The circuit equivalent READ circuit is also shown.

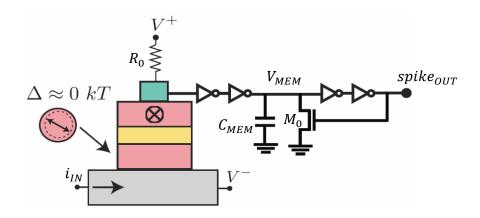

#### Embedded Probabilistic Bit

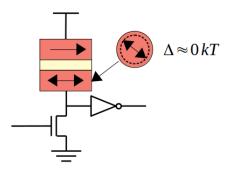

Figure 5: Embedded p-bit circuit.

The Embedded p-bit circuit developed in [65] is a straightforward adaptation of the standard 1-transistor with 1-MTJ circuit typically used in spintronic memory arrays but with a low-energy barrier free layer, as shown in Figure 5. Due to the very low energy barrier ( $\Delta$ ) of the free

layer, the MTJ of the embedded p-bit will stochastically switch between its AP and P states, where the mean retention time for an MTJ ( $\tau$ ) is given by:

$$\tau = \tau_0 e^{\Delta/kT}$$

Where  $\tau_0$  is a material dependent parameter called the attempt time, k is Boltzmann's constant, and T is the temperature in Kelvin [65]. Since the input to the inverter is a voltage divider between the MTJ and the NMOS transistor, the output of the inverter will be a function of the voltage applied to the gate of the NMOS and the probabilistic state of the MTJ, providing a sigmoidal probability of outputting a logic 1 based on the voltage applied to the NMOS. The embedded p-bit is utilized in Chapters 5 and 6 to realize compact and low-power voltage-controlled stochastic spiking neuron circuits.

# CHAPTER THREE: HYBRID SPIN-CMOS DIGITAL CIRCUITS

In this Chapter, the *Domain Wall Coupled Spin Transfer Torque (DWCSTT)* device developed in [30] is described and then utilized to design two new hybrid digital circuits that introduce a novel direct interfacing between spintronic and CMOS devices to realize critical datapath components with enhanced functionality and reduced area costs. The first circuit developed is an edge triggered flip flop utilizing spintronic devices to enable instant store and restore functionality for aggressive power-gating schemes © 2016 IET, reprinted, with permission, from [8]. The next circuit leverages the state-holding properties of a spintronic device to reduce the area overhead of the Muller C-element, which is a critical component in asynchronous architectures, while also imbuing it with instant store and restore functionality, © 2018 IEEE, reprinted, with permission, from [2]. Both circuits illustrate how the use of complementary MTJs in a single device allows a seemless voltage-divider-based integration with CMOS.

### Domain Wall Coupled Spin Transfer Torque Device

Figure 6 (a): Domain Wall Coupled Spin Transfer Torque Device; (b): Low and High states.

The DWCSTT device shown in Figure 6a uses two electrically isolated, but magnetically coupled FM domain wall layers to isolate the read and write mechanisms of the device [30]. The device state is sensed through the two anti-parallel fixed reference pillars, which have MTJs with the underlying domain-wall-based free layer. The domain wall only has two stable states as shown in Figure 6b, and therefore one fixed reference pillar will always be  $R_{High}$  and the other will be  $R_{Low}$ , exclusively, and they will alternate depending upon the location of the domain wall. If the TMR of the MTJs is large enough (~100%), then we can use the two MTJs of the DWCSTT device as a voltage divider to output a  $V_{low}$  or a  $V_{high}$ , which can then be used to switch a CMOS inverter as shown in Figure 7b [8]. The write operation of the device is performed by passing a current through the lower domain wall FM, denoted as the write layer, which is first spin-polarized through the fixed contact layers, and then exerts a STT on the write layer, which moves the domain wall.

Since the upper domain wall FM layer, denoted as the free layer, has strong dipolar coupling with the write layer, its magnetization will rotate in conjunction with the write layer as it undergoes STT. The velocity of the domain wall is linearly related to the current density applied to the write layer, and experimental results show that domain wall velocities up to 125 m/s is achievable with current densities near 1.8e8 A/cm² [66]. Using 16nm PTR CMOS models [67] with a supply voltage of 0.7V, respectable write speeds are achieved by simply applying logic "1" or "0" (vdd or gnd) to the device inputs. By varying the driving transistor widths, the speed and power draw of the device are able to be adjusted. Seo et al. utilized the self-referencing differential nature of the device to read the state of the device by fixing the read out terminal to ground and then comparing the currents of the two fixed reference pillars when a fixed voltage is applied to both [30]. However, with proper read and write path optimization of the DWCSTT, 16nm CMOS gates with balanced transistor widths are capable of both writing to and reading from the device in lieu of using a sense amplifier to compare relative current levels.

### Compact Instant Store/Restore D Flip-Flop

The Hybrid Spin-CMOS edge triggered Flip-Flop (D F/F) focuses on using the non-volatile properties of the DWCSTT to reduce the number of transistors needed compared to the standard pure-CMOS implementation of a master-slave D F/F while providing instant store/restore functionality with full data retention, simplifying the requirements of power-gating techniques [8]. The D F/F developed herein is shown in Figure 7 and consists of a Static Random Access Memory (SRAM)-based master latch, a DWCSTT device as the slave latch, an output inverter, and two

pass gates used for clocking control. While the clock signal is low, the pass gate leading into the master latch from the input is conducting, allowing the master latch to poll the data arriving at the input terminal D. Once the clock signal goes high, the master latch becomes isolated from terminal D and the data stored in the master latch is latched into the DWCSTT slave latch as shown in Figure 7. With this circuit, power gating is achieved by simply disconnecting the entire circuit from VDD since the data is already latched inside the NV element, and no pre-sleep data-storing strategies are necessary. However, since the data stored inside the SRAM master-latch is nondeterministic upon re-powering the circuit, power restoration must commence with the negative edge of the CLK signal to ensure that the proper data stored in the NV slave-latch is propagated through the circuit and the result is ready at the master-latch of the following D F/F before CLK may go high and write the data from the master-latch into the slave-latch. The delay between the clock signal going high and the output updating based on the new data is called the clock-to-Q (C-Q) delay [47], and is dependent upon the speed of the STT-driven domain wall motion in the DWCSTT device, which is proportional to the write current provided by the transistors in the SRAM master-latch. Thus, the C-Q delay can be adjusted by varying the width of the transistors in the SRAM master-latch cell. By increasing the transistor width, we can reduce the C-Q delay for an increased power and area overhead. The relationship between transistor width, power, and C-Q delay is shown in Figure 8, where the x-axis is multiples of the minimum feature size (F) corresponding to  $W_{NMOS} = xF$  and  $W_{PMOS} = 2xF$ . For these simulations, F is taken to be 16nm.

Figure 7: The compact hybrid spin-CMOS D F/F circuit with non-volatile input latching.

## Results

We simulated the Hybrid Spin-CMOS D F/F circuit in HSPICE using the 16nm high-performance transistor models available from Arizona State University [67]. The DWCSTT device was simulated by taking a Verilog-A model from the mCell model available online [68] and modifying it such that it accurately performs the operation of the DWCSTT device. Essentially, the only change from the mCell to the DWCSTT model was to flip one of the reference layers such that the two fixed reference pillars are complementary and to connect a terminal to the free layer shared between the two MTJs. The circuit parameters for the simulation are found in Table 3. The value of R<sub>P</sub> is chosen to be of a high resistance but not out of the range of feasibility [69] in order

to reduce the read power overhead.  $W_{NMOS}$  and  $W_{PMOS}$  are chosen to minimize the C-Q delay, and if one's application can relax the C-Q delay for improved area and power metrics, they may reduce the transistor sizing. The device width, length, TMR, and write path resistivity were all chosen as the base values included in the model of the mCell [68].

The simulated waveforms for the developed D F/F are shown in Figure 9. At the positive CLK edge, the data present at D is written into the DWCSTT slave-latch and is then outputted at terminal Q as depicted. The functionality of this design is critically dependent upon  $V_R$  switching above and below the threshold voltage for an inverter,  $V_{Th}$ , which is shown. Upon power-gating  $V_{DD}$ , the data stored in the slave-latch is saved and immediately restored upon restoration of  $V_{DD}$  to the circuit, illustrating the instant store/restore functionality of the D F/F.

Table 3: Simulation parameters used for the compact hybrid spin-CMOS D F/F

| Parameter              | Value          |

|------------------------|----------------|

| $V_{DD}$               | 0.7V           |

| $R_P$                  | $40k\Omega$    |

| TMR                    | 100%           |

| Device Length          | 12nm           |

| Device Width           | 10nm           |

| $W_{NMOS}$             | 96nm           |

| $W_{PMOS}$             | 192nm          |

| Write Path Resistivity | $200\Omega nm$ |

Compared to previous works [47, 48], the proposed design has a reduced number of transistors and negates the need for store/restore circuitry and signaling prior to power-gating. However, since the C-Q delay of this design is impacted by the relatively slow write speed of the

DWCSTT compared to an SRAM cell, some trade-offs are observed. In particular, compared to [48] the proposed D F/F uses 17 fewer transistors, but has a 1.2ns longer C-Q delay. Although such an increase in C-Q delay is unfavorable for many applications, applications with relaxed speed requirements that utilize power-gating schemes can be benefited with the compact size and simplified power-gating requirements of the proposed design. In addition, further advancements in spintronic research may lead to faster switching designs, which can improve the C-Q delay.

Figure 8: The effects of transistor width on power and C-Q delay of the compact hybrid Spin-CMOS D F/F

Figure 9: Simulated waveforms of the compact hybrid spin-CMOS D F/F

### Discussion

The proposed D F/F design herein is shown to retain its data in a non-volatile spintronic device as a part of its operation, which allows instant store/restore functionality without the need for store/restore signaling or overhead control circuitry. Furthermore, the proposed design uses 10 fewer transistors than a traditional pure-CMOS-based master-slave D F/F [48]. Additionally, we showed that by varying the transistor widths in the SRAM master-latch, it is possible to tune the circuit for the power, delay, and area needs of one's application. The functionality of the design was demonstrated by using 16nm CMOS models and a Verilog-A model of the DWCSTT device in HSPICE. Area results were favorable compared to previous works, but C-Q delay was shown to be worse.

# Spintronic Muller C-Element

The complementary roles of asynchronous architecture with nonvolatile spintronic devices are explored in this section to realize novel improvements for a logic element critical for asynchronous architectures. By redesigning the Muller C-Element to take advantage of spintronic device non-volatility and area-efficiency, benefits such as reduced asynchronous handshaking area overhead, are achieved in addition to instant on/off capabilities for reduced static-power dissipation through power-gating. A novel 8 transistor and 1 spintronic device Muller C-Element design is developed which is 20% faster and uses 68% of the power of previous non-volatile Muller C-Element designs. This spintronic Muller C-Element is demonstrated within a 4-phase dual-rail asynchronous First In First Out (FIFO) pipeline resulting in 48% fewer transistors in comparison with the previous designs. Additionally, bundled-data protocol overheads are shown to be reduced by using the spintronic Muller C-Element proposed herein. Detailed analysis of the effects of driving transistor width and the TMR ratio on device performance characteristics are included.

Figure 10: Null Convention Logic, Weak Conditioned Half Buffer, Muller C-Element gate, CMOS implementation, and the proposed implementation. © 2018 IEEE.

# Overview of Asynchronous Pipelines

Asynchronous pipelines utilize local clock generation control circuits instead of the global synchronization clock found in synchronous pipelines [70]. Local clock generation in lieu of global synchronization provides robust, elastic, and high performance circuits with on-demand power consumption by design [70]. Systems with similar levels of robustness, performance, and power efficiency are difficult, if even possible, to realize using synchronous design [70]. This is due to synchronous designs being limited by the worst case logic delays, register setup and hold times, process variation, and aging-based circuit degradation [70]. Additionally, propagation delays, multiple clock domains, and the exponentially increasing circuit complexity of today's

microprocessors all contribute to increasingly complex clock trees and the associated area and energy overheads relative to the circuits they are controlling in synchronous pipelines [71]. Heat, power, security, and electromagnetic radiation issues also arise from the large power spikes following the clock edge, which is avoided with asynchronous design [72].

Asynchronous design is an established field with a large variety of protocols available, and it is out of the scope of this dissertation to describe them in detail completely. Thus, we will introduce the two protocols used herein. The 4-phase dual-rail quasi-delay-insensitive Null Convention Logic (NCL) pipeline as depicted in Figure 10 is based on dual-rail logic, which uses 2 wires, noted as Data.0 and Data.1, to transfer every bit of data [70]. If Data.0 is asserted logic high, then a logic 0 is transferred. If Data. I is asserted logic high, then a 1 is transferred. If both Data.0 and Data.1 are asserted logic low, then a NULL value is transferred, and it is not allowed for both Data.0 and Data.1 to be asserted logic high at the same time. The basic register element for our particular NCL implementation is called the Weak-Conditioned Half Buffer (WCHB) and is shown in Figure 10. The WCHB works by correlating the request (req) signal of the following stage with the input dual-rail data of the previous stage to determine if it can record the previous stage's data. When a data signal is asserted high, the WCHB resets the ack signal, indicating that it is not ready to accept data, other than a NULL value. Once a NULL value is received, the ack signal is set and indicates that it is ready to accept new data. With this inter-stage handshaking, data flows through the pipeline in a coordinated accurate-by-design method without the need for global synchronization.

The asynchronous Bundled-Data (BD) protocol lacks the dual-rail logic of NCL architectures, which alleviates the overhead needed for two wires per bit, but negates the intrinsic completion detection of NCL designs [70]. By contrast, BD is implemented with standard pipelining of combinational logic and local clock generation by inserting delay elements equivalent to the delay of the combinational logic between clock generating circuits.

Regardless of the protocol, the key element for implementing the inter-stage handshaking that many asynchronous pipelines depend on is the *Muller C-Element* [49]. As depicted in Figure 10, the Muller C-Element asserts a logic 1 when both inputs are logic 1 and asserts a logic 0 when both inputs are logic 0; if the inputs are different, then its output does not change. The key principle of this operation is that an output change indicates that both of the inputs are identical to the output at that transition. One particular low-area CMOS implementation of the Muller C-Element is shown in Figure 10 and utilizes a weak-inverter based SRAM cell to store the output data until a (0,0) or (1,1) condition is reached [73]. The volatile state of this design leads to increased static power dissipation and power-gating overheads by requiring additional store and restore circuitry and delays if power-gating is desired. The work proposed in this Section utilizes the non-volatile memory properties of a particular spintronic device for implementing a compact Muller-C element with instant store/restore functionality for reduced asynchronous pipeline area and power-gating requirements.

The following research contributions are provided for this design:

1) a novel, compact spintronic-based Muller C-element design for reducing asynchronous control area overhead.

- 2) reducing power-gating store and restore delay and circuit overheads by operating in an intrinsically non-volatile manner, and

- 3) realization of a delay-element-free asynchronous Bundled Data pipeline.

# Proposed Spintronic Muller C-Element Designs

When developing the spintronic Muller C-Element, two functionally-correct designs were obtained. The first design developed is shown in Figure 11a and operates by only allowing one p-MOS branch and one n-MOS branch to be "on" when A and B are either (0,0) or (1,1), and all CMOS branches to be in a high-impedance state when A and B are (1,0) and (0,1). This causes current to pass through the write terminals of the DWCSTT device only when the output transitions according the Muller C-element functionality. It also restricts current flow through the write terminals when output transitions do not occur.