# STARS

University of Central Florida

STARS

**Retrospective Theses and Dissertations**

1985

# A Computer Graphics Head-Up Display for Air-To-Air and Air-To-Ground Flight Simulation

Daryl R. Mair University of Central Florida

Part of the Engineering Commons Find similar works at: https://stars.library.ucf.edu/rtd University of Central Florida Libraries http://library.ucf.edu

This Masters Thesis (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Retrospective Theses and Dissertations by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS Citation**

Mair, Daryl R., "A Computer Graphics Head-Up Display for Air-To-Air and Air-To-Ground Flight Simulation" (1985). *Retrospective Theses and Dissertations*. 4804. https://stars.library.ucf.edu/rtd/4804

# A COMPUTER GRAPHICS HEAD-UP DISPLAY FOR AIR-TO-AIR AND AIR-TO-GROUND FLIGHT SIMULATION

BY

DARYL R. MAIR B.S., University of South Florida, 1981

#### THESIS

Submitted in partial fulfillment of the requirements for the degree of Master of Science in the Graduate Studies Program of the College of Engineering University of Central Florida Orlando, Florida

> Spring Term 1985

# TABLE OF CONTENTS

| INTE | RODUCT | TION                             |                              |             |      |             |     |     |     |     |         |     |     |     |    |   |   |   |   |                      |

|------|--------|----------------------------------|------------------------------|-------------|------|-------------|-----|-----|-----|-----|---------|-----|-----|-----|----|---|---|---|---|----------------------|

|      | Objec  | ctives                           |                              |             |      |             |     |     |     |     |         |     |     |     |    |   |   |   |   | 1                    |

|      | Outli  | ine .                            |                              |             |      |             | •   | •   | •   |     | •       |     |     | •   | •  |   | • |   | • | 3                    |

| 1.   | IKONA  | AS GRAP                          | HICS                         | SYS         | TEM  |             | •   |     |     | •   |         |     |     |     |    |   |   |   |   | 8                    |

|      | 1.1    | Hardwa                           | re Ov                        | erv         | iew  |             |     |     |     |     |         |     |     | •   |    |   |   |   |   | 8                    |

|      |        | 1.1.1                            | BPS3                         | 2 P:        | roce | esso        | r/8 | Sec | lue | enc | er      |     |     | •   | •  | • |   | • | • | 10                   |

|      |        |                                  | 1.1.                         |             |      |             |     |     |     |     |         |     |     |     |    |   |   |   |   | 11<br>14             |

|      |        | 1.1.2<br>1.1.3<br>1.1.4<br>1.1.5 | MAlØ<br>CGM4<br>IF/I<br>Vide | Cha<br>K Ha | arac | cter<br>Int | Ge  | ene | era | •to | or<br>• | •   | •   | •   | •  | • | • | • |   | 2Ø<br>25<br>29<br>33 |

|      |        |                                  | 1.1.<br>1.1.<br>1.1.         | 5.2         | F    | rame        | Bu  | ıff | er  | . ( | Con     | ntr | :0] | .10 | er |   | • | • |   | 33<br>35<br>37       |

|      | 1.2    | PDP-11                           | /34 H                        | ost         | Cor  | nput        | er  | •   | •   | •   | •       | •   | •   | •   | •  |   | • |   |   | 39                   |

| 2.   | HEAD   | UP DIS                           | PLAY                         | •           | •••  | • •         | •   | •   | •   | •   | •       | •   | •   | •   | •  |   |   |   | • | 42                   |

|      | 2.1    | Flight                           | Cont                         | rol         | Ini  | Eorm        | ati | ion | 1   |     |         |     |     |     |    |   |   |   |   | 44                   |

|      | 2.2    | Veloci                           | ty Ve                        | ctor        | r.   |             |     |     |     |     |         |     |     |     |    |   |   |   |   | 45                   |

|      | 2.3    | Roll/P                           | itch                         | Lado        | der  |             |     | •   | •   | •   | •       | •   | •   | •   | •  | • | • | • | • | 46                   |

| 3.   | MICRO  | DCODE D                          | EVELO                        | PMEI        | T    |             | •   | •   |     | •   | •       | •   | •   | •   | •  | • | • | • | • | 5Ø                   |

|      | 3.1    | Master                           | Cont                         | rol         | Pro  | ogra        | m   |     |     |     |         |     |     |     |    |   |   |   |   | 53                   |

|      | 3.2   | Rc  | )1] | L/F | Pit | cł  | n V | Vir | ndo | W   | •   | •   | •   | •   | •   | •   | •  | •   | • | • | • | • | • | • | • | 56  |

|------|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|-----|---|---|---|---|---|---|---|-----|

|      | 3.3   | Ch  | ar  | ac  | te  | er  | Ge  | ene | era | ato | or  | Mi  | ici |     | cod | le  |    | •   |   | • |   |   | • | • | • | 59  |

|      | 3.4   | Li  | ne  | e I | ra  | w   | ing | J I | Rou | iti | ine | 2   | •   | •   | •   |     |    |     |   |   |   |   | • | • |   | 63  |

|      | 3.5   | Ma  | tr  | ix  | M   | lu  | lti | p   | Lie | er  | Mi  | icr | op  | pro | gr  | an  | n  |     |   |   |   | • | • | • |   | 64  |

| 4.   | HOST  | PR  | 200 | GRA | MM  | III | ١G  |     |     | •   |     |     | •   |     |     |     |    |     |   |   |   |   |   | • |   | 65  |

| 5.   | DISCU | JSS | IC  | ON  | OF  | • • | VEA | P   | ONS | 5 [ | DEI | LIV | /EF | RY  | FE  | CAI | UF | RES | 5 | • |   | • | • |   | • | 81  |

| 6.   | CONCI | JUS | IC  | N   | •   | •   | •   | •   |     | •   | •   | •   | •   | •   | •   | •   | •  | •   | • | • | • | • |   |   | • | 86  |

| APPE | NDIX  | A   |     | •   |     | •   | •   | •   |     | •   |     |     | •   |     |     | •   | •  | •   | • | • |   | • |   |   | • | 89  |

| APPE | NDIX  | В   | •   | •   |     | •   | •   | •   |     | •   | •   |     |     | •   | •   | •   | •  |     | • |   | • |   |   | • | • | 98  |

|      |       |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |    |     |   |   |   |   |   |   |   |     |

| BIBI | IOGRA | PH  | Y   |     |     |     |     |     |     |     |     |     |     |     |     |     |    |     |   |   |   |   |   |   |   | 113 |

# LIST OF FIGURES

| 1.  | GENERAL BLOCK DIAGRAM OF VTRS SYSTEM | • | • | • | • | • | • | 2  |

|-----|--------------------------------------|---|---|---|---|---|---|----|

| 2.  | BASIC FLIGHT HUD                     |   |   |   |   |   |   | 6  |

| 3.  | BLOCK DIAGRAM OF IKONAS SYSTEM       |   |   | • | • |   |   | 9  |

| 4.  | BLOCK DIAGRAM OF MPS 16              |   |   |   |   |   |   | 12 |

| 5.  | BLOCK DIAGRAM OF BMP32               |   |   |   |   |   |   | 15 |

| 6.  | COEFFICIENT MATRIX EQUATIONS         |   |   |   |   |   |   | 22 |

| 7.  | DIAGRAM OF MA1024 CONTROL FLOW       |   |   |   |   |   |   | 23 |

| 8.  | MA1024 CONTROL ADDRESS FORMAT        | • | • |   |   |   |   | 25 |

| 9.  | FORMAT FOR CGMCB                     |   |   |   |   | • | • | 27 |

| 10. | FORMAT FOR CGM4 BASE CONTROL BLOCK . | • |   |   |   | • |   | 28 |

| 11. | TRANSFER MODE EXAMPLES               | • |   |   |   |   |   | 3Ø |

| 12. | BLOCK DIAGRAM VIDEO OUTPUT CHAIN     |   |   |   |   |   |   | 33 |

| 13. | FRAME BUFFER CONTROL BLOCK           | • |   |   |   |   |   | 36 |

| 14. | VIDEO OUTPUT                         |   |   |   |   |   |   | 38 |

| 15. | PDP-11 CPU BLOCK DIAGRAM             | • |   |   |   |   |   | 4Ø |

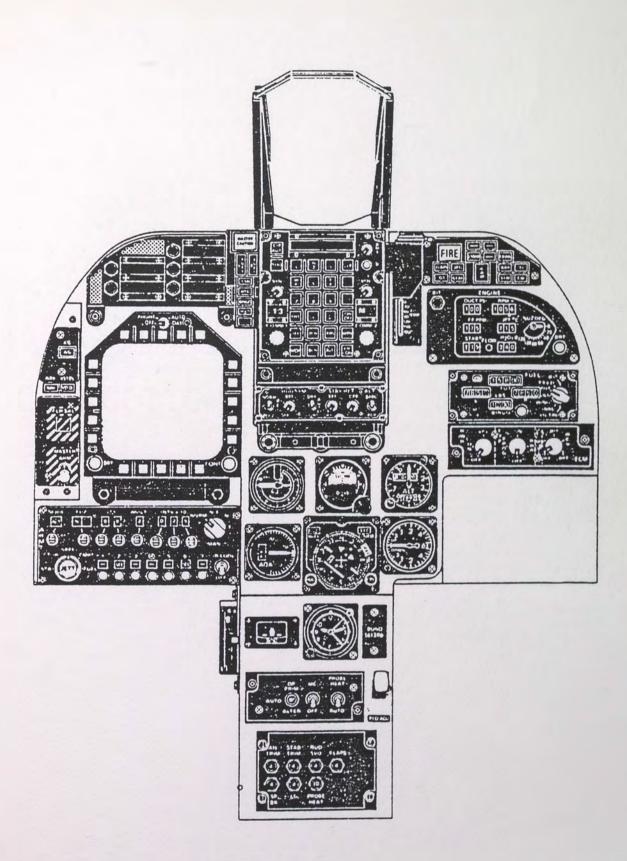

| 16. | MAIN INSTRUMENT PANAL                |   |   | • |   |   |   | 43 |

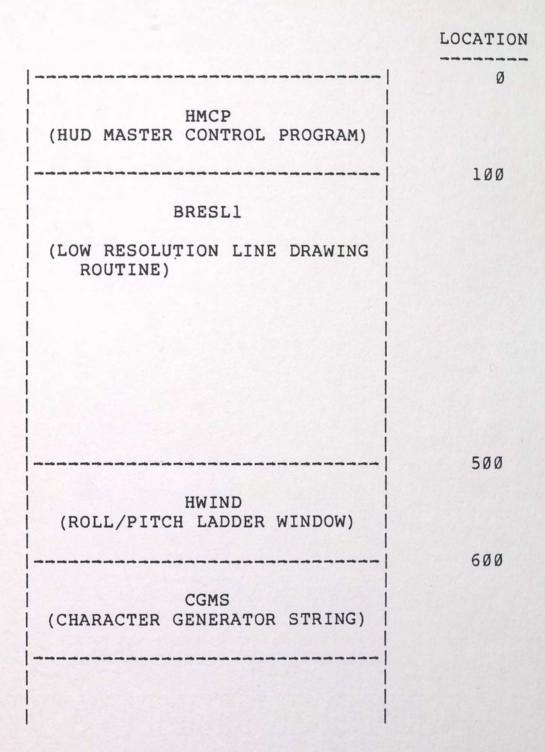

| 17. | BMP32 MICROCODE MEMORY MAP           |   | • |   |   |   |   | 52 |

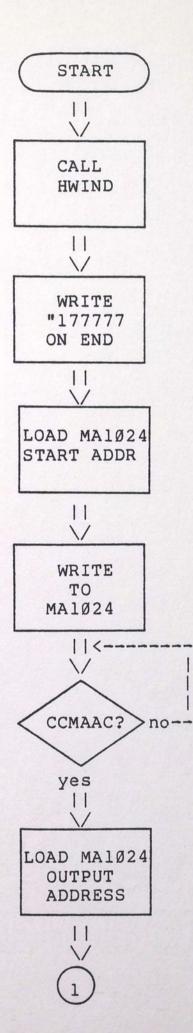

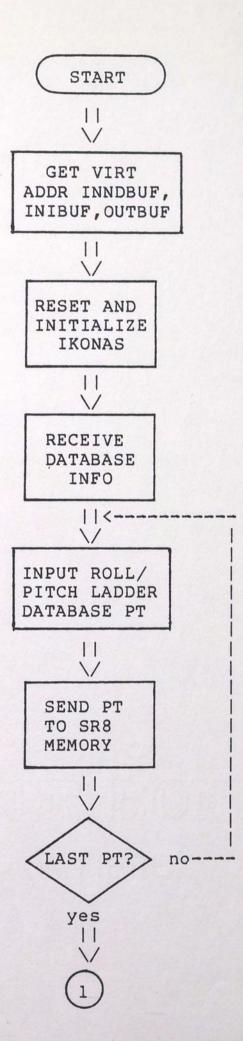

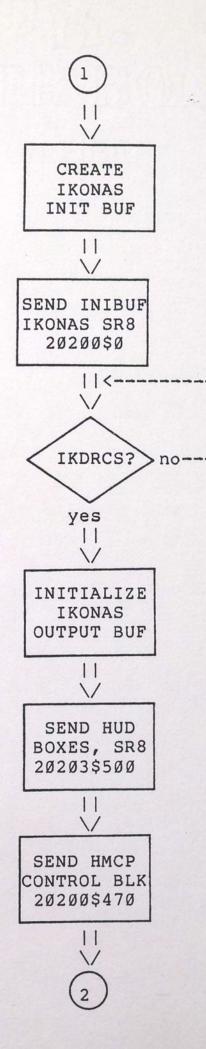

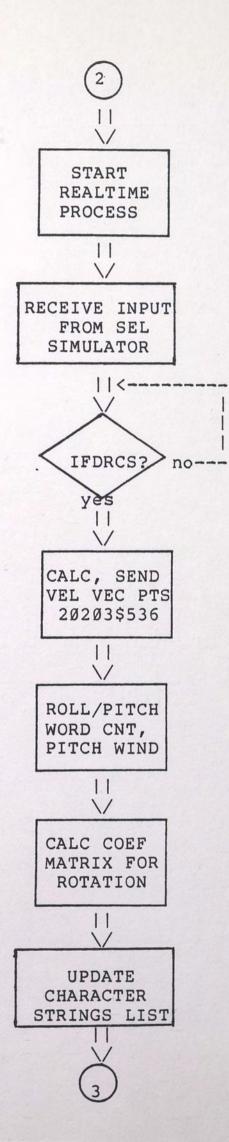

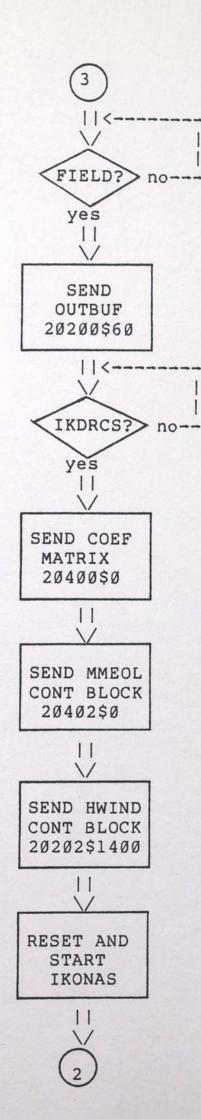

| 18. | HMCP FLOW DIAGRAM                    | • |   | • |   |   |   | 54 |

| 19. | HWIND FLOW DIAGRAM                   | • |   |   |   |   |   | 57 |

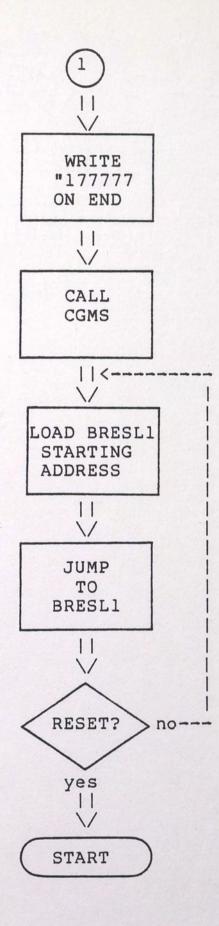

| 20. | CGMS FLOW DIAGRAM                    |   |   |   |   |   | • | 61 |

| 21. | BRESL1 FLAG BITS TRUTH TABLE         |   |   |   |   |   |   | 64 |

iii

| 22. | HOST CONTROL PROGRAM FLOW DIAGRAM | • | • | • | • | • | • | • | 66 |

|-----|-----------------------------------|---|---|---|---|---|---|---|----|

| 23. | IKONAS SR8 MEMORY MAP             |   |   |   |   | • |   |   | 73 |

| 24. | SEL INPUT BUFFER FORMAT           |   | • |   |   |   | • |   | 77 |

| 25. | TARGET DESIGNATION EXAMPLE        |   |   |   | • | • |   | • | 82 |

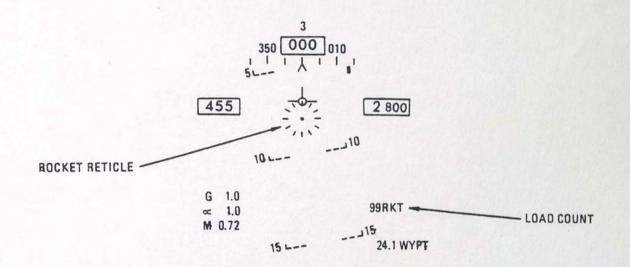

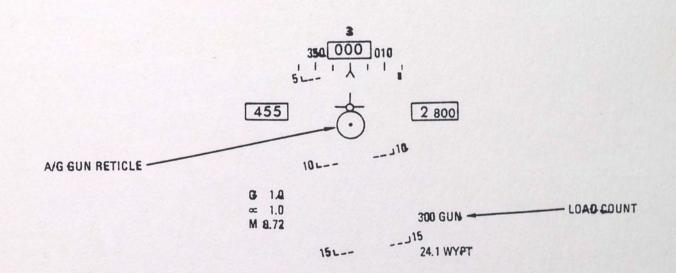

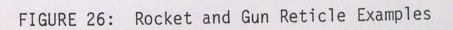

| 26. | ROCKET AND GUN RETICLE EXAMPLES . |   |   |   |   |   |   |   | 84 |

#### ABSTRACT

A computer graphics simulation of an aircraft Head-Up Display was designed using an RDS-3000 Ikonas Graphics Processor and a PDP-11/34 host computer system. The software control and display modules were accomplished using Ikonas microcode and Digital Equipment Corporation Fortran The Head-Up Display system consists of the basic IV-PLUS. flight data, which includes aerodynamic flight information, Roll/Pitch Ladder, and the Velocity Vector or Flight Path The system was designed for flexibility Marker. in modifications and evaluation of various weapons delivery systems. These will be adapted to specific needs by research scientists and engineers at the Visual Technology Research Simulator in Orlando, Florida.

#### INTRODUCTION

The Head Up Display (HUD) is now used in almost all of the United States aircraft involved in Air-to-Air or Air-to-Ground combat. This capability allows the fighter pilot to concentrate on a target, without having to look down to see the instrument readings. At the same time it provides helpful information on the location of the target and calculates an accurate weapon release time for the pilot.

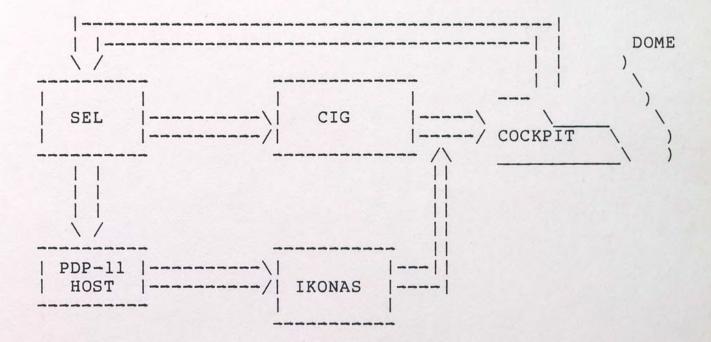

The flight simulator at Visual Technology Research Simulator (VTRS), Naval Training Equipment Center, Herndon Annex, Orlando, Florida, is presently configured as T<sub>2</sub>C a flexibility to simulate other trainer aircraft with the aircraft as well. The simulator's system configuration consists of three modules, with the HUD system being an added peripheral device as shown in Figure 1. A Systems Engineering Laboratories (SEL) computer is used as the dynamic information retrieval and update element. This monitors and updates the information received from system the aircraft cockpit and sends it to a CIG system. The Computer Image Generator (CIG) projects images of Air-to-Air and Air-to-Ground databases. These are updated at 60 Hz and have the capabilities of simulating weapons attacks for rockets, bombs and guns. The CIG uses the dynamic data received from the SEL system to produce the image that results from the pilots actions. The image is then transported to the display module to be projected onto the concave surface of a domed screen surrounding the simulator cockpit.

FIGURE 1: General Block diagram of VTRS system.

The SEL Computers also transfer dynamic data pertaining to the HUD to the PDP-11/34 Host Computer via an High Speed Data (HSD) interface. Once received, the host computer will use the new data to update the old, and send the updated

information to the IKONAS GRAPHICS PROCESSOR. The Ikonas will in tern produce an updated display to the HUD projector at a rate of 30 Hz.

The HUD system which consists of a PDP-11/34 Host Computer and the Ikonas Graphics Processor, is explained in detail in Chapter I. The PDP-11 uses FORTRAN FOUR PLUS and MACRO-11 compilers. Virtual addresses in memory can be defined by the Fortran Task Build procedures. Therefore this will enable the control and update portions at the host to be done in Fortran. All other specialized processing can be accomplished using Ikonas Microcode. The Ikonas is based on the AMD 2903 bit/slice architecture, and uses a multiple Ikonas Bus. The 64 bit microcode instructions are access used for Address and Operation Code processing. The Ikonas sytem is equipped with a Matrix Multiplier unit, a Character Generator, as well as image processing memory and control features. These high speed units assist the processors in the generation of objects and characters in a realtime processing environment.

Prior to the development of the HUD, the flight simulator has made use of an Optical Gunsight which when projected, is a static display with hash marks indicating the Milliradians of depression. The Mill depression is used by the pilot as a means of predicting the trajectory that a certain weapon will take. Once the aircraft is in line with the proper Mill depression, then the weapon can be released.

This system is a primitive method and the need for a more accurate and reliable weapons system is evident.

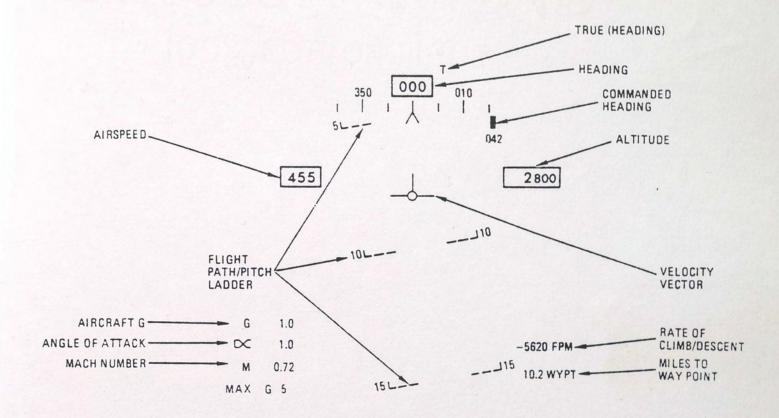

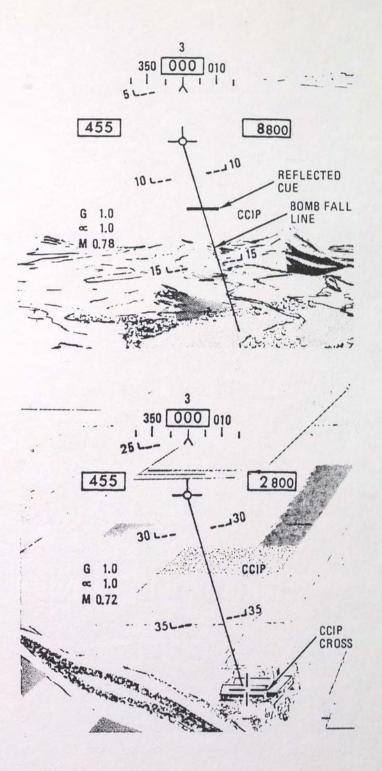

Figure 2 is an illustration of the Basic Flight Control HUD in standard flight. The basic flight data of the HUD consists of three modules:

- 1. Generation of dynamic flight control data.

- 2. The Flight Path Roll/Pitch Ladder.

- 3. Update of the Aircraft Velocity Vector.

The flight control data consists of an alphanumeric display the Heading, Airspeed, and Altitude located in boxes in of the upper quadrant of the HUD display. The Aircraft G, Angle of Attack, Mach Number, and Rate of Climb/Descent are located on the bottom sides. The Roll/Pitch ladder is a dynamic display of the aircraft's viewpoint to the horizon, and gives the flight path in relation to the Velocity Vector. The Velocity Vector or flight path marker is the direction which the aircraft is taking while in flight. The coordination of these three modules basically allows the pilot to fly the aircraft in an upright position only having down to the instruments in the cockpit seldomly. to look From this configuration a number of different weapon status delivery displays can be constructed. These features and are discussed further in Chapter V.

The HUD is designed for a realtime environment, in which the system must be synchronized with the other

functions of the simulator. This requires an analysis of timing as well as a knowledge of the processes of the simulator. The following is a list of the goals included in this research project.

- Implementation of the Basic Flight HUD as described previously.

- The design of software for a Host Control Module to:

- Receive dynamic flight control information from the SEL 32/75 via a High Speed Data (HSD) interface.

- Convert data into visual update and coefficient matrix information.

- 3. Send the data and control information to the locations of the Ikonas Processor Memory.

- Control execution and synchronization of Ikonas microcode.

- 3. Develop Ikonas Microcode For:

- An executive module to call other microcode modules and to synchronize with the Host Control Module.

- A microcode program to create a window to extract portion of roll/pitch ladder to be displayed on the HUD.

- Make any modifications to other microprograms to be used.

- 4. Discuss various forms of weapons control functions.

System requirements, as well as aeronautical specifications must be met, and a detailed definition of

FIGURE 2: Basic Flight HUD

each element of the HUD must be made. The Timing Analysis includes calculation of matrix multiplication rates, and the time required for dynamic character updates and output to the display. These must be synchronized to produce a 30 Hz update rate.

The following chapters in this paper will describe in detail the methods and decisions which were made in the development of the HUD. Chapter I describes the Ikonas Graphics Processor System and its requirements. Chapter II is an explanation of the HUD functions and specification requirements. Chapters III and IV are devoted to describing the firmware and software development, Chapter III explains Microcode and Chapter IV is a detailed the Ikonas description of the host programming. Chapter V is devoted to a discussion of weapons status and release algorithms and their uses. The Results and Conclusions are presented as Chapter VI.

7 .

## CHAPTER I

#### IKONAS GRAPHICS SYSTEM

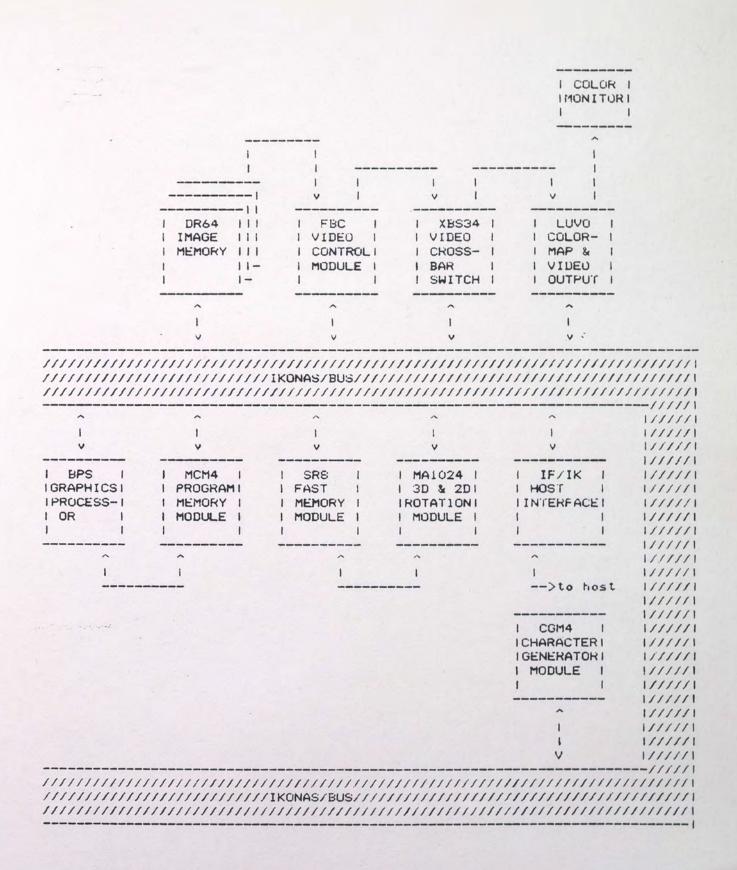

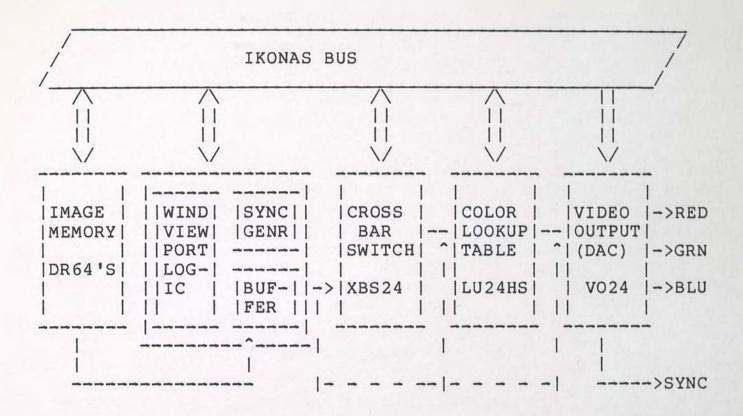

The IKONAS RDS-3000 Graphics System is a 32 bit 200 cycle bipolar processor consisting of several nsec processing units. These all share one common bus called the BUS, which is a 100 nsec, 32 bit data, and 24 bit IKONAS address lines. Figure 3 is a block diagram of the Ikonas System configuration (Ikonas 1980). The BPS32 processor is controlled by 64 bit microcode instructions stored in static memory. The system can be programmed to diplay a variety of graphics applications and can update displays in Image Memory at variable rates of up to 60Hz. The Ikonas Graphics System also includes a PDP-11/34 Host computer, which is interfaced with the Ikonas using a DR11B interface board to the Ikonas Host Interface. This gives the system an external processing power as well as control capabilities from two separate units.

FIGURE 3: Ikonas Processor, Multiplier, Character Generator, Host Interface and Video Output Modules

#### 1.1. Hardware Overview

The processing units for the RDS-3000 system can be isolated into five modules. The BPS32 Processor/Sequencer, MA1024 Matrix Multiplier, CGM4 Character Generator, Host Interface, and the Video Output Chain Modules. These modules all share the Ikonas Bus and require control circuitry or microcode control to interact with each other. The PDP-11/34 Host Computer can also gain access and control of the Ikonas Bus via the Host Interface.

#### 1.1.1 BPS32 Processor/Sequencer

The BPS32 processor and sequencer are based on Advanced Micro Devices Am2903 bipolar bit slice processor and the Am2911 bit slice microprogram sequencer (AMD, 1981). The Ikonas Processor operates with 32 bit registers, and 64 bit microcode instructions. The microcode is used as control and address data for both sequencer and processor modules. Each microcode instruction executes at 200 nsec/cycle, and they can be stored in static RAM microcode memory or in ROM memory. The 64 bit microcode word is separated in two parts. Thirty two bits are used by the MPS 16 Sequencer for next address and immediate data selection. The other 32 bits determine operation selection and ALU functions.

The BMP32 is the processor unit, and carries out the functions selected from the microcode. The MPS 16 sequencer is responsible for fetching microcode instructions, determining next address originations, and selecting some operation fields to be coordinated with the processor. Together these two units function as one module, and after a hardware evaluation of each, will be treated as such.

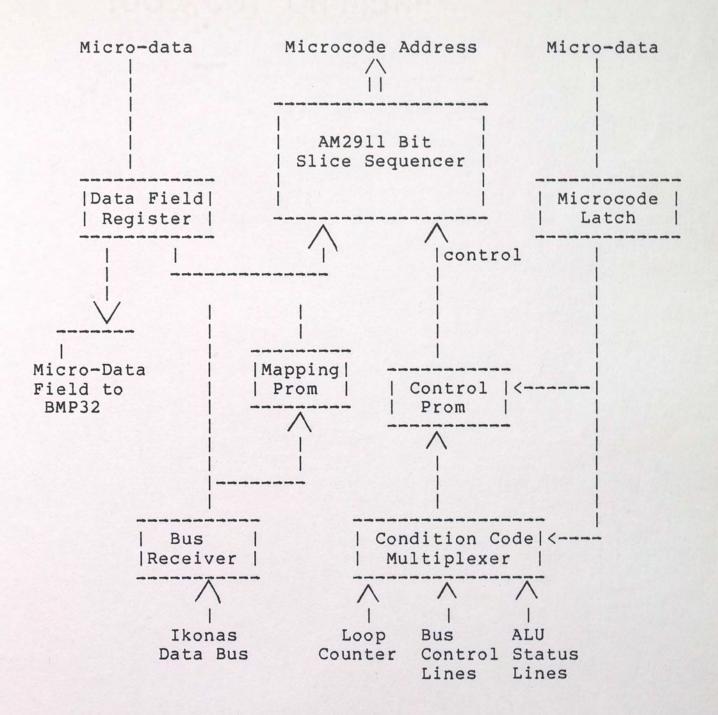

## 1.1.1.1 MPS 16 Sequencer

The MPS 16 sequencer consists of a multiplexer bit slice sequencer (Am 2911) and some control circuitry. Figure 4 is a block diagram of the MPS 16 sequencer. The Data Field Register and Microcode Latch are inputs for microcode data to the sequencer unit. From this the specific field(s) are selected. These fields may consist of next address, Ikonas Bus functions, or Data Field direction operation codes. The fields which can be activated are as follows:

OP CODE: The Op Code function selects an appropriate PROM CONTROL address, which determines the path from which the next microcode address will come from. The address can originate from one of four inputs, the data field, program counter, the on chip four word stack pointer, or a latch delay from the data field. When a path is chosen, that line

FIGURE 4: MPS16 Microsequencer

contains the 16 bit address of the next microcode instruction to be fetched and executed. Using the Am2911 allows loops and subroutines to be executed with no overhead, and the Control Prom has the flexibility of being programmable. The other 32 bits of microcode data is latched to the control portions of the BMP32, and 16 bits of the microsequencer data can be selected to pass as data to the microprogram Data Field Register on the processor.

DATA FIELD: This operation directs one of the three paths onto the data field, depending of the OP CODE and LOAD CONTROL bits selected. It can be sent as immediate data to the BMP32 processor, used as a loop counter for the sequencer, or as a pipeline address for the next microcode instruction.

CONDITION CODE SELECT: The condition codes allow the programmer to execute various OP Codes depending on conditional executions. Options presently implemented are: Host Request High, Matrix Multiply Busy, Image Memory Busy, ALU Overflow, ALU Negative, ALU Zero, and ALU Carryout. The condition code multiplexer is designed such that others can be introduced with very little difficulty. Condition parity can also be selected as to whether an operation takes place on a condition TRUE or FALSE.

LOAD CONTROL: The Load Control determines if the 16 bits of microsequencer data is latched to the processor data register or used as a loop counter for the MPS 16.

IKONAS BUS FUNCTION CODE: This code determines the type of transfer and destination of data to or from Static (32 bit parallel) or Dynamic (1024X1024) RAM, the Matrix Multiplier, or other special purpose devices.

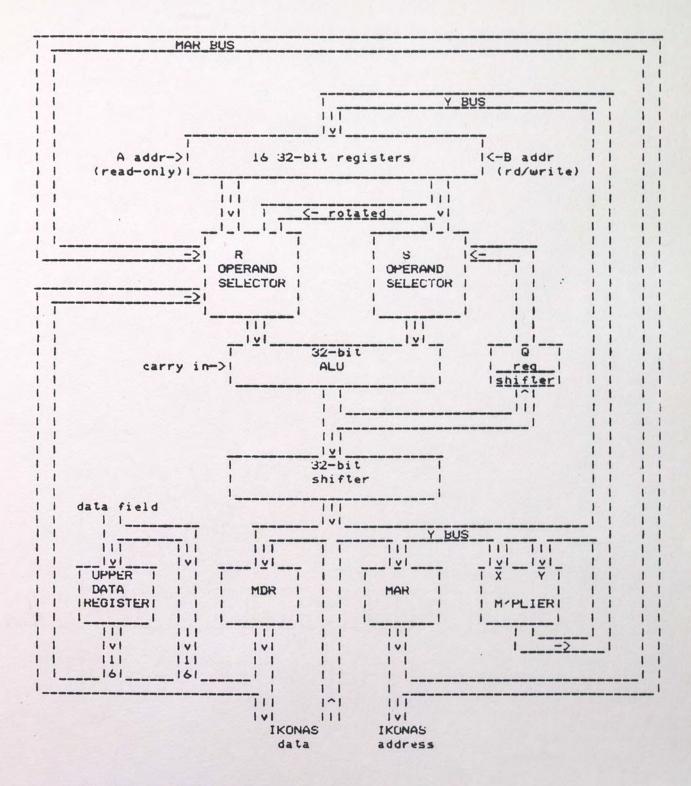

#### 1.1.1.2 BMP32 PROCESSOR

The BMP32 processor consists of sixteen 32 bit general purpose registers, two selectors and shifters as part of the Am 2903 processor, an R bus selector, the Y bus, MDR, MAR, Data Register, and connection circuitry to the Ikonas Bus Data and Address lines. A block diagram of the BMP32 processor and its control circuitry is shown in Figure 5. The Data Registers consist of dual port RAM, such that addresses can be selected from two ports simultaneously and data transmitted thru two address ports A and B independent of each other. Data is written to the registers only through address port B.

The 32 bit microcode instruction that are input to the processor, are used to determine several fields.

- 1. R and S Operand Select

- 2. ALU Instructions

- 3. Carry and Shift Control

- 4. Y Bus Source/Destination

- 5. Data Register Bus Source

- 6. Ikonas Bus Enable/Address Source

All of these fields are selected using different parts of the 32 bits of microcode instruction. The format and execution tables for these fields will be further discussed in Chapter III.

S OPERAND SELECT: The S Operand can be selected as a Y Bus output destination or any of the 16 data registers. The field can also select the Q register as the S Operand.

R OPERAND SELECT: This field can select any of the 16 data registers or the R Bus as the R operand. Using the R Bus there are a few paths which data can take, to the R operand. There is the Data Register, transferring both high and low addresses. The R Operand can also be loaded from MAR, and data from the B register in several forms. These are selected by the ALU FUNCTION field.

ALU FUNCTION: The Arithmetic Logic Unit on the Am 2903 is capable of performing nine logical and seven arithmetic operations on both 32 bit operands. The selection of the Q shifter and Q register are also a part of the ALU Function. There are special functions which the ALU can select as well, such as multiplication, division and normalization. Selection of shifts, either arithmetic or logical are among some of the other functions. These can be determined to be left or right shifts, as well as determining the type of shift required. The write control for the B and Q registers are also selected from this field.

ALU SHIFT AND CARRY CONTROL: Though the direction and type of ALU shift is controlled by the ALU Function code, the selection of either a shift or rotate is made in the Shift Control Field. A shift can be selected as a long shift, 64 bits of both the ALU and Q shifter combined to form one, or short shift, each being used as separate 32 bit shifters. The Carry Control Field is used to select whether operands are to be treated as two 16 bit words, or one 32 bit word. In the 16 bit form two carry bits can be set or cleared, bit Ø and 16. In the 32 bit case only one carry bit is available but has the flexibility of Ø, 1, bit 31, or bit 31 inverted.

YBUS SOURCE/DESTINATION: The Y bus is used as a communication link between the Am 2903 and the other parts of the BMP32 processor. Inputs to the Y bus can come from

# Figura and McDuffie's Model

This speciation scheme was developed in 1980 and divided soluble heavy metals in environmental water samples into four categories. Trace metal species are classified as "very labile" which includes free and hydrated metal ions, "moderately labile," "slowly labile," and "inert." The non-labile fraction includes metal bound in complexes or absorbed on colloidal material with a slow rate of dissociation to the free metal. Examples of "moderately labile" fractions might be Cd-NTA (Cd-nitrilotriacetate) or Cu-humate. Also, some examples of "slowly labile" fractions might be Cd-, Pb-, and Zn-EDTA (Zn-ethylenediaminetetraacetic acid) complexes.

Figura and McDuffie (1980) applied their scheme to St. Lawrence and Susquehanna River waters and Hudson River Estuary samples. The estuary samples were distinctly higher in Cd, Cu, Pb, and Zn content than samples from the St. Lawrence and Susquehanna rivers. The soluble lead represented only 11 to 46 percent of the total metal. Most of the Cd and Zn in all the samples existed as "very labile" or "moderately labile," with a small percentage of "slowly labile" and no "inert" fractions. In contrast, both Cu and Pb existed in forms which are less labile. Copper was found almost entirely in the "moderately The Am 2903 also has special functions which are utilized by the processors ALU. These functions are provided by Ikonas in the form of special ALU operations. These special functions are as follows.

- UMPY-UNSIGNED MULTIPLY: Using B register for result, CARØ and SSØ are used for multiplication of unsigned numbers.

- TCMPY-TWO'S COMPLEMENT MULTIPLY: The result also in B register, using CARØ and LRØ for multiplication of two's compliment numbers.

- 3. INCRS-INCREMENT OPERANDS: the S operand plus l plus the Carry is placed in the B register.

- 4. SMTC-SIGN/MAGNITUDE TO TWO'S COMPLEMENT: Converts S operand from sign/magnitude to two's complement using CARZ and written to the B register.

- 5. TCMPL-TWO'S COMPLEMENT MULTIPLY LAST CYCLE: Two's complement multiply of last step using RSØ and CARZ, is written to the B register.

- 6. SLNML-SINGLE LENGTH NORMALIZE: Used to normalize the Q register with CAR1, SSØ and CCOVR bits. The S operand is incremented and sent to the B register.

- 7. DLNML-DOUBLE LENGTH NORMALIZE: The Double length normalize uses CARØ, LSØ and CCOVR to normalize the Ø register and S operand. Also used for first step in division with CARØ and LR.

- 8. TCDIV-TWO'S COMPLEMENT DIVIDE: Uses CARZ and LR for two's complement divide operation.

- 9. TCDIVC-TWO'S COMPLEMENT DIVIDE CORRECTION: The division correction takes place on the final step and uses CARZ and SS1 bits.

These functions as well as the other operation codes for the BPS32 microcode are presented as tables in Appendix A. The name of the function and the bit numbers in microcode it represents are given. This allows the programmer to construct microprograms with a one-to-one correlation between instruction and microcode.

## 1.1.2 MA1024 MULTIPLIER

The MA1024 Matrix Multiplier is 64 bit a microprogramable, high speed multiplier, capable of processing 300,000 multiply operations per second. It is a 200 nsec, 16X16 bit multiply and 35 bit Add/Subtract accumulator. The 1024X16 on-card memory buffer is used to store transformation arrays. The multiplier has direct access to the dual port 100 nsec 32 bit static RAM module (SR8). Three dimensional transformations can be done with less than microsecond execution time. The a multiplier/accumulator is microprogrammable has and a control module to control access of the Ikonas Bus lines and static RAM modules.

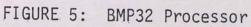

There are several locations to which information can be written to or from within the MA1024 matrix multiplier. Using the Ikonas Bus, information can be written to the MA1024 at several locations: the 1024X16 Coefficient Memory (CM), 1024X32 Microprogram Memory (MPM), or one of three Control Words. Control Word Ø is made up of the microprogram memory starting address which is eight bits, the microprogram memory page of two bits, coefficient memory starting address with eight bits, and coefficient memory page two bits. Control Word 1 consists of the static RAM input and output address both fifteen bits in length. Control Word 2 is for loop counter data and is twelve bits. To read from the MA1024 the following locations can be accessed. Coefficient Memory (CM), the thirty two bit XY and ZS Product Latches, and sixteen bit W. The Auxillary Bus Interface allows access of two to the fifteenth memory locations in static RAM by the MA1024. RAM addresses are loaded by the microcode control from the Ikonas Bus. An Auxillary Bus READ or WRITE is controlled by the static RAM Read/Write Line (SRW-L). A write will send data to the XY or ZS input latches, and a read will send it through the XY or ZS product latches. All of these latches are thirty two bits, and receive the address information from counters which get incremented by microcode control. This enables the multiplier to operate with full parallel processing, and does not require access to the Ikonas Bus to run.

The 4X4 coefficient matrix controls the rotation of a graphics image of a three-dimensional object. The coefficient matrix can be loaded from the Ikonas Bus into the coefficient memory of the MA1024. The basic form in which each point is multiplied with the coefficient matrix and represented as the rotated output points, is shown in Figure 6 (Rogers 1976).

|                            |       | Cxx         | Cxy Cxz            | ØI |

|----------------------------|-------|-------------|--------------------|----|

| [ Xo Yo Zo l ] = [ Xi Yi Z | ; 1 1 |             |                    |    |

|                            | 1 1 ] | Czx         | Cyy Cyz<br>Czy Czz | Ø  |

|                            |       |             | Ty Tz              | 1  |

|                            |       | web and and |                    |    |

FIGURE 6: Coefficient Matrix Equation

Equations for each coefficient were determined using a method for transformation of three-dimentional objects (Newman 1979). The first column of the matrix is devoted to calculating the YAW diffraction, the second calculates the PITCH, and the third is for the ROLL.

Figure 7 is a diagram of the path of flow control in which the MA1024 multiplier follows. The correct procedure for loading control information, data and execution of the MA1024 processor is as follows.

1. Load the correct microcode routine into the MA1024 program memory. The standard rotation microprogram supplied by Ikonas is MMEOL.MOB. This program is used for this application, though the user can write other microcode programs for the MA1024 if desired. The microcode can be loaded from the PDP-11/34 HOST COMPUTER using the system task called the Online Debugging Tool (ODT).

FIGURE 7: MA1024 Control Flow

- 2. Load data to be transformed into the static RAM memory (SR8), terminating the sequence with bit 30 set on the last word.

- Load the coefficient matrix into coefficient memory.

- 4. Send control data to the MA1024 at address 20402\$0. The following data to be stored at these locations.

1. MA1024 microprogram starting address

2. coefficient matrix address (offset from 0)

- 3. Data input address

- 4. Data output address

- 5. Start the Multiplier by storing Ø at address 2Ø4Ø2\$3 using the function sending code 25, if starting from the host computer.

Figure 8 shows the format for the control data sent to the matrix multiplier. This procedure is only for the standard case. If the programmer wishes to use other features of the MA1024 matrix multiplier microcode then this may change (Ikonas 1980).

| 2Ø4Ø2\$Ø | Coefficient Address                             | Microprogram Address    |

|----------|-------------------------------------------------|-------------------------|

|          | محم محل عدى |                         |

| 20402\$1 | Data Output Address                             | Data Input Address      |

|          |                                                 |                         |

| 20402\$2 |                                                 | Loop Counter (optional) |

|          |                                                 |                         |

| 20402\$3 | Clear both locations                            | to start processor      |

|          |                                                 |                         |

# Figure 8: MA1024 Control Address Format

#### 1.1.3 CGM4 CHARACTER GENERATOR

The Ikonas CGM4 is a high speed character generator which is capable of writing one million pixels per second. These can be written directly to the DR64 Image memory framebuffer for output to the display. The character size can be selected by the programmer to a 32X32 pixel size. A user programmed character set or font can be used by the character generator, and is accessed through the Ikonas SR8 memory. The CGM4 comes equipped with an on-board font which gives access to a standard 7X9 pixel character set without any additional font programming. From this the character font may be magnified, or written in variable directions either up, down, left or right. Control of the character generator is done through microcode programs and information sent from the PDP-11 Host Computer. The CGM4 requires a few things other than the font program information.

- Must receive the address in which character strings of certain length are to be displayed.

- 2. The address in the font of a specified character.

- The character string itself should be placed in SR8 memory to be looked up by the character generator.

- 4. The CGM4 Control Blocks, used for Mode settings, and flags, must be sent to 20600\$0 and CGMCB.

The microprogram developed for the dynamic character update process on the HUD is called CGMS.MOB. This is used to control the output character strings of up to eight characters to specified pixel addresses. The character and pixel address information are updated and written to Ikonas memory by the Host Control Program. The programming techniques for the character generator are discussed further in Chapters III and IV.

There are two control blocks which are used by the CGM4, the CGM4 Base Control Block located at 20600\$0, and the Auxilary Control Block (CGMCB), which is addressed by base control block anywhere in SR8 memory. The format the for CGMCB is shown in Figure 9. The character height and The Font Table Offset is the width are done in pixels. If address in SR8 memory where the font table is stored.

the on-board standard font table is to be used then this value would be zero. The character shade is the color in which the pixels representing the character would be. The background shade is for those pixels which are not written as characters, and is only recognized if the Non-Transparent mode is selected by the CGM4 base control block. The character spacing selection gives the numbers of pixel spaces to allow between characters. The starting output address is used only when all characters to be displayed are from one starting address. The microcode CGMS.MOB allows multiple strings of eight characters or less to be displayed from varying starting addresses. The character string address is the address in memory where the ASCII character strings are stored. The CGM4 base control address consists of 2 Ikonas words (32 bits), located at 20600\$0. Figure 10 shows the format to the base control block.

3

3

2

2

2

2

2

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Figure 9: Format For CGMCB Control Block

3

2

2

2

2

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Figure 10: Format For CGM4 Base Control Block

The direction can be selected as ØØ-left to right (normal), Øl-top to bottom, 10-bottom to top, and ll-right to left. The T bit is used for selecting transparent or non-transparent background shade. If set, the background shade color is written. If not the background pixels are left unchanged. The W is used to select word mode writes or pixel mode, the former is the normal case (W=Ø). The F determines whether the use of the on-board font or if a font located in SR8 memory is to be used. The G bit is the Go bit, this is set after all other control words are in place and is ready to start the character generator. The G bit will stay high as long as the CGM4 is busy. When low it becomes ready for another character to be written. The X zoom are used as magnification factors in each and Y respective direction.

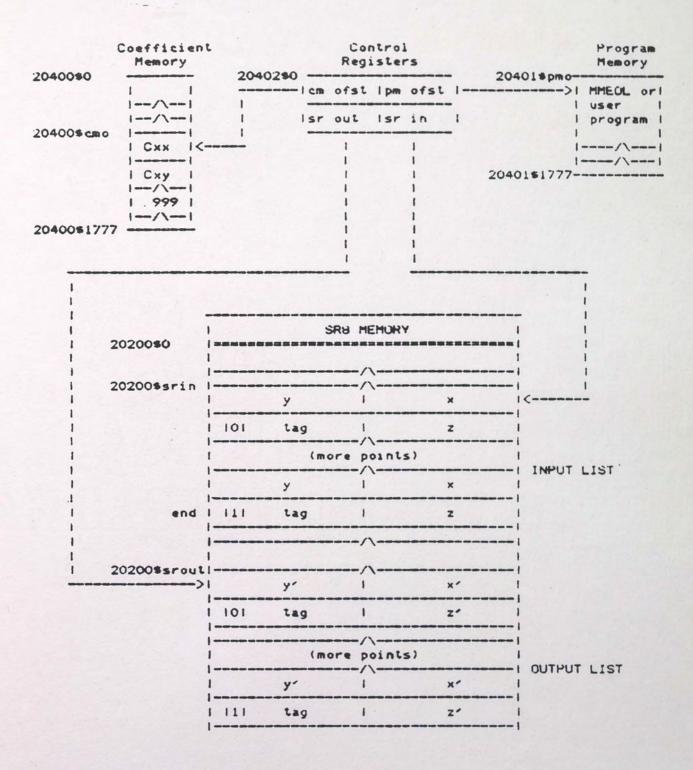

#### 1.1.4 IF/IK HOST INTERFACE

The IF/IK Host Interface has a direct DMA connection between the host PDP-11/34 computer and the Ikonas Bus. It can transfer two million bytes per second when DMA is selected. The interface also has the ability for single word transfers for smaller I/O demands. This reduces the time overhead for transferring smaller blocks of information. There are several modes of transfer which can selected 32, 16, or 8 bit modes allows flexibility and be better efficiency for smaller items. Figure 11 shows examples of the three modes of transfer that can take place either to or from the Ikonas processor. The 32 bit WORD transfer allows easy access to 32 bit data. One 32 bit Ikonas word corresponds to two 16 bit host words. The low order half of the Ikonas word represents the even host word and the odd is the high order half of the Ikonas word. The bit transfer otherwise called HALFWORD mode is used when 16 one 16 bit host word is to represent one 32 bit Ikonas word. high order portion of the Ikonas word is left zero. 8 The bit transfers become desirable in accessing single image components. Any one of the four bytes of an Ikonas word can be accessed or written to. This type transfer is referred The Ikonas interface also to as BYTE mode. supports vectored interrupts from the Ikonas to the host. The host

FIGURE 11: Transfer Mode Examples

can be programmed to control activities on the Ikonas Bus through the interface. An Ikonas system-reset can be accomplished from the host computer.

The PDP-11/34 is tied to the IF/IK Host Interface by a DR-11B Parallel Interface card. The DR-11B can be assigned virtual address locations which correspond to transfer and control lines at the DR-11B. In this manner control programs at the host computer can have access to the lines of the Ikonas interface. This allows transfers to be made using Fortran, and transfer control can be initiated from the Host computer.

The Ikonas Interface Control Register is defined in the host software as IKSCSR and has the format shown below.

|   | 1  | 1 |   | 1 |   | 1 |   | 1 |         | 1 |     |   |   |   |        |   |   |   |   |   |   |     |      |    |   |

|---|----|---|---|---|---|---|---|---|---------|---|-----|---|---|---|--------|---|---|---|---|---|---|-----|------|----|---|

|   | 5  | 4 |   | 3 |   | 2 |   | 1 |         | Ø |     | 9 |   | 8 |        | 7 |   | 6 |   | 5 | 4 | 3   | 2    | 1  | Ø |

|   |    |   |   |   |   |   |   |   | • ••• • |   | • • |   |   |   | • •••• |   |   |   |   |   |   |     |      |    |   |

| 1 | BY | г | 1 | F | 1 | Ρ | 1 | в | 1       | R | 1   | Х | 1 | + | 1      | I | 1 | D | 1 | H | 1 | fur | ncti | on | 1 |

|   |    |   |   |   |   |   |   |   |         |   |     |   |   |   |        |   |   |   |   |   |   |     |      |    |   |

The function code is used to determine the type of transfer to be made. Bit 4 is the read/write line and is set for a write. Therefore the most common function code for a write is \$20 and for a read \$00. There are special cases when reading or writing to particular modules. For example a write to the MA1024 matrix multiplier module would be \$25. The DR64 Image memory has several special function codes to distinguish resolutions and access addresses. The H bit is set for HALFWORD mode and off for WORD or BYTE mode. The D

bit is set when DMA transfer is to take place. The I bit is used for invisible I/O. The + bit is set to increment Ikonas address between words, this is usually always set. The X bit is set when the BPS32 is to execute, when this bit cleared the processor will stop and setting it again is starts the BPS32 processor where it left off. The R bit forces an Ikonas system reset. The B bit is set for BYTE mode, F is read-only and specifies the vertical blanking interval. The P bit is also read-only, when on the Ikonas is requesting service from the host. The BYT is a byte number to be selected for the byte mode transfer, and is used only when bit 11, the B bit is set.

#### 1.1.5 VIDEO OUTPUT CHAIN

The Video Output Chain is a module in the Ikonas system which is responsible for the display of the images produced. This module can be better explained as three units. The DR 64B Image memory, the Frame Buffer Controller (FB/HC), and the Video Output. Figure 12 is a block diagram of the Video Output Chain.

FIGURE 12: BLOCK DIAGRAM OF VIDEO OUTPUT CHAIN

## 1.1.5.1 DR 64B IMAGE MEMORY

The DR64 is organized in bit plane modules of 512X512 of 8 bits or 1024X1024 of 2 bit pixels. This allows the configuration of images which are software selectable between a low resolution (512X512) or high resolution (1024X1024) display. The Image memories can be configured to display up to 512X512X32 or 1024X1024X8 bit resolutions. The DR 64B is a dual port 128K byte dynamic RAM, with a memory access time of 300 nsec. One port is used for communication with the Ikonas Bus, and the other is for video rate I/O. When a pixel is addressed to the DR64's

several of these memory devices are selected at one time. When using the low resolution called LORES, a 512X512 display image is created. Three DR64's are used to create a 24-bit color image, consisting of eight bits of red, green, and blue pixel bits. Using high resolution called HIRES a 1024X1024 image of four 2-bit color codes is produced. LORES and HIRES can only be selected by using the function codes as discussed in the Ikonas Interface sections. The Ikonas Bus function codes for selecting LORES is \$02 for a read, and \$22 for a write. For HIRES the function codes are \$03 and \$33 for read and write modes. In both cases pixels are addressed as (X,Y) coordinates. The LORES pixels are addressed in multiples of two, thus the pixel address values for X and Y, must be doubled to produce the correct output. The HIRES pixel addresses do not require a multiplication factor. The value of the X\$Y coordinate is the actual pixel address.

### 1.1.5.2 FB/HC FRAME BUFFER CONTROLLER

The Frame Buffer Controller determines which data to display, fetches the data from the DR64, and sends it through the video output chain. This is done using the control of the following lines.

- Aspect Ratio The ratio of height to width of the picture display.

- Automatic Erase Erases the screen automatically succeeding each display.

- Cursor A programmable cursor which can be displayed in any shape. The cursor may be up to 32X32 bits and location must be specified.

- Video Synchronization Rates Gives the writing time for each line and the number of lines per field.

- 5. Viewport Selects the size and position of the pixel data within the viewport.

- Zoom The amount of magnification which is applied to each pixel written to the display.

The data is transferred from the the DR 64 through the video output ports in parrallel up to four pixels at a time. The FB/HC then places it in a sequential format and sends it out the serial video bus to the Video Output Module.

The control block for the FBC consists of seven 32 bit registers starting at address 30000\$0. Figure 13 is a diagram of the FBC control block. Registers 0 and 1 are used to determine viewport starting locations and size. The location of the window inside the viewport is established in bit 30000\$2. 30000\$3 controls the zoom or magnification factor, each numerical integer increases or decreases the size of the coordinate by a factor of two.

|   |   | 2 2<br>3 7 |     |     |     |     |     |     |     |     |     |     |   |  | -    |  | l<br>Ø | 9   | 8   | 7   | 6   | 5   | 4  | 3  | 2  | 1  | ø |

|---|---|------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---|--|------|--|--------|-----|-----|-----|-----|-----|----|----|----|----|---|

| ø |   |            |     | 3   | 2 1 | /ie | ewp | 201 | t   | SI  | car | rt  |   |  | <br> |  |        | 2   | X   | /ie | ewr | 201 | t  | st | ar | t  | 1 |

| 1 |   |            |     | ]   | 2 1 | ie  | ewi | 201 | t   | s   | ize | 9   |   |  |      |  |        | 2   | X N | /ie | ewp | por | t  | si | ze |    | 1 |

| 2 | 1 | Y          | w   | ind | lov | v ] | Loc | cat | ic  | on  |     |     |   |  |      |  | X      | W   | ind | lov | v ] | Loc | at | ic | n  |    | 1 |

| 3 |   |            |     |     |     |     | Y   | zo  | 001 | n   |     |     |   |  |      |  |        |     |     |     | Х   | zo  | on | n  |    |    | 1 |

| 4 |   | 1          | nur | nbe | er  | of  | E   | Lir | nes | 5/1 | Era | ame | 9 |  |      |  |        | tir | ne  | pe  | er  | 1 i | ne |    |    |    | 1 |

| 5 |   |            |     |     |     |     | I   | pix | (e) |     | 210 | bel | ٢ |  |      |  | R      | 3   | PC  | 3   | X   | E   |    | H  | CI |    |   |

| 6 |   |            |     | ]   | 2 0 | ur  | s   | or  | po  | si  | ti  | lor | 1 |  | <br> |  |        | >   | < ( | cur | so  | r   | po | si | ti | on | 1 |

Figure 13: FBC control Registers

The Frame Buffer Controller is responsible for setting synchronization information for the video signal. This is accomplished by controlling the number of lines per field, and the amount of time required for each line. The information is stored at address location 30000\$4.

The FB/HC Flag bits are used for setting modes of operation for video output. Register 30000\$5 is used for this purpose. This register is a write-only register to set flag and mode conditions. The C is set if a cursor is to be displayed. Bit H is OFF for a 512X512 LORES pixel display and ON for a 1024X1024 HIRES display. The E bit allows the DR 64's to be cleared after each field. The X bit is used if an external synchronization is to be used. If the video sync is to be produced by the FBC this bit would be zero. PG determines the color map page. These two bit tags are placed at the end of the pixel data to be used in the video output module. The (3) function at bit 9, is set if RS-343 synchronization is required. The R is a flag to determine whether a repeat field (ON) or interlacing is preferred (OFF). The pixel clock field which is seven bits in length, determines the number of nsec/pixel in LORES and nsec/half pixel, for HIRES diplays.

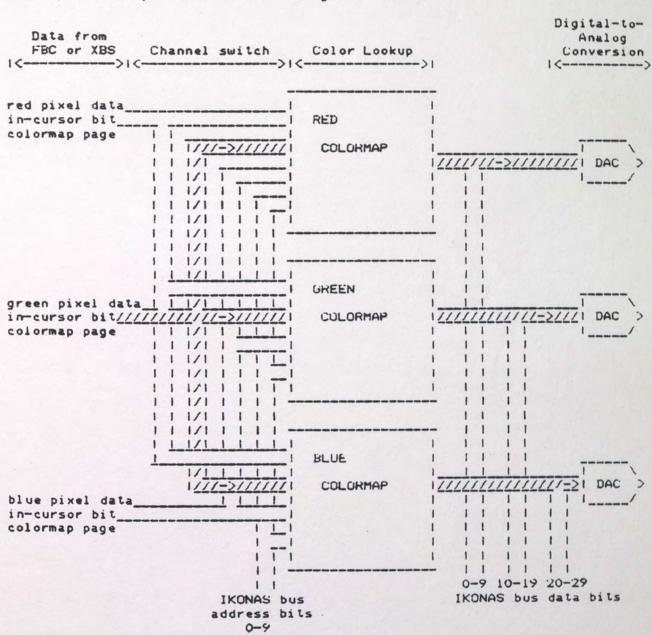

### 1.1.5.3 VIDEO OUTPUT

The Video Output module consists of the XBS34 Crossbar Switch, Color Lookup Table, and Output to Digital to Analog Converters. Figure 14 shows the path in which data will take through the video output. In this case the crossbar switch is set up to produce a mono-colored output, thus it bypasses the color lookup table to the output. This figure also shows an example of pseudo-color operations in which the green channel is selected for video output.

#### LUVO data routing - Pseudocolor Operation

(Example shows pseudocolor from the green channel)

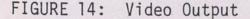

### 1.2 PDP-11/34 HOST COMPUTER

The Programmable Data Processor-11/34 is a minicomputer product of Digital Equipment Corporation. Figure 15 shows the general architecture of the machine, in the form of a block structure. The processor is equipped with a unique data bus called the UNIBUS. The UNIBUS is the key to the PDP-11 families flexibility. It was the first minicomputer data bus to allow information to be sent, recieved, or exchanged without processor intervention or buffering in memory (Digital 1978). This allows interfacing of other devices through the UNIBUS to be accomplished with less difficulty.

The PDP-11 uses the RSX-11M version 4.0 operating software system. This is a multi-tasking, realtime system which supports both development and task execution concurrently. The RSX-11M operating system has a number of user utilities which make program development and operation much easier. Tasks can be written in MACRO-11 Assembly Language or Fortran IV-PLUS (F4P).

The Host computer is interfaced using two DR-11B parrallel interface boards to both the SEL 32/75 simulation computer and the Ikonas Graphics processor. The SEL

FIGURE 15: PDP-11/34 CPU

.

interface is an HSD line that requires a special hardware communication interface to the DR11B, which was designed and implemented by (Sampayo 1982). The interface was designed so that flight data could be transferred from the simulator to the Ikonas Host computer. The interface from the second DR11B to the Ikonas Processor is accomplished through the Ikonas Interface as described previously. This allows transfers to be made as blocks of data (DMA), or as single data types. With these configurations and control capabilities from Host software, all transfers and communications can be syncrhonized.

#### CHAPTER II

### HEAD-UP DISPLAY

The HUD is used in Air-to-Air and Air-to-Ground fighter aircraft and is implemented in almost all of the modern aircraft of the worlds armed forces. As technology advances the levels of sophistication and detail of the flight HUD will increase, presumably until the need for conventional instrumentation becomes secondary.

In a true HUD the display is projected on a combining glass structure mounted on top of the main instrument panel as shown in Figure 16 (Navy 1982). The model simulation HUD implementation will project the HUD image on the simulator dome directly in front of the pilot. The size of the image is calibrated to be approximately the same as that which would be viewed through the combining glass.

Figure 2 was presented in the introduction as the basic flight HUD. This is the portion of the HUD which processes flight information and allows the pilot to fly effectively without looking down at the instruments in the cockpit. The three modules which are responsible for this process are:

FIGURE 16: Basic Flight HUD

- 1. Flight data information

- 2. Roll/Pitch Ladder indicator

- 3. Flight Path Marker or Velocity Vector model

The combination of these processes are the basis for the flight HUD, from this many different variation can be developed, depending on the environment or purpose of the aircraft (McDonnell Douglas 1980). Each of these functions will be discussed separately in terms of definition and implementation factors pertaining to the HUD system at VTRS.

## 2.1 FLIGHT CONTROL INFORMATION

The format for flight control data is the alpha numeric representation of the navigation and steering control information.

HEADING: The Heading indicator is located in the top center box of the HUD display. This is displayed in degrees with zero degrees being due north. The indicator is represented in a clockwise fashion, for example 90 degrees is east and 275 degrees is west.

AIRSPEED: The Airspeed indicator is the box at the left and below the heading indicator. This is represented as an integer number in nautical knots. ALTITUDE: The altitude indicator is represented in the box located at the right and below the heading on the HUD display. The alphanumeric representation in the box is the radar altitude which indicates the value derived from the aircrafts radar system. A backup system can be implemented which would automatically display the barometric altitude in the event that the radar altitude should fail. This would be distinguished from the radar altitude by placing a B on the right-hand side of the box, causing the number to flash on and off.

AIRCRAFT G: The G is located in the bottom left-hand corner of the Head-Up Display. This is the normal acceleration of the aircraft and is displayed in feet per second. The G is represented as a real number with one significant digit.

ANGLE OF ATTACK: The angle of attack is represented on the HUD as an alpha symbol, and is located just below the aircraft G. This is displayed in degrees as the True Angle of Attack. The alpha shown gives the angle at which the aircraft is in relation to the target. MACH NUMBER: The large M displayed just beneath the Angle of Attack symbol represents the Mach number. This is displayed as a two significant digit real number and calculates the fractional airspeed in speed of sound units.

RATE OF CLIMB/DESCENT: The FPM indicator located on the bottom right hand side of the Head-Up Display, gives the rate of climb or descent in Feet Per Minute. The negative sign indicates the aircraft is descending.

# 2.2 VELOCITY VECTOR

The Velocity Vector is represented as the small stick figure aircraft, usually located around the center of the HUD. This gives the pilot the actual flight path of the aircraft. The Velocity Vector is placed on the HUD at a point which describes the path which the aircraft is taking. On the HUD the Velocity Vector is caged to the vertical center line, this allows reference to the Roll/Pitch Ladder and steering information to be used with the Velocity Vector. The equation used by the HUD simulator for calculation of the Velocity Vector is shown below.

### VV=P\*alpha

Where P is the actual Pitch angle of the aircraft and alpha represents the Angle of Attack.

The Velocity Vector is used by the Roll/Pitch Ladder as the center point for the Roll angle. This gives the true roll point, but makes it more difficult to determine the actual pitch angle of the aircraft.

### 2.3 ROLL/PITCH LADDER

Artifical Horizon or Attitude Indicator is the conventional term for the Roll/Pitch Ladder. The Roll/Pitch Ladder or Flight Path/Pitch Ladder is used by the pilot to determine aircraft position with respect to the Flight Path Marker or Velocity Vector. This is determined with a display of flight path pitch lines representing five degree increments. These lines are each numbered at their respective angle and have a range of plus or minus 90 degrees. Positive pitch lines appear above the horizon, and are represented by solid lines. The negative pitch lines are those below the horizon line and are signified by dashed The Roll/Pitch Ladder software is designed for lines. normal operation between -90 and +90 degree pitch values. When a pitch angle is detected which exceeds these limits the angle is treated as the inverted or 180 degree roll

angle and the difference between the actual pitch angle from plus or minus 90 degrees is subtracted from the 90 degree pitch line. This works in the same manner as the glide slope indicator instrument functions in the aircraft cockpit. Thus, for example, an actual pitch of 180 degrees and roll of 0 degrees would appear on the Roll/Pitch Ladder as flying at 0 degree pitch upside down or with 180 degrees roll. The outer segments of the pitch lines adjacent to the character representation of the angle designate the direction toward the zero pitch line or the horizon line. This serves as an aid in determining flight path angle when dynamic elements are rapidly changing.

The Roll/Pitch Ladder database was constructed using a database development program written in FORTRAN specifically for this application. The program is entitled MAKDAT and was designed to allow maximum flexibility in Ladder in database construction. This allows the Roll/Pitch Ladder database to be modified easily and allows size calibrations to be accomplished quickly. Listings of the database the actual base modelling program (MAKDAT), and data (LADDER.DAT), are not presented for purposes of conserving user instructions are document length. Listings and available through the author for those interested.

The size of the Roll/Pitch Ladder as a whole can be adjusted by the user, as an option in the Host Control Program (HCP). This is a scaling factor which is multiplied

into each point representing the Roll/Pitch Ladder database. This feature allows for interactive changes in the size of the entire database. If only a part of the Roll/Pitch Ladder needs adjustment, such as the character size being enlarged, the database modelling program would have to be used.

The Roll of the aircraft is displayed as the rotational portion of the Roll/Pitch Ladder, and rotates about the Velocity Vector.

### CHAPTER III

### MICROCODE DEVELOPMENT

The Ikonas Graphics Processor's modular architecture is designed to allow multiple processing units to share a common bus. Therefore the individual modules within the Ikonas unit, use microcode instructions to process information. There are several different configurations which could be applied to the HUD system, because of the nature of the Ikonas system. Control of the Ikonas Bus can come from either the Host Computer or from within the Ikonas Processing Unit. Microcode instructions are executed independently from each respective Ikonas module, and only needs to communicate with others when requesting the use of Ikonas Bus. Thus a program in the host computer can be the inputting data and updating, while the Ikonas Graphics processor is displaying the previous information. Using this method the processing time would be the time takes it to transfer the necessary information from the PDP-11/34 Host Computer to the Ikonas working memory, plus the Ikonas image processing and display output time. With this

configuration the update rate of the HUD system was accomplished at 30 Hz.

There are two areas within the Ikonas Graphics Processor in which microcode programs for this application are stored. One is in the BMP32 Ikonas processor microcode memory and the other is the MA1024 Matrix Multiplier microcode memory. From these memories each of the respective microcode sequencers can fetch microcode intructions quickly and effectively (Ikonas 1980).

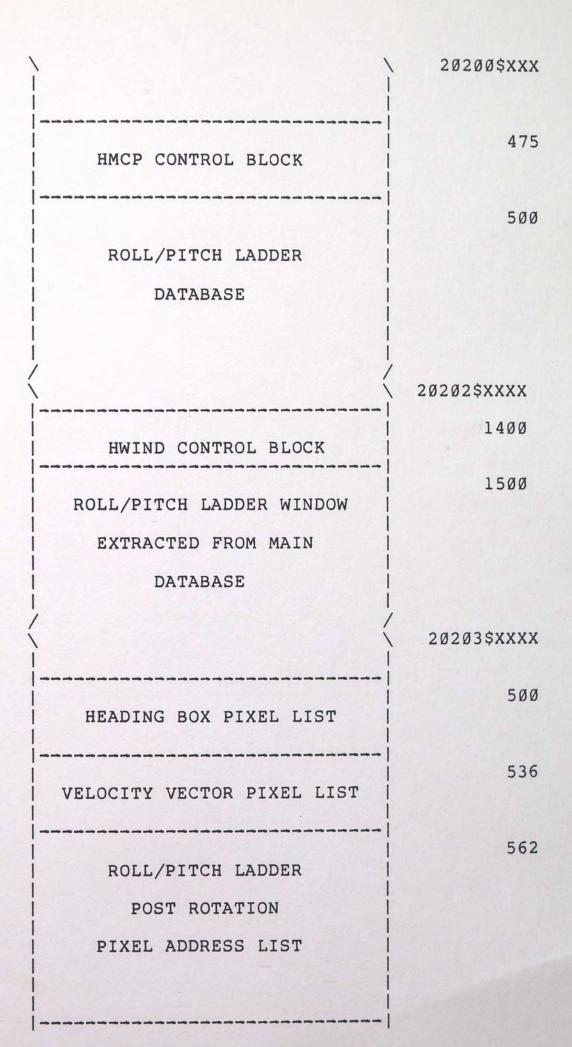

The BMP32 processor is used as the main module and controls access to the bus. A memory map of the BMP32 microcode memory is shown in Figure 17. At location address Ø in microcode memory is HMCP.MOB. This is the HUD Master Control Program (Appendix A). All of the other microprograms are controlled from this sequence of microcode. Location 100 is the start of the line display routine called BRESLL.MOB. This program plots lines from designated origination and termination points. The microcode located at address 500 is HWIND.MOB. This creates a window in the Roll/Pitch Ladder database to be extracted, the HUD rotated by the roll angle, and displayed to The CGMS.MOB microcode starts at projection system. and allows up to eight characters to be location 600 generated as a string, by the Character Generator.

The MA1024 has one microcode program located at address 0 in the matrix multiplier microcode memory. This program,

FIGURE 17: BMP32 Microcode Memory Map

given a coefficient matrix and data address, will rotate a given three-dimensional object.

These microprograms as well as control and status information from the Host Control Program (HCP), display the flight information transferred to it in the form of the Head-Up Display.

### 3.1 MASTER CONTROL PROGRAM (HMCP)

The HMCP microcode was developed as the main module in the Ikonas Processor, which calls the other microcode modules and controls status and bus lines. Figure 18 is a flow diagram of the HMCP program. The processor is started by the Host Control Program when the is processor syncrhonized with the display field (Chapter IV). A listing of the microcode intructions for this program is presented Appendix A-1. The flow diagram shows each subprogram as in they are initiated starting with the Roll/Pitch Ladder window program HWIND. After HWIND has returned completed, the window which was just extracted must have the terminator bits placed in the last word of the buffer. The termination This is byte of "177777 is written in the last location. used by MMEOL to determine where the end of the data is detected. Next the control block address for the MA1024 is loaded This starts the MA1024 processor by and sent. loading the first microcode instruction located at address Ø

FIGURE 18: HMCP Flow Diagram

in MA1024 microcode memory (MMEOL). HMCP then waits for the condition code CCMAAC to go high which indicates the rotation is completed. Once the rotation has finished and new points are placed in the Output Buffer, the the terminating word must again be placed at the end of the buffer. BRESL1 also detects the end of data by the same terminator bits. The next step is to output the character strings required for the HUD flight information displays. is the microcode which sets up and executes the CGMS Character Generator Module and displays character strings of up to eight characters in length. When this is completed HMCP calls BRESLI, which takes the points from the Ikonas Output Buffer and draws the appropriate lines to the This process is repeated until the Ikonas display. processor is reset to zero and the microcode begins again on the next field.

### 3.2 ROLL/PITCH LADDER WINDOW (HWIND)

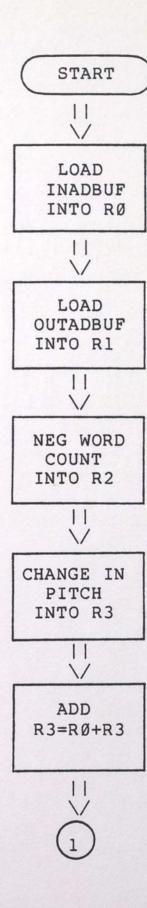

The HWIND microcode routine is used to extract points to be the Roll/Pitch Ladder database, which are from of displayed on the HUD. Figure 20 shows a flow diagram HWIND and the microcode is presented as Appendix A-2. This routine starts by inputting the window control block and bit working the BPS32 processor's 32 loading it into registers. Starting with RØ the following information is

FIGURE 19: HWIND Flow Diagram

read from the HWIND control block located in SR8 scratch memory.

RØ - Address of input buffer

R1 - Address of output buffer

R2 - Negative word count of window points

R3 - Pitch offset within database

From this control data, which is determined and sent by the Program, the correct pitch attitude Control Host is extracted from the remainder of the database. This smaller subset is now ready to receive the roll rotation, before being output. The beginning of the window is determined by adding the input buffer address (RØ), with the calculated pitch attitude (R3). This gives the address of the first point to be extracted and placed in the Memory Address Register (MAR) and the data at that address to be written to 1, and the contents of MDR is output to that Register location. Each of the input and ouput addresses are then incremented to prepare for the transfer of another data point. The negative word count (R2), gives the size which This register is incremented after the window is to be. This indicates that the each cycle until it overflows. entire window has been transferred and contol returns to HMCP.

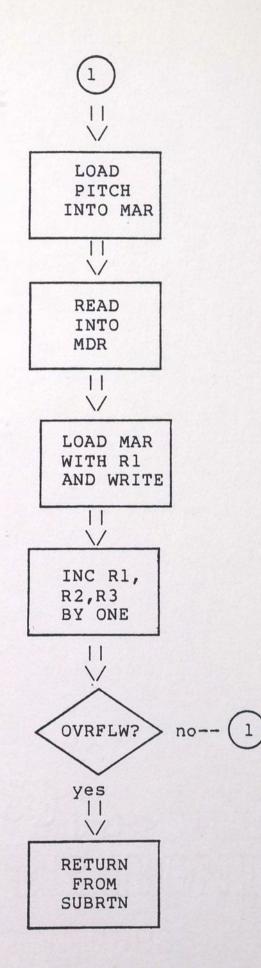

# 3.3 CHARACTER GENERATOR MODULE (CGMS)

The Character Generator can be intialized and controlled in several manners. Control from the Ikonas

processor was determined to be the most straightforward and economical method. The standard on board font table is used by the character generator to produce characters which are displayed with 5X7 pixel dimensions. CGMS is a microprogram loaded in the BMP32 processor, which starts and controls the characters being produced. A listing of this microprogram is given in Appendix A-3. This microcode is a modified version of the original character generator control program CGMMCR.MOB (Sampayo 1982). Figure 20 is a flow diagram of microcode routine. The program starts by loading the CGMS the CGMS Control Block from the SR8 working memory, into the BPS32 processor's 32 bit registers. The descriptions of each control word and their locations in memory are given in flow diagram. A working buffer in SR8 memory of three the Ikonas 32 bit words is set aside and cleared for use by the The program then fetches the first character generator. which the character string is to be pixel address in Then the appropriate character string is placed displayed. into the working buffer.

The Character Generator is started by first sending the address of the Character Generator control block to location 20600\$1, and then sending the correct startup and control bits to location 20600\$0. While the character string is being output, the processor increments the pixel address and character string pointers and checks for an ALU overflow, which indicates the last string is presently being output.

FIGURE 20: CGMS Flow Diagram

If an overflow does not occur the program begins processing the next character string. Once complete, control returns to the Hud Master Control Program (HMCP).

#### 3.4 MATRIX MULTIPLY (MMEOL)

The Matrix Multiply routine is a system subroutine which is supplied by Ikonas Graphics Inc (1982). MMEOL is stored in the MA1024 microcode memory and starts up when the MA1024 processor is activated. This microcode routine will utilize MA1024 coefficient memory for multiplication of the data points with the coefficient matrix. The coefficient matrix is calculated and sent to the MA1024 by the Host Computer after each frame occurs. The Roll/Pitch Ladder points database is located in SR8 memory. After the HWIND microcode program extracts the active database segment, MMEOL will input the first point to be rotated. Once the matrix multiplication is complete, MMEOL will output the transformed point to an output buffer in SR8 memory, and increments the address pointer for the next point to be rotated. The end of the data base segment is detected by using flag bits. The last word of the each point MMEOL In the case of indicates the type of action to be done. MMEOL, if bits 30 and 31 are high, it indicates the end of points to be rotated.

### 3.5 LINE DRAWING (BRESL1)

The Line Drawing Routine is also a microcode subroutine supplied by Ikonas, and it resides in the BPS32 microcode memory. This microcode is called when it is required to draw lines between points on the diplay. BRESL1 inputs points from SR8 memory, calculates the slope between two points, and generates a line segment on the display. This program also uses flag bits to determine the type of point which is input. Bits 30 and 31 of the last word representing a point, are used as indicators. Figure 21 shows a truth table of the different flag bit settings.

| BI | TS |   |       |                                         |

|----|----|---|-------|-----------------------------------------|

| 31 | 3Ø | 1 |       | ACTION                                  |

|    |    |   |       |                                         |

| Ø  | Ø  |   | MOVE  | TO POINT                                |

| 1  | ø  | 1 | DRAW  | LINE TO POINT                           |

| 1  | 1  | 1 | LAST  | POINT, DRAW TO                          |

| Ø  | 1  | 1 | XXXXX | XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX |

|    |    |   |       |                                         |

#### FIGURE 21: BRESL1 Flag Bits

If a 00 is sent, this represents a starting point for BRESL1 to move to before drawing a line. A 10 indicates a line is to be drawn to that point from the previous point. And a 11 represents the last point to be drawn to and the end of the input buffer.

# CHAPTER IV

## HOST PROGRAMMING

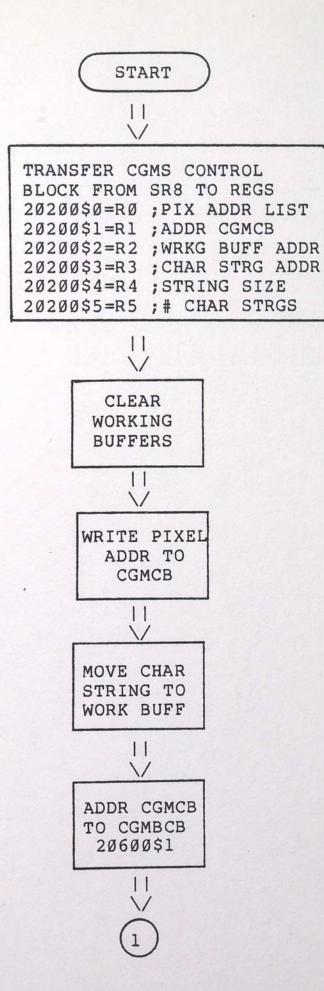

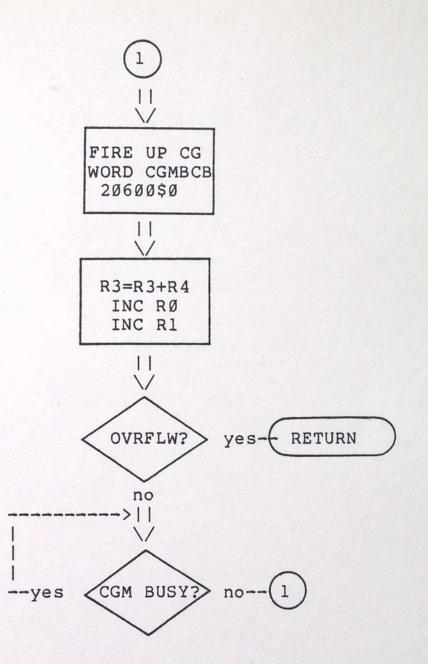

The Host Control Program is written using PDP-11 Fortran IV-plus and executes the initialization, startup and update in a realtime environment. Figure 22 is a flow diagram of the Host Control Program (HCP.FTN), and a listing of this program appears in Appendix B. The first step in is to obtain the physical addresses of the input and HCP output data arrays. A detailed description of this calculation is given in the documentation of the HCP program listings. This procedure is the step which allows the host programming to be accomplished using Fortran. By obtaining the virtual address of an array, it can be accessed and transferred by the DR11B interface, using Fortran statements. There are two DR11B interfaces used in the HUD/Ikonas applications. The control variables are linked The to the Host Control Program as common memory locations. Option function is used during task building, to allow common virtual memory locations, between the program and the interfaces. The command lines are used to initialize DR11B

FIGURE 22: Host Control Program (HCP) Flow Diagram

the virtual memory address which are used in the Host Control Program.

>LINK/CODE: FPP/PRIVILEGED: 4/OPTIONS HCP

OPTION?

VSECT=PAGADF:172350:2:1

OPTION?

VSECT=IFDR11:172450:10:1

OPTION?

VSECT=IKDR11:172460:16:1

The COMMON statement is used in the program to identify the interface control locations with program variable names.

COMMON/IFDR11/IFDRWC, IFDRBA, IFDRDR

COMMON/IKDR11/IKDRWC,IKDRBA,IKDRCS,IKDRDR, \*IKSLAD,IKSHAD,IKSCSR

The IFDR11 us used as a label for the SEL-PDP-11 DR11B interface, and the IKDR11 represents the PDP-11-IKONAS DR11B interface.

To determine the actual physical address of the input and output buffers, a link between the program and the Page Address Field (PAF) in the PAR register, must be made.

COMMON/PAGADF/PAF

A system subroutine called GETADR is used to obtain the virtual address of each buffer and place them in an array called VIRTAD.

CALL GETADR (VIRTAD, INIBUF(1), INNBUF(1), OUTBUF(1))

Once this is accomplished the physical address can be found using VIRTAD and the PAF.

The Ikonas reset and initialization steps utilize the buffers set up for the DR11B interface. The following is a list of the Ikonas DR11B interface variables and their function. Using these variables, information can be transferred to the Ikonas system through the DR11B interface.

| 1. | IKSLAD | - | LOW 16 BITS OF IKONAS MEMORY ADDRESS  |

|----|--------|---|---------------------------------------|

| 2. | IKSHAD | - | HIGH 16 BITS OF IKONAS MEMORY ADDRESS |

| 3. | IKSCSR | - | IKONAS FUNCTION CODE REGISTER         |

| 4. | IKDRDR | - | SINGLE TRANSFER REGISTER              |

| 5. | IKDRWC | - | IKONAS BLOCK TRANSFER NEG WORD COUNT  |

| 6. | IKDRBA | - | BLOCK TRANSFER INPUT ADDRESS          |

| 7. | IKDRCS | - | DR11B STATUS CONTROL REGISTER         |

The Ikonas interface is reset by first setting the Ikonas function code line and then clearing it. The processor is set up to allow automatic erase, by sending the proper status bits to Ikonas location 30000\$5. With this capability, the screen will automatically erase at each field to prepare to the drawing of the next field. This requires that every object on the display be generated at each 30Hz field interval.

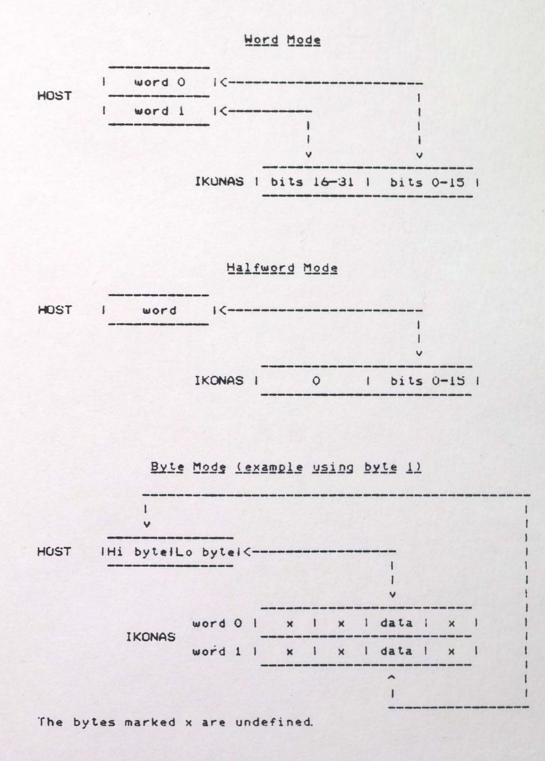

The Host Control Program allows for user input from the system terminal, to determine the position of display features, select input database, and choose a scaling factor increase or decrease the size of the display. Detailed to descriptions of these options and their uses are qiven in Users Guide. The database is read into a scratch the HUD array and immediately transferred to Ikonas SR8 memory. A Memory Map of the Ikonas SR8 memory for the HUD application is shown in Figure 23. The database starts at Ikonas memory location 20200\$500, and can consume up to "2700 Ikonas 32 bit words in SR8 memory. Each data point of the database is represented by 2 Ikonas words, therefore approximately 750 points can be stored. Appendix C gives detailed descriptions of data types and formats necessary.

Once the database is input, HCP begins the inialization phase of the program. The Inialization Buffer INIBUF is created, containing control block and address information. first block of data is the CGMS control block, which is The responsible for the addresses of a11 the other control used by the Character Generator module to initialize blocks and execute. The character string pixel address list is placed at the end of the intialization buffer to be used by the generator when outputting character string data. INIBUF sent to the Ikonas SR8 memory, using a block is then Setting up the character transfer, to location 20200\$0. buffer is done for error-debugging purposes. If an output

|                                                                                                                          | LOCATION         |

|--------------------------------------------------------------------------------------------------------------------------|------------------|

| POINTER TO PIXEL ADDRES LIST                                                                                             | 20200\$ X<br>Ø   |

| PTR CGMCB PIXEL ADDRESS LIST                                                                                             | 1                |

| POINTER TO WORKING BUFFER                                                                                                | 2                |

| PTR TO CHARACTR STRINGS LIST                                                                                             | 3                |

| SIZE OF STRINGS, IKONAS WORD                                                                                             | 4                |

| NO. CHAR IN STRINGS LIST 2'S                                                                                             | 5                |

| CGMBCB STARTUP CONTROL WORD                                                                                              | 6                |

| SR8 ADDRESS OF CGMCB                                                                                                     | 7                |

| CGMCB CONTROL BLOCK                                                                                                      | 10               |

| STARTING PIXEL ADDRESS<br>CHAR STRINGS LIST ADDR<br>CHARACTER STRINGS PIXEL<br>ADDRESS LIST<br>CHARACTER STRINGS<br>LIST | <b>1</b> 5<br>бØ |

FIGURE 23: IKONAS SR8 MEMORY MAP

error occurs the character output can be traced, without requiring communication with the simulator computers. The SIZE buffer is used to set character string lengths for each output.

Pixel addresses for the three indicator boxes displayed on the HUD are generated and output to Ikonas SR8 memory, starting at location 20203\$500. This is the beginning address of the Ikonas display data output buffer, which is used by the line drawing microcode routine BRESL1 and output to the HUD display.

The next step is preparing to enter the realtime module, by setting up control data and sending all information to the Ikonas which does not have to be updated every field. Here the control block for HMCP microcode is sent to SR8 memory starting at location 20200\$470.

The first step in the realtime module is to receive the dynamic data input buffer from the Systems Engineering Laboratories simulator computers. This is accomplished in the same manner as the Ikonas Interface transfers, with the exception that only read attributes are required. No handshaking communications are necessary for a High Speed Data (HSD) transfer, thus only inputs are required. The IFDR11 is LINKED to the Host Program and the following control variables may be used for transfer of the 256 byte input buffer INNBUF from the SEL to the PDP-11 Host computer.

| 1. | <b>TEDRAC</b> | <br>SEL | BLOCK | TRANSFER | NEG | WORD | COUNT |  |

|----|---------------|---------|-------|----------|-----|------|-------|--|

|    |               |         |       |          |     |      |       |  |

- 2. IFDRBA SEL BLOCK TRANSFER BUFFER ADDRESS

- 3. IFDRCS SEL/DR11B FUNCTION CODE REGISTER

- 4. IFDRDR SINGLE WORD TRANSFER REGISTER