Retrospective Theses and Dissertations

2001

# Gate and Throughput Optimizations for NULL Convention Selftimed Digital Circuits

Scott Christopher Smith

University of Central Florida, smithsco@uark.edu

Find similar works at: https://stars.library.ucf.edu/rtd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Retrospective Theses and Dissertations by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS Citation**

Smith, Scott Christopher, "Gate and Throughput Optimizations for NULL Convention Self-timed Digital Circuits" (2001). *Retrospective Theses and Dissertations*. 1359. https://stars.library.ucf.edu/rtd/1359

# GATE AND THROUGHPUT OPTIMIZATIONS FOR NULL CONVENTION SELF-TIMED DIGITAL CIRCUITS

By Scott Christopher Smith

2001

UCF

# GATE AND THROUGHPUT OPTIMIZATIONS FOR NULL CONVENTION SELF-TIMED DIGITAL CIRCUITS

by

#### Scott Christopher Smith

MSEE, University of Missouri-Columbia, 1998 BSEE, University of Missouri-Columbia, 1996 BSCompE, University of Missouri-Columbia, 1996

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Engineering in the field of Computer Architecture and Digital Systems in the School of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida

Orlando, Florida

Spring Term 2001

Major Professor: Dr. Ronald DeMara

#### **ABSTRACT**

NULL Convention Logic (NCL) provides an asynchronous design methodology employing dual-rail signals, quad-rail signals, or other Mutually Exclusive Assertion Groups (MEAGs) to incorporate data and control information into one mixed path. In NCL, the control is inherently present with each datum, so there is no need for worse-case delay analysis and control path delay matching. This dissertation focuses on optimization methods for NCL circuits, specifically addressing three related architectural areas of NCL design.

First, a design method for optimizing NCL circuits is developed. The method utilizes conventional Boolean minimization followed by table-driven gate substitutions. It is applied to design time and space optimal fundamental logic functions, a time and space optimal full adder, and time, transistor count, and power optimal up-counter circuits. The method is applicable when composing logic functions where each gate is a state-holding element; and can produce delay-insensitive circuits requiring less area and fewer gate delays than alternative gate-level approaches requiring full minterm generation.

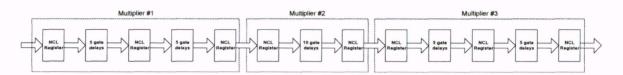

Second, a pipelining method for producing throughput optimal NCL systems is developed. A relationship between the number of gate delays per stage and the worse-case throughput for a pipeline as a whole is derived. The method then uses this relationship to minimize a pipeline's worse-case throughput by partitioning the NCL

combinational circuitry through the addition of asynchronous registers. The method is applied to design a maximum throughput unsigned multiplier, which yields a speedup of 2.25 over the non-pipelined version, while maintaining delay-insensitivity.

Third, a technique to mitigate the impact of the NULL cycle is developed. The technique further increases the maximum attainable throughput of a NCL system by reducing inherent overheads associated with an integrated data and control path. This technique is applied to a non-pipelined 4-bit by 4-bit unsigned multiplier to yield a speedup of 1.61 over the standalone version.

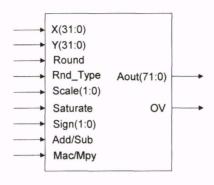

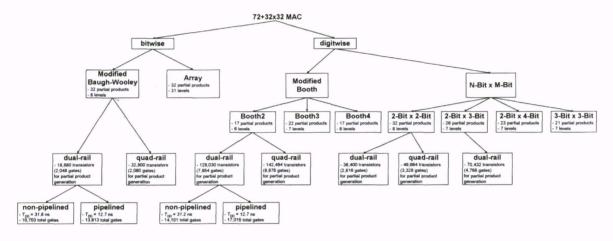

Finally, these techniques are applied to design a 72+32×32 multiply and accumulate (MAC) unit, which outperforms other delay-insensitive/self-timed MACs in the literature. It also performs conditional rounding, scaling, and saturation of the output, whereas the others do not; thus further distinguishing it from the previous work. The methods developed facilitate speed, transistor count, and power tradeoffs using approaches that are readily automatable.

#### **ACKNOWLEDGEMENTS**

I would like to thank Theseus Logic, Inc. for their financial support and the opportunity to work with such novel and exciting technology. I would like to thank Dr. DeMara for his technical and editorial advice that has helped shape this work. I would like to thank the committee members who have taken the time to review and comment on this dissertation. I would also like to thank the state of Florida for the fellowships provided that have allowed me the opportunity to pursue this degree. But most of all I would like to thank my loving wife Tamara, for her patience and support in my continued education.

### TABLE OF CONTENTS

| LIST OF TAI | BLESx                                             |

|-------------|---------------------------------------------------|

| LIST OF FIG | URES xi                                           |

| CHAPTER 1.  | INTRODUCTION                                      |

| 1.1. O      | bjective1                                         |

| 1.2. H      | istory and Benefits of NCL1                       |

| 1.3. R      | esearch Challenges5                               |

| 1.4. D      | issertation Overview6                             |

| CHAPTER 2.  | PREVIOUS WORK8                                    |

| 2.1. O      | verview of Asynchronous Methods9                  |

|             | 2.1.1. Gate-Level Delay-Insensitive Methods       |

|             | 2.1.2. Transistor-Level Delay-Insensitive Methods |

| 2.2. O      | verview of NCL12                                  |

|             | 2.2.1. Delay-Insensitivity                        |

|             | 2.2.2. Logic Gates and Functional Blocks          |

|             | 2.2.3. Completeness of Input                      |

|             | 2.2.4. Observability                              |

|             | 2.2.5. NCL Registration                           |

|             | 2.2.6. NCL Completion                             |

| CHA  | PTER 3. THRESHOLD COMBINATIONAL REDUCTION METHOD               | 31 |

|------|----------------------------------------------------------------|----|

|      | 3.1. Chapter Outline                                           | 32 |

|      | 3.2. TCR Method Definition                                     | 32 |

|      | 3.2.1. Method 1: Incomplete Functions                          | 34 |

|      | 3.2.2. Method 2: Dual-Rail Optimizations                       | 34 |

|      | 3.2.3. Method 3: Quad-Rail Optimizations                       | 36 |

|      | 3.2.4. Performance Assessment                                  | 37 |

|      | 3.3. Application to Input-Complete Fundamental Logic Functions | 38 |

|      | 3.4. Application to Full Adder                                 | 40 |

|      | 3.5. Application to Up-Counter                                 | 47 |

|      | 3.5.1. Method 1: Incomplete Functions                          | 51 |

|      | 3.5.2. Method 2: Dual-Rail Encoding Optimizations              | 53 |

|      | 3.5.3. Method 3: Quad-Rail Encoding Optimizations              | 57 |

|      | 3.5.4. Other MEAG Optimizations                                | 61 |

|      | 3.5.5. Up-Counter Performance Summary                          | 64 |

| CHAI | PTER 4. GATE-LEVEL PIPELINING OPTIMIZATIONS                    | 66 |

|      | 4.1. Chapter Outline                                           | 67 |

|      | 4.2. Previous Work                                             | 67 |

|      | 4.2.1. Relation of NCL to Previous Work                        | 70 |

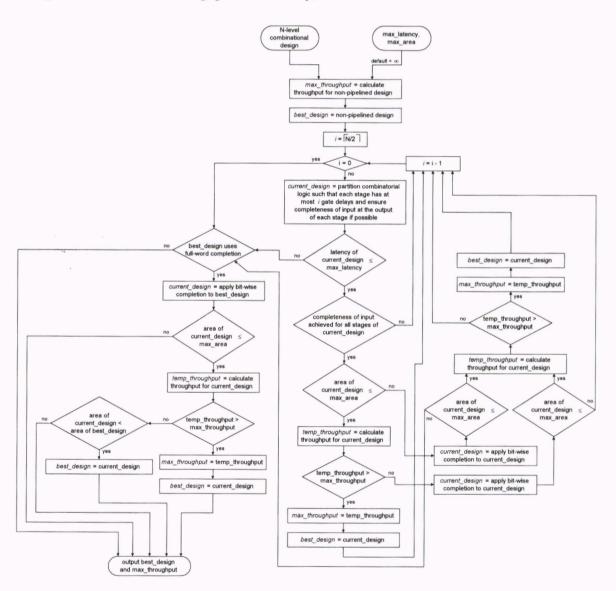

|      | 4.3. Method Definition                                         | 72 |

|      | 4.3.1. Throughput Derivation                                   | 75 |

|      | 4.3.1.1 Idealized Completion Circuitry                         | 77 |

| 4.3.1.2. Non-Zero Delay Completion Circuitry                 | 79    |

|--------------------------------------------------------------|-------|

| 4.3.2. Bit-Wise Completion                                   | 82    |

| 4.4. Application to Unsigned Multiplier                      | 85    |

| 4.4.1. Pipelined Multipliers with Full-Word Completion       | 87    |

| 4.4.2. Summary of Multiplier Designs using Full-Word Complet | ion93 |

| 4.4.3. Applying Bit-Wise Completion                          | 93    |

| 4.5. Conclusion                                              | 94    |

| CHAPTER 5. NULL CYCLE REDUCTION TECHNIQUE                    | 96    |

| 5.1. Introduction                                            | 96    |

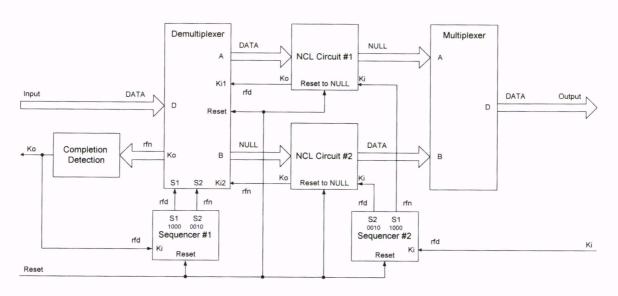

| 5.2. NULL Cycle Reduction                                    | 97    |

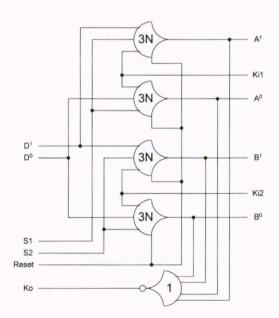

| 5.2.1. Demultiplexer                                         | 99    |

| 5.2.2. Completion Detection Circuitry                        | 100   |

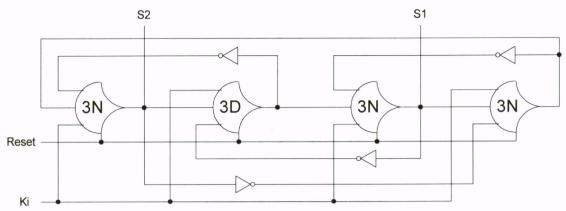

| 5.2.3. Sequencer #1                                          | 100   |

| 5.2.4. Multiplexer                                           | 101   |

| 5.2.5. Sequencer #2                                          | 102   |

| 5.3. Simulation Results                                      | 103   |

| CHAPTER 6. NCL MULTIPLY AND ACCUMULATE UNIT                  | 106   |

| 6.1. Introduction                                            | 107   |

| 6.2. Previous Work                                           | 108   |

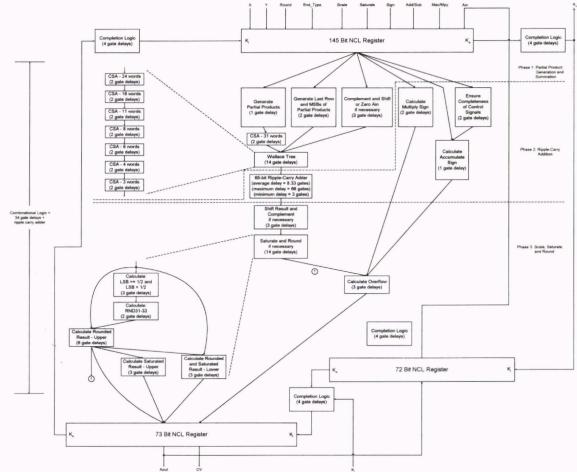

| 6.3. Self-Timed MAC Design Methods                           | 109   |

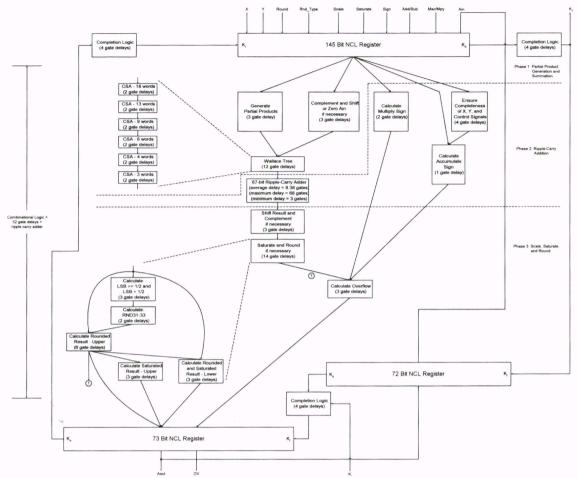

| 6.3.1. Non-Pipelined Modified Baugh-Wooley MAC               | 111   |

| 6311 Operation                                               | 111   |

| 6.3.1.2. Design Optimizations               | 115 |

|---------------------------------------------|-----|

| 6.3.1.3. Average Cycle Time Determination   | 117 |

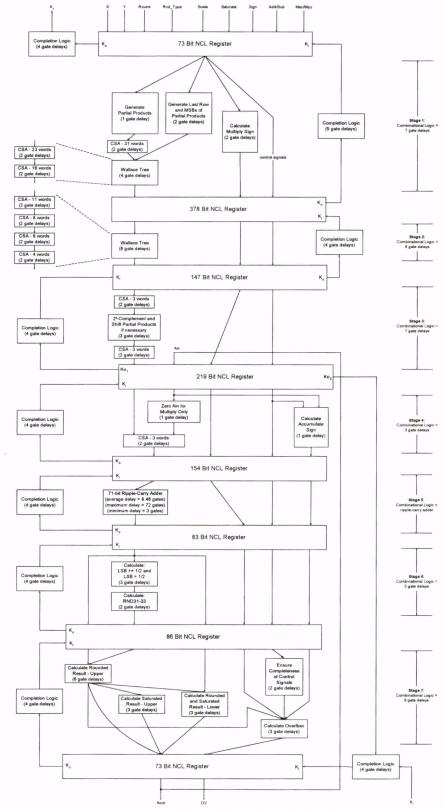

| 6.3.2. Non-Pipelined Modified Booth2 MAC    | 118 |

| 6.3.2.1. Operation                          | 118 |

| 6.3.2.2. Design Optimizations               | 120 |

| 6.3.2.3. Average Cycle Time Determination   | 120 |

| 6.3.3. Pipelined Modified Baugh-Wooley MAC  | 120 |

| 6.3.3.1. Operation                          | 120 |

| 6.3.3.2. Throughput Maximization            | 122 |

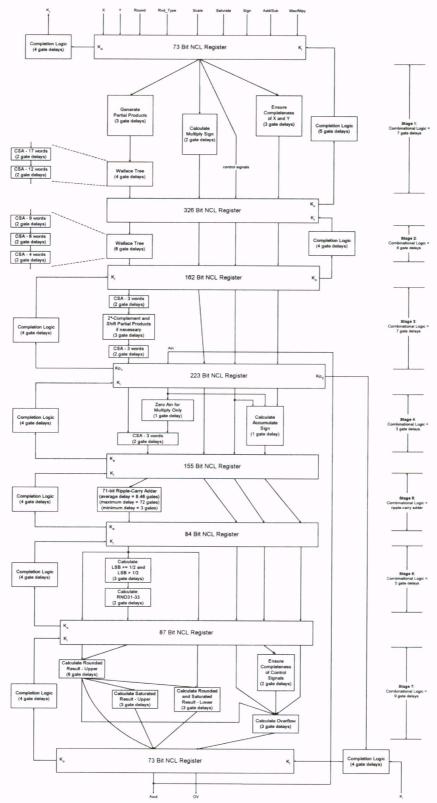

| 6.3.4. Pipelined Modified Booth2 MAC        | 126 |

| 6.3.4.1. Operation                          | 126 |

| 6.3.4.2. Throughput Maximization            | 128 |

| 6.3.5. Simulation Results                   | 128 |

| 6.4. Carry-Propagate Adder Comparison       | 129 |

| 6.5. Gate Requirements for Proposed Designs | 132 |

| 6.5.1. Modified Baugh-Wooley MAC            | 133 |

| 6.5.2. Modified Booth2 MAC                  | 133 |

| 6.5.3. Array MAC                            | 134 |

| 6.5.4. Modified Booth3 MAC                  | 135 |

| 6.5.5. Modified Booth4 MAC                  | 136 |

| 6.5.6. Combinational 2-Bit × 2-Bit MAC      | 137 |

| 6.5.7. Combinational 2-Bit × 3-Bit MAC      | 138 |

|              | 6.5.8. Combinational 2-Bit × 4-Bit MAC | 139  |

|--------------|----------------------------------------|------|

|              | 6.5.9. Combinational 3-Bit × 3-Bit MAC | 140  |

|              | 6.5.10. Quad-Rail MACs                 | 142  |

| 6.6. Co      | nclusion                               | 142  |

| CHAPTER 7.   | Conclusion                             | 145  |

| 7.1. Sur     | mmary                                  | .145 |

| 7.2. Fut     | ture Work                              | .147 |

| LIST OF REFI | ERENCES                                | .150 |

# LIST OF TABLES

| I.    | Attributes of clocked Boolean and asynchronous methods3                     |

|-------|-----------------------------------------------------------------------------|

| II.   | Attributes of self-timed methods                                            |

| III.  | 27 NCL macros                                                               |

| IV.   | Performance characteristics of input-complete NCL logic functions40         |

| V.    | Full adder using various delay-insensitive methods                          |

| VI.   | Delay-insensitive methods for $f(a, b, c, d) = a \cdot b' \cdot c \cdot d'$ |

| VII.  | Alternate designs for NCL up-counter increment circuit65                    |

| VIII. | Discrete timing chart for the idealized NCL cycle                           |

| IX.   | Discrete timing chart for the general NCL cycle80                           |

| X.    | Stage delay and throughput for various multiplier designs                   |

| XI.   | Sequencer output 101                                                        |

| XII.  | NCR vs. pipelining for multiplier application                               |

| XIII. | Saturation table                                                            |

| XIV.  | Propagation delay and gate count for 4-bit adders                           |

| XV.   | Algorithm, technology, and cycle time for various self-timed MACs144        |

# LIST OF FIGURES

| 1.  | Symbolic incompleteness of a Boolean AND gate13                                       |

|-----|---------------------------------------------------------------------------------------|

| 2.  | NCL AND function: $Z = X \bullet Y$ and associated waveforms                          |

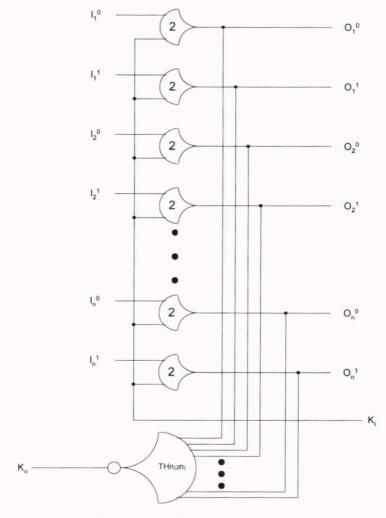

| 3.  | THmn threshold gate                                                                   |

| 4.  | Static CMOS implementation of a TH23 gate                                             |

| 5.  | NULL flowing through combinational circuitry                                          |

| 6.  | Completion detection of NULL output                                                   |

| 7.  | DATA flowing through combinational circuitry                                          |

| 8.  | Completion detection of DATA output                                                   |

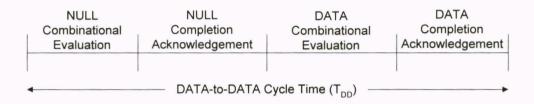

| 9.  | DATA-to-DATA cycle time (T <sub>DD</sub> )20                                          |

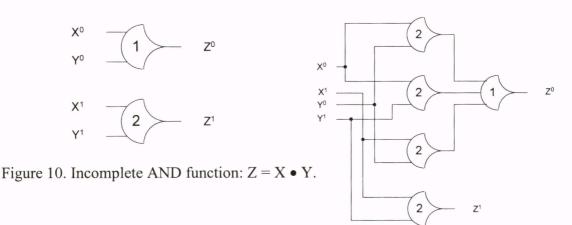

| 10. | Incomplete AND function: $Z = X \bullet Y$                                            |

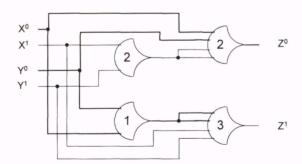

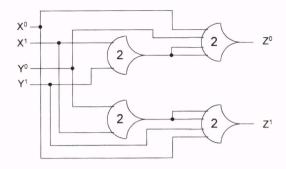

| 11. | Conventional input-complete AND function: $Z = X \bullet Y$                           |

| 12. | Incorrect XOR function: $Z = X \oplus Y$ (orphans may propagate through a gate)22     |

| 13. | Correct XOR function: $Z = X \oplus Y$ (orphans may not propagate through any gate)23 |

| 14. | n-bit dual-rail registration                                                          |

| 15. | Initial register state                                                                |

| 16. | Register state after traversing combinational circuitry                               |

| 17. | Register state after NULL wavefront passes through downstream register27              |

| 18. Register state after DATA wavefront passes through current register  | 27 |

|--------------------------------------------------------------------------|----|

| 19. Register state after NULL wavefront passes through upstream register | 28 |

| 20. Static register state                                                | 28 |

| 21. Single-bit dual-rail register                                        | 29 |

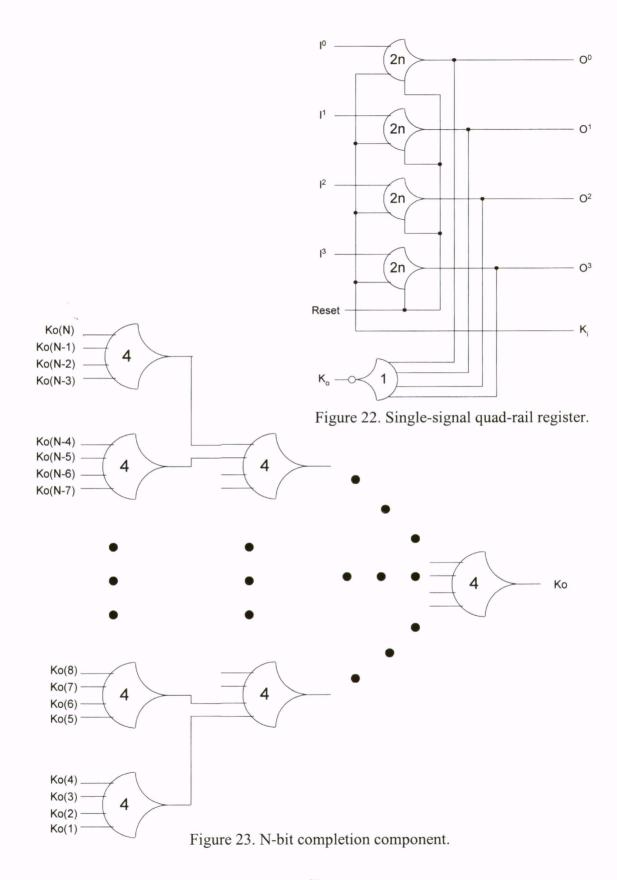

| 22. Single-signal quad-rail register                                     | 30 |

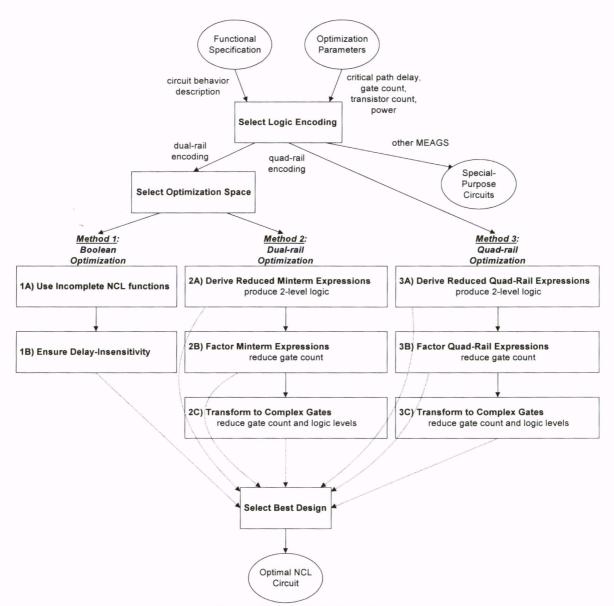

| 23. N-bit completion component                                           | 30 |

| 24. TCR design flow                                                      | 33 |

| 25. Conventional input-complete OR function: $Z = X + Y$                 | 39 |

| 26. Conventional input-complete XOR function: $Z = X \oplus Y$           | 39 |

| 27. Truth table for full adder                                           | 41 |

| 28. K-map for $C_o$ output of full adder                                 | 41 |

| 29. K-map for S output of full adder                                     | 41 |

| 30. Optimized NCL full adder                                             | 41 |

| 31. Full adder using Anantharaman's approach or DIMS                     | 43 |

| 32. Full adder using Seitz's approach                                    | 44 |

| 33. Full adder using David's approach                                    | 45 |

| 34. Full adder using Singh's approach                                    | 46 |

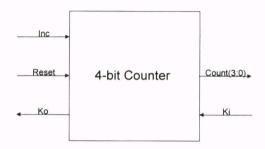

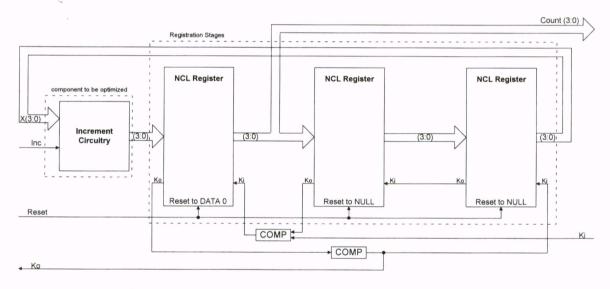

| 35. 4-bit up-counter block diagram                                       | 48 |

| 36. Up-counter with three-register feedback                              | 48 |

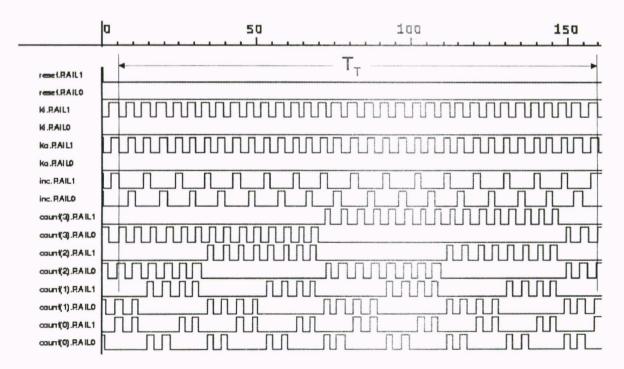

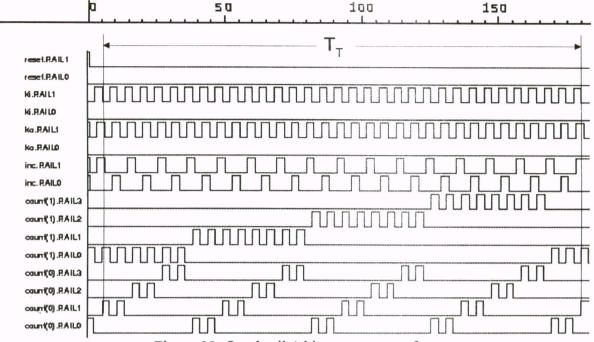

| 37. Dual-rail 4-bit counter waveforms                                    | 49 |

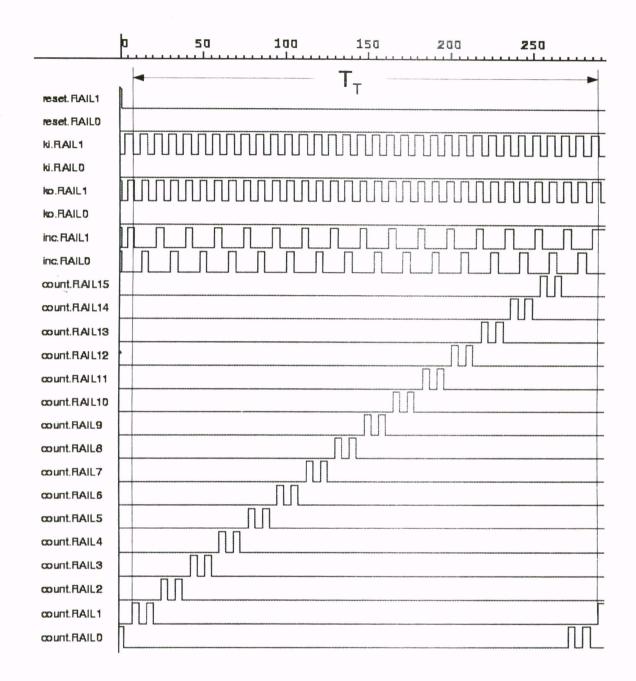

| 38. 16-rail MEAG 4-bit counter waveforms                                 | 50 |

| 39. Quad-rail 4-bit counter waveforms                                    | 51 |

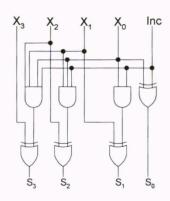

| 40. Boolean increment circuit                                        | 52 |

|----------------------------------------------------------------------|----|

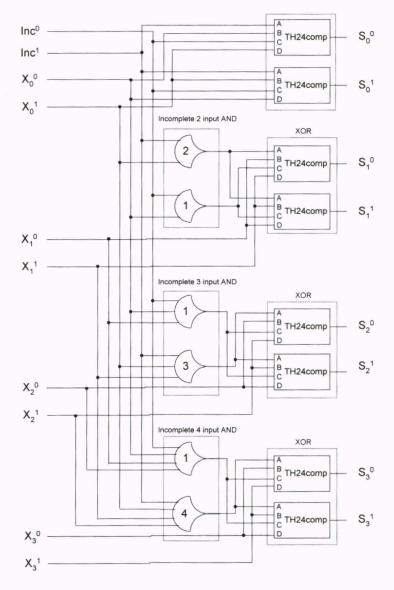

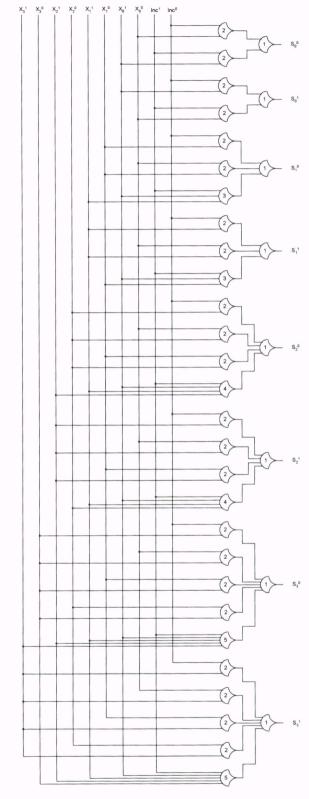

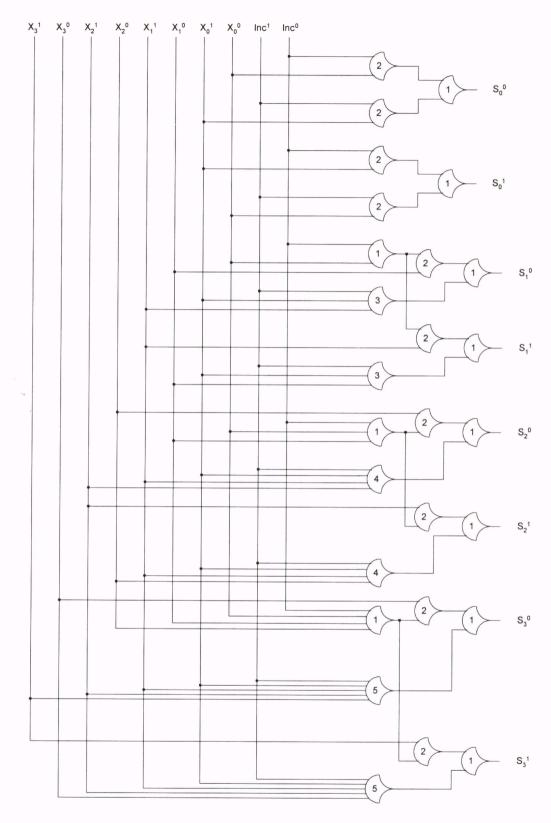

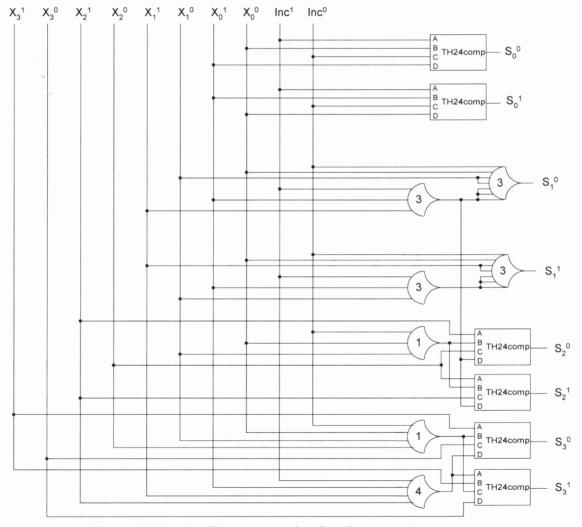

| 41. Increment circuit using incomplete AND functions                 | 52 |

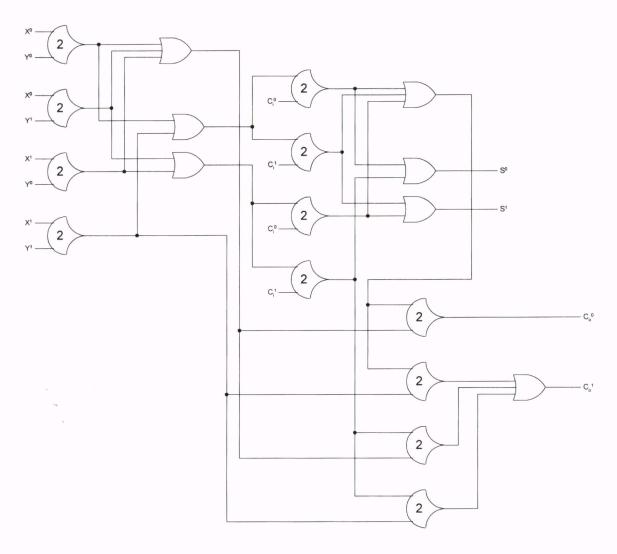

| 42. Increment circuit using dual-rail reduced minterm expressions    | 54 |

| 43. Increment circuit using dual-rail factored minterm expressions   | 55 |

| 44. Dual-rail increment circuit using complex gates                  | 56 |

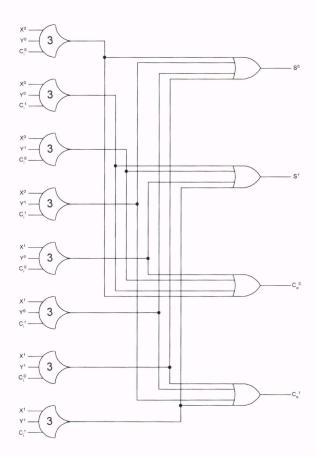

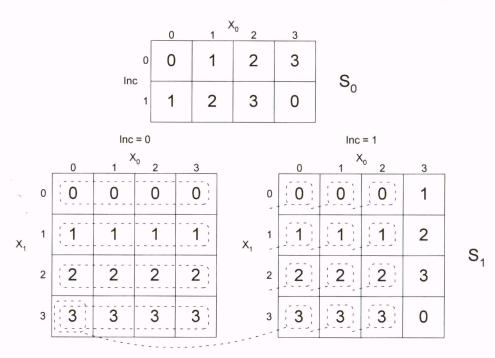

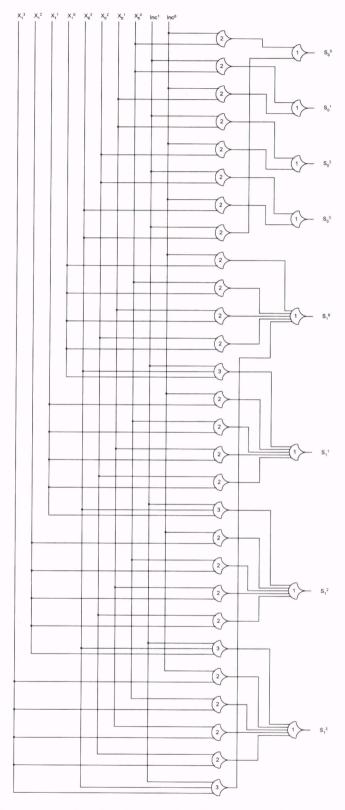

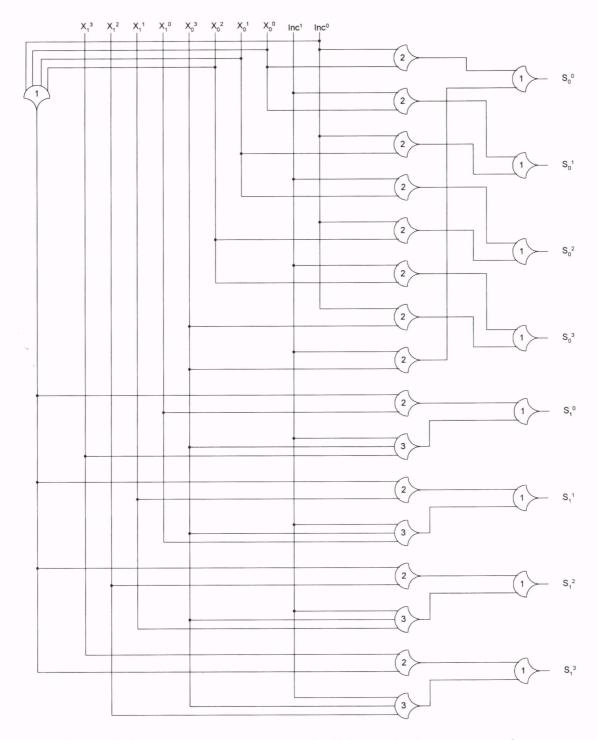

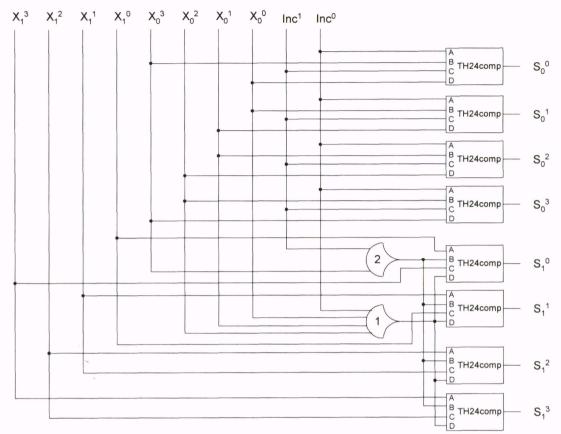

| 45. Karnaugh maps for quad-rail counter                              | 57 |

| 46. Increment circuit using quad-rail reduced minterm expressions    | 58 |

| 47. Increment circuit using quad-rail factored minterm expressions   | 60 |

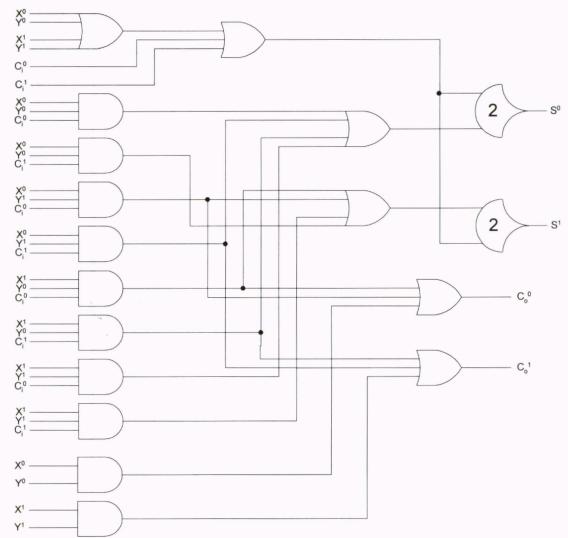

| 48. Quad-rail increment circuit using complex gates                  | 61 |

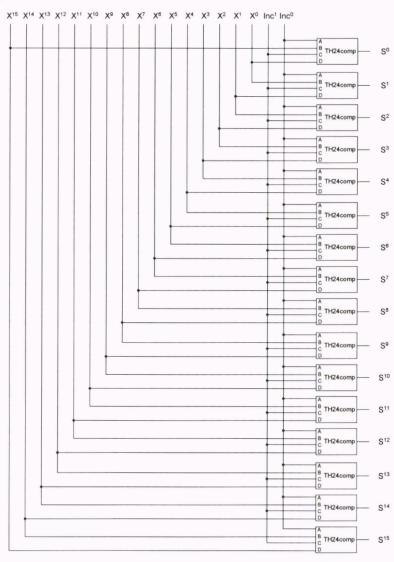

| 49. 16-rail MEAG increment circuit.                                  | 62 |

| 50. 16-rail MEAG register                                            | 63 |

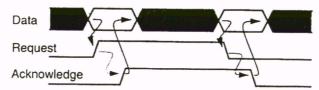

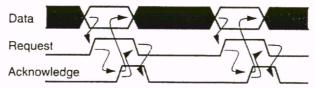

| 51. Two-phase handshaking protocol                                   | 69 |

| 52. Four-phase handshaking protocol                                  | 69 |

| 53. GLP design flow                                                  | 73 |

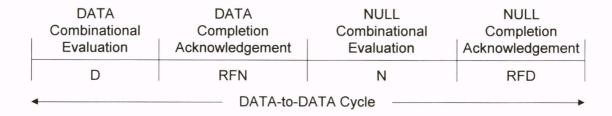

| 54. Sub-cycles of the NCL cycle                                      | 76 |

| 55. Pipeline showing NCL sub-cycle times                             | 76 |

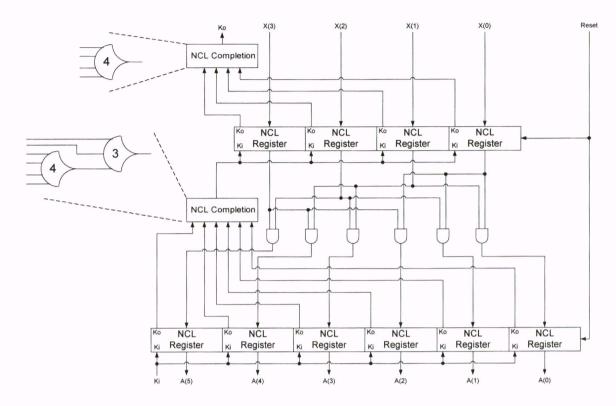

| 56. Full-word completion                                             | 84 |

| 57. Bit-wise completion                                              | 84 |

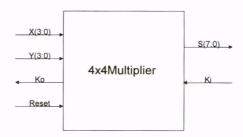

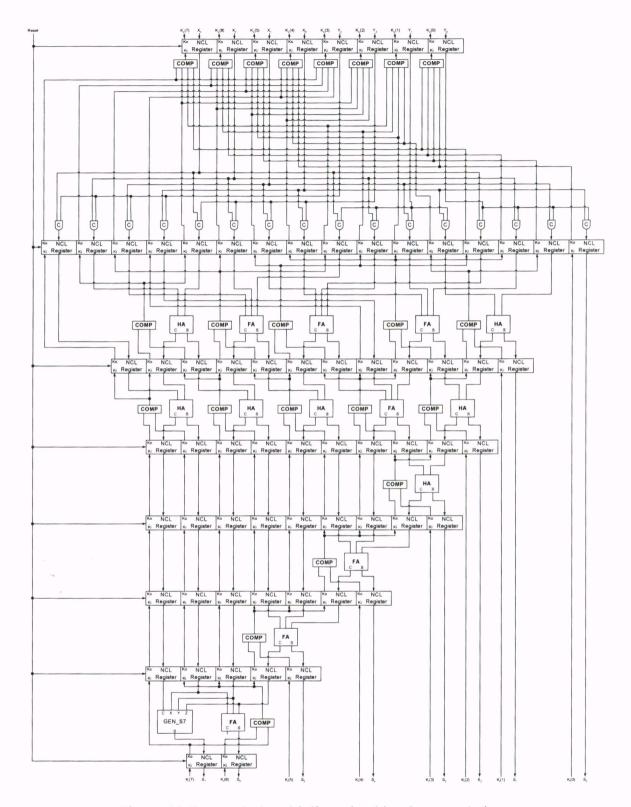

| 58. 4×4 multiplier block diagram                                     | 85 |

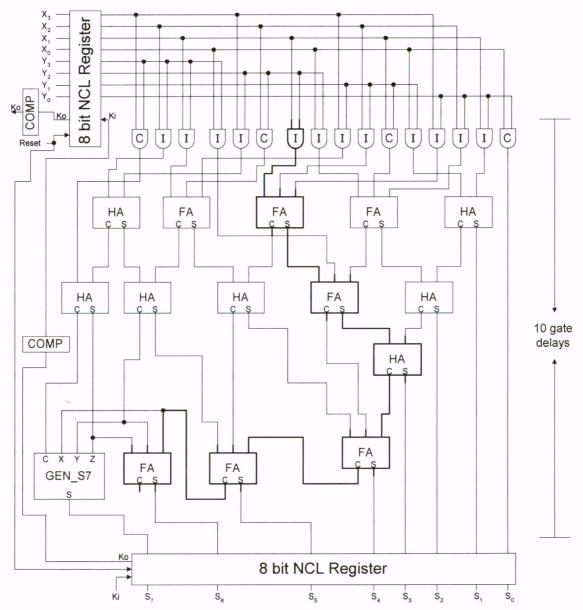

| 59. Non-pipelined, 1-stage 4×4 multiplier using full-word completion | 86 |

| 60. Half adder                                                       | 87 |

| 61. GEN S7 component                                                 | 87 |

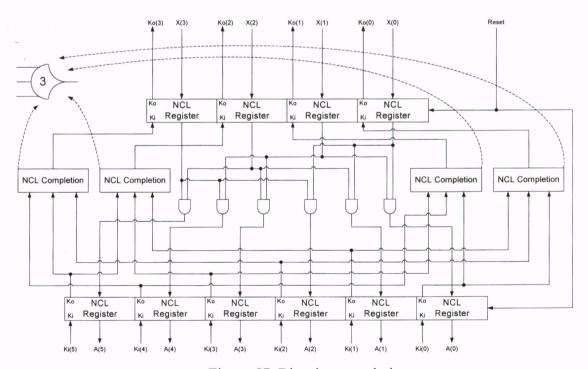

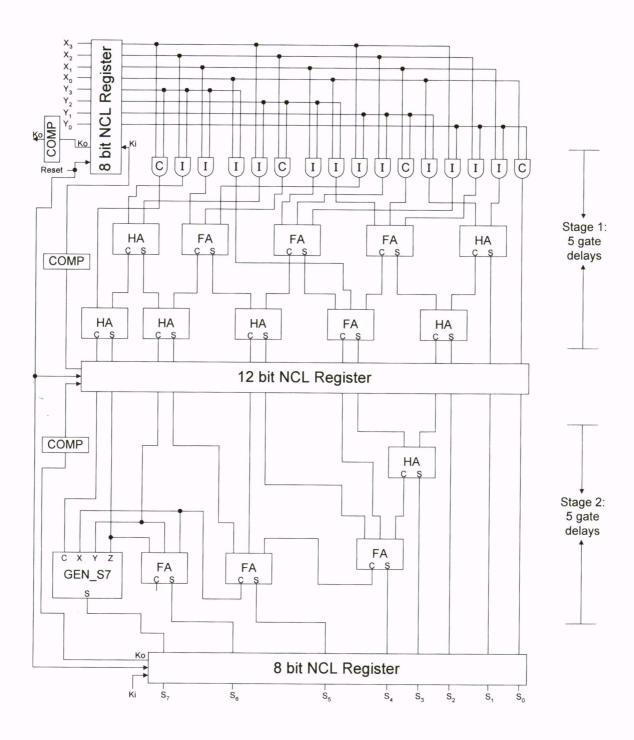

| 62. 2-stage 4×4 multiplier using full-word completion             |

|-------------------------------------------------------------------|

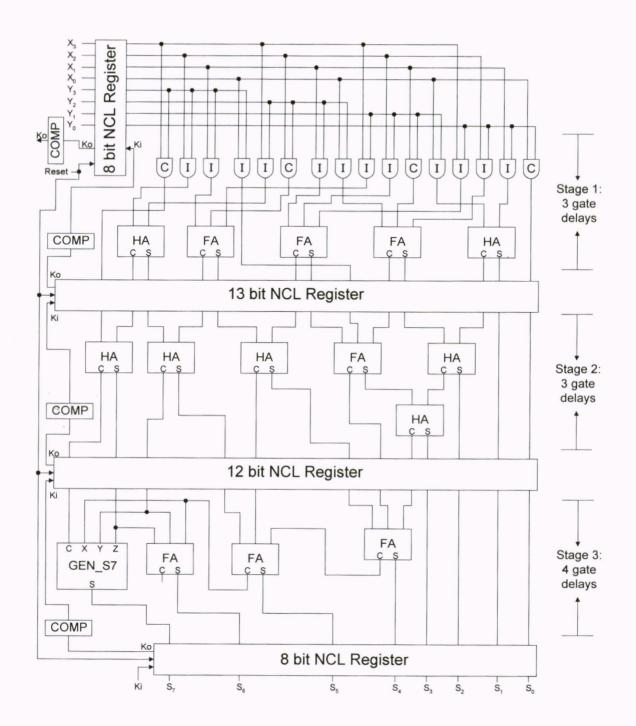

| 63. 3-stage 4×4 multiplier using full-word completion             |

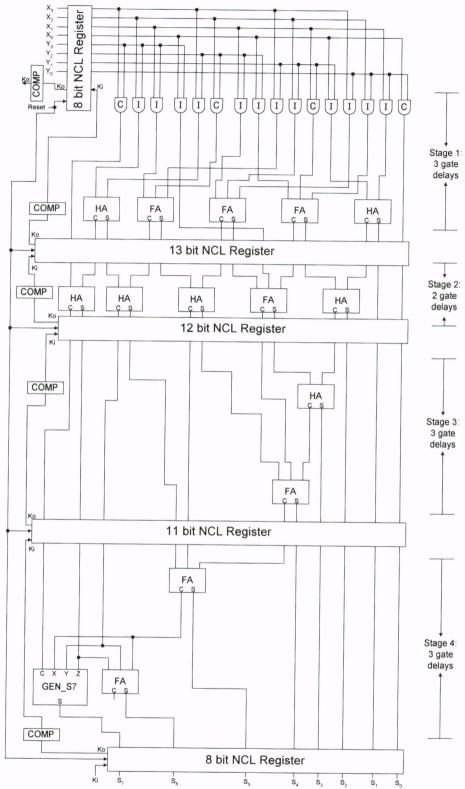

| 64. 4-stage 4×4 multiplier using full-word completion             |

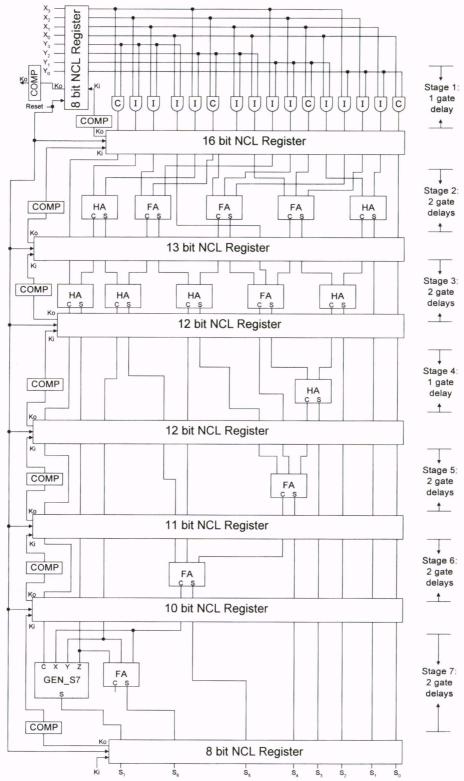

| 65. 7-stage 4×4 multiplier using full-word completion             |

| 66. 7-stage 4×4 multiplier using bit-wise completion95            |

| 67. NCR architecture                                              |

| 68. 1-bit Demultiplexer                                           |

| 69. Sequence generator                                            |

| 70. 1-bit Multiplexer                                             |

| 71. NCL pipeline with one slow stage                              |

| 72. MAC block diagram                                             |

| 73. Taxonomy of 72+32×32 MAC                                      |

| 74. Non-pipelined Modified Baugh-Wooley MAC                       |

| 75. Output divisions for up-scaling, no scaling, and down-scaling |

| 76. Non-pipelined Modified Booth2 MAC119                          |

| 77. Pipelined Modified Baugh-Wooley MAC                           |

| 78. Pipelined Modified Booth2 MAC                                 |

| 79. 4-bit carry-lookahead adder                                   |

#### 1.0 INTRODUCTION

#### 1.1 Objective

This Ph.D. dissertation is intended to familiarize the reader with the syntax and semantics of NULL Convention Logic (NCL), to develop NCL design methods and optimization techniques, and to discuss analytical and experimental results. The main focus will be on architectural aspects of NCL as discussed at the gate level.

#### 1.2 History and Benefits of NCL

Various design aspects of NCL were patented by Karl Fant and Scott Brandt in April of 1994 [1]. Acknowledging that clocked circuits unnecessarily restricted execution flow, consumed power proportional to the operating frequency, occupied significant device area for the clock tree, and greatly complicated the design process, they sought a clockless design approach. But eliminating clocks as in traditional asynchronous design presented race conditions and made timing optimizations like pipelining difficult. By eliminating clocks but retaining control information in the datapath, NCL aims at designing VLSI devices with greater ease, with a reduced power budget, lower electromagnetic interface effects, and reduced noise margins.

Karl Fant founded Theseus Logic, Inc., which began operations in Minnesota in January of 1996, to develop NCL-based Application Specific Integrated Circuits (ASICs)

and "soft cores" for electronics manufacturers. The company has demonstrated the viability of NCL technology through government programs with Honeywell, Lockheed Martin, the Defense Advanced Research Projects Agency (DARPA), the Ballistic Missile Defense Organization (BMDO), the US ARMY Communication Electronics Command (CECOM), and the National Security Agency (NSA). A privately held company, Theseus is now headquartered in Orlando, Florida and also has a research and development office in Sunnyvale, California.

In August 1999, Theseus and the University of Central Florida were awarded a state—funded grant for a joint research project involving NCL ASIC design and development of formal design methods for NCL. In October 1999 Theseus formed a strategic technology alliance with Motorola's Semiconductor Products Sector to jointly implement NCL versions of various Motorola microcontrollers. And in September 2000 Theseus formed a strategic technology alliance with Synopsys for development of NCL-based design tools. Many potential applications from mobile, handheld low-power DSP devices to general purpose CPUs lie ahead.

Table I lists the advantages of asynchronous design, both bounded-delay and delay-insensitive models, over clocked Boolean design. It shows that clocked Boolean design necessitates a global clock, where asynchronous design does not; and that only delay-insensitive methods have no glitch power, deliver average-case verses worse-case performance, and provide for ease of design reuse. Table I also lists that power, noise, and EMI are disadvantages for clocked Boolean circuits, but are advantages for their asynchronous counterparts, as detailed below.

Table I. Attributes of clocked Boolean and asynchronous methods.

| Maria de Maria    |        |        | Performance |        |       |       |       |     |

|-------------------|--------|--------|-------------|--------|-------|-------|-------|-----|

|                   | Global | Glitch | Average-    | Worse- | Reuse |       |       |     |

| Design Paradigm   | Clock  | Power  | Case        | Case   | Ease  | Power | Noise | EMI |

| Clocked Boolean   | Y      | Y      | N           | Y      | N     | D     | D     | D   |

| Bounded-Delay     | N      | Y      | N           | Y      | N     | Α     | Α     | Α   |

| Delay-Insensitive | N      | N      | Y           | N      | Υ     | Α     | Α     | Α   |

Traditional clocked Boolean circuits suffer from the layout nightmare of clock distribution and require high power surges at the clock edge, when switching is most prevalent. Synchronous circuits also cannot operate at their maximum potential due to clock skew. These trends have led to a large revival of interest in the asynchronous approach.

In asynchronous design approaches each component in the system is not controlled by a clock signal. Thus, timing design margins are not required to compensate for clock skew. An asynchronous design theoretically should allow data to flow through a circuit at the maximum rate of the underlying switching technology being used. As the required inputs arrive, a function should be executed and its results sent to the required destination(s).

Nonetheless, traditional asynchronous design techniques have drawbacks of their own. An asynchronous circuit is traditionally designed as having a datapath and a control path. Since there is no clock to synchronize these two paths, there must be extensive timing analysis performed in order to determine the worse-case delay in the datapath.

This delay must then be matched in the control path in order to synchronize the two paths without the use of a clock. This method of asynchronous circuit design is classified as

bounded-delay. Both clocked Boolean and bounded-delay designs suffer from the problem of limiting the maximum operating frequency based on the worse-case delay in the datapath. Bounded-delay design also alleviates the complex task of clock distribution, but it introduces another complex task of determining the worse-case datapath delay and matching this delay in the control path. An important benefit of NCL is asynchronous execution that is completely delay-insensitive, assuming that wire forks are isochronic [2, 3]. When designing in NCL there is no need for worse-case delay analysis and delay matching, which makes the NCL design process significantly less complex than traditional asynchronous design.

NCL on the other hand, allows a system to run at its maximum frequency regardless of the input. For inputs which traverse a path with minimal delay, the output will arrive much faster than for inputs which traverse a longer delay path. This property allows a NCL circuit to potentially operate faster than a traditional Boolean asynchronous design. NCL circuits are also much more adaptive, and facilitate easier reuse than Boolean asynchronous circuits, since timing analysis is unnecessary due to NCL's delayinsensitivity.

As the trend towards higher clock frequency continues, power consumption, noise, and electromagnetic interference (EMI) of synchronous designs increase significantly. PCs are becoming more widespread and consume an increasingly substantial percentage of the world's electrical power. With the absence of a clock, NCL systems promise to reduce power consumption, noise, and EMI. NCL circuits, designed using CMOS, also exhibit an inherent idle behavior since they only switch when useful

work is being performed, unlike clocked Boolean circuits that switch every clock pulse.

NCL circuits adhere to monotonic transitions between DATA and NULL, so there is no glitching, unlike clocked Boolean circuits that produce substantial glitch power. NCL systems also distribute the demand for power over time and area, reducing the occurrence of hot spots, system noise, and peak power demand, unlike clocked Boolean circuits where all circuitry switches simultaneously at the clock edge. Furthermore, NCL systems are very tolerant of power supply variations such that cheaper power supplies can be used and voltage can be reduced dramatically to meet performance criterion while reducing power consumption. Therefore, a very fast NCL circuit can be run at a lower voltage to reduce power consumption when high performance is not required.

The initial version of Motorola STAR08 processor using NCL technology shows a 40% reduction in power and a 10 dB reduction in noise over its clocked Boolean counterpart, while operating at a comparable frequency. Since NCL circuits have been demonstrated to consume significantly less power than clocked Boolean designs, NCL has a promising future in the field of mobile electronics, where power consumption is a major design consideration.

#### 1.3 Research Challenges

This dissertation focuses on three architectural areas of NCL, all related to circuit design and optimization. Since NCL is still conceptually young, there is no current formal method for designing optimal NCL circuits. NCL differs significantly from Boolean logic; so traditional Boolean techniques for circuit simplification cannot be

applied to NCL circuits without major modifications. Thus, the first goal is to devise a new formal method for NCL circuit simplification, such that optimal designs are readily obtained.

The unique structure of NCL lends itself to pipelining, even though a clock is not present. Since there is no clock in NCL to synchronize pipeline stages, the design of a NCL pipeline will be significantly different than a Boolean pipeline design. A related need is to develop a means for determining the maximum number of gate delays per stage to yield the maximum attainable throughput when pipelining a given design. Thus, the second goal is to develop a formal method for designing throughput optimal NCL systems.

The NULL cycle accounts for approximately half of the cycle time of a NCL circuit, therefore reducing the system's maximum attainable throughput by a factor of two. Thus, the third goal is to devise a technique to reduce the NULL cycle, further increasing system performance. This further speedup may be essential for especially time critical circuits.

#### 1.4 Dissertation Overview

This dissertation is organized into seven chapters. Chapter 2 presents previous work and contains an in-depth discussion of fundamental NCL terminology, concepts, and components, which will provide the notation and basis for the rest of the dissertation. In Chapter 3, a formal method for designing different types of optimal combinational, simplified NCL circuits is developed. This method is then tested on the design of

fundamental logic functions, a full adder, and a 4-bit counter, with simulation times, gate counts, and transistor counts included. In Chapter 4, a formal method for producing pipelined designs, which yield the maximum attainable throughput, is devised. This method is tested on the design of a 4-bit by 4-bit multiplier, and includes comprehensive simulation times and pipeline stage information. Chapter 5 develops a technique for reduction of the NULL cycle, and applies it to a non-pipelined 4-bit by 4-bit multiplier. Chapter 6 details the design of a throughput and area optimal 72+32×32 MAC. Chapter 7 highlights the contributions of this dissertation and provides direction for future research.

#### 2.0 PREVIOUS WORK

For the last two decades the focus of digital design has been primarily on synchronous, clocked architectures. However, as clock rates have significantly increased while feature size has decreased, clock skew has become a major problem. High performance chips must dedicate increasingly larger portions of their area for clock drivers to achieve acceptable skew, causing these chips to dissipate increasingly higher power. As these trends continue, the clock is becoming more and more difficult to manage. This has caused renewed interest in asynchronous digital design.

NULL Convention Logic (NCL) offers a delay-insensitive logic paradigm where control is inherent with each datum. NCL follows the so-called "weak conditions" of Seitz's delay-insensitive signaling scheme [4]. As with other delay-insensitive logic methods discussed herein, the NCL paradigm assumes that forks in wires are isochronic [2, 3]. The origins of various aspects of the paradigm, including the NULL (or spacer) logic state from which NCL derives its name, can be traced back to Muller's work on speed-independent circuits in the 1950s and 1960s [5].

Earlier work by Seitz presents an extensive discussion of delay-insensitive logic, illustrating its advantages over traditional clocked logic, and includes one approach to designing such circuits [2]. Some other methods of designing delay-insensitive circuits are detailed in [6, 7, 8, 9]. These techniques concentrate on developing circuits from a

standardized set of gates, while other techniques [10, 11] emphasize formal logic methods that directly yield designs at the transistor-level. In the application of CMOS technology, processors implemented with this type of signaling scheme include the MIPS R3000 [12] and another at Caltech [13], the FLYSIG processor at the University of Paderborn [14], the MSL16A at the Chinese University of Hong Kong [15], and the TITAC processor at the Toyko Institute of Technology [16]. NCL differs from the above mentioned methods in that they only utilize one type of state-holding gate, the *C-element* [5]. On the other hand, all NCL gates are state-holding. Thus, NCL optimization methods can be considered as a subclass of the techniques for developing delay-insensitive circuits using a pre-defined set of more complex components with built-in hysteresis behavior. In functions that do not require full minterm generation, such attributes may allow optimizations that produce smaller, faster delay-insensitive combinational circuits.

#### 2.1 Overview of Asynchronous Methods

Asynchronous circuits fall into two main categories: delay-insensitive and bounded-delay models. Paradigms, like NCL, assume delays in both logic elements and interconnects to be unbounded, although they assume that wire forks are isochronic. This implies the ability to operate in the presence of indefinite arrival times for the reception of inputs. Completion detection of the output signals allows for handshaking to control input wavefronts. On the other hand, bounded-delay models such as *Huffman circuits* [17], *burst-mode circuits* [18], and *micropipelines* [19] assume that delays in both gates and wires are bounded. Delays are added based on worse-case scenarios to avoid hazard

conditions. This leads to extensive timing analysis of worse-case behavior to ensure correct circuit operation. Since NCL exhibits neither of these characteristics, bounded-delay models are not addressed further.

Table II summarizes the attributes of various self-timed methods. It lists that only micropipelines add explicit delays, while the other methods rely on completion detection; and that only micropipelines exhibit worse-case performance, verses the average-case performance of the other methods. Table II also shows that only Seitz's, Anantharaman's, and DIMS approaches require full minterm generation, while all approaches use C-elements exclusively for their state-holding gates, except for micropipelines that do not require any state-holding elements, NCL that utilizes numerous state-holding gates, and Martin's method that does not use a standardized set of gates but instead develops each element at the transistor level, as detailed below.

Table II. Attributes of self-timed methods.

|                | Explicit |            | Full Minterm | State-     | Perforr  | nance  |

|----------------|----------|------------|--------------|------------|----------|--------|

| Self-Timed     | Delays   | Completion | Generation   | Holding    | Average- | Worse- |

| Method         | Inserted | Detection  | Required     | Gates      | Case     | Case   |

| Micropipelines | Υ        | N          | N            | None       | N        | Υ      |

| Seitz          | N        | Υ          | Y            | C-elements | Υ        | N      |

| DIMS           | N        | Υ          | Y            | C-elements | Y        | N      |

| Anantharaman   | N        | Υ          | Y            | C-elements | Y        | N      |

| Singh          | N        | Υ          | N            | C-elements | Y        | N      |

| David          | N        | Y          | N            | C-elements | Y        | N      |

| NCL            | N        | Υ          | N            | Numerous   | Υ        | N      |

| Martin         | N        | Y          | N            | N/A        | Υ        | N      |

#### 2.1.1 Gate-Level Delay-Insensitive Methods

Most gate-level delay-insensitive methods combine *C-elements* [5] with Boolean gates for circuit construction. A C-element behaves as follows: when all inputs assume the same value then the output assumes this value, otherwise the output does not change. Seitz's method [2] employs a sum of products network using AND and OR gates, combined with a network to OR both rails of all inputs together. The output of the OR network is then combined with the sum of products outputs, using C-elements, to produce the circuit outputs, DIMS [9] and Anantharaman's approach [7] are similar to each other in that each produces a sum of products circuit using OR gates and C-elements, instead of AND gates. Singh's method [8] combines small self-timed logic functions to produce the desired functionality, while David's method [6] produces self-timed circuits with n inputs and m outputs, composed of four subnets, ORN, CEN, DRN, and OUTN. ORN consists of n 2-input OR gates, which OR together both rails of each dual-rail input. CEN is an n-input C-structure, which is equivalent to an n-input C-element, whose inputs are the n outputs from ORN. DRN is a monotonic implementation of each rail of the dual-rail output(s). OUTN produces the circuit output and consists of 2m 2-input C-elements, each with the output of CEN as one input, and an output from DRN as the other input. Seitz's method, Anantharaman's approach, and DIMS require the generation of all minterms to implement a function, where a minterm is defined as the logical AND, or product, of input signals. While Singh's and David's methods do not require full minterm generation, they rely solely on C-elements for delay-insensitivity.

Since Seitz's and Anantharaman's approaches, along with DIMS, require the generation of all minterms, no optimization is possible. However, Singh's and David's approaches allow for some Boolean optimization to be performed, but they may not facilitate the same potential for optimization provided by NCL's many state-holding gates, as will be shown in Chapter 3.

#### 2.1.2 Transistor-Level Delay-Insensitive Methods

Other delay-insensitive methods such as Martin's [30] consist of constructing transistor-optimized circuits from their Boolean equations through formal logic transformations. Most of the resulting transistor level circuits are state-holding. However, since these methods do not target a specific set of gates, they are not directly comparable to gate-level delay-insensitive methods, including NCL.

#### 2.2 Overview of NCL

NCL gates are a special case of the logical operators or gates available in digital VLSI circuit design [20]. Such an operator consists of a set condition and a reset condition that the environment must ensure are not both satisfied at the same time. If neither condition is satisfied then the operator maintains its current state. A number of NCL-based designs have been commercially developed by Theseus Logic, Inc., which has formed strategic alliances with Motorola for microcontroller design and Synopsys for NCL-based design tool development.

#### 2.2.1 Delay-Insensitivity

NCL uses symbolic completeness of expression [21] to achieve self-timed behavior. A symbolically complete expression is defined as an expression that only depends on the relationships of the symbols present in the expression without a reference to the time of evaluation. Traditional Boolean logic is not symbolically complete; the output of a Boolean gate is only valid when referenced with time. For example, assume it takes 1 ns for output Z of an AND gate to become valid once its inputs X and Y have arrived. As shown in Figure 1, suppose X = 1, Y = 0, and Z = 0, initially. If Y changes to 1, Z will change to 1 after 1 ns; so Z is not valid from the time Y changes until 1 ns later. Therefore output Z not only depends on the inputs X and Y, but time must also be referenced in order to determine the validity of Z. This can be critical when Z is used as an input to another circuit.

Figure 1. Symbolic incompleteness of a Boolean AND gate.

In particular, dual-rail signals, quad-rail signals, or other *Mutually Exclusive*Assertion Groups (MEAGs) can be used to incorporate data and control information into one mixed signal path to eliminate time reference [22]. A dual-rail signal, D, consists of two wires,  $D^0$  and  $D^1$ , which may assume any value from the set {DATA0, DATA1, NULL}. The DATA0 state ( $D^0 = 1$ ,  $D^1 = 0$ ) corresponds to a Boolean logic 0, the

DATA1 state ( $D^0 = 0$ ,  $D^1 = 1$ ) corresponds to a Boolean logic 1, and the NULL state  $(D^0 = 0, D^1 = 0)$  corresponds to the empty set meaning that the value of D is not yet available. The two rails are mutually exclusive, so that both rails can never be asserted simultaneously; this state is defined as an illegal state. A quad-rail signal, O, consists of four wires,  $Q^0$ ,  $Q^1$ ,  $Q^2$ , and  $Q^3$ , which may assume any value from the set {DATA0, DATA1, DATA2, DATA3, NULL}. The DATA0 state  $(Q^0 = 1, Q^1 = 0, Q^2 = 0, Q^3 = 0)$ corresponds to two Boolean logic signals, X and Y, where X = 0 and Y = 0. The DATA1 state  $(Q^0 = 0, Q^1 = 1, Q^2 = 0, Q^3 = 0)$  corresponds to X = 0 and Y = 1. The DATA2 state  $(Q^0 = 0, Q^1 = 0, Q^2 = 1, Q^3 = 0)$  corresponds to X = 1 and Y = 0. The DATA3 state  $(Q^0 = 0, Q^1 = 0, Q^2 = 0, Q^3 = 1)$  corresponds to X = 1 and Y = 1, and the NULL state  $(Q^0 = 0, Q^1 = 0, Q^2 = 0, Q^3 = 0)$  corresponds to the empty set meaning that the result is not yet available. The four rails of a quad-rail NCL signal are mutually exclusive, so no two rails can ever be asserted simultaneously; these states are defined as illegal states. Both dual-rail and quad-rail signals are space optimal delay-insensitive codes, requiring two wires per bit. Other higher order MEAGs are not typically wire count optimal, however they can be more power efficient due to the decreased number of transitions per cycle.

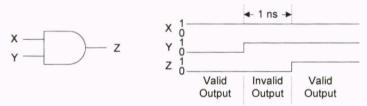

Consider the behavior of a symbolically complete AND function using NCL as shown in Figure 2. Assume it takes 1 ns for output Z of a NCL AND function to become valid once its inputs X and Y have arrived. Also, initially suppose X is DATA1, Y is DATA0, and Z is DATA0. Before the next set of inputs can be applied, all inputs must first transition to NULL, which causes the output to transition to NULL, 1 ns later. Once

the output has transitioned to NULL, the next input set can be applied. If the next input set consists of X = DATA1 and Y = DATA1, Z will become DATA1 after 1 ns, signaled by Z transitioning from NULL to DATA. Output Z will remain DATA1 until both inputs, X and Y, transition to NULL, due to the hysteresis behavior inherent in each threshold gate. Time is never referenced to determine the validity of Z. The 1 ns delay is an arbitrary gate transition delay and does not affect the validity of Z.

Figure 2. NCL AND function:  $Z = X \bullet Y$  and associated waveforms.

#### 2.2.2 Logic Gates and Functional Blocks

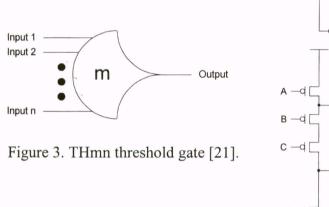

NCL uses threshold gates with hysteresis [23] for its composable logic elements. One type of threshold gate is the *THmn gate*, where  $1 \le m \le n$ , as depicted in Figure 3. A THmn gate corresponds to an operator with at least m signals asserted as its set condition and all signals de-asserted as its reset condition. THmn gates have n inputs. At least m of the n inputs must be asserted before the output will become asserted. Because threshold gates are designed with hysteresis, all asserted inputs must be de-asserted before the output will be de-asserted. Hysteresis is used to provide a means for monotonic

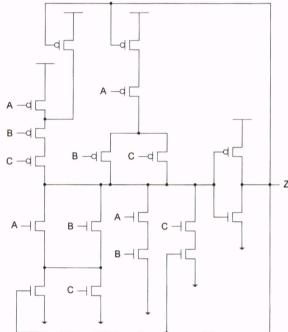

transitions and a complete transition of multi-rail inputs back to a NULL state before asserting the output associated with the next wavefront of input data. In a THmn gate, each of the n inputs is connected to the rounded portion of the gate. The output emanates from the pointed end of the gate. The gate's threshold value, m, is written inside of the gate. Figure 4 shows a static CMOS implementation of a TH23 gate, with inputs A, B, and C, and output Z. [23] details various design implementations (static, semi-static, and dynamic) of THmn gates.

Figure 4. Static CMOS implementation of a TH23 gate.

Another type of threshold gate is referred to as a weighted threshold gate, denoted as THmnWw<sub>1</sub>w<sub>2</sub>...w<sub>R</sub>. Weighted threshold gates have an integer value,  $m \ge w_R > 1$ , applied to inputR. Here  $1 \le R < n$ ; where n is the number of inputs; m is the gate's threshold; and  $w_1, w_2, ...w_R$ , are the integer weights of input1, input2, ... inputR,

respectively. For example, consider a TH34W2 gate, whose n = 4 inputs are labeled A, B, C, and D. The weight of input A, W(A), is therefore 2. Since the gate's threshold, m, is 3, this implies that in order for the output to be asserted, either inputs B, C, and D must all be asserted, or input A must be asserted and any other input, B, C, or D must also be asserted. NCL threshold gates may also include a reset input to initialize the gate's output. Resetable gates are denoted by either a D or an N appearing inside the gate, along with the gate's threshold, referring to the gate being reset to logic 1 or logic 0, respectively.

By employing threshold gates for each logic rail, NCL is able to determine the output status without referencing time. Inputs are partitioned into two separate wavefronts, the NULL wavefront and the DATA wavefront. The NULL wavefront consists of all inputs to a circuit being NULL, while the DATA wavefront refers to all inputs being DATA, some combination of DATA0 and DATA1. Initially all circuit elements are reset to the NULL state. First, a DATA wavefront is presented to the circuit. Once all of the outputs of the circuit transition to DATA, the NULL wavefront is presented to the circuit. Once all of the outputs of the circuit transition to NULL, the next DATA wavefront is presented to the circuit. This DATA/NULL cycle continues repeatedly. As soon as all outputs of the circuit are DATA, the circuit's result is valid. The NULL wavefront then transitions all of these DATA outputs back to NULL. When they transition back to DATA again, the next output is available.

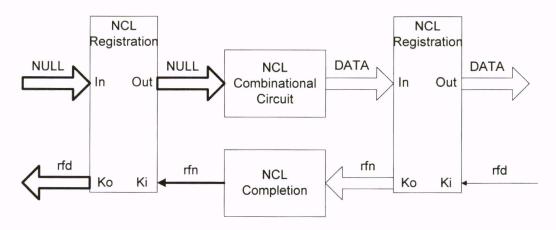

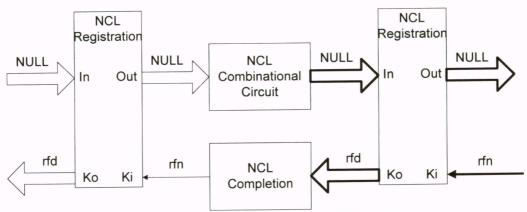

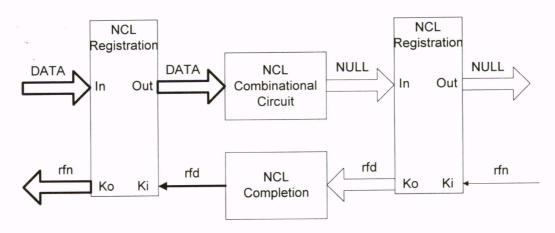

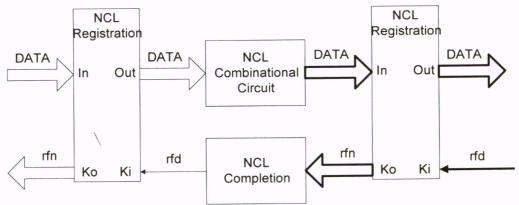

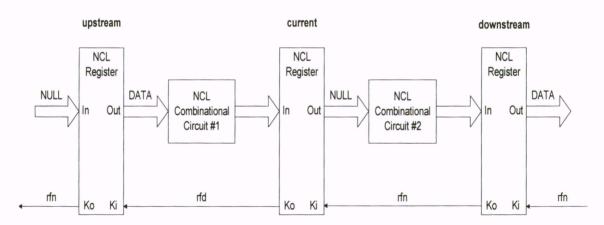

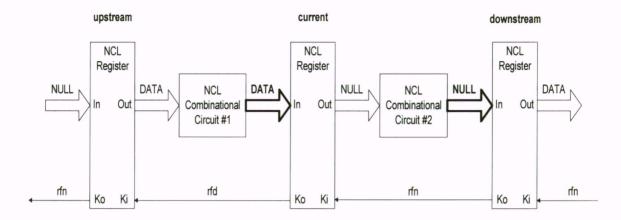

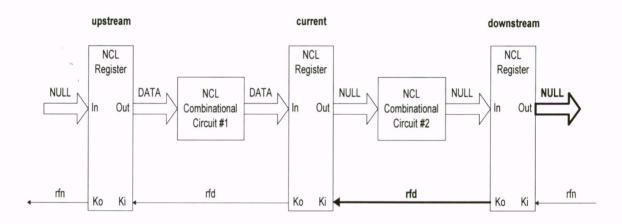

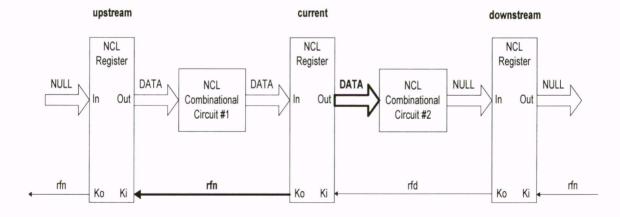

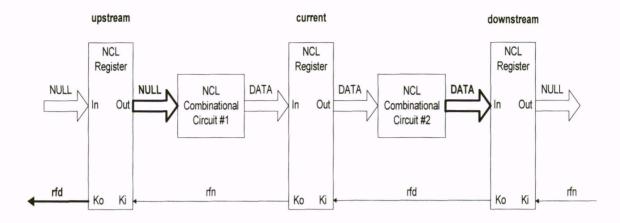

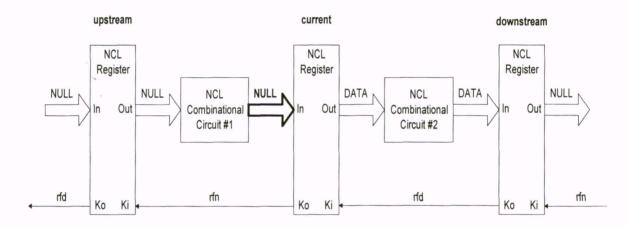

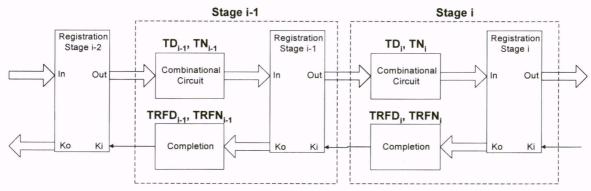

Figure 5 shows the primary functional blocks of a NCL circuit. The NCL registration stages act to control the DATA/NULL wavefronts, through their request input lines,  $K_i$ , and their request output lines,  $K_o$ . The NCL completion detects complete

DATA and NULL sets, where all outputs are DATA or all outputs or NULL, respectively, at the output of NCL registration. *NCL combinational circuits* provide the fundamental functionality of a NCL system. Since every NCL circuit continually cycles through NULL followed by DATA, one complete cycle will consist of NULL flowing through the combinational circuitry as shown in Figure 5, followed by NULL flowing through the completion circuitry as shown in Figure 6, followed by DATA flowing through the combinational circuitry as shown in Figure 7, and finally followed by DATA flowing through the completion circuitry, back to the input as shown in Figure 8. *rfn* refers to *request for NULL* and *rfd* refers to *request for DATA*. Each phase of this cycle, depicted in the Gantt chart of Figure 9, will be referred to here on out as the DATA-to-DATA cycle; and the period of this cycle will be called the DATA-to-DATA cycle time (*T*<sub>DD</sub>). *T*<sub>DD</sub> has an analogous role to the clock period in a synchronous system.

Figure 5. NULL flowing through combinational circuitry.

Figure 6. Completion detection of NULL output.

Figure 7. DATA flowing through combinational circuitry.

Figure 8. Completion detection of DATA output.

Figure 9. DATA-to-DATA cycle time (T<sub>DD</sub>).

#### 2.2.3 Completeness of Input

The *input-completeness* criterion [21], which NCL circuits must maintain in order to be delay-insensitive, requires that:

- the outputs of a circuit may not transition from NULL to DATA until all inputs have transitioned from NULL to DATA, and

- the outputs of a circuit may not transition from DATA to NULL until all inputs have transitioned from DATA to NULL.

In circuits with multiple outputs, it is acceptable for some of the outputs to transition without having a complete input set present, as long as all outputs cannot transition before all inputs arrive. This signaling scheme is equivalent to the "weak conditions" of delay-insensitive signaling defined by Seitz [4]. Consider the incomplete NCL AND function shown in Figure 10. The output can change from NULL to DATA0 without both inputs first transitioning to DATA. For instance, if A = DATA0 and B = NULL then C = DATA0, which breaks the completeness of input criterion. Figure 11 shows a complete NCL AND function since the output cannot transition until both inputs have transitioned.

Figure 11. Conventional input-complete AND function:  $Z = X \cdot Y$ .

Completeness of DATA can be ensured for an N input function as shown in Algorithm 2.1. If a function is complete with respect to DATA, it is also complete with respect to NULL due to the hysteresis functionality of every NCL gate. This completeness check takes  $O(N \cdot 2^{N-1})$ ; however, this is unnecessary for many functions due to their inherent completeness. For example, the XOR function, the full adder, and the increment circuitry, all are inherently complete such that it is impossible to know the output without all of the inputs being known.

```

for (i = 1 to N) loop INPUT_i = NULL group INPUTS_j (1 \leq j \leq N, j \neq i) such that they form an N-1 bit word called REMAINDER for (k = 0 to 2^{N-1}-1) loop REMAINDER = k if (all output bits are DATA) then return (INCOMPLETE) end loop end loop return (COMPLETE)

```

Algorithm 2.1. Input-completeness pseudocode.

#### 2.2.4 Observability

There is one more condition that must be met in order for NCL to retain delayinsensitivity. No *orphans* may propagate through a gate. An orphan is defined as a wire

that transitions during the current DATA wavefront, but is not used in the determination

of the output. Orphans are caused by wire forks and can be neglected through the

isochronic fork assumption, as long as they are not allowed to cross a gate boundary. This *observability* condition ensures that every gate transition is observable at the output.

Consider an incorrect version of an XOR function shown in Figure 12, where an orphan

is allowed to pass through the TH12 gate. For instance, when X = DATA0 and Y = DATA0, the TH12 gate is asserted, but does not take part in the determination of the

output, Z = DATA0. This orphan path is shown in boldface in Figure 12. A correct, fully

observable version of the XOR function is given in Figure 13, where no orphans

propagate through any gate. An orphan checker tool, as a Synopsys shell, is run on each

design to ensure observability.

Figure 12. Incorrect XOR function:  $Z = X \oplus Y$  (orphans may propagate through a gate).

Figure 13. Correct XOR function:  $Z = X \oplus Y$  (orphans may not propagate through any gate).

## 2.2.5 NCL Registration

With the input-completeness and observability criteria met, a NCL circuit is therefore delay-insensitive, because the output will not transition until all of its inputs transition and two consecutive DATA wavefronts will always remain separated despite arbitrarily large gate delays. Henceforth, the circuit will wait indefinitely until it receives all of its inputs and the inputs traverse the logic, before requesting the next either NULL or DATA wavefront.

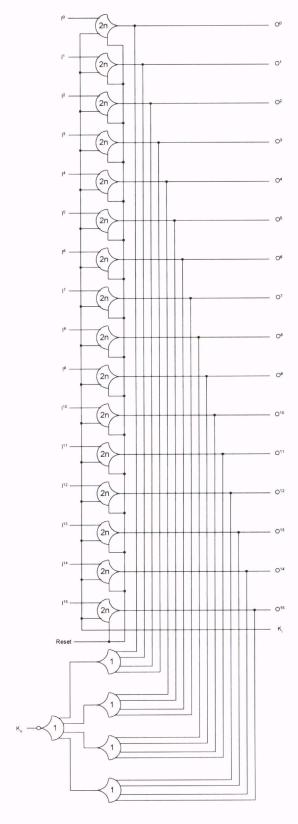

With this in mind, there must be a device that monitors the outputs of NCL circuits in order to detect when there is a complete DATA set or a complete NULL set, and upon detection of a complete output set, request the next wavefront. The NCL register, shown in Figure 14, does just that. When the request input line,  $K_i$ , is rfd, any of the register inputs, I, that are asserted are allowed to pass through their respective TH22 gate, to the output of the register. Likewise, when the request input line,  $K_i$ , is rfn, any of the register inputs, I, that are de-asserted are allowed to pass through their respective TH22 gate, to the output of the register. Only after all n inputs to the register have

transitioned to DATA, causing their respective outputs to transition to DATA as well, will the register's request output line,  $K_o$ , transition to rfn, meaning that the register has received the DATA wavefront and is requesting the NULL wavefront. And, only after all n inputs to the register have transitioned to NULL, causing their respective outputs to transition to NULL as well, will the register's request output line,  $K_o$ , transition to rfd, meaning that the register has received the NULL wavefront and is requesting the DATA wavefront.

Figure 14: n-bit dual-rail registration.

The NCL register does not assure completeness of input, it only assures completeness of output. The NCL register will not request the NULL wavefront until the current DATA wavefront has been received; and likewise the next DATA wavefront will not be requested until the current NULL wavefront has been received. This would not prevent the NULL wavefront from being requested before all of the inputs become DATA, if the output was all DATA, caused by some inputs being DATA and combinational logic which is not complete with respect to its inputs.

Assume that the registers shown in Figure 15 have the following values: the output of the *upstream* register is DATA, so it is requesting NULL; the output of the current register is NULL, so it is requesting DATA; and the output of the downstream register is DATA, so it is requesting NULL. Also assume that the input to the upstream register is NULL and that the request input,  $K_i$ , to the downstream register is rfn. The NULL input to the upstream register will be blocked because the upstream register's request input line,  $K_i$ , is set to rfd. The DATA output from the upstream register will flow through the first set of combinational logic, to the input of the current register, while the NULL output of the current register flows through the second set of combinational logic to the input of the downstream register, as depicted in Figure 16. Once the DATA wavefront reaches the input of the current register, it is blocked, because the current register's request input line,  $K_i$ , is rfn. But when the NULL wavefront reaches the input of the downstream register, it is allowed to pass through to the output because the downstream register's request input line,  $K_i$ , is rfn. When every output of the downstream register transitions to NULL, the downstream register's request output line,  $K_o$ , will

transition to rfd, shown in Figure 17, which will allow the DATA wavefront at the input of the current register to pass through to the output of the current register and start flowing through the second set of combinational logic. When all outputs of the current register have transitioned to DATA, the request output line,  $K_o$ , of the current register will transition to rfn, as shown in Figure 18, which will allow the NULL wavefront at the input of the upstream register to pass through to the output of the upstream register and start flowing through the first set of combinational logic, as depicted in Figure 19. As shown in Figure 20, once the NULL wavefront has passed through the first set of combinational logic, the circuit will be in a static state; and no more transitions can occur until the request input line,  $K_i$ , of the downstream register transitions to rfd, signifying that the NULL wavefront at the output of the downstream register has been received by the next register after the downstream register. The registers will continue to control the NULL/DATA cycles in this fashion, insuring that the next wavefront is sent only after the current wavefront has produced all of its outputs.

Figure 15. Initial register state.

Figure 16. Register state after traversing combinational circuitry.

Figure 17. Register state after NULL wavefront passes through downstream register.

Figure 18. Register state after DATA wavefront passes through current register.

Figure 19. Register state after NULL wavefront passes through upstream register.

Figure 20. Static register state.

All NCL systems have at least two register stages, one at both the input and output; and all NCL systems with feedback have at least three register stages in the feedback loop [21]. This technique of organizing registers into a ring is fully discussed in [24, 9]. These register stages interact through handshaking to prevent DATA set<sub>i</sub> from overwriting DATA set<sub>i-1</sub> by ensuring that the two consecutive DATA sets are always separated by a NULL set.

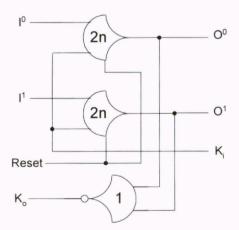

## 2.2.6 NCL Completion

Actual NCL registration is realized through cascaded arrangements of single-bit dual-rail registers or single-signal quad-rail registers, depicted in Figure 21 and 22, respectively. Therefore, an N-bit register stage, comprised of N single-bit dual-rail NCL registers, requires N completion signals, one for each bit. The NCL Completion component, shown in Figure 23, uses these  $NK_0$  lines to detect complete DATA and NULL sets at the output of every register stage and request the next NULL and DATA set, respectively. The single-bit output of the completion component is connected to all  $K_i$ lines of the previous register stage. Since the maximum input threshold gate currently supported is the TH44 gate, the number of logic levels in the completion component for an N-bit register is given by log<sub>4</sub> N. Likewise, the completion component for an N-bit quad-rail registration stage requires  $\frac{N}{2}$  inputs, and can be realized in a similar fashion using TH44 gates. The registers shown in Figures 21 and 22 are reset to NULL. Either register could be instead reset to a DATA value by replacing exactly one of the TH22n gates with a TH22d gate.

Figure 21. Single-bit dual-rail register.

## 3.0 THRESHOLD COMBINATIONAL REDUCTION METHOD

Delay-insensitive logic design methods are developed using *Threshold* Combinational Reduction (TCR) within the NULL Convention Logic (NCL) paradigm. NCL logic elements are realized using 27 distinct transistor networks implementing the set of all functions of four or fewer variables, thus facilitating a variety of gate-level optimizations. TCR optimizations are formalized for NCL and then assessed by comparing levels of gate delays, gate counts, and transistor counts of the resulting designs. The methods are illustrated to produce fundamental logic functions, and a full adder with reduced critical path delay and transistor count over various alternative gatelevel synthesis approaches. As an example of circuits employing feedback, TCR is applied to derive time and space optimized increment circuits for a 4-bit up-counter. Results demonstrate support for a variety of optimizations utilizing conventional Boolean minimization followed by table-driven gate substitutions. Whereas previous work on optimization of circuits constructed from logical operators has concentrated on transistorsizing [25] and decomposition of high fan-in operators [26], this chapter will emphasize composable circuit construction utilizing a set of complex state-holding gates, and will illustrate circuit minimization techniques, their application, and associated tradeoffs.

## 3.1 Chapter Outline

This chapter is organized into five sections. In Section 3.2, the TCR method for optimizing combinational NCL circuits is developed. The method is demonstrated in Sections 3.3, 3.4, and 3.5. Section 3.3 presents optimal input-complete AND/NAND, OR/NOR, and XOR/NXOR logic functions, designed using TCR. Section 3.4 applies TCR to produce a delay-insensitive Full Adder that significantly reduces critical path delay and transistor count over previous gate-level delay-insensitive approaches.

Section 3.5 illustrates the use of TCR to derive a variety of time and space optimized NCL increment circuitries for an up-counter with a feedback circuit.

## 3.2 TCR Method Definition

As depicted in Figure 24, the design process begins with a specification of the circuit functional behavior and desired optimization criteria. Circuit behavior is specified as Boolean logic expressions, truth tables, and/or narrative descriptions. The optimization criteria include parameters such as critical path delay, gate count, transistor count, or power consumption, that are to be minimized in the target design. Several alternate designs are generated, which are then assessed against the optimization criteria, allowing the preferred design to be selected for implementation.

First, a logic encoding scheme is selected such as dual-rail, quad-rail, or other MEAG representations, as depicted in Figure 24. Typically either dual-rail or quad-rail is chosen since these encodings yield the minimum of two wires per bit. If a dual-rail encoding is used, the next step is to select the optimization space in which minimization

will be performed. The proposed TCR design methods have been numbered "1", "2", and "3", each with design steps labeled "A", "B", or "C", appropriately.

Figure 24. TCR design flow.

## 3.2.1 Method 1: Incomplete Functions

As depicted in Figure 24, Method 1 corresponds to Boolean optimization.

Maximal use of incomplete NCL logic functions, such as the incomplete AND function shown in Figure 10, generates the individual outputs, while maintaining the completeness of input criterion for the circuit as a whole. For example, gates in Boolean designs that target the basic logical operators (AND, OR, XOR, NAND, NOR, NXOR, NOT) are directly mapped to a NCL design by using as many incomplete NCL functions as possible. As described in Step 1A of Figure 24, each Boolean gate is replaced with its NCL equivalent function, using incomplete versions whenever possible. Step 1B ensures input-completeness for the circuit as a whole by employing complete functions only for selected gates in the data path, so that the computation of an entire output set implies that the complete input set has arrived. The observability criterion must also be ensured.

## 3.2.2 Method 2: Dual-Rail Optimizations

Method 2 is based on dual-rail optimization. In Step 2A, the NCL circuit is optimized by using reduced minterm expressions for both rails of the output. These expressions are then mapped to TH1n and THnn gates. As in Boolean circuits, a Karnaugh map can be constructed for each output. The  $\theta s$  in the Karnaugh map refer to a signal's  $rail^{\theta}$  line and the  $\theta s$  refer to a signal's  $rail^{\theta}$  line. Reduced minterm expressions for both the  $\theta s$  and  $\theta s$  in the Karnaugh map are derived. After these expressions for the outputs have been obtained, an assessment must be made to ensure that the complete output set cannot be generated without all of the inputs being present. If under any timing

scenario, a complete output set can be generated without all of the inputs being present, the missing logic terms must be added to the reduced expressions to guarantee that the completeness of input criterion holds. This method will always generate two-level logic, given that threshold gates with a sufficiently large number of inputs are available. The first level will consist of THnn gates, to produce the required minterms; and the second level will consist of TH1n gates, which act to OR the minterms together to produce the desired outputs. Step 2A is similar to Anantharaman's approach [7] and DIMS [9]. In Step 2B, the common sub-expressions are factored and consolidated to reduce the gate count. Finally, the factored expressions for each rail are manipulated in Step 2C to obtain equations of the forms contained in Table III. The observability criterion must be ensured for every circuit output from Steps 2A, 2B, and 2C.

Table III lists the 27 transistor networks, along with their corresponding Boolean equations, used to construct NCL circuits. These 27 transistor networks, implemented as macros, constitute the set of all functions consisting of four or fewer variables. Since each rail of a NCL signal is considered a separate variable, a four variable function is not the same as a function of four literals, which would normally consist of eight variables.

Twenty four of these macros can be realized using complex threshold gates, identical to the standard threshold gate forms for functions of four or fewer variables [27, 28, 29].

The other three macros could be constructed from threshold gate networks, but have been implemented as transistor networks to provide completeness. Table III also contains the transistor count for these 27 macros.

Table III. 27 NCL macros.

| NCL Macro | Boolean Function            | <b>Transistor Count</b> |

|-----------|-----------------------------|-------------------------|

| TH12      | A + B                       | 6                       |

| TH22      | AB                          | 12                      |

| TH13      | A + B + C                   | 8                       |

| TH23      | AB + AC + BC                | 18                      |

| TH33      | ABC                         | 16                      |

| TH23w2    | A + BC                      | 15                      |

| TH33w2    | AB + AC                     | 14                      |

| TH14      | A + B + C + D               | 10                      |

| TH24      | AB + AC + AD + BC + BD + CD | 27                      |

| TH34      | ABC + ABD + ACD + BCD       | 26                      |

| TH44      | ABCD                        | 20                      |

| TH24w2    | A + BC + BD + CD            | 23                      |

| TH34w2    | AB + AC + AD + BCD          | 22                      |

| TH44w2    | ABC + ABD + ACD             | 23                      |

| TH34w3    | A + BCD                     | 19                      |

| TH44w3    | AB + AC + AD                | 16                      |

| TH24w22   | A + B + CD                  | 18                      |

| TH34w22   | AB + AC + AD + BC + BD      | 22                      |

| TH44w22   | AB + ACD + BCD              | 24                      |

| TH54w22   | ABC + ABD                   | 18                      |

| TH34w32   | A + BC + BD                 | 17                      |

| TH54w32   | AB + ACD                    | 20                      |

| TH44w322  | AB + AC + AD + BC           | 20                      |

| TH54w322  | AB + AC + BCD               | 21                      |

| THxor0    | AB + CD                     | 20                      |

| THand0    | AB + BC + AD                | 20                      |

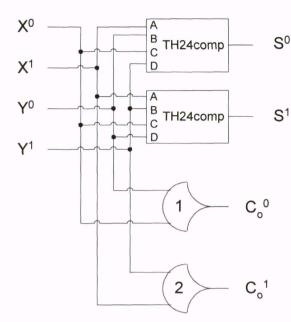

| TH24comp  | AC + BC + AD + BD           | 18                      |

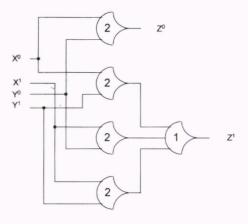

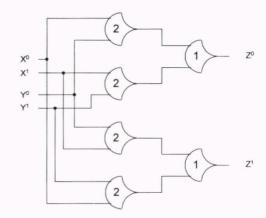

# 3.2.3 Method 3: Quad-Rail Optimizations

For some circuits, it may be advantageous to use quad-rail optimization, referred to as Method 3 in Figure 24. Two dual-rail signals yield the same five logic states as one quad-rail signal, however using quad-rail logic signals may lead to a more efficient design. Quad-rail optimization follows the same steps as does dual-rail optimization. In Step 3A, the NCL circuit is optimized by using reduced minterm expressions for all four rails of the output. These expressions are then mapped to TH1n and THnn gates. As in

dual-rail optimization, a Karnaugh map can be constructed for each output, but instead of only 0s and 1s, corresponding to a signal's  $rail^0$  and  $rail^1$ , respectively, the K-map also contains 2s and 3s, which correspond to a signal's  $rail^2$  and  $rail^3$ , respectively. Reduced minterm expressions for the 0s, 1s, 2s, and 3s in the Karnaugh map are derived. After these expressions for the outputs have been obtained, an assessment must be made to ensure that the complete output set cannot be generated without all of the inputs being present. If under any timing scenario, a complete output set can be generated without all of the inputs being present, the missing logic terms must be added to the reduced expressions to guarantee that the completeness of input criterion holds. This method will always generate two-level logic, given that threshold gates with a sufficiently large number of inputs are available. The first level will consist of THnn gates, to produce the required minterms; and the second level will consist of TH1n gates, which act to OR the minterms together to produce the desired outputs. In Step 3B, the common subexpressions are factored and consolidated to reduce the gate count. Finally, the factored expressions for each rail are manipulated in Step 3C to obtain equations of the forms contained in Table III. The observability criterion must be ensured for every circuit output from Steps 3A, 3B, and 3C.

#### 3.2.4 Performance Assessment

To assess the performance of alternate designs, Synopsys, a commercial design tool, was used to simulate the circuits to generate their timing characteristics. All NCL circuits presented herein have been exhaustively tested and their average cycle time,  $T_{DD}$ ,

has been reported. The Synopsys technology library for the 27 macros is based on Spice simulations of static 0.25 µm CMOS gates, operating at 3.3V. Along with the average cycle time, the number of gates and transistors has also been tabulated for comparison. The design that best meets the desired criteria can then be selected for implementation.

# 3.3 Application to Input-Complete Fundamental Logic Functions

Several optimizations can be used to generate designs that are very competitive in terms of speed and area as compared to other self-timed approaches. For example, Figures 11, 25, and 26 show the conventional implementations of the logic functions: AND, OR, and XOR, respectively. Each of these may be obtained directly from their minterm form. Method 2 is readily applicable. Dual-Rail Encoding Optimization achieves significant reduction in both area and speed. TCR Step 2C can be applied directly from the minterm form to reduce the circuit complexity and improve performance. Specifically, consider the objective of realizing an optimized input-complete 2-input OR function: Z = X + Y. The minterm expression for  $Z^0$  is given by:  $Z^0 = X^0Y^0$ , which directly maps to a TH22 gate in Table III. The minterm expression for  $Z^{l}$  is given by:  $Z^1 = X^1Y^1 + X^0Y^1 + X^1Y^0$ , which directly maps to a TH and 0 gate. Similarly, an optimized input-complete 2-input AND function:  $Z = X \bullet Y$  can be realized. The minterm expression for  $Z^0$  is given by:  $Z^0 = X^0Y^0 + X^0Y^1 + X^1Y^0$ , which directly maps to a THand0 gate. The minterm expression for  $Z^{l}$  is given by:  $Z^{1} = X^{1} Y^{1}$ , which directly maps to a TH22 gate. The derivation of an optimized 2-input XOR function:  $Z = X \oplus Y$ is a bit more complex. The minterm expression for  $Z^0$  is given by:  $Z^0 = X^0Y^0 + X^1Y^1$ ,

which directly maps to a THxor0 gate. The minterm expression for  $Z^I$  is given by:  $Z^1 = X^1Y^0 + X^0Y^1$ , which also directly maps to a THxor0 gate. However, two transistors can be eliminated for each rail of Z by adding the two *don't care* terms, representing the cases when both rails of either X or Y are simultaneously asserted. The new equations for  $Z^0$  and  $Z^I$  are as follows:  $Z^0 = X^0Y^0 + X^1Y^1 + X^0X^1 + Y^0Y^1$  and  $Z^1 = X^1Y^0 + X^0Y^1 + X^0X^1 + Y^0Y^1$ , both of which now map to TH24comp gates.

Figure 25. Conventional input-complete OR function: Z = X + Y.

Figure 26. Conventional input-complete XOR function:  $Z = X \oplus Y$ .

As shown in Table IV, the AND, OR, and XOR functions produced using TCR outperform the conventional minterm designs in terms of both area and throughput. In particular, the TCR optimized AND and OR functions are 2.2-fold faster and require 43% fewer transistors than the conventional minterm designs. Furthermore, the optimized XOR function is 2.3-fold faster and requires 40% fewer transistors than the conventional minterm design. The inverse logic functions, NAND, NOR, and NXOR, can easily be

attained by exchanging the output rails of the AND, OR, and XOR functions, respectively.

Table IV. Performance characteristics of input-complete NCL logic functions.

| Complete AND | Component List   | Gate Delays | <b>Gate Count</b> | <b>Transistor Count</b> | T <sub>DD</sub> |

|--------------|------------------|-------------|-------------------|-------------------------|-----------------|

| Conventional | 4xTH22, 1xTH13   | 2           | 5                 | 56                      | 1.58 ns         |

| TCR Method 2 | 1xTHand0, 1xTH22 | 1           | 2                 | 32                      | 0.71 ns         |

| Complete OR  | Component List   | Gate Delays | <b>Gate Count</b> | <b>Transistor Count</b> | T <sub>DD</sub> |

|--------------|------------------|-------------|-------------------|-------------------------|-----------------|

| Conventional | 4xTH22, 1xTH13   | 2           | 5                 | 56                      | 1.58 ns         |

| TCR Method 2 | 1xTHand0, 1xTH22 | 1           | 2                 | 32                      | 0.71 ns         |

| XOR          | Component List | Gate Delays | <b>Gate Count</b> | <b>Transistor Count</b> | T <sub>DD</sub> |

|--------------|----------------|-------------|-------------------|-------------------------|-----------------|

| Conventional | 4xTH22, 2xTH12 | 2           | 6                 | 60                      | 1.70 ns         |

| TCR Method 2 | 2xTH24comp     | 1           | 2                 | 36                      | 0.75 ns         |

## 3.4 Application to Full Adder

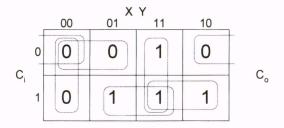

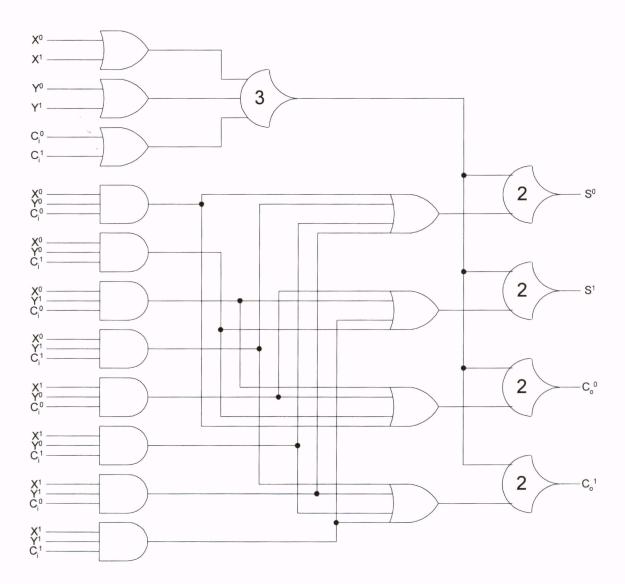

The truth table for a full adder circuit is shown in Figure 27, where X and Y denote the input addends and  $C_i$  denotes the carry input. S and  $C_o$  denote the sum and carry output, respectively. This circuit can be extensively optimized using TCR Method 2. Applying TCR Step 2A, the K-map for the  $C_o$  output is obtained as shown in Figure 28, yielding:  $C_o^0 = X^0Y^0 + C_i^0X^0 + C_i^0Y^0$  and  $C_o^1 = X^1Y^1 + C_i^1X^1 + C_i^1Y^1$ . Both functions directly map to a TH23 gate, so factoring in Step 2B is not necessary. Since a TH23 gate does not produce an output which is complete with respect to any of its inputs, there must be another output or set of outputs that enforce the completeness of input criterion. As explained below, the sum output, S, will enforce the completeness of input criterion for the circuit as a whole, thus allowing the carry output to be incomplete.

| X | Υ | Ci | Со | S |

|---|---|----|----|---|

| 0 | 0 | 0  | 0  | 0 |

| 0 | 0 | 1  | 0  | 1 |

| 0 | 1 | 0  | 0  | 1 |

| 0 | 1 | 1  | 1  | 0 |

| 1 | 0 | 0  | 0  | 1 |

| 1 | 0 | 1  | 1  | 0 |

| 1 | 1 | 0  | 1  | 0 |

| 1 | 1 | 1  | 1  | 1 |

Figure 28. K-map for  $C_o$  output of full adder.

Figure 27. Truth table for full adder.

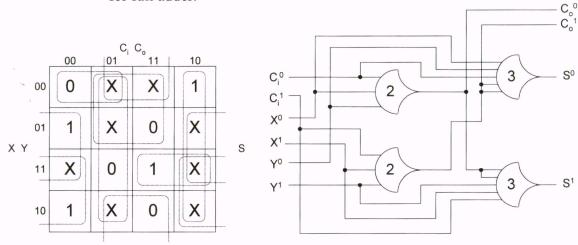

Figure 29. K-map for S output of full adder. Figure 30. Optimized NCL full adder [21].

The K-map for S, based on X, Y,  $C_i$ , and the intermediate output  $C_o$ , is shown in Figure 29, with essential prime implicants covered. This cover yields:  $S^0 = C_o^{-1}X^0 + C_o^{-1}Y^0 + C_o^{-1}C_i^{-0} + X^0Y^0C_i^{-0} \text{ and } S^1 = C_o^{-0}X^1 + C_o^{-0}Y^1 + C_o^{-0}C_i^{-1} + X^1Y^1C_i^{-1}, \text{ both of which directly map to TH34W2 gates, so factoring in Step 2B is not necessary. <math>C_o$  is taken as the A input such that  $W(C_o) = 2$ , as shown in Figure 30. Checking input-completeness, the carry output requires at least two inputs to be generated and the sum output requires either the carry output and one more input, or all three inputs to be

generated; so all three inputs are needed to generate the sum output. Therefore, the completeness of input criterion holds for the circuit as a whole.

As shown in Table V, the NCL design of the full adder produced using TCR optimizations can outperform those of other delay-insensitive methods, such as Anantharaman's and DIMS, Seitz's, David's, and Singh's approaches, shown in Figures 31, 32, 33, and 34, respectively. Here n-input C-elements are drawn as THnn gates since their functionality is identical. The NCL design has far fewer gates and transistors, while requiring fewer logic levels to produce the carry output,  $C_o$ . NCL also requires fewer logic levels to produce the sum output, S, than three of the five other methods, and has the same number of logic levels for S as the other two. Notice that the NCL full adder uses the carry output as an input to compute the sum output, whereas the other methods compute the sum and carry outputs independently. This is because for the other methods it is not practical to use the carry output to help generate the sum output. For the other methods the carry output is generated in the same number of logic levels, or more, as the sum output. Therefore, to use the carry output as an input for calculating the sum output would require more logic levels, as well as more gates. Besides NCL, only Seitz's full adder can be designed such that  $C_0$  can be computed before the  $C_i$  input is known for the cases A = DATA0, B = DATA0 and A = DATA1, B = DATA1. This optimization is important if the full adder component is to be used in an N-bit ripple-carry addition; since it allows the addition to be performed in  $O(\log_2 N)$  on average instead of O(N). This optimization could be applied to DIMS, Anantharaman's approach, and David's method,

if their signaling scheme was slightly changed such that it coincided with the "weak conditions" of delay-insensitive signaling defined by Seitz [4] and used by NCL.

Table V. Full adder using various delay-insensitive methods.