# STARS

University of Central Florida

STARS

**Retrospective Theses and Dissertations**

1986

# Multiprocessor scheduling with practical constraints

Kenneth Burton Donovan University of Central Florida

Part of the Computer Sciences Commons Find similar works at: https://stars.library.ucf.edu/rtd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Retrospective Theses and Dissertations by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS Citation**

Donovan, Kenneth Burton, "Multiprocessor scheduling with practical constraints" (1986). *Retrospective Theses and Dissertations*. 4901. https://stars.library.ucf.edu/rtd/4901

#### MULTIPROCESSOR SCHEDULING WITH PRACTICAL CONSTRAINTS

by

#### KENNETH BURTON DONOVAN

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science the University of Central Florida Orlando, Florida

### May 1986

Major Professor: Dr. Amar Mukherjee

#### ABSTRACT

The problem of scheduling tasks onto multiprocessor systems has increasing practical importance as more applications are being addressed with multiprocessor systems. Actual applications and multiprocessor systems have many characteristics which become constraints to the general scheduling problem of minimizing the schedule length. These practical constraints include precedence relations and communication delays between tasks, yet few researchers have considered both these constraints when developing schedulers.

This work examines a more general multiprocessor scheduling problem, which includes these practical scheduling constraints, and develops a new scheduling heuristic using a list scheduler with dynamically computed priorities. The dynamic priority heuristic is compared against an optimal scheduler and against other researchers' approaches for thousands of randomly generated scheduling problems. The dynamic priority heuristic produces schedules with lengths which are 10% to 20% over optimal on the average. The dynamic priority heuristic performs better than other researchers' approaches for scheduling problems with the practical constraints. We conclude that it is important to consider practical constraints in the design of a scheduler and that a simple heuristic can still achieve good performance in this area.

#### ACKNOWLEDGMENTS

I would like those who helped me - my family, my teachers, my work colleagues and my friends. I am very grateful to General Electric, especially all my managers who were flexible with finances and work schedules to support my graduate studies. Dr. Mukherjee and my graduate committee have provided continual assistance as I developed an initial concept into a complete dissertation. And with my wife Martha, who has offered support and encouragement in all my efforts, I share this accomplishment which came from us both.

## TABLE OF CONTENTS

| LIST OF TABLES                                      | V                          |

|-----------------------------------------------------|----------------------------|

| LIST OF FIGURES                                     | vi                         |

| CHAPTER 1 PRACTICAL MULTIPROCESSOR SCHEDULING       | 1<br>1<br>2<br>23          |

| CHAPTER 2 REVIEW OF RELATED WORK                    | 28<br>28<br>31<br>33<br>36 |

| CHAPTER 3 SCHEDULING ALGORITHMS                     | 46<br>47<br>61<br>73<br>79 |

| CHAPTER 4 SCHEDULING ALGORITHM RESULTS AND ANALYSES | 87<br>87<br>89<br>109      |

| 5.1 Dissertation Summary                            | 119<br>119<br>122<br>124   |

| LIST OF REFERENCES                                  | 126                        |

# LIST OF TABLES

| 1. | Image Generation Tasks' Communication and Memory Requirements | 9  |

|----|---------------------------------------------------------------|----|

| 2. | Processor Execution Performance of Each Task                  | 17 |

| 3. | IPC for Normal and Pipeline Configuration                     | 18 |

| 4. | Scheduling Constraints Addressed by Previous Researchers      | 29 |

| 5. | Sequence of Events for Example Problem                        | 51 |

# LIST OF FIGURES

| 1.  | Example Geometry of Perspective Image Generation  | •  |    | • |  | • | 5  |

|-----|---------------------------------------------------|----|----|---|--|---|----|

| 2.  | Eight Tasks of Image Generation                   |    |    |   |  | • | 6  |

| 3.  | Multiprocessor Architecture for Image Generation  |    |    |   |  |   | 15 |

| 4.  | A Feasible Schedule for the Example Problem       |    |    |   |  |   | 22 |

| 5.  | A Better Schedule which Exploits Parallelism      |    |    |   |  |   | 24 |

| 6.  | Graph Theory Scheduling Approach                  |    |    |   |  |   | 32 |

| 7.  | Kartashev's Combined Resource Diagram             |    |    |   |  |   | 42 |

| 8.  | Four States of a Processor                        |    |    |   |  |   | 49 |

| 9.  | Optimal Scheduler Procedure                       |    |    |   |  |   | 63 |

| 10. | M-ary Allocation Tree of N Tasks                  |    |    |   |  |   | 65 |

| 11. | Find Next Allocation Subroutine                   |    |    |   |  |   | 67 |

| 12. | Find Next Sequence Subroutine                     |    |    |   |  |   | 70 |

| 13. | Next Sequence Subroutine                          |    |    |   |  |   | 72 |

| 14. | Constraint Relaxing Heuristic Procedure           |    |    |   |  |   | 76 |

| 15. | Modified Next Sequence Subroutine                 |    |    |   |  |   | 78 |

| 16. | Dynamic Priority Heuristic Procedure              |    |    |   |  |   | 83 |

| 17. | GET HIGH PRIORITY Subroutine for Dynamic Priority |    |    |   |  |   | 85 |

| 18. | Random Instances Created by Random Instance Gener | at | or | • |  |   | 90 |

| 19. | Optimal Scheduler Solution of Example Problem .   |    |    |   |  |   | 92 |

## LIST OF FIGURES

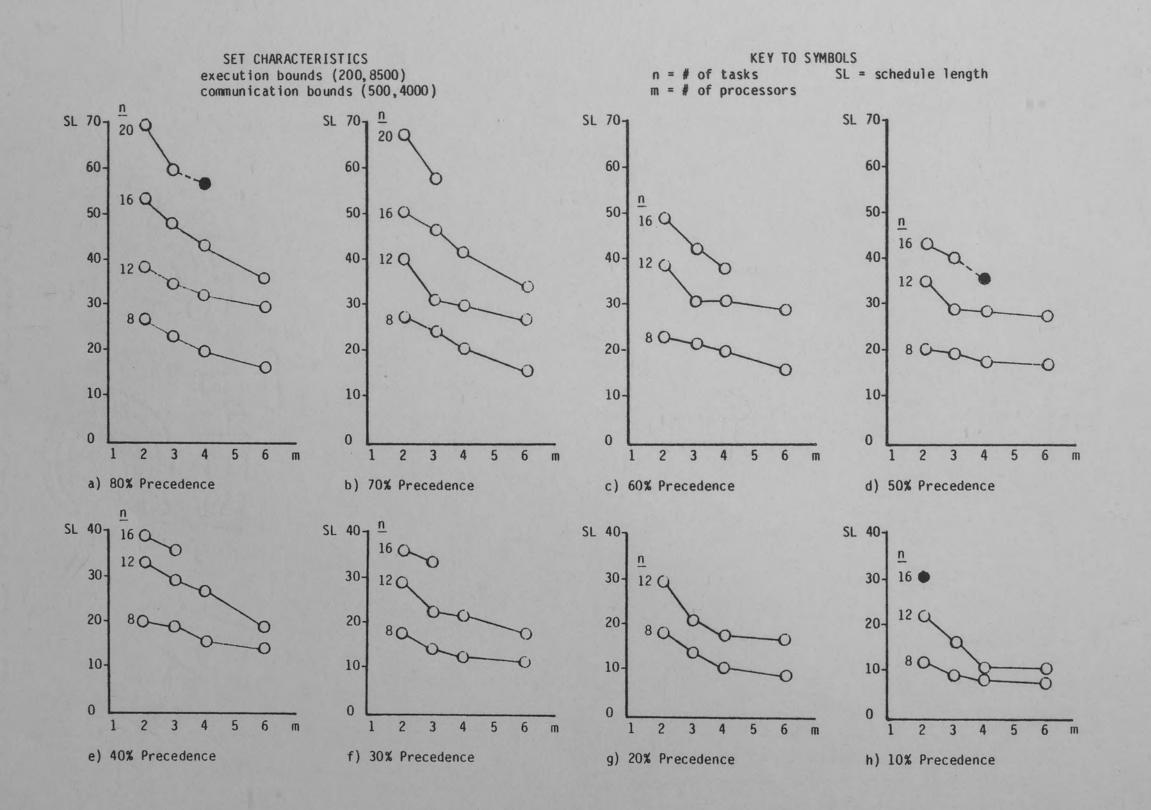

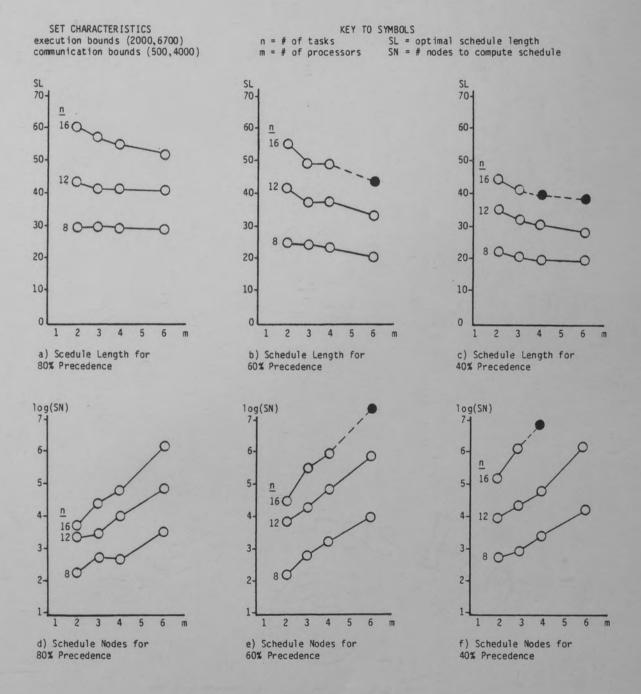

| 20. | Set 1 Optimal Schedule Length Results                        | 95  |

|-----|--------------------------------------------------------------|-----|

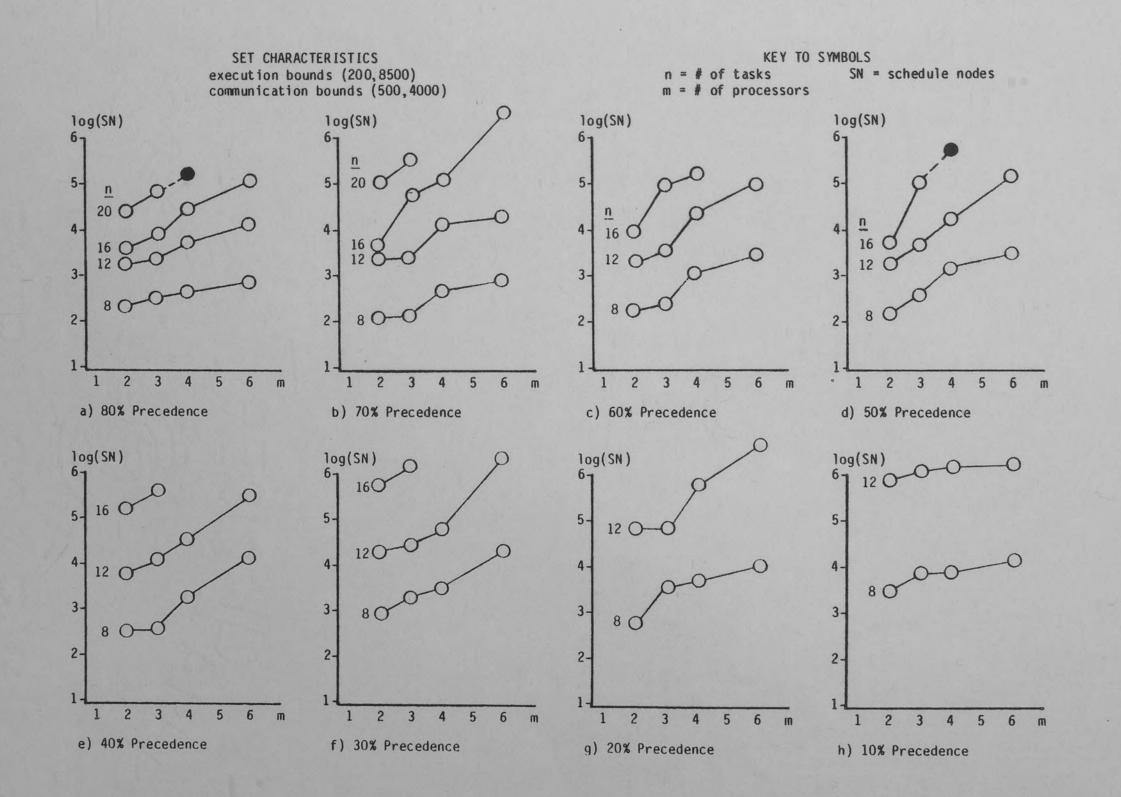

| 21. | Set 1 Optimal Schedule Node Results                          | 96  |

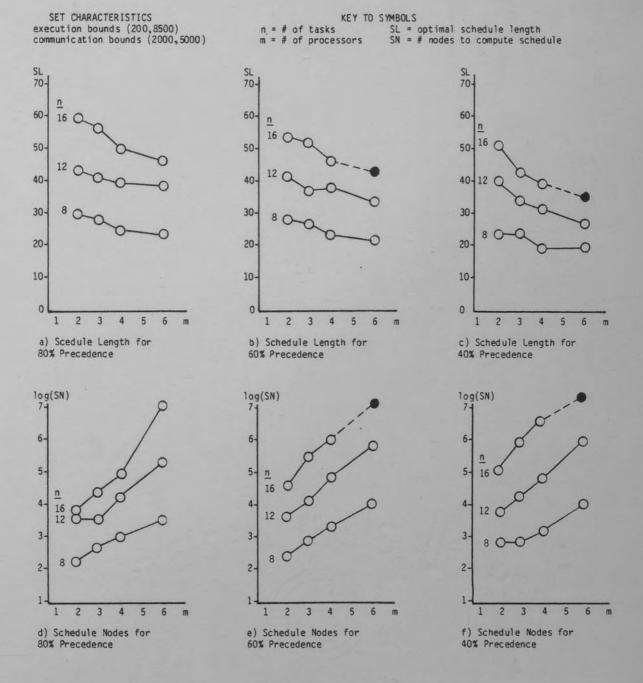

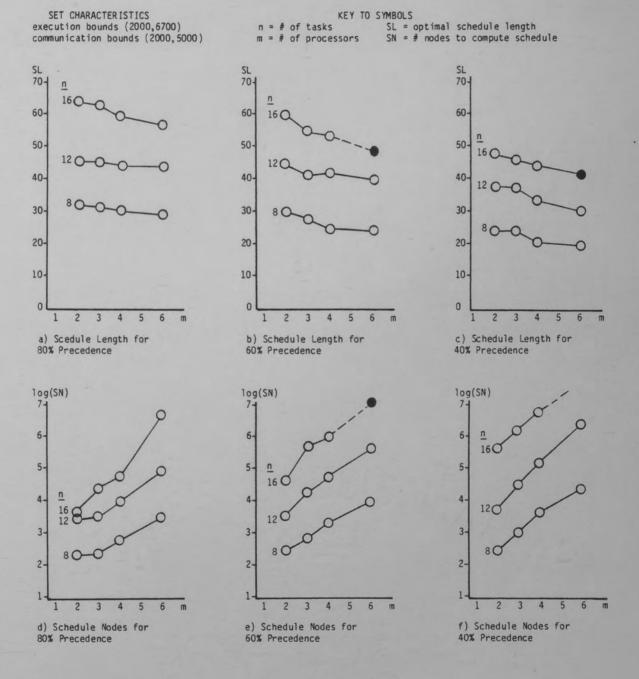

| 22. | Set 2 Optimal Results - More Communication Time              | 97  |

| 23. | Set 3 Optimal Results - Less Execution Variance              | 98  |

| 24. | Set 4 Optimal Results - More Communication, Less Execution . | 99  |

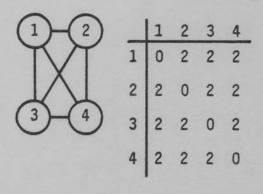

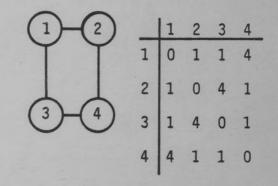

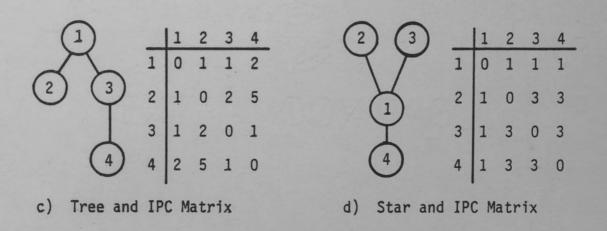

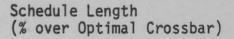

| 25. | Four Communication Configurations                            | 105 |

| 26. | Communication Configuration Schedule Length Comparison       | 108 |

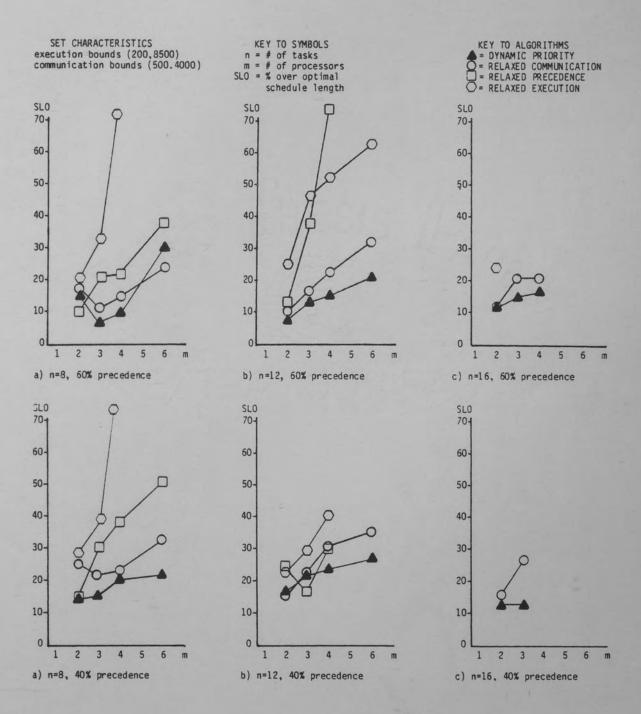

| 27. | Set 1 Heuristic Schedule Length Results                      | 112 |

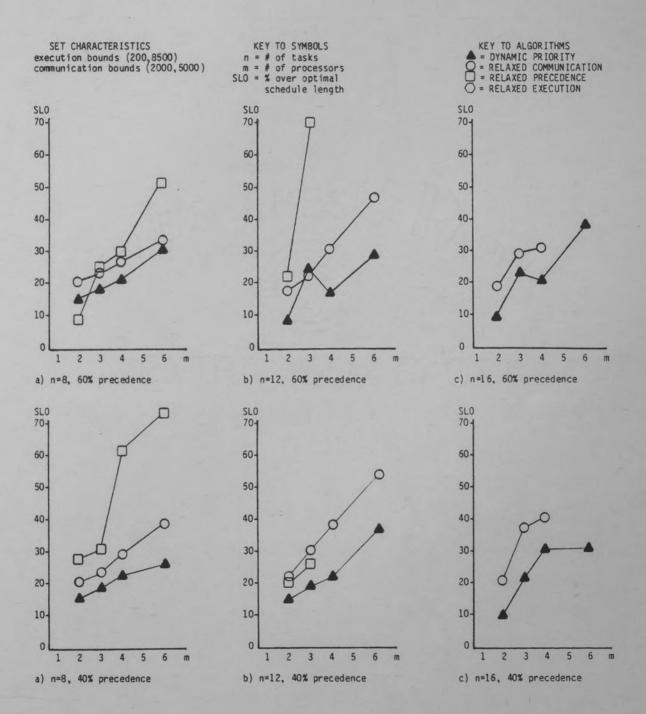

| 28. | Set 2 Heuristic Schedule Length Results                      | 113 |

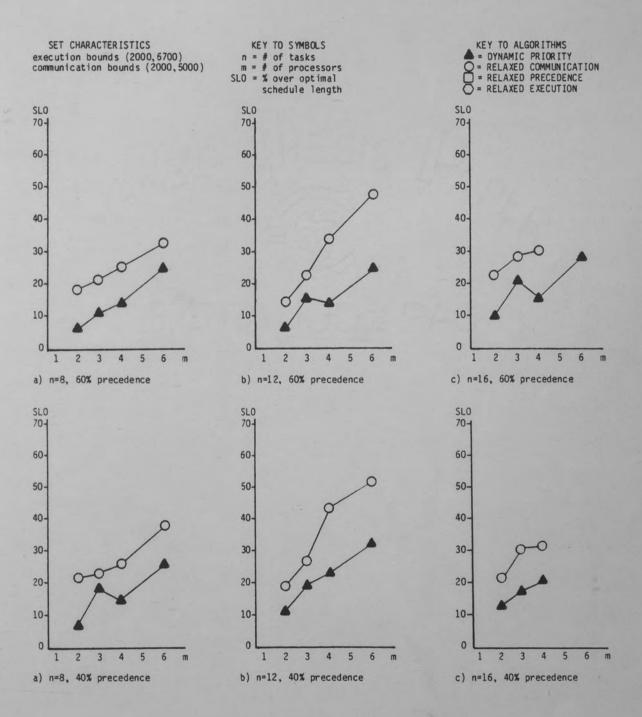

| 29. | Set 3 Heuristic Schedule Length Results                      | 114 |

| 30. | Set 4 Heuristic Schedule Length Results                      | 115 |

#### CHAPTER 1 PRACTICAL MULTIPROCESSOR SCHEDULING

#### 1.1 Scope

Multiprocessor systems are being considered for an increasing number of problem applications which demand large amounts of processing power. This trend is driven by the lower cost of individual processors which makes multiprocessor systems economical. However, the problem of scheduling processing tasks onto a multiprocessor system can severely limit the effective processing power of such systems. Thus, multiprocessor scheduling is becoming more important for actual systems.

The system designer must deal with the scheduling problem in a practical environment where the interaction between processing tasks can be complex. The classical work on the scheduling problem is not generally applicable because it does not consider many of the practical constraints found in real systems, such as task precedence, communication, or task deadlines. Some researchers are developing actual multiprocessor schedulers, but their ad hoc approach gives little direction for other systems.

In this dissertation, we formulate the practical multiprocessor scheduling problem in a systematic way and we develop schedulers which consider the practical constraints. We develop an optimal scheduling algorithm (with exponential time complexity) as a reference point and measure its performance, via simulation, over a variety of scheduling problem examples. We also develop and evaluate two heuristic approaches which consider the practical constraints. Our problem formulation and scheduler investigation should provide some guidance for the designers of future multiprocessor systems and schedulers. The analysis in the results section indicates which constraints are critical and should be considered when developing a multiprocessor schedule. The results also show that our heuristic which considers different practical constraints performs better than "optimal" schedulers which do not account for practical constraints.

#### 1.2 Problem Area and Example

Our problem area is scheduling tasks onto processors to satisfy the requirements of a given application. In Section 1.2.1 we discuss the types of applications we are concerned with and how we will represent an application as a collection of task modules with some constraints. In Section 1.2.2 we discuss multiprocessor architectures and how we will represent any architecture as a collection of processors with some constraints. Finally, in Section 1.2.3, we show how to formulate the scheduling problem in terms of the application and architecture representations.

#### 1.2.1 Classes of Applications under Consideration

The problem of multiprocessor scheduling occurs in a variety of applications. Weather prediction, ballistic missile defense, image generation, and image processing are among those commonly identified. We are primarily concerned with these kinds of problems which require "supersystem" processing power in excess of one billion operations per second (Transactions of Computers 1982; Computer 1980). These systems achieve this processing power through tightly coupled networks of processors in a variety of intercommunication configurations. The successful use of such a system depends on properly scheduling each processor to complete its work in coordination with the rest of the system. Because of this tight coupling between processors, inefficient scheduling techniques can cause many processors to become idle and severely degrade system performance. Therefore, the scheduling problem is especially critical for these applications.

These applications are normally represented as a collection of processes or task modules. Each task requires an amount of execution time, memory, and communication with other tasks. Precedence relations and deadlines govern the period during which the task must complete its processing.

We are concerned with deterministic scheduling in which the application has already been divided into a set of tasks and all of the task constraints (i.e., execution requirement, precedence, etc.) can be determined a priori. The assumption that this kind of information will

be obtainable is one reason that the class of applications is limited to supersystem-type problems. Such applications can justify the overhead costs involved in gathering this information which may require data flow analysis and test runs of the tasks. These types of applications are often scheduled deterministically in order to guarantee average and worst case behavior.

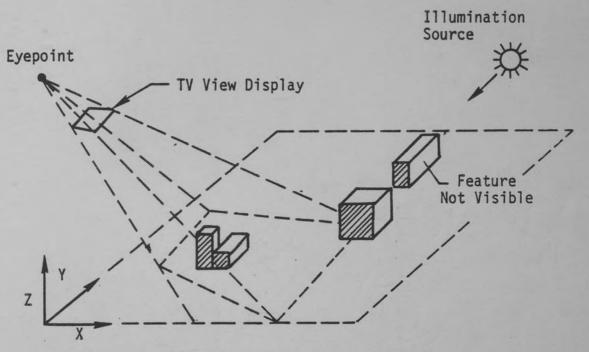

1.2.1.1 Example: Image Generation Application. We now define a simplified version of the image generation application to illustrate the constraints of the scheduling problem. We will refer to this example throughout the dissertation. The example function produces a perspective view of a data base of three-dimensional features, as shown in Figure 1. The inputs are the view window position and orientation, the sun illumination angle, and the data base features. For this example the features will be composed of planar faces where the face position is defined by the vertices of the face in Cartesian space. The output is a TV raster line display (512x512 pixels) which represents the perspective scene from the view window position. The view window and possibly the data base features can move, so a new image must be computed at a 60 hertz TV field rate (every 16 milliseconds).

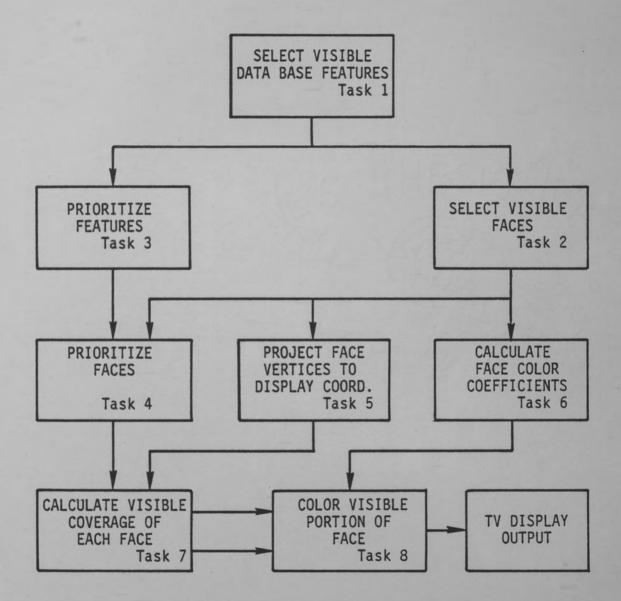

The image generation function is represented as eight tasks as shown in Figure 2. Task 1 (T1) searches through the data base to select the features which are potentially visible, as shown in Figure 1a. T2 then checks all faces of the selected features to determine which faces are potentially visible (i.e., T2 eliminates faces on the "back side"

Step B: Project Visible Faces into TV Display Coordinates.

Step C: Color Visible Portions of Visible Features.

Figure 1. Example Geometry of Perspective Image Generation.

Figure 2. Eight Tasks of Image Generation.

of the feature). T3 prioritizes the features by distance so that closer features appear in front of more distant features. Figure 1b shows this where the vertical box is closer than the horizontal box and therefore box has vertical higher priority. T4 performs a similar the prioritization on the individual faces of each feature. T5 projects the face vertices from the data base coordinate system (X,Y,Z) to the display coordinate system (pixel row and column). T7 uses the face vertex positions to determine which pixels are covered by the face. T7 also resolves overlapping faces using the priority defined by T4 (e.g., in Figure 1b portions of the horizontal box overlap with the vertical box, but the faces of the vertical box have higher priority and will be used to cover those pixels). T6 calculates the color coefficients for each face. These coefficients are then used by T8 to determine the shade of color for each pixel covered by a face. The color coefficients determine the fading and shading of the face due to distance and illumination angle. The output of T8 is the color intensities (R,G,B) for each pixel in the video memory.

The eight tasks of the image generation application have precedence constraints as indicated by the directed arcs in Figure 2. For example, T3 cannot start until T1 finishes, T4 cannot start until both T3 and T2 finish, etc. We use the double lines between T7 and T8 to indicate that tasks 7 and 8 can be executed in a pipeline fashion. This is where T8 can start working on an output of T7 before T7 has finished all outputs. Each task has an execution time constraint which is the time needed to execute the task. This is a function of both the number of processing steps to be performed and the rate of execution. Since the rate of execution can vary for different processors, we will defer defining the execution times of the example until the next section on processor architecture.

Each task has a requirement to use one or more processors concurrently. For this example, only one processor is required for each task. More than one processor could be specified for a single task when a task represents a special function which requires multiple processors. An example is a producer/consumer relationship between two processing functions. This can be modeled as a single "task" which requires two processors simultaneously.

Each task also has a deadline. The image generation function has a cycle time requirement of 16 millisec, which is represented by placing a 16 millisec external deadline on the last task, T8. Deadlines can then be propagated internally throughout the precedence tree by using the minimum execution times of each task. Other applications could have multiple external deadlines, such as when some intermediate results are required by another system at a particular time.

Another constraint on the tasks is the intertask communication requirement, or ITC. The ITC for the image generation tasks is given in Table 1a. T2 and T3 must receive 500 words from T1, T4 must receive 2000 words to T2, etc. This communication transfer will be defined to

## TABLE 1

# IMAGE GENERATION TASKS' COMMUNICATION AND MEMORY REQUIREMENTS

|              | A) INTERTASK COMMUNICATION<br>(WORDS) |     |         |           |      |      |   |      | <pre>B) TASK MEMORY     REQUIREMENTS     (WORDS)</pre> |                    |  |  |

|--------------|---------------------------------------|-----|---------|-----------|------|------|---|------|--------------------------------------------------------|--------------------|--|--|

| FROM<br>TASK | 1                                     | 2   | TO<br>3 | TASK<br>4 | 5    | 6    | 7 | 8    | TASK                                                   | MEMORY<br>REQUIRED |  |  |

| 1            | -                                     | 500 | 500     | 0         | 0    | 0    | 0 | 0    | 1                                                      | 1k                 |  |  |

| 2            |                                       | -   | 0       | 2000      | 2000 | 2000 | 0 | 0    | 2                                                      | 3k                 |  |  |

| 3            |                                       |     | -       | 500       | 0    | 0    | 0 | 0    | 3                                                      | 10k                |  |  |

| 4            |                                       |     | •       | -         | 0    | 1000 | 0 | 0    | 4                                                      | 10k                |  |  |

| 5            |                                       |     |         |           | -    | 1000 | 0 | 0    | 5                                                      | 10k                |  |  |

| 6            |                                       |     |         |           |      | -    | 0 | 1000 | 6                                                      | 15k                |  |  |

| 7            |                                       |     |         |           |      |      | - | 2000 | 7                                                      | 5k                 |  |  |

| 8            |                                       |     |         |           |      |      |   | -    | 8                                                      | 5k                 |  |  |

occur after the sender completes execution and immediately before the receiver starts execution. This implies that the sender is always of higher precedence than the receiver (i.e., the sender must be executed prior to the receiver). A zero ITC is allowed between two precedence related tasks, as in the case of output dependence where both tasks output to the same data area.

The amount of communication time required is related to the number of words in the ITC and the communication rate between processors. We normally define the communication rates so that if two tasks are coresident (i.e., they execute in the same processor) then no communication time is required. This is because the two tasks share the same processor memory and have immediate access to the data to be communicated. If the tasks are not coresident then the data must be transferred by the receiving processor from the sending processor according to the available communication rate. The communication rate will be discussed in the next section on processor architecture.

The final constraint we will consider for application tasks is the task memory requirement. This is shown in Table 1b where T1 requires 1k words, etc. This requirement can reflect the memory space needed for program code and/or data storage, depending on the application and architecture. For this example the figures given include both code and data since the processors defined in the next section have a single memory for both. The sum of the memory requirements of coresident tasks cannot exceed the processor memory capacity.

<u>1.2.1.2 Application Representation</u>. From the previous discussion, we will represent any application in the following terms:

- An application is a collection of tasks. Each task represents a processing function, similar to the concept of a subroutine.

- o The application tasks have several constraints:

- task precedence a task cannot begin execution until all tasks of higher precedence are completed.

- task execution time a task will require a fixed amount of time to execute on a given processor. Execution shall be nonpreemptive. The size of task execution time may vary between different processors.

- number of task processors a task will normally require one processor for execution. If more than one processor is required, the specified number of processors must be dedicated simultaneously to the given task.

- intertask communication requirement (ITC) the number of words which must be shared between two tasks. If tasks are not coresident then a period of communication time will be required between the processors executing the tasks.

- task memory size the number of words which must be allocated from a processor's memory space for the task. For the set of tasks scheduled on a given processor, the sum of the task memory sizes must fit within the processor memory capacity.

- task deadline the time limit for a task to complete execution. The time is measured from the start of the highest precedence task. The schedule length must be less than or equal to the deadline of the last task to complete execution.

This representation has intuitive appeal because these factors are considered in any system design process. As we will see in Chapter 2, however, current research in multiprocessor scheduling generally makes simplifying assumptions which eliminate some of these constraints. This representation does restrict the class of applications which will be able to take advantage of our scheduling work. The primary restriction is that all constraints must be deterministic to allow for a deterministic scheduling. We will see that most researchers in this area make a similar assumption. However, this assumption does require that the information defining the task constraints be gathered analytically or empirically. This process can be costly and time-consuming. Thus the class of applications is narrowed to those which can afford such overhead, and supersystem-type problems generally meet this condition.

#### 1.2.2 Computer Architectures under Consideration

There is a wide variety of computer architectures used to solve supersystem problems. Architectures are always composed of general purpose processors (e.g., a 16-bit floating point processor with a 16 k word memory), special purpose processors (e.g., a 64-point Fast Fourier Transform with a 256 k word staging memory), and communication paths between processors. Architectures can be application specific (e.g., a computer image generator), algorithm type specific (e.g., a vector processor), or general purpose (e.g., a reconfigurable architecture). We desire a model which can represent, at the system level, any type of architecture used to solve the targeted class of applications.

We represent an architecture by the performance of the individual processors on each task, the processor memory capacity, the "distance" (in time units) of communicating between each pair of processors, and the overhead time required when changing communication configurations. These characteristics or constraints effectively define any computer system for purposes of scheduling. The execution time required by a given task can vary on different processors to differentiate between general and special purpose processors in the system. The special purpose processor will normally have excellent performance with tasks for which it was intended and arbitrarily poor performance otherwise.

The communication "distances" are specified for each pair of processors and represent the number of time units required per word during a communication between the pair of processors. The distance values can be used to represent the presence (or absence) of communication paths and the efficiencies of dedicated paths versus the penalties of shared paths. A reconfigurable architecture would have a different set of communication distances for each possible configuration. By manipulating the distance values, many different architectures can be simulated because the primary difference between pipeline, array, and vector architectures is the time required for communication.

The final architecture constraint is the configuration overhead time. This reconfiguration time is used to model the overheads of setting up a pipeline or, for the case of a reconfigurable architecture, establishing the communication paths of a new configuration.

We will generally assume that these constraints are known, which is the case when the application is to be implemented on a specific

architecture. Natural extensions can be made to develop architecture designs which would be well-suited for a given subset of problems. One example extension would be to determine the minimum number of processors needed to maintain a feasible schedule. Another extension is to investigate different communication paths (e.g., star, shared bus, cluster) to determine which type works best for a given subset of problems.

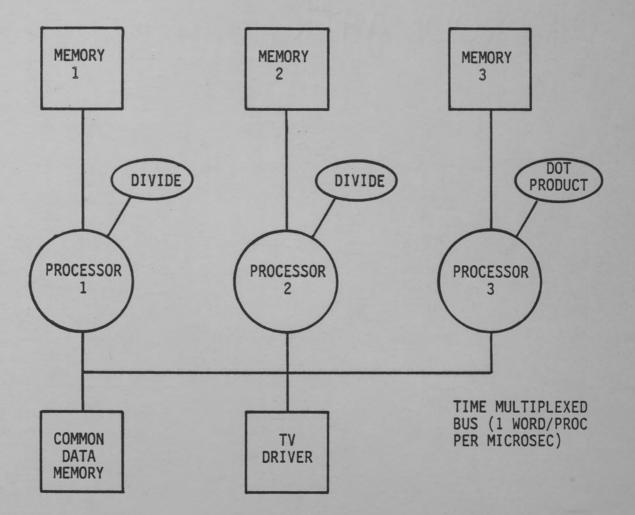

<u>1.2.2.1 Example: Image generation architecture</u>. The image generation application introduced in the last section is to be scheduled on the architecture shown in Figure 3. We will use this example to illustrate how we will represent an architecture in terms of processor performance, memory capacity, interprocessor communication distance and configuration change overhead.

The architecture has three processors which operate in either an independent or pipeline mode. These processors must use the inputs from the Data Memory to create the 512x512 pixel video memory image of the TV display. The 512x512 pixel video memory is also located in the Data Memory so that the TV Driver can access the data and drive the raster scan display.

The three processors are identical except for the hardware assist functions. Processor 1 (P1) and P2 are equipped with a divide function and P3 is equipped with a dot product function. Each 32-bit processor has a 64K word memory which holds the program code and working storage of all tasks to be executed on the processor. The basic execution rate

Figure 3. Multiprocessor Architecture for Image Generation.

is 5 million operations per second (MOPS) and the performance of the processors for each of the eight tasks is shown in Table 2. The difference in performance between Pl and P3 is due to the code mix of the tasks with respect to the hardware assist functions.

This performance table immediately shows that all tasks cannot execute on a single processor because the sum of execution times on any processor exceeds the deadline of 16 millisec (or 16000 microsec). Since more than one processor will be required to execute the eight tasks and the tasks have communication requirements, the interprocessor communication (IPC) time or distance becomes relevant. For the independent mode, we will assume that any processor can communicate with any other processor on the shared bus at a rate of one word every one microsec. Therefore, if X words are to be read by a task starting on P1 from a task which completed on P2, P1 must spend X microsec receiving the data from P2. The independent operation with the shared bus is shown in Table 3a by the IPC matrix where each processor is 1 microsec away from its neighbors.

As noted in the previous section, T7 and T8 can operate in a pipeline fashion where each output of T7 is allowed to be processed by T8. Table 3b shows the effective communication configuration used to implement the pipeline where the IPC has gone to zero. This reflects a configuration in which data is passed between processors over the bus during the task execution, so the time period used to transfer the block of data between T7 and T8 is not needed.

## TABLE 2

# PROCESSOR EXECUTION PERFORMANCE OF EACH TASK

| TASK  | PROCESSOR 1<br>(MICROSEC) | PROCESSOR 2<br>(MICROSEC) | PROCESSOR 3<br>(MICROSEC) |

|-------|---------------------------|---------------------------|---------------------------|

| 1     | 5000                      | 5000                      | 1500                      |

| 2     | 1500                      | 1500                      | 3000                      |

| 3     | 3000                      | 3000                      | 1500                      |

| 4     | 2500                      | 2500                      | 7500                      |

| 5     | 3000                      | 3000                      | 6000                      |

| 6     | 500                       | 500                       | 3000                      |

| 7     | 4500                      | 4500                      | 4500                      |

| 8     | 4500                      | 4500                      | 4500                      |

|       |                           |                           |                           |

| TOTAL | 24500                     | 24500                     | 31500                     |

## TABLE 3

#### IPC FOR NORMAL AND PIPELINE CONFIGURATION

A) IPC (MICROSEC) FOR INDEPENDENT CONFIGURATION B) IPC(MICROSEC) FOR PIPELINE CONFIGURATION

|                   | TO | PROCE | SSOR |                   | TO PROCESSOR |   |   |  |

|-------------------|----|-------|------|-------------------|--------------|---|---|--|

| FROM<br>PROCESSOR | 1  | 2     | 3    | FROM<br>PROCESSOR | 1            | 2 | 3 |  |

| 1                 | 0  | 1     | 1    | 1                 | 0            | 0 | 0 |  |

| 2                 | 1  | 0     | 1    | 2                 | 0            | 0 | 0 |  |

| 3                 | 1  | .1    | 0    | 3                 | 0            | 0 | 0 |  |

The example system does have an overhead penalty for entering the pipeline mode. The time required to effect such a configuration change for this system will be 500 microsec. This models the time lost to achieve synchronous pipeline operation and to fill the pipeline. The scheduler must decide whether to put T7 and T8 on the same processor, on two different processors in the independent configuration, or on a set of processors in a pipeline configuration (and incur the configuration change overhead).

<u>1.2.2.2 Architecture Representation</u>. From the previous discussion, we will represent any architecture in the following terms:

- o An architecture is a collection of processors.

- o The architecture made up of processors has several constraints:

- processor performance the performance of each processor is rated in terms of the time to execute each task. A special purpose processor will perform well with those tasks which use the special function.

- interprocessor communication (IPC) the amount of time required to transfer one word between two processors. The IPC is defined with different values for each configuration.

- configuration change the time overhead caused by changing the configuration, which changes the IPC.

- processor memory capacity the amount of memory available to each processor to satisfy the task memory requirements. We will assume that all tasks are loaded into the processor memory prior to the beginning of the application run.

Therefore the sum of the task memory requirements cannot exceed a processor's memory capacity.

This representation captures all of the architecture factors which influence scheduling. The class of architectures covered is generally unrestricted since any architecture can be defined in these terms for scheduling purposes.

1.2.3 The Multiprocessor Scheduling Problem under Consideration

For a given application and architecture which can be represented in the terms defined in the previous sections, we wish to develop a scheduling which satisfies all of the application and architecture constraints. We assume all constraints are known a priori so we can define a deterministic schedule. The schedule is to be nonpreemptive and is established prior to the start of execution by assigning each task to run on a particular processor.

Given a schedule and the task constraints (execution time, precedence, etc.) we can compute the exact start time of each task, and, therefore, we know the schedule length. The application requirements may be such that the goal is to find any feasible scheduling, rather than an optimal feasible scheduling which minimizes the schedule length.

We conclude this chapter by illustrating the scheduling problem for the image generation example and then more formally defining the scheduling problem in terms of the application and architecture constraints.

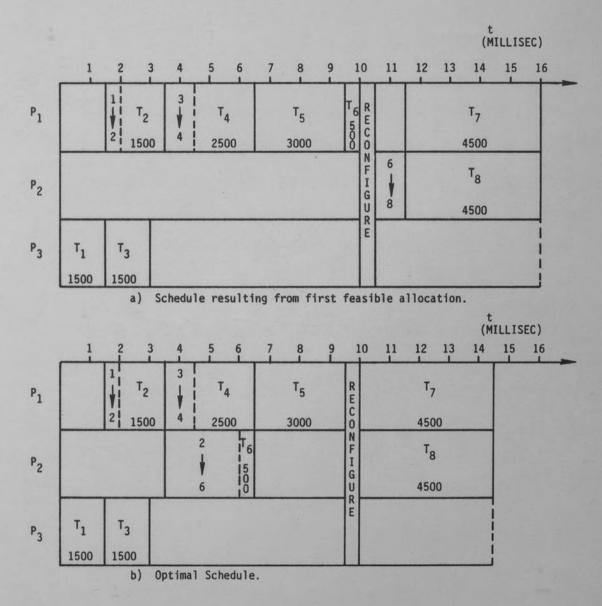

<u>1.2.3.1 Example: Image Generator Scheduling</u>. The image generator scheduling example deals with eight tasks to be executed by a three

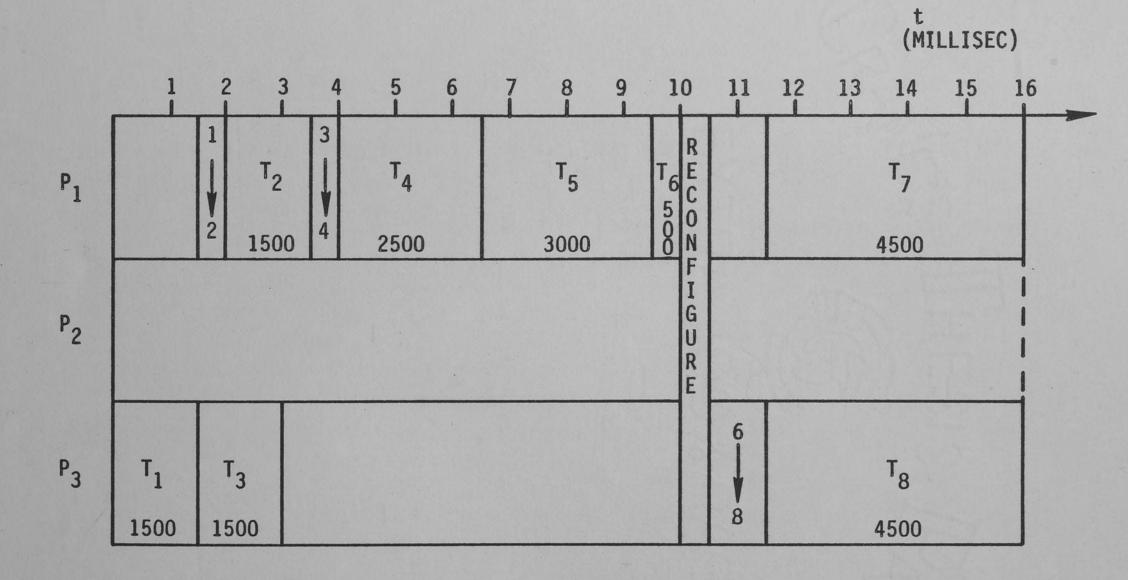

processor system in 16 millisec. Even this simplified problem is nontrivial and we could not guarantee an optimal solution without exercising our optimal scheduler developed later. These example schedules shown were developed manually, although the third schedule does minimize the schedule length, and is, therefore, optimal.

The simplest solution which minimizes communication time (to zero) is to schedule all tasks on a single processor. However this is not a feasible schedule since the execution time on any single processor is greater than 23 millisec (reference Table 2 for task execution times on each processor).

A second schedule, shown in Figure 4, was developed by scheduling tasks on those processors which have the best performance and which minimize communication time. This schedule is feasible since it finishes within 16 millisec. Examining this schedule in more detail, we see that task 1 (T1) is executed on Processor 3 (P3) to take advantage of P3's performance of 1500 microsec. Since T2 and T3 can be executed in parallel, and T2 runs faster on P1 than on P3, T2 is scheduled on P1 while T3 is placed on P3. However 500 microsec must be spent transferring data from P1 to P3. (reference Figure 2 for task precedence and Table 1 for ITC.) T4, T5 and T6 are also scheduled to run on P1 to reduce execution and communication times. The schedule concludes by changing the configuration to pipeline T7 and T8. This allows the two tasks to execute concurrently, but a 500 microsec change overhead is incurred and 1000 units of communication time is required for T8 to get data computed by T6.

KEY:  $T_1 = TASK 1$ ; 1 - 2 = Comm. from  $T_1$  to  $T_2$

Figure 4. A Feasible Schedule for the Example Problem.

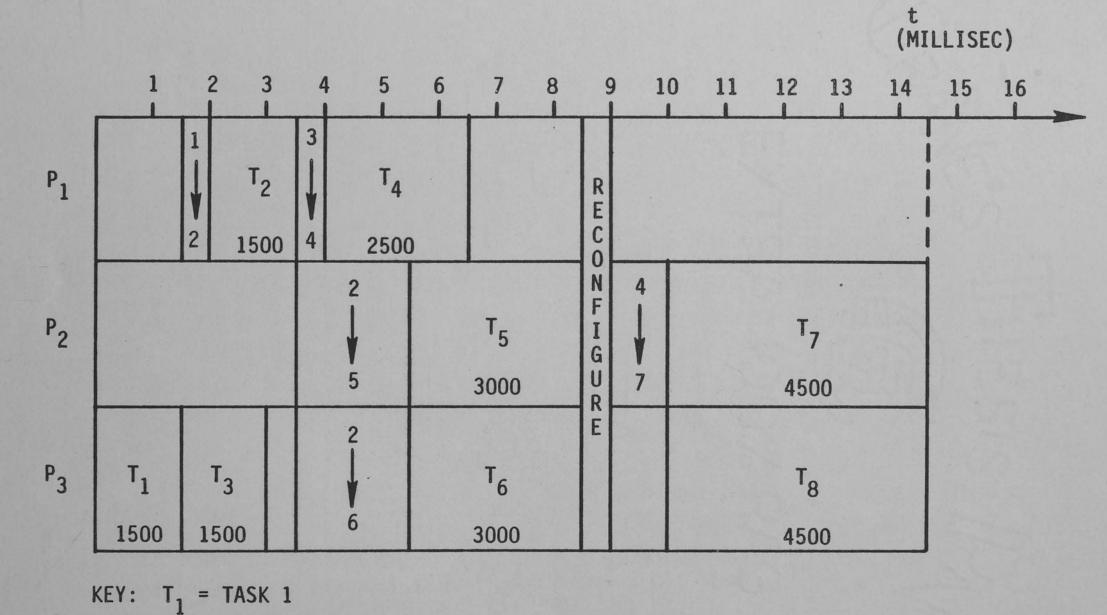

A third schedule is shown in Figure 5. This schedule is the shortest of the three. It has more execution time and communication time than either the first or second schedule. However it provides a better balance of running tasks on different processors to take advantage of performance, while reducing the communication overhead which does occur.

<u>1.2.3.2 Summary of the multiprocessor'scheduling problem</u>. From the discussion in the previous sections of the applications and architectures under consideration, the scheduling problem is stated as follows:

Given a set of tasks, a set of processors, and the following constraints:

- 1) task execution time per processor

- 2) task precedence relations

- 3) intertask communication requirement

- 4) task memory requirement and processor capacity

- 5) task execution deadlines

- 6) interprocessor communication cost

- 7) number of coprocessors required per task

- 8) configuration change overhead

- a.) Find a feasible schedule of the tasks on the processors, where a feasible schedule assigns each task to a processor, assigns at most one task to a processor at a time, and satisfies all constraints.

- b.) Find an optimal feasible schedule which minimizes the schedule length.

#### 1.3 Contents

The remaining chapters provide the background for this problem and describe the work which was performed. Chapter 2 reviews the related

$1-2 = COMMUNICATION OF T_1 TO T_2$

Figure 5. A Better Schedule with Exploits Parallelism.

work to see how others have approached this problem. We show that the body of reported work has considered only subsets of the general scheduling problem that we define.

Chapter 3 contains a formal definition of the scheduling problem and describes the three algorithms which we developed to solve the scheduling problem. The first algorithm considers all of the task and processor constraints. It is optimal in that it guarantees to find the feasible schedule with the shortest schedule length, or report failure if no feasible schedule exists. However, this optimal algorithm exhibits the exponential time complexity of the NP-hard scheduling problem and is not applicable for scheduling large numbers of tasks or processors.

The second algorithm is intended to simulate other scheduling algorithms which do not consider all the scheduling constraints. This "constraint relaxing" heuristic first develops a schedule without considering one or more of the scheduling constraints. Then the true performance of the "relaxed" schedule is computed by applying the relaxed schedule to the real problem, i.e., with all of the scheduling constraints. This algorithm is based on the optimal algorithm so that the relaxed schedule is "optimal" (for the problem with the relaxed constraint). However, the true performance is generally not optimal because some of the constraints had been ignored when creating the schedule. The third algorithm is the dynamic priority heuristic which considers all the practical scheduling constraints. The heuristic is based on priority list scheduling. The priorities are dynamically computed to guide the scheduler toward the "right" scheduling choices. This dynamic priority heuristic offers the polynomial time complexity needed for scheduling large numbers of tasks and processors.

Chapter 4 discusses the performance of these three algorithms. A problem generator is described which automatically creates scheduling problems to be solved. The optimal algorithm is evaluated for a variety of scheduling problems. The results indicate the problem sizes which can be solved using the optimal scheduler and also characterize the relationship between schedule constraints and optimal schedule length.

The constraint relaxing algorithm is evaluated to measure the performance of schedules which do not consider all practical constraints. The constraints of task precedence, communication delay, and variable task execution times are each relaxed. The schedule lengths are compared to the true optimal schedule lengths to quantify the effectiveness of other researchers' approaches when applied to scheduling problems with practical constraints.

The dynamic priority heuristic is measured against the previous two to determine how well it solves the multiprocessor scheduling problem. Although this heuristic is quite simple, it performs well because it considers the practical constraints. The performance of the dynamic priority heuristic is better than the constraint relaxing algorithm over a variety of scheduling problems. While the heuristic could be improved upon for a given application, it verifies that successful schedulers must consider the practical scheduling constraints in a systematic way.

Chapter 5 concludes this work with a discussion of the key characteristics of the scheduling problem and algorithms. We also suggest some direction for future work in this area of multiprocessor scheduling with practical constraints.

#### CHAPTER 2 REVIEW OF RELATED WORK

#### 2.1 Overview

This chapter reviews related research to show how others have attacked this problem of scheduling multiprocessor systems. Previous authors have provided a tutorial and bibliography of research approaches in this area, for example Chu (1980). Our primary concern is the types of constraints the different research approaches have considered. In particular, we will show that researchers have generally considered either precedence or communication constraints, but not both. We begin by a summary of how the previous work relates to our problem of multiprocessor scheduling with the practical constraints introduced in Chapter 1. We then provide an overview of representative work in each of three approaches to the scheduling problem:

- o Graph Theory

- o Integer Programming

- o Heuristics

Other approaches, such as analytical models (e.g., queueing theory) are not relevant because they do not consider communication or precedence constraints between tasks.

Table 4 shows how the reviewed work relates to our proposed research. Each previous work is summarized according to how the work dealt with the eight scheduling constraints listed in 1.2.3.2.

| T | A | B | L | E | 4 |

|---|---|---|---|---|---|

|   |   |   |   |   |   |

# SCHEDULING CONTRAINTS ADDRESSED BY PREVIOUS RESEARCHERS

| [                       | PREVIOUS RESEARCHERS (section reviewed) |                                 |                                        |                                   |                              |                                              |                                         |                                            |  |

|-------------------------|-----------------------------------------|---------------------------------|----------------------------------------|-----------------------------------|------------------------------|----------------------------------------------|-----------------------------------------|--------------------------------------------|--|

| SCHEDULE<br>CONSTRAINTS | GRAPH<br>THEORY<br>(2.2)                | INTEGER<br>PROGRAMMING<br>(2.3) | INT PROG<br>WITH<br>HEURISTIC<br>(2.3) | PRACTICAL<br>SCHEDULER<br>(2.4.1) | LOAD<br>BALANCING<br>(2.4.2) | AUTO-DESIGN<br>TASK<br>ARCHITECT.<br>(2.4.3) | DYNAMIC<br>ARCHITEC-<br>TURE<br>(2.4.4) | HI-SPEED<br>MULTI-<br>PROCESSOR<br>(2.4.4) |  |

| EXECUTE<br>TIME         | OPT                                     | OPT                             | ОРТ                                    | HEUR                              | HEUR                         | HEUR                                         | HEUR                                    | HEUR                                       |  |

| PRECEDENCE              |                                         |                                 |                                        | HEUR                              |                              | HEUR                                         |                                         | HEUR                                       |  |

| TASK<br>COMMUN.         | OPT                                     | OPT                             | OPT                                    |                                   | HEUR                         | HEUR                                         | HEUR                                    | HEUR                                       |  |

| TASK<br>MEMORY          |                                         | OPT                             | OPT                                    |                                   |                              | HEUR                                         | HEUR                                    |                                            |  |

| DEADLINES               |                                         |                                 | HEUR                                   | HEUR                              |                              |                                              | HEUR                                    |                                            |  |

| COMMUN.<br>DISTANCE     | OPT                                     | ОРТ                             | ОРТ                                    |                                   | HEUR                         | HEUR                                         |                                         |                                            |  |

| # PROC<br>PER TASK      |                                         |                                 |                                        |                                   |                              |                                              | HEUR                                    | HEUR                                       |  |

| CONFIG.<br>OVERHEAD     |                                         |                                 |                                        |                                   |                              |                                              | HEUR                                    | HEUR                                       |  |

KEY:

OPT - Researcher considered constraint using optimal approach. HEUR - Researcher considered constraint using heuristic approach.

The graph theory approach attempts to allocate the tasks onto processors by minimizing the execution and communication required using graph partitioning. This approach assumes all tasks are independent, so the task precedence constraint is not considered. This approach also does not consider the actual sequencing of the tasks on the processors, so is unable to consider deadline constraints or reconfiguration.

The integer programming approach deals with the classic task scheduling problem, with complications such as interprocessor communication and task memory. As with the graph theory approach, the integer programming formulation develops a partitioning of tasks onto processors in order to minimize the execution and communication required. This approach can consider interprocessor communication distances and memory constraints. However, it does not consider precedence or other sequence-related constraints.

The heuristic group of papers deal with a larger set of the scheduling constraints. One paper describes good heuristics for solving the scheduling problem with precedence constraints. Two of the papers discuss how to schedule tasks onto a general multiprocessor system with the communication constraint. The last two papers discuss how to execute a given set of algorithms on reconfigurable architectures. Between the five papers, all of our practical constraints are addressed in some fashion. However none of the papers address all of the constraints in a systematic fashion.

Our own work, defined in Chapter 3, investigates optimal and heuristic algorithms which consider all constraints. Note that none of the related work covers all of our constraints, and that the previous work with optimal schedules covers only a small subset. Our work, which considers all of the constraints in a systematic fashion, will be discussed in the next chapters. The rest of this chapter briefly reviews representative works in each of the three areas of previous research to identify the constraints addressed by the previous researchers.

### 2.2 Graph Theory Approach

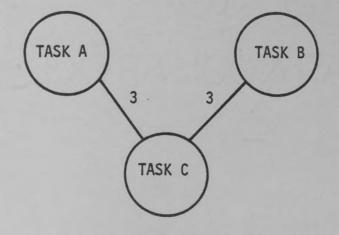

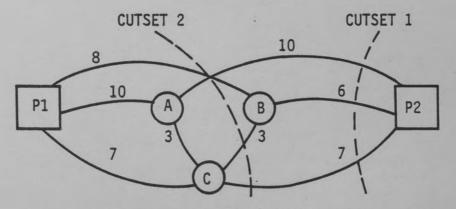

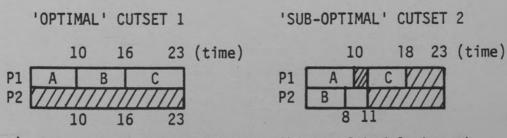

This approach selects a task allocation which produces a minimal cutset in a network flow graph (Stone 1977; 1978). The network flow graph represents the execution and communication costs of "flow requirement" as weighted edges connecting processors and tasks. Figure 6a shows three tasks, A, B, and C, where A and B both have a communication requirement with C. Figure 6b shows the addition to the graph of two processor nodes, P1 and P2. The weighted edges connecting task nodes with processor nodes specify the task execution time on the other processor. Therefore, an execution requirement of 8 for task B on processor P2 is represented by an edge from B to P1 with weight 8.

The minimal cutset (shown as 1 in Figure 6b) partitions the tasks onto the processors contained in the cutset. In this case, all of the tasks would be assigned to P1 with a total cost of 23.

a) Process Communication Requirements.

b) Process Communication and Execution Requirements. Two Cutsets are shown in dashed lines.

Sub-optimal Cutset Produces Shorter Schedule Length because of Concurrency.

Figure 6. Graph Theory Scheduling Approach.

This approach has serious drawbacks. The flow graph does not include precedence relationships between tasks to model the delay of a task waiting for another task. This approach also does not minimize the schedule length, or time to complete all processors. Figure 6c shows a "nonoptimal" cutset which reduces schedule time by increasing concurrency.

#### 2.3 Integer Programming Approaches

The research using this approach generally assumes a known multiple instruction, multiple data (MIMD) architecture and a set of tasks to be scheduled (allocated) onto the architecture. The problem is to allocate tasks onto processors to minimize the schedule time. The approaches develop an allocation by weighing requirements for task execution, intertask communication and processor load balancing.

The problem of task allocation, or task scheduling, has been investigated for over 20 years and the general problem is NP-hard (Coffman 1973). Thus, the work has concentrated on solving sub-problems (e.g., task with equal execution times or tasks in special precedence graphs) which allow a solution in polynomial time, measuring the effectiveness of heuristic methods (e.g., largest processing time first for independent tasks, list scheduling), or the effect of allowing preemption or processor sharing.

Practical work in this area followed the development of multiple processor systems for distributed information processing (Chen 1980;

Chu 1980) and for tightly coupled multiprocessor system (Efe 1982; Ma 1984). This work considers both processor execution time and interprocessor communication (IPC) time because communication can become the bottleneck in a real system.

This approach chooses a task allocation which minimizes a cost objective function. The cost objective function includes execution time and communication time, along with other application unique parameters such as storage cost for information systems. The objective function is then minimized using a branch and bound technique (BB).

Chen (1980) used this approach to design a distributed information system for a banking system. The input specification defined four cities as nodes which generated transactions, the transaction traffic, transaction processing and data base requirements, etc. Chen's integer programming model used BB to optimize an objective function with nine cost components (execution, storage, data base update, etc.) and eight constraints (communication line capacity, existence of data base, existence of a tasks on a computer, etc.). The solution output defined the optimal configuration of communication lines between cities, existence of computer and/or data base at cities, and the capacity of the system components.

Ma (1981; 1982; 1984) used the BB integer programming technique to allocate tasks to a distributed computing system. The inputs are a known MIMD system, a set of tasks, the execution requirement of each task, and the amount of intertask communication. The cost function, F, is a summation over the task execution times and the intertask communication. The objective is to find an allocation of tasks onto processors which minimizes the sum of the execution times and the communication times. This approach considers variable task execution times, nonhomogeneous processors, variable task communication times and nonhomogeneous communication rates, or "costs", between processors. The constraints include:

- a. the memory capacity of each processor must not be exceeded by the memory requirements of the tasks allocated to it.

- a task preference matrix specifies which tasks can execute on each processor.

- c. a task exclusive matrix specifies which tasks cannot be allocated to the same processor.

The output of the Ma's model is a task allocation which minimizes the cost objective function.

The main weakness in both these linear programming models is the exclusion of constraints on task dynamics such as precedence constraints or deadlines for tasks or task threads. As we showed with the graph theory approach, the model tends to group tasks on a few processors in order to minimize execution time and communication time. Thus, overhead is reduced at the expense of reducing concurrency. Ma attempts to compensate by introducing preference and exclusion matrices which force concurrency despite higher communication cost. Unfortunately, these matrices must be manually created which effectively requires part of the allocation to be specified manually, using ad hoc criteria.

# 2.4 Heuristic Approaches

In this section we examine five heuristics for the general multiprocessor scheduling problem. These heuristics consider at least task precedence or task communication in developing a task allocation.

# 2.4.1 Critical Path Extension Heuristic

Kasahara (1984) proposes an extension to the critical path heuristic called CP/MISF (critical path/most immediate successors first). This heuristic uses a list scheduling approach with the task priorities computed based on a critical path determination. If two or more tasks have the same critical path priority, a further prioritization is made based on the number of immediate successors (descendants). A task with more immediate successors is given higher priority. This heuristic is evaluated and the worst case error (i.e. the percentage over optimal length for the heuristic schedule length) is shown to be better than the standard critical path error. The average performance is also evaluated and shown to be in the range of 5% longer than optimal. Kasahara then develops a better heuristic scheduler by using the CP/MISF in a heuristic tree search algorithm (branch and bound type). This approach is effective for the scheduling problem with precedence and execution time constraints only. However many constraints, such as communication time and nonhomogeneous processors, are not addressed by Kasahara. This work is well supported and our own research approach described in Chapters 3 and 4 uses similar evaluation techniques.

#### 2.4.2 Load Balancing Heuristics

The heuristic methods of Efe (1982) and Stankovic (1985) choose a task allocation by trading the communication cost against the execution load balancing (i.e., the execution load of each processor). Efe proposes a deterministic scheduler which computes the schedule before task execution begins. Stankovic proposes a realtime scheduler which accepts random task arrivals and schedules the tasks onto available processors. Both techniques consider the same set of constraints as discussed later. Efe's approach is reviewed here.

A two-stage heuristic iterates until a "sufficient" solution is found. The first stage clusters the tasks to reduce intertask communication. The second stage reassigns certain tasks from overloaded processors to underloaded processors. The resulting allocation of tasks strikes a balance between the communication and processor load balancing.

The first stage, called the task clustering algorithm, is a heuristic which assigns tasks to processors so that intertask communication is reduced. A local search technique is used which iteratively clusters tasks with the most intertask communication. When the number of clusters will fit on the available processors, the clusters are assigned accordingly. Some provision is made for reserving certain processors for special tasks (similar to the preference matrix of Ma discussed in 2.3).

The second stage evaluates the load balancing by comparing each processor load to the theoretical average determined by the total serial task execution time and the number of processors. The processors which have acceptable loads are removed from the allocation problem along with the tasks assigned to those processors. The underloaded and overloaded processors will then be adjusted to get closer to the theoretical average.

A new problem is defined which consists of the underloaded processors, overloaded processors, task clusters from the underloaded processors, and individual tasks from the overloaded processors. The communication costs between an "underloaded cluster" and an "overloaded task" are then increased to encourage the migration of tasks to the underloaded processor. The size of the communication increase is proportional to the load difference between the processors. The new (hopefully reduced) problem is then used for another iteration of the heuristic. The heuristic terminates when all processors are acceptably balanced or the same assignment is found by two successive passes. The heuristic may not terminate.

The weakness of Efe's approach is that the model does not provide for delays from precedence constraints and communication. Also, the authors do not support the heuristic approaches by either theoretical analysis or empirical data. Stankovic's model is better supported and does provide for communication delays, however precedence constraints are also not considered.

### 2.4.3 Automated Design of Task-specific Architectures

Ward (1982) proposes a procedure for automatically designing a special purpose architecture which can execute a particular set of algorithms. The target applications are those where the high frequency of execution and the high speed requirements justify a special purpose machine. The goal is to automate the initial design process, and no attempt is made to produce machines capable of adapting to different algorithms.

The four steps in Ward's approach are:

- Extract parallel tasks from sequential programs and determine firing conditions.

- Allocate tasks to processors to meet time requirement.

- 3. Specify architecture using components from knowledge base.

4. Compile and load tasks into architecture.

The tasks are assigned to processors to maximize parallelism, i.e., so no two tasks on the same processor are ready for execution at the same time. Then the number of processors is reduced to minimize the system size and to reduce interprocessor communication. After the final assignment of tasks to processors, the architectural requirements such as memory size, processing power, and interprocessor communication are established. From this estimate, a knowledge base of architectural components is referenced to select processors and communication links.

The final step is to compile and load the tasks and their execution order. The operation of the architecture is similar to a data flow machine. A task is enabled and ready to execute when all predecessor tasks have executed. The task then executes and, when finished, enables its successors or descendants. The author does not report on the effectiveness of this technique.

### 2.4.4 Reconfigurable Architecture Heuristics

A class of architectures is being developed called reconfigurable or dynamic architectures. "Reconfigurable" refers to the ability of a multiprocessor system to change the way subsets of processors communicate and interact. These architectures are of special interest because the researchers who develop the architectures are forced to consider the scheduling or mapping of tasks onto their architectures in order to justify the reconfiguration capability.

We are interested in architectures which reconfigure in order to improve the performance of the active algorithms (or tasks). We are not interested in reconfigurable system for improving reliability. We also do not include systems such as ETH's Empress (Buehrer 1982) which is a multiprocessor machine, but which does not allow for different configurations, such as pipeline or SIMD. We shall review the works of researchers who propose reconfigurable architectures and who deal with the problem of how to prepare algorithms to be executed on their architectures. We consider two reconfigurable architectures, proposed by Kuck (1978) and Kartashev (1982).

Kartashev's reconfigurable architecture is called the Dynamic Computer (DC) (Vick 1980; Kartashev 1981; 1982a; 1982b). The problem of mapping an application onto the DC architecture is dealt with in two steps. The first step is to decompose the application into tasks or programs and measure the program resource. This is done using a P-resource (program resource) diagram which shows the memory requirement of the program and the required word width (in bits) for each major program phase or interval. The diagram also shows the execution time requirement of each interval.

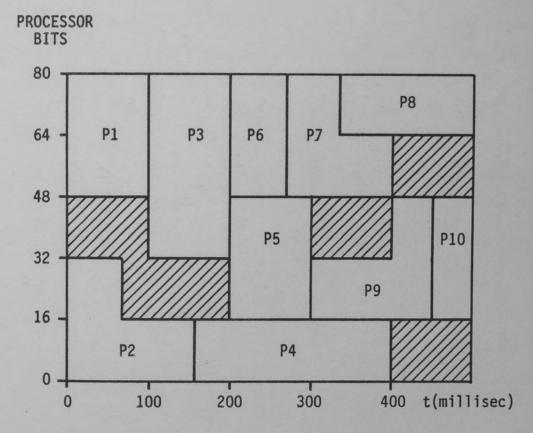

The second step is to fit the P-resource diagrams of all the programs into a combined schedule or combined resource diagram. This is done using a first-fit, priority heuristic. The combined resource diagram also indicates the changes in the reconfigurable communication bus which are needed to effect different word width computers. Figure 7 is an example of the combined resource diagram and shows the fit of ten

Figure 7. Kartashev's Combined Resource Diagram.

different programs (P1,P2,...,P10) onto a set of processors. Each processor is 16-bits, so the system shown in Figure 7 has five processors (80 bits). The bits required by each program defines which processors will execute the program in whole or in part.

The collection of Kartashevs' work is fairly complete, from the architecture description to the procedure for mapping programs onto the architecture. However, the concentration in developing the schedule is on fitting different word width computers together, rather than using the DC in its various modes: pipeline, master/slave, etc. Also, the performance of the heuristic for performing the schedule is not measured or evaluated by the author.

Kuck's architecture is called simply "a high-speed multiprocessor" (Kuck 1979; Padua 1980). The system is composed of multiple processor clusters (PCs) connected by a global alignment network and a global shared memory. Each PC can operate independently, can synchronize with other PCs via the global network, or can operate as a slave, with some other PCs, under control of a global control unit. Processors within a PC can operate independently, synchronized with other processors through the local network, or as a slave under control of the array control unit. Each processor has program and data memory.

This architecture can operate as an SEA (Single Execution on an Array of Data) by forcing all processors to execute the same instruction on data in their local memory. It can operate as an MEA (Multiple Execution, Array) by dividing into multiple SEAs - either to

perform multiple pipelined operations on the same array or to concurrently process multiple arrays. It can also operate as a MES (Multiple Execution, Scalar) which is a data flow type machine (Empress operates in MES mode exclusively). Reference (Kuck 1978) for further detail on Kuck's machine taxonomy.

Kuck's approach to mapping an algorithm onto the architecture has three steps. The first step is to convert the algorithm to a DAG (Directed Acyclic Graph) of Pi-blocks where a Pi-block is a simple computational node. The Pi-block is a statement or small group of statements which are "strongly connected," i.e., the data dependence between statements is cyclic. Practically, this means that the statements in a Pi-block have to be executed sequentially to ensure determinancy. Since all cycle dependencies are in Pi-blocks, any algorithm can be represented as a DAG of Pi-blocks.

The second step is to analyze the dependency of Pi-blocks which are within iteration control constructs (i.e., DO FOR loops) to increase parallelism. The techniques include rearranging the loop control structures, identifying potential concurrency within a loop, and "pipelining." Pipelining breaks a loop into smaller loops which are chained together (i.e., the ith iteration of loop j cannot start until the ith iteration of loop j-1 has completed). An evaluation is also made to determine whether the pipeline approach will be dominated by bottlenecks, where most processors in the pipeline are idle because of unequal Pi-block execution times. The third step is to assign Pi-blocks to processors. This is similar to the task allocation in a distributed computer system problem as discussed earlier. Kuck does not add to this body of knowledge; he does note that the problem is NP-complete and that it is a common problem in scheduling theory.

The lack of discussion on the multiprocessor scheduling problem by Kuck is indicative of the need for a systematic investigation of the multiprocessor scheduling for practical systems such as Kuck's high speed multiprocessor.

# CHAPTER 3 SCHEDULING ALGORITHMS

As shown in Chapter 2, the previous work in this area has developed optimal algorithms for only a subset of constraints. We also reviewed some heuristic approaches which do consider a more complete set of constraints, yet these heuristics cannot be properly evaluated since there is no comparable optimal algorithm.

In this chapter we develop an optimal algorithm and heuristic algorithms to solve the multiprocessor scheduling problem. We begin with a formal definition of the scheduling problem in terms of the constraints discussed in Chapter 1. We then describe the optimal algorithm and sketch the procedures which are used to implement the algorithm. The optimal algorithm has exponential time complexity and we discuss the theoretical worst case complexity. We then describe the constraint relaxing heuristic which is used to evaluate the performance of the other researchers' scheduling approaches. Finally, we introduce the dynamic priority scheduling heuristic which considers the key practical constraints when developing the multiprocessor schedule. The optimal algorithm and the two heuristics will be evaluated in Chapter 4 and used to investigate key characteristics of the scheduling problem.

3.1 Formal Definition of the Scheduling Problem

We define the scheduling problem as follows:

Given a set of tasks, a set of processors, and the following constraints:

- task execution time per processor

task precedence relations

intertask communication requirement

task memory requirement

task execution deadlines

interprocessor communication cost

number of coprocessors required per task

configuration change overhead

- a.) Find a feasible schedule of the tasks on the processors, where a feasible schedule assigns each task to a processor, assigns at most one task to a processor at a time, and satisfies all constraints.

- b.) Find an optimal feasible schedule which minimizes the schedule length.

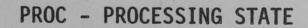

The processor scheduling problem can be formulated as a combination allocating/sequencing problem. In our formulation, the function to be minimized is the schedule length and the system of constraints account for the application and architecture constraints listed above.

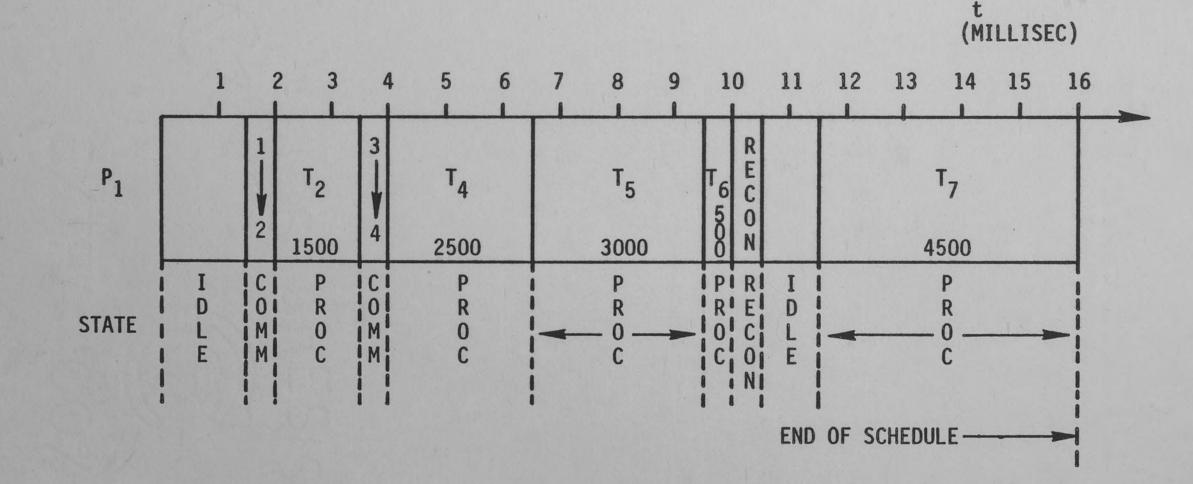

### 3.1.1 Schedule and Schedule Length

Define the scheduling problem as having a set of m processors, P = (P1, P2, ..., Pm), and a set of n tasks, T = (T1, ..., Tn). Any schedule can be modeled as an allocation of tasks and a sequence of scheduling events. The allocation defines which tasks execute on which processors and the sequence defines the order that the tasks process on the processors. For our system, we consider several phases of the task processing: execution, communication, and configuration. So any processor can be in one of four states: executing a task, communicating with another processor due an intertask communication requirement, reconfiguring due to a change in communication configuration, or idling. This definition is quite general since most other processor functions, such as operating system overhead, can be included as part of the task processing time. Figure 8 illustrates this state definition as applied to our example in Chapter 1.

The scheduling events will define any change between the four states listed above. Thus, a schedule, SCHED, is defined by the sequence, SEQ, and the task allocation, ALL:

SCHED = (SEQ, ALL)

where SEQ is a sequence of z events

SEQ = (E1, E2, ... Ez)

and ALL is an assignment of the n tasks onto processors and configurations

ALL = (A1, A2, ..., An).

Each event, Eq, is a two tuple, Eq = (ETYPEi, ETIME), where ETIME is the time of the event and ETYPEi is one of the six task events which indicate the start or finish of one of the task processor states:

S-RFIGi = start reconfiguration required for Ti

F-RFIGi = finish " " "

S-COMMi = start communication of Ti

F-COMMi = finish " "

FOUR STATES:

**RECON - RECONFIGURING STATE**

**COMM - COMMUNICATION STATE**

IDLE - IDLE STATE

Figure 8. Four States of a Processor (From Figure 4).

S-EXECi = start execution of Ti F-EXECi = finish " "

We will use the notation t(ETYPEi) to indicate the time that ETYPEi occurred and INDEX(ETYPEi) to indicate the event sequence index of ETYPEi. In a similar fashion, we use t(Eq) to indicate the time of event q and we use TYPE(Eq) to indicate the type of event Eq. Note that the idle state is not explicitly represented but is easily computed as the absence of any other state. Each of the six event types is recorded for each task, so z = 6\*n. The scheduling events for a given task will always occur in the order shown above, i.e.,  $t(S-RFIGi) \leq t(F-RFIGi) \leq t(S-COMMi)$ , etc. Multiple events can occur at the same time, such as when two tasks start execution simultaneously, i.e., t(S-EXECi) = t(S-EXECj), or when a task has no communication requirement, i.e., t(S-COMMi) = t(F-COMMi). As an example, Table 5 gives sequence events from the schedule shown in Figure 5 of Chapter 1.

Each allocation defines which processor(s), Pk, a task is assigned to and which communication configuration, R, is to be used for that task:

### Ai = (Pk, R)

Normally a task requires only one processor and Pk identifies that processor. For cases where a group of coprocessors are required, we will identify the set as Pk where Pk is the first processor of the set, ordered by processor index. We will use ALLOC(Pk) to indicate the set of tasks which are assigned to Pk. The communication configuration R is a

# TABLE 5

# SEQUENCE OF EVENTS FOR EXAMPLE PROBLEM

EVENT - (STATE, TIME) EVENT - (STATE, TIME)

| q1 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | - (S- | RFIG1, | 0)    | a25               | - | (S-COMM4, | 3500)  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|-------|-------------------|---|-----------|--------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | RFIG1, | 0)    |                   |   | (S-COMM5, | 3500)  |