Retrospective Theses and Dissertations

1984

# Pilot Study of Applicability of a Generic Microprocessor Assembly Language

Joseph H. Bartlett University of Central Florida

Find similar works at: https://stars.library.ucf.edu/rtd University of Central Florida Libraries http://library.ucf.edu

This Masters Thesis (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Retrospective Theses and Dissertations by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

### **STARS Citation**

Bartlett, Joseph H., "Pilot Study of Applicability of a Generic Microprocessor Assembly Language" (1984). *Retrospective Theses and Dissertations.* 4673.

https://stars.library.ucf.edu/rtd/4673

# PILOT STUDY OF THE APPLICABILITY OF A GENERIC MICROPROCESSOR ASSEMBLY LANGUAGE

BY

JOSEPH HENRY BARTLETT

B.S., University of Central Florida, 1978

### THESIS

Submitted in partial fulfillment of the requirements for the degree of Master of Science in the Graduate Studies Program of the College of Engineering University of Central Florida Orlando, Florida

Fall Term 1984

#### ABSTRACT

The purpose of this investigation is to research the utility of a standardized generic microprocessor assembly language. More precisely, use of a generic language implementation on a given microprocessor and its effect on programmer productivity will be investigated. Programmer productivity will be scored in terms of an inverse function of the time taken to complete a programming task correctly. Shorter times imply better programmer productivity and longer times imply the opposite.

# ACKNOWLEDGEMENTS

I wish to thank my friend, Ron Elliott, for all of the assistance, guidance, encouragement and motivation which he provided at the appropriate times and without which this thesis could not have been completed.

I also wish to thank Dana Welch for being such a good friend.

# TABLE OF CONTENTS

| Chapter |      |      |     |    |    |    |     |     |    |    |   |  |   |  |  |   |     |

|---------|------|------|-----|----|----|----|-----|-----|----|----|---|--|---|--|--|---|-----|

| I.      | INT  | RODU | CT  | IC | N  |    |     |     |    |    |   |  |   |  |  |   | 1   |

| II.     | THE  | PRO  | BL  | EM |    |    |     |     |    |    |   |  |   |  |  |   | 7   |

| III.    | STA  | TIST | CIC | S  |    |    |     |     |    |    |   |  |   |  |  |   | 9   |

| IV.     | EQU: | IPME | NT  |    |    |    |     |     |    |    |   |  |   |  |  |   | 13  |

| V.      | SUB. | JECI | S   |    |    |    |     |     |    |    |   |  |   |  |  |   | 15  |

| VI.     | EXP  | ERIM | EN  | TA | L  | ME | ETH | IOD | OI | OG | Y |  |   |  |  |   | 16  |

| VII.    | REST | JLTS |     |    |    |    |     |     |    |    |   |  |   |  |  |   | 19  |

| VIII.   | DISC | cuss | IO  | N  | OF | R  | ES  | SUL | TS |    |   |  |   |  |  |   | 22  |

| Appendi |      |      |     |    |    |    |     |     |    |    |   |  |   |  |  |   |     |

| A       |      |      | •   | •  | •  | •  | •   |     |    |    |   |  | • |  |  | • | 28  |

| в       |      |      |     |    |    |    |     |     |    |    |   |  |   |  |  |   | 5 6 |

| BIBLIOG | RAPE | HY.  |     |    |    |    |     |     |    |    |   |  |   |  |  |   | 89  |

# CHAPTER 1

The emergence of a wide assortment of microprocessors in recent years has presented a variety of challenges to those responsible for software development. This uncontrolled proliferation of microprocessors and their associated assembly languages have been the key obstacles to wider usage of the latest microprocessors in new applications. Although the sophistication and number of high order microprocessor languages, which are essentially machine independent, have been hot topics in today's literature, the need for assembly language programming will always be with us. The improvement in speed and memory economy possible with assembly language programming make it the language of need and/or choice in hardware intensive applications and in real time situations.

The phenomena of today's microprocessor industry is not only the proliferation of faster and more efficient microprocessors, but also that hardware costs are continuing to decrease while software costs are increasing at escalating rates. Companies face the no win battle of deciding between adopting a new microprocessor because of its more desirable

capabilities (and thus abandoning their existing assembly language software base) or maintaining their current microprocessor configuration (and thus facing the consequences of forfeiting a possible competitive edge).

Assembly languages are, more often than not, determined by the manufacturers with little regard for the software problem at hand. Microprocessor manufacturers copywrite their mnemonic instruction lists to help preserve proprietary software. This has forced the use of nonstandard instruction mnemonics, assembler directives, addressing modes, etc. upon the programmer. It is obvious that the inconsistencies between assembly languages for microprocessors need to be transformed to provide a more workable software environment.

A large body of microprocessor assembly language programmers—hobbyists, students, teachers and professional programmers—should benefit greatly from use of a standardized generic microprocessor assembly language.

Time spent on the learning curve to become proficient with assembly language programming on a new microprocessor should be reduced considerably. The fact that the programmer is already knowledgeable of the instruction mnemonics, data and addressing formats, and assembler directives would allow him to concentrate on

learning only the differences in the particular assembly language standard instruction subset implemented on the current microprocessor.

Elaborate algorithms coded in a nonstandard assembly language on one microprocessor would no longer be essentially unintelligible to someone experienced with another instruction set. This would thus allow, and probably encourage, a freer flow of information in the literature.

Programming environments on dedicated development systems and mini or mainframe computers could be used more effectively. The time to develop a resident assembler and/or cross assembler would be reduced. Increasing efficiency in the development of a programming environment for a new microprocessor would allow quicker release of hardware and software support and development facilities.

Software maintenance, which can account for a very large portion of the total software cost, should also benefit from a standardized generic microprocessor assembly language. Maintenance is often performed by someone not familiar with the application being maintained and not experienced with the assembly language itself.

There would, of course, be problems associated with putting a standardized microprocessor assembly language into effect on a large scale. Actual implementation would be a relatively large if not impossible task.

The repertoire of instructions for specific microprocessors could sometimes be very different. A microprocessor dedicated to signal processing would probably have only a few instructions similiar to those of the more common microprocessors.

The number and types of condition codes or status flags, and setting and resetting of these codes are all microprocessor hardware dependent.

Each programmer shall need to be thoroughly familiar with the functional operation and the standardized generic assembly language subset implemented on the given microprocessor.

The actual degree of effectiveness of a standardized microprocessor assembly language can only be truly ascertained after its extended use.

The IEEE Task P694/D11 (Fischer et al. 1979) is a standard which proposes to consolidate existing assembly language features and conventions for present and future microprocessors. Its goal is to standardize the usage of instruction names, mnemonics, address modes, labels, comments and assembler directives. The standard should help to improve programmer productivity.

Cross assemblers that are used to generate and communicate software from the host computer to the target system have been in constant demand. Methods to generate an automated cross assembler development facility for new microprocessors are currently in use (Johnson et al., 1977, Korn, 1975 and Cohen et al., 1979).

High level languages such as UCSD Pascal, which compile to P-code, are in widespread use on a variety of different microprocessors. The P-code instructions for the given implementation are converted to machine code via the microprocessor dependent P-code compiler (Crespi-Reghizzi et al., 1980).

The actual usage of given operations in instruction sets has been investigated (Fairclough, 1982). It was found that even with the large instruction sets now available on microprocessors, a relatively small number of instructions comprise the most widely used.

The "ease of use" of current mnemonic-based microprocessor assembly languages may be outclassed by symbolic assemblers and structured programming techniques (Kriger, 1979 and Crespi-Reghizzi et al., 1980).

Implementation on the Zilog Z80 microprocessor of the Intel 8080 mnemonic instruction set has been accomplished by Technical Design Labs. The TDL assembler provides an extension of 8080 mnemonics to include the entire Z80 instruction repertoire. This assembler has been in widespread usage ever since the beginning of the Z80's popularity.

### CHAPTER II

#### THE PROBLEM

The purpose of this investigation is to research the utility of a standardized generic microprocessor assembly language. More precisely, use of a generic language implementation on a given microprocessor and its effect on programmer productivity will be investigated. Programmer productivity will be scored in terms of an inverse function of the time taken to complete a programming task correctly. Shorter times imply better programmer productivity and longer times imply the opposite.

Of particular interest is the investigation of this productivity when the microprocessor is unfamiliar to the programmer. The manufacturer's assembly language would then be a new language to learn. The standardized generic language would allow knowledge of its previous use to be carried over to the current application.

This report investigates the significance of the following hypothesis:

H<sub>O</sub>: There is no difference in programmer

"productivity" when using a manufacturer's assembly

language versus using a standardized generic

assembly language when both are implemented on an unfamiliar microprocessor.

$\mathrm{H}_1$ : There is a difference in programmer productivity when using the above described assembly languages.

Instead of investigating an actual standardized generic assembly language applicable across several microprocessors (as outlined in Appendix A), the use of one of the generic assembly languages implemented will be investigated. It will be considered a generic language with extensions specific to a given microprocessor.

Technical Design Labs released their TDL mnemonics when the Zilog Z80 microprocessor first came on the scene. TDL assembly language is simply a superset of the Intel 8080 assembly language extended to include the entire Z80 instruction set. The term generic assembly language will be used in the remainder of this paper when referring to TDL assembly language.

Inference shall be made by induction that a standardized assembly language (such as IEEE Task P694/D11) does or does not improve "productivity" as previously defined.

# CHAPTER III STATISTICS

A testing procedure was designed to determine whether or not there was a difference in programmer "productivity" when using the generic assembly language (TDL Z80) versus the manufacturer's assembly language (Zilog Z80). This testing procedure consisted of one test program which the subjects coded using the generic assembly language (TDL Z80) and the manufacturer's assembly language (Zilog Z80). The purpose of this program was to locate the first occurrence of the ASCII letters "AB" in a memory block. The memory block starts at location 1000H and continues through and includes The memory block is first searched for the 10FFH. character "A". When an "A" is found, the next location is compared with the letter "B". If a "B" is found in this location the address of the start of the "AB" character sequence is written into locations 1100H and 1101H (least significant byte first). The search is continued at most 255 times if no match is found.

The test population was divided into two groups at random, each containing approximately half of the subjects. Group 1 programmed first using the manufacturer's assembly language (Zilog Z80) and then

the generic assembly language (TDL Z80). Group 2 programmed first using the generic assembly language (TDL Z80) and then the manufacturer's assembly language (Zilog, Z80). The programmer "productivity" was calculated by using the mean of each of the two groups of test times. That is, the mean time of the test using the generic assembly language (TDL Z80) was compared to the mean time of the test using the manufacturer's assembly language (Zilog Z80). The larger mean time implies lower productivity. The standard deviation was used to give a quantitative figure for how large an experimental spread existed in each group about its mean. The t-test was used to ascertain statistical significance of the experiment results.

The mean time for each group was calculated as follows:

$$t_{mn} = \frac{\sum_{i=1}^{N_n} t_{in}}{\sum_{i=1}^{N_n} t_{in}}$$

where

- 1 Manufacturer group

- n = 2 Generic group

- $N_n = Number of subjects for group n$

- tin = Time of successful completion for the ith subject for group n

and the standard deviation for each group was determined by:

$$S = \sqrt{\frac{\sum_{i=1}^{N_n} (t_{in} - t_{out})^2}{N_n - 1}}$$

The statistical significance of the two sets of data was found by calculating the t-value:

$$t = \frac{t_{m1} - t_{m2}}{\sqrt{\frac{s^2}{N_1} + \frac{s^2}{N_2}}}$$

where

$$s^{2} = \frac{\sum_{i=1}^{N_{1}} (t_{i1} - t_{m1})^{2} + \sum_{i=1}^{N_{2}} (t_{i2} - t_{m2})^{2}}{\sum_{i=1}^{N_{1} + N_{2} - 2}}$$

The degrees of freedom were found by :

$$df = N_1 + N_2 - 2$$

A significance level of 0.20 was used to indicate a correlation in the experimental data. The large significance value was used in this pilot study to better decrease the likelihood of making a type II error (test does not actually show a difference when there is a real one) for small N. This significance choice increased the chances of finding a difference if there really was one, which was the purpose of the pilot study.

# CHAPTER IV

## EQUIPMENT

An Altos Z80 based microcomputer using the CP/M operating system was used to conduct the research. A Hazeltine 1500 video terminal was used for input and output, and a Qume printer was available to produce hardcopy.

A Z80 assembler capable of using either Zilog mnemonics (manufacturer) or TDL mnemonics (generic) was used to generate machine code from a stored assembly language source file. A word processor editor was used to enter and edit the source file.

Command files were used to initiate the assembler, load the object file, execute it, and display the results of each program run. The full screen editor is relatively straightforward to use, has a help function available for command reference, uses cursor control keys to facilitate moving the cursor to any position on the screen, and allows insertion and deletion of characters and lines.

The primary reason this equipment and system software was chosen is because it was readily available

on a day-to-day basis. Learning to use the assembler and editor was anticipated to be and was of little concern.

# CHAPTER V SUBJECTS

To achieve statistically valid conclusions, as

large a population as possible should be used. It would

have been advantageous to have had a large subject

sample, but only five were found who were available.

There was no requirement as to age, sex or experience.

It was required, though, that subjects be familiar with Intel 8080 assembly language mnemonics (which acted as the generic language in this study), and who were relatively unfamiliar with the Z80 Zilog mnemonics, (which acted as the manufacturer's new assembly language).

A pretest interview was used to ascertain information from each subject as to their experience with assembly language, familiarity with the Z80 and 8080, and software expertise in general.

#### CHAPTER VI

### EXPERIMENTAL METHODOLOGY

The test population was divided into two groups at random, each containing approximately half of the subjects. Group I programmed using the manufacturer's assembly language (Zilog Z80) first and then the generic assembly language (TDL Z80). Group 2 programmed using the generic assembly language (TDL Z80) first and then the manufacturer's assembly language (Zilog Z80).

Information on both Z80 assembly language instruction sets, the editor, the assembler and the debugger was supplied to each participant one hour prior to the start of the timed test. This fixed time provided sufficient instruction study time for all subjects to become familiar with the instruction sets, equipment and software tools to be used.

Each subject was asked to write a given program in both Zilog Z80 and TDL Z80 mnemonics. All subjects were given the same program to implement in both languages. The program algorithm was outlined in written form, Program Design Language form and flowchart form.

Information on each Z80 assembly language instruction set, editor, assembler and debugger were also available during testing.

The study's dependent variable was the time needed to correctly complete the given programming task. This is related to productivity as previously discussed.

The independent variable was the language being used in the given programming task, the manufacturer's assembly language or the standardized generic assembly language.

Unfortunately other variables may well have affected this study drastically. Variables that the author had some degree of control over through the subject selection process include the subjects software experience and previous experience with either Z80 or 8080 assembly languages.

Because the subject population was small, it was decided that each individual would program the same algorithm in each of the two languages to increase sample size for each language. This of course introduced other problems. One was in test learning. A learning process was bound to occur due to the experience gained from the use of the first language. This problem was minimized by having half the population start by using one language, and the other half start by

using the other language. Therefore, learning during the test was effectively eliminated as a concern.

Also, in planning it was recognized that there may have been particular individuals who would have problems understanding the program algorithm. To help alleviate this possibility, the algorithm was described in several different ways, in verbal form, in a flowchart and in Program Design Language form.

It was also thought that problems might have cropped up concerning ease of use of the equipment for particular subjects. The assembler and editor were user friendly which helped to reduce possible problems in this area.

Most of the problems mentioned above would not be significant if a large enough population were available. The effect of one subject (or a small number of subjects) on the statistics would not then be so catastrophic to the study.

# CHAPTER VII

# RESULTS

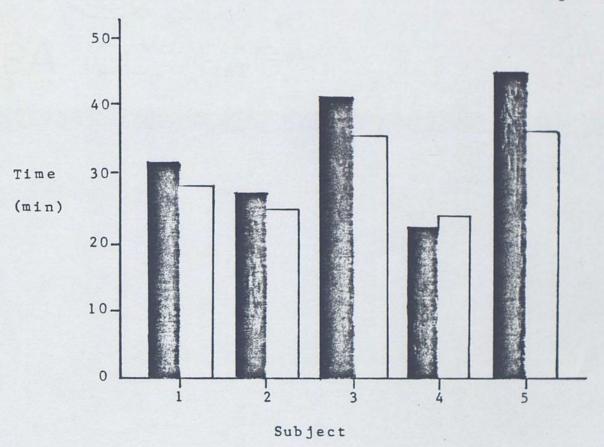

The following table shows the time each subject took to succussfully complete the given programming task using both Zilog mnemonics and standardized generic TDL mnemonics.

| SUBJECT            | TIME (MI<br>ZILOG<br>MNEMONICS | NUTES) TDL MNEMONICS |  |  |  |  |  |

|--------------------|--------------------------------|----------------------|--|--|--|--|--|

| 1                  | 31                             | 28                   |  |  |  |  |  |

| 2                  | 2.7                            | 25                   |  |  |  |  |  |

| 3                  | 42                             | 3 5                  |  |  |  |  |  |

| 4                  | 22                             | 23                   |  |  |  |  |  |

| 5                  | 45                             | 3 7                  |  |  |  |  |  |

| AVERAGE<br>STD DEV | 33.4<br>9.8                    | 29.6<br>6.1          |  |  |  |  |  |

The following histogram compares the time taken to successfully complete the program task using both Zilog and standardized generic TDL mnemonics for all subjects.

Zilog TDL

The t value is computed as described in the statistics section. It is found as follows:

$$S^{2} = \frac{385 \cdot 2 + 151 \cdot 2}{8} = 67.05$$

$$t = \frac{33.4 - 29.6}{\sqrt{\frac{2(67.05)}{5}}} = .73$$

The experimental t-test value for 8 degrees of freedom is 0.73.

# CHAPTER VIII DISCUSSION OF RESULTS

This pilot study was conducted with the gracious aid of its five subjects who donated several hours of their time. Each subject was given the program and instructions included in Appendix B. The subjects were given one hour to become familiar with the editor, assembler and debugger, as well as the individual mnemonic instruction sets.

No particularly insurmountable problems were encountered, although each subject spent about two to three hours overall on the test. All subjects had very little trouble becoming familiar with the editor, assembler and debugger.

All five subjects used in this pilot study would be considered "expert" programmers, but they have varying degrees of assembly language experience. Subjects 1, 2 and 4 had extensive experience with both Intel 8080 and Zilog Z80 microprocessors. Subjects 3 and 5 had passing knowledge of Intel 8080 assembly language only.

Subjects 1, 3 and 5 were given the task to program using TDL standardized generic mnemonics first, and then Zilog. Subjects 2 and 4 were given the tests in the opposite order.

The literature search turned up no examples of experimental investigation into the use of generic standardized assembly language.

The general trend of the data shows slightly shorter times when using the standardized generic TDL mnemonics. But in most cases there did not seem to be a very significant difference in programming time. The standard deviation for each set of samples was calculated to be fairly large.

One subject successfully completed the task in a shorter time using Zilog mnemonics. This particular case is probably attributible to the fact that this subject was extremely familiar with Zilog assembly language.

Formally, the statistical t-test pilot study value was considerably smaller (0.73<<1.387) than the value found in the t-test tables (Shneiderman, 1980).

Therefore, no significant statistical difference can be shown in this study. The pilot study hypothesis is thus left unconfirmed.

Although the null hypothesis was not disproven, further investigation into the problem area has much merit. The small population size allowed the large variety of assembly language experience in the sample population to become the major factor controlling the outcome of the study.

The t-test is a powerful statistical test, but there are several conditions, however, which must be satisfied to insure confidence in its probability statements. The following are the major conditions:

- 1) observations must be independent

- 2) observations must be normally distributed

- 3) observations must have the same variance.

Except for the condition of equal sample variances,

these conditions are not normally tested. They are

generally presumed to be true unless there is evidence

to the contrary (Davies, 1960).

For this investigation, Condition 1 is inferred from the nature of the experiment. Condition 3 can be verified from the experimental data and Condition 2 can only be achieved by using enough study subjects.

The number of observations required in the t-test to compare mean values is dependent upon their standard deviation, and the desired significance of type I ( $\alpha$ ) and II ( $\beta$ ) errors. This number is determined from a table of N values versus  $\alpha$ ,  $\beta$ ,  $\sigma$  and  $\delta$  ( $\delta$  is the smallest time that can be assumed to be significant in the study). If  $\alpha = \beta = 0.05$  and  $D = \frac{\delta}{\sigma} = 5/9.8 = 0.5$ , then the number of observations needed in a t-test to determine the significance of the difference between two sample means is 110 (Davies, 1960).

The current pilot study does not provide for acceptance of the hypothesis, but does provide the sample group's standard deviation which is necessary to estimate the sample size to be used in a more complete study.

It is recommended that a future investigation of this type, comparing the use of Zilog and standardized generic TDL mnemonics, be implemented. This proposed study should follow the guidelines of the current pilot study. The sample size for each assembly language task group should be at least on the order of 110 to insure accuracy of the t-test statistics.

A second proposed study should eventually investigate the IEEE standardized assembly language implementation on a number of 8- and 16-bit microprocessors. Perhaps a performance test of comprehension can be better used to study a very large subject sample set than the pilot study's test procedure.

Given a particular program implemented on all available microprocessors, fill-in-the-blank questions could be asked concerning output for given inputs, inputs necessary to achieve a given output, impact of minor program alterations, and sequence of procedures executed (Shneiderman, 1980). Scoring could be less

subjective by using several graders and the test would be made less time consuming to the subject participants.

A number of problems will probably show up when a portable generic microprocessor assembly language is implemented. The microprocessor machine architecture will probably not lend itself easily to assembly language standardization. The problems involved include: differing word lengths, addressing modes and byte versus word addressing, flags and status, separate instruction and data spaces, total memory addressing space available, and the wide assortment of register and input-output configurations.

The complete study of programmer productivity when using a standardized generic microprocessor assembly language is overwhelming. It shall require many programmer subjects, encompass many processors and extend over several years of study. It is a task that shall probably be attacked in a piecemeal fashion, one facet at a time.

APPENDICES

#### APPENDIX A

### IEEE GENERIC INSTRUCTION SET

This section describes the functional operation of each standard instruction. The operation described may be implemented in any microprocessor (independent of word length) with the appropriate conditions. This standard does not necessarily define the circumstances under which microprocessor conditions are set or cleared, but implies possible usage. The grouping of instructions in this section is arbitrary, and is not intended to imply necessary relationships.

INSTRUCTION NAMES: The naming of instructions shall be in accordance with the following rule: instruction names shall begin with an action verb. Examples are: Add with Carry, Rotate Right, Branch if Less Than, And, Return if Zero, Shift Left, Test, etc. Certain exceptions, the results of common usage, are noted herein.

INSTRUCTION MNEMONICS: The selection of mnemonics for instructions not contained in this standard shall be in accordance with the following rules (exceptions are noted herein):

- a) The first character of the mnemonic shall be the first letter of the action verb.

- b) Addressing modes shall not be embedded in the mnemonic.

- c) Operand designations shall not be embedded in the mnemonic.

- d) Conditions shall be embedded in the mnemonic.

- e) Operand type may be indicated, where appropriate, by the last character of the mnemonic as shown below (the default operand type is word):

- B: Byte

- H: Halfword

- L: Long (Double Word)

- D: Decimal

- F: Floating Point

- 1: Bit

- 4: Nibble or Digit

- M: Multiple

SYNONYMOUS MNEMONICS: Depending on the microprocessor architecture, several standard mnemonics may assemble into the same machine instruction. In those cases, all such mnemonics shall be included in the assembly language.

MULTIFUNCTION INSTRUCTIONS: The representation of multifunction instructions shall be by the use of two or more standard mnemonics on the same line, unless a standard mnemonic exists which describes the

multifunction instruction, in which case that mnemonic shall be used in the assembly language.

mnemonics shall be constructed by concatenating the generic instruction name with the condition name. An example would be "Branch if Zero" (BZ), which is formed from an abbreviated Branch (B-) and "if Zero" (Z-). When the opposite condition state is used, then the letter "N" for "Not True" or "No" shall be inserted between the instruction mnemonic and the condition mnemonic to define the false condition as in "Branch if Not Zero" (BNZ).

Conditions are generally utilized with the following instruction types:

- a) Branch (B-)

- b) Skip (SK-)

- c) Call subroutine (CALL-)

- d) Return from subroutine (RET-)

- e) Increment and Branch (IB-)

- f) Increment and Skip (ISK-)

- g) Decrement and Branch (DB-)

- h) Decrement and Skip (DSK-)

The standard condition mnemonics are defined in this section. The dash character "-" represents the instruction mnemonic letter(s) to be replaced with the generic instruction name.

- 1. Zero (-Z) The instruction is executed if the zero condition is true. Note that this condition may be the same as the Equal condition.

- 2. Not Zero (-NZ) The instruction is executed if the zero conditioon is false. Note that this condition may be the same as the Not Equal condition.

- 3. Equal (-E) The instruction is executed if the equal condition is true. Note that this condition may be the same as the Zero condition.

- 4. Not Equal (-NE) The instruction is executed if the equal condition is false. Note that the condition may be the same as the Not Zero condition.

- 5. <u>Carry (-C)</u> The instruction is executed if the carry condition is true.

- 6. No Carry (-NC) The instruction is executed if the carry condition is false.

- 7. <u>Positive (-P)</u> The instruction is executed if the positive condition is true.

- 8. <u>Negative (-N)</u> The instruction is executed if the negative condition is true.

- 9. Overflow (-V) The instruction is executed if the arithmetic overflow condition is true.

- 10. No Overflow (-NV) The intruction is executed if the arithmetic overflow condition is false.

- 11. Greater Than (-GT) The instruction is executed if an arithmetic (signed) greater than condition exists.

This condition is not equivalent to the Higher condition.

- 12. <u>Greater Than Or Equal (-GE)</u> The instruction is exectued if an arithmetic (signed) greater than or equal condition exists. This condition is not equivalent to the Not Lower condition.

- 13. Less Than (-LT) The instruction is executed if an arithmetic (signed) less than condition exists. This condition is not equivalent to the Lower condition.

- 14. Less Than Or Equal (-LE) The instruction is executed if an arithmetic (signed) less than or equal condition exist. This condition is not equivalent to the Not Higher condition.

- 15. <u>Higher (-H)</u> The instruction is executed if an unsigned greater than condition exists. This condition is not equivalent to the Greater Than condition.

- 16. <u>Not Higher (-NH)</u> The instruction is executed if an unsigned less than or equal condition exists. This condition is not equivalent to the Less Than or Equal condition.

- 17. Lower (-L) The instruction is executed if an unsigned less than condition exists. This condition is not equivalent to the Less Than condition.

- 18. Not Lower (-NL) The instruction is executed if an unsigned greater than or equal condition exists. This condition is not equivalent to the Greater Than or Equal condition.

- 19. <u>Parity Even (-PE)</u> The instruction is executed if the even parity condition exist. This condition is the negation of Parity Odd.

- 20. <u>Parity Odd (-PO)</u> The instruction is executed if the odd parity condition exist. This condition is the negation of Parity Even.

ARITHMETIC INSTRUCTIONS: The following are arithmetic instructions.

- 1. Add (ADD) This instruction performs an addition.

- 2. Add With Carry (ADDC) This instruction performs an addition and adds any previous carry to the result.

- 3. <u>Subtract (SUB)</u> This instruction performs a subtraction.

- 4. <u>Subtract Reverse (SUBR)</u> This instruction performs a subtraction in reverse order.

- 5. <u>Subtract with Carry//Borrow (SUBC)</u> This instruction performs a subtraction and incorporates a previous borrow into the result. The borrow may or may not be related to the carry.

- 6. <u>Increment</u> (INC) This instruction causes a one to be added to the specified operand.

- 7. <u>Decrement</u> (DEC) This instruction causes a one to be subtracted from the specified operand.

- 8. <u>Multiply</u> (MUL) This instruction performs a multiplication.

- 9. Divide (DIV) This instruction performs a division.

- 10. <u>Compare (CMP)</u> This instruction does a comparison and sets the appropriate condition(s) according to the results.

- 11. Negate (NEG) This instruction causes the specified operand to be replaced with its arithmetic negative (two's complement).

- 12. Extend (EXT) This instruction extends an operand to fill a specified larger field.

LOGICAL INSTRUCTIONS: The following are logical instructions.

- 1. And (AND) This instruction performs a logical "AND".

- 2. Or (OR) This instruction performs a logical "OR".

- 3. Exclusive Or (XOR) This instruction performs a logical "Exclusive OR". Note that this instruction mnemonic violates the mnemonic naming rule, but is retained in deference to common usage.

- 4. Not (NOT) This instruction causes the specified operand to be replaced with its one's complement (logical not).

- 5. Not Carry (NOTC) This instruction causes the carry condition to be complemented.

- 6. Shift Right (SHR) This instruction causes the specified operand to be shifted one or more places to the right (toward the LSB), with the most significant bit(s) being replaced with zero(s).

- 7. Shift Left (SHL) This instruction causes the specified operand to be shifted one or more places to the left (toward the MSB), with the least significant bit(s) being replaced with zero(s).

- 8. Shift Right Arithmetic (SHRA) This instruction causes the specified operand to be shifted one or more places to the right with the most significant bit (sign) being preserved and propagated to the right.

- 9. Rotate Right (ROR) This instruction causes the specified operand to be shifted one or more places to the right, with the MSB being replaced by the LSB on each shift.

- 10. Rotate Left (ROL) This instruction causes the specified operand to be shifted one or more places to the left, with the LSB being replaced by the MSB on each shift.

- 11. Rotate Right Through Carry / Link (RORC) This instruction causes the specified operand to be shifted one or more places to the right with the previous state

of the link being loaded into the MSB, and the LSB being loaded into the link. Note that the link may be associated with the carry flag.

- 12. Rotate Left Through Carry / Link (ROLC) This instruction causes the specified operand to be shifted one or more plaes to the left with the previous state of the link being loaded into the LSB, and the MSB being loaded into the link.

- 13. Test (TEST) This instruction causes the specified operand to be tested and sets the appropriate condition(s) according to the result.

DATA TRANSFER INSTRUCTIONS: The following are data transfer instructions.

- 1. Load (LD) This instruction causes the contents of a memory location specified as the source to be transferred to a register specified as the destination.

- 2. Store (ST) This instruction causes the contents of a register specified as the source to be transferred to a memory location specified as the destination.

- 3. Move (MOV) This instruction causes the contents of a register to be transferred to another register, or the contents of a memory location to be transferred to another memory location.

- 4. Move Block (MOVBK) This instruction causes the transfer of a block of data.

- 5. <u>Move Multiple</u> (MOVM) This instruction causes the contents of a momory location to be copied into multiple memory locations.

- 6. Exchange (XCH) This instruction causes the specified operands to be exchanged.

- 7. <u>Input (IN)</u> This instruction causes the data at an input port to be transferred to a register or memory location.

- 8. Output (OUT) This instruction causes the contents of a register or a memory location to be transferred to an output port.

- 9. <u>Clear (CLR)</u> This instruction causes the specified operand to be replaced by zero(s).

- 10. <u>Clear Carry (CLRC)</u> This instruction causes the carry to be set to the not true or no carry state.

- 11. <u>Clear Overflow (CLRV)</u> This instruction causes the overflow to be set to the not true or no overflow state.

- 12. <u>Set (SET)</u> This instruction causes the specified operand to be replaced by one(s).

- 13. <u>Set Carry (SETC)</u> This instruction causes the carry to be set to the true or carry state.

- 14. <u>Set Overflow (SETV)</u> This instruction causes the overflow to be set to the true or overflow state.

BRANCH INSTRUCTIONS: The following are branch instructions.

- 1. <u>Branch (BR)</u> This instruction causes the contents of the program counter to be replaced by the effective address, thereby transferring control to the memory location specified by that address. The condition(s) for execution of the following instructions were described earlier. For brevity, only the instruction titles and mnemonics of the branch instructions are given here.

- 2. Branch If Zero (BZ)

- 3. Branch If Not Zero (BNZ)

- 4. Branch If Equal (BE)

- 5. Branch If Not Equal (BNE)

- 6. Branch If Carry (BC)

- 7. Branch If No Carry (BNC)

- 8. Branch If Positive (BP)

- 9. Branch If Negative (BN)

- 10. Branch If Overflow (BV)

- 11. Branch If No Overflow (BNV)

- 12. Branch If Greater Than (BGT)

- 13. Branch If Greater Thab Or Equal (BGE)

- 14. Branch If Less Than (BLT)

- 15. Branch If Less Than Or Equal (BLE)

- 16. Branch If Higher (BH)

- 17. Branch If Not Higher (BNH)

- 18. Branch If Lower (BL)

- 19. Branch If Not Lower (BNL)

- 20. Branch If Parity Even (BPE)

- 21. Branch If Parity Odd (BPO)

SKIP INSTRUCTIONS: The following are skip instructions.

- 1. Skip (SKIP) This instruction causes the program counter to be incremented such that the execution of the next instruction(s) is skipped. The condition(s) for execution of the following instructions were described earlier. For brevity, only the instruction titles and mnemonics of the skip instructions are given here.

- 2. Skip If Zero (SKZ)

- 3. Skip If Not Zero (SKNZ)

- 4. Skip If Equal (SKE)

- 5. Skip If Not Equal (SKNE)

- 6. Skip If Carry (SKC)

- 7. Skip If Not Carry (SKNC)

- 8. Skip If Positive (SKP)

- 9. Skip If Negative (SKN)

- 10. Skip If Overflow (SKV)

- 11. Skip If No Overflow (SKNV)

- 12. Skip If Greater Than (SKGT)

- 13. Skip If Greater Than Or Equal (SKGE)

- 14. Skip If Less Than (SKLT)

- 15. Skip If Less Than Or Equal (SKLE)

- 16. Skip If Higher (SKH)

- 17. Skip If Not Higher (SKNH)

- 18. Skip If Lower (SKL)

- 19. Skip If Not Lower (SKNL)

- 20. Skip If Parity Even (SKPE)

- 21. Skip If Parity Odd (SKPO)

SUBROUTINE CALL INSTRUCTIONS: The following are subroutine call instructions.

- 1. <u>Call Subroutine (CALL)</u> This instruction causes the program counter to be saved and replaced by the specified operand, thereby transferring control to the memory location specified by the operand. The condition(s) for execution of the following instructions were described earlier. For brevity, only the instruction titles and mnemonics of the call instructions are given here.

- 2. Call If Zero (CALLZ)

- 3. Call If Not Zero (CALLNZ)

- 4. Call If Equal (CALLE)

- 5. Call If Not Equal (CALLNE)

- 6. Call If Carry (CALLC)

- 7. Call If No Carry (CALLNC)

- 8. Call If Positive (CALLP)

- 9. Call If Negative (CALLN)

- 10. Call If Overflow (CALLV)

- 11. Call If No Overflow (CALLNV)

- 12. Call If Greater Than (CALLGT)

- 13. Call If Greater Than Or Equal (CALLGE)

- 14. Call If Less Than (CALLLT)

- 15. Call If Less Than Or Equal (CALLLE)

- 16. Call If Higher (CALLH)

- 17. Call If Not Higher (CALLNH)

- 18. Call If Lower (CALLL)

- 19. Call If Not Lower (CALLNL)

- 20. Call If Parity Even (CALLPE)

- 21. Call If Parity Odd (CALLPO)

RETURN INSTRUCTIONS: The following are return instructions.

- 1. Return From Subroutine (RET): This instruction causes the previously saved contents of the program counter to be restored, thereby returning control to the routine that called the subroutine or was interrupted. The condition(s) for execution of the following instructions were described earlier. For brevity, only the instruction titles and mnemonics are given for the conditional instructions.

- 2. Return If Zero (RETZ)

- 3. Return If Not Zero (RETNZ)

- 4. Return If Equal (RETE)

- 5. Return If Not Equal (RETNE)

- 6. Return If Carry (RETC)

- 7. Return If No Carry (RETNC)

- 8. Return If Positive (RETP)

- 9. Return If Negative (RETN)

- 10. Return If Overflow (RETV)

- 11. Return If No Overflow (RETNV)

- 12. Retrun If Greater Than (RETGT)

- 13. Return If Greater Than Or Equal (RETGE)

- 14. Return If Less Than (RETLT)

- 15. Return If Less Than Or Equal (RETLE)

- 16. Return If Higher (RETH)

- 17. Return If Not Higher (RETNH)

- 18. Return If Lower (RETL)

- 19. Return If Not Lower (RETNL)

- 20. Return If Parity Even (RETPE)

- 21. Return If Parity Odd (RETPO)

- 22. Return With Skip (RETSK) This instruction causes the previously saved contents of the program counter to be incremented some amount and restored, thereby returning control to the routine that called the subroutine at some point after the subroutine call.

- 23. Return From Interrupt (RETI) This instruction returns control to the routine that was interrupted.

MISCELLANEOUS INSTRUCTIONS: The following are miscellaneous instructions.

1. No Operation (NOP) This instruction causes the processor to take no action other than to advance to the

next instruction. This instruction's name violates the naming rules, but is kept in deference to common usage.

- 2. <u>Push (PUSH)</u> This instruction causes the contents of the specified operand(s) to be transferred to the top of a stack.

- 3. Pop (POP) This instruction causes the contents of the top of a stack to be transferred to the designated operand(s).

- 4. <u>Halt (HALT)</u> This particular instruction causes the microprocessor to stop executing instructions until an external condition occurs.

- 5. <u>Wait (WAIT)</u> This particular instruction causes the microprocessor to stop executing instructions until an external or internal condition occurs or changes.

- 6. <u>Break (BRK)</u> This instruction causes an interrupt sequence to be initiated by the microprocessor.

- 7. Adjust (ADJ) This instruction makes an adjustment such that the operand or implied accumulator contents will represent the correct result, usually a binary-coded-decimal representation.

- 8. Enable Interrupt (EI) This instruction causes the designated interrupt(s) to be enabled.

- 9. <u>Disable Interrupt (DI)</u> This instruction causes the designated interrupt(s) to be disabled.

10. <u>Translate</u> (TR) This instruction references a specified table to replace an operand with value(s) selected from the table on the basis of the value of that operand.

OPERANDS AND SYNTAX: The following are operands and syntax.

1. Addressing Modes Addressing modes in microprocessors with more than one addressing mode shall be specified by special character(s). The special character(s) shall precede the address expression except where pre or post specification implies an operational sequence. note that the address expression (addr) may refer to either a memory location or register. The following prefix and postfix characters shall be used to define the specified address modes:

| MODE                                       | SYMBOL                   | EXAMPLE      |

|--------------------------------------------|--------------------------|--------------|

| Absolute                                   | prefix /                 | /addr        |

| Base page                                  | prefix !                 | !addr        |

| Indirect                                   | prefix @                 | @addr        |

| Relative                                   | prefix \$                | \$addr       |

| Immediate                                  | prefix #                 | #value       |

| Index                                      | enclosing parenthesis () | addr(index)  |

| Register                                   | prefix.                  | •addr        |

| Auto-pre-increment                         | prefix +                 | +addr        |

| Auto-post-increment                        | postfix +                | addr+        |

| Auto-pre-decrement                         | prefix -                 | -addr        |

| Auto-post-decrement                        | postfix -                | addr-        |

| Indirect-pre-indexed Indirect-post-indexed | prefix () @ prefix @,    | addr(index)@ |

| •                                          | postfix ()               | @addr(index) |

|                                            |                          |              |

Assemblers may have the option of coercing the addressing mode for instructions that have only one addressing mode. As an example, a branch instruction which allows only relative addressing may be coded without the "\$" character preceding the address designation in the operand field. Such coercion should be flagged in the assembly listing.

For microprocessors that have several address modes for a particular instruction, the assembler may select the address mode if the programmer does not specify it. The means used to indicate which address mode was selected shall be specified. The default address mode should be relative.

2. Expressions An assembler should allow the use of expressions which are evaluated at assembly time. When expression evaluation capabilities are included in the assembler, those expressions operators that are implemented shall be designated by the following infix special symbols:

# SYMBOL(S)

-\* / / / .AND. .OR. .XOR.

.NOT. .SHL. .SHR.

#### OPERATION

Add

Subtract

Multiply

Divide (Signed)

Divide (Unsigned)

AND

OR

Exclusive OR

NOT

Left Shift

Right Shift

SYMBOL(S)

.MOD.

\*\*

<:>

OPERATION

Modulo Exponentiate Bit Alignment

A bit alignment example: the expression A<p:q>

means align bits p through q inclusive of A. Hierarchy

is not specified. Parenthesis may be used to group

expressions.

ASSEMBLER DIRECTIVES: The following are assembler directives.

1. General Assembler directives are commands to the assembler instead of instructions for the microprocessor. They direct the assembler to perform specific tasks during the assembly process.

This standard does not specify the syntax necessary to support macros or conditional assembly.

Naming of assembler directives and of assembler directive mnemonics shall follow the rules used for instructions. If the following functions are implemented, the specified mnemonic shall be used.

2. Originate (ORG) This assembler directive sets the current location counter to the value specified by the operand. The assembler shall initialize all location counters to zero at the beginning of the program.

- 3. Equate (EQU) This assembler directive equates a symbol to a constant, an address, or an expression.

- 4. End (END) This assembler directive informs the assembler that the end of source has been reached.

- 5. <u>Page (PAGE)</u> This assembler directive causes the assembler to advance the assembly listing to the top of the next page.

- 6. <u>Title (TITLE)</u> This assembler directive causes the assembler to advance the assembly listing to the next page and to insert the specified title into the header of that and each of the following pages.

- 7. <u>Date (DATA)</u> This assembler directive causes the assembler to fill the next memory location(s) with the specified value(s). A letter may be appended to the mnemonic as specified earlier to indicate data type.

- 8. Reserve Memory (RES) This assembler directive reserves a block of storage locations. The number of locations reserved is specified by a constant or an expression. The content of the reserved storage location(s) may be unspecified.

- 9. <u>Base (BASE)</u> This assembler directive causes the assembler to change the current implied number base.

# STANDARD INSTRUCTION MNEMONICS FOR 6800

| INSTRUCTION                 | CHANDADD             | WOMODOTA             |

|-----------------------------|----------------------|----------------------|

| INSTRUCTION                 | STANDARD<br>MNEMONIC | MOTOROLA<br>MNEMONIC |

|                             |                      |                      |

|                             |                      |                      |

| ARITHMETIC                  |                      |                      |

|                             |                      |                      |

| Addith Comme                | AD D<br>AD D C       | ADD, ABA<br>ADC      |

| Add with Carry<br>Subtract  | SUB                  | SUB, SBA             |

| Increment                   | INC                  | INC, INS,            |

|                             |                      | INX                  |

| Decrement                   | DEC                  | DEC, DES,<br>DEX     |

| Compare                     | CMP                  | CMP, CBA,            |

| oompa20                     |                      | CPX                  |

| Negate                      | NEG                  | NEG                  |

|                             |                      |                      |

|                             |                      |                      |

| LOGICAL                     |                      |                      |

| And                         | AND                  | AND                  |

| Or                          | OR                   | ORA                  |

| Exclusive Or                | XOR                  | EOR                  |

| Not                         | NOT                  | COM                  |

| Shift Right                 | SHR                  | LSR                  |

| Shift Left                  | SHL                  | ASL                  |

| Shift Right Arithmetic      | SHRA                 | ASR<br>ROR           |

| Rotate Right<br>Rotate Left | ROL                  | ROL                  |

| Test                        | TEST                 | BIT, TST             |

|                             |                      |                      |

|                             |                      |                      |

| DATA TRANSFER               |                      |                      |

| DATA TRANSFER               |                      |                      |

| Load                        | LD                   | LDA, LDS,            |

|                             | a m                  | LDX                  |

| Store                       | ST                   | STA, STS,<br>STX     |

| Move                        | MOV                  | TAB, TBA,            |

|                             |                      | TAP, TPA,            |

|                             | O. P.                | TSX, TXS             |

| Clear Carry                 | CLR<br>CLRC          | CLC                  |

|                             |                      |                      |

| Clear Overflow<br>Set Carry<br>Set Overflow                                                                                                                                                                                                                                                       | CLRV<br>SETC<br>SETV                                    | CLV<br>SEC<br>SEV                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------|

| BRANCH                                                                                                                                                                                                                                                                                            |                                                         |                                                                          |

| Branch Branch if Zero Branch if Not Zero Branch if Equal Branch in Not Equal Branch if Carry Branch if Positive Branch if Negative Branch if Negative Branch if Greater Than Branch if Greater Than Branch if Less Than Branch if Higher Branch in Not Higher Branch if Lower Branch if Not Lower | BR BZ BNZ BE BNE BC BP BN BV BNV BGT BGE BLT BH BNH BNH | BRA, JMP BEQ BNE BEQ BNE BCS BPL BMI BVS BVC BGT BGE BLT BHI BLS BCS BCS |

|                                                                                                                                                                                                                                                                                                   |                                                         |                                                                          |

| SUBROUTINE CALL Call Subroutine                                                                                                                                                                                                                                                                   | CALL                                                    | BSR, JSR                                                                 |

| RETURN                                                                                                                                                                                                                                                                                            |                                                         |                                                                          |

| Return from Subroutine<br>Return from Interrupt                                                                                                                                                                                                                                                   | RET<br>RETI                                             | RTS<br>RTI                                                               |

| MISCELLANEOUS                                                                                                                                                                                                                                                                                     |                                                         |                                                                          |

| No Operation Push Pop Wait Adjust Decimal Enable Interrupt Disable Interrupt Break                                                                                                                                                                                                                | NOP PUSH POP WAIT ADJ EI DI BRK                         | NOP<br>PSH<br>PUL<br>WAI<br>DAA<br>SEI<br>CLI<br>SWI                     |

# STANDARD INSTRUCTION MNEMONICS FOR Z80, 8080,8085

| INSTRUCTION                      | STANDARD<br>MNEMONIC |                   | INTEL<br>MNEMONIC    |

|----------------------------------|----------------------|-------------------|----------------------|

|                                  |                      |                   |                      |

| ARITHMETIC                       |                      |                   |                      |

| Add                              | ADD                  | ADD               | ADD, ADI,<br>DAD     |

| Add with Carry<br>Subtract       | ADDC<br>SUB          | ADC<br>SUB        | ADC, ACI<br>SUB, SUI |

| Subtract with Carry<br>Increment | SUBC                 | SBC               | SBB, SBI<br>INX, INR |

| Decrement<br>Compare             | D E C<br>CMP         | DEC<br>CP,CPI,    | DCX, DCR<br>CMP, CPI |

| Compare, Multiple                | CMPM                 | CPD<br>CPIR, CPDR |                      |

| Negate Negate                    | NEG                  | NEG NEG           | -                    |

| LOGICAL                          |                      |                   |                      |

|                                  |                      |                   |                      |

| And                              | AND                  | AND               | ANA, ANI             |

| Or<br>Exclusive Or               | OR                   | OR<br>XOR         | ORA, ORI<br>XRA, XRI |

| Not                              | NOT                  | CPL               | CM A                 |

| Not Carry                        | NOTC                 | CCF               | CMC                  |

| Shift Right                      | SHR                  | SRL               | -                    |

| Shift Left                       | SHL                  | SLA               | ADD, DAD             |

| Shift Right Arithmetic           | SHRA                 | SRA               | -                    |

| Rotate Right                     | ROR                  | RRCA, RRC         | RAR                  |

| Rotate Left                      | ROL                  | RLCA, RLC         | RAL                  |

| Rotate Right Through Carry       | RORC                 | RR, RRA           | RRC                  |

| Rotate Left Through Carry        | ROLC                 | RL, RLA           | RLC                  |

| Rotate Right Decimal             | ROR4                 | RLD               | -                    |

| Rotate Left Decimal              | ROL4                 | RLD               | -                    |

| Test Bit                         | TEST1                | BIT               | -                    |

|                                  |                      |                   |                      |

### DATA TRANSFER

| DILLI THINDI DI                  |                    |                                  |                                 |

|----------------------------------|--------------------|----------------------------------|---------------------------------|

| Load                             | LD                 | LD                               | MOV, LXI,<br>LHLD,              |

| Store                            | ST                 | LD                               | LDA, MVI<br>MOV, STAX,<br>SHLD, |

| Move                             | MOV                | LD, LDI,                         | STA<br>MOV, MVI,<br>SPHL        |

| Move Block<br>Exchange           | M O V B K<br>X C H | LDIR, LDDR<br>EX, EXX            | XCHG,<br>XTHL                   |

| Input                            | IN                 | IN, INI,<br>IND                  | IN, RIM                         |

| Input Block<br>Output            | INBK               | INIR, INDR<br>OUT, OUTI,<br>OUTD |                                 |

| Output Block<br>Set Bit          | OUTBK<br>SET1      | OTIR, OTDR                       |                                 |

| Clear Bit                        | CLRI               | RES                              | -                               |

| Set Carry                        | SETC               | SCF                              | STC                             |

| Set Interrupt Mode               | SETI               | IM                               | -                               |

| BRANCH                           |                    |                                  |                                 |

| Branch                           | BR                 | JP                               | JMP, PCHL                       |

| Branch if Zero                   | BZ                 | JP Z, JR Z                       |                                 |

| Branch if Not Zero               | BNZ                | JP NZ,<br>JR NZ                  | JNZ                             |

| Branch if Equal                  | BE                 | JP Z, JR Z                       |                                 |

| Branch if Not Equal              | BNE                | JP NZ,<br>JR NZ                  | JNZ                             |

| Branch if Carry                  | BC                 | JP C, JR C                       | -                               |

| Branch if No Carry               | BNC                | JP NC,<br>JR NC                  | JNC                             |

| Branch if Positive               | BP                 | JP P                             | JP                              |

| Branch if Negative               | BN                 | JP M                             | JM                              |

| Branch if Parity Even            | BPE                | JP PE                            | JPE                             |

| Branch if Parity Odd             | BPO                | JP PO                            | JPO                             |

| Branch if Low                    | BL                 | JP C                             | JC                              |

| Branch if Not Low                | BNL                | JP NC                            | JNC                             |

| Decrement and Branch if Not Zero | DBNZ               | DJNZ                             | -                               |

| CALL                             |                    |                                  |                                 |

| Call                             | CALL               | CALL, RST                        | CALL, RST                       |

| Call if Zero                     | CALLZ              | CALL Z                           | CZ                              |

| Call if Not Zero                 | CALLNZ             | CALL NZ                          | CNZ                             |

| Call if Equal                    | CALLE              | CALL Z                           | CZ                              |

| Call if Not Equal     | CALLNE | CALL NZ | CNZ  |

|-----------------------|--------|---------|------|

| Call if Carry         | CALLC  | CALL N  | CC   |

| Call if No Carry      | CALLNC | CALL NC | CNC  |

| Call if Positive      | CALLP  | CALL P  | CP   |

| Call if Negative      | CALLN  | CALL M  | CM   |

| Call if Parity Even   | CALLPE | CALL PE | CPE  |

| Call if Parity Odd    | CALLPO | CALL PO | CPO  |

| Call if Low           | CALLL  | CALL C  | CC   |

| Call if Not Low       | CALLNL | CALL NC | CNC  |

|                       |        |         |      |

|                       |        |         |      |

| RETURN                |        |         |      |

|                       |        |         |      |

| Return                | RET    | RET     | RET  |

| Return if Zero        | RETZ   | RET Z   | RZ   |

| Return if Not Zero    | RETNZ  | RET NZ  | RNZ  |

| Return if Equal       | RETE   | RET Z   | RZ   |

| Return if Not Equal   | RETNE  | RET NZ  | RNZ  |

| Return if Carry       | RETC   | RET C   | RC   |

| Return if No Carry    | RETNC  | RET NC  | RNC  |

| Return if Positive    | RETP   | RET P   | RP   |

|                       | RETN   |         |      |

|                       |        | RET M   | RM   |

| Return if Parity Even | RETPE  | RET PE  | RPE  |

| Return if Parity Odd  | RETPO  | RET PO  | RPO  |

| Return if Lower       | RETL   | RET C   | RC   |

| Return if Not Lower   | RETNL  | RET NC  | RNC  |

| Return from Interrupt | RETI   | RETI    | 7    |

| Return from Interrupt |        |         |      |

| Non-Maskable          | RETIN  | RETN    | -    |

|                       |        |         |      |

| MISCELLANEOUS         |        |         |      |

|                       |        |         | WOR  |

| No operation          | NOP    | NOP     | NOP  |

| Push                  | PUSH   | PUSH    | PUSH |

| Pop                   | POP    | POP     | POP  |

| Wait                  | WAIT   | HALT    | HLT  |

| Adjust Decimal        | ADJ    | DAA     | DAA  |

| Enable Interrupt      | EI     | EI      | EI   |

| Disable Interrupt     | DI     | DI      | DI   |

|                       |        |         |      |

# IEEE STANDARD INSTRUCTION MENEMONICS FOR THE 8086

| INSTRUCTION                | STANDARD<br>MNEMONIC | INTEL<br>MNEMONIC |

|----------------------------|----------------------|-------------------|

|                            | MNEMONIC             | HNEMONIC          |

|                            |                      |                   |

| ARITHMETIC                 |                      |                   |

| Add                        | ADD                  | ADD               |

| Add with Carry             | ADDC                 | ADC               |

| Subtract                   | SUB                  | SUB               |

| Subtract with Carry        | SUBC                 | SBB               |

| Increment                  | INC                  | INC               |

| Decrement                  | DEC                  | DEC               |

| Negate                     | NEG                  | N EG              |

| Multiply                   | MUL                  | IMUL              |

| Multiply, Unsigned         | MULU                 | MUL               |

| Divide                     | DIV                  | IDIV              |

| Divide, Unsigned           | DIVU                 | DIV               |

| Compare                    | CMP                  | CMPW              |

| Compare, Byte              | CMPB                 | CMPB              |

| Compare, Block             | CMPBK                | SCAW              |

| Compare, Block, Byte       | СМРВКВ               | SCAB              |

| Extend                     | EXT                  | CBW               |

| Extend, Long               | EXTL                 | CWD               |

|                            |                      |                   |

| TOGTGAT                    |                      |                   |

| LOGICAL                    |                      |                   |

| And                        | AND                  | AND               |

| Or                         | OR                   | OR                |

| Exclusive Or               | XOR                  | XOR               |

| Not                        | NOT                  | NOT               |

| Shift Right                | SHR                  | SHR               |

| Shift Left                 | SHL                  | SHL, SAL          |

| Shift Right Arithmetic     | SHRA                 | SAR               |

| Rotate Right               | ROR                  | ROR               |

| Rotate Left                | ROL                  | ROL               |

| Rotate Right Through Carry | RORC                 | RCR               |

| Rotate Left Through Carry  | ROLC                 | RCL               |

| Test                       | TEST                 | TEST              |

| Not Carry                  | NOTC                 | CMC               |

JNP/JPE

JNP/JPO

JCXZ

LOOP

LOOP/

LOOPE

BPE

BPO

BCXZ

DBNZ

DBNZE

Branch if Parity Even Branch if parity Odd Branch if CX Zero

Decrement and Branch if

Decrement and Branch if

Not Zero and Equal

Not Zero

| DATA TRANSFER                   |          |                                    |

|---------------------------------|----------|------------------------------------|

| Load                            | LD       | MOV, LEA,<br>LES,<br>LODS,<br>LODW |

| Load, Byte                      | LDB      | LODB                               |

| Store                           | ST       | MOV                                |

| Store, Byte                     | STB      | STOB                               |

| Move                            | MOV      | MOV, LAHF                          |

| Move, Byte                      | MOVB     | MOVB                               |

| Exchange                        | XCH      | XHCG                               |

| In                              | IN       | INW                                |

| In, Byte                        | INB      | IN                                 |

| Out                             | OUT      | OUTW                               |

| Out, Byte                       | OUTB     | OUT                                |

| Clear Carry                     | CLRC     | CLC                                |

| Set Carry                       | SETC     | STC                                |

| Clear Direction                 | CLRD     | CLD                                |

| Set Direction                   | SETD     | STD                                |

| Break                           | BRK      | INT                                |

| Break on Overflow               | BRKV     | INTO                               |

| Escape                          | ESC      | ESC                                |

| Lock                            | LOCK     | LOCK                               |

|                                 |          |                                    |

| BRANCH                          |          |                                    |

| Branch                          | BR       | JMP                                |

| Branch if Zero/Equal            | BZ,BE    | JZ, JE                             |

| Branch in Not Zero/Not Equal    | BNZ, NBE | JNZ, JNE                           |

| Branch if Positive              | BP       | JS                                 |

| Branch if Negative              | BN       | JNS                                |

| Branch if Overflow              | BV       | JNO                                |

| Branch if No Overflow           | BNV      | JNO                                |

| Branch if Greater Than          | BFT      | JNLE/JG                            |

| Branch if Greater Than or Equal | BHE      | JNL/JGE                            |

| Branch if Less Than             | BLT      | JL/JNGE                            |

| Branch if Less Than or Equal    | BLE      | JLE/JNG                            |

| Branch if Higher                | ВН       | JNBE/JA                            |

| Branch if Not Higher            | BNH      | JBE/JNA                            |

| Branch if Lower                 | BL       | JB/JNAE                            |

| Branch if Not Lower             | BNL      | JNB/JAE                            |

| Decrement and Branch if<br>Not Zero and Not Equal | DBNZNE | LOOPNZ/<br>LOOPNE |

|---------------------------------------------------|--------|-------------------|

| SUBROUTINE CALL                                   |        |                   |

| Call Call                                         | CALL   | CALL              |

|                                                   |        |                   |

| RETURN                                            |        |                   |

| Return                                            | RET    | RET               |

| Return from Interrupt                             | RETI   | IRET              |

| MISCELLANEOUS                                     |        |                   |

| Halt                                              | HALT   | HLT               |

| Wait                                              | WAIT   | WAIT              |

| Enable Interrupt                                  | EI     | STI               |

| Disable Interrupt                                 | DI     | CLI               |

| Adjust Nibble Subtract                            | ADJ4S  | DAS               |

| Adjust Nibble Add                                 | ADJ4A  | DAA               |

| Adjust Byte Subrtact                              | ADJBS  | AAS               |

| Adjust Byte Add                                   | ADJBA  | AAA               |

| Convert Binary to Decimal                         | CVTBD  | AAM               |

| Convert Decimal to Binary                         | CVTDB  | AAD               |

| Push                                              | PUSH   | PUSH, PUSHF       |

| Pop                                               | POP    | POP, POPF         |

| Repeat                                            | REP    | REP               |

| Translate                                         | TR     | XLAT              |

#### APPENDIX B

#### MATERIAL PROVIDED TO SUBJECTS

The purpose of this program is to locate the first occurrence of the ASCII letters "AB" in a memory block. The memory block starts at location 1000H and continues through and including 10FFH. The memory block is first searched for the character "A". When an "A" is found, the next location is compared with the letter "B". If a "B" is found in this location the address of the start of the "AB" character sequence is written into locations 1100H and 1101H (least significant byte first). The search is continued at most 255 times if no match is found.

#### PROGRAM DESIGN LANGUAGE

```

Start

BC<--OFFH

HL<--1000H

Do While BC>0

A<--" A"

If A=M(HL)

Then HL<--HL+1

A<--"B"

If A=M(HL)

Then HL<--HL-1

Exit Do

End If

Else HL<--HL+1

End If

C<--C-1

End Do

(1100) <-- HL

Finish

```

The Z80 microprocessor contains three groups of registers. The first group consists of a set of 8 bit registers. The 8 bit registers (A,B,C,D,E,H,L) may be used individually or as 16-bit registers in pairs (BC,DE,HL). In addition, there is an 8-bit accumulator and a flag register.

The second group is an exact duplicate of the first. The alternate register set (A',B',C',D',E',H',L') and (B'C', D'E', H'L') is made available to the programmer via the "exchange" instruction group.

The third group of registers consists of two 16-bit index registers (IX and IY), the stack pointer (SP), the program counter (PC), as well as the interrupt vector (I) and the dynamic memory refresh register (R).

#### MAIN REGISTER SET

#### ALTERNATE REGISTER SET

| A | Ac | cum | u1 | at | or |

|---|----|-----|----|----|----|

|   |    |     |    |    |    |

F Flag Register

B General Purpose

C General Purpose

D General Purpose

E General Purpose

H General Purpose

L General Purpose

A' Accumulator

F' Flag Register

B' General Purpose

C' General Purpose

D' General Purpose

E' General Purpose

H' General Purpose

L' General Purpose