University of Central Florida

STARS

Electronic Theses and Dissertations, 2004-2019

2011

# Lateral Power Mosfets Hardened Against Single Event Radiation Effects

Patrick Michael Shea University of Central Florida

Part of the Electrical and Electronics Commons Find similar works at: https://stars.library.ucf.edu/etd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS Citation**

Shea, Patrick Michael, "Lateral Power Mosfets Hardened Against Single Event Radiation Effects" (2011). *Electronic Theses and Dissertations, 2004-2019.* 1711. https://stars.library.ucf.edu/etd/1711

## LATERAL POWER MOSFETS HARDENED AGAINST SINGLE EVENT RADIATION EFFECTS

by

PATRICK MICHAEL SHEA B.S.E.E. University of Central Florida, 2006 M.S.E.E. University of Central Florida, 2007

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Fall Term 2011

Major Professor: Z. John Shen

© 2011 Patrick Michael Shea

## ABSTRACT

The underlying physical mechanisms of destructive single event effects (SEE) from heavy ion radiation have been widely studied in traditional vertical double-diffused power MOSFETs (VDMOS). Recently lateral double-diffused power MOSFETs (LDMOS), which inherently provide lower gate charge than VDMOS, have become an attractive option for MHz-frequency DC-DC converters in terrestrial power electronics applications [1]. There are growing interests in extending the LDMOS concept into radiation-hard space applications. Since the LDMOS has a device structure considerably different from VDMOS, the well studied single event burn-out (SEB) or single event gate rapture (SEGR) response of VDMOS cannot be simply assumed for LDMOS devices without further investigation.

A few recent studies have begun to investigate ionizing radiation effects in LDMOS devices, however, these studies were mainly focused on displacement damage and total ionizing dose (TID) effects, with very limited data reported on the heavy ion SEE response of these devices [2]-[5]. Furthermore, the breakdown voltage of the LDMOS devices in these studies was limited to less than 80 volts (mostly in the range of 20-30 volts), considerably below the voltage requirement for some space power applications.

In this work, we numerically and experimentally investigate the physical insights of SEE in two different fabricated LDMOS devices designed by the author and intended for use in radiation hard applications. The first device is a 24 V Resurf LDMOS fabricated on P-type epitaxial silicon on a P+ silicon substrate. The second device is a much different 150 V SOI Resurf LDMOS fabricated on a 1.0 micron thick N-type silicon-on-insulator substrate with a 1.0 micron thick buried silicon dioxide layer on an N-type silicon handle wafer. Each device contains internal features, layout techniques, and process methods designed to improve single event and total ionizing dose radiation hardness. Technology computer aided design (TCAD) software was used to develop the transistor design and fabrication process of each device and also to simulate the device response to heavy ion radiation. Using these simulations in conjunction with experimentally gathered heavy ion radiation test data, we explain and illustrate the fundamental physical mechanisms by which destructive single event effects occur in these LDMOS devices. We also explore the design tradeoffs for making an LDMOS device resistant to destructive single event effects, both in terms of electrical performance and impact on other radiation hardness metrics.

Dedicated to my family.

### ACKNOWLEDGMENTS

I would like to express my sincere gratitude and appreciation to Professor John Shen, my advisor and director of the Power Semiconductor Research Laboratory (PSRL) at the University of Central Florida. His enthusiastic lectures in an introductory semiconductor physics course first drew me toward the study of microelectronics and helped me realize my calling in this field. Our work together in the field of power semiconductor devices has been an incredibly exciting and rewarding experience.

I would like to acknowledge the support of Sandia National Laboratories in the fabrication and characterization of the 25 V LDMOS device presented in this work. Specifically, I would like to thank Brandon Witcher, Bruce Draper, Ralph Young, Daniel Savignon, and the rest of the Sandia microfabrication team involved in the project. I would also like to thank Paul Dodd for taking the initiative to present this work at the 2009 NSREC conference and later in the IEEE TNS.

I would like to thank Matthew Landowski, formerly of the UCF PSRL and presently at Lockheed Martin, for his continuation of the 25 V LDMOS work after I diverted my attention to development of the 150 V SOI device. Matthew is a good friend. His kind demeanor and enthusiasm for his work make him a pleasure to work with.

I would also like to thank Leif Scheick of NASA JPL for his open advice and informative discussions regarding SEE in vertical power MOSFETs. The sharing of his time and expertise is greatly appreciated.

## **TABLE OF CONTENTS**

| LIST OF FIGURES                                                        |

|------------------------------------------------------------------------|

| LIST OF TABLES xiv                                                     |

| LIST OF ACRONYMS AND ABBREVIATIONSxv                                   |

| CHAPTER ONE: INTRODUCTION1                                             |

| Evolution of Modern Power Electronics and Power Semiconductor Devices3 |

| Introduction to Power MOSFET Design Considerations                     |

| Conduction Losses in Power MOSFETs7                                    |

| Switching Losses in Power MOSFETs12                                    |

| Recent Advances in Lateral Power MOSFET Technology17                   |

| Motivation23                                                           |

| Review of Ionizing Radiation Effects in Semiconductor Devices27        |

| Carrier Generation27                                                   |

| Single Event Effects                                                   |

| Single Event Upset and Single Event Latchup                            |

| Single Event Burnout                                                   |

| Single Event Gate Rupture35                                            |

| Total Dose Effects                                                     |

| CHAPTER TWO: SINGLE EVENT RADIATION EFFECTS IN POWER MOSFETS.41        |

| Single Event Burnout in Planar VDMOS42                                 |

| Physical Mechanisms of Single Event Burnout44                          |

| Hardening Against SEB in Vertical Power MOSFETs51                      |

| Single Event Gate Rupture in Planar VDMOS            | 52  |

|------------------------------------------------------|-----|

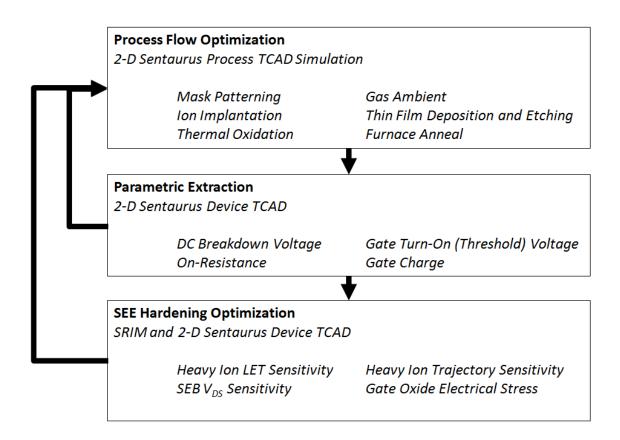

| CHAPTER THREE: MODELING AND DESIGN METHODOLOGY       | 56  |

| Overview of Design Methodology                       | 56  |

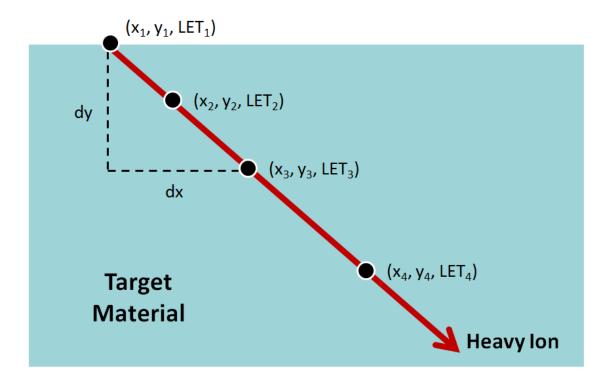

| TCAD SEE Modeling                                    | 60  |

| CHAPTER FOUR: 25 V LDMOS ON P-TYPE EPITAXIAL SILICON | 62  |

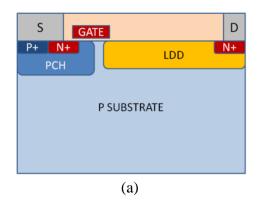

| Prior Art LDMOS Device Structures                    | 63  |

| 25 V Rad-Hard LDMOS Device Concept                   | 69  |

| Design Considerations                                | 76  |

| First Iteration Experimental Results                 | 90  |

| First Iteration SEE Test Results                     | 93  |

| Second Iteration Modeling and Design                 | 95  |

| Second Iteration Experimental Results                | 116 |

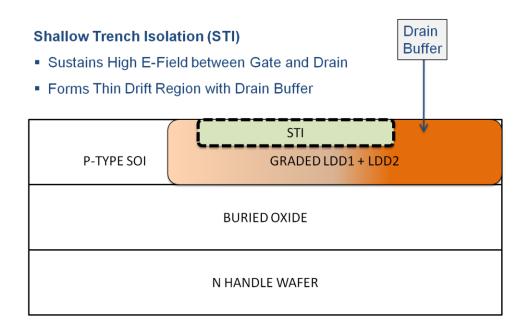

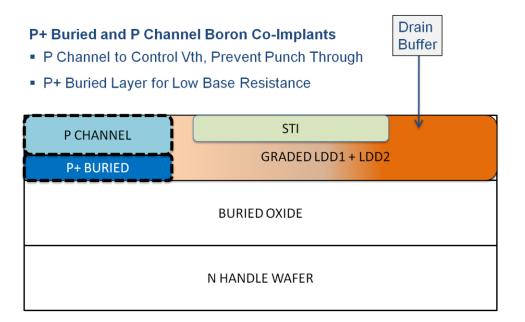

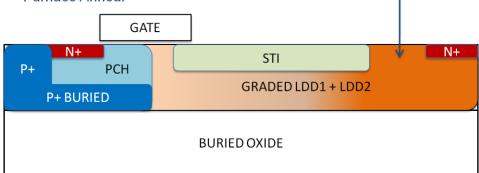

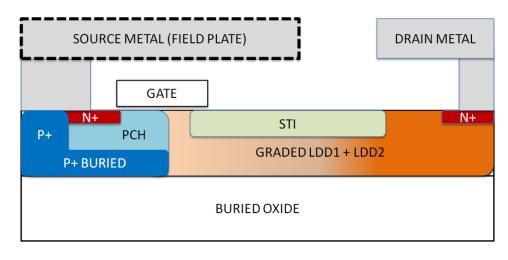

| CHAPTER FIVE: 150 V SOI RESURF THIN FILM LDMOS       | 120 |

| Prior Art SOI Resurf LDMOS                           | 121 |

| Device Concept                                       | 124 |

| Modeling and Design                                  | 129 |

| Fabrication Process                                  | 134 |

| SEE Modeling                                         | 137 |

| Analysis of SEB Failure Mechanism                    | 145 |

| Experimental Results                                 | 149 |

| AC and DC Electrical Characterization                | 149 |

| SEE Testing Results                                  | 154 |

| CHAPTER SIX: CONCLUSIONS |  |

|--------------------------|--|

| Summary                  |  |

| Future Work              |  |

| LIST OF REFERENCES       |  |

## LIST OF FIGURES

| Figure 1: Coupling of Modern Digital Systems and Power Electronics         | 4  |

|----------------------------------------------------------------------------|----|

| Figure 2: Point-of-Load DC-DC Converter Architecture                       | 5  |

| Figure 3: Planar VDMOS Device Structure                                    | 9  |

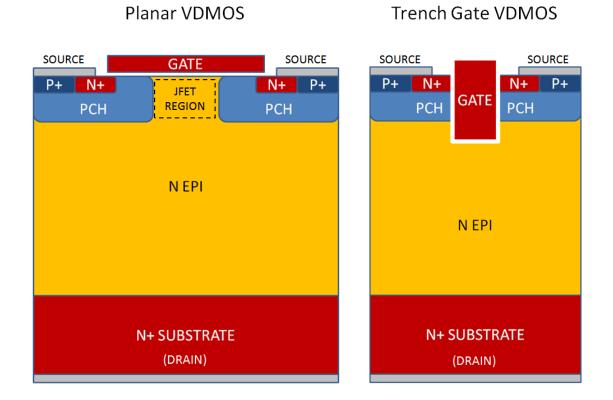

| Figure 4: Planar VDMOS and Trench Gate VDMOS Device Cross Sections         | 12 |

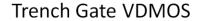

| Figure 5: Internal Gate Capacitances in Planar and Trench VDMOS Structures | 14 |

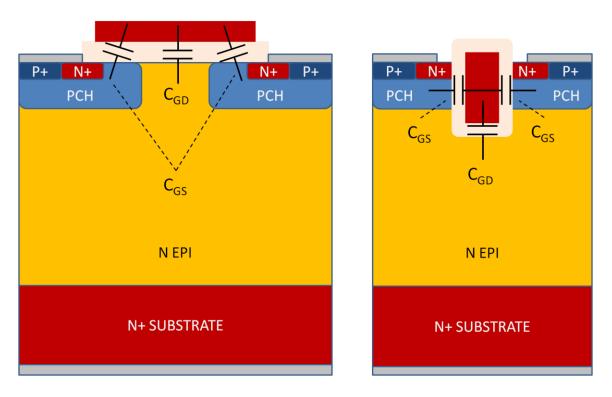

| Figure 6: Resurf LDMOS Transistor Cell                                     | 21 |

| Figure 7: FOM Comparison of Rad-Hard vs Commercial Power MOSFETs           | 25 |

| Figure 8: Electron-Hole Pair Production                                    | 27 |

| Figure 9: Heavy Ion Charge Deposition                                      | 32 |

| Figure 10: Planar VDMOS and Parasitic NPN Bipolar Junction Transistor      | 43 |

| Figure 11: Planar VDMOS and Heavy Ion Charge Collection                    | 46 |

| Figure 12: Time Evolution of Single Event Burnout in Planar VDMOS          | 50 |

| Figure 13: Power MOSFET Modeling Workflow                                  | 58 |

| Figure 14: Representation of Heavy Ion LET and Trajectory Input from SRIM  | 61 |

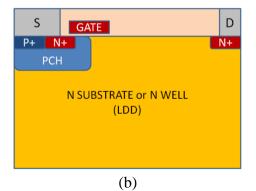

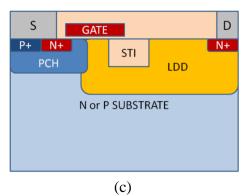

| Figure 15: Prior Art LDMOS Device Structures                               | 68 |

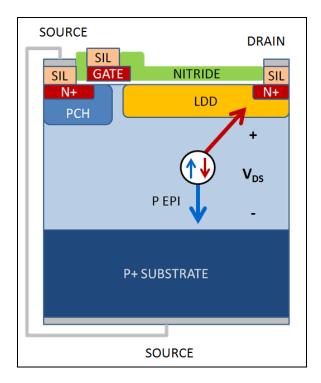

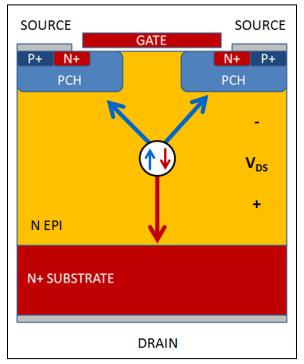

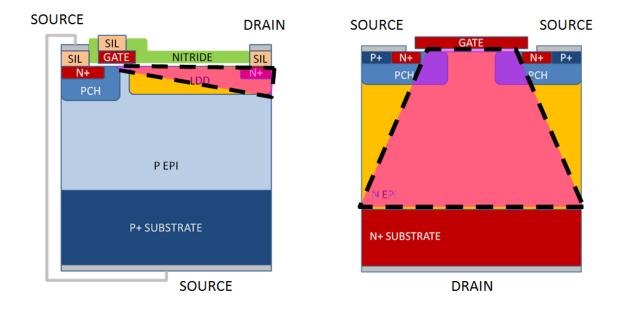

| Figure 16: Standard LDMOS and Proposed Rad-Hard LDMOS                      | 70 |

| Figure 17: Theorized Charge Collection in Rad-Hard LDMOS and Planar VDMOS  | 72 |

| Figure 18: Heavy Ion Trajectories Shunting Gate to Drain                   | 74 |

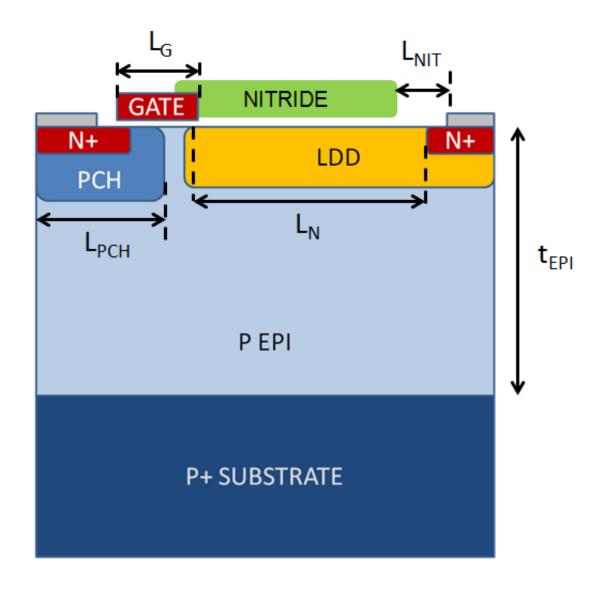

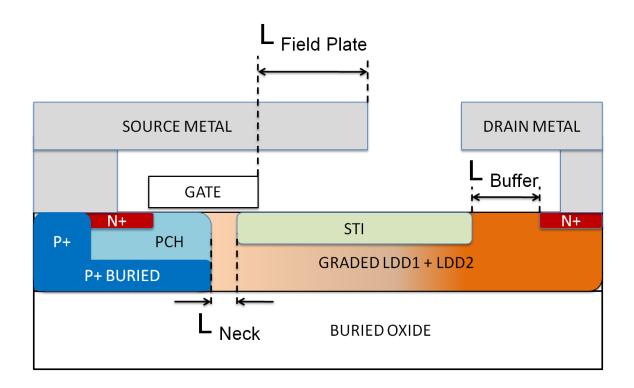

| Figure 19: LDMOS Critical Design Dimensions                                | 76 |

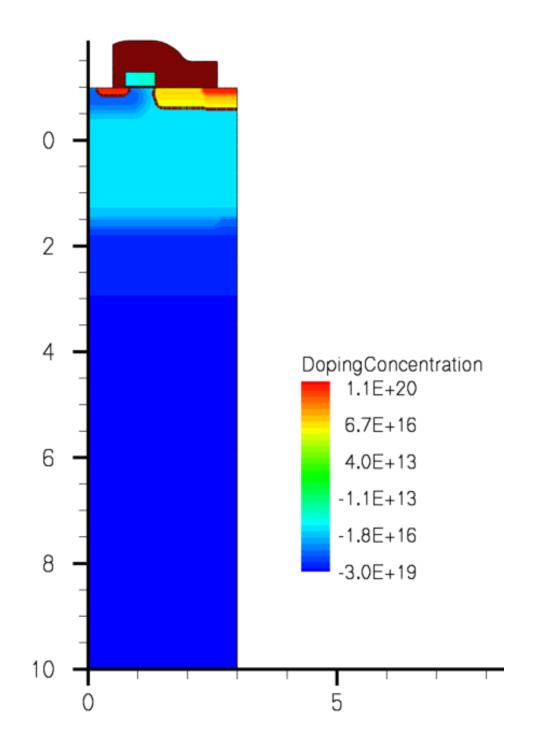

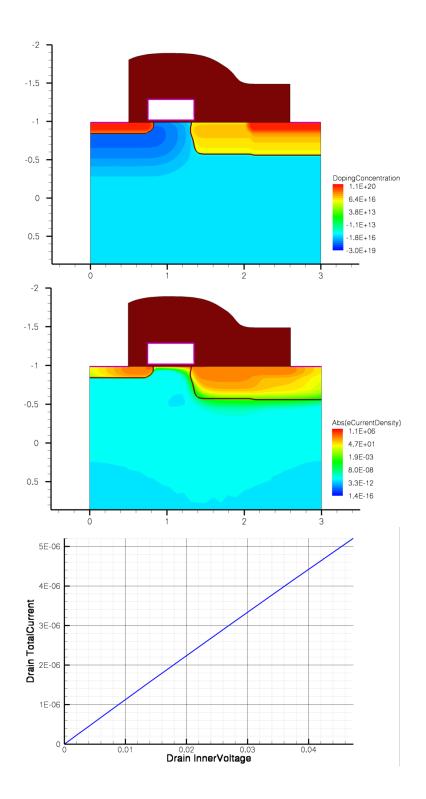

| Figure 20: Simulated 25 V LDMOS Structure                                  | 81 |

| Figure 21: | Simulated 25 V LDMOS ON-State Operation                                    | .82 |

|------------|----------------------------------------------------------------------------|-----|

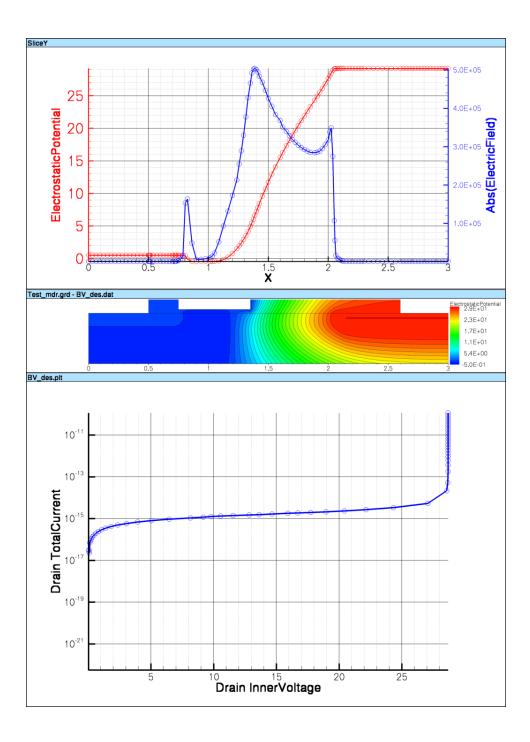

| Figure 22: | Simulated 25 V LDMOS Surface Potential and Electric Field                  | .83 |

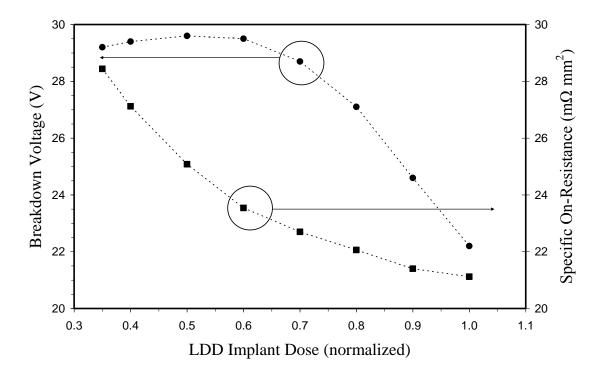

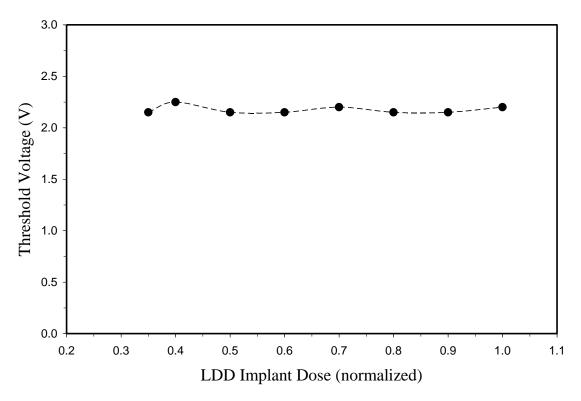

| Figure 23: | Simulated LDD Implant Dose versus BV <sub>DSS</sub> and R <sub>DSON</sub>  | .84 |

| Figure 24: | Simulated LDD Implant Dose vs. Threshold Voltage                           | .85 |

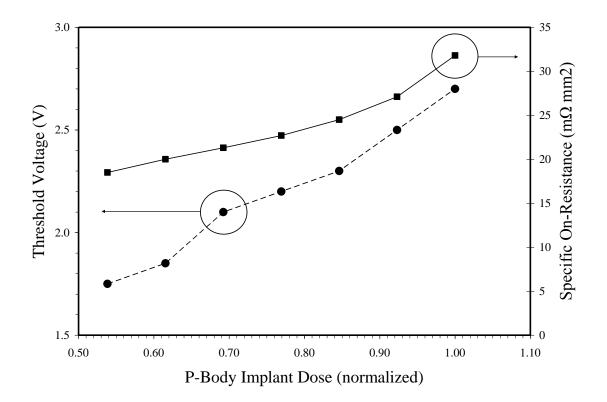

| Figure 25: | Simulated P-Body Implant Dose versus $V_{\text{TH}}$ and $R_{\text{DSON}}$ | .86 |

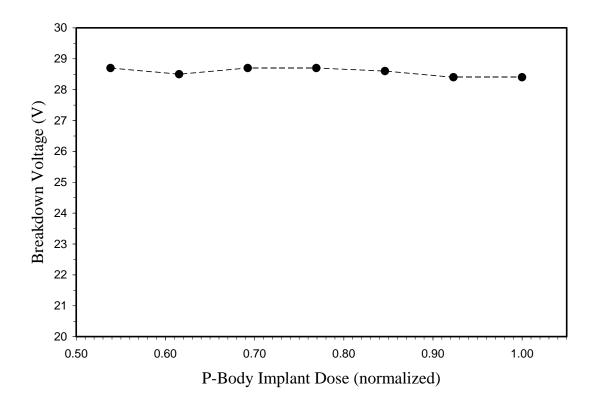

| Figure 26: | Simulated P-Body Implant Dose versus BV <sub>DSS</sub>                     | .87 |

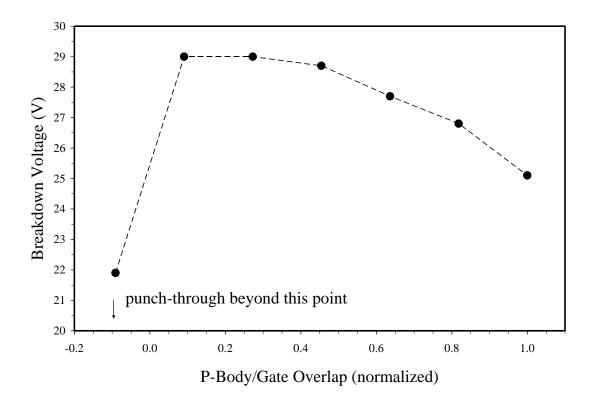

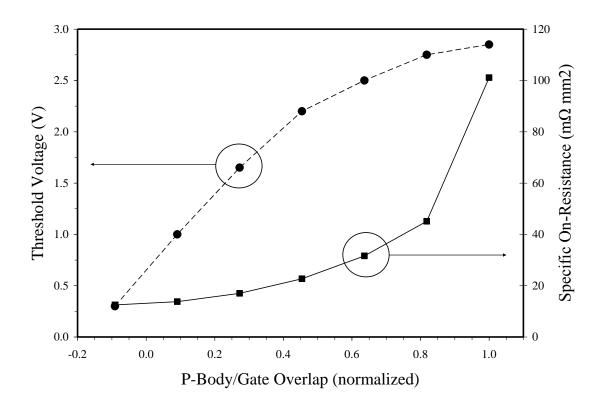

| Figure 27: | Simulated P-Body/Gate Overlap versus BV <sub>DSS</sub>                     | .88 |

| Figure 28: | Simulated P-Body/Gate Overlap versus $V_{\text{TH}}$ and $R_{\text{DSON}}$ | .89 |

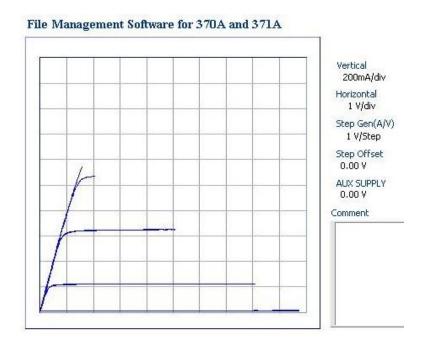

| Figure 29: | Measured Forward IV Characteristic of PCM Test Transistor                  | .91 |

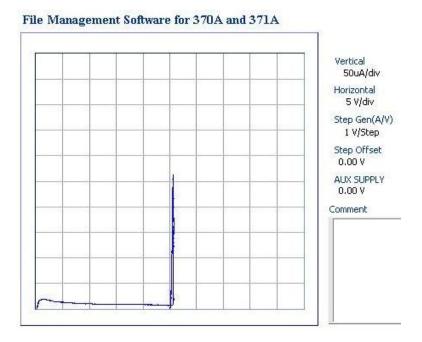

| Figure 30: | Measured BVDSS of PCM Test Transistor                                      | .91 |

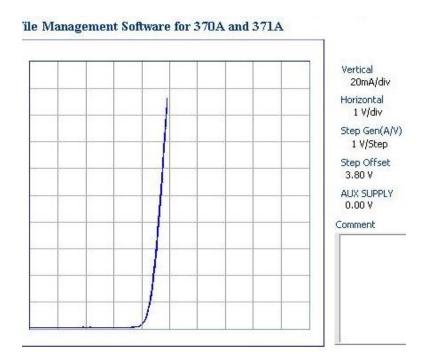

| Figure 31: | Measured VTH of PCM Test Transistor                                        | .92 |

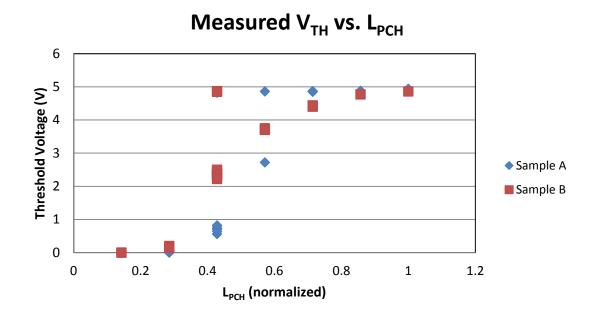

| Figure 32: | Measured Threshold Voltage vs. P-Channel Length                            | .92 |

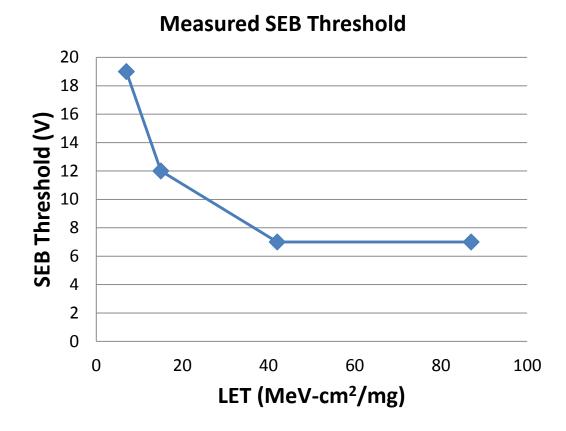

| Figure 33: | Measured SEB Threshold Voltage vs. LET                                     | .94 |

| Figure 34: | LDMOS Structure for SEE Simulations (Design 1)                             | .96 |

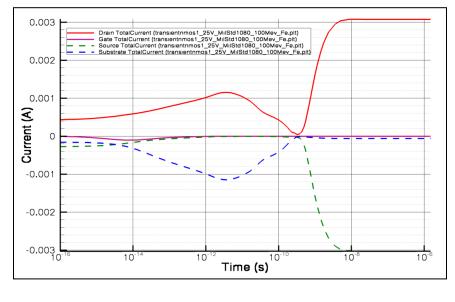

| Figure 35: | Simulated Single Event Burnout Waveforms (Design 1)                        | .98 |

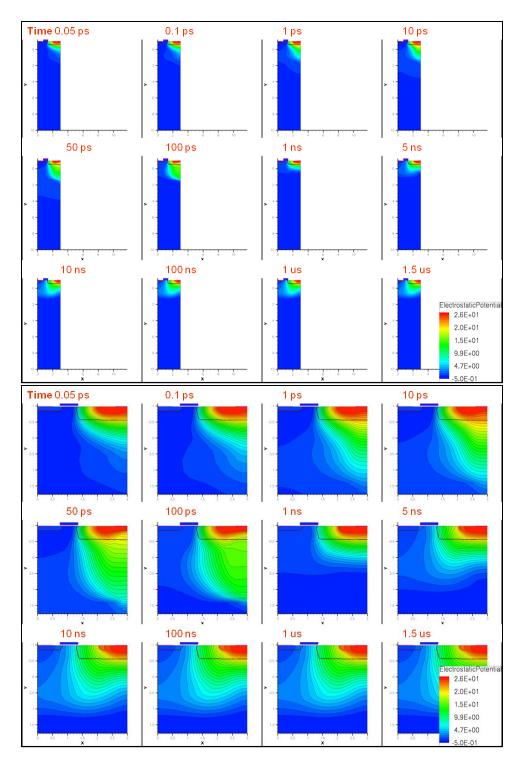

| Figure 36: | Simulated Electrostatic Potential During Heavy Ion Strike (Design 1)       | .99 |

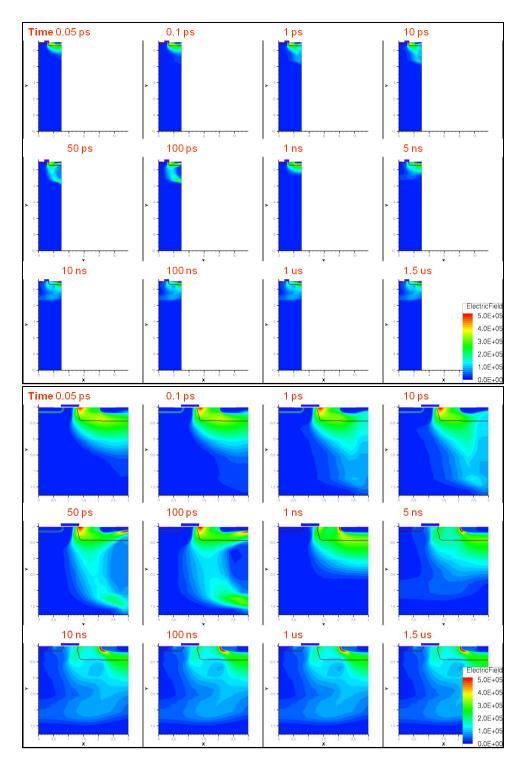

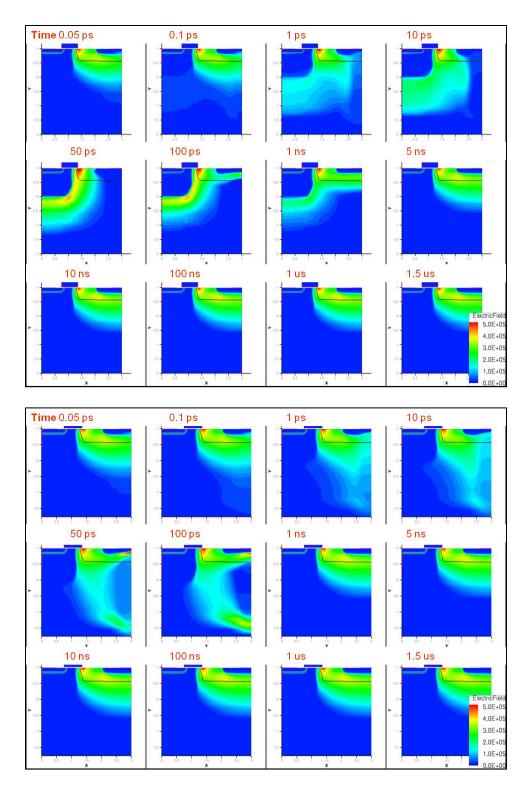

| Figure 37: | Simulated Electric Field During Heavy Ion Strike (Design 1)1               | 00  |

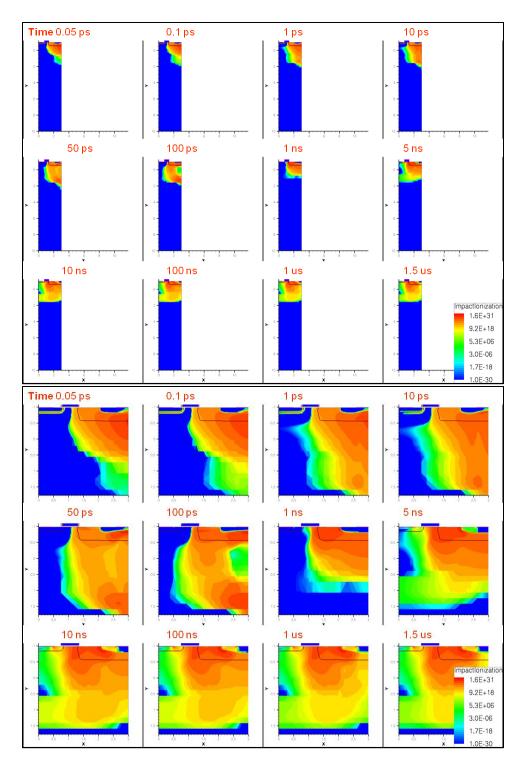

| Figure 38: | Simulated Impact Ionization During Heavy Ion Strike (Design 1)1            | 01  |

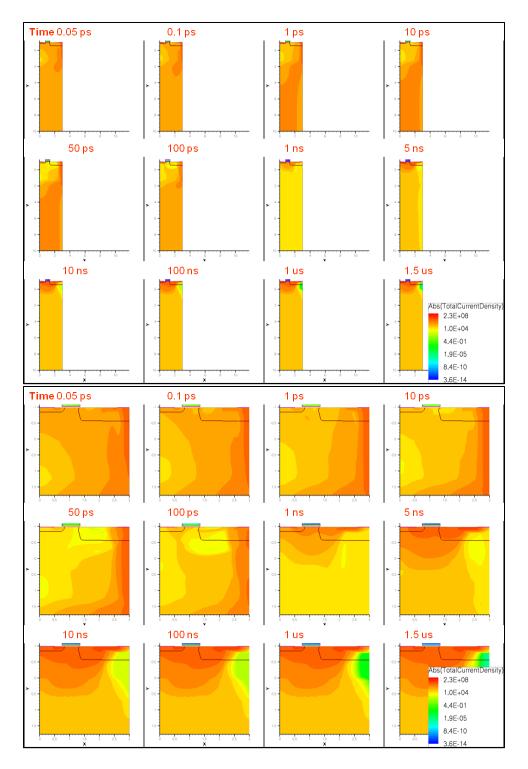

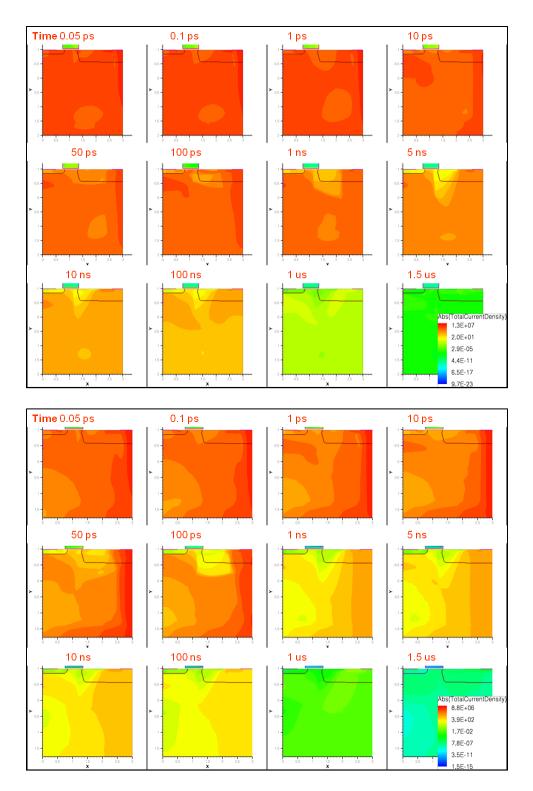

| Figure 39: | Simulated Total Current Density During Heavy Ion Strike (Design 1)1        | 02  |

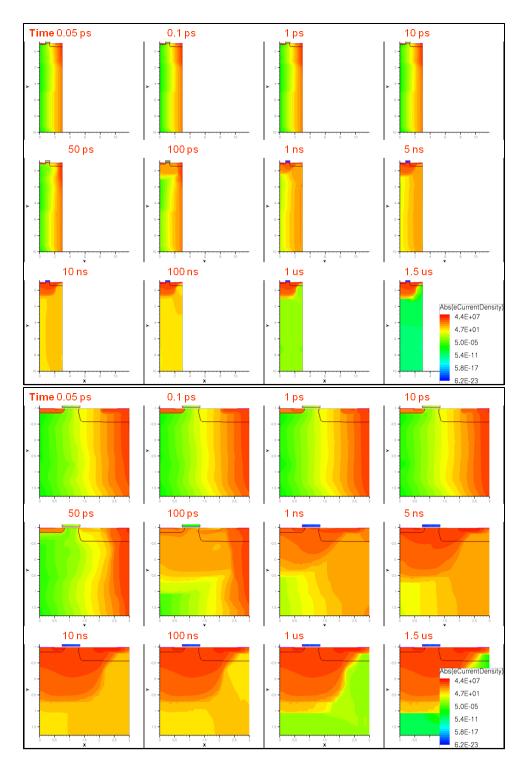

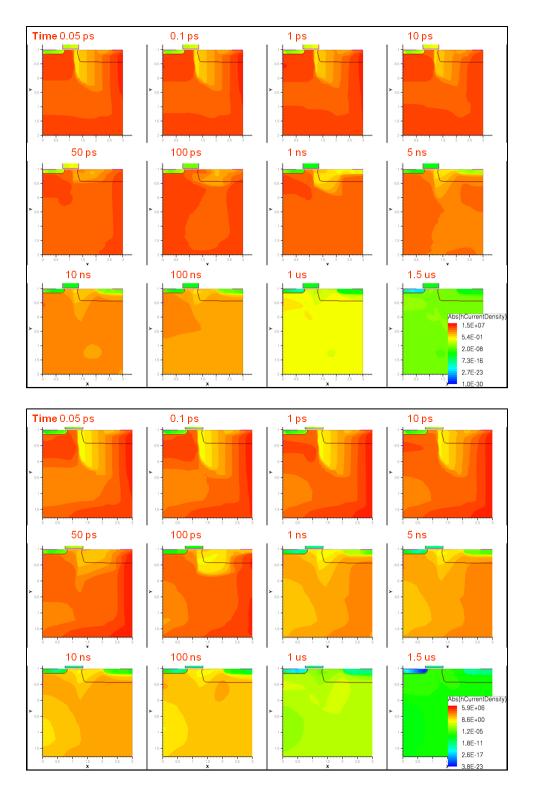

| Figure 40: | Simulated Electron Current Density During Heavy Ion Strike (Design 1)1     | .03 |

| Figure 41: | Hole Current Density During Heavy Ion Strike (Design 1)1                   | 04  |

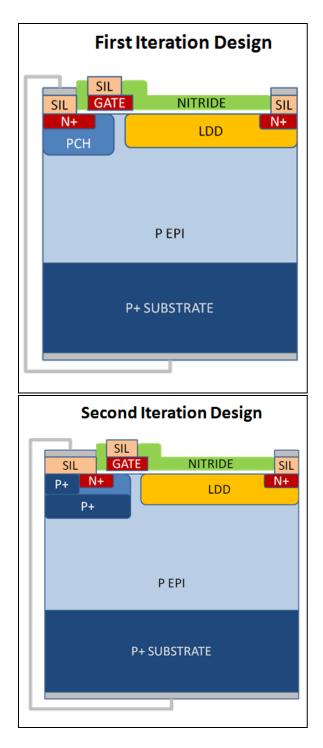

| Figure 42: | First and Second Iteration 25 V LDMOS Designs1                             | 06  |

| Figure 43: | Redesigned 25 V LDMOS with P+ Buried Layer Source Tie                                   | .107 |

|------------|-----------------------------------------------------------------------------------------|------|

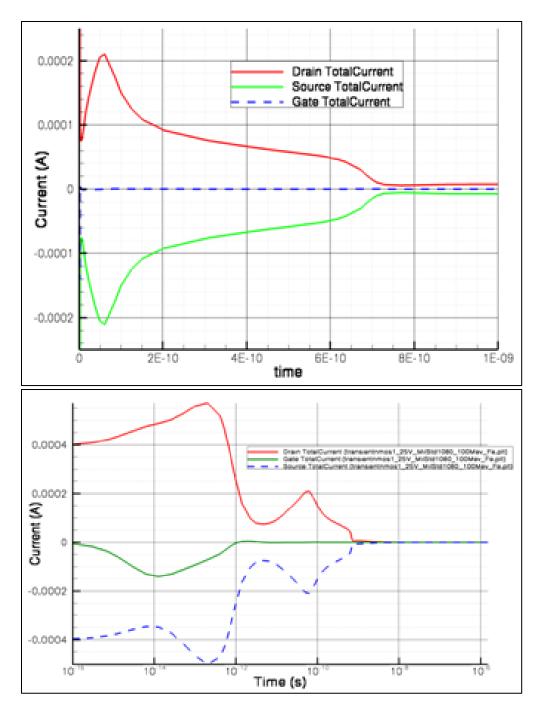

| Figure 44: | Simulated Single Event Transient Waveforms<br>(Design 2 Floating Substrate)             | .109 |

| Figure 45: | Simulated Single Event Transient Waveforms<br>(Design 2 Grounded Substrate)             | .110 |

| Figure 46: | Simulated Electrostatic Potential During Heavy Ion Strike (Design 2)                    | .111 |

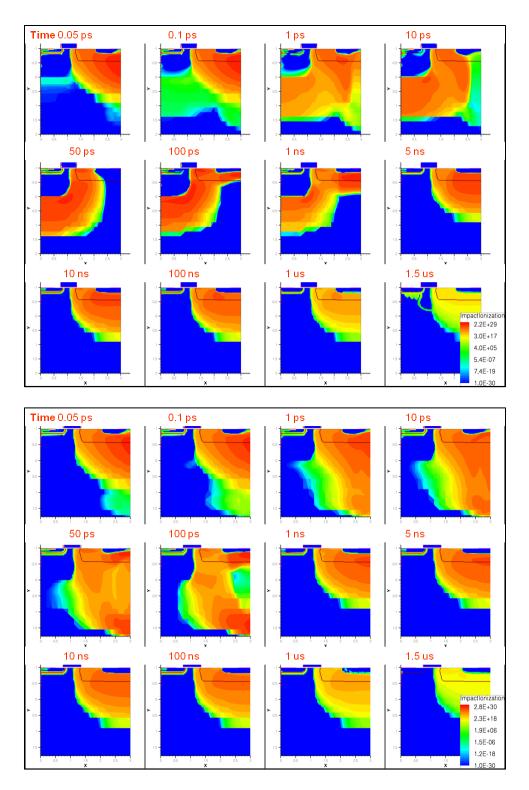

| Figure 47: | Simulated Electric Field During Heavy Ion Strike (Design 2)                             | .112 |

| Figure 48: | Simulated Impact Ionization During Heavy Ion Strike (Design 2)                          | .113 |

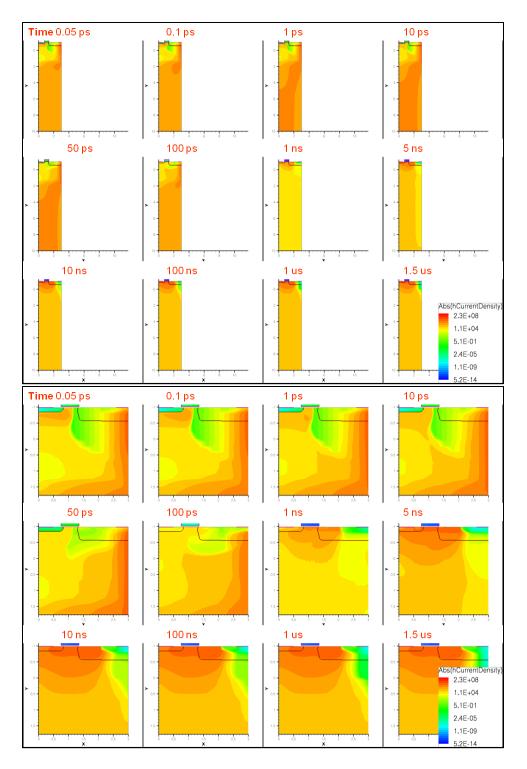

| Figure 49: | Simulated Total Current Density During Heavy Ion Strike (Design 2)                      | .114 |

| Figure 50: | Simulated Hole Current Density During Heavy Ion Strike (Design 2)                       | .115 |

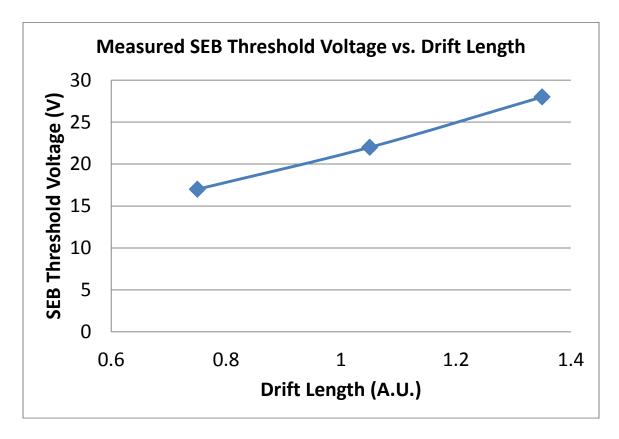

| Figure 51: | Measured SEB Threshold vs. Drift Length (Second Iteration)                              | .117 |

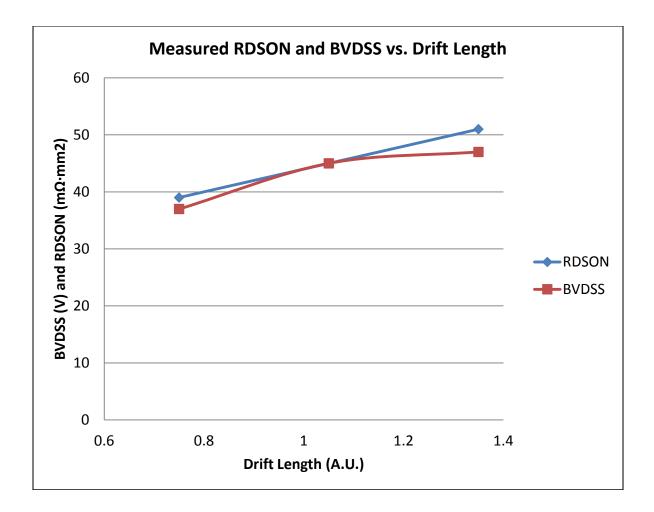

| Figure 52: | Measured $BV_{DSS}$ and $R_{DSON}$ vs. Drift Length (Second Iteration)                  | .118 |

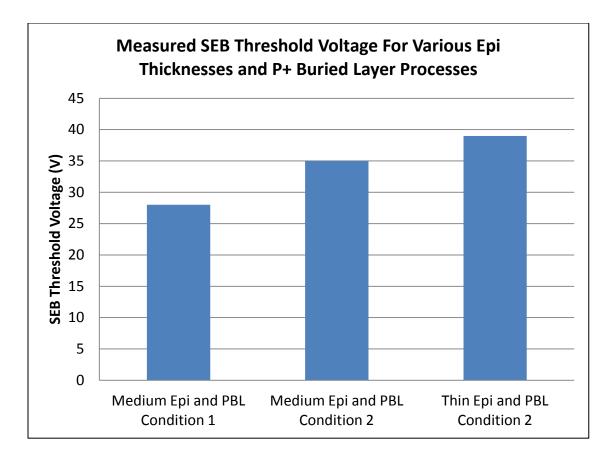

| Figure 53: | SEB Threshold Voltage vs. Epi Thickness and P+ Buried Layer Implant                     | .119 |

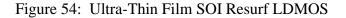

| Figure 54: | Ultra-Thin Film SOI Resurf LDMOS                                                        | .123 |

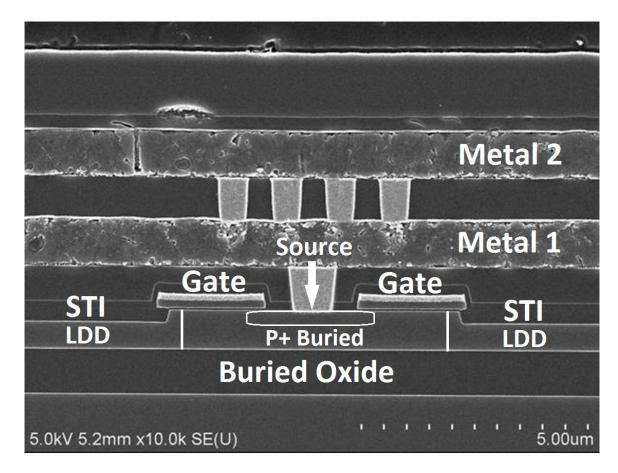

| Figure 55: | SOI LDMOS on N-Type SOI with Field Oxide and Gate Field Plate                           | .123 |

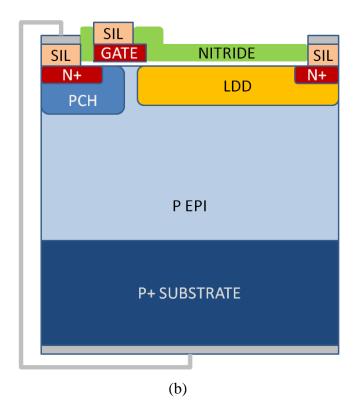

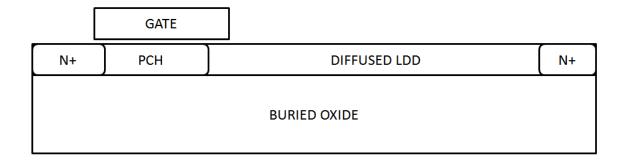

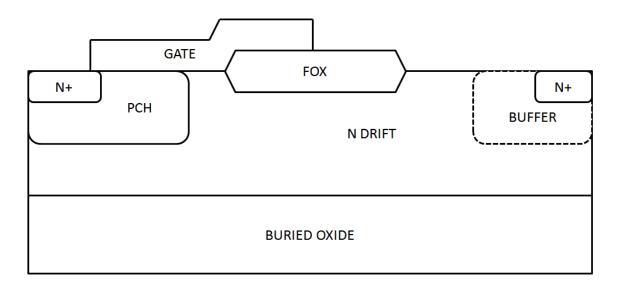

| Figure 56: | Cross Section Drawing of SEE-Hardened 150 V SOI Resurf LDMOS                            | .125 |

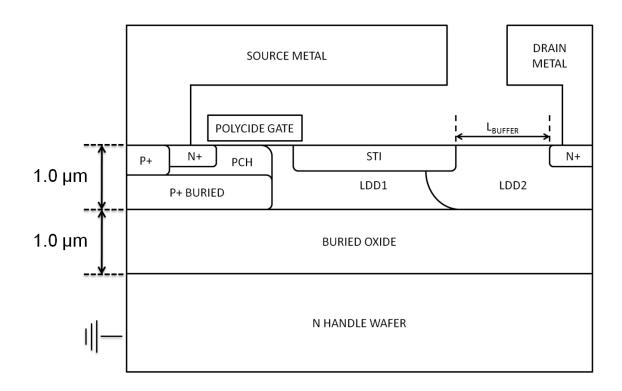

| Figure 57: | 150 V SOI LDMOS SEM Cross Section                                                       | .126 |

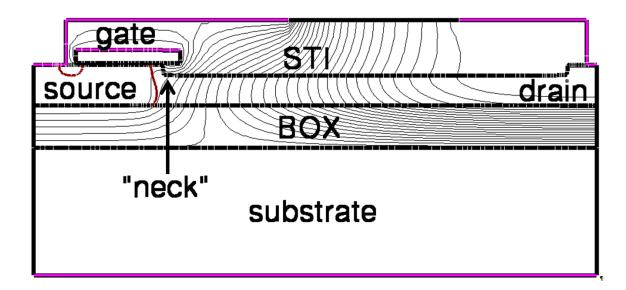

| Figure 58: | Critical Layout Dimensions of 150 V SOI Resurf LDMOS                                    | .129 |

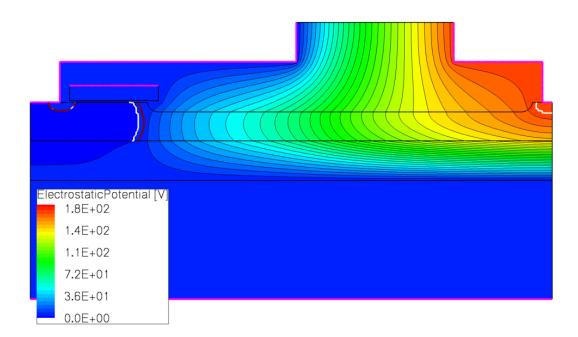

| Figure 59: | Simulated Equipotential Contours of SOI LDMOS at $V_{DS} = 150 \text{ V}$               | .131 |

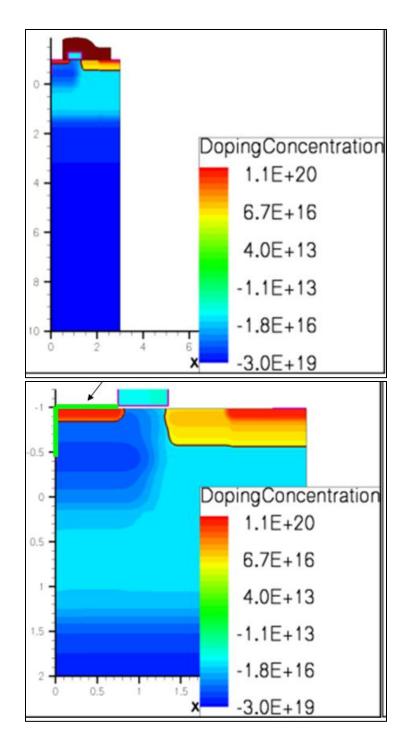

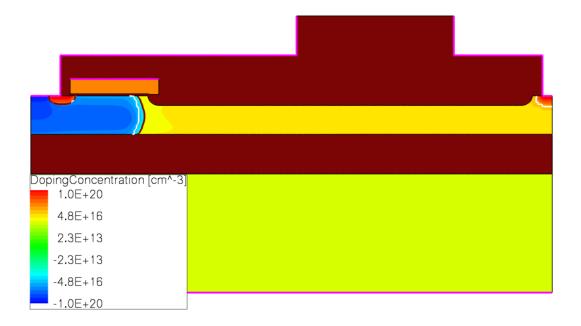

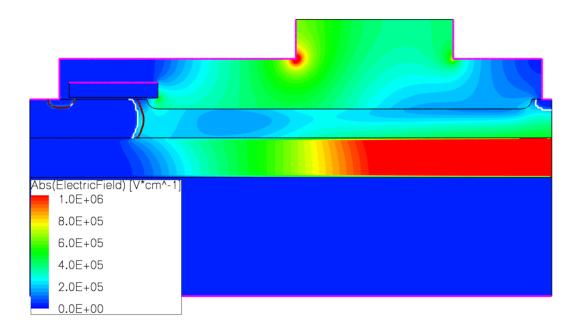

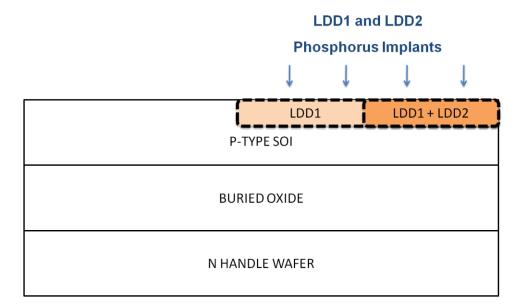

| Figure 60: | Simulated Doping Concentration of 150 V SOI Resurf LDMOS<br>Without Buffer              | .132 |

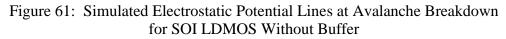

| Figure 61: | Simulated Electrostatic Potential Lines at Avalanche Breakdown for LDMOS Without Buffer | .132 |

| Figure 62: | Simulated Electric Field Magnitude During Avalanche Breakdown for LDMOS Without Buffer  | .133 |

| Figure 63: | 150 V SOI Resurf LDMOS Fabrication Process Flow                                |

|------------|--------------------------------------------------------------------------------|

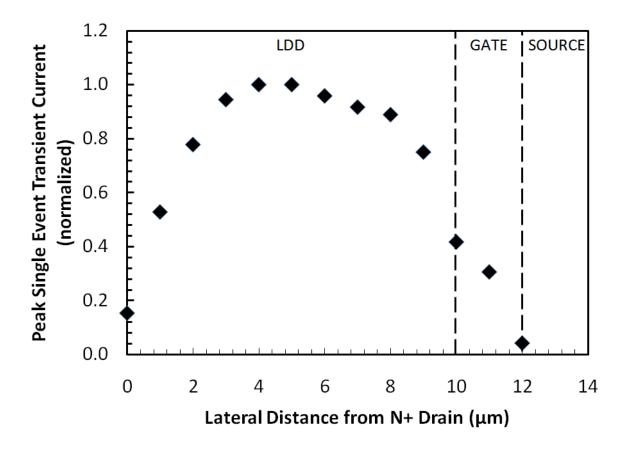

| Figure 64: | Simulated SOI LDMOS Sensitivity to Ion Strike Location                         |

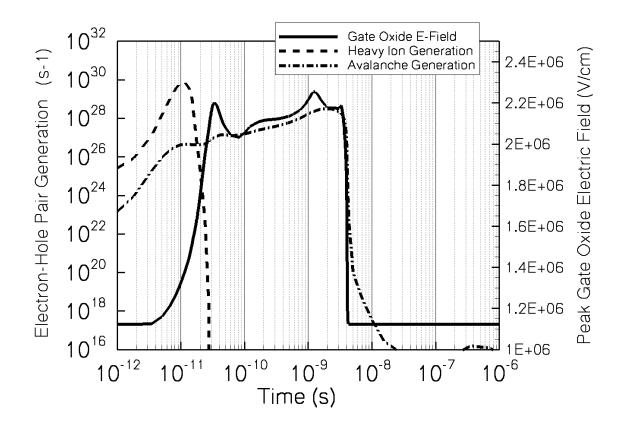

| Figure 65: | Simulated Single Event Transient Waveform                                      |

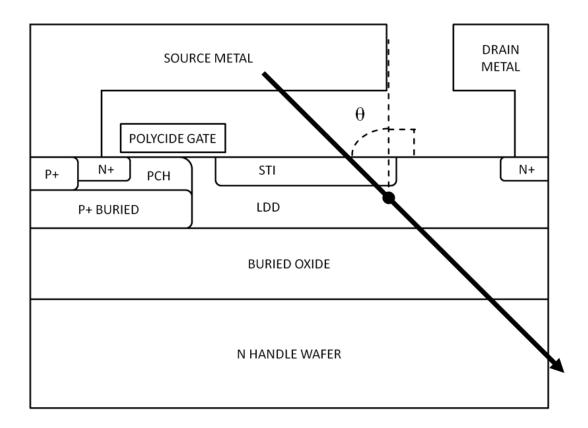

| Figure 66: | Diagram of Heavy Ion Angled Trajectory143                                      |

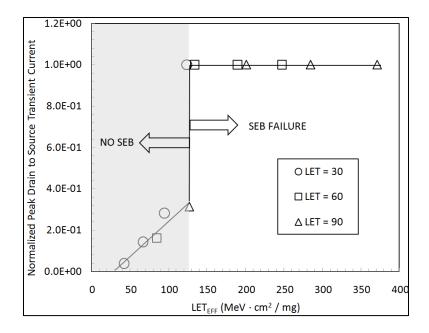

| Figure 67: | Simulated 150 V SOI LDMOS SEB Safe Operating Area144                           |

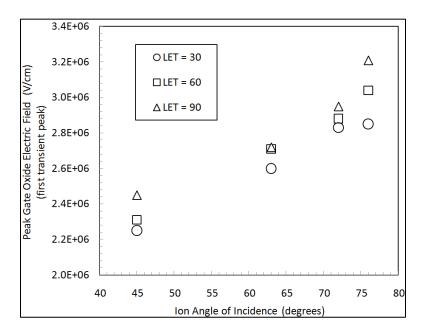

| Figure 68: | Simulated Gate Oxide Electrical Stress vs. Ion Angle of Incidence144           |

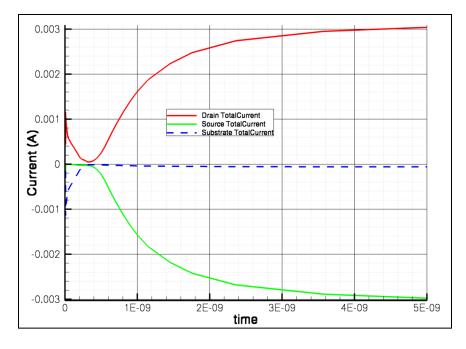

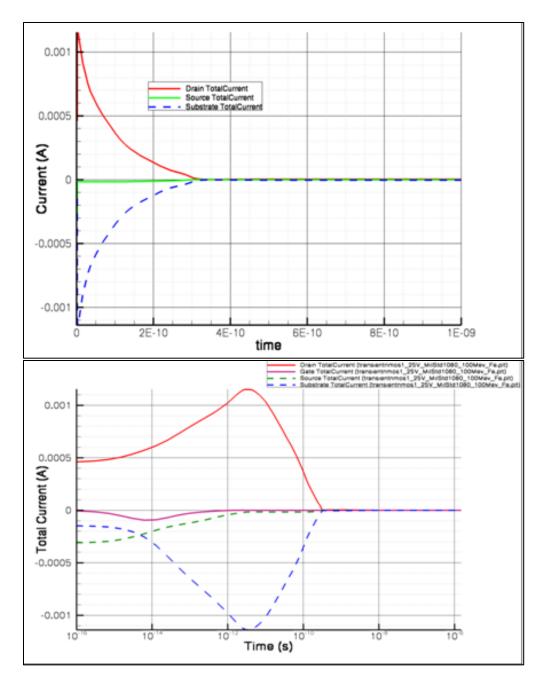

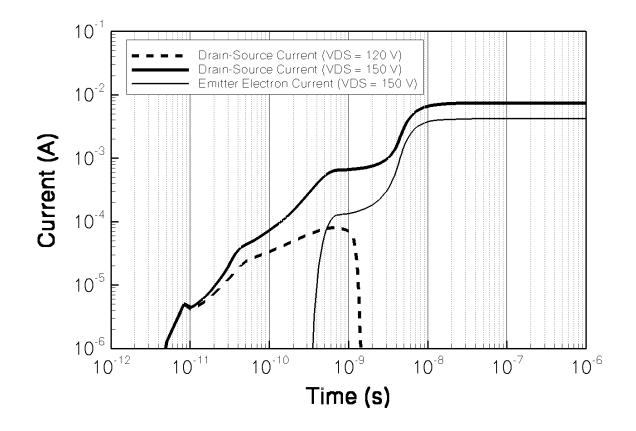

| Figure 69: | Simulated Single Event Transient and Single Event Burnout Waveforms 147        |

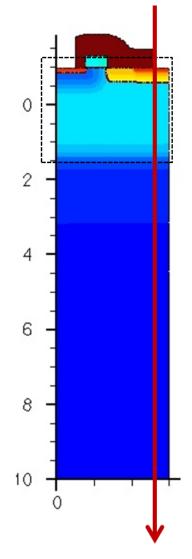

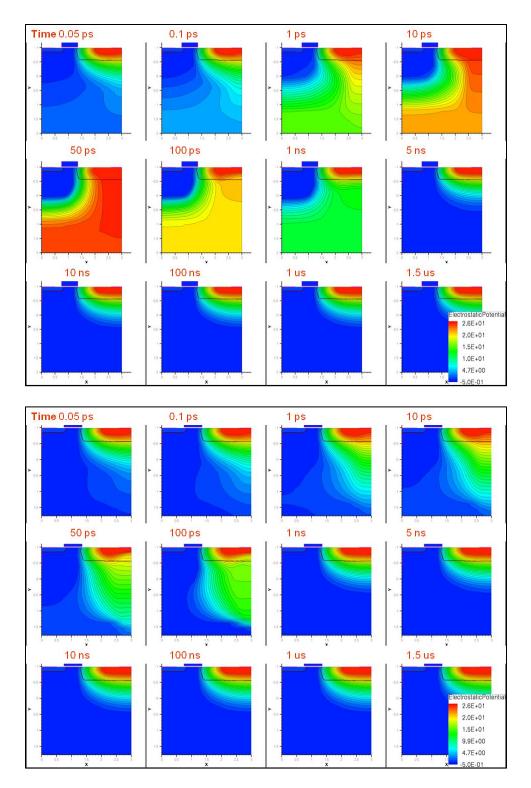

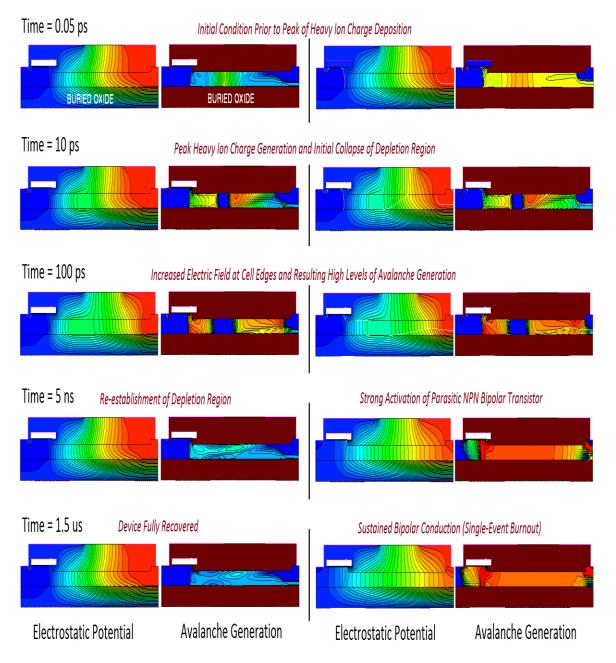

| Figure 70: | 150 V SOI LDMOS Time Evolution of Heavy Ion Strike<br>and Single Event Burnout |

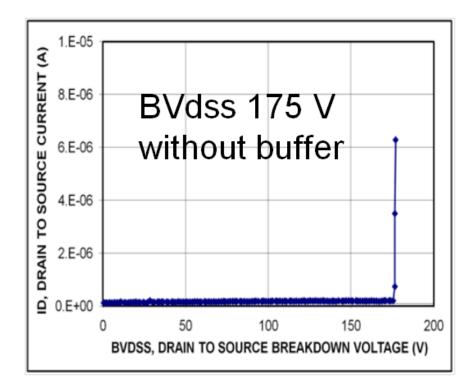

| Figure 71: | Measured BV <sub>DSS</sub> of SOI Resurf LDMOS                                 |

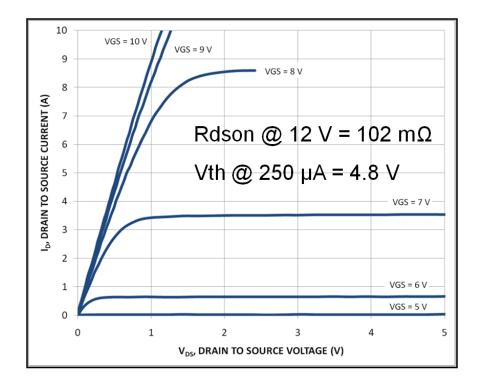

| Figure 72: | Measured Forward IV Characteristic of SOI Resurf LDMOS151                      |

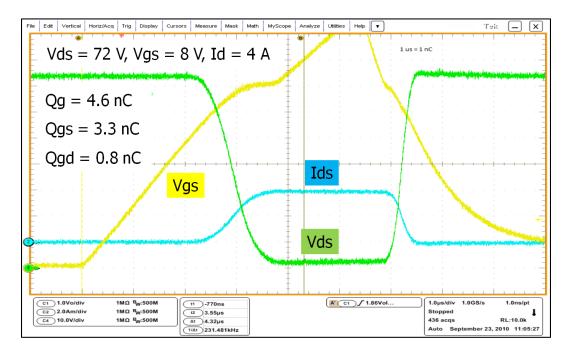

| Figure 73: | Measured Gate Charge Waveform of SOI Resurf LDMOS152                           |

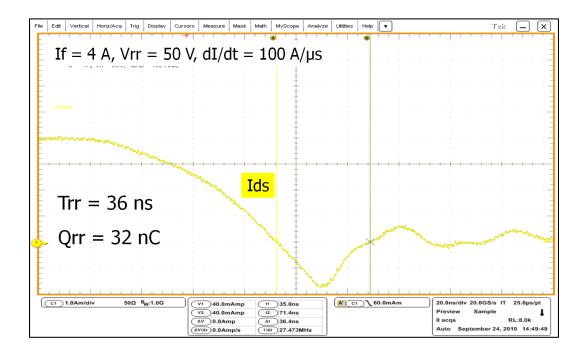

| Figure 74: | Measured Body Diode Reverse Recovery Waveform<br>of SOI Resurf LDMOS           |

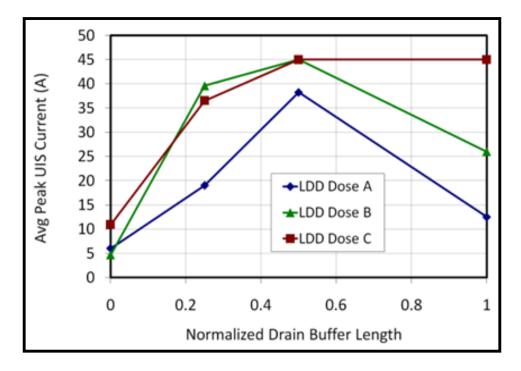

| Figure 75: | Measured UIS Current vs Drain Buffer Length<br>for Various Process Splits      |

## LIST OF TABLES

| Table 1: | Requirements of Power MOSFETs in Modern POL DC-DC Converters17  |     |  |

|----------|-----------------------------------------------------------------|-----|--|

| Table 2: | : Design Considerations for Improving SEB Safe Operating Area51 |     |  |

| Table 3: | Simulated 25 V LDMOS Fabrication Process                        | 80  |  |

| Table 4: | Key Electrical Parametrics: Comparison Against Modern 150 V Pow | /er |  |

|          | MOSFETs1                                                        | 53  |  |

| Table 5: | Heavy Ion SEB / SEGR Experimental Results1                      | 56  |  |

## LIST OF ACRONYMS AND ABBREVIATIONS

- BV<sub>DSS</sub>.....Drain to Source Breakdown Voltage

- BJT.....Bipolar Junction Transistor

- DUT .....Device Under Test

- EPI.....Silicon Epitaxial Layer

- FET .....Field Effect Transistor

- FOM ......Figure of Merit

- g<sub>m</sub> .....MOSFET Transconductance

- IC.....Integrated Circuit

- L<sub>D</sub>.....Drift Length

- LDD .....Lightly Doped Drain

- LDMOS.....Lateral Double-Diffused MOSFET

- MOSFET......Metal-Oxide-Semiconductor Field Effect Transistor

- N<sub>D</sub>.....N Drift Region Doping Concentration

- PCH.....P-Channel Region (also called P-Base)

- Q<sub>G</sub>.....Gate Charge

- Q<sub>GD</sub>.....Gate to Drain Charge

- Q<sub>GS</sub>.....Gate to Source Charge

- Q<sub>RR</sub>.....Body Diode Reverse Recovery Charge

- R<sub>B</sub>.....Base Resistance

- R<sub>D</sub>.....Drift Resistance

R<sub>DSON</sub>.....Drain to Source On-State Resistance

Resurf......Reduced Surface Field Effect

SEB .....Single Event Burnout

SEE .....Single Event Effect(s)

SEL .....Single Event Latchup

SEGR .....Single Event Gate Rupture

SET .....Single Event Transient

SEU.....Single Event Upset

TID.....Total Ionizing Dose

TrenchFET ..... Trench Gate Vertical Power MOSFET

T<sub>RR</sub>.....Body Diode Reverse Recovery Time

VDMOS ......Vertical Double-Diffused MOSFET

V<sub>DS</sub>.....Drain to Source Voltage

V<sub>GS</sub>.....Gate to Source Voltage

V<sub>TH</sub>.....MOSFET Gate to Source Turn-On Voltage (Threshold Voltage)

x<sub>i</sub>.....Junction Depth

## **CHAPTER ONE: INTRODUCTION**

Modern electronics systems are based in most part upon silicon metal oxide semiconductor field effect transistor (MOSFET) technology. This technology is not only found in all types of modern digital electronics but also is the driving force within the power electronics circuits that drive those digital systems. As with all modern MOS technology, the specialized transistors used in power supplies remain vulnerable to all types of damaging and destructive effects caused by ionizing radiation [6][7]. These effects do not represent a significant concern in most environments, however they are of paramount importance for electronics systems designed to operate in ionizing radiation environments such as nuclear power facilities, medical equipment, and especially the most hostile radiation environments – earth orbit and deep space. Because ionizing radiation effects are only found in these and a few other unique environments, most MOS devices are not designed to withstand these effects. Devices and systems that are specially designed to withstand ionizing radiation effects are termed "radiation-hardened", or simply rad-hard.

In the case of power MOSFET technology, the differences between standard commercial devices and rad-hard devices are significant, not only in terms of cost, but also in terms of design and fabrication. The special features and design methods found in today's rad-hard power MOSFETs have arisen from decades of study of ionizing radiation effects in MOS devices, and specifically a wealth of study of one power device in particular – the planar VDMOS. The planar VDMOS has exclusively dominated the

market of rad-hard power MOSFETs, but unfortunately this device offers no further potential in terms of improving electrical performance. This leaves rad-hard power electronics technology at an impasse. Without the development of a replacement power MOSFET technology, the further advancement of power electronics in radiation environments is basically halted. For this reason, there has been a recent drive to develop alternatives to rad-hard VDMOS technology.

One such alternative we are exploring is the power LDMOS. Recently this device has found use in some of the most advanced MHz frequency DC-DC converter systems in the world. The LDMOS therefore offers huge potential for the modernization of radiation hard power systems, but it also presents some unique challenges, not the least of which is a lack of previous scientific study of ionizing radiation effects in lateral power MOSFET structures. A wealth of information is available for deep submicron NMOS devices, which are lateral structures, but these studies cannot take into account the radiation-induced failure mechanisms specific to higher voltage power MOSFET structures, specifically the single event effects such as single event burnout and single event gate rupture.

As part of an investigation into destructive SEE in lateral power MOSFETs, the author has designed and fabricated two types of discrete power LDMOS device with features, layout, and fabrication methods intended to provide hardness against SEE and other ionizing radiation effects. These devices are presented as characteristic representatives of two different power LDMOS technologies, both intended for use in MHz frequency switching DC-DC converters, similar in terms of electrical performance to state of the art commercial trench VDMOS power MOSFET (TrenchFET) technology.

### Evolution of Modern Power Electronics and Power Semiconductor Devices

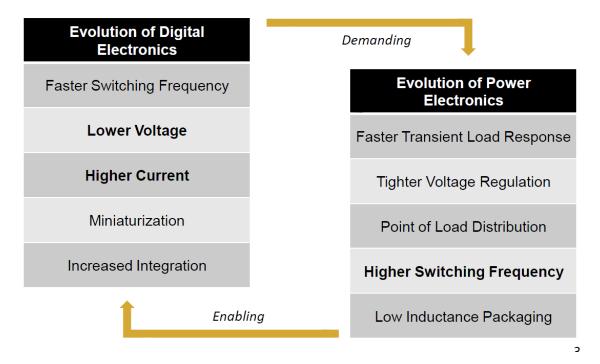

Advancements in semiconductor device scaling and integration, especially in digital circuits, have largely driven the advancement of all types of modern electronics systems. Across the history of their development, digital components have become smaller and faster, with ever increasing density and complexity. Today's microprocessors operate at ever decreasing voltages and increasing currents, and as the requirements of these systems have changed, the technology of power electronics must become more advanced in order to keep pace. Figure 1 outlines some of the important relationships between advances in digital electronics and the accompanying demands placed on power electronics. Without corresponding advances in power electronics, modern computer systems would be penalized both in terms of computing performance and electrical efficiency.

The power electronics circuit which has the most impact on overall computer system electrical efficiency is the DC-DC converter. Most computing systems run off a 12 V DC bus, which is then stepped down to lower DC voltages throughout the system, depending on the demands of various computer components. The various microprocessors, memories, controllers, fans, drives, and other components each may come with different voltage and current requirements. Power dissipation across these different loads may range from milliWatts to tens or even hundreds of Watts. As such, an all-in-one DC-DC converter system does not yield ideal efficiency across such a wide variety of loads, especially when these loads are scattered throughout the computer system, with relatively large distances between components.

**Coupling of Modern Digital Systems and Power Electronics**

The enablement of modern digital electronics systems through recent advances in power electronics technology.

Figure 1: Coupling of Modern Digital Systems and Power Electronics

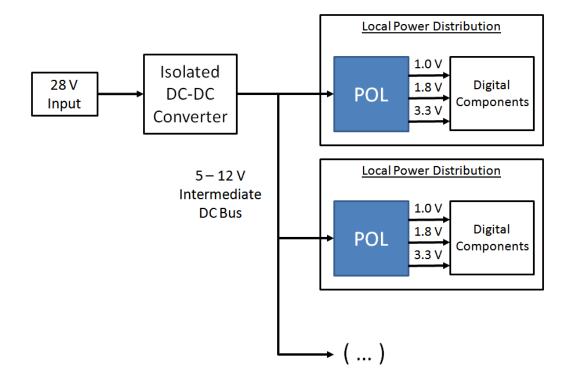

Modern DC-DC converter technology has therefore evolved to match the distributed nature of these power demands with so-called distributed point-of-load (POL)

power architectures. POL power architecture refers to a method of distributing multiple DC-DC converter circuits throughout a system, with each converter being placed in close proximity to its own specific load [4]. Each converter is designed to meet the voltage and current requirements of its load in the most efficient way possible. An illustration of the distributed POL architecture is provided in Figure 2.

Simplified illustration of a distributed POL power architecture for a battery-powered space satellite system Figure 2. Point-of-Load DC-DC Converter Architecture

In addition to new types of power distribution architectures, many modern digital systems also demand miniaturization of surrounding power electronics circuits and components. The requirement for small volume, along with a need for faster transient load response, has driven power electronics circuits to operate at higher and higher switching frequencies, with some modern POL DC-DC converters now operating in the MHz frequency range. By switching at higher frequencies, a smaller inductor can be used in the DC-DC converter circuit. Since the inductor is by far the largest component in the circuit, this results in significant decrease in overall volume for the converter.

This increase in switching frequency brings several challenges. Switching tens of amps at MHz frequencies requires extremely low inductance packaging and routing. At such high dI/dt, even small parasitic inductances can cause transient voltage spikes can easily damage sensitive digital components, not to mention the power semiconductor components themselves. This requirement for low inductance design and packaging has resulted in a trend toward surface mounted "brick" DC-DC converter technology in desktop and server computers and monolithically integrated power system on chip (PSoC) technology for handheld devices, both of which are designed to operate at MHz frequencies with high volumetric power density (hundreds of W/in<sup>3</sup>).

## Introduction to Power MOSFET Design Considerations

These new demands on power electronics circuits, specifically higher current, lower voltage, and higher switching frequency place new requirements on the power semiconductor devices which drive those circuits. The power semiconductor device at the heart of the modern DC-DC converter is the n-channel power MOSFET. The overall efficiency of the power switching circuit is influenced primarily by power losses across the power MOSFET. These power losses can be separated into two main types: *conduction* losses and *switching* losses.

#### Conduction Losses in Power MOSFETs

Conduction loss refers to power dissipation across the power MOSFET while it is operating in the "on" state, that is to say a positive  $V_{GS}$  potential is applied, and the MOSFET is actively conducting current through the MOS channel. Conduction power losses are determined primarily by the drain to source on-state resistance R<sub>DSON</sub> of the MOSFET, and the power loss relationship is simply  $I_{DS}^2 \cdot R_{DSON}$ , where  $I_{DS}$  is the total onstate current. In terms of power MOSFET design, R<sub>DSON</sub> is influenced by many factors. The most direct influence on R<sub>DSON</sub> is the die size of the MOSFET. A power MOSFET die is actually a plurality of hundreds or even thousands of smaller parallel transistor cells, with the drains and sources of each cell electrically connected together in parallel, and each tied to a common gate terminal. Naturally, a larger die contains more area and therefore more parallel transistor stripes. Thus R<sub>DSON</sub> has an inverse linear relationship with die size. Die size, however, is more or less independent of device technology and transistor cell design, and comparing the R<sub>DSON</sub> of devices with two different die sizes tells very little about the merits of the technologies themselves. In order to effectively compare competing technologies, the R<sub>DSON</sub> must be normalized to die area. This normalized measurement is known as "area-specific  $R_{DSON}$ ", or simply "specific  $R_{DSON}$ ", and is generally given in units of m $\Omega \cdot mm^2$ . The lower the specific  $R_{DSON}$  of a power MOSFET, the smaller die size will be required to achieve the same  $R_{DSON}$ , and therefore the more efficient the technology.

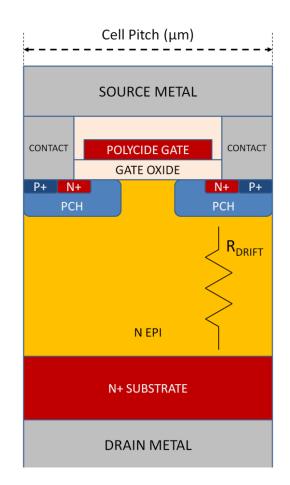

Specific  $R_{DSON}$  is influenced by many components, the most important of which for medium to high voltage power MOSFETs are the transistor cell pitch and the transistor drift resistance. Cell pitch is simply the length of the repeatable transistor structure, usually from contact to contact. Specific  $R_{DSON}$  has a linear relationship with transistor cell pitch, so the most direct method of reducing specific  $R_{DSON}$  is to reduce the cell pitch. Drift resistance refers to the resistance of the n-type lightly doped drain region (the n epitaxial layer in a VDMOS) between the N+ substrate and the P-Channel diffusion. Figure 3 shows a typical planar VDMOS power MOSFET cell, with the cell pitch and drift resistance labeled.

In terms of minimizing  $R_{DRIFT}$ , the classic design tradeoff is between  $R_{DRIFT}$  and drain to source breakdown voltage (BV<sub>DSS</sub>). In any power MOSFET structure, BV<sub>DSS</sub> is primarily determined by two design variables, drift length (L<sub>D</sub>) and drift region doping concentration (N<sub>D</sub>), both of which directly affect  $R_{DRIFT}$ . Higher breakdown voltage requires a longer L<sub>D</sub> and a smaller N<sub>D</sub>, both of which increase  $R_{DRIFT}$ . Very little can be done to reduce L<sub>D</sub> for a device with a given BV<sub>DSS</sub> rating, because of the fundamental limitation of the critical electric field (E<sub>CRIT</sub>) in silicon, which is somewhat dependent on doping concentration and lies approximately between  $2.5 \times 10^5$  and  $5.0 \times 10^5$  V/cm. Once the applied drain to source voltage (V<sub>DS</sub>) causes E<sub>CRIT</sub> to form within the silicon, high levels of impact ionization occur within the device, and the MOSFET is unable to sustain the applied voltage without conducting large amounts of current. In this condition, the MOSFET is said to be under avalanche breakdown, and the voltage at which this occurs is called the "avalanche voltage". The rated  $BV_{DSS}$  which appears on a power MOSFET datasheet is always less than the actual avalanche voltage, generally by 10 – 20%. This difference between the rated  $BV_{DSS}$  and the avalanche voltage is called "de-rating".

Planar VDMOS structure showing cell pitch and drift resistance ( $R_{DRIFT}$ ) through the n epitaxial layer, which are the two most influential factors in determining area-specific on-resistance ( $R_{DSON}$ ) of medium to high voltage power MOSFETs.

Figure 3: Planar VDMOS Device Structure

Since L<sub>D</sub> is more or less fixed for a given avalanche voltage, most methods of reducing R<sub>DRIFT</sub> focus on increasing N<sub>D</sub> for a given BVDSS. Two such methods for increasing  $N_D$  both rely upon the so-called reduced surface field effect principle, or "Resurf" principle [8][9]. The Resurf principle is a method of increasing the natural breakdown voltage of a p-n junction by using carefully designed doping distributions, field plates, or other special doping and device geometries to control the spatial distribution of the electric field around the reverse-biased p-n junction. In an ideal Resurf design, the electric field at each point in the depleted semiconductor remains uniform. That is to say, there are no electric field "hot spots" in or around the depletion region which limit the breakdown voltage of the device. In practice, a completely uniform electric field distribution is impossible to achieve, but the spatial electric field distribution in a well designed Resurf structure comes reasonably close and looks very different from a normal p-n diode, in which the peak electric field occurs at the junction and decreases linearly toward the edges of the depletion region. The most popular Resurf design used in modern power devices is a so-called double Resurf or "superjunction" doping profile. A detailed discussion of this design technique is beyond the scope of this work, but a wealth of published literature is available on the subject. Another Resurf technique which applies only to LDMOS power devices is SOI Resurf, which is discussed in detail later in this work. Sufficed to say that implementation of Resurf designs has been the dominant influence on the reduction of R<sub>DRIFT</sub> in modern power MOSFETs.

As mentioned before, the other important metric which directly affects  $R_{DSON}$  for any power MOSFET is the transistor cell pitch. By decreasing the cell pitch, more parallel transistor stripes can be arranged per unit area on the MOSFET die, resulting in a direct linear relationship between transistor cell pitch and specific  $R_{DSON}$ . The cell pitch in a VDMOS device is primarily determined by the design of the source, channel, and junction field effect transistor (JFET) regions, which lie at the surface of the device. The JFET region is the N epi region underneath the poly gate and between the two adjacent P-channel diffusions. This is also sometimes called the "neck" region, which is the preferred terminology in this dissertation, since the term "neck" can also be used in discussion of LDMOS device structure which do not contain a parasitic JFET.

There is little that can be done to reduce the length of the source and channel regions of a power MOSFET, since these feature sizes are constrained by the limits of the available fabrication technology and also the need to prevent punch through or short channel effects between the drain and source. Low R<sub>DSON</sub> VDMOS structures with reduced cell pitch have therefore resulted from the re-design of the more addressable JFET region, resulting in a new type of VDMOS structure known as the Trench Gate VDMOS or so-called "TrenchFET". A simplified TrenchFET device cross section is shown in figure 4. In a TrenchFET, the JFET and poly gate regions are replaced by a trench, which is surrounded by a thin thermal oxide and then refilled with polysilicon. The MOS channel is then formed vertically along the sidewalls of the trench, rather than laterally across the silicon surface as is the case with the planar VDMOS. By replacing the relatively wide JFET and channel regions with a much narrower trench gate, the TrenchFET results in a much smaller cell pitch than the planar VDMOS, and therefore boasts greatly reduced R<sub>DSON</sub>.

Simplified device cross sections for two types of vertical double diffused (VDMOS) power MOFETS. The more modern Trench Gate VDMOS (TrenchFET) exhibits greatly reduced area-specific  $R_{DSON}$  compared to the planar VDMOS, because of its reduced transistor cell pitch.

Figure 4: Planar VDMOS and Trench Gate VDMOS Device Cross Sections

### Switching Losses in Power MOSFETs

Switching losses refers to the power required to turn the MOSFET on and off during operation in the power switching circuit. In terms of the switching efficiency of a DC-DC converter, this term could include power losses related to design of the MOSFET gate driving circuit, however, in a discussion of power semiconductor devices, the term refers only to power losses due to the internal capacitances of the power MOSFET. The two most critical MOSFET parametrics which determine switching efficiency are gate charge ( $Q_G$ ) and body diode reverse recovery charge ( $Q_{RR}$ ). Total gate charge is made up of the sum of gate to drain charge ( $Q_{GD}$ ) and gate to source charge ( $Q_{GS}$ ).  $Q_{GD}$  is also referred to sometimes as "Miller" capacitance. The ratio between  $Q_{GS}$  and  $Q_{GD}$  is determined by the power MOSFET device structure, i.e. how much the gate oxide overlaps either the source or drain regions within the transistor cell. Total  $Q_G$  for a discrete power MOSFET is determined by the gate oxide thickness and the total gate oxide area on the die. The doping concentrations in the silicon near the gate also have a secondary affect on QG, with lighter doping concentrations resulting in lower gate charge. Equation 1 shows a simple method for calculating QG:

$$Q_G = \frac{V \cdot A \cdot \varepsilon_{ox} \cdot \varepsilon_0}{t_{ox}} \tag{1}$$

, where V is the applied voltage across the gate oxide, A is the gate oxide area,  $\varepsilon$  ox is the dielectric constant of the gate oxide (3.9 for SiO2),  $\varepsilon$ 0 is the permittivity of free space, and tox is the gate oxide thickness.

Figure 5 shows cross sections of the planar and trench VDMOS structures with the internal gate capacitances labeled. As is the case with cell pitch, there are certain unavoidable device structure limitations which affect the magnitude of  $Q_G$ , specifically the length of the P-channel and N+ source regions. As such,  $Q_{GS}$  for a given technology remains more or less fixed. Most of the flexibility in terms of designing for low  $Q_G$  is in the reduction of  $Q_{GD}$ , which again is closely related to design of the neck region of the MOSFET. In the planar VDMOS,  $Q_{GD}$  can be reduced by removing some portion of the poly gate which lies over the JFET region. In the trench VDMOS,  $Q_{GD}$  can be reduced by offsetting the polysilicon from the bottom of the trench with a thick insulator. One drawback of the TrenchFET is that the increased cell density per unit area, which gives the device its low specific  $R_{DSON}$ , also results in higher  $Q_G$  per unit area, which makes lowering  $Q_G$  the most challenging aspect of TrenchFET design.

**Planar VDMOS**

Device cross sections showing internal gate capacitances of the planar VDMOS and trench VDMOS power MOSFET structures. Internal gate capacitance is the most important device parametric which influences power MOSFET switching efficiency.

Figure 5: Internal Gate Capacitances in Planar and Trench VDMOS Structures

The other key device parametric for characterizing switching losses is  $Q_{RR}$ , which is the reverse recovery charge of the MOSFET's internal body diode (the diode formed by the drain and source). During normal operation in DC-DC converter circuits, the body diode of the power MOSFET is temporarily forward biased during each switching cycle. This results in an injection of electrons from the N+ drain into the drift region. In order for the MOSFET to full turn off, these electrons must first be removed from the semiconductor. The amount of charge which survives recombination and is collected at the device terminals is  $Q_{RR}$ , and the time required to collect this charge under a given current slew rate and biasing condition is  $T_{RR}$ , the reverse recovery time.

The power losses during reverse recovery are the product of the reverse recovery current multiplied by the junction potential of the body diode, which is usually estimated as 0.7 V. The device designer has very little control over the body diode junction potential, so methods of minimizing reverse recovery power losses focus instead on reducing  $Q_{RR}$ . There are two practical ways to minimize  $Q_{RR}$ . One way is to control the amount of stored charge in the device, which is done by minimizing the volume of the body diode [10]. The other way is to increase the electron recombination rate in the body diode, which is done by increasing the doping concentration of the P-channel region, or the P-base as it is sometimes called. A heavier p doping concentration results in a lower electron lifetime, meaning more electrons recombine in the P-base before being collected at the source electrode.

As is the case for nearly all power MOSFET design considerations, these two methods do not come without tradeoffs. The depth of the body diode is determined primarily by the drift length,  $L_D$ , and it was explained earlier that  $L_D$  cannot be arbitrarily reduced without resulting in a decrease in BV<sub>DSS</sub>. So for a VDMOS device, the reduction in charge collection volume is primarily a function of area, that is to say die size, and so the same techniques used to reduce specific R<sub>DSON</sub> and shrink the die size also help to reduce Q<sub>RR</sub>.

The other method – increasing minority carrier recombination in the P-base – requires either an increase in P-base doping concentration or an increase in channel length. The first, an increase in doping concentration, will result in a corresponding increase in Q<sub>GS</sub> and gate to source turn on voltage (V<sub>TH</sub>), if the p doping concentration near the gate oxide is increased. If  $V_{TH}$  becomes too high, then the device will not even function in the circuit. So, any design which seeks to decrease P-base minority carrier lifetime must be done in such a way as to not strongly influence the doping concentration in the MOS channel region. The second recombination control method, an increase in channel length, results in a decrease in transconductance (g<sub>m</sub>), which is reflected in higher R<sub>DSON</sub>. Additionally, for a planar VDMOS structure, a longer channel results in a longer cell pitch, which again further increases R<sub>DSON</sub>. For a TrenchFET, a longer channel requires a deeper gate trench, which in turns requires a thicker epi layer. This results in a corresponding increase in stored reverse recovery charge, albeit an incremental increase for all but very low voltage devices. In any case this method is not desirable, since it probably does not result in any net increase in device efficiency.

## Recent Advances in Lateral Power MOSFET Technology

As the demands of modern power electronics circuits have evolved toward lower output voltage, higher output current, and higher switching frequency, new demands have been placed on power MOSFETs which has prompted a re-examination of some of the fundamental design tradeoffs related to power MOSFET conduction losses and switching losses. Table 1 illustrates some of the ways in which these new circuit requirements have influenced power MOSFET design in recent years, particularly power MOSFETs designed for use in POL DC-DC converters.

| Demands of Power Electronics in<br>Modern Digital Systems                                  | Impact on Power MOSFET Design                                                                             |

|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Low Voltage                                                                                | MOSFET BV <sub>DSS</sub> < 10 V                                                                           |

| High Current                                                                               | MOSFET $R_{DSON} < 1 \text{ m}\Omega$                                                                     |

| MHz Switching Frequency<br>(enables miniaturization and faster<br>transient load response) | Requires Low MOSFET Gate Charge<br>(Q <sub>G</sub> )<br>Low Inductance Packaging<br>(DirectFET, Flipchip) |

|                                                                                            | Monolithic Integration (SoC)                                                                              |

Table 1. Requirements of Power MOSFETs in Modern POL DC-DC Converters

The power regulation requirements of modern digital electronics drive corresponding advances in power semiconductor device technology.

Older DC-DC converter circuits operated at slower switching frequencies, and most power losses were a result of conduction losses in the MOSFET. As such, the primary design tradeoff for older power MOSFETs was  $BV_{DSS}$  vs.  $R_{DSON}$ . This is still an important tradeoff, but as power MOSFETs are operated at higher switching frequencies, the switching power losses are now equally if not more significant than the conduction losses. Therefore the primary design tradeoff for modern power MOSFETs is no longer  $BV_{DSS}$  vs  $R_{DSON}$ , but is now instead  $R_{DSON}$  vs  $Q_G$ . This is expressed in the modern-day power MOSFET efficiency figure of merit (FOM),  $Q_G \times R_{DSON}$ . From a first order consideration, the power MOSFET with the lowest FOM offers the best efficiency in a fast switching circuit [11].

Modern POL converters not only operate at higher switching frequencies but also at higher current levels. This results in extremely high current slew rates, dI/dt. Just as these high dI/dt's have prompted a move toward low inductance packaging for DC-DC converter modules, so have they prompted similar advances in low inductance power MOSFET packaging. Such advances include so-called DirectFET<sup>™</sup> and flipchip packaging technology, as mentioned in Table 1. Another method of reducing parasitic inductance is to co-package or even monolithically integrate multiple power MOSFET dies. The extreme case of such integration is the power system on chip (PSoC), where the entire DC-DC converter circuit, including magnetic components, is integrated onto a single die. These types of converters might be switched at frequencies in the tens of MHz in order to work with very small integrated inductors.

The higher current levels also demand MOSFETs with very low  $R_{DSON}$ . Fortunately, this requirement for ultra-low R<sub>DSON</sub> comes with a corresponding relaxation of the BV<sub>DSS</sub> requirement. As stated earlier, there are design tradeoffs involved which counterbalance BV<sub>DSS</sub> and R<sub>DSON</sub>, and the two generally have an inverse relationship – generally, but not always. Unfortunately, as planar and trench vertical power MOSFETs are scaled to very low BV<sub>DSS</sub>, there comes a point at which there is no corresponding decrease in  $R_{DSON}$ . This occurs somewhere around 20 V, although the exact number of course depends very much on the specific technology. The reasons behind this point of diminishing returns are simple. First, as mentioned before, the cell pitch of a VDMOS transistor (either trench or planar), is more or less fixed for a given fabrication technology. There is no decrease in cell pitch corresponding to a decrease in the  $BV_{DSS}$ requirement. This means the only methods for reducing specific R<sub>DSON</sub> in a VDMOS is in the vertical direction, by reducing the drift length (epi thickness) and reducing the parasitic N+ substrate resistance. Modern low voltage trench MOSFETs employ methods such as using specially doped "red phosphorus" substrates with very low resistivity. Manufacturers also thin down the wafers during processing to reduce the thickness of the N+ substrate down to just a few tens of microns, further reducing the substrate resistance. Finally, the epi layers are kept as thin as possible for the given breakdown voltage and gate trench depth, but care must be taken to avoid placing the bottom of the gate trench too close to the N+ substrate. Given the process tolerances involved with these methods, there are physical limitations to how much the epi and

substrate resistances can be reduced, and somewhere near  $BV_{DSS} = 20$  V, these parasitic resistances make up a large portion of the total device  $R_{DSON}$ .

Finally, it was mentioned in the previous section that the low specific  $R_{DSON}$  of the TrenchFET comes with a corresponding tradeoff of high  $Q_G$ , due to increase in transistor cell density per unit area (high density of transistor gates). When scaling to lower  $BV_{DSS}$  with correspondingly lower  $V_{TH}$  requirements,  $Q_G$  becomes even higher, due to the thinner gate oxide required to meet the lower  $V_{TH}$  requirements.

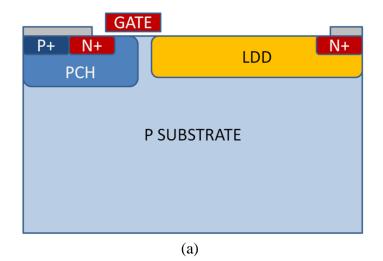

Taking into account all these design tradeoffs, device designers are driven toward the consideration of new device structures specifically for fast switching, low voltage power supplies. One recently developed technology is the discrete lateral power MOSFET based on CMOS fabrication technology. These power MOSFETs are based on LDMOS or NMOS transistor cell structures which are then integrated and arranged in parallel to form a large scale power MOSFET. A basic LDMOS transistor cell structure is shown in figure 6. Prior to the development of flipchip interconnect technology, it was not possible to create a large scale, low resistance lateral power MOSFET. This is because a lateral MOSFET requires that both the source and drain metal interconnects be placed on the surface of the die, which contrasts the very low resistance metal planes on either side of a VDMOS die. The resistance of the interdigitated source and drain metal stripes increase as the transistor is scaled to a larger area. In the case of a low voltage MOSFET, this metal interconnect resistance would far outweigh the actual silicon resistance. With the advent of flipchip technology, Shen et al presented a method by which a lateral power MOSFET could be formed to an arbitrarily large die size, with no corresponding "lateral scaling penalty" in RDSON [1].

Simplified cross sectional drawing of a Resurf LDMOS transistor cell. There are many types of n-channel LDMOS technologies, including some fabricated on an N substrate. This example is fabricated on a P substrate with an LDD region which is formed adjacent to the poly gate using a self-aligned ion implant process. This type of LDMOS offers very low  $Q_{GD}$ , which is a key metric of switching power efficiency.

Figure 6: Resurf LDMOS Transistor Cell

Being able to overcome the lateral scaling penalty meant that very low voltage lateral power MOSFETs could be developed using submicron CMOS fabrication technology and then scaled to meet the high current demands of the modern POL converter. The transistor cell pitch of these lateral power devices could be made very small – as small as was possible while still supporting the required  $BV_{DSS}$ . At the same time, the metal interconnect resistance of the flipchip design was so low, that there was no practical limit for scaling of  $R_{DSON}$  and  $BV_{DSS}$ . The result of this work was the world's first power MOSFET with  $R_{DSON} < 1 \text{ m}\Omega$  with a  $BV_{DSS}$  rating of only 7 V and a record setting  $Q_G \times R_{DSON}$  FOM.

Later, the development of discrete lateral power MOSFETs branched into higher voltages using LDMOS technologies. It was found that even though the specific  $R_{DSON}$  of the LDMOS structure was far greater than the TrenchFET, the FOM of the lateral devices were comparable if not lower than the TrenchFET due to the naturally low  $Q_G$  of the LDMOS structure [11]. LDMOS devices have much lower area-specific  $Q_G$  than TrenchFETs for two main reasons. The first reason is the larger cell pitch of the LDMOS, which results in fewer parallel gate stripes on the same chip area. The second reason is the fabrication method by which the LDD region is self-aligned with the poly gate, which results in the smallest possible  $Q_{GD}$  of any fabrication technology. Having a similar FOM with lower  $Q_G$ , along with the ultra-low inductance flipchip packaging, meant that the lateral FETs were especially well suited for use in POL converters operating in the MHz frequency range. Power MOSFET technology had finally broken through into the very low voltage, very high current regime.

#### **Motivation**

There is a long-standing disparity between terrestrial electronics and radiation hardened electronics in terms of performance and cost. Although modern sub-micron CMOS technology shows proven radiation tolerance, radiation-hardened power electronics continue to fail to meet the requirements of state-of-the-art digital circuits and This results in space craft being equipped with slower therefore limit their use. computers, less efficient power systems, and electronics of higher mass and volume than would be found on Earth in similar applications. The slow pace of technological evolution in the rad-hard power MOSFET field is due mostly to the unique fabrication and design challenges involved in making a power MOSFET resistant to ionizing radiation, also in part to the rigorous and costly qualification testing required to certify a part as rad-hard, and finally to the natural reluctance of engineers in the high reliability electronics sector to adopt the risks associated with using unproven semiconductor technology in a harsh ionizing radiation environment. Additionally, the cost of special radiation-hardened electronics remains very high due to low sales volume and a long development cycle. The cost of developing hardened components, coupled with the financial risk inherent in competing within a niche market, has resulted in an overall lack of competition among manufacturers of this specialized technology. This lack of driving market forces has resulted in an overall lack of development of new technologies, specifically in the arena of power semiconductor devices.

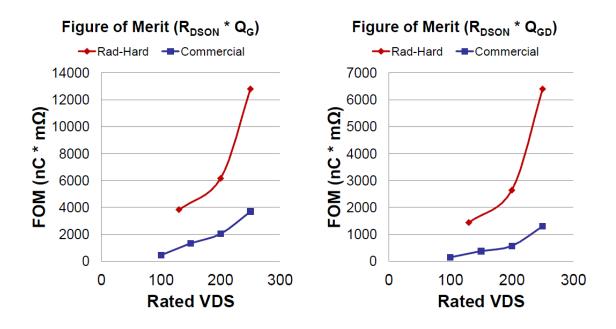

As described in the previous section, the heart of modern low-voltage power supplies is the power MOSFET. The performance of power electronics systems is most affected by the technology of these transistors. When compared with older systems, the power MOSFETs required to supply modern digital systems must switch at higher frequencies and exhibit lower conduction losses and internal capacitance. There is presently a lack of rad-hard power transistors with these characteristics. Rad-hard power MOSFET products have not benefited from recent advances in commercial power MOSFET technology, and therefore rad-hard power MOSFETs suffer from significantly higher specific  $R_{DSON}$  and higher  $Q_G$  than their commercial counterparts. Figure 7 illustrates the differences in FOM between modern day commercial and rad-hard power MOSFETs.

Present day rad-hard power MOSFETs are based on planar VDMOS technology, whereas TrenchFETs and lateral power MOSFETs (LDMOS) are used in today's most advanced commercial power electronics products. Although they lag far behind modern FETs in terms of performance, there are advantages to rad-hard planar VDMOS technology. First is a proven track record after decades of flight time in radiation environments. The second is a wealth of scientific study and understanding of the fundamental physical mechanisms that affect planar VDMOS device reliability in radiation environments. However, without the development of an advanced rad-hard TrenchFET or LDMOS, or some other similarly-performing technology, the state of the art in rad-hard power electronics systems will continue to lag decades behind the commercial world. At some point, it must be decided whether the risks inherent with adopting a new rad-hard technology are outweighed by the potential benefits in terms of being able to efficiently power more advanced digital systems in these environments.

Source: International Rectifier Datasheets (<u>http://www.irf.com</u>): Rad-Hard Parts (SEE and TID) IRHNJ5133SE, IRHNJ57230SE, IRHNJ5234SE, Commercial Parts: IRF6644, IRF6643, IRF6641, IRF5025

Figure 7: FOM Comparison of Rad-Hard vs Commercial Power MOSFETs

Aside from the significant performance penalty associated with the use of outdated planar VDMOS technology, rad-hard power MOSFET performance is further hindered by the severe electrical de-rating required to safely operate power MOSFETs in a radiation environment which might produce single event radiation effects (SEE) [12]-[14]. SEE refers to a broad array of disruptive, and sometimes catastrophically destructive, transient radiation events affecting semiconductor devices. Power MOSFETs remain especially vulnerable to destructive SEE, because of their high operating voltages and correspondingly high electrical stresses. The mechanisms of why this is true will be explained in great detail later in this work. Recently published data suggests that modern rad-hard planar VDMOS can experience destructive SEE failure at operating voltages less than 20% of their rated DC voltages [15][16]. This data will be discussed in more detail later in this work during the discussion of the physical mechanisms of destructive SEE. Given the need for such extreme electrical de-rating, it is worthwhile to explore whether other power MOSFET structures exhibit SEE sensitivities similar to the planar VDMOS. If an alternative power MOSFET structure with a lower performance FOM could be developed, which also demonstrates an improved SEE safe operating area, then the electrical performance benefit would be compounded by a relaxation of the de-rating requirement. Furthermore, it is possible that the overall reliability of the rad-hard power electronics circuit could be improved.

# Review of Ionizing Radiation Effects in Semiconductor Devices

## **Carrier Generation**

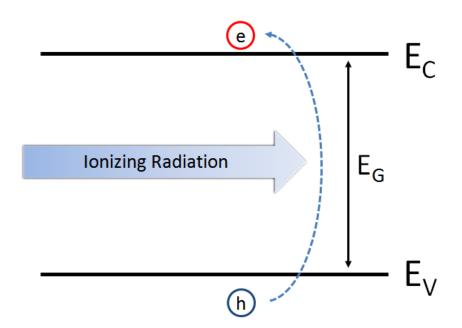

Ionizing radiation generates electron-hole pairs as energy is transferred from a radiation source (photons, subatomic particles, or nuclei) to an absorbing material, such as a semiconductor. A simplified illustration appears in figure 8, which shows a generic diagram of the energy bandgap between the conduction band and the valance band in an arbitrary target material. In the simplest terms, ionization occurs as energy from the incident radiation is absorbed by electrons in the target material, which are then accelerated from the valence band into the conduction band, leaving a hole behind.

Energy from ionizing radiation is absorbed by the target material, accelerating electrons from the valence band to the conduction band, leaving a hole behind.

Figure 8: Electron-Hole Pair Production

Different carrier generation mechanisms are associated with radiation of different types and energies [6][17]-[20]. Particle radiation such as protons, neutrons, and larger nuclei generate carriers via direct ionization mechanisms, either through collisions with or Coulombic interactions with nearby atoms. An example of Coulombic interactions would be a positively charge heavy ion passing through a material, wherein the positive charge of the large nucleus exerts enough Coulombic force to pull negatively charged electrons away from their orbital shells in nearby atoms.

Another possible ionization mechanism associated with nuclear particle collisions is indirect ionization from nuclear decay [21]. In this case, the total energy absorbed by the target material can be more than was present in the original particle, due to the energy release of the nuclear fission reaction. The by-products of nuclear fission, namely the smaller nuclei and any associated EM radiation, can also be ionizing in nature. Furthermore, long term localized ionization may occur as decayed atoms remain trapped within the lattice, causing a displacement defect.

In the case of high energy photons (X-rays,  $\gamma$ -rays), there are three associated carrier generation mechanisms. In order of energy required, these three effects are the photoelectric effect, the Compton effect (Compton scattering), and pair production. In the case of the photoelectric effect, the entire energy of the photon is absorbed by an electron, which is energized into the conduction band, leaving a hole behind. In the case of Compton scattering, the energy and momentum of the photon accelerates an electron into the conduction band, but the electron in turn recoils, giving back some kinetic energy and sending a photon of reduced energy off in a new direction. For a wide spectrum of

photon energies (<0.1 to >10 MeV), Compton scattering is the dominant carrier generation mechanism in silicon [20]. Finally, in the pair production process, a high energy photon is absorbed and ejects both an electron and a positron. The positron is quickly annihilated and releases two 0.51 MeV  $\gamma$ -rays, which may then cause further ionization.

In terms of the spatial distribution of ionization, exposure to most EM radiation sources generally occurs more or less uniformly across the entire semiconductor device or integrated circuit (IC). One notable exception would be an artificially-generated beam, such as a laser. Naturally, ionization from particle radiation is much more localized, and free carriers are generated generally within a submicron radius along the path of the incident particle. This path becomes a highly conductive region, which when caused by heavy ion radiation is sometimes referred to as an "ion shunt".

Linear Energy Transfer (LET) is the metric which quantifies the magnitude of energy deposition as radiation penetrates its target material. Usually LET is used to describe energy transfer from particle radiation, although it can also be applied to EM radiation. LET is expressed in units of deposited energy per unit length, and then normalized to material density, as shown in equation 2:

$$LET = \frac{Energy}{Length} \times \frac{1}{Density} = \frac{MeV \cdot cm^2}{mg}$$

(2)

The LET-dependent rate of electron-hole pair production is shown in equation 3:

$$\frac{\#ehp}{cm^3} = LET \cdot \rho \cdot \phi \cdot \frac{1}{E_p} \tag{3}$$

, where  $\rho$  is the density of the target material,  $\phi$  is the fluence of the incident radiation, and  $E_p$  is the material-dependent energy required to generate an electron-hole pair. For reference,  $E_p(Si) = 3.6 \text{ eV}$  and  $E_p(SiO_2) = 17 \text{ eV}$ .

LET is not constant for a given type of radiation as it passes through a material. As the radiation sheds its energy, its rate of energy transfer also changes. In this way, the instantaneous LET is constantly changing. So, in order to predict the LET of a given particle, both its mass and energy must be known, as well as the properties of the target material. Comparing two particles of the same mass, fast moving particles generally shed less energy than slow moving particles. At least this is the case until a particle slows to a specific energy, at which the linear energy transfer reaches a peak, known as the Bragg peak. A energies below its Bragg peak, the particle will quickly deposit all of its remaining energy within the target material. This behavior becomes very important when conducting radiation testing where the location of the Bragg peak plays a role in determining the response of the semiconductor device, as is later shown to be the case with power MOSFETs.

Generation of electron-hole pairs in and of itself does not describe ionizing radiation effects in semiconductor devices. The effects of interest actually occur during the subsequent transport and recombination of the generated carriers. There are numerous classifications of ionizing radiation effects in semiconductor devices, but most fall under the larger umbrellas of single event effects (SEE) or total ionizing dose (TID) effects. The next sections introduce these two types of effects in more detail.

### Single Event Effects

The term "single event effect" describes exactly what the name implies, that is an effect arising from a non-recurring interaction with a single radiation source or event. SEE are the effects of sudden events, not prolonged exposure, and they are normally associated with *high photocurrent density* in the semiconductor device. For example, shining a household light bulb on a photodiode for a long time will produce a sustained photocurrent, but a household bulb is unlikely to produce sufficient current density to result in single event effects. By contrast, exposing the same photodiode to a short high energy laser pulse will produce a sudden large increase in current, the effects of which could be classified as SEE.

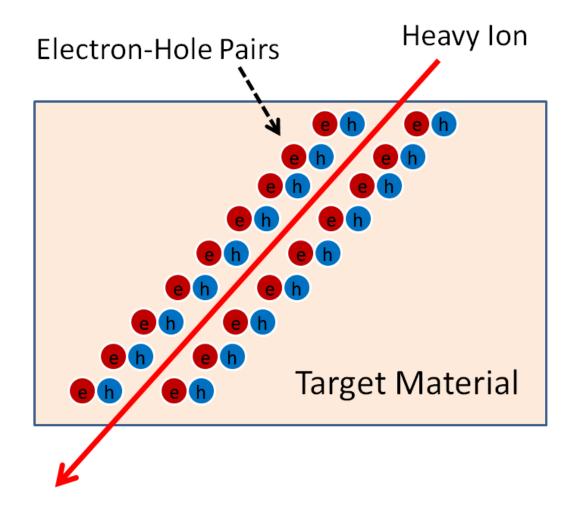

Technically, single event effects can occur as a result of sudden exposure to sufficient levels of any type of ionizing radiation, but the term SEE is used most commonly when discussing exposure to particle radiation, usually nuclei. These are the SEE referred to in this work. The "single event" itself will be defined as the highly localized interaction between the semiconductor device and a single particle. The "single event effects" describe the transient response of a semiconductor device to the localized generation of free electrons along the path of the incident particle. The localized electron generation associated with SEE is frequently referred to as "charge deposition", and the total amount or concentration of generated electrons is called the "deposited charge". A simple illustration of charge deposition is shown in figure 9.

This example shows electron-hole pair generation around the trajectory of a heavy ion passing through an arbitrary target material. Linear energy transfer (LET) describes how radiation sheds its energy per unit length as it passes through a target material. The rate of electron-hole pair generation is proportional to LET. When a heavy ion passes through an electric field in a semiconductor device, the highly conductive trajectory of the ion is sometimes referred to as an "ion shunt".

Figure 9: Heavy Ion Charge Deposition

In a semiconductor device, SEE are caused by the transport and collection of deposited charge at the device terminals. There are many classifications of SEE, most of which do not apply to power MOSFETs.

# Single Event Upset and Single Event Latchup

Single event upset (SEU) and single event latchup (SEL) are the most frequently studied SEE in integrated circuits but do not apply to power MOSFETs. SEU refers to a short spike of photocurrent which upsets the input or output of a node within an integrated circuit. In fast switching logic circuits, whose function relies on precise timing and control of current pulses, such SEU frequently generates data errors. Similar photocurrent perturbations in analog circuits must either be filtered out, or they can lead to erroneous operation of the circuit. Device and circuit designers cannot eliminate the photocurrent pulses which SEU. They can only try to minimize and contain the resulting circuit effects through careful design, which among others includes techniques related to circuit layout, fabrication process, and error handling. In cases where the photocurrent current pulse is known simply as a single event transient (SET).

SEL by contrast is a destructive effect which occurs in devices with a four-layer structure with three back-to-back p-n junctions. This type of structure is often referred to as a parasitic thyristor, after the power semiconductor device of the same name. Multiple well bipolar and CMOS technology usually contain these parasitic thyristor structures. The parasitic thyristor can be represented as an NPN and PNP bipolar junction transistor (BJT) connected in a self-amplifying configuration, where the emitter of each transistor is tied to the base of the other. At a given critical charge, under a given bias condition, the BJT pair "latches up". That is to say, it enters a self-sustaining regime of current amplification and positive feedback. Eventually the current density reaches a point at which the power dissipation heats the semiconductor lattice to its melting point.

Due to the small feature sizes of modern deep submicron CMOS devices, a relatively small amount of deposited charge is required to generate SEE in those devices. Consequently, SEE in deep submicron CMOS devices can arise from interaction with alpha particles and even subatomic particles.

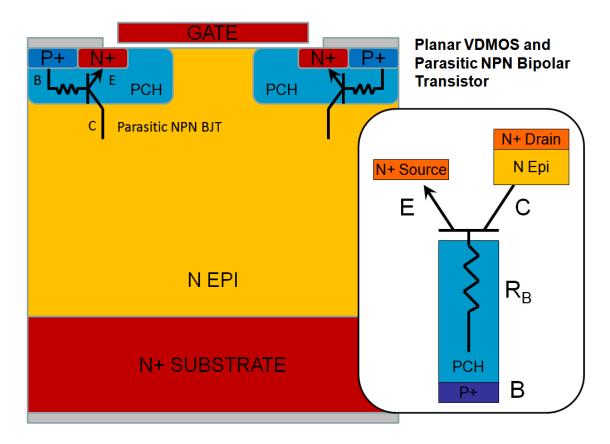

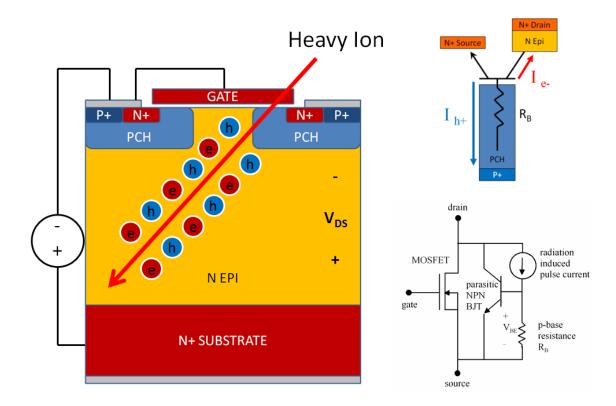

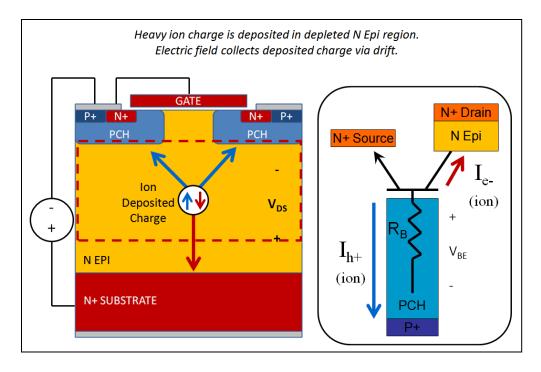

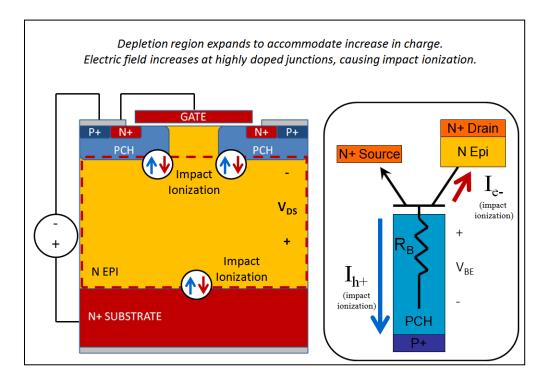

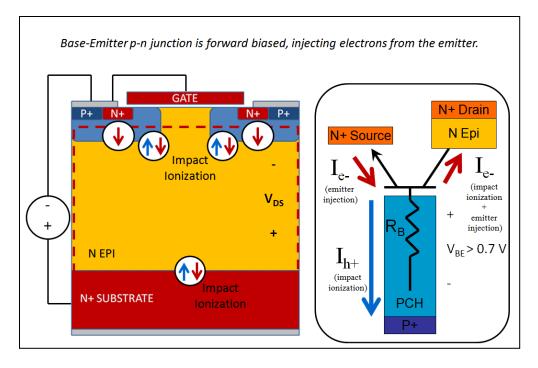

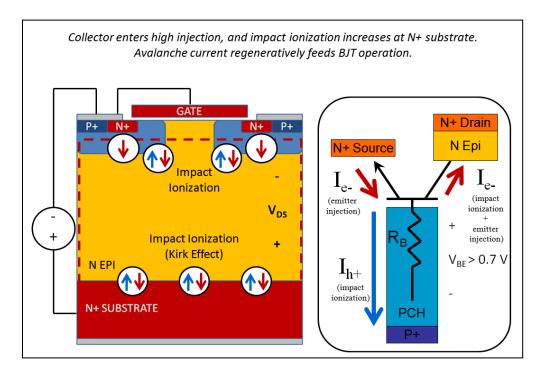

# Single Event Burnout

Single-event burnout (SEB) is a destructive SEE that occurs primarily in Nchannel power transistors [7]. SEB is most often associated with heavy ion radiation, but it can occur as a result of any type of radiation which produces high levels of photocurrent within the device. The basic mechanism is similar to SEL, except SEB occurs in devices where there is no parasitic thyristor structure. Instead, all that is required to cause SEB is a single parasitic bipolar junction transistor. SEB occurs when the parasitic BJT is put into a self-sustaining forward active operating mode as a result of high photocurrent. The forward active operation is initiated and sustained by a complex mechanism, which is described in detail later in this work. Whether or not SEB occurs for a particular device depends on a combination of factors. Independent of device design, the most influential factors on SEB are the LET and trajectory of the radiation (assumed to be a heavy ion), and the biasing conditions at the device terminals [22]. It should be noted that N-channel devices are more susceptible to SEB, because their parasitic NPN bipolar transistor has higher current gain than the parasitic PNP bipolar transistor of a P-channel MOSFET. Unfortunately, N-channel devices are almost exclusively used in power switching applications, in part because their R<sub>DSON</sub> is typically half that of a similar P-channel device, and also because power switching circuits generally require a normally "OFF" power MOSFET.

#### Single Event Gate Rupture

Single Event Gate Rupture (SEGR) is another destructive SEE mostly associated with power MOSFETs and heavy ion radiation. SEGR occurs when a power MOSFET is biased in the OFF state, and a high electric field, on the order of MV/cm is applied across the gate dielectric of a power MOSFET. When a heavy ion passes through the gate oxide under these biasing conditions, it generates electron-hole pairs within the oxide, according to the ion LET and the electric field-dependent generation rate inside the dielectric. At almost the same instant, electron-hole pairs are being generated. both within the polysilicon above the gate oxide, and also in the silicon layers along the ion trajectory underneath the oxide. In this way, an ion shunt is formed through the gate oxide, connecting the gate terminal at ground potential to some portion of the drain region of the MOSFET, which lies at a higher potential. This potential difference results in high photocurrent density below the gate oxide and high electrical stress across the gate oxide. It is thought that SEGR occurs as a result of interaction between the temporary conductivity of the oxide and the high electric stress across the oxide, resulting in a localized current filament through the oxide [23].

In some cases, SEGR manifests as a small increase in gate-to-source leakage current, suggesting highly localized damage [24]. In other cases, SEGR is catastrophically destructive, resulting in much higher levels of gate leakage current and loss of control over the MOSFET. Another case occurs in which both SEGR and SEB occur more or less simultaneously. Conclusions about the physical mechanisms behind this type of failure can be drawn based on which bias conditions caused the failure. It is likely that in some cases SEGR leads to SEB, whereas in other cases SEB leads to SEGR [7].

### Total Dose Effects

The quantitative measure of accumulated energy absorbed from ionizing radiation is called the "dose". The SI unit for radiation dose is the Gray [Gy], however when discussing ionizing radiation effects in semiconductor devices, the dose is commonly measured in units of rads [rd]. One Gray represents the dose of ionizing radiation required to transfer 1 J of energy per kilogram of target material, and 1 Gy = 100 rads.

Both units are material-specific, because the amount of generated electron-hole pairs corresponding to a given type and energy of radiation varies according to the properties of the target material. These units are therefore a way of normalizing radiation dose measurement across different materials. In the notation of radiation dose units, the material name appears in parentheses after the unit. For example, rads(Si) are units of absorbed radiation dose for silicon, whereas rads(SiO<sub>2</sub>) are units for silicon dioxide.

In contrast to SEE, total ionizing dose (TID) effects, refer to the effects of accumulated ionizing radiation exposure and the resulting damage within a semiconductor device. TID effects can be categorized into two major types - charge trapping effects and displacement damage. Charge trapping effects occur in the semiconductor device insulating layers, whereas displacement damage can occur within the semiconductor crystal lattice itself. Displacement damage is caused by exposure to high energy protons, neutrons, and nuclei, where the incident particle deposits sufficient energy to displace atoms either through collision or via a nuclear reaction. Charge trapping effects can be caused by any type of ionizing radiation, and the effects are highly dependent on the characteristics of both the incident radiation and the semiconductor or insulator target material [25]. In most cases, charge trapping effects in MOS devices manifest as a gradual degradation of device performance and functionality due to the buildup of charge in the MOSFET gate oxide. In bipolar devices, charge trapping effects are normally associated with a decrease in transistor gain and cutoff frequency, due to the increase in recombination that occurs in the charge trapping sites. Microdose effects are a very specific type of TID effect that arise due to exposure to heavy ion radiation.

The mechanism of charge trapping in silicon dioxide has to do with the difference in electron and hole mobility in SiO<sub>2</sub>, where electron mobility is more than 10,000 times greater than that of holes. This means that as electron-hole pairs are generated within SiO<sub>2</sub>, the electrons can be swiftly swept away by any applied electric field, whereas the holes remain more or less fixed within the oxide. For this reason, most of the electrons and holes are not able to recombine within the oxide, and a large number of holes become trapped within the oxide bulk. Meanwhile, electrons remain trapped at the Si/SiO<sub>2</sub> interface. At the interface, dangling bonds are present between the amorphous SiO<sub>2</sub> and the silicon crystal lattice. These interface states act as charge trapping centers by allowing electrons to remain at energy levels that fall within the normally forbidden energy bandgap of silicon.

Because charge transport is the underlying mechanism behind TID charge trapping, the ratio of unrecombined holes as a fraction of generated electron-hole pairs is highly dependent on electric field. A stronger electric field will sweep away the electrons more quickly, resulting in a higher fraction of unrecombined holes. At fields near 5 MV/cm, the fraction of unrecombined holes approaches almost 100% [26]. Trapped charge density is also highly dependent on oxide thickness. From a first order perspective, the magnitude of bulk trapped charge is linearly proportional to oxide thickness [27]. Finally, the "quality" of the oxide, which generally describes the density of bulk and interface states prior to radiation, has a severe impact on the susceptibility to TID effects.

The most commonly studied TID effects are threshold voltage shifts and increased leakage current in MOS devices. Threshold voltage shifts are attributed to the accumulation of trapped charge within the gate oxide and along the gate oxide interface. Positive trapped charge lowers the magnitude of the threshold voltage ( $V_{TH}$ ) of NMOS devices, while negative trapped charge has the same effect for PMOS devices. Threshold voltage shifts over time can become so dramatic that N-channel transistors become normally "ON" devices [28].

Increased leakage current is the other commonly observed effect, particularly in CMOS integrated circuits. Aside from leakage through the MOS channel of a severely affected transistor, parasitic leakage paths also commonly occur along the shallow trench isolation (STI) oxides used in many IC layouts to isolate circuit elements. The deposited STI oxide generally contains more bulk and interface states than a thermally grown gate oxide. Also, the thickness of the STI oxide is several orders of magnitude larger than that of a typical gate oxide. The combination of an extremely thick oxide with a high number of bulk and interface states means that a lower radiation dose is required to generate the same amount of oxide and interface trapped charge.

Leakage around STI oxides occurs when the oxides lie over lightly doped regions which connect otherwise isolated device structures. As charge accumulates in the STI oxide, the lightly doped silicon underneath can become easily inverted, much the same way inversion occurs in the channel of a MOSFET as it is turned ON. These parasitic channels can be eliminated through careful layout techniques and also by avoiding the placement of STI over lightly doped regions. Methods of hardening ICs using such techniques are referred to as "hardening by design".

# CHAPTER TWO: SINGLE EVENT RADIATION EFFECTS IN POWER MOSFETS

More destructive single event effects occur in power MOSFETs than in low voltage integrated circuits, due to the fact that power MOSFETs operate at higher voltages with large inductive and capacitive loads. From the point of view of a power MOSFET designer, the only two single event effects of any real concern are the destructive effects of SEB and SEGR. These effects occur almost exclusively in power MOSFETs and are not generally observed in low voltage integrated circuits. Conversely, many other SEE are applicable only to integrated circuits and do not apply to power MOSFETs. These include the effects of single event upset and single event latchup. Single event transients can and do occur in power MOSFETs, however whether these SETs cause an upset in the power electronics circuit is more dependent on circuit design than MOSFET design. Therefore, in terms of hardening power MOSFETs against SEE, the focus is on SEB and SEGR.