Electronic Theses and Dissertations, 2004-2019

2013

# Analysis And Design Optimization Of Multiphase Converter

Kejiu Zhang University of Central Florida

Part of the Electrical and Electronics Commons

Find similar works at: https://stars.library.ucf.edu/etd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

### **STARS Citation**

Zhang, Kejiu, "Analysis And Design Optimization Of Multiphase Converter" (2013). *Electronic Theses and Dissertations*, 2004-2019. 2947.

https://stars.library.ucf.edu/etd/2947

### ANALYSIS AND DESIGN OPTIMIZATION OF MULTIPHASE CONVERTER

by

# KEJIU ZHANG B.S. Beijing University of Aeronautics and Astronautics, 2005 M.S. University of Central Florida, 2008

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida

Orlando, Florida

Fall Term

2013

Major Professor: Thomas Xinzhang Wu (Chair) Issa Batarseh (Co-Chair) © 2013 Kejiu Zhang

# TO MY PARENTS WUSHAN ZHANG AND WENXIU DUAN

TO MY WIFE

SIQI GUO

### **ABSTRACT**

Future microprocessors pose many challenges to the power conversion techniques. Multiphase synchronous buck converters have been widely used in high current low voltage microprocessor application. Design optimization needs to be carefully carried out with pushing the envelope specification and ever increasing concentration towards power saving features. In this work, attention has been focused on dynamic aspects of multiphase synchronous buck design. The power related issues and optimizations have been comprehensively investigated in this paper.

In the first chapter, multiphase DC-DC conversion is presented with background application. Adaptive voltage positioning and various nonlinear control schemes are evaluated.

Design optimization are presented to achieve best static efficiency over the entire load range. Power loss analysis from various operation modes and driver IC definition are studied thoroughly to better understand the loss terms and minimize the power loss. Load adaptive control is then proposed together with parametric optimization to achieve optimum efficiency figure.

New nonlinear control schemes are proposed to improve the transient response, i.e. load engage and load release responses, of the multiphase VR in low frequency repetitive transient. Drop phase optimization and PWM transition from long tri-state phase are presented to improve the smoothness and robustness of the VR in mode transition. During high frequency repetitive transient, the control loop should be optimized and nonlinear loop should be turned off. Dynamic current sharing are thoroughly studied in chapter 4. The output impedance of the multiphase

synchronous buck are derived to assist the analysis. Beat frequency is studied and mitigated by proposing load frequency detection scheme by turning OFF the nonlinear loop and introducing current protection in the control loop.

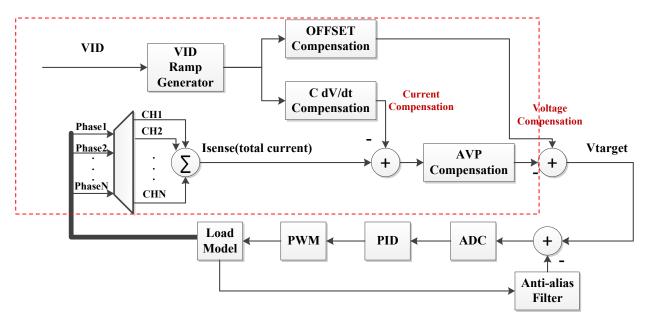

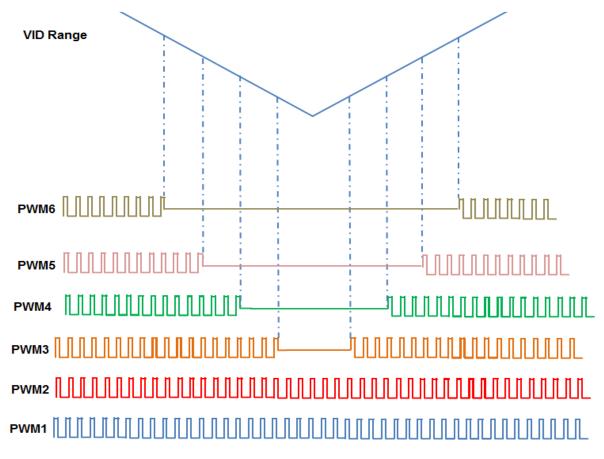

Dynamic voltage scaling (DVS) is now used in modern Multi-Core processor (MCP) and multiprocessor System-on-Chip (MPSoC) to reduce operational voltage under light load condition. With the aggressive motivation to boost dynamic power efficiency, the design specification of voltage transition (dv/dt) for the DVS is pushing the physical limitation of the multiphase converter design and the component stress as well. In this paper, the operation modes and modes transition during dynamic voltage transition are illustrated. Critical dead-times of driver IC design and system dynamics are first studied and then optimized. The excessive stress on the control MOSFET which increases the reliability concern is captured in boost mode operation. Feasible solutions are also proposed and verified by both simulation and experiment results. CdV/dt compensation for removing the AVP effect and novel nonlinear control scheme for smooth transition are proposed for dealing with fast voltage positioning. Optimum phase number control during dynamic voltage transition is also proposed and triggered by voltage identification (VID) delta to further reduce the dynamic loss. The proposed schemes are experimentally verified in a 200 W six phase synchronous buck converter.

Finally, the work is concluded. The references are listed.

### **ACKNOWLEDGMENTS**

With the deepest appreciation in my heart, I would like to thank my advisor Dr. Thomas Xinzhang Wu for his guidance, support and encouragement in my Ph.D. study at University of Central Florida. His talent, integrity and scholarship have been a continuous source of my inspiration. Without his guidance, persistent help and constant 'regulation', this dissertation would not have been possible.

I would also like to thank my co-advisor Dr. Issa Batarseh for giving me the opportunity to work in Florida Power Electronics Center (FPEC) at the University of Central Florida. His technical leadership and critical thinking have provided an exemplary example for me to follow. I would also like to express my gratitude to Dr. John Shen, who has also offered me a lot of insightful ideas.

I would like to thank my committee members, Professor Yuan, Professor Sundaram and Professor Chow. Their insightful comments, constructive suggestions and rigorous scholarship have refined the quality of this work.

I would like to express my deep appreciation to Dr. Shiguo Luo, who is the first and foremost mentor in my industrial career. He has set the top standard of industrial rigorousness and innovativeness for me to follow and often kindly gave me insightful directions and suggestions for my academic research from the industrial point of view.

I would like to express my deep love and gratitude to my parents. Their merits, as parents and medical doctors have been always influencing and guiding me through the journey of my life.

I would thank my uncle, Yashan Zhang, who is the role model from my early childhood and follow his steps to come to America to further my dream.

The last but not the least, I would like to thank my wonderful wife, Siqi Guo, for her unstopping love and understanding and for the endless happiness and enjoyment.

# **TABLE OF CONTENTS**

| LIST OF FIGURES                               | xi    |

|-----------------------------------------------|-------|

| LIST OF TABLES                                | xvii  |

| LIST OF ACRONYMS                              | xviii |

| CHAPTER ONE: INTRODUCTION                     | 1     |

| 1.1 Introduction to Multiphase Buck Converter | 4     |

| 1.2 Adaptive Voltage Positioning              | 8     |

| 1.3 Review of Prior Arts                      | 10    |

| 1.3.1 Constant ON-time (COT)                  | 11    |

| 1.3.2 Current Mode Hysteresis                 | 13    |

| 1.3.3 EAPP                                    | 15    |

| 1.4 Dissertation Outlines                     | 16    |

| CHAPTER TWO: OPTIMIZATION ON STATIC OPERATION | 19    |

| 2.1 Compensation Design                       | 20    |

| 2.1.1 Direct Digital Design                   | 22    |

| 2.1.2 Root Locus and Bode Plot                | 23    |

| 2.2 Power Loss Analysis                       | 25    |

|   | 2.3 Driver Interface                                     | . 30 |

|---|----------------------------------------------------------|------|

|   | 2.4 Light Load Operation                                 | . 36 |

|   | 2.5 Switching Waveforms                                  | . 41 |

|   | 2.6 Efficiency Optimization                              | . 44 |

| C | HAPTER THREE: LOW FREQUENCY TRANSIENT AND SYSTEM DYNAMIC | 51   |

|   | 3.1 DCR Sense Network Impact                             | . 51 |

|   | 3.2 Nonlinear Control Scheme                             | . 52 |

|   | 3.2.1 Load Engage Enhancement                            | . 54 |

|   | 3.2.2 Load Release Enhancement                           | . 56 |

|   | 3.3 Drop Phase Optimization                              | . 64 |

|   | 3.4 PWM HiZ to High Transition in Shedded Phase          | . 66 |

| C | HAPTER FOUR: HIGH FREQUENCY TRANSIENT                    | . 74 |

|   | 4.1 Sampling Effects of PWM Converters                   | . 74 |

|   | 4.2 Output Impedance Optimization                        | . 77 |

|   | 4.3 Beat Frequency Mitigation                            | . 79 |

|   | 4.4 Dynamic Current Sharing                              | . 81 |

| C | HAPTER FIVE: DYNAMIC VOLTAGE SCALING                     | . 86 |

|   | 5.1 Modes of Operation                                   | . 86 |

| 5.2 Driver Dead-time in Sink Mode             | 88  |

|-----------------------------------------------|-----|

| 5.3 Control MOSFET Stress Suppression         | 91  |

| 5.4 DVS Responsiveness Optimization           | 97  |

| 5.4.1 Nonlinear Control Scheme                | 97  |

| 5.4.2 CdV/dt Compensation                     | 98  |

| 5.4 Current Sharing during DVS                | 103 |

| 5.5 Phase Number Control during DVS Operation | 107 |

| CHAPTER SIX: CONCLUSIONS AND FUTURE WORK      | 112 |

| 6.1 Major Contributions                       | 112 |

| 6.2 Future Works                              | 113 |

| LIST OF REFERENCES                            | 114 |

# LIST OF FIGURES

| Figure 1. 1. The world market for power management IC by application                | 1  |

|-------------------------------------------------------------------------------------|----|

| Figure 1. 2. Voltage regulator real estate in server motherboard                    | 2  |

| Figure 1. 3. A typical power management map for server system.                      | 3  |

| Figure 1. 4. A multiphase synchronous buck converter for CPU application            | 4  |

| Figure 1. 5. Normalized ripple current as a function of phase number and duty cycle | 5  |

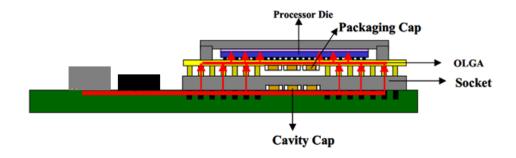

| Figure 1. 6. A typical power delivery path for today's microprocessors              | 6  |

| Figure 1. 7 Power distribution impedance versus frequency.                          | 6  |

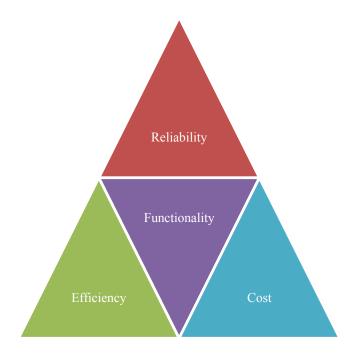

| Figure 1. 8. Robustness, efficiency and cost pyramid in server power design         | 7  |

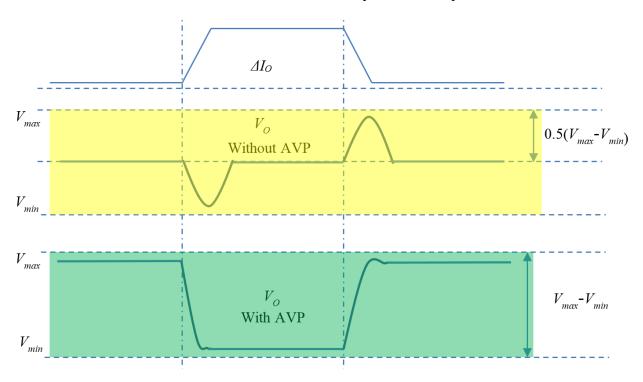

| Figure 1. 9. Load transient without and with AVP implementation.                    | 8  |

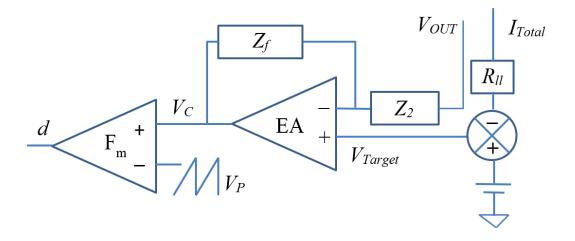

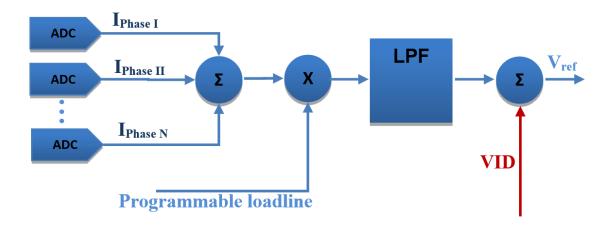

| Figure 1. 10. Block diagram of AVP design in analog realization.                    | 9  |

| Figure 1. 11. Block diagram of AVP design in digital realization.                   | 9  |

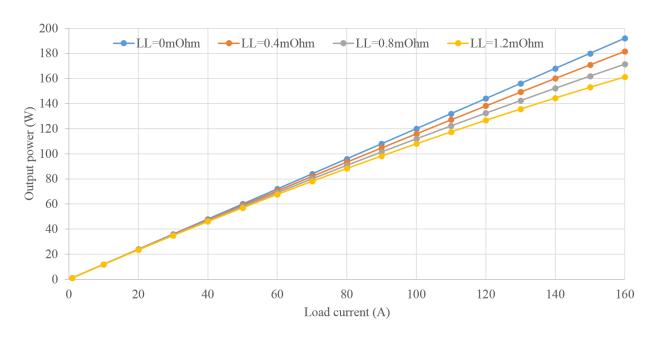

| Figure 1. 12. Output power comparison with different LL.                            | 10 |

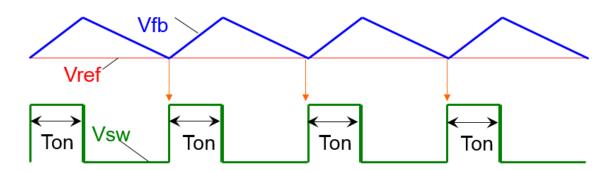

| Figure 1. 13. Constant ON time.                                                     | 11 |

| Figure 1. 14. Simplified voltage mode COT architecture with ripple injection        | 12 |

| Figure 1. 15. Simplified R4 <sup>TM</sup> modules for PWM generation.               | 13 |

| Figure 1. 16. Simplified operation waveform during load transient.                  | 14 |

| Figure 1. 17. Schematic diagram of EAPP circuitry                                   | 15 |

| Figure 1. 18. Dual-Edge and Variable-Frequency Operational Waveforms.               | 16 |

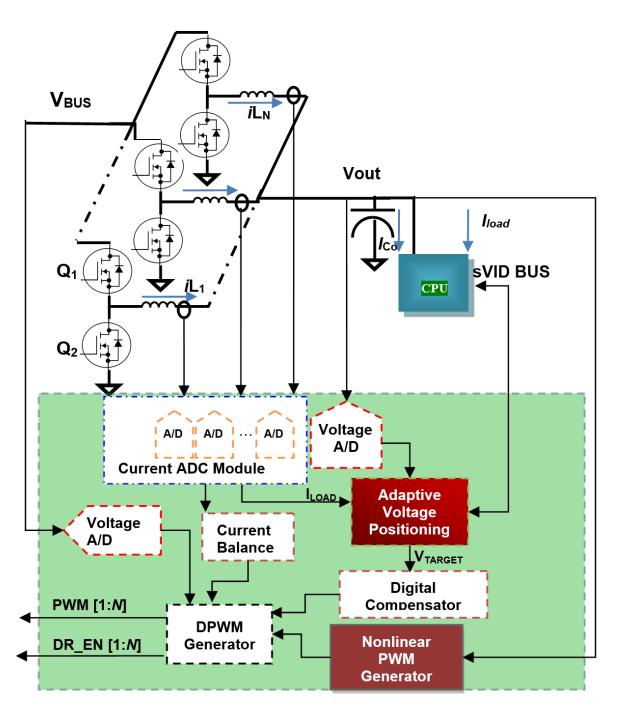

| Figure 2. 1. The architecture of the bidirectional multiphase synchronous controller. | 19    |

|---------------------------------------------------------------------------------------|-------|

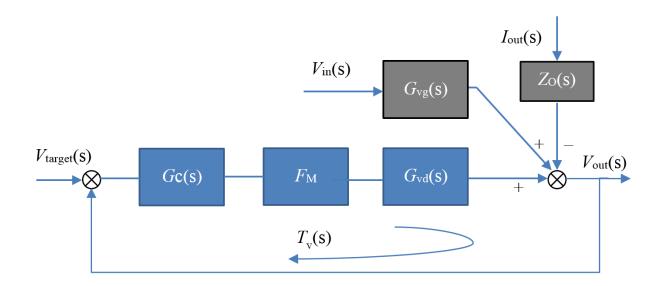

| Figure 2. 2. Small signal model of voltage mode buck converter.                       | 21    |

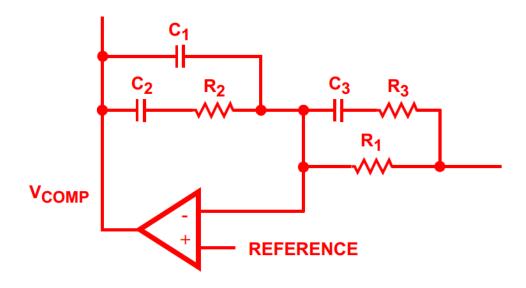

| Figure 2. 3. Generic type III compensation network.                                   | 22    |

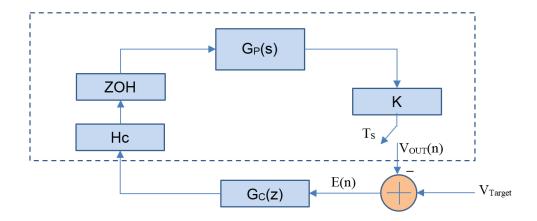

| Figure 2. 4. Digital control loop block diagram.                                      | 23    |

| Figure 2. 5. Root Locus.                                                              | 24    |

| Figure 2. 6. Bode plot.                                                               | 24    |

| Figure 2. 7. A power design breakdown in server application.                          | 25    |

| Figure 2. 8. Power loss distribution of a synchronous buck in buck mode               | 26    |

| Figure 2. 9. Diode reverse-recovery waveforms                                         | 28    |

| Figure 2. 10. Power loss distribution of a synchronous buck in boost mode             | 29    |

| Figure 2. 11. Driver IC block diagram with proposed dead-time management              | 31    |

| Figure 2. 12. Timing diagram of driver interface: (a) DR_EN is asserted; (b) DR_I     | EN is |

| toggling during operation.                                                            | 33    |

| Figure 2. 13. Timing diagram of driver interface: PWM vs. Boot switch                 | 33    |

| Figure 2. 14. LS turning ON/OFF.                                                      | 35    |

| Figure 2. 15. Simulation result of LS turning ON/OFF.                                 | 35    |

| Figure 2. 16. An example of resonant gate-drive circuit.                              | 36    |

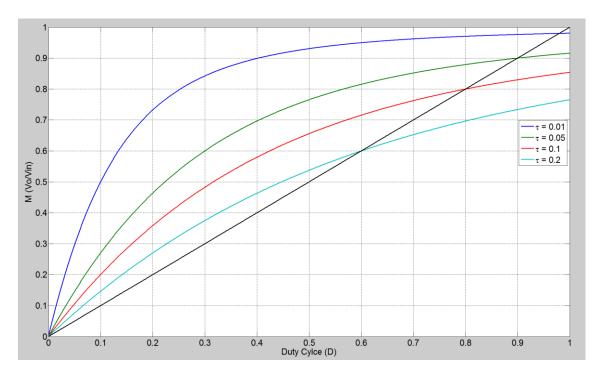

| Figure 2. 17. Transfer ratio M vs. duty cycle D.                                      | 37    |

| Figure 2. 18. Operational waveforms of PFM operation.                                 | 38    |

| Figure 2. 19. Power loss distribution of a synchronous buck in PFM.                   | 39    |

| Figure 2. 20. PFM to CCM transition (load: 1 A).                                      | 40    |

| Figure 2. 21. LS V <sub>DS</sub> rising waveform due to diode reverse recovery.      | . 41 |

|--------------------------------------------------------------------------------------|------|

| Figure 2. 22. Discrete solution of the converter considering circuitry parasitics in | the  |

| buck mode.                                                                           | . 42 |

| Figure 2. 23. Simetrix simulation of Gate waveforms.                                 | . 42 |

| Figure 2. 24. HS V <sub>DS</sub> waveforms comparison.                               | . 43 |

| Figure 2. 25. Light load CCM vs. PFM.                                                | . 44 |

| Figure 2. 26. Power loss reduction (PFM minus CCM) vs. VID.                          | . 45 |

| Figure 2. 27. Efficiency vs. switching frequency.                                    | . 46 |

| Figure 2. 28. Efficiency vs. FET drive voltage.                                      | . 47 |

| Figure 2. 29. Measured efficiency of multiphase buck converter with operating differ | rent |

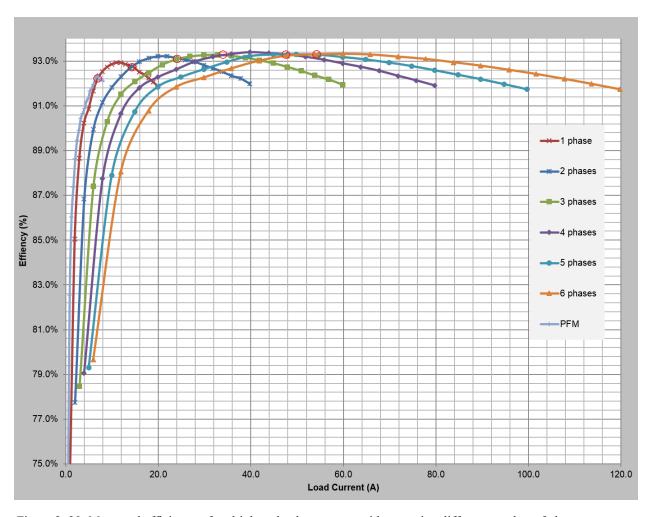

| number of phases.                                                                    | . 48 |

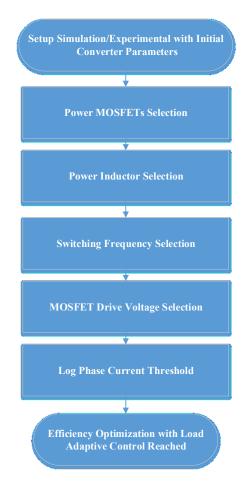

| Figure 2. 30. Power efficiency optimization flow chart.                              | . 49 |

| Figure 2. 31. Diagram of Load adaptive control.                                      | . 50 |

|                                                                                      |      |

| Figure 3. 1. DCR sense network RC time constant.                                     | . 52 |

| Figure 3. 2. The ATR timing architecture of the multiphase controller.               | . 54 |

| Figure 3. 3. Load engage response with pure voltage mode control.                    | . 55 |

| Figure 3. 4. Load engage response w/ auto-phasing.                                   | . 56 |

| Figure 3. 5. Inductor current profile and gate-drive signals for the correspond      | ling |

| operations.                                                                          | . 57 |

| Figure 3. 6. Load release response comparison.                                       | . 58 |

| Figure 3. 7. Inductor current slew rate difference during load release                     |

|--------------------------------------------------------------------------------------------|

| Figure 3. 8. Adaptive body-braking control (pulsing control)                               |

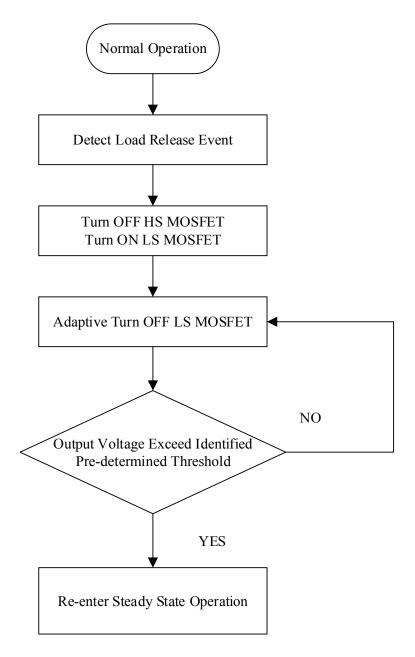

| Figure 3. 9. Flow chart of adaptive body-braking control (pulse control)                   |

| Figure 3. 10. Adaptive body-braking control (Body diode ON)                                |

| Figure 3. 11. Flow chart of adaptive body-braking control (Body diode ON)                  |

| Figure 3. 12. Overshoot during phase shedding. 64                                          |

| Figure 3. 13. Current balance block diagram. 65                                            |

| Figure 3. 14. Simulated inductor current with smooth gain                                  |

| Figure 3. 15. Simulation results of VR entering tri-state. 67                              |

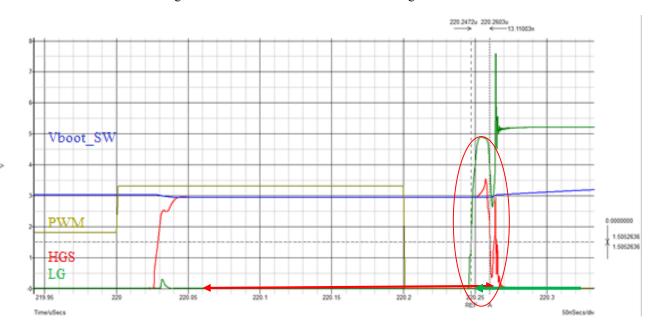

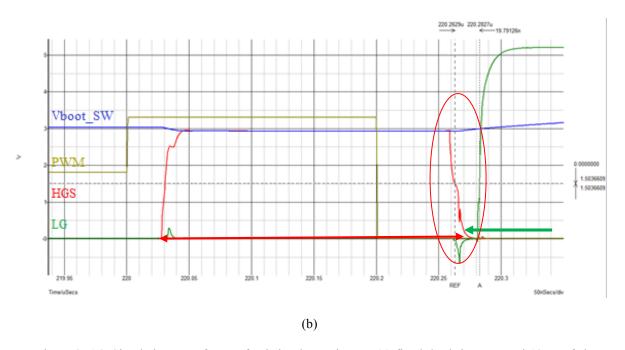

| Figure 3. 16. Simulation waveforms of existing long tri-state: (a) fixed dead-time: around |

| 13 ns of shoot-through (b) adaptive dead-time: No shoot-through captured                   |

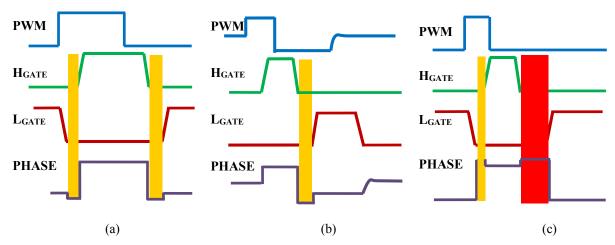

| Figure 3. 17. Operational waveforms of existing long tri-state: (a) around 10 ns of shoot- |

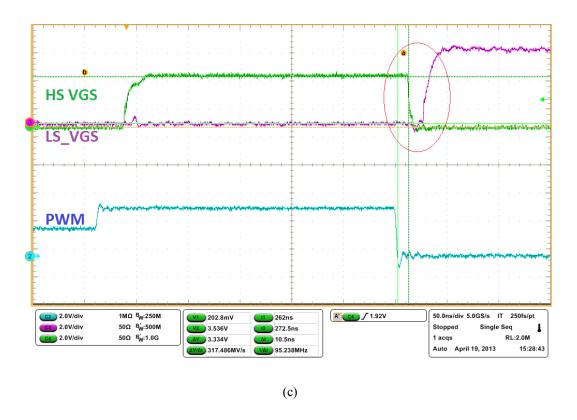

| through; (b) No shoot-through captured by PWM going low first when exiting tri-state. (c)  |

| No shoot-through captured with "adaptive" shoot-though protection                          |

| Figure 3. 18. Dead-time management diagram when VR exist tri-state                         |

|                                                                                            |

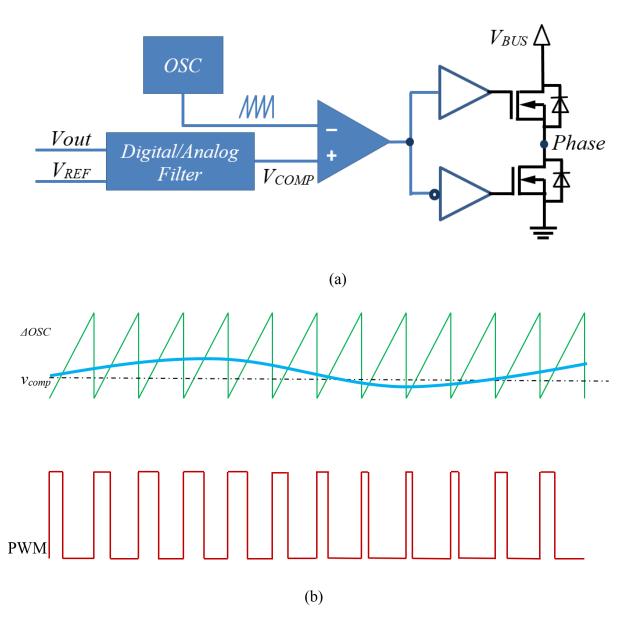

| Figure 4. 1. PWM modulator diagram and $V_{\text{COMP}}$ perturbation waveform: (a) PWM    |

| Modulator; (b) modulation waveform with V <sub>COMP</sub> perturbations                    |

| Figure 4. 2. Frequency response of zero-order hold: (a) Gain; (b) Phase                    |

| Figure 4. 3. Small-signal control block diagram of the closed loop output impedance 77     |

| Figure 4. 4. Plots of $ Z_v $ and $ Z_{OC} $                                               |

| Figure 4. 5. Block diagram of load frequency detection (LFD)                                                  |

|---------------------------------------------------------------------------------------------------------------|

| Figure 4. 6. A load transient response. Load step: $10A$ - $141A$ , slew rate: $450~A/\mu S$ . Rep            |

| rate: 400 kHz. (a) Nonlinear loop enabled. (b) Nonlinear loop disabled                                        |

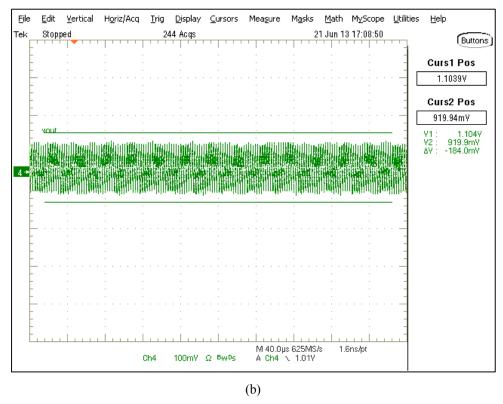

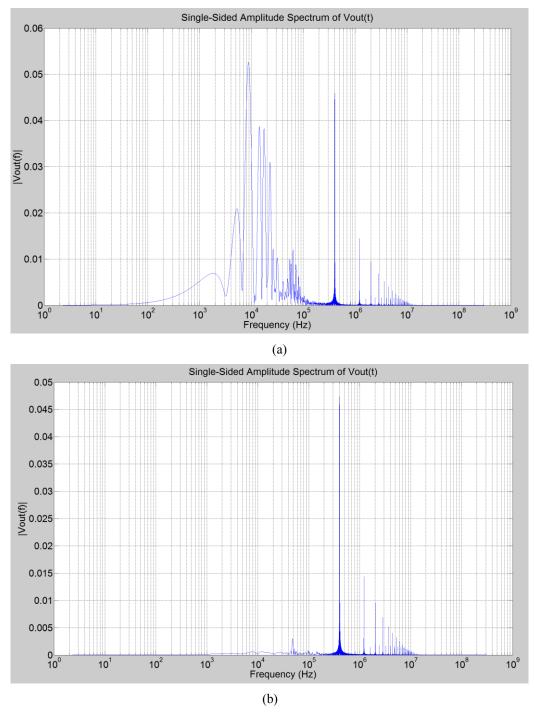

| Figure 4. 7. Magnitude of an N-point DFT on $V_{\text{OUT}}$ (high frequency rep rate transient). (a)         |

| Nonlinear loop enabled. (b) Nonlinear loop disabled. 83                                                       |

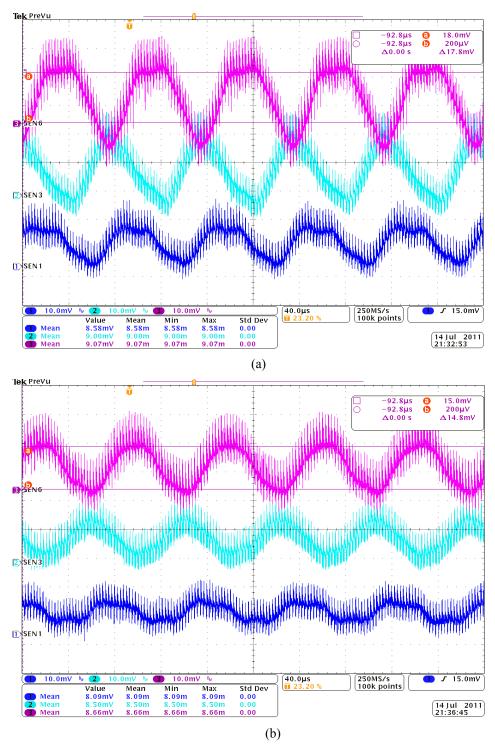

| Figure 4. 8. Phase currents oscillation: transient step: 132A-165A, load frequency 385                        |

| kHz. (a) LFD disabled. (b) LFD enabled. 84                                                                    |

|                                                                                                               |

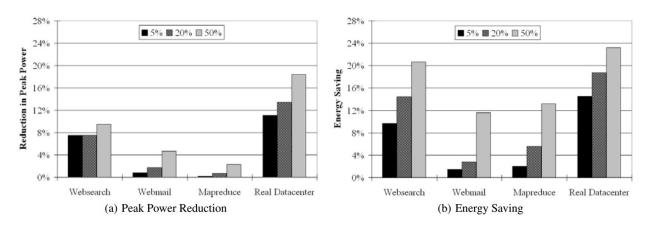

| Figure 5. 1. The impact of DVS operation at datacenter level                                                  |

| Figure 5. 2. Operational waveforms with the critical dead times: (a) Buck (Source) CCM;                       |

| (b) Buck (Source) PFM; (c) Boost (Sink) Mode                                                                  |

| Figure 5. 3. Operational waveforms during mode transition. 88                                                 |

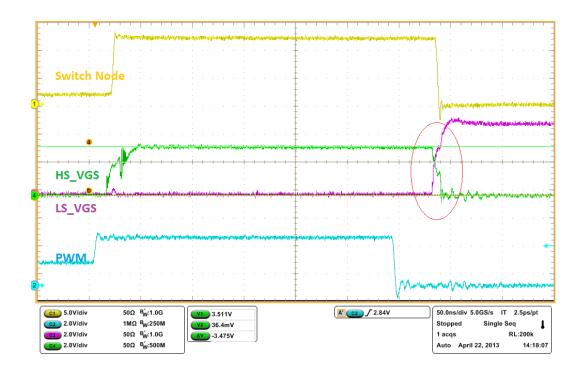

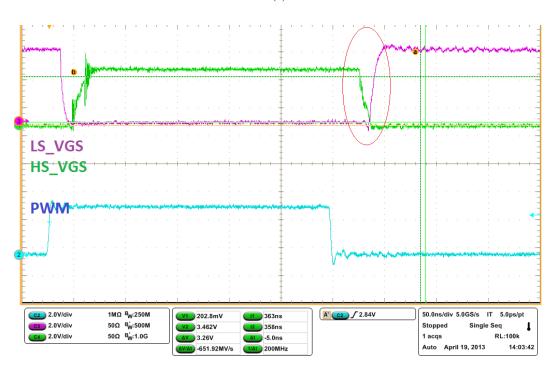

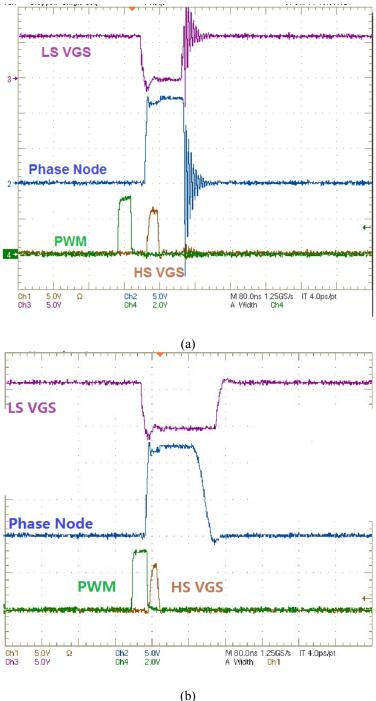

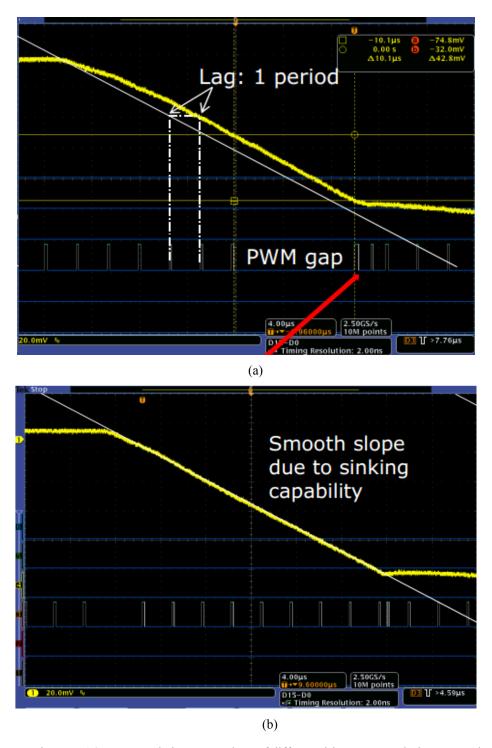

| Figure 5. 4. System dynamic comparison of different driver t <sub>watch-dog</sub>                             |

| Figure 5. 5. Experimental waveforms with different design of twatch-dog: (a) Boost (Sink)                     |

| mode: $t_{\text{watch-dog}} = 60 \text{ ns}$ ; (b) Boost (Sink) mode: $t_{\text{watch-dog}} = 120 \text{ ns}$ |

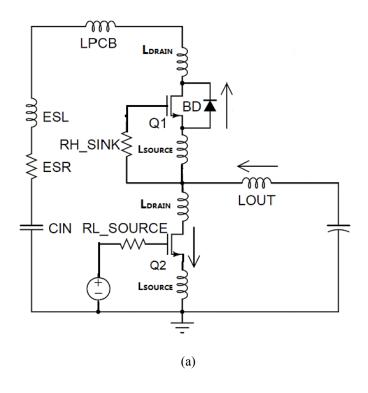

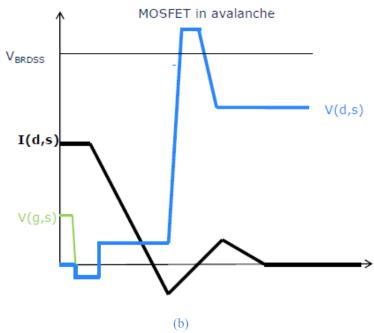

| Figure 5. 6. (a) Discrete solution of the converter considering circuitry parasitics in the                   |

| boost mode; (b) HS MOSFET enters avalanche due to high di/dt and parasitic inductance.                        |

| 92                                                                                                            |

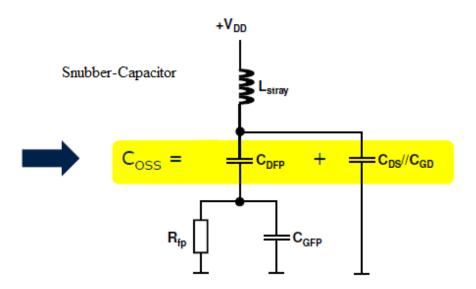

| Figure 5. 7. Equavelent circuitry with snubber when MOSFET is in off state                                    |

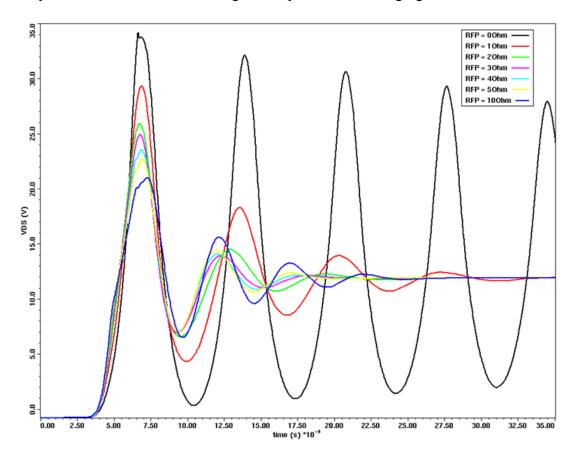

| Figure 5. 8. Simulation result of HS $V_{DS}$ waveforms with different snuber resister $R_{fb}$ . 94          |

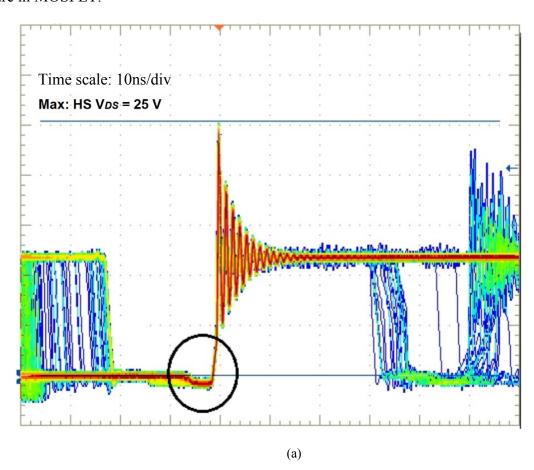

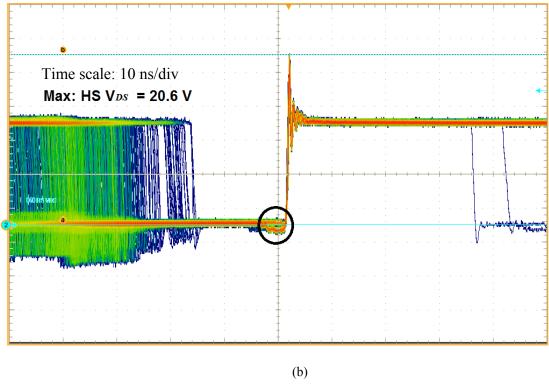

| Figure 5. 9. High side $V_{DS}$ during repetitive DVID operation: (a) $Q_{RR}$ = 20 nC and   |

|----------------------------------------------------------------------------------------------|

| without snubber circuitry; (b) $Q_{RR}$ = 10 nC with snubber circuitry. Channel 2: HS drain- |

| source voltage, 5V/div. 96                                                                   |

| Figure 5. 10. The timing architecture of the multiphase controller                           |

| Figure 5. 11. Architecture of DVID module with compensations                                 |

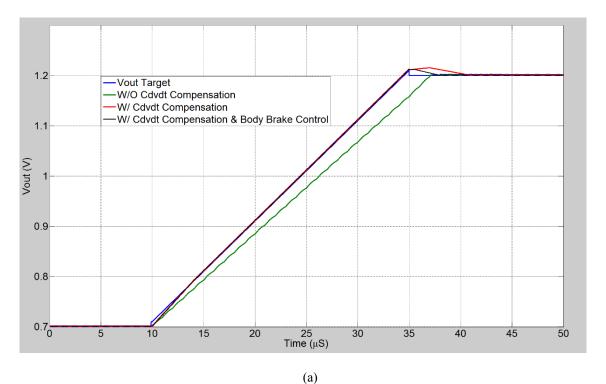

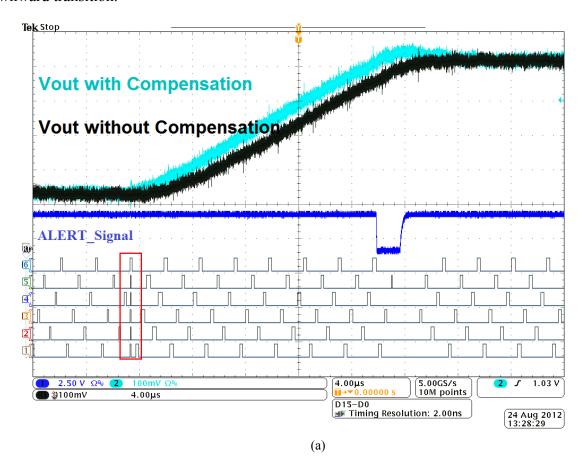

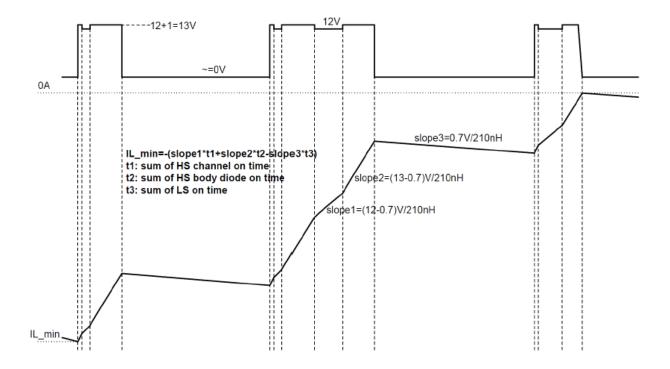

| Figure 5. 12. Matlab simulation result of DVID transition with and without droop             |

| compensation and nonlinear control: (a) DVID upward transition; (b) DVID downward            |

| transition. 100                                                                              |

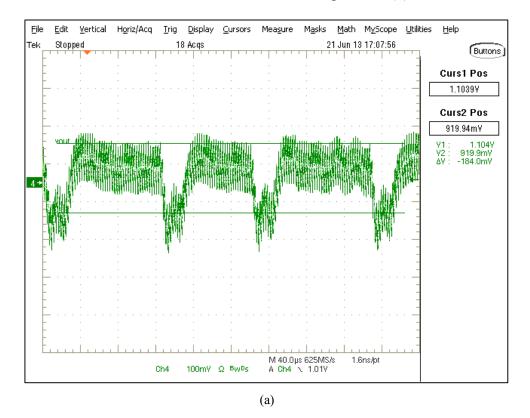

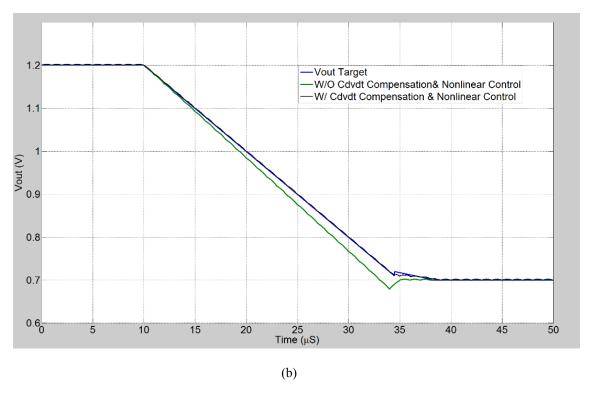

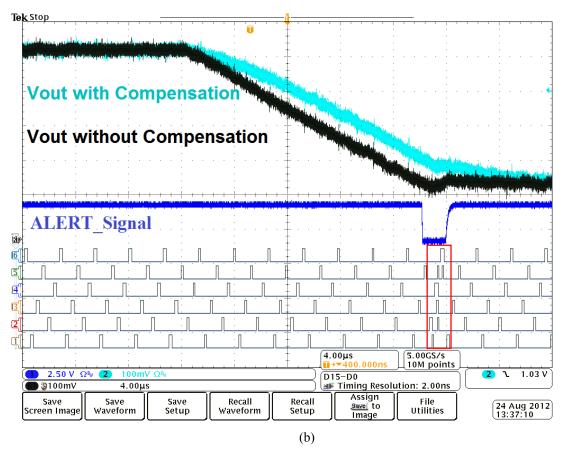

| Figure 5. 13. Experimental waveforms of fast DVID transitions with/without $C \cdot dV/dt$   |

| compensation: (a) Fast DVID upward transition; (b) Fast DVID downward transition. 102        |

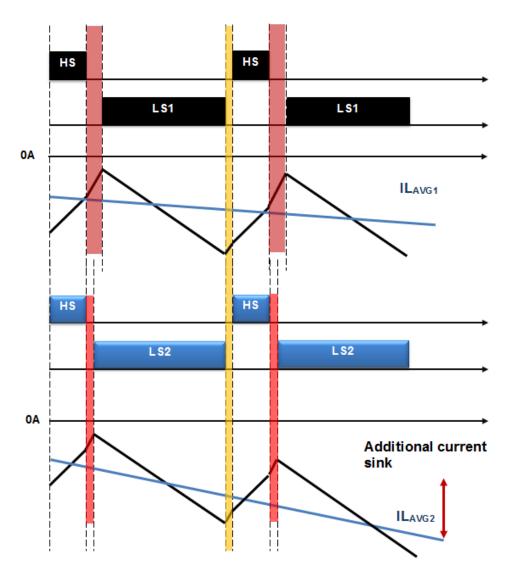

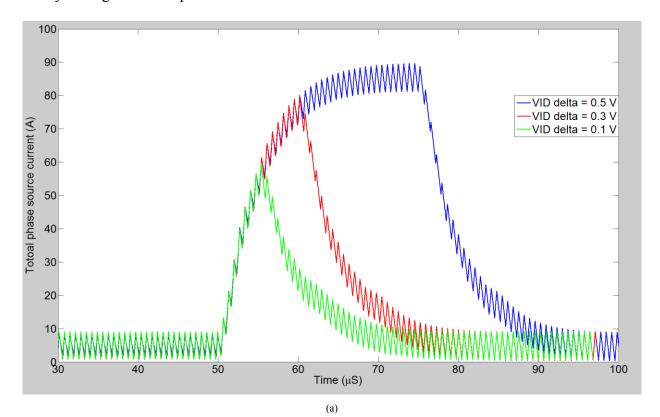

| Figure 5. 14. Simulation result of total phase current. (a) Source current at different VID  |

| transition. (b) Sink current at different VID transition. 104                                |

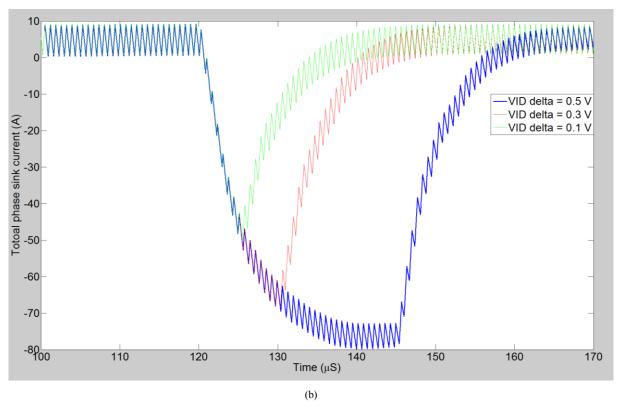

| Figure 5. 15. Negative current calculation in DVID downward transition                       |

| Figure 5. 16. Vout regulation comparison of different driver twatch-dog during DVID down.    |

|                                                                                              |

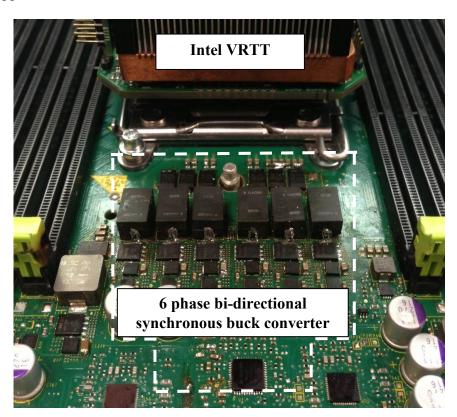

| Figure 5. 17. A six phase synchronous buck converter with Intel VRTT                         |

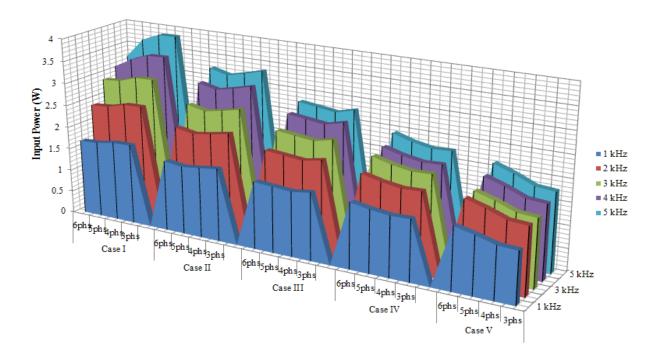

| Figure 5. 18. Input power consumption matrix(4×5×5): number of active phases in 5 VID        |

| thresholds and repetative DVID operation. 109                                                |

| Figure 5 19 Phase number control based on VID delta                                          |

# LIST OF TABLES

| Table 2. 1 DIVER DEFINTION           | 34  |

|--------------------------------------|-----|

| Table 2. 2 THE CONVERTER PARAMETERS  | 49  |

| Table 5. 1 Switching Characteristics | 107 |

| Table 5 2 MOSFET CHARACTERISTICS     | 107 |

### LIST OF ACRONYMS

AVP Adaptive voltage positioning

PFM Pulse frequency modulation

CCM Continues conduction mode

DPWM Digital pulse width modulation

LL Load line

IIR Infinite impulse response

Q<sub>g</sub> MOSFET gate charge

R<sub>G</sub> MOSFET gate resistance

$Q_{RR}$  Reverse recovery charge

FOM figure of merit

*fsw* Switching frequency

C<sub>OSS</sub> Output capacitance

C<sub>DS</sub> Drain-source capacitance

C<sub>GD</sub> Gate-drain capacitance

C<sub>GS</sub> Gate-source capacitance

C<sub>DFP</sub> Drain-field plate capacitance

V<sub>SD</sub> Diode forward voltage drop

$V_{GS(th)}$  Gate-source threshold voltage

BV<sub>DSS</sub> Drain-Source Breakdown Voltage

R<sub>fp</sub> Snubber resister in MOSFET cell

$V_{BUS}$  Input voltage of the converter

Vo Output voltage of the converter

V<sub>FET\_DRV</sub> MOSFET driving voltage

DCR Direct current resistance

LSB Least significant bit

GPIB General purpose interface bus

ZCS Zero current switching

ZVS Zero voltage switching

### **CHAPTER ONE: INTRODUCTION**

Power conversion techniques have been continuing to be the focus in the power management industry. With ever increasing the emphasis on power efficiency, switch mode power supplies and power management ICs are extensively used in automotive, smart phones, TVs, desktop PCs, servers, notebooks and etc. According to IMS research [1] power management & driver IC reaches \$13.9567 billion in revenue in the fiscal year 2011.

The current and forecast worldwide market for power management ICs shipment (units in million) are shown in Figure 1. 1. [1].

# Power Management & Driver ICs by Application (Shippment in MU) 8000 7000 6000 4000 3000 2000 1000 Authorities Symptometric Application (Shippment in MU)

Figure 1. 1. The world market for power management IC by application.

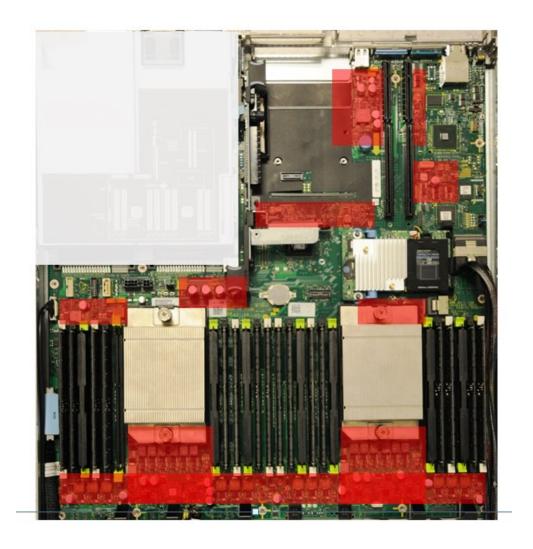

Figure 1. 2. Voltage regulator real estate in server motherboard.

This is the newly released Dell PowerEdge R620 Server motherboard. It can support two 150 W high end CPUs and 4 memory channels up to 768GB of memory (32GBx24dimms). The multiphase voltage regulators, 2 for CPU, 4 for MEM and the rest point of load (POL) VRs are highlighted in red. The VRs convert 12V DC from the PSU output to various voltage levels to power up the CPUs, memories, hard drives, ASICs on board and peripheral cards. It occupies more than 10% area of the motherboard.

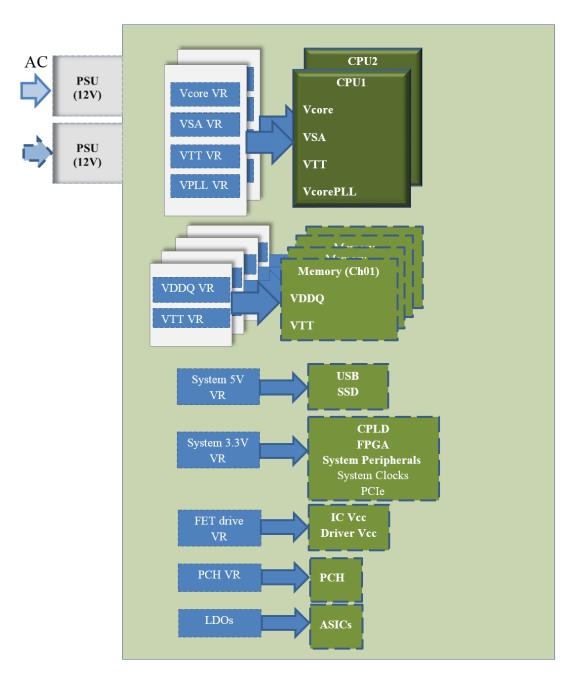

Figure 1. 3. A typical power management map for server system.

Figure 1. 3 shows a simplified power management map for a typical 2S (socket) server system. System interaction is eliminated in the illustration and the focus is only on the power conversion.

### 1.1 Introduction to Multiphase Buck Converter

As the complexity and number of transistors exponentially rise in the modern high end processors, the supply current specification is common to be above 100A. Paralleling the regulators is the only way to alleviate the thermal stress on the power components (power MOSFETs, power inductor). Therefore, multiphase buck converter has been employed in the power conversion field. Although the initial concept has been adopted in power management industry for quite a while, there are still a lot of areas worth investigating due to the increasing complexity of the power architecture and growing focus on the green energy. Green energy here refers to less power conversion loss and less output capacitors.

Figure 1. 4. A multiphase synchronous buck converter for CPU application.

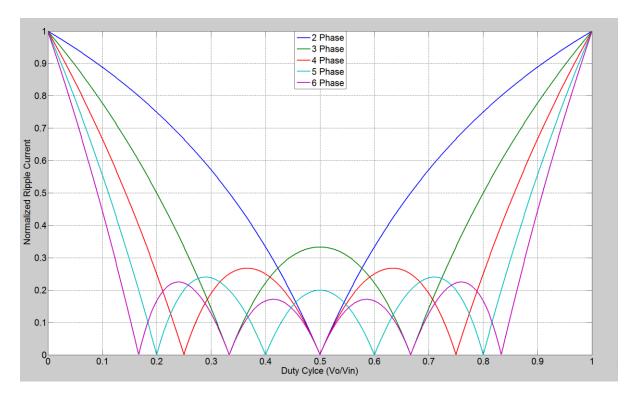

Figure 1. 5 shows the relationship of normalized ripple current between duty cycle and phase number.

Figure 1. 5. Normalized ripple current as a function of phase number and duty cycle.

The benefits of adopting multiphase buck converter in the design are bulleted as follows:

- Decreased I<sub>RMS</sub> and reduced power loss;

- Increased inductor current slew rate:  $L_{effective} = \frac{L}{N_{phase}}$ ;

- Output inductor current cancellation and voltage ripple reduction;

- Optimized efficiency over the whole load range, especially, in light load

- Load adaptive control(LAC)

- Pulse skipping control(PFM)

- Better dynamic voltage regulation capability

However, with those advantages, there are challenges that the multiphase converter have brought in as well. The challenges are the major focus of this dissertation.

Figure 1. 6. A typical power delivery path for today's microprocessors.

Figure 1. 6 shows a typical power delivery path for today's microprocessors. With all the mechanical restriction, the power inductors and output capacitors need to be placed close to the processors in order to reduce the power distribution loss.

### Power Distribution Impedance versus Frequency Zone 1 Zone 2 Ω Output Filter PWM Droop control Bulk & MLCC & compensation BW Z<sub>LL Max</sub> Z target = Z<sub>LL</sub> Zone 3 Inductive effects $Z_{LL\ Min}$ MLCC ESL + Socket F<sub>break</sub> VR'BW 500 kHz 700 kHz

Figure 1. 7 Power distribution impedance versus frequency.

Closed-loop output impedance of voltage regulator is an important specification in the frequency domain. Figure 1. 7 [2] shows the output impedance plot of a power supply for CPU application with AVP. The output impedance, as shown by the red curve, is determined by the

power supply's AVP design value within the loop bandwidth of the VR. At higher frequency, the output impedance will be dominated by the ESL of MLCC and the socket.

Figure 1. 8 shows the pyramid of server power design. Robustness is of the top priority in the power design since the system are running with various kinds of customer's data, some of which are very critical. The power related failures can stop the transaction or communication and would create substantial loss. The power conversion efficiency is the foundation of the power design. Design parametric optimization and latest silicon technology adoption should be rigorously studied. Functionality, such as, phase shedding control and load transient enhancements, shows the advancement of the design and can improve the system reliability, efficiency and reduce the cost. Cost reduction is the final step to optimize the design and give environment less burden.

Figure 1. 8. Robustness, efficiency and cost pyramid in server power design.

# 1.2 Adaptive Voltage Positioning

Due to the working mode of the processors, load transient is an important design requirement for multiphase synchronous buck converter. Adaptive voltage positioning (AVP) has been adopted to lower the power dissipation, especially at heavy load [3] - [5]. The introduced constant output impedance reduces the value of output capacitance.

Figure 1. 9 illustrates the comparison results of AVP implementation when load transient events occur. The introduced AVP window can be fully utilized to optimize the load transient.

Figure 1. 9. Load transient without and with AVP implementation.

Figure 1. 10. AVP design in analog realization.

Figure 1. 10 illustrates the block diagram of AVP design in an analog realization [6]

Figure 1. 11. AVP design in digital realization.

To make it simple, the adaptive voltage position (AVP) design is to use the entire AVP window for voltage excursions during the transient event. As depicted in Figure 1. 12, another design benefit of adopting AVP scheme is that the output power of the multiphase VR at full load, thus, less thermal burden compared to the implementation without AVP.

Figure 1. 12. Output power comparison with different LL.

The differential output of the sensed inductor current feeds into the dedicated ADC and digitized values are summed together for the total load current. The  $V_{REF}$  is generated by the current VID minus the filtered (averaged) output of summation of phase current multiplied by the load line.

$$V_{Target} = VID - I_{LOAD} \cdot R_{LL} \tag{1.1}$$

### 1.3 Review of Prior Arts

In order to meet the stringent transient requirement, novel control schemes [12] -[15] should be adopted to meet the specification and minimize the output capacitance. Traditional voltage mode based buck converter is the most popular thus widely adopted topology in the power management industry. It is a clock based converter and the VR needs to wait the entire switching cycle to issue the next PWM on pulse no matter when the transient event occurs. Constant ON-time (COT) is a popular scheme. Traditional COT uses ESR of output capacitor as

output current feedforward term to initial the pulse. Current mode hysteretic control [17] [18] is a very popular topology to achieve fast transient response. It uses sensed/synthetic inductor current to compare against the hysteresis band. In [18] authors propose current mode hysteretic control that can accomplish the AVP by the natural hysteresis band, however, the fairly constant hysteretic window cannot pull in the pulse fast enough when the transient event occurs.

### 1.3.1 Constant ON-time (COT)

Constant ON-time (COT) is a popular frequency modulation scheme which is capable of achieving fast transient response.

Figure 1. 13. Constant ON time.

The core of the modulator is the one-shot that sets the HS ON-time. The  $T_{ON}$ , as shown in (1.2), is inversely proportional to  $V_{IN}$  and proportional to the  $V_{OUT}$ :

$$T_{ON} = T_{SW} \frac{V_{OUT}}{V_{IN}} \tag{1.2}$$

As shown in Figure 1. 13, when  $V_{FB}$  becomes lower than  $V_{REF}$ , the next ON period is initiated. On pulse period stays for a predetermined period as equation (1.2) indicates. The clockless architecture shows the advantage that the HS pulse can be initiated sooner when transient

event occurs. There will be a minimum OFF-time between the HS pulses to guarantee the current sensing purpose. The minimum OFF-time also decides the maximum duty cycle that the VR can support.

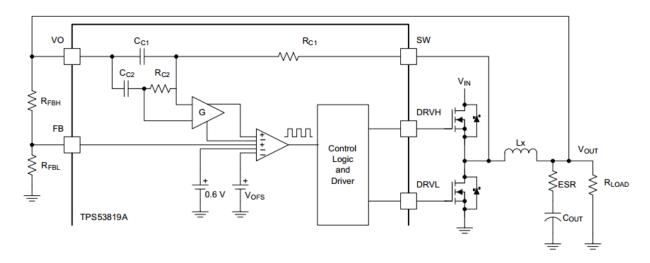

Figure 1. 14. Simplified voltage mode COT architecture with ripple injection.

The D-CAP2 control scheme [19], introduced by Texas instruments, includes an internal ripple generation circuitry, RCC, as the red block in Figure 1. 14. Compared with first generation of D-CAP, multi-layer ceramic capacitors (MLCC) solution with very low ESR can be used due to the ripple injection. The hybrid control mode is to employ the emulated inductor current ripple and then combine it with the voltage feedback signal.

To meet small-signal stability, the output capacitance value should be governed by (1.3)

$$5 \times f_{C2} \le \frac{R_{C1} \times C_{C1} \times 0.6 \times (0.67 + D)}{2\pi \times G \times L \times C_{OUT} \times V_{OUT}} \le \frac{f_{SW}}{3}$$

(1.3)

where G =0.25.  $R_{C1} \times C_{C1}$  time constant can be referred to TPS53819 datasheet. D is the duty cycle.

### 1.3.2 Current Mode Hysteresis

Hysteretic control is a very popular topology for fast transient required application. A drawback of traditional hysteretic control from the static point of view is the switching frequency is variable (clock-less), which is defined by parasitic elements, primarily the ESR of the output capacitor. Advanced hysteretic control incorporates the frequency control (phase-locked loop) to stabilize the switching frequency.

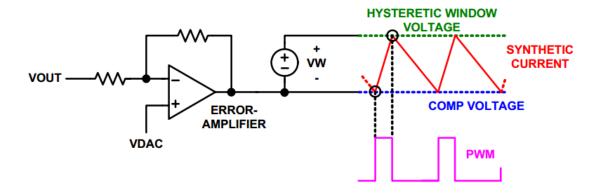

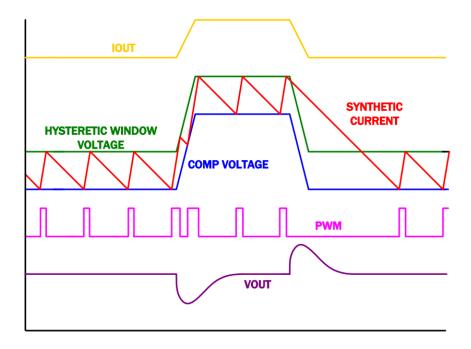

Intersil refers to the R4 (Robust Ripple Regulator as described with R3) Modulator as a "Current-Mode Hysteretic" modulator (CMH). It is a variable frequency switching architecture which operates without a clock and uses a hysteretic band against which a "current" signal is compared. However, true inductor current is not used for the modulation, unlike a true current-mode controller. A synthesized (synthetic) current ripple is generated and compared against the hysteretic window that is created relative to the voltage loop feedback to determine power switch on and off times. Also there is no compensating ramp utilized. The architecture does not make use of any voltage feedback compensation and no integrator. Therefore it has the capacity for fast transient response and easier deployment of a design.

Figure 1. 15. Simplified R4<sup>TM</sup> modules for PWM generation.

Figure 1. 15 [22] shows the modulator core of the R4 controller, the error-amplifier, synthetic current generator and the hysteretic window comparator. The error voltage, generated by the VDAC minus feedback, compares against monitors the synthetic current signal against and corresponding window voltage to determine the PWM switching events.

Figure 1. 16. Simplified operation waveform during load transient.

Figure 1. 16 [22] shows the operational waveform during load assertion and load release. Switching frequency, as the magenta curve indicates, speeds up during load assertion and slows down during load release. Both PWM edges are modulated since the synthetic current compares against Hysteric upper window and  $V_{\text{COMP}}$  voltage.

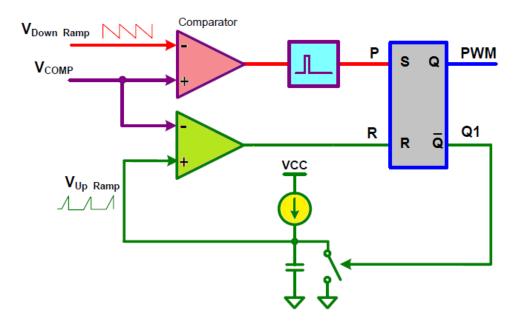

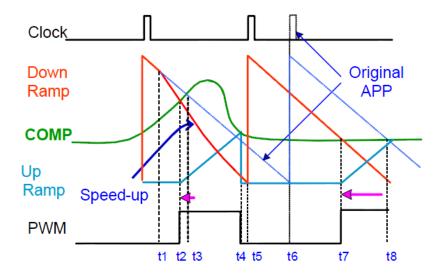

### 1.3.3 EAPP

Minimizing the delay in control loop is critical during transient event. Based on the advantages of trailing/leading edge modulation during turning OFF/ON, the enhanced active pulse positioning (EAPP) is able to minimize both ON/OFF delays by combining the schemes as discussed in [24].

Figure 1. 17. Schematic diagram of EAPP circuitry.

The simplified block diagram and the corresponding operational waveforms are illustrated in Figure 1. 17. During transient event, EAPP will turn on PWM early (from t3 to t2) and move the next PWM ahead (from t8 to t7) to reduce the blanking time. Figure 5 shows transient load engage response of 3-phase VR with EAPP [24], [25].

Figure 1. 18. Dual-Edge and Variable-Frequency Operational Waveforms.

### 1.4 Dissertation Outlines

The primary focus and objective of the dissertation is to comprehensively investigate the current and voltage dynamics of the multiphase synchronous buck converter. We focus on optimizing the topology to achieve best efficiency and highest possible reliability based on the real system running condition and corner case scenarios.

In chapter 1, we introduce the background information of the importance of power management IC in different business sectors, then the scenario multiphase synchronous buck converter and briefly talk about the AVP design that can reduce output capacitors and power dissipation. The ongoing research and advanced control topologies are reviewed and several nonlinear control schemes are studied

In chapter 2, we start the efficiency optimization from static operation. First, we design the compensation of the voltage mode controller with digitized format. We meticulously study the power loss in several modes of operation, i.e. buck, PFM and boost modes, which cover all the operation scenarios of CPU VR. Driver interface is thoroughly investigated here for operation and efficiency purposes. Switching waveforms are understood better with all the parasitics. An efficiency optimization routine is generated by parametric variation.

In chapter 3, we propose the load transient enhancement schemes to minimize the output voltage excursion during low repetitive load transient. We first study the DCR current sense impact for the AVP loop, which can effectively shape the output voltage excursion. During load engage, the pulse should be pulled in fast enough to compensate the voltage deviation. During load release, adaptive body braking schemes are proposed to adaptively suppress the voltage overshoot during load release. Special design consideration needs to be carried out during slow phase shedding that the inductor current in the shedded phase needs to be ramped down to zero before turn OFF the phase. A corner case operation with potential power MOSFETs shoot-through is captured and new dead-time management scheme is proposed to maintain the high efficiency, eliminate the shoot-through and hence ensure the system reliability.

In chapter 4, we first study the sampling nature of PWM converter. The closed loop system output impedance is derived and the compensation network are optimized in the high frequency range to attenuate the high frequency system noise. Beat frequency is studied and load frequency detection scheme and current protection in the control loop are proposed to mitigate the issue and bound the phase current.

Multiphase converter design capable of dynamic voltage scaling (DVS) is presented in chapter 5. Modes of operation are thoroughly studied first. Optimized driver dead-time in boost

mode operation are illustrated and DVID downward transition can be achieved with shared phase current. The excessive stress on the control MOSFET which increases the reliability concern is captured in boost mode operation. Feasible solutions are also proposed and verified by both simulation and experiment results. CdV/dt compensation for removing the AVP effect and novel nonlinear control scheme for smooth transition are proposed for dealing with fast voltage positioning. Optimum phase number control during dynamic voltage transition is also proposed and triggered by voltage identification (VID) delta to further reduce the dynamic loss.

Chapter 6 presents the conclusions and the future work is outlined.

# **CHAPTER TWO: OPTIMIZATION ON STATIC OPERATION**

Figure 2. 1. The architecture of the bidirectional multiphase synchronous controller.

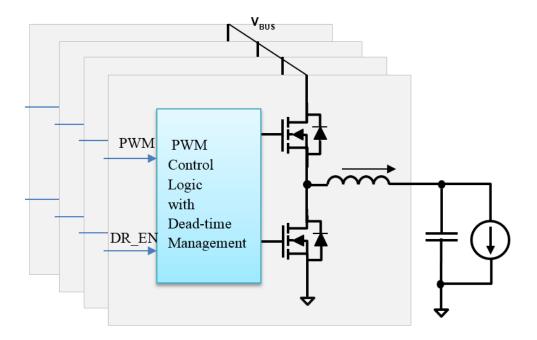

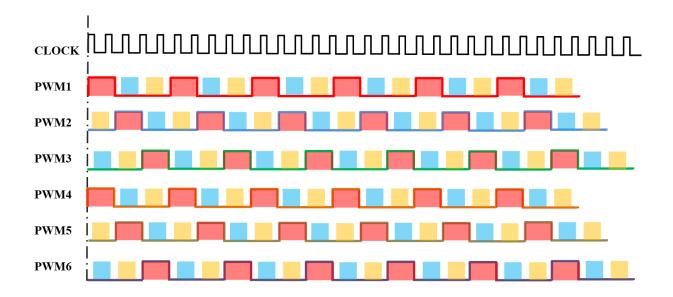

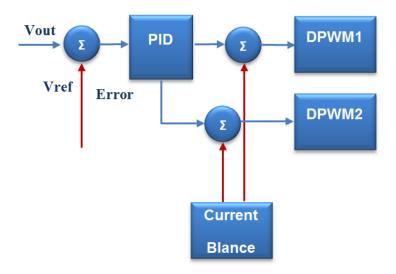

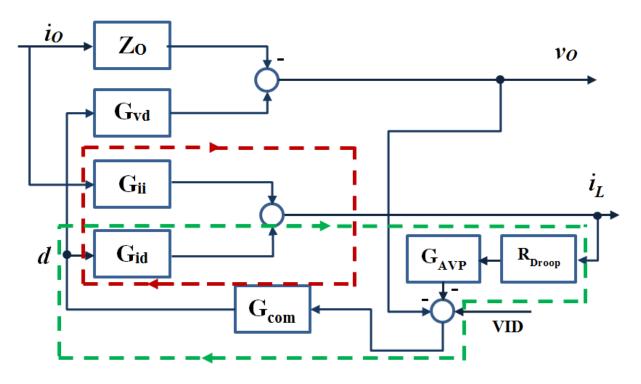

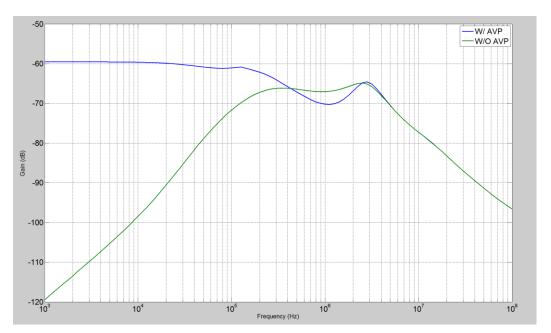

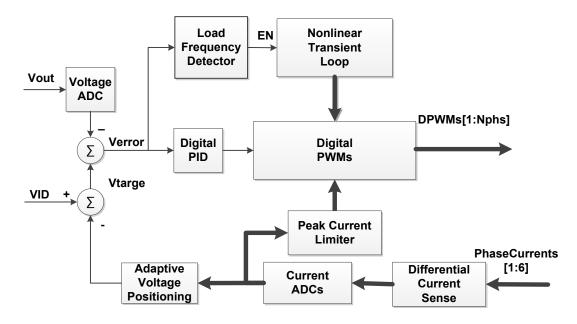

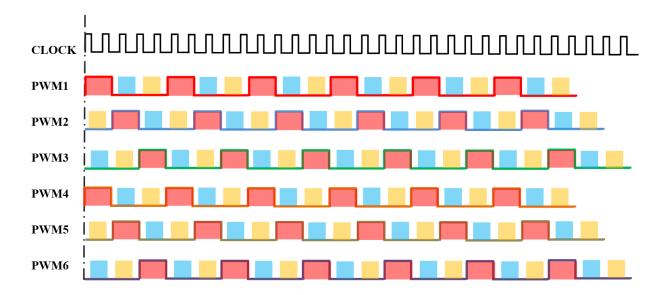

Figure 2. 1 shows the architecture of the multiphase synchronous buck converter which can be working in the bidirectional fashion. Each phase is interleaved by 360/N<sub>PHASE</sub> to achieve optimal ripple cancellation. In the controller section, the main sub-circuit modules are illustrated. Current ADC module samples and digitizes each phase current, which is the voltage across the cap of inductor DCR the sense network, in the real time manner. Voltage ADCs sense and digitize both the V<sub>OUT</sub> and V<sub>BUS</sub>, and the digitized V<sub>BUS</sub> acts as feed-forward term in the control loop. Adaptive voltage positioning (AVP) module decodes the VID command and generates the reference based the digitized total phase current information with DVID compensation. Digital compensator filters the error voltage generated by ADC output and AVP blocks and feeds into the DPWM generator block. Current balance module, which is designed as 1/5 of the voltage loop, and Nonlinear PWM generator both modifies DPWM patterns in different fashions. The control outputs of DPWM generators are the PWM and driver enable (DR EN) signals.

# 2.1 Compensation Design

Compensator design is the core of VR design [7] [8]. As shown in Figure 2. 2, a small signal ac model is presented.  $V_{\text{out}}(s)$  is the function of the reference voltage  $V_{\text{target}}(s)$ , line input voltage  $V_{\text{in}}(s)$  and the output load current  $I_{\text{out}}(s)$ . The design objective is the VR capable of rejecting the disturbances of the line input voltage and output load current, good transient response and stability.

Figure 2. 2. Small signal model of voltage mode buck converter.

$$\hat{v}_{out}(s) = G_{vd}(s)\hat{d}(s) + G_{vq}(s)\hat{v}_{in}(s) - Z_o(s)\hat{i}_{out}(s)$$

(2.1)

$$G_{vd}(s) = \frac{\hat{v}_{out}(s)}{\hat{d}(s)} \big|_{\hat{v}_{out}(s)=0}^{\hat{v}_{in}(s)=0} = \frac{V_{in}(1 + sR_{ESR}C_{OUT}) \frac{R_{Load}}{(R_{Load} + R_{DCR})}}{s^2 LC_{OUT} \left(\frac{R_{Load} + R_{ESR}}{R_{Load} + R_{DCR}}\right) + s\left(\frac{L}{R_{Load} + R_{DCR}} + C_{OUT}R_{ESR} + R_{Load}//R_{DCR}\right) + 1} (2.2)$$

$$Z_{o}(s) = \frac{\hat{v}_{out}(s)}{\hat{v}_{out}(s)} |\hat{d}(s)=0 = \frac{\left(1 + \frac{sL}{R_{DCR}}\right) (1 + sR_{ESR}C_{OUT}) \frac{R_{Load}R_{DCR}}{(R_{Load} + R_{DCR})}}{s^{2}LC_{OUT} \left(\frac{R_{Load} + R_{ESR}}{R_{Load} + R_{DCR}}\right) + s\left(\frac{L + R_{Load}R_{DCR} + C_{OUT}R_{ESR}(R_{Load} + R_{DCR})}{R_{Load} + R_{DCR}}\right) + 1}} (2.3)$$

$$G_{vg}(s) = \frac{\hat{v}_{out}(s)}{\hat{v}_{in}(s)} \Big|_{\hat{v}_{out}(s)=0}^{\hat{d}(s)=0} = D \frac{\frac{R_{DCR}(1+sR_{ESR}c_{OUT})}{R_{Load}+R_{DCR}}}{\frac{s^2Lc_{OUT}(R_{Load}+R_{ESR})}{R_{Load}+R_{DCR}} + s \frac{(L+c_{OUT}(R_{ESR}(R_{Load}+R_{DCR})+R_{Load}R_{DCR})}{R_{Load}+R_{DCR}} + 1} (2.4)$$

$$T_{\nu}(s) = G_{\mathcal{C}}(s)F_{\mathcal{M}}G_{\nu d}(s) \tag{2.5}$$

The derivation is based on the state-space averaging model.

Gvd(s) is a state-space averaging model for the plant, which represents open loop control-to-output voltage transfer function.

Zo(s) is the output current-to-output voltage transfer function.

Gvg(s) is the open loop input-to-output voltage transfer function.

## 2.1.1 Direct Digital Design

Due to the double pole of output filter in the voltage mode control, as shown in Figure 2.

3, two zeros from the type III compensation network are needed so that the phase can be boosted by 180 degrees. There are two methods to design the digital compensation network:

- (1) Emulation method, design the analog compensation first in Laplace domain and transfer to digital domain.

- (2) Direct digital design, design the compensation network in digital domain by first digitizing the plant.

Figure 2. 3. Generic type III compensation network.

Figure 2. 4. Digital control loop block diagram

To digitize the plant, there are several methods can be used, for example Zero-Pole matching (ZPM), Impulse Invariant Mapping, as well as, Tustin approximation. We use ZPM as the method of conversion. The matched DC gains is necessary for analog and discretized systems. The zeros and poles are transformed by the following equation:

$$z_i = e^{s_i/F_S} \tag{2.6}$$

where,  $s_i$  is the ith pole or zero of the continuous-time system.  $z_i$  is the ith zero or pole of the discretized system accordingly.  $F_S$  is the sampling frequency.

#### 2.1.2 Root Locus and Bode Plot

Root locus is a graphical technique of studying the roots (poles and zeros) of the characteristic equation of a linear system [9]. Matlab SISO design tool [10] can be utilized to move the poles and zeros location so that the desired system bandwidth and phase margin can be guaranteed.

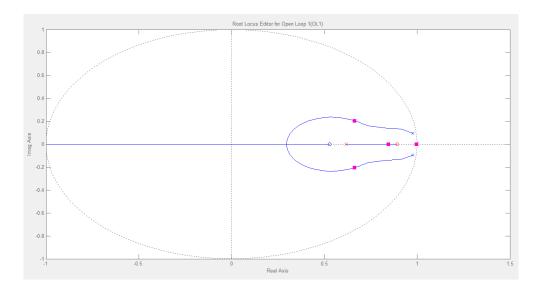

Figure 2. 5. Root Locus.

Figure 2. 5 shows the system root locus plot using Matlab.

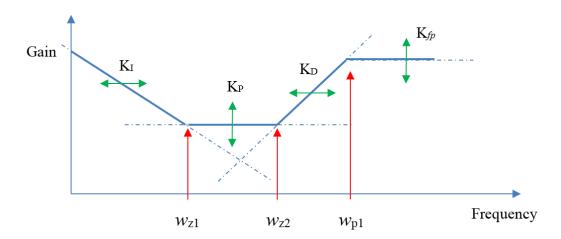

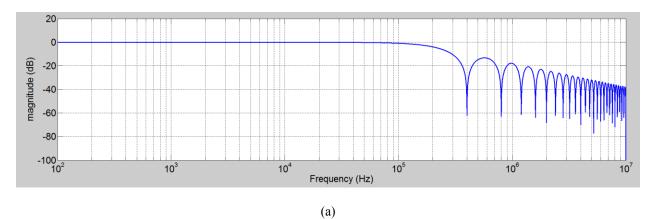

Figure 2. 6. Bode plot.

Figure 2. 6 shows the compensator gain in frequency domain.  $K_I$  and  $K_D$  are dominating in both low frequency and high frequency ranges.  $K_P$  maintains compensator gain in middle frequency range, which affects loop BW.  $K_{fp}$  is essential for high frequency noise reduction which rolls off loop gain at high frequency.

# 2.2 Power Loss Analysis

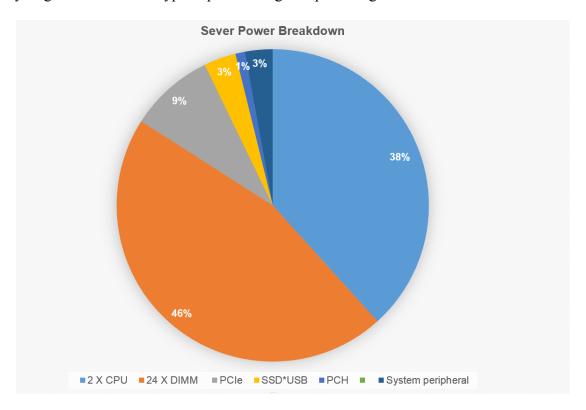

In order to support various system running configuration, the VR design (multiphase + single phase) in server application need to cover the entire loading condition and then budget wisely. Figure 2. 7 shows a typical power budget in percentage scale.

Figure 2. 7. A power design breakdown in server application.

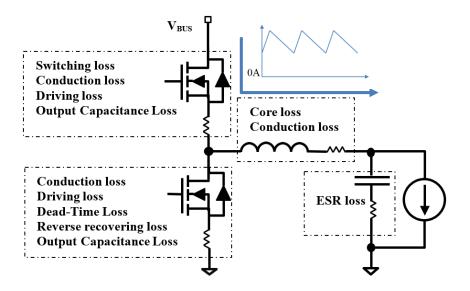

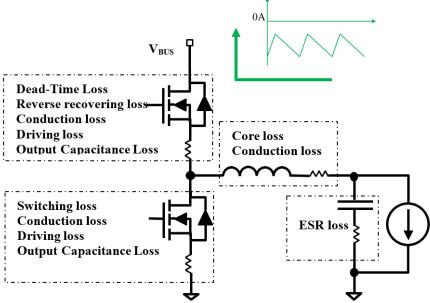

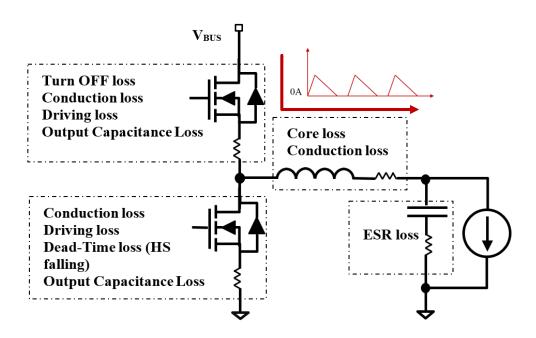

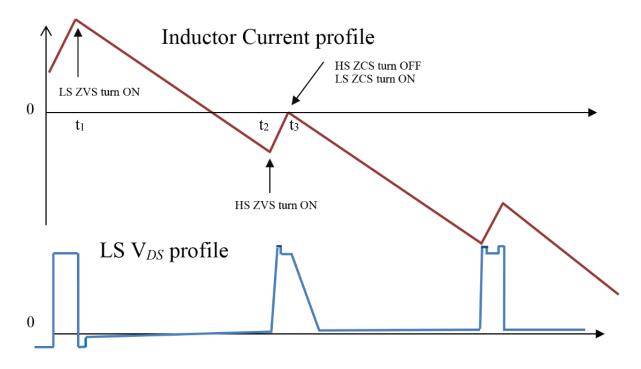

The power conversion loss [26] - [29] should be understood well first then optimized accordingly. Due to the different operation modes of buck converter, the loss model is divided in three cases, CCM buck, CCM boost and PFM buck, respectively. The corresponding power loss representations with inductor current profiles are shown in Figure 2. 8, Figure 2. 10 and Figure 2. 19, respectively.

Figure 2. 8. Power loss distribution of a synchronous buck in buck mode.

Power loss simulation and experimental verification should be both carried out with varying switching frequency and PVCC( MOSFET drive voltage). The following equations shows power loss portion when the VR is operating in synchronous buck mode.

The recent development of power MOSFETs has been focusing on the ultra-low channel resistance and ultra-fast switching speed. FOM is a fast measure to gauge the MOSFET under the same breakdown voltage. Infineon's OptiMOS<sup>TM</sup> and Fairchild Semi's PowerTrench® are considered industry leading technologies of low voltage power MOSFETs.

$$FOM = R_{ds\_ON} \cdot Q_g \tag{2.7}$$

The conduction loss is the resistive loss due to current conducted through the channel resistance  $R_{ds\_{\rm ON}}$ .

$$P_{COND} = I_{RMS}^{2} \cdot R_{ds \ ON} \tag{2.8}$$

$$I_{RMS(LS)} = \sqrt{\left(\frac{I_{out}^2 - I_{ripple}^2}{N^2}\right)(1-D)}$$

(2.9)

$$I_{RMS(HS)} = \sqrt{\left(\frac{I_{out}^2}{N^2} + \frac{I_{ripple}^2}{12}\right)D}$$

(2. 10)

P<sub>COSS</sub> is the power loss caused by the output capacitance of MOSFET

$$P_{COSS} = 0.5 \cdot Q_{OSS} \cdot V_{BUS} \cdot f_{SW} \tag{2.11}$$

P<sub>deadtime</sub> represents the body diode conduction loss during t<sub>deadtime</sub>.

$$P_{deadtime} = V_{SD} \cdot f_{SW} \cdot \left[ \left( I_{OUT} - \frac{I_{ripple}}{2} \right) t_{deadtime(r)} + \left( I_{OUT} + \frac{I_{ripple}}{2} \right) t_{deadtime(f)} \right]$$

(2. 12)

where  $V_{SD}$  is diode forward voltage drop;  $t_{deadtime(r)}$  represents rising edge dead-time between LS turn off and HS turn on;  $t_{deadtime(f)}$  represents rising edge dead-time between HS turn off and LS turn on.

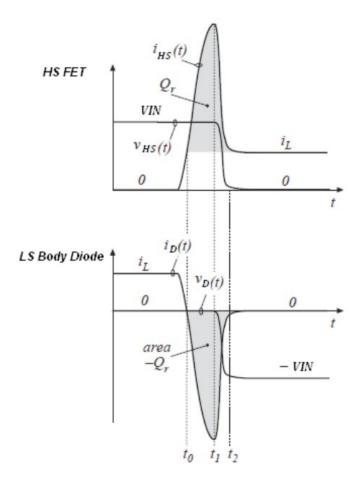

$P_{QRR}$ , the LS body diode reverse-recovery loss, is induced during the phase of turning off of the LS body diode.

$$P_{ORR} = Q_{RR(LS)} \cdot V_{BUS} \cdot f_{SW} \tag{2.13}$$

where  $Q_{RR}$  is the excess minority carrier charge in the reverse recovery transient.

Figure 2. 9. Diode reverse-recovery waveforms

In the buck mode operation, the LS MOSFET is considered as soft switching. The HS MOSFET turn on/off loss incorporating common source inductance due to device package can be accurately calculated by:

$$P_{SW(ON)} = V_{BUS} \cdot f_{SW} \cdot \left(I_{OUT} - \frac{I_{ripple}}{2}\right) \cdot \left(\frac{\frac{\frac{0.5 \cdot Q_{gS2(HS)}}{V_{FET_{DR}} - V_{PL(HS)}}}{R_{g(HS)} + R_{driver} + L_{csi} \cdot \frac{I_{OUT} - \frac{I_{ripple}}{2}}{Q_{gS2(HS)}}} + \frac{1}{R_{g(HS)} + R_{driver}} + \frac{1}{\sqrt{\frac{R_{g(HS)} + R_{driver}}{2} + \frac{L_{csi} \cdot Q_{OSS(LS)}}{Q_{gd(HS)}^2}}}}{\frac{2^{L_{csi} \cdot Q_{OSS(LS)}}}{Q_{gd(HS)}^2} + \frac{1}{\sqrt{\frac{R_{g(HS)} + R_{driver}}{2} + \frac{L_{csi} \cdot Q_{OSS(LS)}}{Q_{gd(HS)}^2}}}}}\right)}$$

$$(2. 14)$$

$$P_{SW(ON)} = V_{BUS} \cdot f_{SW} \cdot \left(I_{OUT} + \frac{I_{ripple}}{2}\right) \cdot \underbrace{\begin{pmatrix} \frac{\frac{0.5 \cdot Q_{gS2(HS)}}{V_{PL(HS)}}}{\frac{I_{OUT} + \frac{I_{ripple}}{2}}{Q_{gS2(HS)}}} + \\ \frac{\frac{1}{R_{g(HS) + R_{driver} + L_{csi}} \frac{I_{OUT} + \frac{I_{ripple}}{2}}{Q_{gS2(HS)}}}{\frac{0.5 \cdot Q_{gd(HS)}}{Q_{gd(HS)}}} \\ \frac{-\left(R_{g(HS) + R_{driver}}\right) + \sqrt{\left(R_{g(HS) + R_{driver}}\right)^{2} + \frac{L_{csi} \cdot Q_{OSS(LS)}}{Q_{gd(HS)}}\left(V_{PL(HS)}\right)}}{\frac{2^{L_{csi} \cdot Q_{OSS(LS)}}}{Q_{gd(HS)}}} \right)}$$

(2. 15)

where *I<sub>OUT</sub>*, *V<sub>BUS</sub>*, *V<sub>FET\_DR</sub>*, R<sub>g</sub>, V<sub>PL</sub>, R<sub>driver</sub>, Lcis, Q<sub>ds</sub> and Q<sub>gd</sub> are the output current, Bus voltage, gate drive voltage, gate drive resistance, HS MOSFET plateau voltage, HS MOSFET source inductance, current, HS MOSFET Q<sub>ds</sub> and HS MOSFET Q<sub>gd</sub>, respectively.

The gate charge induced loss:

$$P_{gate} = (Q_{g(HS)} + Q_{g(LS)}) \cdot V_{FET\_DR} \cdot f_{SW}$$

(2. 16)

The switching frequency and  $V_{FET\_DR}$  should be optimally selected based on the minimum power loss.

Figure 2. 10. Power loss distribution of a synchronous buck in boost mode.

When the inductor current flow reversely, as shown in Figure 2. 10, the converter is enforced working in sink mode, or boost mode. The loss formulas change accordingly. HS power MOSFETs are soft switching.

$$P_{QRR} = Q_{RR(HS)} \cdot V_{BUS} \cdot f_{SW} \tag{2.17}$$

LS power MOSFETs are consequently hard switching in the boost mode. The simplified turn ON/OFF losses are:

$$P_{SW(ON)} = (V_{BUS} + V_{SD}) \cdot f_{SW} \cdot \left(I_{OUT} + \frac{I_{ripple}}{2}\right) \cdot \left(\frac{Q_{SW}}{\frac{V_{FET\_DR} - V_{PL}}{R_g + R_{driver}}}\right)$$

(2. 18)

$$P_{SW(OFF)} = (V_{BUS} + V_{SD}) \cdot f_{SW} \cdot \left(I_{OUT} - \frac{I_{ripple}}{2}\right) \cdot \left(\frac{Q_{SW}}{\frac{V_{FET\_DR} - V_{PL}}{R_g + R_{driver}}}\right)$$

(2. 19)

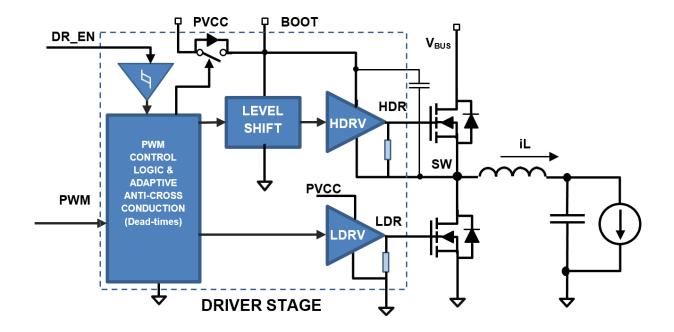

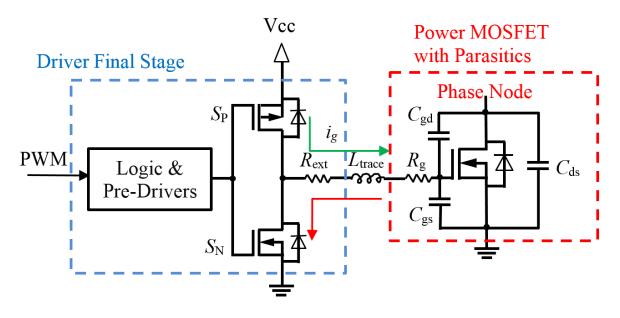

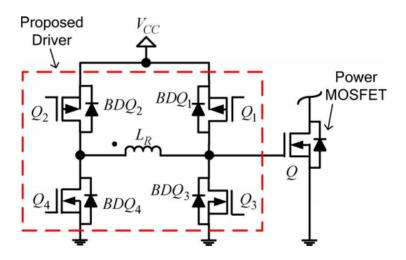

### 2.3 Driver Interface

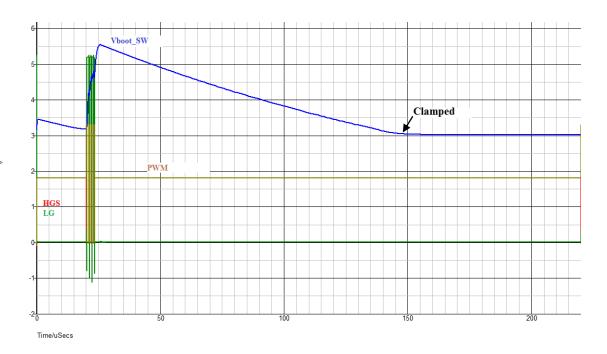

One phase of the multiphase synchronous buck converter with the dead-times management is shown in Figure 2. 11. Dead time  $t_{\text{dead-time}}$  [30] during which both power MOSFETs (Q<sub>1</sub> and Q<sub>2</sub>) are off, is inserted between the gate signal cycle to avoid cross-conduction and guarantee safe operation of the circuitry. There is another dead time which is very critical in the driver IC design for the DVID downward operation, i.e. watch-dog timer  $t_{\text{watch-dog}}$ , which is defined as from HS gate signal is low and switch node is still high, after this defined time length, the LS MOSFET is turning on. The detailed analysis of system impact by  $t_{\text{watch-dog}}$  is in chapter V.

Figure 2. 11. Driver IC block diagram with proposed dead-time management.

Dead-time must be sufficient enough to guarantee no cross conduction between high & low side MOSFETs. However, a longer dead-time will bring in more switching power loss to a VR since the body diode but not channel of low-side MOSFET turn on during dead-time. On the other hand, a shorter dead-time may increase risk of cross-conduction. Therefore, Dead-time management is critical in a MOSFET driver, which will directly impact VR efficiency and reliability.

The discrete driver dead-time design should consider MOSFET parameter variation ( $R_G$ ,  $C_{ISS}$ ,  $V_{GS(TH)}$ ) and the dead-time should be adaptive to the MOSFETs. The adaptive dead-time scheme measures the actual voltage on the gate and only when the voltage on the gate is below a proper value (1V, since this is a good value for 90% of the MOSFET), the transition is allowed to turn on the other gate. Adaptive dead-time control has been used in a general MOSFET driver

circuitry that can drive discrete MOSFETs. Adaptive dead time is the improvement of the long fixed dead-time (fixed delay block). As a result, actual dead-time is usually pretty long (12ns is the best from industrial leading suppliers). Dead-time impacts the system efficiency as discussed in (2.12). To reduce the dead-time and  $Q_{RR}$  loss, LS Schottky barrier diode ( $V_{SD} = 0.56V$ , Infineon BSC014NE2LSI) should be incorporated in the design. By calculation, adding extra 5 ns dead-times will result in 0.2% of efficiency penalty.

Integrated power stage containing MOSFETs and driver has been increasingly used in recent years especially for high density design such as blade server. In order to boost the power conversion efficiency, the fixed driver dead-time with simpler logics can be used in a power stage since parasitic MOSFET parameters inside power stage package is predictable and in a relatively small variation range. However, the fixed driver dead-time may create a shoot-through scenario in a multiphase VR when the shedded phases are in tri-state for a long period, then recovered to operation mode. Both MOSFETS are kept in the OFF state when the driver receives a PWM tri-state signal.

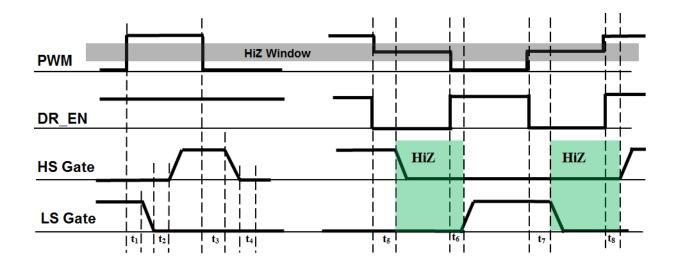

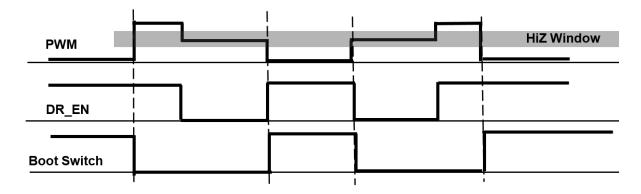

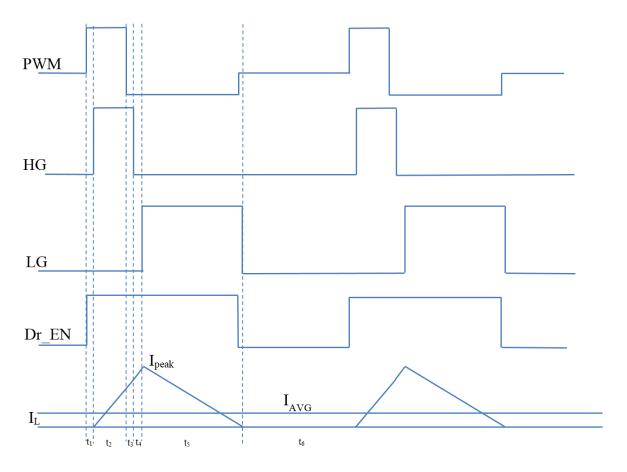

PWM and DR\_EN are both control input signals for driver IC which are generated by the state machine of PWM controller. Figure 2. 12 shows the timing diagram of driver interface with HiZ management. HiZ here refers to the high-impedance stage by keeping all MOSFETs in off state. HiZ window is defined as voltage range of the PWM between 1.2 V and 2.2 V for a 3.3 V application. t<sub>1</sub> and t<sub>3</sub> represent propagation delay of LS Gate and HS Gate, respectively. t<sub>2</sub> and t<sub>4</sub> represent dead times from LS falling and HS falling, respectively. t<sub>5</sub> and t<sub>8</sub> both represent hold-off times. t<sub>6</sub> and t<sub>7</sub> represent propagation delay of DR EN rising and falling.

Figure 2. 12. Timing diagram of driver interface: (a) DR\_EN is asserted; (b) DR\_EN is toggling during operation.

Figure 2. 13 shows timing diagram of the boot switch which is embedded inside of driver. The boot switch is ON when the LS is ON to charge the bootstrap capacitor. The boot switch is OFF when the HS is ON. During PWM HiZ, the switch must remain OFF since the negative current can discharge the boot cap if the switch is ON.

Figure 2. 13. Timing diagram of driver interface: PWM vs. Boot switch.

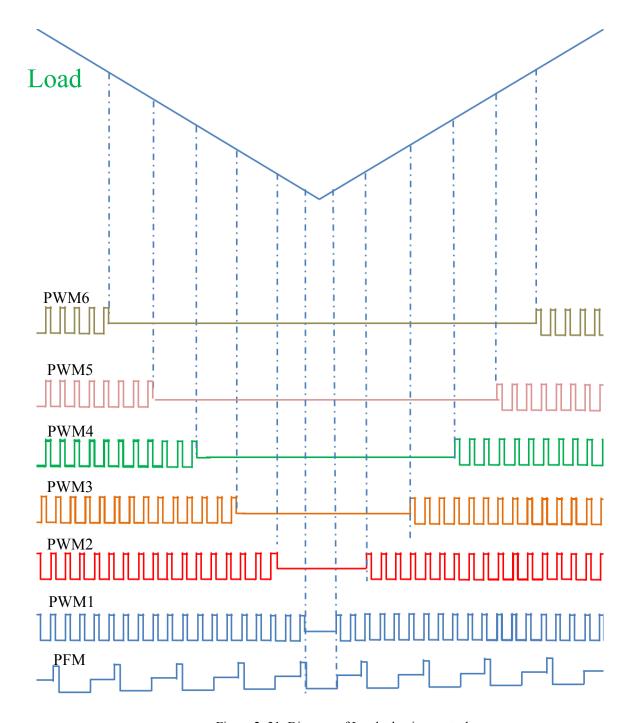

To obtain the optimum static efficiency for the whole load range, not only the lower FOM of power MOSFETs should be employed, the driver capability and the parameters associated with the power loss should be carefully studied and optimally defined. Finally, phase shedding control needs to be implemented to improve the efficiency in mid-light load, and the control thresholds are the intersection points of adjacent phases in efficiency plot.

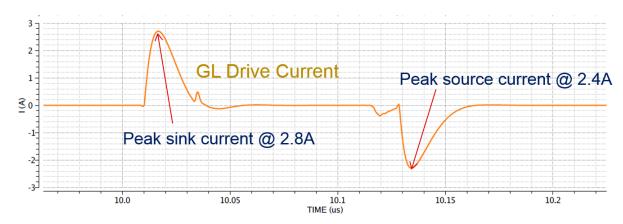

Table 2. 1 DIVER DEFINTION

| Upper driver source/sink current   | 2A / 2A            |

|------------------------------------|--------------------|

| Upper driver source/sink impedance | 0.8 Ohm / 0.6 Ohm  |

| Lower driver source/sink current   | 2A / 4A            |

| Lower driver source/sink impedance | 0.8 Ohm / 0.35 Ohm |

| $t_{deadtime(f)}$                  | 8 ns               |

| $t_{deadtime(r)}$                  | 15 ns              |

It's very important to correctly define and strengthen the driving capability of the power MOSFETs driver to minimize the HS switching loss during commutation (the overlapped area). TABLE I shows the definition of driving capability and dead times. The low sink impedance is extremely important to avoid Cdv/dt induced turn on phenomenon (shoot-through) [32] in the LS MOSFET during the fast turn on of HS MOSFET.

Figure 2. 14. LS turning ON/OFF.

Figure 2. 14 shows color coded procedures of LS MOSFET turning ON/OFF. The speed of turning ON and OFF is limited by the parasitic RLC as illustrated in the loop. The red arrows in Figure 2. 15 represents the peak source and sink current, respectively. Sink current needs to be bigger to avoid the shoot-through. There is also a need of minimum OFF time latch in the driver design to ensure the energy on the gate are fully discharged when turn OFF.

Figure 2. 15. Simulation result of LS turning ON/OFF.

Figure 2. 16. An example of resonant gate-drive circuit.

Figure 2. 16 [33] shows a resonant gate driver structure. It is an interesting idea that the energy on the gate can be recovered by the resonance [33] - [35]. However, it is not applicable for the hard switching design. The loss analysis from the previous section reveals that the gate drive loss is only the smallest portion in a typical design. Moreover, a resonant gate driver puts timing constraints on the switching transitions (MOSFETs are not driven hard) and the switching goes from inductively limited to MOSFET limited. That means that the dynamic losses will increase substantially. The only way to resolve this is to have an entirely resonant buck topology. With the larger phase currents, this offsets the benefits by additional conduction loss.

# 2.4 Light Load Operation

Reducing power conversion loss during light load is one of the major focus in computing industry [36] [37] The power saving features should be implemented in VR. In this dissertation,

we treat the terms, diode emulation (DE), discontinuous conduction mode (DCM), pulse skipping, and pulse frequency modulation (PFM) the same.

The voltage gain during PFM can be found:

$$M = \frac{2}{1 + \sqrt{1 + \frac{8I_{OUT}L}{T_{ON}^2 f_{SW}}}}$$

(2. 20)

where  $M = \frac{V_o}{V_{in}}$ , T<sub>ON</sub> is the ON time of the control MOSFET. L is the per phase inductance. I<sub>OUT</sub> is the load current.

Figure 2. 17. Transfer ratio M vs. duty cycle D.

Assume  $T_{ON}$  is constant during PFM, the  $f_{SW}$  is linearly proportional to the load current to achieve the same regulation of the output voltage. Therefore, the light load efficiency can be improved since the switching frequency can be decreased based on the load condition.

From Figure 2. 12, we can easily find

$$\tau = I_{OUT} L f_{SW} \tag{2.21}$$

$\tau$  is the normalized inductor time constant.

When CPU is in idle state, it is normally the condition of load current less than half of the inductor current ripple. The VR should be operating in PFM to reduce power loss [36] [37] However, once the VR receives the dynamic VID transition command, the VR should be able to immediately transition from PFM to CCM operation. It is noted that the VR is not able to sink current in PFM, which means downward transition cannot be accomplished in this mode.

Figure 2. 18. Operational waveforms of PFM operation.

In PFM, as shown in Figure 2. 18, PWM transitions from HiZ to high. Phase node moves from output voltage level to  $V_{BUS}$ . To achieve fast HiZ operation as depicted in Figure 2. 12(b), EN toggle should be utilized in PFM operation. When the inductor current reaches zero, the LS is turning off. The output voltage then decays as a function of load. Power MOSFETs remain HiZ until the output voltage drop below the regulation target to trigger a PWM on pulse. If the turn off LS operation is through PWM entering tri-state (slow HiZ operation), the hold-off time would create a delay and then negative inductor current.

Figure 2. 19. Power loss distribution of a synchronous buck in PFM.

Other than the reduced loss caused by reduced switching frequency, there are several other loss items eliminated in PFM as well. There is no turn ON loss in HS due to ZCS. LS body diode reverse recovery loss is gone since there is no current freewheeling during HiZ time period.

Similarly, there is no HS rising dead-time loss if accurate zero current detection scheme can be implemented. The power loss in PFM is summarized in Figure 2. 19.

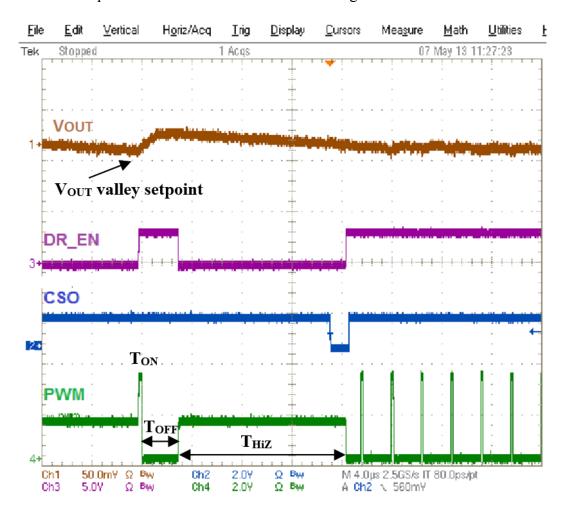

Figure 2. 20. PFM to CCM transition (load: 1 A).

Figure 2. 20 shows the mode transition from PFM to CCM initiated by power stage change. PWM ON time pulse is triggered by the  $V_{OUT}$  below the setpoint. The  $T_{ON}$  pulse is calculated by incorporating the converter parameters and  $V_{OUT}$  ripple requirement.  $T_{OFF}$  pulse is estimated by zero current crossing.  $T_{HiZ}$  is depending upon the load condition. The bigger

voltage ripple in PFM is expected due to the excessive charge of inductor ripple current (minus load) built upon the output capacitor compare to CCM operation.

## 2.5 Switching Waveforms

Switching waveforms, LS V<sub>DS</sub>, LS V<sub>GS</sub>, HS V<sub>DS</sub> and HS V<sub>GS</sub>, are critical parts of evaluating the robustness of the VR design. The waveforms should be within the defined range so that the MOSFETs are not stressed and thus the reliability is not a concern. Since the measurements can be only taken at the pins of the package, not the silicon die, it is needed to study the delta between the measured waveforms at the pin and at the die. Having a good understanding of the above waveforms are essential to optimize the overall VR design.

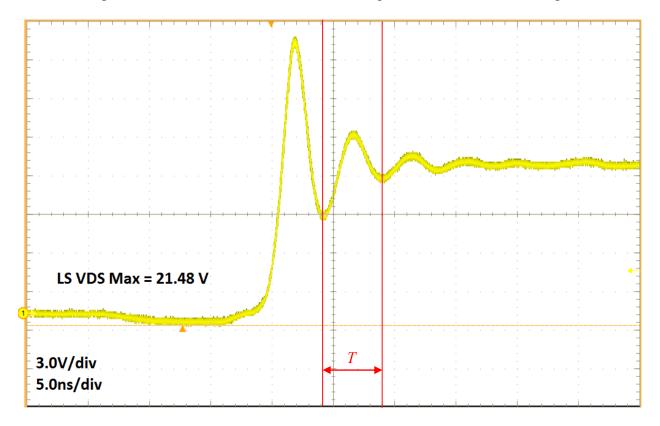

Figure 2. 21. LS  $V_{DS}$  rising waveform due to diode reverse recovery.

$$L_{para} = \frac{T^2}{(2\pi)^2 C_{OSS}} \tag{2.22}$$

Since the  $C_{OSS}$  can be looked up from the curve in the datasheet, therefore,  $L_{para}$  can be calculated by using (2.22).

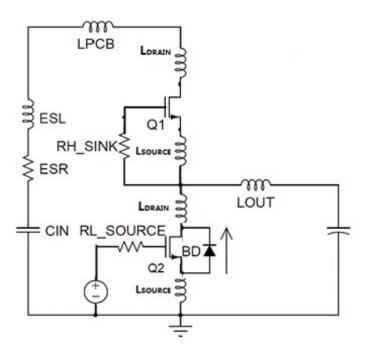

Figure 2. 22. Discrete solution of the converter considering circuitry parasitics in the buck mode.

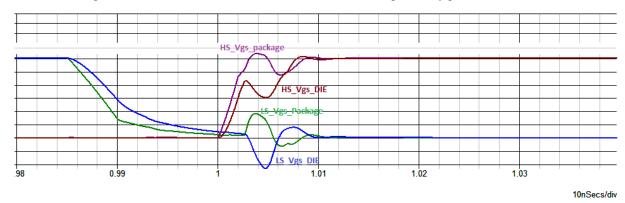

Figure 2. 23. Simetrix simulation of Gate waveforms.

Figure 2. 23 shows the simetrix simulation of gate drive waveforms comparison. There is a quite big delta between the actual waveform on the silicon die and the waveform on the package. There is a shoot-through concern of LS bump back, as depicts in green curve, however, the measurement result is misleading since it includes the parasitics and the real waveform on the silicon die is very low, as depicts in blue curve, the peak of which is lower than the  $V_{GS(th)}$  of LS MOSFET.

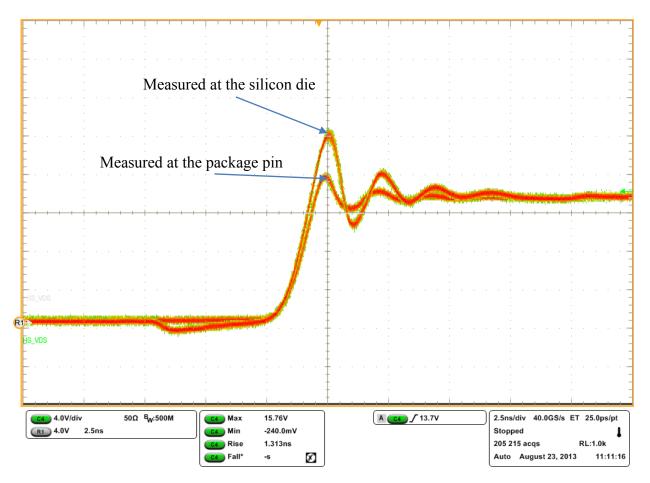

Figure 2. 24. HS  $V_{DS}$  waveforms comparison.

Figure 2. 24 shows the HS  $V_{DS}$  waveform measured at the power pin (source) on the package and at the silicon die as the arrows indicate. As depicted clearly in the fast acquisition

scope shot, the true  $V_{DS}$  is around 4V more than the result usually taken at the package. The voltage delta is caused by the combination effect of fast di/dt and source clip inductance.

## 2.6 Efficiency Optimization

It is critical to optimize the static efficiency of power stage first since it is one of the key performance metrics of the VR design. Load adaptive control (LAC) is proposed and experimentally verified. The multiphase VR operation mode and phase number is the function of the load current. FET drive voltage should also be adaptively adjusted to achieve the optimal efficiency. Switch frequency,  $f_{SW}$ , should be optimally chosen with nonlinear control loop enabled so that the relatively low switching frequency would not impact the load transient behavior.

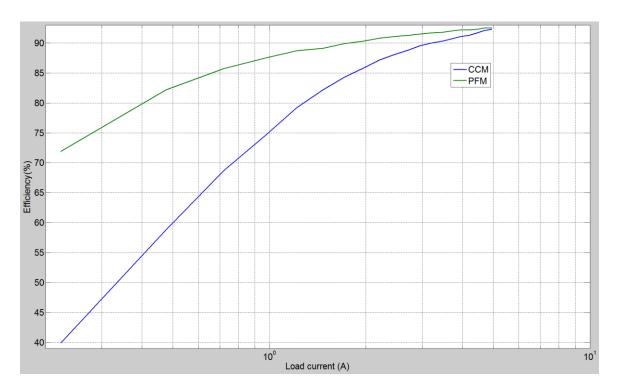

Figure 2. 25. Light load CCM vs. PFM.

Figure 2. 25 shows the efficiency comparison at light load. PFM operation shows a big advantage over CCM operation as expected and two curves are eventually converged at the load which is around half of the inductor current ripple.

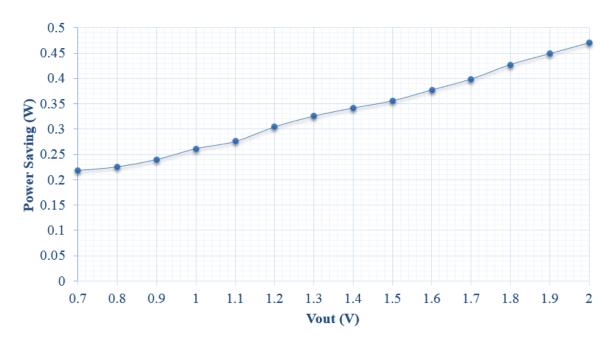

Figure 2. 26. Power loss reduction (PFM minus CCM) vs. VID.

Figure 2. 26 shows the power saving plot with increasing  $V_{OUT}$  with 10mA of load current. As the  $V_{OUT}$  increases, it becomes more important to enable the VR working in the PFM when the load current is small.

Converter parameters are in TABLE I, except for the disabled LL.  $V_{OUT}$  is regulating at 1.05 V and measured at the output inductor. A GPIB based automated efficiency program, which communicates to the data acquisition unit (Agilent 3497A) and electric load (Sorensen).is written to record,  $V_{IN}$ ,  $I_{IN}$ ,  $V_{OUT}$ ,  $I_{OUT}$ ,  $V_{FET\ DR}$ ,  $I_{FET\ DR}$  and plot the efficiency curve.

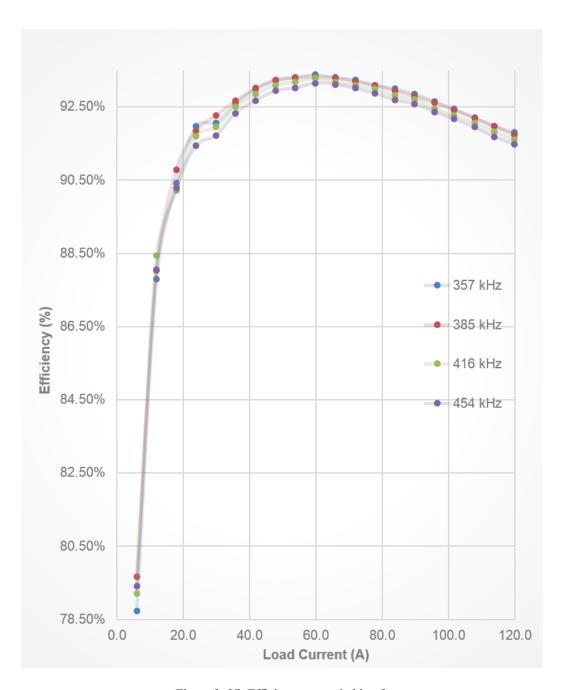

Figure 2. 27. Efficiency vs. switching frequency.

Switching frequency,  $f_{SW}$ , is the key parameter that needs to be optimized for achieving optimum efficiency. Figure 2. 27 shows the efficiency comparison between different  $f_{SW}$  cases.

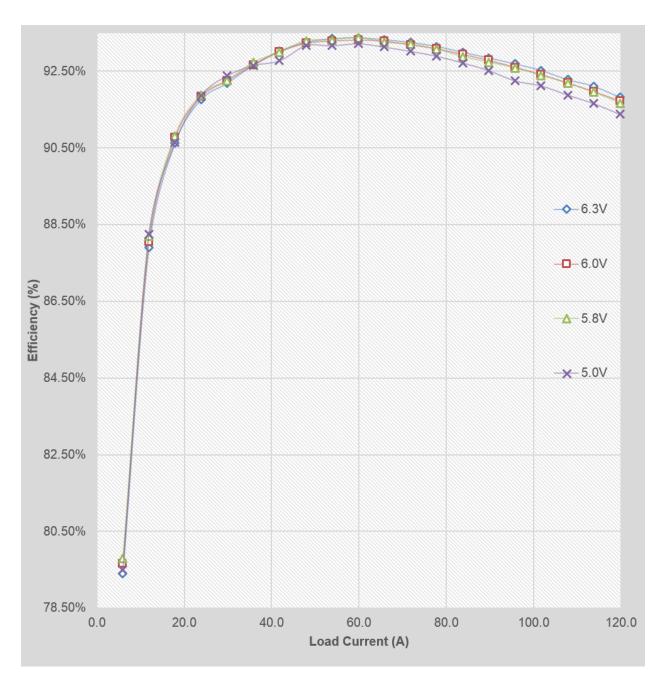

Figure 2. 28. Efficiency vs. FET drive voltage.

The driver voltage of power MOSFETs is also an important parameter to be optimized. In the total power loss formula, it affects the Rdson of (2.6) and (2.14).

Figure 2. 29. Measured efficiency of multiphase buck converter with operating different number of phases.

Figure 2. 29 shows the measured efficiency plot of multiphase buck converter with statically configured operation modes and different number of phases. There are in total seven cases in this plot: one phase PFM and one to six phase CCM. The cross points between adjacent phases operation can be programmed into the non-volatile memory (NVM) for this specific power stage for auto phasing shedding purpose to flatten the efficiency curve over the entire load range.

Figure 2. 30. Power efficiency optimization flow chart.

Table 2. 2 THE CONVERTER PARAMETERS

| $ m V_{BUS}$              | 12 V                                              |

|---------------------------|---------------------------------------------------|

| $ m V_{ m O}$             | 0.7 V~1.2 V                                       |

| $ m V_{FET\_DRV}$         | 6.0 V                                             |

| $f_{SW}$                  | 385 <i>k</i> Hz                                   |

| Loadline slope            | $0.8~m\Omega$                                     |

| Output inductor per phase | L = 230 nH                                        |

| Output capacitor          | $6\times470~\mu F$ Panasonic SP-Caps EEFSX0D471XE |

|                           | $44\times22~\mu F$ MLCC                           |

Figure 2. 31. Diagram of Load adaptive control.

Figure 2. 31 shows the diagram of load adaptive control based on previous optimization results.

# CHAPTER THREE: LOW FREQUENCY TRANSIENT AND SYSTEM DYNAMIC

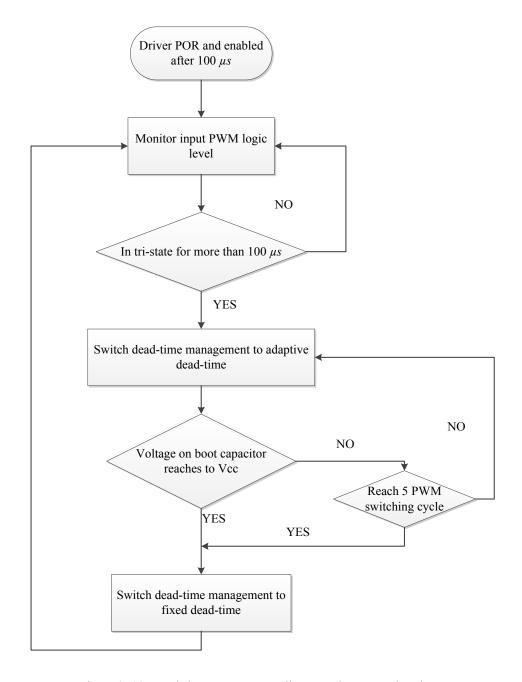

In this chapter, load transient enhancement schemes are introduced for low frequency transient operation. Adaptive body braking control is proposed to actively suppress the load release. There is a consideration for dynamically adding and dropping phases so that the Vout excursion can be minimized. Load adaptive control has provided the benefit in power saving perspective, however, it also creates a corner case scenario that shoot-through can be induced. Hence, we propose a new dead-time management scheme incorporating both fixed and adaptive dead-times so that the system reliability is secured and the power conversion efficiency during normal operation is improved.

## 3.1 DCR Sense Network Impact

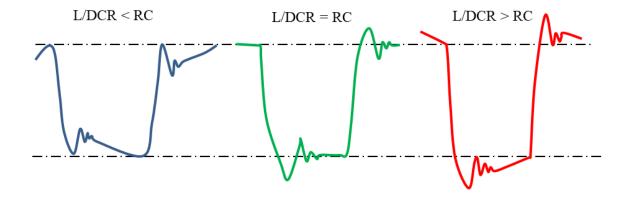

Accurate load current monitoring is an important feature and requirement in multiphase converter design. The RC network across the definition points of the inductor can be implemented to monitor the total phase current. The first design tuning in transient operation to make the DCR sense match.

$$\frac{L}{DCR} = RC \tag{3.1}$$

Figure 3. 1. DCR sense network RC time constant.

In a pure voltage mode control with correct compensation as an optimization starting point, Figure 3. 1 illustrates the Vout impacted by the DCR sense network and the Vout excursions are color coded as blue, green and red. Green curve represents the ideal RC time constant without nonlinear control enabled. If RC time constant is too large, as blue curve indicates, Vout is sluggish due to the delay in AVP loop and the overshoot can hurt the reliability of CPU; if RC time constant is too small, as depicted in red curve, there will be a Vout sag during load insertion and the excessive undershoot can create a system hang in the computing systems.

## 3.2 Nonlinear Control Scheme

In this section, control schemes are proposed and implemented to improve the system dynamics during load transient operation.

Output voltage deviations or excursions that exceed the pre-defined window thresholds are treated as load transient event [41] and a fast correction signal must be applied accordingly. Without losing the benefit (high DC gain) of the voltage mode control during static operation,

the fast nonlinear loop includes a programmable multi-threshold window comparator, pulse generation circuitry and interfacing circuitry to the normal PWM. When the sensed voltage is out of the programmable window, the ATR asynchronously signals the modified PWM patterns for compensating the output voltage. There are basically two types of asynchronous responses, i.e. Active Load Release Response (ALRR) and Active Load Engage Response (ALER). The nonlinear response essentially extends effective regulation bandwidth while maintain constant output impedance over frequency. The red rectangles represent the time slot in each phase that ALRR event can initiate. The orange and blue rectangles represent ALER event can be triggered and they are threshold 1 and threshold 2, respectively. The internal counter module in each phase is synchronous with switching frequency and points where the nonlinear events should be added. For example in load engage event, the asynchronous pulses in each phase boost the switching frequency to MHz range in the transient event, which effectively pumping the inductor current energy to the output capacitance bank. The extra voltage generated by the nonlinear loop:

$$V_{EX} = \frac{\sum_{K=1}^{N} \int iL_K(t+\theta_K)dt}{c_{OUT}}$$

(3.2)

where  $iL_K(t)$  represent the inductor ripple generated by the asynchronous pulse in phase K.  $\theta_K$  represents the phase angle difference between phase one. N presents the number of the active phases. For simplicity  $C_{OUT}$  represent the total capacitance of bulk and ceramic caps.

Figure 3. 2. The ATR timing architecture of the multiphase controller.

AVP scheme is to maintain constant output impedance so that less output capacitors can be populated and the output power of VR at full load can be reduced [1] -[5]. The nominal loadline equation is mathematically expressed in (3.3) given system impedance (R<sub>LL</sub>):

$$V_{Target} = VID - I_{LOAD} \cdot R_{LL} \tag{3.3}$$

### 3.2.1 Load Engage Enhancement

Nonlinear control scheme is a very critical technology and should be adopted in the slow transient application (below 50 kHz). In VR application, nonlinear control schemes during load engage transient event represent pulling-in PWM pulses or asserting PWM pulses faster than the response from the linear loop. It reduces the voltage excursion and saves output capacitors.

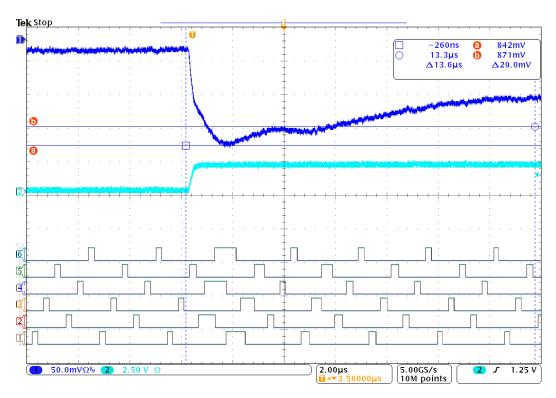

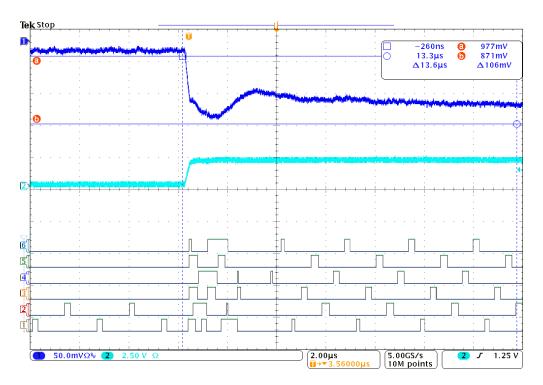

Figure 3. 3 shows load engage response. The load current step is 131 A and the associated slew rate is  $524A/\mu s$ . The 6 digital channels represent 6 PWMs and the lighter blue is the load current and darker blue is the voltage output.

Figure 3. 3. Load engage response with pure voltage mode control.

This is purely the voltage mode response and the 80 kHz control bandwidth can never respond fast enough (fire the phases sooner rather than waiting the internal clock cycle) to compensate the unwanted extra 60 mV undershoot. The ESR and ESL of the output caps are causing the first sharp dip. Because the inductor current slew rate is far less than the slew rate of output load current, due to the physics of the charge balance, the undershoot when load engage can never be removed, but the undershoot can be improved if nonlinear control scheme can be used.

Figure 3. 4. Load engage response w/ auto-phasing.

Figure 3. 4 depicts the load engage response of the multiphase buck converter with ALER enabled. The same step and slew rate are adopted which are 131A and  $524A/\mu s$ , respectively. The 6 digital channels represent 6 PWMs and the cyan blue represents the load current while darker blue represents the voltage output. Before the load is applied, it's running with 2 phase.

### 3.2.2 Load Release Enhancement

Existing methods for dealing with the overshoot voltage include increasing the output capacitance of the VR to suppress the overshoot voltage, or "body braking" by using the body diode of the power MOSFET in the VR to dissipate the excess current. Both options are problematic, however, as large capacitors increase the cost and size of the VR and "body braking"

generates additional power loss and excess heat. Therefore, we propose a method to pulse the LS gate ON and OFF to achieve the compromised result.

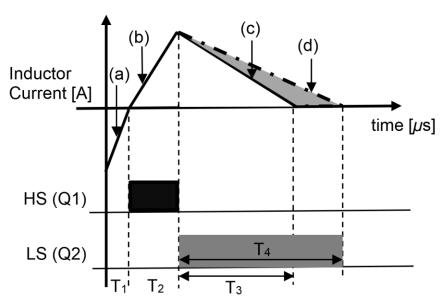

The equation set in (3.4) represents all operation scenarios or inductor current slopes in the converter. Equation (a) represents the charging slope when converter is operating is the boost (sink) mode with body diode of HS conducting. Equation (b) represents the charging slope when converter is working is the buck mode. Equation (c) represents the discharging (freewheeling) slope when LS is in asynchronous operation and body diode conducts (body braking). Equation (d) represents the discharging slope when LS is turned on.

$$iL_{Slew} = \begin{cases} \frac{V_{BUS} - V_{OUT}(t) + V_{SD}}{L} & (a) \\ \frac{V_{BUS} - V_{OUT}(t)}{L} & (b) \\ -\frac{V_{OUT}(t) + V_{SD}}{L} & (c) \\ -\frac{V_{OUT}(t)}{L} & (d) \end{cases}$$

(3.4)

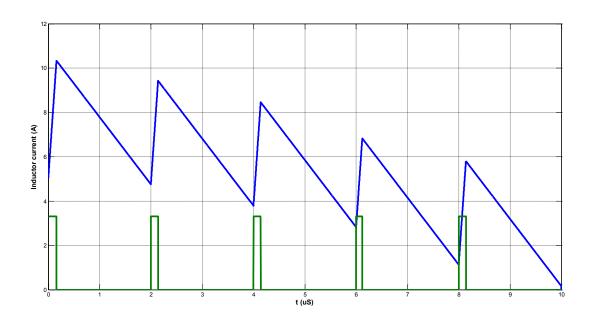

Figure 3. 5. Inductor current profile and gate-drive signals for the corresponding operations.

Figure 3. 5 depicts the all possible inductor current slopes or buck/boost mode from equation (1) and corresponding gate-drive signals of synchronous and asynchronous operations. Interval T<sub>1</sub> and interval T<sub>2</sub> represents HS body diode conducting and HS channel conducting, respectively. Interval T<sub>3</sub> and interval T<sub>4</sub> represent asynchronous and synchronous rectifier control, respectively.

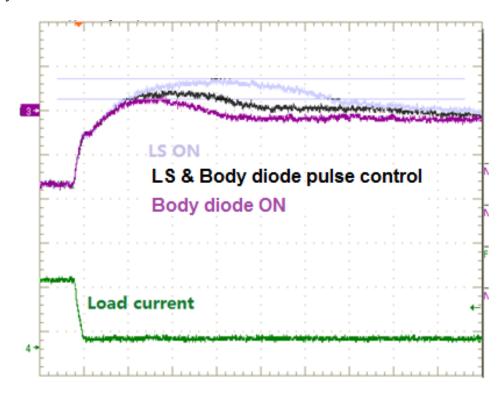

Figure 3. 6. Load release response comparison.

As depicted in Figure 3. 6, the scope shot shows comparison effects of suppressing the load release, which are the LS MOSFET ON, LS MOSFET OFF, and LS MOSFET Pulse control. The colors of the waveforms are light blue, black and magenta, respectively. Overshoot = 58 mV (Body diode ON). Overshoot = 68 mV (LS & Body diode ON).

# Inductor current profile with during load release $iL_{slew} = \frac{Vout(t) + V_D}{L}$

Figure 3. 7. Inductor current slew rate difference during load release

Figure 3. 7 shows the resultant inductor current profiles during load release.

By using the pulse control of the LS during load release, the temperature is 7 degrees lower than turning off the LS to freewheel the load current. Figure 3. 8 shows the inductor current slopes difference when body diode ON, pulsing the LS and LS ON, respectively.

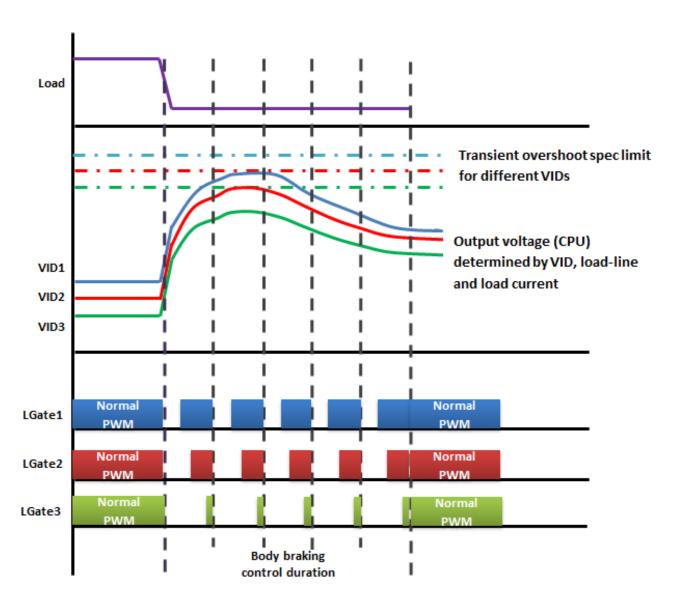

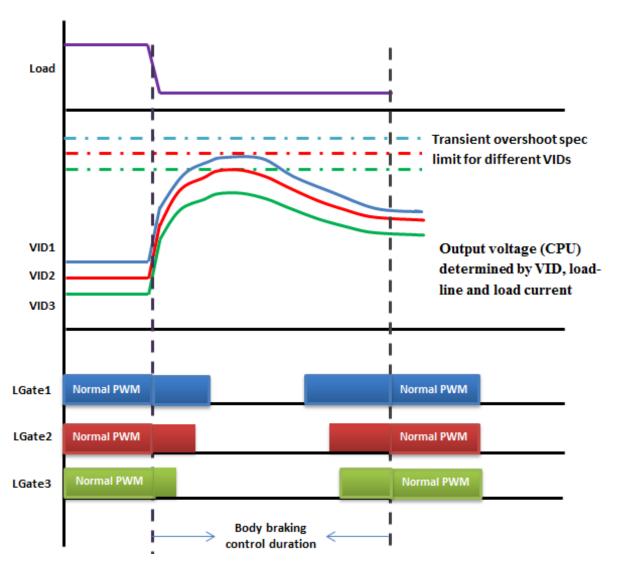

When a transient load such as a CPU operates in a large voltage range, the worst case overshoot usually occurs at the lowest VID. Conventional body braking methods include turning off the LS FET for either a whole cycle or a period of time targeting the lowest VID only. Unfortunately, this braking method is typically too aggressive for higher VID levels. As a result, power will be unnecessarily dissipated in body diode, which may also cause a thermal issue.

Figure 3. 8. Adaptive body-braking control (pulsing control).

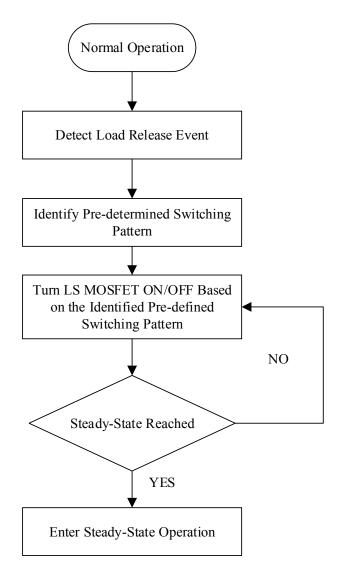

Figure 3. 9. Flow chart of adaptive body-braking control (pulse control).

The flow chart of adaptive body-braking control in pulse control mode is shown in Figure

3. 9.

Figure 3. 10. Adaptive body-braking control (Body diode ON).

In Figure 3. 10, in body braking control duration, the pulse pattern is pulsing the LS gate, but the duration of the OFF time is still adaptively changing according to the current VID, which still based on the worst case overshoot in the lowest VID. Figure 3. 11 shows the related flow chart.

Figure 3. 11. Flow chart of adaptive body-braking control (Body diode ON).

# 3.3 Drop Phase Optimization

As analyzed in chapter 2, the phase number of the multiphase converter is the function of load current and should follow adaptively with the load change from the static operation perspective. However, there is extra care needs to be taken when shutting off the phase, which is ramping down the inductor current before the drop operation.

Figure 3. 12. Overshoot during phase shedding.

Figure 3. 12 shows the phase shedding during load release. The yellow channel is  $V_{OUT}$ . The blue channel is load current. PWM2 and PWM3 are green and magenta channels respectively. The load current step is 30A and slew rate is  $10A/\mu s$ . There are three overshoots in this scope shots circled in red. The first one is normal and is caused by the load step. The rest overshoots are the result of dropping phase 2 and 3. When the two phases are turning off, the corresponding phase still carries some current in the inductor. The turning OFF slew rate is

increased when the phase is off state because the current is freewheeling through the LS body diode.

Once the phase dropping command is initiated, the state-machine of the current balance module starts to modify the modulated ON time generated by PID and ramping down the inductor current in the phase that is going to be turned off, meanwhile also increase the current in other phase to take over the total load current. The overshoot caused by phase dropping can be eliminated.

Figure 3. 13. Current balance block diagram.