Electronic Theses and Dissertations, 2004-2019

2017

# Design and Simulation of Device Failure Models for Electrostatic Discharge (ESD) Event

Meng Miao University of Central Florida

Part of the Electrical and Computer Engineering Commons

Find similar works at: https://stars.library.ucf.edu/etd

University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS Citation**

Miao, Meng, "Design and Simulation of Device Failure Models for Electrostatic Discharge (ESD) Event" (2017). *Electronic Theses and Dissertations, 2004-2019*. 5388. https://stars.library.ucf.edu/etd/5388

# DESIGN AND SIMULATION OF DEVICE FAILURE MODELS FOR ELECTROSTATIC DISCHARGE (ESD) EVENT

by

# MENG MIAO B.S. Zhejiang University, 2009 M.S. Zhejiang University, 2012

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida

Orlando, Florida

Spring Term 2017

Major Professor: Kalpathy B. Sundaram

© 2017 Meng Miao

#### **ABSTRACT**

In this dissertation, the research mainly focused on discussing ESD failure event simulation and ESD modeling, seeking solutions for ESD issues by simulating ESD event and predict possible ESD reliability problem in IC design. The research involves failure phenomenon caused by ESD/ EOS stress, mainly on the thermal failure due to inevitable self-heating during an ESD stress. Standard Complementary Metal-Oxide-Semiconductor (CMOS) process and high voltage Doublediffusion Metal-Oxide-Semiconductor (DMOS) process are used for design of experiment. A multi-function test platform High Power Pulse Instrument (HPPI) is used for ESD event evaluation and device characterization. SPICE-like software ADICE is for back-end simulation.

Electrostatic Discharges (ESD) is one of the hazard that may affect IC circuit function and cause serious damage to the chip. The importance of ESD protection has been raised since the CMOS technology advanced and the dimension of transistors scales down. On the other hand, the variety of applications of chips is also making corresponding ESD protection difficult to meet different design requirement. Aside from typical requirements such as core circuit operation voltage, maximum accepted leakage current, breakdown conditions for the process and overall device sizes, special applications like radio frequency and power electronic requires ESD to be low parasitic capacitance and can sustain high level energy. In that case, a proper ESD protection design demands not only a robust ESD protection scheme, but co-design with the inner circuit. For that purpose, it is necessary to simulate the results of ESD impact on IC and find out possible weak point of the circuit and improve it. The first step of the simulation is to have corresponding

models available. Unfortunately, ESD models, especially there are lack of circuit-level ESD models that provide quick and accurate prediction of ESD event.

In this dissertation paper, ESD models, especially ESD failure models for device thermal failure are introduced, with modeling methodology accordingly. First, an introduction for ESD event and typical ESD protection schemes are introduced. Its purpose is to give basic concept of ESD. For ESD failure models, two typical types can be categorized depends on the physical mechanisms that cause the ESD damage. One is the gate oxide breakdown, which is electric field related. The other is the thermal-related failure, which stems from the self-heating effect associated with the large current passing through the ESD protection structure. The first one has become increasingly challenging with the aggressive scaling of the gate dielectric in advanced processes and ESD protection for that need to be carefully designed. The second one, thermal failure widely exists in semiconductor devices as long as there is ESD current flow through the device and accumulate heat at junctions. Considering the universality of thermal failure in ESD device, it is imperative to establish a model to simulate ESD caused thermal failure.

Several works related to ESD model can be done. One crucial part for a failure model is to define the failure criterion. As common solution for ESD simulation and failure prediction. The maximum current level or breakdown voltage is used to judge whether a device fails under ESD stresses. Such failure criteria based on measurable voltage or current values are straightforward and can be easy to implemented in simulation tools. However, the shortcoming of these failure criteria is each failure criterion is specifically designed for certain ESD stress condition. For example, the failure voltage level for Human Body Model and Charged Device Model are quite different, and it is hard to judge a device's ESD capability under standard test

conditions based on its transmission line pulse test result. So it is necessary to look deeper into the physical mechanism of device failure under ESD and find a more universal failure criterion for various stress conditions.

As one of the major failure mechanisms, thermal failure evaluated by temperature is a more universal failure criterion for device failure under ESD stress. Whatever the stress model is, the device will fail if a critical temperature is reached at certain part inside the device and cause structural damage. Then finding out that critical temperature is crucial to define the failure point for device thermal failure. One chapter of this dissertation will focus on discussing this issue and propose a simple method to give close estimation of the real failure temperature for typical ESD devices.

Combined these related works, a comprehensive diode model for ESD simulation is proposed. Using existing ESD models, diode I-V characteristic from low current turn-on to high current saturation can be simulated. By using temperature as the failure criterion, the last point of diode operation, or the second breakdown point, can be accurately predicted.

Additional investigation of ESD capability of devices for special case like vertical GaN diode is discussed in Chapter IV. Due to the distinct material property of GaN, the vertical GaN diode exhibits unique and interesting quasi-static I-V curves quite different from conventional silicon semiconductor devices. And that I-V curve varies with different pulse width, indicating strong conductivity modulation of diode neutral region that will delay the complete turn-on of the vertical GaN diode.

To my parents Zhenqing Miao and Hongli Wang

#### **ACKNOWLEDGMENTS**

It is a great experience for me as a graduate student in UCF. It won't be possible for me to accomplish this and finish this work without the support from people around me. It is their selfless help and encouragement that keeps me push forward.

First, I'd like to thank Prof. Juin J. Liou for his guidance during my Ph.D study. His expert advice always help me a lot when I encounter obstacle in my research and keep me working on the right track. Prof. Liou is my academic advisor as well as my friend. We can discuss freely on research problems, which is a great help on my projects. Prof. Liou put his trust on me and let me participate in the funded research projects with Analog Devices Inc. (ADI), in which, I learned a lot and accomplished several publication that enables me to graduate as a Ph.D student.

I want to thank Dr. Kalpathy B. Sundaram who helped me a lot during my Ph.D program. He is helpful and give support to students. Also, his advice is always inspiring with his expertise in device physics and fabrication.

I want to show my great gratitude to Dr. Yuanzhong Zhou, who mentors me on my research projects. It was a great experience to work with him on research projects funded by ADI. His ideas and advice are invaluable and always help me to find the right solution in my research. He is helpful and resourceful, revising papers for me with great patience.

I want to also thank Dr. Jean-Jacques Hajjar and members in ESD group, ADI. Dr. Hajjar is an experienced manager, and his team always solve problems and guarantee the reliability of

the product. I also would like to thank Javier Salcedo for his support on my research. And Srivatsan Parthasarathy offering valuable suggestions and discussions to this research work.

I would like to thank my dissertation committee members, Dr. Jiann S. Yuan, Dr. Xun Gong, Dr. Javier Salcedo and Dr. Yier Jin, for their invaluable suggestions and comments on improving this research work. I want to thank Analog Device Inc. for giving the opportunity to me and let me participate in the joint research project between ADI and UCF, from which I gained real world industrial experience.

I acknowledge and thank many valuable UCF professors who shared with me their wisdom and invaluable time, and the talented students from our research group. Special thanks to Dr. Wen Liu (GF), David Elis, Dr. Qiang Cui (Qorvo), Shurong Dong (ZJU), Zhixin Wang (UCF), Yunfeng Xi (UCF), Wei Liang (UCF), Aihua Dong (UCF), Linfeng He (UCF), Hang Li (UCF), for the valuable time we spent together in UCF.

I would like to express my gratitude to the financial, academic and technical support from University of Central Florida and its staff. And all the instructors at UCF, Zhejiang University, Zhoushan Secondary School, who guided my learning and provide me exemplary academic and moral teachings.

Last but not least, I am deeply indebted to my parents, Zhenqing Miao and Hongli Wang, Their love and support is my greatest motivation to accomplish this research work.

# **TABLE OF CONTENTS**

| LIST OF FIGURE | ES                          | xii  |

|----------------|-----------------------------|------|

| LIST OF TABLES | S                           | xvi  |

| LIST OF ACRON  | YMS                         | xvii |

| CHAPTER 1 IN   | TRODUCTION                  | 1    |

| 1.1 ES         | SD Event and ESD Failure    | 1    |

| 1.1.1          | HBM Model                   | 3    |

| 1.1.2          | CDM Model                   | 4    |

| 1.1.3          | MM Model                    | 5    |

| 1.1.4          | IEC and HMM model           | 5    |

| 1.1.5          | ESD Testing Method          | 6    |

| 1.1.6          | Multi-pin Test              | 8    |

| 1.1.7          | Latch-up Test               | 11   |

| 1.2 Ba         | asic ESD protection devices | 12   |

| 1.2.1          | Introduction                | 12   |

| 1.2.2          | Diode                       | 14   |

| 1.2.3          | MOSFET                      | 19   |

| 1.2.4          | SCR                         | 21   |

| 1.3 Di         | ssertation outline          | 24   |

| CHAPTER 2  | JUNCTION THERMAL FAILURE MODEL FOR DEVICES SUBJECT T                | O'  |

|------------|---------------------------------------------------------------------|-----|

| ELECTROST  | ATIC DISCHARGE STRESSES                                             | 25  |

| 2.1        | Introduction                                                        | 25  |

| 2.2        | Modeling and Characterization                                       | 28  |

| 2.3        | Model Parameter Extraction.                                         | 30  |

| 2.4        | Model Verification                                                  | 37  |

| 2.5        | Conclusion                                                          | 44  |

| CHAPTER 3  | INVESTIGATION OF FAILURE TEMPERATURES OF SEMICONDUC                 | TOR |

| DEVICES UN | DER ELECTROSTATIC DISCHARGE STRESSES                                | 45  |

| 3.1        | Introduction                                                        | 45  |

| 3.2        | Experimental Methodology                                            | 46  |

| 3.3        | Measurement Results and Analysis                                    | 51  |

| 3.4        | Conclusion.                                                         | 60  |

| CHAPTER 4  | A COMPREHENSIVE DIODE MODEL FOR SIMULATION UNDER                    |     |

| ELECTROST  | ATIC DISCHARGE STRESSES                                             | 61  |

| 4.1        | Introduction                                                        | 61  |

| 4.2        | Modeling of Overshoot at Diode Forward Turn-on                      | 64  |

| 4.3        | Failure Prediction and Temperature Monitoring.                      | 66  |

| 4.4        | Modeling of On-resistance Variation of Diode at High Current Region | 66  |

| 4.5        | Parameter Extraction and Simulation Results                         | 70  |

| 4.6         | Conclusion                                                                | . 76 |

|-------------|---------------------------------------------------------------------------|------|

| CHAPTER 5   | INVESTIGATION ON FORWARD TRANSIENT CHARACTERISTICS OF                     | Ē    |

| GaN P-N DIO | DES ON BULK GaN SUBSTRATE                                                 | . 77 |

| 5.1         | Introduction                                                              | . 77 |

| 5.2         | Experiments and Analysis                                                  | . 78 |

| 5.3         | Turn-on Characteristics of Vertical GaN diode under Different Temperature | . 84 |

| 5.4         | Conclusion                                                                | . 86 |

| CHAPTER 6   | SUMMARY AND OUTLOOK                                                       | . 87 |

| LIST OF REF | ERENCES                                                                   | 90   |

# **LIST OF FIGURES**

| Figure 1-1 A simplified equivalent circuit for HBM ESD model.                             | 3      |

|-------------------------------------------------------------------------------------------|--------|

| Figure 1-2 An equivalent circuit for CDM ESD stress model.                                | 4      |

| Figure 1-3 An equivalent circuit for MM ESD stress model.                                 | 5      |

| Figure 1-4 A TLP equivalent diagram.                                                      | 7      |

| Figure 1-5 A diagram shows how a TLP I-V curve is plotted.                                | 8      |

| Figure 1-6 Diagrams show 8 test pattern for ESD test for multi-pin chips.                 | 10     |

| Figure 1-7 Latch-up test and the input test signal.                                       | 12     |

| Figure 1-8 ESD design window.                                                             | 14     |

| Figure 1-9 Cross-sections of typical diode structures for ESD application in CMOS process | s 16   |

| Figure 1-10 Cross-sections of P+/Nwell diodes with parasitic BJT paths embedded           | 17     |

| Figure 1-11 TCAD simulation of the total current density charts in a diode string.        | 19     |

| Figure 1-12 Layout and cross-section of a multi-finger GGNMOS configuration.              | 20     |

| Figure 1-13 Cross-section and the equivalent circuit of the SCR structure.                | 22     |

| Figure 2-1 Input power-to-failure as a function of electrical pulse width, for a constant | nt ΔT, |

| across a reverse-biased junction.                                                         | 27     |

| Figure 2-2 Simulated lattice temperature contours with three different thermal regions    | 29     |

| Figure 2-3 Time dependent temperature variation along the depth of junction structure u   | nder a |

| transient pulse stress.                                                                   | 30     |

| Figure 2-4 Equivalent circuit for the compact junction thermal failure model.             | 32     |

| Figure 2-5 Failure power vs. time waveform as the product of Vt2 and It2 waveforms        | 33     |

| Figure 2-6 ADS software tool setup for parameters extraction                              | 35     |

| Figure 2-7 Simulated temperature vs, time curves in the three thermal regions of the square-        |

|-----------------------------------------------------------------------------------------------------|

| shape diode subject to TLP pulses having different pulse widths and failure power                   |

| Figure 2-8 Comparison of simulated and measured failure power/energy vs. failure time data for      |

| a rectangle shape diode under different pulse widths.                                               |

| Figure 2-9 Simulation results using a TLP pulse that caused device failure (the solid lines for the |

| measurement and the dash lines for the simulation)                                                  |

| Figure 2-10 HBM power waveforms from measurement and simulation and the corresponding               |

| simulated temperature at the stress levels close to device failure                                  |

| Figure 2-11 Simulation of secondary snapback in a GGNMOS with combination of the therma             |

| failure model and ESD capable MOS device model                                                      |

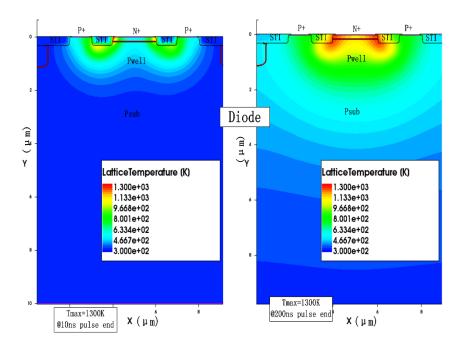

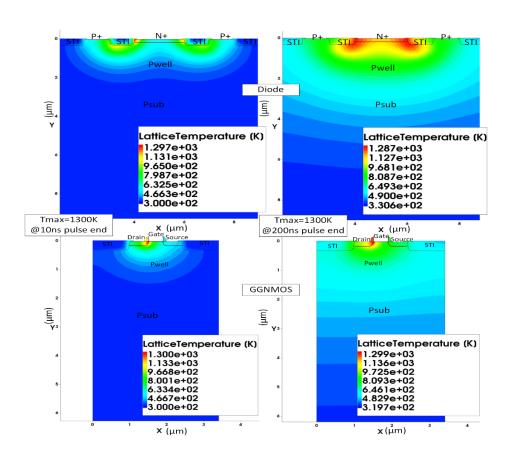

| Figure 3-1 Simulated temperature distributions in a diode under a short (10 ns) (left) and a long   |

| (200 ns) (right) electrical pulses.                                                                 |

| Figure 3-2 One-stage thermal equivalent circuit. The voltage on capacitor C is equivalent to the    |

| average temperature in the region under stress                                                      |

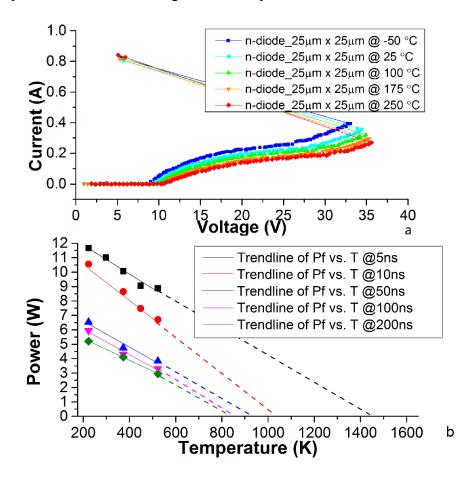

| Figure 3-3 (a) I-V curves of a reverse-biased n-diode stressed under 5ns pulses at different        |

| ambient temperatures, and (b) failure power vs. temperature lines and extracted failure             |

| temperatures (intercept points on the x-axis) for the same diode                                    |

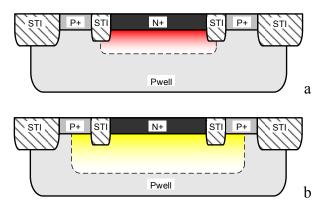

| Figure 3-4 Difference of average temperature under short (a) and long (b) pulse stress              |

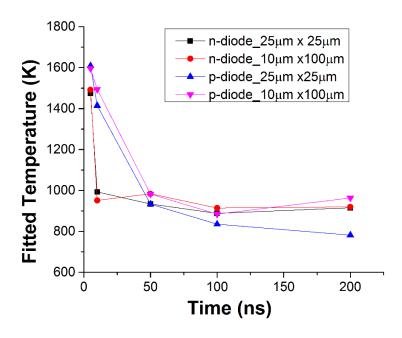

| Figure 3-5 Effective failure temperature vs. pulse duration characteristics obtained for four       |

| different diodes: single-finger n-diode and p-diode with a square shape (25μm x 25μm) and a         |

| rectangular shape (10μm x 100μm). 52                                                                |

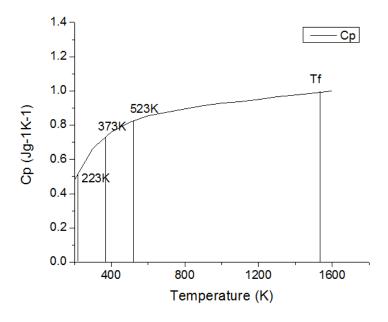

| Figure 3-6 Temperature dependence of thermal capacity                                               |

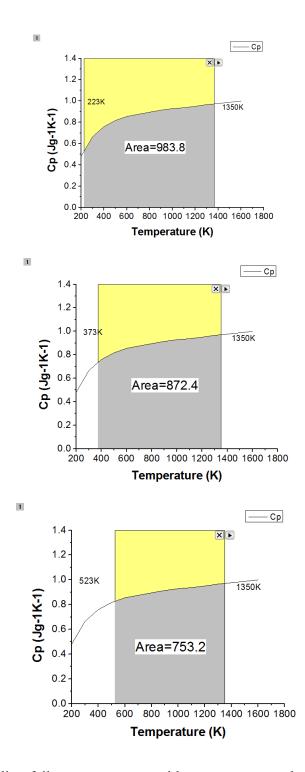

| Figure 3-7 Finding failure temperature with a non-constant thermal capacitance                   |

|--------------------------------------------------------------------------------------------------|

| Figure 3-8 Simulated temperature distributions in a diode (top) and in a GGNMOS (bottom)         |

| under the short (10ns) (left) and long (200ns) (right) pulses. 58                                |

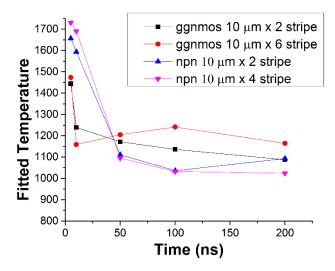

| Figure 3-9 Effective failure temperature vs. pulse duration characteristics obtained for four    |

| devices: two GGNMOS and two NPN BJTs. 59                                                         |

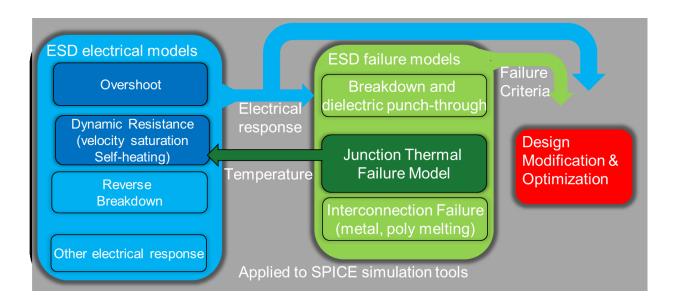

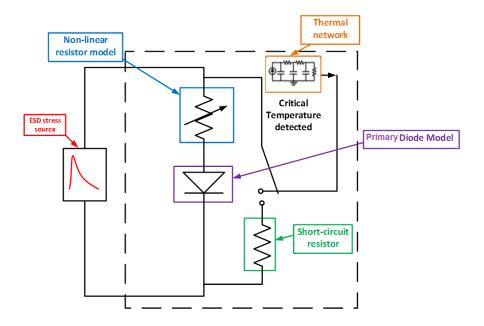

| Figure 4-1 A diagram of a comprehensive ESD model consists of several compact models 62          |

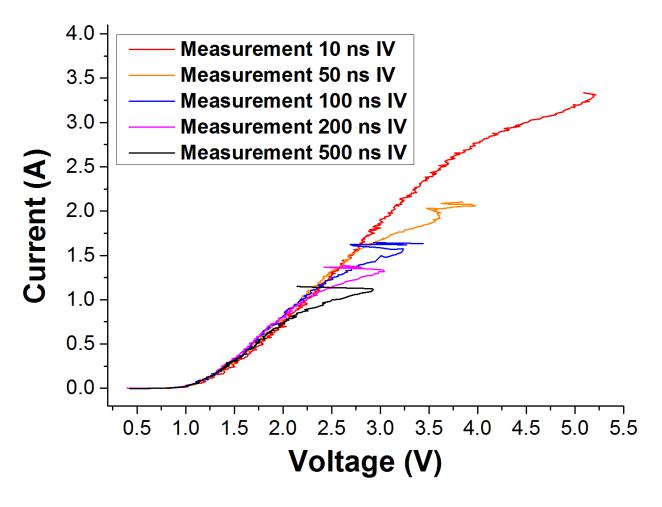

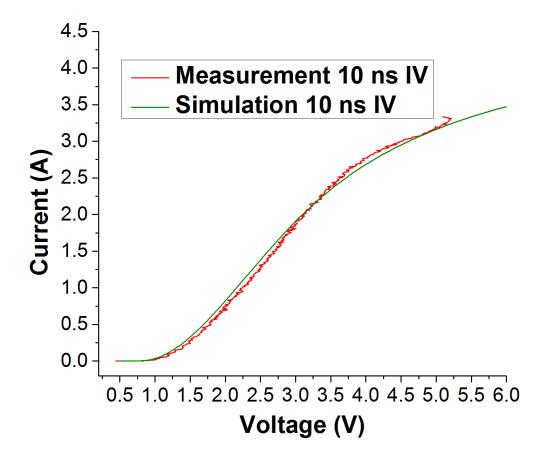

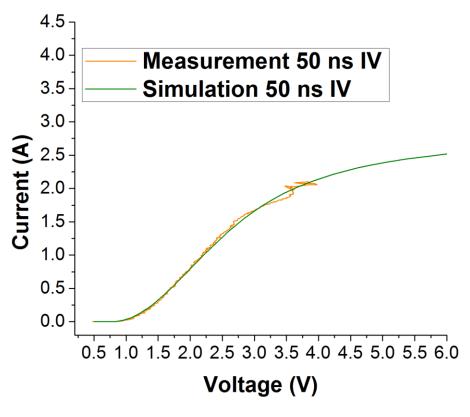

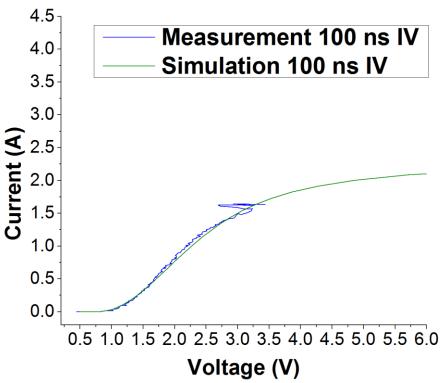

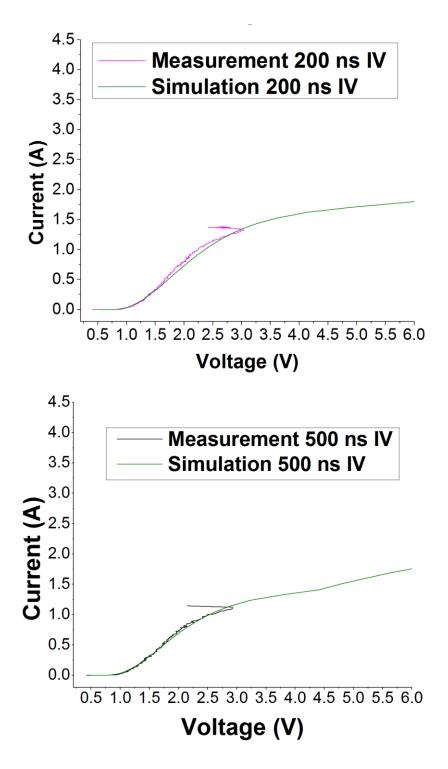

| Figure 4-2 Measured TLP I-V curves under different pulse widths, ranging from 10ns to 500ns.     |

|                                                                                                  |

| Figure 4-3 Full schematic of comprehensive diode model                                           |

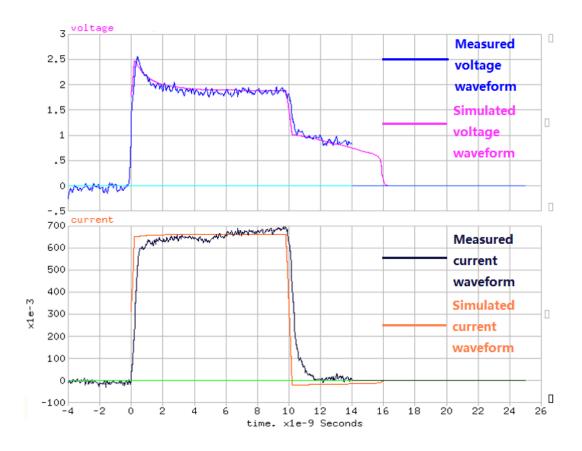

| Figure 4-4 Measured and simulated transient waveforms under a 10ns TLP pulse with voltage        |

| overshoot peak                                                                                   |

| Figure 4-5 TLP IV simulations fit with measured IV under different pulse width, ranging from     |

| 10ns to 500ns                                                                                    |

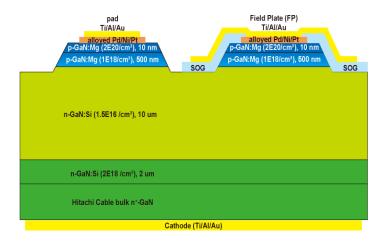

| Figure 5-1 Cross-section of the GaN on GaN substrate P-N diodes without field plate (left) and   |

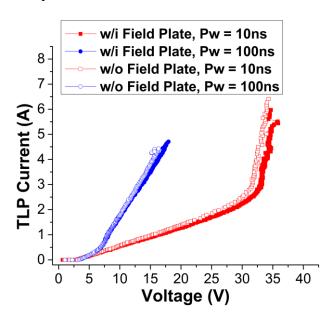

| with field plate (right)                                                                         |

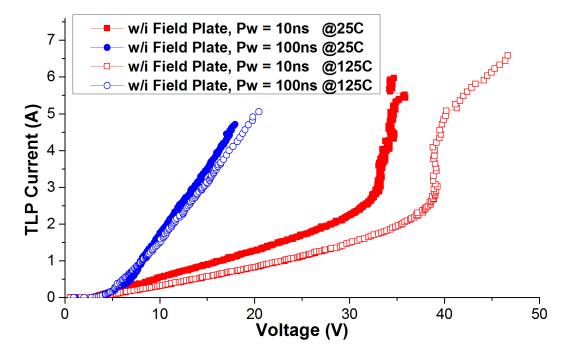

| Figure 5-2 Quasi-static I-V curves of vertical GaN diodes, w/i field plate (solid) and w/o field |

| plate (hollow), under 100ns (blue) and 10ns (red) pulse width                                    |

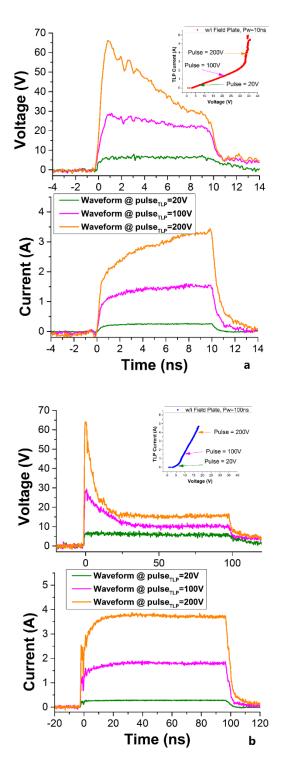

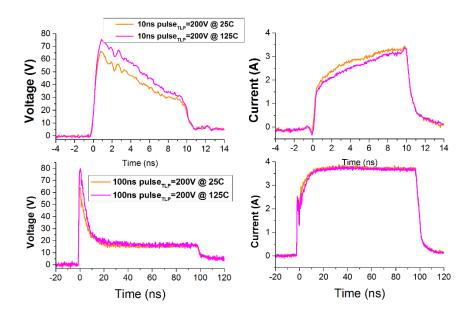

| Figure 5-3 Transient voltage (upper figures) and current (lower figures) waveforms for 10ns (a)  |

| and 100ns (b) stress pulses                                                                      |

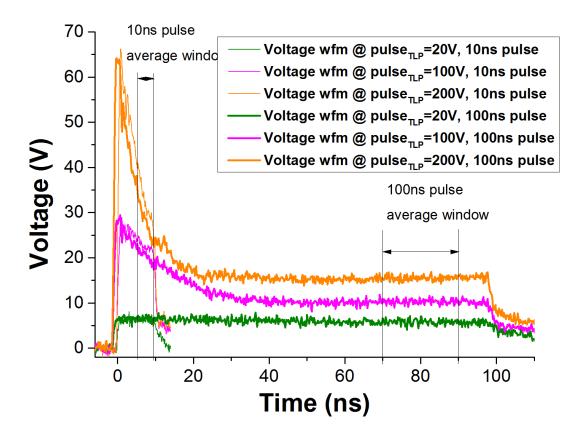

| Figure 5-4 Voltage waveform Comparison of 10ns vfTLP test and 100ns TLP test. Waveforms          |

| captured at pulse voltage at 20V, 100V and 200V.                                                 |

| Figure 5-5 TLP I-V curves for a vertical GaN diode with field plate under room temp | erature |

|-------------------------------------------------------------------------------------|---------|

| (25°C) and high temperature (25 °C), for short pulse (10ns) and long pulse (100ns)  | 84      |

| Figure 5-6 Comparison of transient voltage/current waveforms at Vpulse=200V, a      | mbien   |

| temperature at 25°C and 125°C, respectively.                                        | 85      |

# LIST OF TABLES

| Table 2-1 MEASURED FAILURE POWER FOR MODEL FITTING. | 34 |

|-----------------------------------------------------|----|

|                                                     |    |

| Table 2-2 Extracted R and C values                  | 35 |

#### LIST OF ACRONYMS

BJT Bipolar Junction Transistor

CDM Charged Device Model

CMOS Complementary Metal-Oxide-Semiconductor

DMOS Doublediffusion Metal-Oxide-Semiconductor

DUT Device Under Test

EOS Electrical Overstress

ESD Electrostatic Discharge

GGNMOS Gate-Grounded N-type MOSFET

GaN Gallium Nitride

HBM Human Body Model

HMM Human Metal Model

HPPI High Power Pulse Instrument

IC Integrated Circuits

IEC International Electrotechnical Commission

MM Machine Model

MEMS Micro Electro Mechanical System

SCR Silicon Controlled Rectifier

SOG Spin on Glass

TCAD Technology Computer Aided Design

TDR Time Domain Reflection

TDT Time Domain Transmission

TDRT Time Domain Reflection and Transmission

TLP Transmission Line Pulsing

VFTLP Very Fast Transmission Line Pulsing

#### CHAPTER 1 INTRODUCTION

#### 1.1 ESD Event and ESD Failure

Since the first Integrated Circuit (IC) was invented in 1950s, the semiconductor IC has evolved dramatically in both dimension and scale. Following the "Moore's Law" for decades, the performance of IC has improved a lot with more transistors integrated on a single small chip [1]. On the other hand, with the shrinking dimension of transistors, problems in manufacture and reliability have emerged increasingly. To meet various requirement of applications (radio frequency [2], power electronics [3], MEMS [4], magnetic recording [5]), the fabrication and function of ICs has been greatly specified.

Long before the IC manufacture entered the era of sub-micrometer. Electrostatic Discharge (ESD) event is one of the major effect that influence the IC product reliability [6-8]. It is an inevitable event during the whole cycle of IC fabrication, packaging, transportation and application. Once there is electric charge generated and accumulated either by ordinary movement, like rubbing a doorknob or walking on a carpet, or transfer charge from one object to another, electrostatic discharge may occur, causing short-time but high voltage spark. Such discharge flowing through electric device may damage the vulnerable part of the IC, especially at the input/output port.

A whole protection design for ESD event is a systematic work, which involves both IC design and manufacture. Protection must include on-chip and off-chip design. Thus, it is a difficult work requires case-by-case solutions. It is reported that during the whole cycle of IC product, 37% failure is caused by ESD/EOS event [7]. The solution for ESD/EOS problem must be taken seriously.

Before IC manufacture entered sub-micrometer, ESD was not a big problem in IC design. The transistor was large with thick gate oxide that can sustain significant ESD stress without extra protection. IC was able to pass ESD test with only a few protection at the I/O port. The major attention is paid to other reliability issue, like circuit soft failure, threshold voltage shift and latch-up [9, 10]. While with advanced IC technology, semiconductor transistor has become smaller but it has to face the same level of ESD stress and it makes IC more vulnerable, hard failure (gate oxide breakdown, P-N junction secondary breakdown, metal interconnection melting) may occur.

On the other hand, different IC products are fabricated for different application. For example, the ESD protection design for radio frequency circuit require not only a robust ESD protection, but an inserted ESD unit with very low parasitic effect[11, 12]. Special fabrication process such as Micro-Electro-Mechanical Systems (MEMS) and carbon nano-tube may need extra consideration of ESD [13, 14]. Even ordinary IC may encounter the dilemma between ESD robustness and compact circuit area. Such special requirement for different circuit application means there is no universal ESD protection for every situation.

To better evaluate ESD stress under various situations, people have standardize ESD into several ESD models:

- (1) HBM (Human-Body-Model) [15];

- (2) CDM (Charged- Device-Model) [16];

- (3) IEC (International-Electrotechnical-Commission);

- (4) HMM (Human-Metal-Model) [17, 18];

- (5) MM (Machine-Model) [19];

These are the main ESD models that IC designer must concern. They cover major ESD event a chip may encounter and require corresponding ESD protection schemes. The following section will introduce these ESD models briefly.

#### 1.1.1 HBM Model

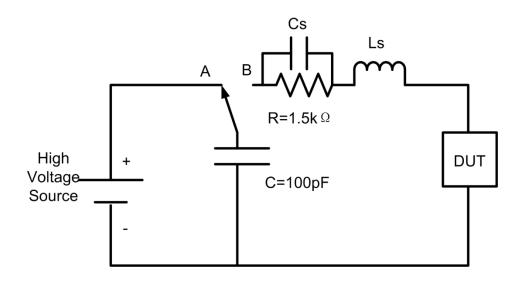

Figure 1-1 A simplified equivalent circuit for HBM ESD model.

HBM represents a charged human body contacts one pin of a grounded semiconductor device or an IC directly, transferring the charge into the device. Figure 1-1 shows its equivalent circuit. The C=100pF represents the equivalent capacitance of human body, the charge generated by rubbing or transferred from other objects is stored on this capacitance temporarily. Once the switch is closed with node B, namely the human body touches a grounded semiconductor device, electrostatic energy will discharge through a simple circuit and release on the device.

In the HBM equivalent circuit,  $R_{HBM} = 1.5k\Omega$  and  $L_{HBM} = 7500nH$  are used to replicate a charged human body. Those values may vary a bit according to different standards include MIL-STD-883E [20], ESDA/JEDEC JS-001-2014 [21].

#### 1.1.2 CDM Model

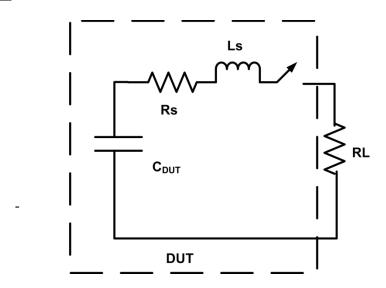

Figure 1-2 An equivalent circuit for CDM ESD stress model.

The charge device model (CDM) was aiming to model a package IC with charge already on it, and discharge the ESD energy through its pin when a pin contacts a grounded object or conductive surface. Such situation is highly possible during the manufacturing and assembly of ICs. Figure 1-2 gives the equivalent circuit of CDM. It should be noted that the parasitic resistance is smaller than the resistance in HBM, causing a much fast discharge event with higher overshoot peak at the very beginning of CDM event. This may be more deadly event for some applications, especially for the thin gate oxide of MOS transistors in more advanced process technology. Also due to the fast and short overshoot, damage may still occur even the circuit if

protected by ESD unit if the ESD unit doesn't respond fast enough. The commonly used standard for CDM are known as ESDA/JEDEC JS-002-2014 [22].

#### 1.1.3 MM Model

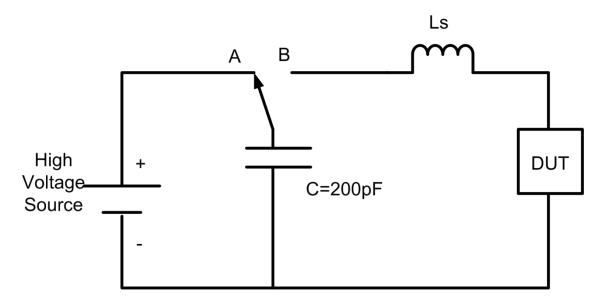

Similar to HBM, MM is to model charged machines (metal tools, mechanical arm) contacts with one pin of a grounded chip. But MM has some parasitic inductance and lower parasitic capacitance than HBM, which will cause ESD impact in reverse direction, leading to more severe damage to the chip. Figure 1-3 is the typical equivalent circuit for MM. The commonly used standard for CDM are known as STM5.2-2012 – Electronic [23].

Figure 1-3 An equivalent circuit for MM ESD stress model.

#### 1.1.4 <u>IEC and HMM model</u>

HBM, CDM and MM are ESD models for single component, they can be tested on wafer level or packaged chips. When the ICs are integrated with other components and assembled in a

system, the performance of component level ESD may degrade. The overall performance of a system must be evaluated with new ESD models. To ensure the system-level ESD robustness, IEC standard was developed for system level ESD testing [24-26]. An ESD gun, specialized tester, is usually used to produce such ESD stress. The HMM model is used to predict system level ESD robustness prior to assembly [27, 28]. It reproduce the situation that ESD discharge caused by a human touching a pin of a grounded component with a metal tool.

#### 1.1.5 ESD Testing Method

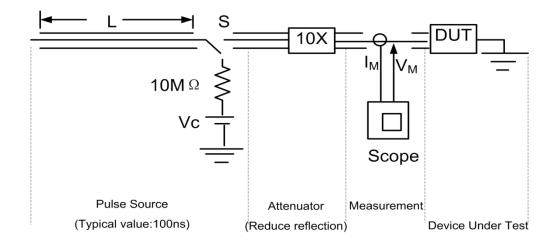

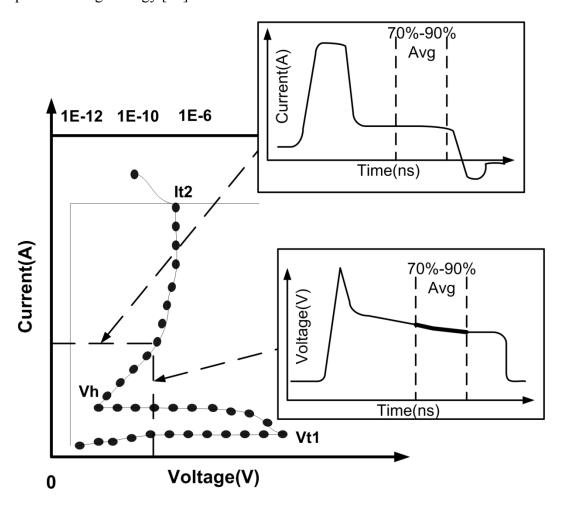

Most ESD models can only evaluated the ESD level of a device under test (DUT), but cannot characterize it. It requires a method to reveal how the DUT behave under ESD stresses. The transmission-line pulse (TLP) system has been used to characterize on-chip ESD protection structure in the integrated circuit industry [29, 30]. This technique has been introduced by T.J.Maloney and N.Khurana in 1985 [31]. A schematic of a TLP system is shown in Figure 1-4. It is composed of a pulse generator, the transmission line and the DUT, together they form a closed transmission line. The incident and reflection waveforms on the transmission line are captured and recorded. Unlike a DC measurement using a step in test waveform, TLP generates a sequence of discrete waveforms but with increasing magnitude. Each waveform and its results are recorded and a I-V characterization curve is plotted.

Figure 1-4 A TLP equivalent diagram.

Typical TLP system generated pulses with a rise time of 0.5 ns ~ 10ns, pulse width of 75 ns ~ 150 ns. There are several types of TLP system depending on how the pulse is generated and measured, such as Time Domain Reflection (TDR), Time Domain Transmission (TDT), Time Domain Reflection and Transmission (TDRT) and Current source (with 500 ohm load resistance). For the TDR, it can be categorized into TDR-O and TDR-S. Figure 1-5 gives one example of how a TLP I-V curve is plotted. As pulse is generated and flow through the transmission line, the incident and reflected voltage/current waveforms are captured by a high sampling rate oscilloscope. Using the stabilized portion (70% ~ 90%) of the voltage/current waveforms as one pair of voltage/current values, a sequence of voltage/current data points can be obtained with the increasing magnitude of the TLP pulses. Connecting those data dots, a TLP I-V curved can be drawn as represented in Figure 1-5. It must be noticed that even the other portion of the TLP waveforms contains valuable information. It can be seen that at the very beginning of the transient voltage waveform, there is a sharp peak, which is called overshoot [32]. The overshoot

with its peak value and the duration is the key criterion that reflects the response time of the ESD protection unit. With a smaller overshoot, the ESD device can turn-on much faster to handle fast ESD impact with large energy [33].

Figure 1-5 A diagram shows how a TLP I-V curve is plotted.

#### 1.1.6 Multi-pin Test

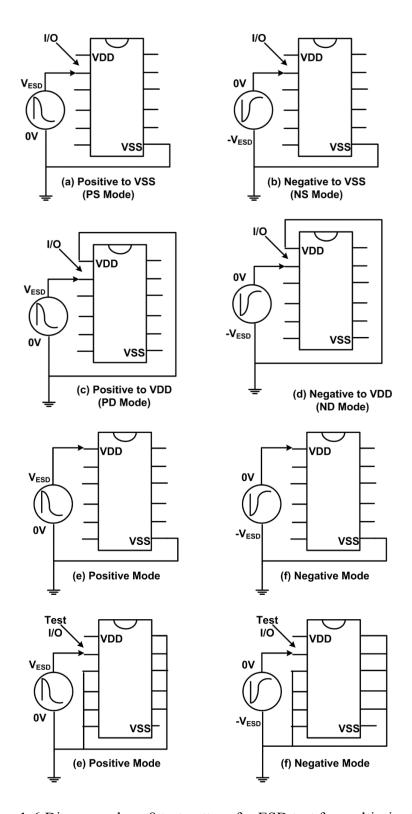

For packaged chip, it usually has multi-pin configuration, depending on the chip and package type. To evaluate the ESD robustness of the product comprehensively, it requires the

chip being tested under different ESD models, and pass certain level for each model. In general, an industrial IC product will require HBM  $\geq$  2KV, CDM  $\geq$  1KV, MM  $\geq$  200V. For applications that the I/O contacts outer interface frequently, like USB, HDMI and RFIC, higher ESD levels are mandatory. Besides ESD models, most IC product have to pass the latch-up test to ensure the chip functions normally under ESD/EOS situations. As aforementioned, the product must pass several IEC model tests to ensure the product at system level ESD and its Electro Magnetic Compatibility (EMC).

Since a chip usually has multi-pin configuration but conventional ESD test is a pin-to-pin test, a test pattern is needed when performed a full chip test. The below Figure 1-6 depicts eight test configurations for full chip test. It covers most situation that ESD current flow through the chip.

Figure 1-6 Diagrams show 8 test pattern for ESD test for multi-pin chips.

#### 1.1.7 <u>Latch-up Test</u>

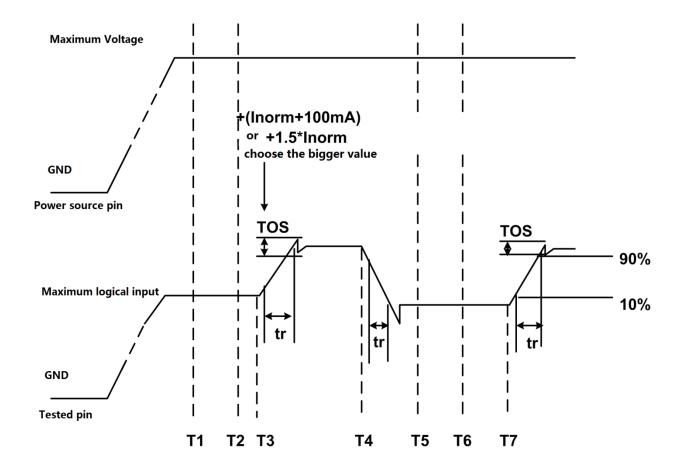

Although it's not an ESD damage, latch-up event is usually boned with ESD test. By draining voltage/current through the chip, it can check latch-up immunity of the chip and prevent possible hard/soft failure due to the defects of the design. Below Figure 1-7 is a standard procedure of latch-up test:

- 1) All inputs tie to high;

- 2) Outputs are floating;

- 3) At time T2, the DUT is tested at its normal operation condition (from VDD to VSS);

- 4) Adding drain voltage/current test signal during time T3 to T4 (current at I/O pins, voltage on VDD and VSS);

- 5) Measure the current between VDD and VSS at time T5, compare it with recorded current value at time T2;

- 6) If  $I_{norm} < 25 \text{mA}$ , then  $I_{T5} > I_{norm} + 10 \text{mA}$  is a latch-up. If  $I_{norm} > 25 \text{mA}$ , then  $I_{T5} > 1.5*I_{norm}$  is a latch-up.

Figure 1-7 Latch-up test and the input test signal.

## 1.2 <u>Basic ESD protection devices</u>

#### 1.2.1 <u>Introduction</u>

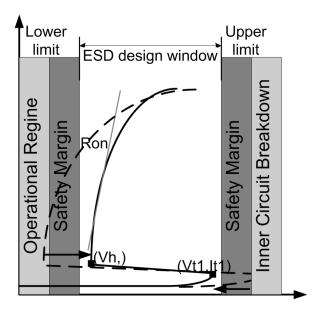

Before we discuss about different device used for ESD protection, it is necessary to introduce the basic concept of ESD design window and ESD protection schemes.

As aforementioned that ESD protection is a case-by-case design, for different protection target, proper ESD unit must be chosen carefully. There is a concept of ESD design window must be met for each design. Figure 1-8 shows a typical ESD design window and I-V characteristics of a basic ESD protection device. The ESD design window has two boundaries.

The lower limit is defined by the normal operation voltage of the circuit being protected. The holding voltage, or the lowest voltage that ESD unit can reach must higher than this lower limit, or the circuit may in risk of latup-up during ESD/EOS event. The upper limit of the ESD design window is defined by the hard failure voltage of the protected circuit, usually it is the gate oxide breakdown voltage of an input MOSFET or the drain-source breakdown voltage of the output drive transistor [34, 35]. The ESD unit cannot work beyond the upper limit, otherwise the inner circuit may be damaged by the ESD/EOS stress. A 10% safety margin is usually needed to make ESD protection designs more reliable. An ideal ESD protection unit has a fixed trigger voltage and very low on-resistance, however, which is contradicted with reality. A conventional ESD device will turn-on with a certain on-resistance and this on-resistance will gradually increase at high current region due to self-heating effect. Moreover, with more advanced IC process technology, the ESD design window is shrinking with upper and lower boundary closing in. Thus, it's getting difficult to design proper ESD protection scheme for advanced CMOS technology.

Figure 1-8 ESD design window.

There are several typical devices that can be used for ESD protection, all are evolved from conventional device but due to the purpose for ESD protection, modifications are made.

## 1.2.2 <u>Diode</u>

P-N junction diode is the simplest structure but a very effective ESD protection device. It has very low parasitic effect and easy to do metal interconnection [36, 37]. However, as most semiconductor devices designed for ESD protection, it comes with pros and cons.

1) Diode has very low turn-on voltage  $(0.6V \sim 0.8V)$  at forward direction, which could be either an advantage or disadvantage. For low voltage protection, we cannot find any other device that provides such low turn-on voltage. However, for operation voltage a bit higher, like over 2V, it requires three or four diodes in series, that series

- connection will probably introduce a parasitic effect called Darlington effect and increase the leakage of diodes in series.

- 2) Although the turn-on voltage of diode's reverse direction is pretty high, the current capability of reverse conduction is very low. To achieve acceptable ESD current capability by using a reverse-biased diode, that diode must be very large, which will occupy a significant layout area.

- 3) Nonetheless, the parasitic capacitance per unit area for diode is very low, which makes diode an ideal candidate for RF ESD protection. Moreover, due to the simple structure of diode, its SPICE model is more accurate than other devices with complicated structures, thus circuit design could simulate and predict circuit performance with diode ESD protection in-situ.

- 4) Fast turn-on speed is another merit comes with diode protection. Short term ESD event like CDM requires ESD protection unit to respond within 1ns. To meet such rigid requirement, diodes are usually used as a secondary protection for CDM event.

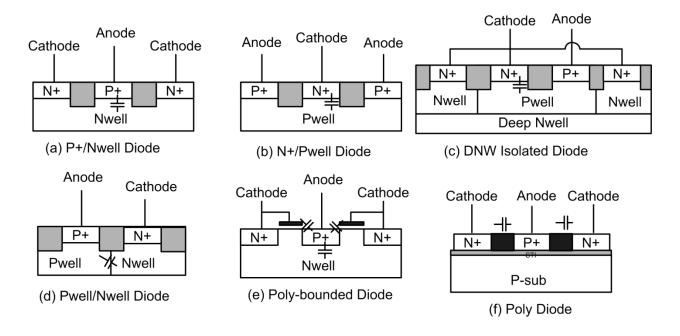

There are several variations of diodes, below Figure 1-9 gives some typical examples.

Figure 1-9 Cross-sections of typical diode structures for ESD application in CMOS process.

As we may expect, diodes with poly gate structure has fast turn-on speed but will introduce extra parasitic capacitance. To prevent this, metal interconnection and layout of these diodes is a delicate work.

As aforementioned, diodes in series may increase the leakage current due to the Darlington effect. It is a negative side-effect we must diminish when designing diode string protection scheme. As Figure 1-10 shows there is always a substrate to support the P-N junction diodes, thus for P+/Nwell diode, there is a parasitic P+/Nwell/Psub BJT as T1, T2 and T3 in the figure. The emitter of T2 is connected with the base of T1, The emitter of T3 is connected with base of T2. In that case, three BJTs form a cascade configuration and amplify the leakage current. As current operation equation of BJT states

Figure 1-10 Cross-sections of P+/Nwell diodes with parasitic BJT paths embedded.

$$I_E = (1 + \beta)I_B \tag{1.1}$$

and

$$I_D = I_S \cdot \exp\left(\frac{V_D}{V_T}\right) \tag{1.2}$$

we got

$$V_1 = V_T ln \frac{I_{E_1}}{I_S} = V_T ln \frac{(\beta+1)I_{E_2}}{I_S} = \cdots V_T ln \frac{(\beta+1)^{n-1}I_{E_n}}{I_S} = V_n + (n-1)V_T \ln(\beta+1)$$

(1.3)

suppose the gain of each diode is  $\beta$ , then the total voltage across the diode string is

$$V_{sum} = \sum_{i=1}^{n} V_n = nV_1 - \frac{n(n-1)}{2} V_T \ln(\beta + 1) = nV_T \left[ \ln \frac{I_{E1}}{I_S(\beta + 1)^{\frac{n-1}{2}}} \right]$$

(1.4)

finally, the leakage current caused by Darlington effect could be

$$I_{Leakage} = I_{E1} = I_S \cdot \exp\left(\frac{V_{sum}}{nV_T}\right) \cdot (1+\beta)^{\frac{n-1}{2}}$$

(1.5)

compared with the static current of an ideal diode string, which is

$$I_{Leakage} = I_s \cdot \exp\left(\frac{V_{sum}}{nV_T}\right) \tag{1.6}$$

the leakage is increased by a factor of  $(1+\beta)^{\frac{n-1}{2}}$ , and  $I_{Bn}=I_{E1}\cdot\frac{1}{(1+\beta)^n}$

As the above analysis, due to the Darlington effect, the static leakage is a large portion of the total current. Due to the Webster Effect [38], such high current injection will lower the resistance of the base region and reduce efficiency of the emitter. Thus the ESD current capability of the diode string is reduce equivalently.

This negative effect is not very obvious when diodes are place far away from each other, however, as a compact layout is required in advanced CMOS process, devices are putting closely to each other to save layout area. In that case, the gain of the paracitc BJT will increase significantly, causing the inevitable Darlington Effect. Technology Computer Aided Design (TCAD) simulation gives an example in detail (Figure 1-11). When current increases, the high current region in red color has moved from diode string to the substrate and continuously reduce current flowing through the diode string. Such phenomenon has been reported in [39].

Figure 1-11 TCAD simulation of the total current density charts in a diode string.

#### 1.2.3 <u>MOSFET</u>

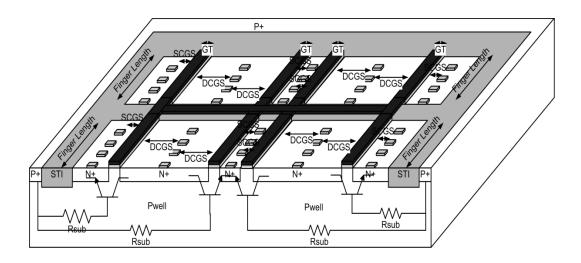

Compared with diodes and SCRs, grounded-gate NMOS (GGNMOS) is more like a compromise option. It has better ESD area efficiency but still lower than SCR. The snapback is not as deep as SCR's, but enough for GGNMOS provide proper current capability. Because of these merit of GGNMOS, it can easily meet corresponding ESD window and widely used in standard I/O cell.

Unlike a NMOS for circuit application using the channel region to conduct current, rather, GGNMOS works as a BJT using the body region to conduct large portion of the ESD current. When a GGNMOS triggers under ESD stress, the channel will conduct the early portion of the ESD current. The gate and channel structure ensure the GGNMOS will turn-on soon enough

before the ESD energy cause damage to the inner circuit. As current increases, current flows through the channel will assist the embedded BJT to turn-on. Although the single GGNMOS structure is simple, it is more concerned about GGNMOS in multi-finger configuration when used in real situations.

Figure 1-12 Layout and cross-section of a multi-finger GGNMOS configuration.

Figure 1-12 is an overview of a multi-finger GGNMOS. It can be seen that for multi-finger configuration, except the gate length, finger width and drain contact to gate space these single finger parameters, another major change introduced is the body tie. Since the P+ body tie is only around the multi-finger GGNMOS array, each finger has different distance to the body tie. This may cause non-uniformly conducting when triggering the multi-finger GGNMOS. To mitigate this, several technology is introduced. The most commonly used one is the silicide block and ballast resistor. The silicide block layer will prevent the generation of silicide at drain side,

adding a small resistance at drain side. Although this will slightly degrade the performance of each GGNMOS, the overall uniformly conducting is improved.

Another advantage of using GGNMOS as I/O ESD protection is saving area. Albeit the GGNMOS itself is not the ESD device with the most area efficiency, its value in I/O protection is intrinsic. As we know, for port with input and output function both, input MOSFET transistors are in parallel with output MOSFET transistors. In that case, those MOSFET can not only be drive transistors, but provide ESD protection capability in off-state.

#### 1.2.4 SCR

Another type of commonly used snapback ESD protection device is silicon controlled rectifier (SCR) [40, 41]. It is a commonly used power electronic device, but its high power, high current capability is very valuable for ESD protection.

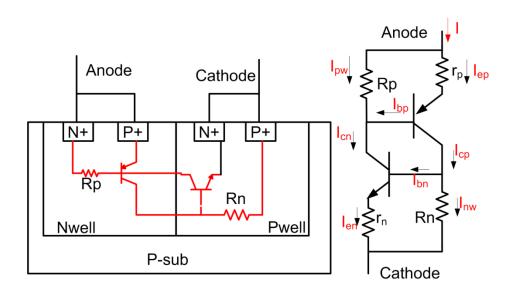

The cross-section of a standard SCR structure is shown in below Figure 1-13. By adding P+ and N+ in the adjacent Pwell and Nwell, a PNP BJT and a NPN BJT are interconnected. Figure 1-13 gives the equivalent circuit of SCR. The collector of PNP is connected with the base of NPN, and NPN is draining current from the base of PNP. Thus, a positive feedback is formed. Once ESD current flow through the well resistor of both BJTs and forms a voltage bias, BJTs are turned on and finally SCR start to conduct [42].

Figure 1-13 Cross-section and the equivalent circuit of the SCR structure.

The emitter current flowing through both BJTs occupies the majority of the ESD current, as  $I_{en}=I_{ep}\gg I_{pw}$ ,  $I_{nw}$ . For both PNP and NPN, we have

$$I_{cn} \cong I_{bp} \tag{1.7}$$

$$I_{cp} \cong I_{bn} \tag{1.8}$$

in that case we have

$$I_{bp} \cong I_{cn} = \beta_n I_{bn} \le \beta_p I_{cp} = \beta_n \beta_p I_{bn} \tag{1.9}$$

or, as SCR in snapback condition

$$\beta_n \beta_p \ge 1 \tag{1.10}$$

when including well current  $I_{pw}$  and  $I_{nw}$ , it will be

$$I = I_{ep} + I_{nw} \tag{1.11}$$

$$I = I_{en} + I_{pw} (1.12)$$

thus, the total current should be

$$I = I_{cp} + I_{cn} = \alpha_p I_{ep} + I_{cp0} + \alpha_n I_{en} + I_{cn0}$$

(1.13)

$$I = \alpha_p(I_{ep} + I_{nw}) = \alpha_p I_{nw} + I_{cp0} + \alpha_n(I_{en} + I_{pw}) = \alpha_n I_{pw} + I_{cn0}$$

(1.14)

where  $\alpha_p$ ,  $\alpha_n$  are the common base gain of PNP and NPN BJT,  $I_{cp0}$ ,  $I_{cn0}$  are saturation current of PNP and NPN in reverse direction. Finally, we can get

$$I = \frac{\beta_p(\beta_n + 1)I_{nw} + \beta_n(\beta_p + 1)I_{pw}}{\beta_p \beta_p - 1} = I_H$$

(1.15)

where  $I_H$  is the holding current when SCR enters snapback state.

for the holding voltage, the emitter resistors  $r_{ep}$  and  $r_{en}$  must be considered.

$$V_H = V_{pBE} + V_{nBE} + I \cdot r_{ep} \cdot V_{nBE} + I \cdot r_{en} + V_{potential}$$

(1.16)

As we can see, with increasing I, the voltage across  $I \cdot r_{ep} \cdot V_{nBE} + I \cdot r_{en}$  is increasing, which represents as the on-resistance of the SCR. The V<sub>potential</sub> is barrier across the reversed Nwell/Pwell. It is influenced by the junction shape, doping concentration of the Nwell/Pwell junction. In that case, one way to increase the holding voltage is to stretch the base width of two BJTs or lower the doping concentration, however, this will reduce the current gains of PNP and increase the junction reverse breakdown voltage, or the trigger voltage. If the gains are lowered too much, the condition  $\beta_n\beta_p \geq 1$  may not meet, the SCR will not turn-on into a positive feedback.

Due to the positive feedback and deep snapback feature, SCRs usually possess the feature of high trigger voltage and very low holding voltage. Although this will provide very high ESD current capability and very low on-resistance, the I-V curve of SCR may not meet the ESD design window. To improve this, many modifications are made to SCRs.

## 1.3 Dissertation outline

Different technologies and applications require customized ESD consideration at the early stage of design and development. The goal of this research is to develop compact models for circuit level ESD simulation and investigate ESD failure related issues. This dissertation is summarized as following:

Chapter 1 presents some of related the background information, from the ESD event, ESD test models and test method. Since this dissertation focuses on ESD models, ESD failure and failure model related topics are. Chapter 2 gives one approach of ESD failure model and model parameter extraction method. This modeling methodology uses temperature instead of voltage or current values to predict device failure due to thermal energy. Chapter 3 takes a deep look into the physical mechanism behind device thermal failure, and proposed a new method to estimate the failure temperature for typical ESD devices. Chapter 4 reports a comprehensive diode model for circuit level ESD simulation. ESD related issues like overshoot, on-resistance variation and in-device temperature increment during stress, are included in this model. Chapter 5 investigate the ESD performance of vertical Gallium nitride (GaN) diode in forward conducting. The experiment results show interesting turn-on delay phenomenon for vertical GaN diode, especially under short duration pulses.

# CHAPTER 2 JUNCTION THERMAL FAILURE MODEL FOR DEVICES SUBJECT TO ELECTROSTATIC DISCHARGE STRESSES

#### 2.1 Introduction

As the ICs is highly integrated with shrinking transistor size, the silicon ICs are becoming more vulnerable to ESD stresses, thus, simulating ESD event and finding potential reliability defects prior to fabrication is highly valuable for developing and improving IC designs. Since ESD stresses tend to push devices to operate beyond their normal region of operation, conventional models are incompetent to support simulations in the ESD current-voltage regime. Moreover, as ESD stress may push devices to their final failure point, failure prediction models are also required when simulating for ESD Classification test levels.

Compact models are established based on physical mechanism, and there are two major ESD-induced damages responsible for the catastrophic failure[43, 44]; dielectric breakdown, which is electric field-related [45], and thermal failure, which is energy dissipation/temperature-related [46-48]. Dielectric breakdown typically occurs at the gate of MOS devices, and is getting increasingly important due to the aggressive scaling of MOS-gate dimensions as well as dielectric thicknesses in advanced CMOS processes [49]. On the other hand, thermal failure is more common as current flows through any layer or junction in the IC and continuously heats the structure.

Thermal failures have been reported in the literature and can be simulated in many ways [46-52]. It is a delicate way using TCAD software to solve the differential heat conduction equations numerically and predict thermal conduction in devices. Such method, however, are

limited by the complexity when simulating a small circuit performed in mixed-mode. They are incompatible with parameter-based compact circuit models.

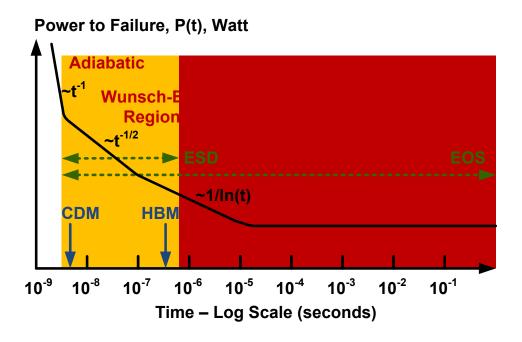

The thermal failure of a semiconductor component is evaluated by the power-to-failure ( $P_f$ ) within a stress pulse time ( $t_f$ ), assuming the stress power is constant. Reports in the literature [46, 47] established physical electro-thermal models to describe the  $P_f$  as a function of pulse duration. Wunsch-Bell first described the thermal failure process as linear curves with time dependency of  $t^{1/2}$  in a log timescale plot using one dimensional analysis [46]. Later, a wider pulse time spectrum was expanded and divided into different time ranges, describing the observed dependence of  $P_f$  with respect to  $t_f$  in experiments [47, 48]. Dwyer's work [48] extended the Wunsch-Bell model into a larger time-scale range in which the three dimensional thermal diffusion is divided into several time regions using the time scales  $t_a$ ,  $t_b$ , and  $t_c$ . As the curve depicted in Figure 2-1, the first portion of the curve is the adiabatic region, typically within short time of 10ns. It has a time dependence of 1/t. From tens of nanoseconds to microseconds, it is the Wunsch-Bell region where the plot fits a  $1/t^{1/2}$  slope. For a very long stress time, typically beyond 100  $\mu$ s, the power enters a steady state as the thermal equilibrium has been established.

Figure 2-1 Input power-to-failure as a function of electrical pulse width, for a constant  $\Delta T$ , across a reverse-biased junction.

Other Circuit-level simulation of thermal failure in ESD events has been proposed using different approaches. Some [51, 52] used the above described power-to-failure or Wunsch-Bell relations to predict failure in rectangle pulses with constant power. An approach has been using thermal networks with infinite stages, based on the differential heat diffusion equation [50]. This necessitated elaborated program coding to incorporate them in circuit simulators, which limited its adoption. These methods assumes thermal failure under constant stress, but the reality is that ESD stresses are characterized by electrical waveforms with irregular shapes. Others try to use the average power of an ESD pulse [53] or exponentially decaying current profile [54] to represent a given ESD stress, such as the HBM, however, such methods indicate we must establish different failure models according to different ESD stress model, such as Charged

CDM or HMM. Additionally, the input stress waveform may be distorted after passing through various circuitry interfaces. To address these shortcomings in the successful adoption of thermal failure models for large scale circuit simulation, defining a modeling framework that can be implemented in SPICE and applicable in simulations using arbitrary ESD stress conditions urgently needed [55].

#### 2.2 Modeling and Characterization

A sub-circuit compact model for device failure under ESD stress is proposed. The model is designed to be fully compatible with SPICE circuit simulation tools. For a given ESD stress, it reproduces the thermal behavior in the device by simulating temperature variations in discrete stages. Model parameters are extracted using measurement data from a High Power Pulse Instrument (HPPI) tester which generates pulses with widths ranging from 5ns to 500 ns. The p-n junction structures are first picked up to establish the model, since they are the most fundamental building blocks in many devices. Once model parameters are extracted, temperature variation can be simulated within the sub-circuit model. The compact model is verified by comparing the measured and calculated failure power with respect to failure time results.

Most thermal failures occurring in semiconductors are related to current filament that pushes lattice temperature to a critical level. As a fundamental structure in the CMOS process, p-n junctions function as a trigger element of most passive ESD protection devices and across which, the majority of ESD stress drops on it. Thus, it is susceptible to ESD damage when the discharged energy flows through the device.

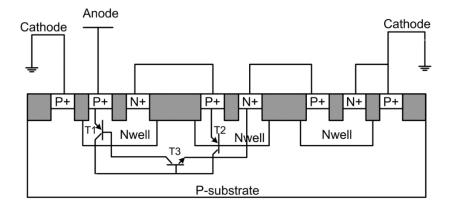

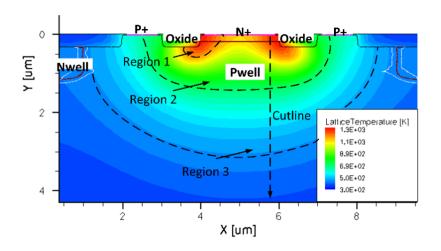

Figure 2-2 shows the TCAD simulation of temperature distribution in a reverse biased p-n diode at the end of an ESD stress. When the pulse voltage exceeds the junction reverse breakdown voltage, leakage current increases exponentially and heats the junction area continuously. The silicon region with the highest temperature is the hotspot and is located near the silicon surface [56]. Due to the competition between heat generation and heat dissipation, heat id generated at hotspot and diffuses into deep silicon. The temperature keeps rising until the end of the pulse stress or a thermal equilibrium state is reached. Whenever a critical temperature is reached at the hotspot during this period, the device fails.

Figure 2-2 Simulated lattice temperature contours with three different thermal regions.

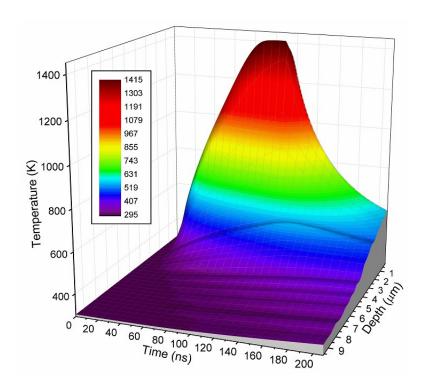

A cutline in Figure 2-2 is drawn from the hotspot near the surface of the device to deep silicon region, by combining temperature contours at different time frame, the time dependent temperature variation of a 100 ns pulse stress can be probed (Figure 2-3). The temperature at the hotspot region rises when the electrical pulse stress is applied. The region deep into the silicon

follows slowly due to the delay in the heat diffusion. After pulse ends in 100 ns, the highest temperature is recorded in the hotspot region. The temperature begins to drop thereafter.

Figure 2-3 Time dependent temperature variation along the depth of junction structure under a transient pulse stress.

# 2.3 Model Parameter Extraction

According to time-dependent temperature variation depicted in Fig. 2-3, heat dissipates from the hotspot towards the silicon bulk, which contributes to a temperature gradient in device. Thus, the device may be partitioned into thermal regions with different temperature levels they represent. The junction region in Figure 2-2 is divided into three regions as the dashed lines indicate. The small one in red color is the hotspot region with the highest temperature,

surrounded by the Region-2 with a lower temperature. Between the Region-2 and the rest of the bulk material is Region-3, in which the temperature gradually degrades until the ambient temperature is reached.

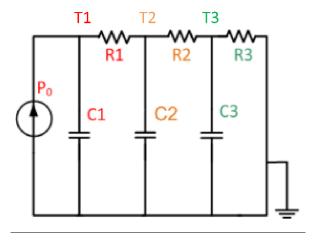

A Cauer ladder thermal equivalent circuit has been used to model device self-heating [57]. Based on the analogy between electrical and thermal conductions [58, 59], the thermal behavior can be reproduced as an electrical circuit. The electrical equivalent of power and temperature are current and voltage, respectively. The thermal capacity is similar to a capacitor in an electrical circuit, and the efficiency of heat dissipation is measured by thermal resistors. Thus, the larger the thermal capacitor, the more thermal energy it can store, and the smaller thermal resistor, the faster heat transfers between adjacent regions.

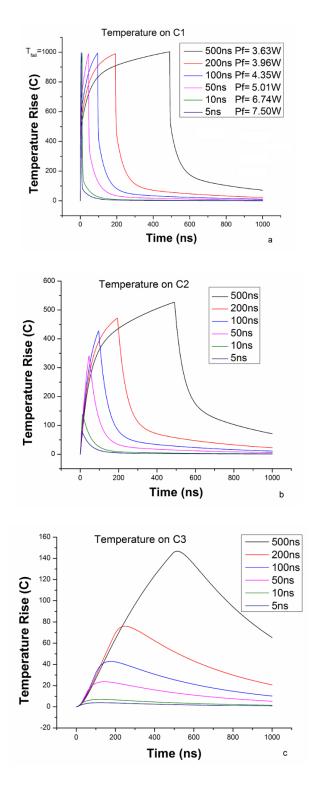

The three stage circuit shown in Figure 2-4 has been used as the thermal failure model in this study. The current source  $P_0$  represents the input ESD power that generates heat in unit of watt. The capacitor and resistor pairs represent the volume of thermal energy and heat dissipation efficiency in the thermal regions as shown in Figure 2-2. The hotspot region is equivalent to the C1 capacitor in the thermal circuit. Since the capacitors represent the region from the hotspot (small volume) to deep bulk inside the silicon (large volume), the boundary condition for the capacitor values must be C1 < C2 < C3.

Figure 2-4 Equivalent circuit for the compact junction thermal failure model.

There is always heat dissipation as long as there is temperature differential between two adjacent regions. The values of the resistors define how fast heat can be transferred from inner region to outer silicon. A small resistances indicate fast heat dissipation. It is obvious that a model with more stages can achieve higher accuracy, to balance between accuracy and complexity, we choose a three-stage model here. Given the values of the R's and the C's, the thermal behavior in a p-n junction region can be mapped into temperature variation in the model with discrete stages,

The parameters of the thermal circuit are extracted from experimental measurement under different pulse stresses. Two types of p-n diodes, namely P+/Nwell and N+/Pwell, and one GGNMOS are used for the extraction. The diodes' dimensions are 25  $\mu$ m  $\times$  25  $\mu$ m square shape and 10  $\mu$ m  $\times$ 100  $\mu$ m rectangle shape for both n-type and p-type diodes. As for the ggNMOS, it is designed as multi-finger device with 200  $\mu$ m total width. The characterization is carried out by an HPPI transmission line pulse (TLP) tester with 4-pin probe Kelvin configuration. A high

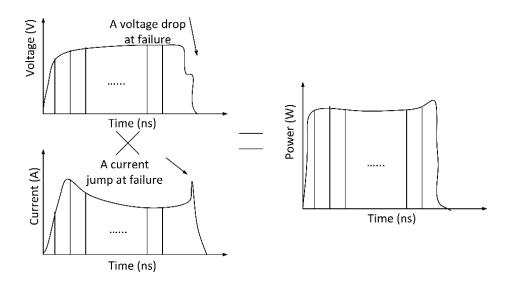

frequency oscilloscope at the back-end of data sampling is used to capture the reflected waveforms. Six pulse widths of 5, 10, 50, 100, 200, and 500 ns have been used to characterize the device.

This time range covers most of the ESD stresses of interest. The TLP tester stresses the device with increasing pulse levels until hard failure occurs. Failure is identified as the current (It2) and voltage (Vt2) where the voltage collapses or the current increases exponentially. Six pulse widths indicate there will be six thermal failure points obtained for each device tested. The product of the Vt2 and It2 yields the power-to-failure ( $P_f$ ), as shown in Figure 2-5. Six pulse widths yield six  $P_f$  waveforms accordingly. Table 2-1 lists the extracted  $P_f$  values for model fitting. A square-like waveform approximation is used in this case, for both, forward and reverse bias.

Figure 2-5 Failure power vs. time waveform as the product of Vt2 and It2 waveforms

Table 2-1 Measured failure power for model fitting

| $P_f(W)\&t(ns)$ |           | 5     | 10    | 50    | 100  | 200  | 500  |

|-----------------|-----------|-------|-------|-------|------|------|------|

| Reverse         | Square    | 7.50  | 6.74  | 5.01  | 4.35 | 3.96 | 3.63 |

|                 | Rectangle | 15.75 | 15.05 | 10.71 | 9.22 | 8.43 | 7.48 |

| Forward         | Square    | 24.15 | 17.53 | 11.92 | 9.97 | 7.78 | 6.01 |

|                 | Rectangle | 22.32 | 15.69 | 11.77 | 8.56 | 6.25 | 4.69 |

| ggNMOS          | 200μm     | 83.92 | 51.96 | 27.86 | 21.8 | 18.9 | 13.9 |

The next step in the modeling process is to extract the parameters of components in the equivalent circuit. First,  $P_f$  functions as the initial power  $P_\theta$  in Figure 2-4. With the boundary conditions of  $P_\theta$  and pulse width, the values of the R's and the C's were extracted by using the fitting tool like ADS to fit the end pulse temperature on C1 to correspond to a fail temperature,  $T_{fail}$ . Notice that there is still no conclusive  $T_{fail}$  value for thermal failure temperature in silicon, users can define any value as the  $T_{fail}$ , but the extracted R and C parameters will change accordingly. Once  $T_{fail}$  is reached on C1 in the simulation, the device is permanently damaged marked as the device hard failure.

Assuming that during the stress, device temperature increment is 1,000 from background temperature of 0 and ends at  $T_{fail}$ =1,000, the temperature variation in the device can be simulated as three discrete temperatures on thermal capacitors in Figure 2-4.

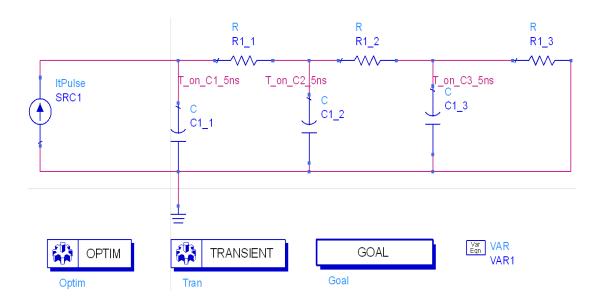

Figure 2-6 is one example of the fitting setup to extract R and C values using ADS software. An optimization goal is setup that the temperature increment under six different pulse width stresses reaches a consistent  $T_{fail}$ =1,000, then the R and C values right for the optimization, namely the parameters for the thermal failure model. To avoid false parameters being extracted, the optimization confinement must be set as C1<C2<C3.

Figure 2-6 ADS software tool setup for parameters extraction

Table 2-1 gives extracted R and C values for the thermal circuit model. Parameters for both forward and reverse directions are extracted. With these parameters, temperature variation during the pulse stress is reproduced as the discrete temperature curves on the three thermal stages. Figure 2-7 shows one such example of a 25  $\mu$ m × 25  $\mu$ m square shape diode and its temperature simulation curve.

Table 2-2 Extracted R and C values

| $R(\Omega)\&C(nF)$ |           | C1     | R1   | C2    | R2   | C3    | R3 |

|--------------------|-----------|--------|------|-------|------|-------|----|

| Reverse            | Square    | 0.0107 | 131  | 0.404 | 108  | 7.203 | 71 |

|                    | Rectangle | 0.003  | 56   | 0.780 | 53   | 7.394 | 29 |

| Forward            | Square    | 0.072  | 55   | 0.498 | 23   | 1.828 | 99 |

|                    | Rectangle | 0.062  | 64   | 1.396 | 176  | 4.014 | 13 |

| ggNMOS             | 200µm     | 0.32   | 29.6 | 3.051 | 20.4 | 10.76 | 57 |

Figure 2-7 Simulated temperature vs, time curves in the three thermal regions of the square-shape diode subject to TLP pulses having different pulse widths and failure power.

Although only the discrete temperature distribution in the silicon region is simulated, it still reflects the correct physical mechanisms within the device. Just as the assumption of the thermal failure, for high power stress, thermal energy is generated fast and dissipation is slow, thus failure temperature is reached in a very short period of time. While during a long pulse with much lower power levels, the temperature rises slowly, leading to a very long period of time before failure temperature is reached.

Figure 2-7 (b) and Figure 2-7(c) also show the simulated temperature variation curves on the C2 and C3 capacitors, which verify the assumption of the thermal failure. They represent the rest of silicon region adjacent to background bulk region. As heat diffuse into deep silicon, the temperature decays gradually from Region-1 to Region-3. For short pulse failure, when C1 reaches the failure temperature, there is little thermal energy dissipate into Region-2 and Region-3, thus temperature increment is very low in these two regions. However, when device fails under long pulse, there is enough time for heat to dissipate into deep silicon, heating Region-2 and Region-3 to higher temperatures. These simulated results correlate well with the numerical TCAD simulations shown in Figure 2-2.

#### 2.4 Model Verification

In the previous mentioned modeling framework, the thermal failure in silicon was evaluated as power-to-failure at a failure time, and when silicon device fails, a collapse in the voltage and an increase in the current transient waveforms can be observed. Based on such an assumption, additional  $P_f$  vs. failure time data can be obtained by using different pulse duration

with different power level. These test results can be used for model verification to complement the six fixed pulse widths discussed earlier.

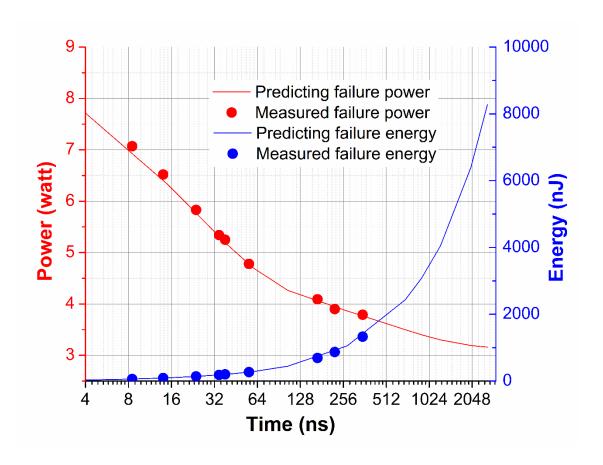

Assuming stressing the same device with higher power level but longer pulse width, we can observe thermal failure will occurs at the mid of a long pulse as voltage waveform drop off or current waveform jump up. In Figure 2-8, the continuous curves are predicting curve of  $P_f$  vs. failure time (red curve) and failure energy vs. failure time (blue curve) obtained by the model simulation in previous section. Red dots and blue dots are measured  $P_f$  vs. failure time and failure energy vs. failure time data points, respectively. It can be seen that all the measured failure points correlate with the simulated points, the shorter the pulse the higher the failure power. It should be noted that  $P_f$  decreases exponentially as pulse width increases, which conforms to the exponential decreasing trend in Figure 2-1.

Figure 2-8 Comparison of simulated and measured failure power/energy vs. failure time data for a rectangle shape diode under different pulse widths.

The thermal failure model has been implemented using Verilog-A as a failure monitor in a SPICE-type simulator. The monitor uses the current and voltage, the product of which is used to calculate the injected instantaneous power, and it is fed into the thermal equivalent circuit. The monitor gives the temperature rise as its output. A temperature controlled switch is added in parallel with the diode model. The switch is open under normal operation conditions, and once the temperature at C1 reaches the critical value  $T_{fail}$ , the switch will become closed. When the

ESD stress causes the diode to fail a low resistance path between the diode anode and cathode is established indicative of a failure.

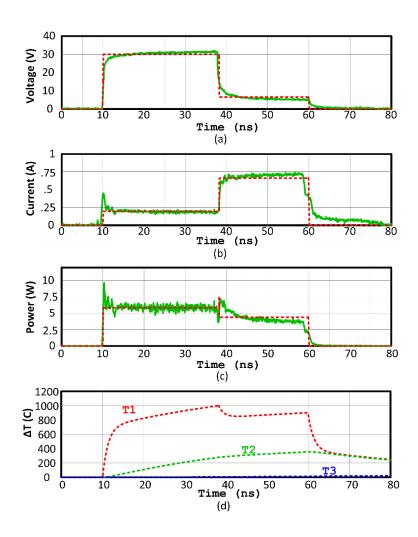

In that case, we can apply the thermal failure monitor in circuit level ESD simulation. Figure 2-9 demonstrates the simulation results, as well as the measurement data, for the 25  $\mu$ m  $\times$  25  $\mu$ m diode during a TLP pulse that caused device failure. The ESD stress source is a rectangular pulse with 50  $\Omega$  impedance. The pulse width of this specific stress is 50 ns.

Figure 2-9 Simulation results using a TLP pulse that caused device failure (the solid lines for the measurement and the dash lines for the simulation).

The diode uses the standard SPICE diode model. The measured data showed that when hard failure occurs, the voltage dropped significantly in the middle of the stress pulse and the current became several times higher at the same time point. The power, derived from the product of current and voltage, decreased approximately 25%. The leakage current measured before and after the pulse stress indicated that the device had failed during the stress and the voltage drop and current rise were obviously the result of the failure. The simulation matches the measured voltage, the measured current and the measured power very well (curves in green color). The simulated temperatures are plotted in Figure 2-9(d) from which we can see the temperature at C1 reaching the critical failure point of  $T_{fail}$ =1,000 at around 37 ns. Also, we can observe temperature variation in deep silicon regions, represented by C2 and C3, with much lower temperature increment. This thermal failure model has no restriction on stress power profile and can be applied to more complicated transient stress waveforms.

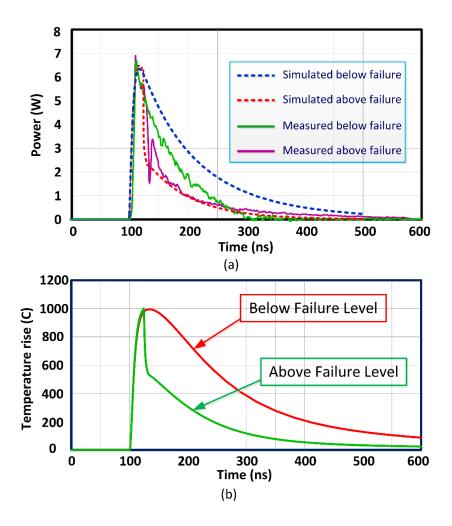

Figure 2-10 shows the SPICE simulation results under HBM stress. The waveform changes immediately before and after device failure for the same diode shown in Figure 2-9. The measurement data were obtained using an HPPI TLP tester. The simulated temperature at C1 was also plotted in Figure 2-10(b). Once failure temperature is reached during simulated stress, the device turns into a short circuit configuration and the power has an abrupt change. Compared to the measured waveform, this simulation accurately predicted the device failure under transient HBM stress. It can be seen that the temperature rises very quickly at the rising edge of the stress pulse and keeps rising even after the power reaches its maximum.

Figure 2-10 HBM power waveforms from measurement and simulation and the corresponding simulated temperature at the stress levels close to device failure.

Functions as a core model only for monitoring temperature rise and thermal failure, this model has no explicit geometric parameters. In other words, it is not a scalable model yet. However, the geometry effects are actually included and embedded in the device models as R and C values. Extracted R and C values will changed with different junction geometries. Combined with existing electrical models for simulation under ESD stress [60], this model can be used as a thermal failure monitor in ESD event simulation for any devices, according to the

different device types or dimensions, the extracted model parameters will change accordingly as proper capacitance and resistance values.

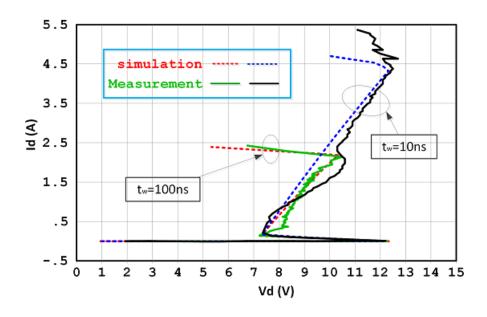

As aforementioned, the thermal failure model can be applied to different device as long as the device's temperature rises under an ESD stress and fails due to thermal failure. Figure 2-11 shows an example of a GGNMOS with silicide block. After the GGNMOS trigger and snapbacks into a low resistance state, ESD current flows through the reversed p-n junction at the drain-body interface and continuously heat the device. With the diode being replaced by a 200 µm GGNMOS model, the voltage and current simulated are convert into stress power. As failure temperature reached, a secondary snapback phenomenon can be observed as device fails and turns into a short circuit state. The NMOS model includes the core MOS component and the parasitic bipolar NPN device [60]. The measured I-V curve was obtained using 100 ns TLP and 10 ns vfTLP measurement, respectively.

Figure 2-11 Simulation of secondary snapback in a GGNMOS with combination of the thermal failure model and ESD capable MOS device model.

## 2.5 Conclusion

A compact model designed for predicting the device thermal failure under the ESD stress has been proposed. The model is derived from the physical thermal behavior in device during an ESD stress. Device geometry is accounted for in the effective parameter extraction procedure. It can be implemented SPICE like simulator using Verilog-A, making it compatible with industry-standard circuit-level simulators. Simulations by this model were found consistent with the physics and in good agreement with the measurement. Under rectangular TLP pulse and transient HBM stresses the accuracy of the model simulation is verified. The model can be used as a thermal failure monitor, along with ESD capable compact models of devices, to predict thermal failure in circuit-level simulation for classical ESD events such as HBM, CDM, and HMM.

# CHAPTER 3 INVESTIGATION OF FAILURE TEMPERATURES OF SEMICONDUCTOR DEVICES UNDER ELECTROSTATIC DISCHARGE STRESSES

#### 3.1 Introduction

Thermal runaway is one of the major mechanism responsible for semiconductor device's irreversible damage. In-device temperature under test rises in-situ during an electrical stress due to inevitable self-heating. The competition between heat generation and heat dissipation will determine whether the device fails due to reaching a critical failure temperature or entering a thermal equilibrium state. As a common failure criteria, failure voltage and/or current values are use as ESD design parameter, however, extracting the thermal failure temperature gives better physical insight into the degradation of the device. Moreover, the failure criterion of temperature can be potentially valuable for ESD simulation under arbitrary stress waveform. That doesn't mean the two sets of parameters are mutually exclusive, and actually failure current/voltage as well as failure temperature can complement each other when performing ESD simulations [55].

Although with such pros, there is difficulty to apply temperature as a failure criterion, for direct measurement of the failure temperature in a device during an ESD event is very challenging, or even impossible, as the self-heating by an ESD event may be too short to be captured by a thermal detector. Moreover, little thermal energy may escape from the device's surface as most of the heat diffuses into the bulk [56]. This makes a direct observation of temperature very difficult.

On the other hand, different temperature values have been used as boundary conditions for thermal failure analysis, and there is still dispute on which as a failure criterion. It is commonly accepted that devices fail when the temperature reaches the silicon melting temperature (~1,414 °C). While it has been argued that the device damage threshold is much lower due to the temperature where the intrinsic carrier concentration is equal to the background doping concentration [61], or known as the intrinsic temperature. It was also reported that the onset of thermal breakdown occurs when the thermally generated free carriers become significant in comparison with the avalanche generated free carriers [62]. Besides the junction region through which most current flows, failures may also take place at the silicon-aluminum interface where the eutectic temperature is approximately 550°C. However, none of the failure mechanisms have been decisively verified by experiments. And it is highly possible that failure temperature varies according to device types and stress conditions.

To determine the critical temperature responsible for an ESD-induced thermal failure, an experimental procedure based on the electrical-thermal analogy is proposed in this paper [63]. Such a methodology enables the extraction of the failure temperature for typical device types and, consequently, the determination of the proper failure criterion for the purpose of ESD event simulations. Physical insights into the extracted failure temperature with respect to stress time are also illustrated and discussed.

# 3.2 Experimental Methodology

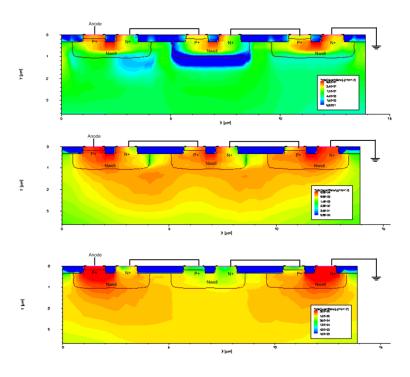

Device thermal behavior under ESD stress is difficult to observe directly, and it is highly dependent on stress power and duration. With shorter stress duration, the visibility of thermal emission decreases. TCAD simulations provides one solution to look into the thermal flow in semiconductors. Figure 3-1depicts the thermal profile in a diode stressed by short and long

electrical pulses. By adjusting the stress levels of a 10ns pulse and a 200ns pulse, the same maximum lattice temperature can be achieved at the end of each pulse. Their temperature distribution, however, will be very different. Under a short pulse, the thermal region barely expands, while for the longer pulse the peak temperature is reached with a much bigger corresponding thermal region.

Figure 3-1 Simulated temperature distributions in a diode under a short (10 ns) (left) and a long (200 ns) (right) electrical pulses.

Thermal failure in semiconductor devices can be described by the power-to-failure (Pf) versus time (t) relationship

$$P_f = f(T_f - T_0, t^n) \tag{3.1}$$

where  $T_{\theta}$  is the ambient temperature and also the starting temperature, n is the time index depending on the time range of the ESD event, and  $T_f$  is the failure temperature. The equation

can be expressed in different forms depending on the time duration which ranges from the adiabatic region to thermal equilibrium state [48].

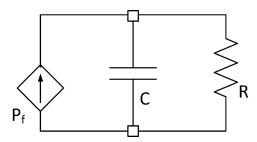

Since there is an analogy between heat conduction and electrical conduction [58], the time-dependent thermal diffusion and the expansion of the thermal region in a semiconductor device can be mapped into an equivalent circuit [55, 64], as shown in Figure 3-2. The voltage across the circuit corresponds to the temperature increase in the device, moreover, since there is only one stage in the equivalent circuit, we are assuming a uniform heating of the material.

Figure 3-2 One-stage thermal equivalent circuit. The voltage on capacitor C is equivalent to the average temperature in the region under stress.

During a transient stress, heat is generated in the device and diffuses from the hotspot to the deep silicon, namely the heat-sink. When a constant power P is applied at time t=0, the temperature change can be expressed analytically as

$$T - T_0 = P \cdot R \cdot \left(1 - e^{\frac{-t}{RC}}\right) \tag{3.2}$$

where P is the power-to-failure, R stands for the thermal diffusion efficiency, C represents the thermal capacity of the thermal region, and t represents the duration of the stress. For the case where a device fails under a stress with a fixed pulse width but at different ambient temperatures

$T_0$ , the temperature T reaches the failure temperature  $T_f$  and (2) can be simplified into a linear equation

$$T_f - T_0 = P_f \cdot B \tag{3.3}$$

where  $B = R(1-e^{-t/RC})$  is a constant representing for a given pulse width t. In case of the linear form of the equation, it indicates that  $P_f$  is lower for a higher  $T_\theta$  and if the starting temperature  $T_\theta$  is high enough, stress power could be equal to zero. Therefore,  $T_f$  can be extracted from the intercept of the  $P_f$  vs.  $T_\theta$  plot.

Note that there is only one stage in the equivalent circuit, thus we are assuming only one temperature representing the device temperature and the voltage across C in Figure 3-2 is a value representing the average temperature in the heated region. While this is not accurate for actual physical behavior behind thermal failure because the device does not heat uniformly due to the nature of thermal conduction.