Electronic Theses and Dissertations, 2004-2019

2016

# Study of Novel Power Semiconductor Devices for Performance and Reliability.

Karthik Padmanabhan University of Central Florida

Part of the Electrical and Electronics Commons

Find similar works at: https://stars.library.ucf.edu/etd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### STARS Citation

Padmanabhan, Karthik, "Study of Novel Power Semiconductor Devices for Performance and Reliability." (2016). *Electronic Theses and Dissertations, 2004-2019.* 4904. https://stars.library.ucf.edu/etd/4904

# STUDY OF NOVEL POWER SEMICONDUCTOR DEVICES FOR PERFORMANCE AND RELIABILITY

by

#### KARTHIK PADMANABHAN

B.S. Electrical Engineering, BITS, Pilani-Dubai Campus, 2005M.S. Electrical Engineering, University of Florida, 2008

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida

Orlando, Florida

Spring Term 2016

Major Professor: Jiann S. Yuan

© 2016 Karthik Padmanabhan

#### **ABSTRACT**

Power Semiconductor Devices are crucial components in present day power electronic systems. The performance and efficiency of the devices have a direct correlation with the power system efficiency. This dissertation will examine some of the components that are commonly used in a power system, with emphasis on their performance characteristics and reliability.

In recent times, there has a proliferation of charge balance devices in high voltage discrete power devices. We examine the same charge balance concept in a fast recovery diode and a MOSFET. This is crucial in the extending system performance at compact dimensions. At smaller device and system sizes, the performance trade-off between the ON and OFF states becomes all the more critical. The focus on reducing the switching losses while maintaining system reliability increases. In a conventional planar technology, the technology places a limit on the switching performance owing to the larger die sizes. Using a charge balance structure helps achieve the improved trade-off, while working towards ultimately improving system reliability, size and cost.

Chapter 1 introduces the basic power system based on an inductive switching circuit, and the various components that determine its efficiency. Chapter 2 presents a novel Trench Fast Recovery Diode (FRD) structure with injection control is proposed in this dissertation. The proposed structure achieves improved carrier profile without the need for excess lifetime control. This substantially improves the device performance, especially at extreme temperatures (-40°C to 175°C). The device maintains low leakage at high temperatures, and it's Qrr and Irm do not

degrade as is the usual case in heavily electron radiated devices. A 1600 diode using this structure has been developed, with a low forward turn-on voltage and good reverse recovery properties. The experimental results show that the structure maintains its performance at high temperatures.

In chapter 3, we develop a termination scheme for the previously mentioned diode. A major limitation on the performance of high voltage power semiconductor is the edge termination of the device. It is critical to maintain the breakdown voltage of the device without compromising the reliability of the device by controlling the surface electric field. A good termination structure is critical to the reliability of the power semiconductor device. The proposed termination uses a novel trench MOS with buried guard ring structure to completely eliminate high surface electric field in the silicon region of the termination. The termination scheme was applied towards a 1350 V fast recovery diode, and showed excellent results. It achieved 98% of parallel plane breakdown voltage, with low leakage and no shifts after High Temperature Reverse Bias testing due to mobile ion contamination from packaging mold compound.

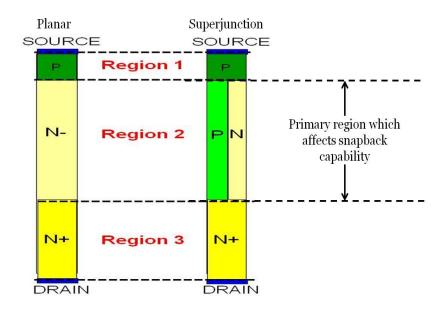

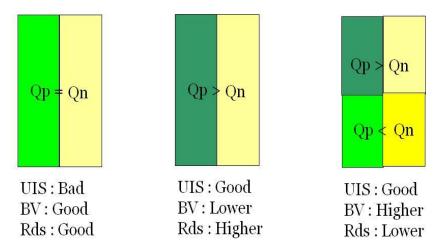

In chapter 4, we also investigate the device physics behind a superjunction MOSFET structure for improved robustness. The biggest issue with a completely charge balanced MOSFET is decreased robustness in an Unclamped Inductive Switching (UIS) Circuit. The equally charged P and N pillars result in a flat electric field profile, with the peak carrier density closer to the P-N junction at the surface. This results in an almost negligible positive dynamic Rds-on effect in the MOSFET. By changing the charge profile of the P-column, either by increasing it completely or

by implementing a graded profile with the heavier P on top, we can change the field profile and shift the carrier density deeper into silicon, increasing the positive dynamic Rds-on effect.

Simulation and experimental results are presented to support the theory and understanding.

Chapter 5 summarizes all the theories presented and the contributions made by them in the field. It also seeks to highlight future work to be done in these areas.

To my parents T.V. and Jaya Padmanabhan

#### **ACKNOWLEDGMENTS**

I would first like to thank my advisor Dr. Peter Yuan for his unending support toward my PhD and this dissertation. Sustaining motivation for finishing this dissertation was a difficult task and he managed to constantly ensure I did whatever was required to meet my goal. This would not have been possible without his presence. He became my advisor in less than ideal circumstances and I greatly appreciate all his help and assistance. I would also like to thank Dr. Kalpathy Sundaram for his constant guidance and support during this endeavour.

I also deeply appreciate all the feedback and comments from Dr.Ronald DeMara, Dr. George Atia and Dr. Lee Chow which eventually helped sharpen my dissertation and make it more cohesive.

I would especially like to mention Dr. John Shen, who was the reason I got inspired to pursue a PhD in power semiconductor design. His role in being the initial catalyst in my research is what eventually led me to this stage. I also cannot forget the assistance from Dr. Patrick Shea, who I met while a student in Dr. Shen's lab. Patrick has been a valuable support and sounding board during this entire journey, and his feedback and comments have had a huge role in shaping my dissertation.

This acknowledgement would be incomplete is I fail to mention my employers, Alpha and Omega Semiconductor. From teaching me the practical applications of all my theoretical learnings and constantly encouraging me to pursue my PhD, while also graciaouly allowing me

to use some of work toward my PhD, it is sufficient to say that this dissertation would simply not exist if not for their presence and support. I would especially like to thank my colleagues and managers Jun Hu, Lingpeng Guan and Madhur Bobde in this regard.

Last but not the least, they say family plays a huge role in everything you accomplish, and my case is no different. I would like to especially like to thank my parents and my sister, Vidhya, for supporting me and putting up with me while I finished my PhD. Apart from my own family, the role played by my uncle N.C.Murthy in constantly pushing me to complete my PhD is both invaluable and vital in me doing so. Beyond them, all assistance from my friends and extended family for this task is most appreciated.

Thank you all.

# TABLE OF CONTENTS

|                                     | <u>page</u> |

|-------------------------------------|-------------|

| LIST OF FIGURES                     | xi          |

| LIST OF TABLES                      | XV          |

| LIST OF ABBREVIATIONS               | xvi         |

| INTRODUCTION                        | 1           |

| Inductive Switching Circuit         | 1           |

| Charge Balanced Devices             |             |

| High Voltage Edge Termination       | 5           |

| Superjunction Ruggedness            | 7           |

| FAST RECOVERY DIDOE                 | 11          |

| Introduction                        | 11          |

| Prior Art                           |             |

| External Lifetime Control           |             |

| Electron Radiation                  | 19          |

| Gold Diffusion                      | 22          |

| Platinum Diffusion                  |             |

| Injection Control                   | 23          |

| Schottky Controlled Injection Diode |             |

| Hydrogen Implant                    |             |

| CIBH Diode                          |             |

| Trench Shielded Fast Recovery Diode | 27          |

| Fabrication                         |             |

| Step 1: Epi Growth                  |             |

| Step 2: Trench Etch                 |             |

| Step 3: Thermal Drive               |             |

| Step 4: Polysilicon Deposition      |             |

| Step 5: P-Base Implant              |             |

| Step 6: Topside Metallization       |             |

| Step 7: Backside Metallization      |             |

| Impact of Injection Control         |             |

| Results                             |             |

| Conclusion                          |             |

| HIGH VOLTAGE EDGE TERMINATION       | 46          |

| Introduction                        | 16          |

| Prior Art                                       | 47        |

|-------------------------------------------------|-----------|

| Junction Termination Edge                       | 47        |

| Field Rings                                     |           |

| Metal Plates                                    |           |

| Field Plate Based Edge Termination Structures   |           |

| Charge Imbalance Termination                    |           |

| Edge Termination Based on Oxide Filled Trenches |           |

| Proposed Structure Design                       |           |

| Fabrication                                     |           |

| Step 2B: Trench Etch+BGR Implant                | 57        |

| Process Variations                              | 59        |

| Design Features                                 |           |

| Results and Discussion                          | 66        |

| Conclusion                                      | 68        |

|                                                 |           |

| SUPERJUNCTION MOSFET RUGGEDNESS                 | 69        |

| Turn hardan                                     | <b>60</b> |

| Introduction                                    |           |

| Prior Art                                       |           |

| Device Simulations and Analysis                 |           |

| Superjunction MOSFET Design for Improved UIS    |           |

| P Heavy Structure                               |           |

| N Heavy Structure                               |           |

| Graded SJ MOSFET Structure                      |           |

| Summary                                         | 83        |

| CONCLUSION AND FUTURE WORK                      | 86        |

|                                                 |           |

| Summary                                         | 86        |

| Future Work                                     |           |

| Trench Based Fast Recovery Diode.               | 89        |

| Edge Termination                                | 90        |

| Superjunction Robustness                        |           |

|                                                 |           |

| APPENDIX A: TRENCH DIODE SCHEME CODE            | 92        |

| APPENDIX B: TERMINATION SCHEME CODE             | 102       |

| MILITAL D. ILKWIIIATION SCHEWE CODE             | 102       |

| I IST OF REFERENCES                             | 124       |

# LIST OF FIGURES

| <u>Figure</u>                                                                                                             | page |

|---------------------------------------------------------------------------------------------------------------------------|------|

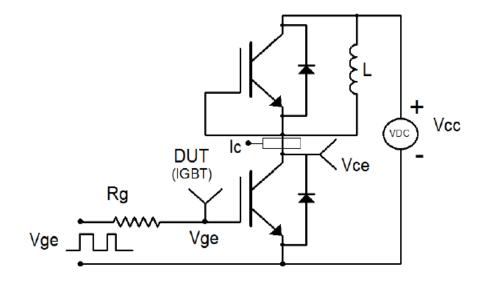

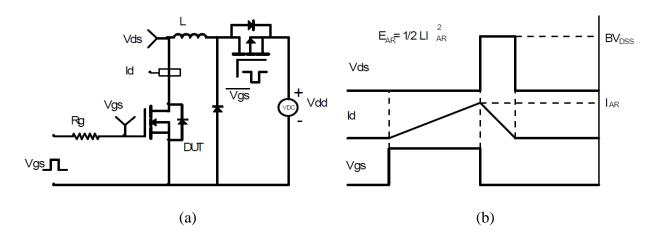

| Figure 1.1. A Conventional Inductive Switching Circuit.                                                                   | 1    |

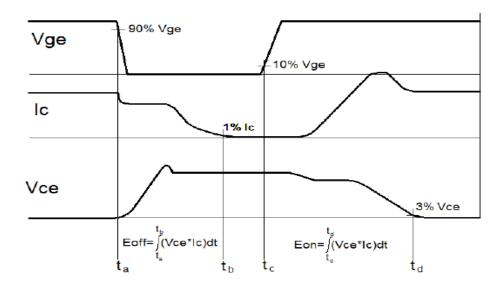

| Figure 1.2. Switching waveforms in an Inductive Switching Circuit.                                                        | 2    |

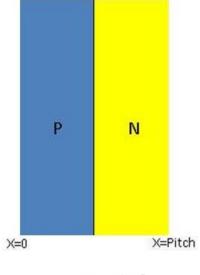

| Figure 1.3. A conventional charge balance structure and the accompanying equation governing the net charge.               | 4    |

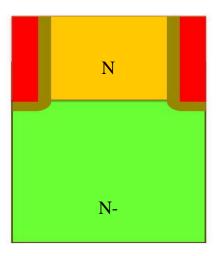

| Figure 1.4. A partial superjunction epi with a Trench MOS structure on top                                                | 5    |

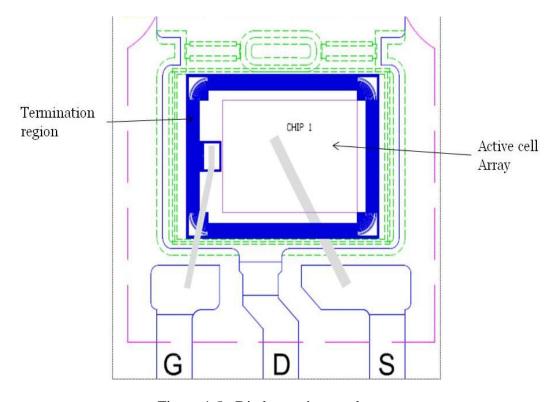

| Figure 1.5. Die layout in a package.                                                                                      | 6    |

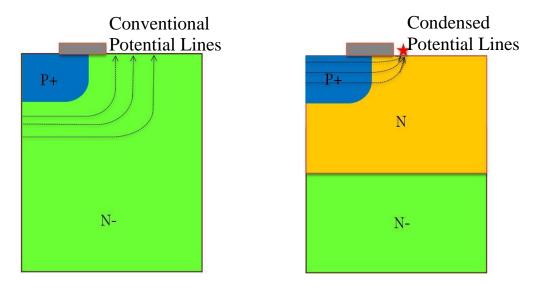

| Figure 1.6. Effect of highly doped topside N region on the potential lines around a surface field guard ring.             | 7    |

| Figure 1.7. (a) A UIS circuit and (b) the accompanying current and voltage waveforms seen in the DUT (MOSFET).            | 8    |

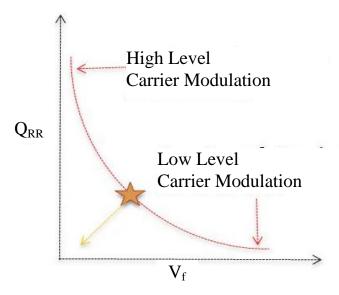

| Figure 2.1. Performance Curve illustrating the Vf-Qrr trade-off                                                           | 13   |

| Figure 2.2. RC-IGBT Structure.                                                                                            | 14   |

| Figure 2.3. Application circuit for the diode                                                                             | 15   |

| Figure 2.4. Device theory behind (a) conduction and (b) blocking modes of the diode [3]                                   | 16   |

| Figure 2.5. A typical diode reverse recovery curve.                                                                       | 17   |

| Figure 2.6. Device structure indication carrier flow for both a non-lifetime controlled and a lifetime controlled device. | 19   |

| Figure 2.7. Effect of carrier lifetime control on the reverse recovery charge                                             | 20   |

| Figure 2.8. Effect of electron radiation on leakage current of a conventional planar device                               | 21   |

| Figure 2.9. Effect of electron radiation on the reverse recovery charge of a conventional planar device                   | 21   |

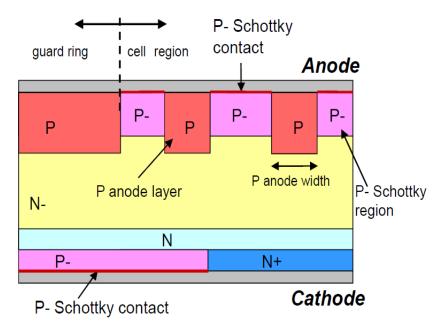

| Figure 2.10. Schottky Controlled Injection Diode [24].                                                                    | 24   |

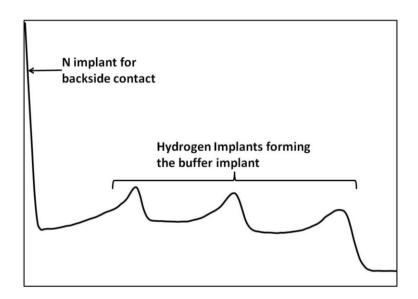

| Figure 2.11. Buffer formation and backside injection control using hydrogen implant                                       | 25   |

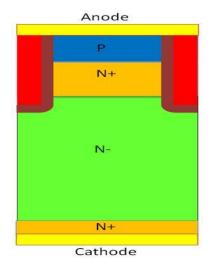

| Figure 2.12. Construction of the CIBH Diode [25].                                                                         | 26   |

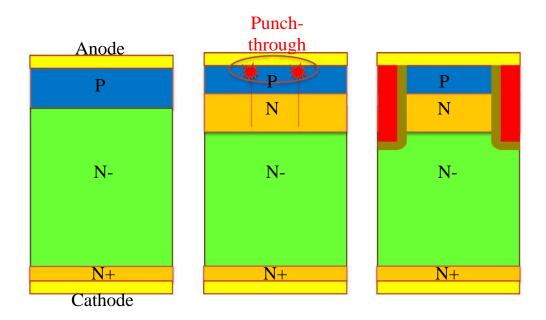

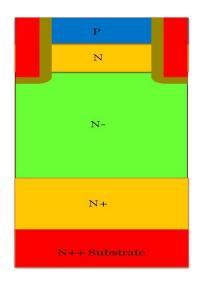

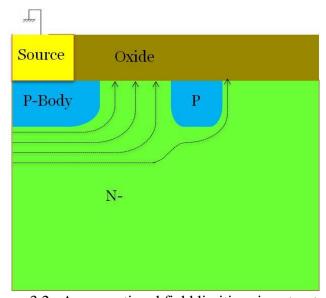

| Figure | 2.13. | Basic cell structure of the proposed trench shielded fast recovery diode                                                     | .27 |

|--------|-------|------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure |       | Effect of the polysilicon filled trench on the device avalanche capability pared to a conventional planar structure.         | .28 |

| Figure |       | Distribution of electrostatic potential lines around the trench and in the trench oxide.                                     | .29 |

| Figure |       | Impact Ionization point in the proposed structure which shows the region e avalanche occurs.                                 | .29 |

| Figure | 2.17. | Electric Field distribution in the structure.                                                                                | .30 |

| Figure |       | Doping Concentration Profile showing the effect the topside N heavy region on the injection from the P-base.                 | .32 |

| Figure | 2.19. | Starting epi structure profile for the diode.                                                                                | .33 |

| Figure | 2.20. | Process steps involved in forming the trench.                                                                                | .34 |

| Figure | 2.21. | Process steps showing formation of the trench liner oxide                                                                    | .35 |

| Figure |       | Process steps showing deposition of the heavily N-doped polysilicon in the h                                                 | .36 |

| Figure | 2.23. | Structure after P-Base implant and diffusion.                                                                                | .37 |

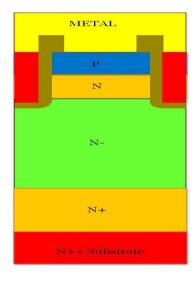

| Figure | 2.24. | Structure after topside metallization.                                                                                       | .38 |

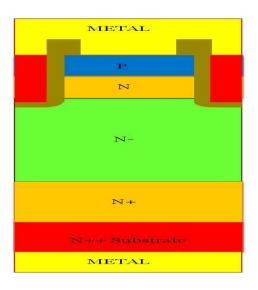

| Figure | 2.25. | Structure after backside metallization.                                                                                      | .39 |

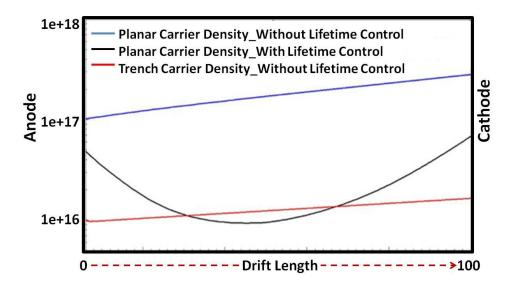

| Figure |       | Effect of lifetime and injection control on the catenary profile in the diode drift n.                                       | .40 |

| Figure |       | Measured Voltage and Current waveforms of the FRD during reverse recovery                                                    | .41 |

| Figure |       | Measured Idss values of conventional Electron Radiated Device and proposed ture at room temperature and higher temperatures. | .42 |

| Figure |       | Measured Qrr curves of proposed structure compared with a conventional ron Radiated Device at -40, 25 and 175°C.             | .43 |

| Figure | 3.1.  | JTE Termination schemes in a plane and planar p-n junctions [51]                                                             | .47 |

| Figure | 3.2   | Δ conventional field limiting ring structure                                                                                 | 18  |

| Figure | 3.4. A Trench filled metal plate termination for superjunction structures [60]                                                                                                    | 0          |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Figure | 3.5. A charge imbalance based termination scheme for superjunction devices5                                                                                                       | 1          |

| Figure | 3.6. An oxide filled trench based termination scheme for superjunction devices [60]5                                                                                              | 2          |

| Figure | 3.7. Basic building block of the proposed termination structure5                                                                                                                  | 3          |

| Figure | 3.8. Proposed termination scheme                                                                                                                                                  | 4          |

| Figure | 3.9. (a) Cross section of a single polysilicon filled trench and the buried guard ring, and (b) accompanying electric field                                                       | 5          |

| Figure | 3.10. Structure illustrating the addition of P implant during the trench etch phase5                                                                                              | 7          |

| Figure | 3.11. Final structure of termination unit cell after thermal drive                                                                                                                | 8          |

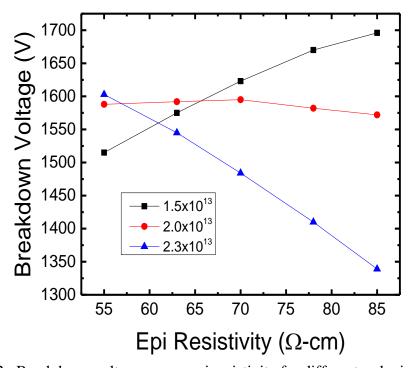

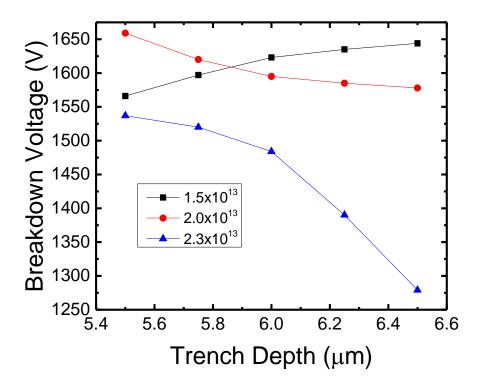

| Figure | 3.12. Breakdown voltage versus epi resistivity for different p-doping concentrations5                                                                                             | 9          |

| Figure | 3.13. Breakdown voltage versus trench depth for different p-doping concentrations6                                                                                                | 60         |

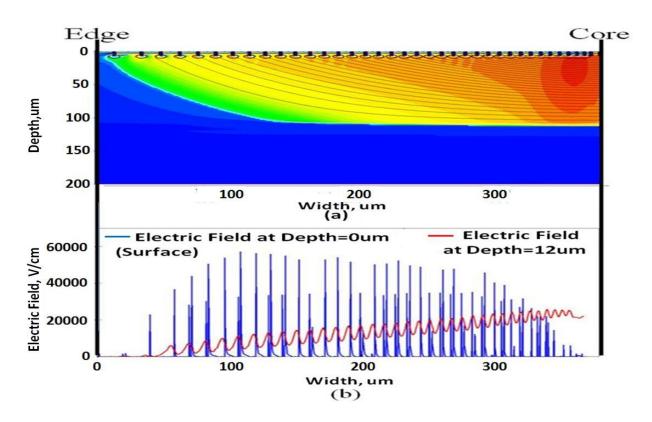

| Figure | 3.14. Different characteristics of the termination scheme are shown. (a) full termination with location of impact ionization hot spot and (b) distribution of the electric field. | 51         |

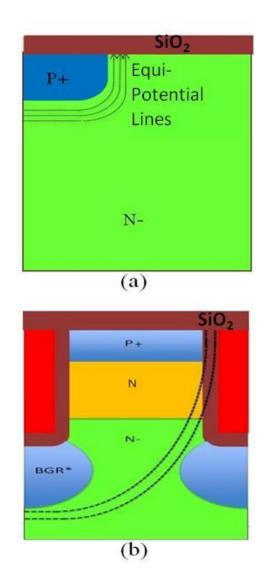

| Figure | 3.15. Comparison of the termination schemes and the shape of the electric potential lines for (a) planar FLR, and (b) trench structure.                                           | i3         |

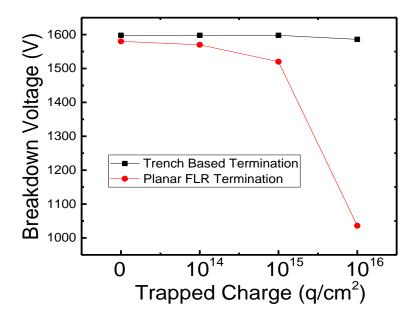

| Figure | 3.16. Breakdown voltage as a function of trapped oxide charge6                                                                                                                    | <b>i</b> 4 |

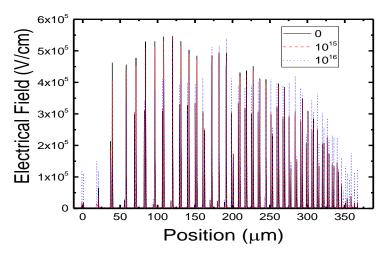

| Figure | 3.17. Effect of trapped oxide charge on the electric field distribution lines for the proposed trench based termination.                                                          | 54         |

| Figure | 3.18. Effect of trapped oxide charge on the electric field distribution lines for a planar FLR based termination                                                                  | 55         |

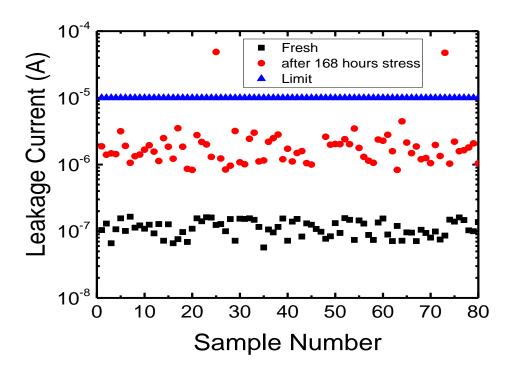

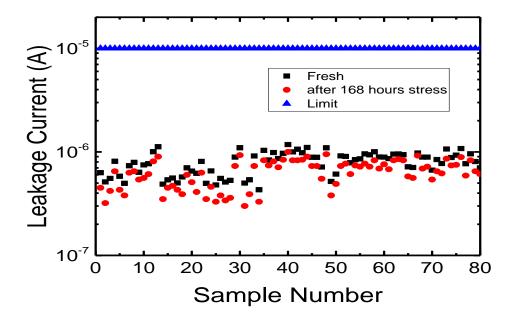

| Figure | 3.19. Leakage current reliability data for planar termination6                                                                                                                    | 7          |

| Figure | 3.20. Leakage current reliability data for trench based termination6                                                                                                              | 7          |

| Figure | 4.1. Simulated body diode core cells of a planar DMOSFET and a superjunction MOSFET                                                                                               | ′1         |

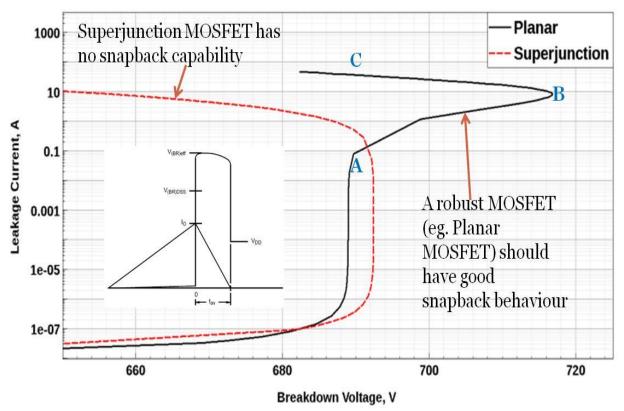

| Figure | 4.2. Simulated Breakdown Voltage I-V curve comparison between planar and superiunction MOSFET.                                                                                    | 1)         |

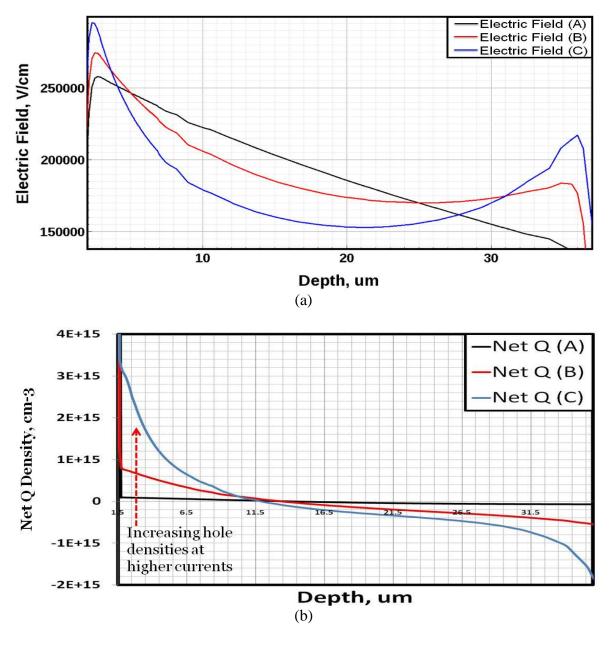

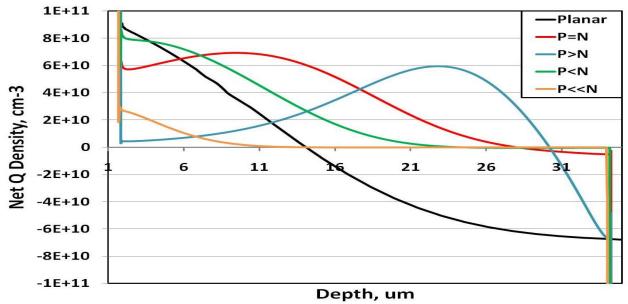

| Figure 4.3. Comparing the (a) electric fields and (b) net charge distribution for the planar MOSFET.                       | 73 |

|----------------------------------------------------------------------------------------------------------------------------|----|

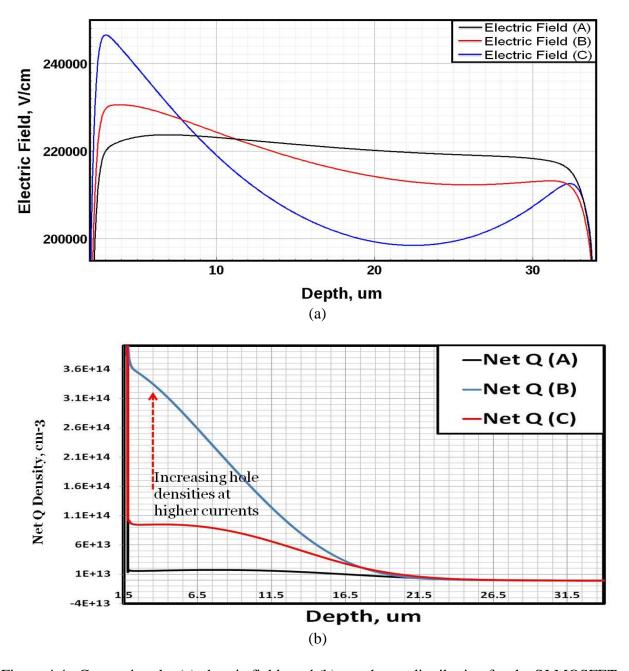

| Figure 4.4. Comparing the (a) electric fields and (b) net charge distribution for the SJ MOSFET.                           | 75 |

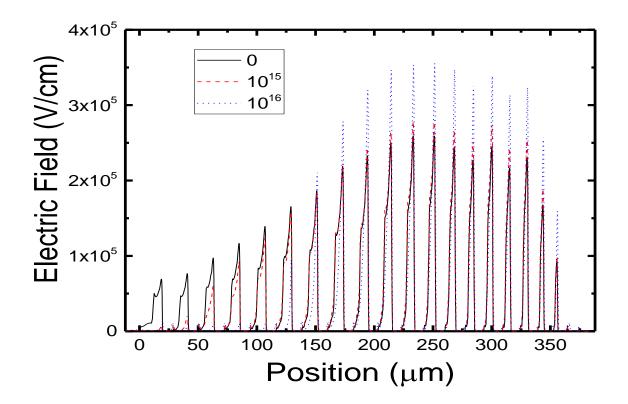

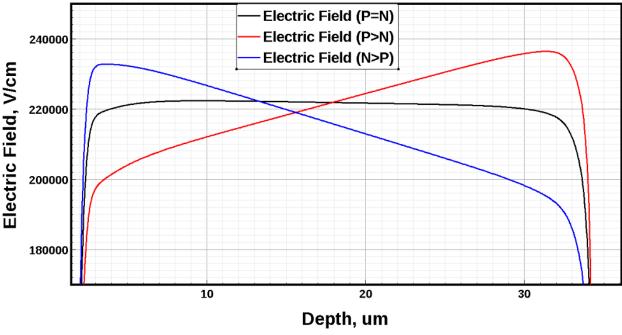

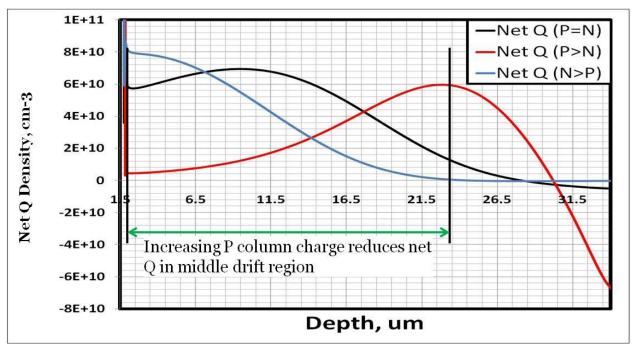

| Figure 4.5. Effect of charge imbalance on the electric field profile.                                                      | 76 |

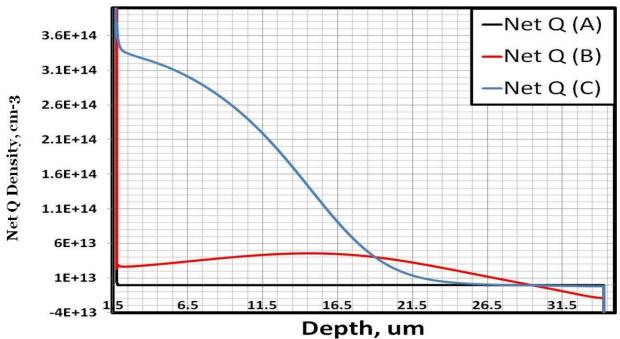

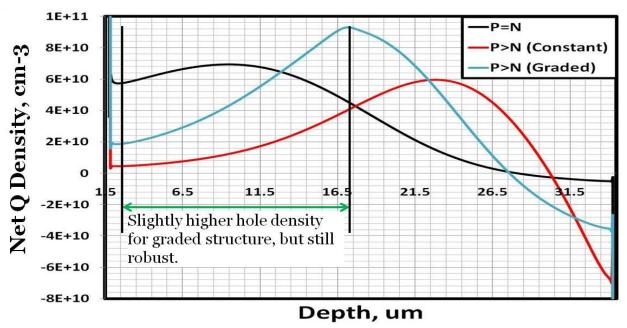

| Figure 4.6. Effect of charge imbalance on the net charge density.                                                          | 77 |

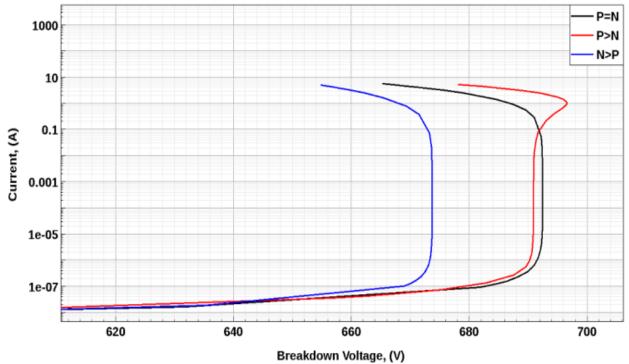

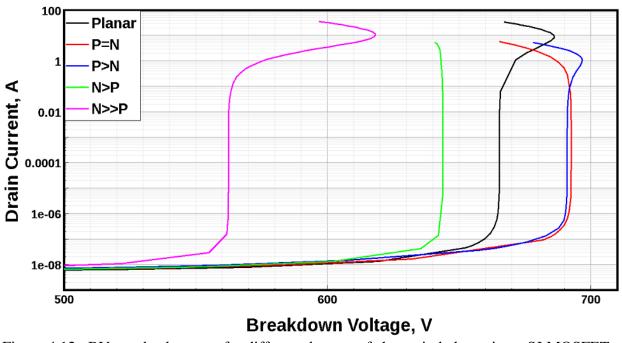

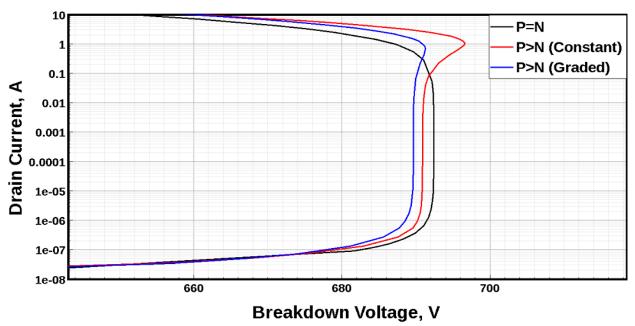

| Figure 4.7. Effect of charge imbalance on the BV snapback curves.                                                          | 78 |

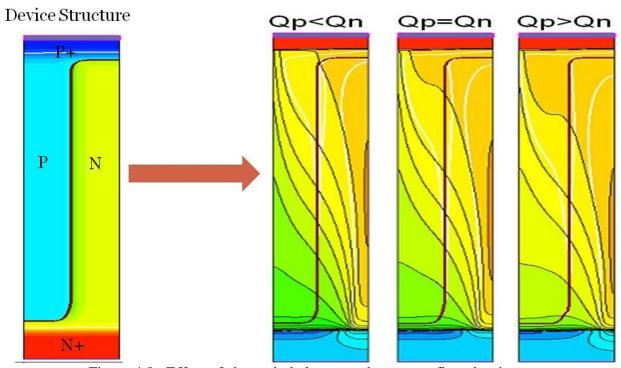

| Figure 4.8. Effect of charge imbalance on the current flow density.                                                        | 78 |

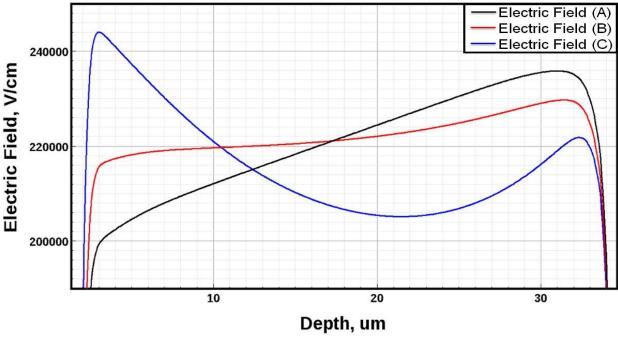

| Figure 4.9. Electric field profiles for a P heavy SJ MOSFET at different points on the BV snapback curve.                  | 80 |

| Figure 4.10. Net charge density distribution profiles for a P heavy SJ MOSFET at different points on the BV snapback curve | 80 |

| Figure 4.11. Net charge density distribution profiles for different degrees of charge imbalance in an SJ MOSFET.           | 82 |

| Figure 4.12. BV snapback curves for different degrees of charge imbalance in an SJ MOSFET                                  | 82 |

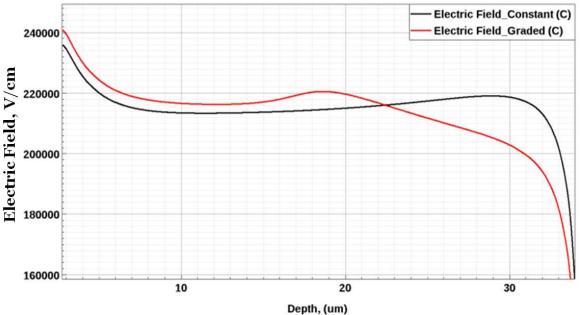

| Figure 4.13. Comparing electric field profiles in constant and graded P heavy SJ MOSFETs                                   | 83 |

| Figure 4.14. Comparing net carrier density distribution profiles in constant and graded P heavy SJ MOSFETs.                | 84 |

| Figure 4.15. Comparing BV snapback curves for constant and graded P heavy SJ MOSFETs.                                      | 84 |

| Figure 4.16. Summary of the trade-offs involved with designing a charge imbalanced SJ MOSFET for improved robustness.      | 85 |

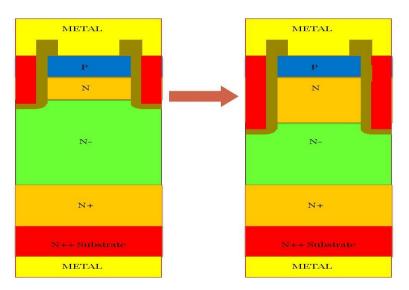

| Figure 5.1. Extension of the Trench MOS structure within the design for improved efficiency                                | 89 |

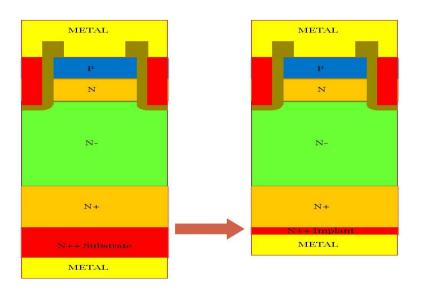

| Figure 5.2. Removal of substrate for backside injection control.                                                           | 90 |

# LIST OF TABLES

| <u>Table</u>                                                       | page |

|--------------------------------------------------------------------|------|

| Table 2.1. I <sub>RM</sub> and softness values of compared devices | 44   |

| Table 5.1. Comparison of different diode technologies              | 87   |

| Table 5.2. Comparison of different edge termination schemes        | 88   |

#### LIST OF ABBREVIATIONS

BGR Buried Guard Ring

BI Burn In

BJT Bipolar Junction Transistor

BV Breakdown Voltage

DUT Device Under Test

ER Electron Radiation

FLR Field Limiting Ring

FP Field Plate

FRD Fast Recovery Diode

GR Guard Ring

IGBT Insulated Gate Bipolar Transistor

JTE Junction Termination Extension

MOSFET Metal Oxide Semiconductor Field Effect Transistor

QRR Reverse Recovery Charge

RDYN Dynamic Resistance

SJ Super-Junction

UIS Unclamped Inductive Switching

VF Forward Voltage

# CHAPTER 1 INTRODUCTION

#### **Inductive Switching Circuit**

Power electronic systems, especially at high power levels, place a premium on system efficiency. Even a marginal shift in efficiency can greatly impact the system performance. It is for this reason that the power semiconductor devices which are commonly used in these systems are constantly upgraded in technology for better performance characteristics.

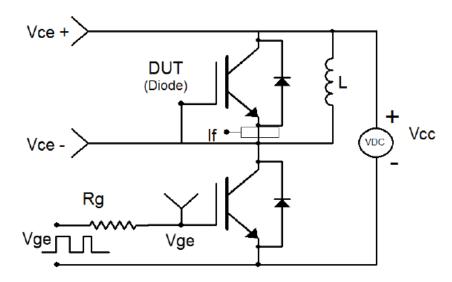

Figure 1.1. A Conventional Inductive Switching Circuit.

Figure 1.1 shows the commonly used switching circuit for most power systems, which happens to be the inductive switching circuit. The circuit is part of a half-bridge configuration, with a low side and high side switch, where they alternate between conducting and blocking mode. The semiconductor switches used in this circuit are conventionally either MOSFETs or IGBTs. Primarily, the circuit requires the high side device to have a free-wheeling diode.

When the low side FET is operational, the high side diode is in blocking mode. When the low side FET is turned off, the current through the inductor needs to cycle through the diode, thus putting the diode into conducting mode. While the MOSFET has an anti-parallel diode built into the structure, the presence of the P type drain in the IGBT prevents the IGBT from having the same. This necessitates the addition of a diode along with the IGBT when used in this configuration. This is also beneficial form a design stand-point because it allows the designed to individually optimize the diode performance to increase the overall system efficiency.

The Vf of the diode is crucial in determining the conduction losses, while Qrr is essential in determining the Eon of the low-side FET. This is illustrated in Figure. 1.2.

Figure 1.2. Switching waveforms in an Inductive Switching Circuit.

As seen in Figure 1.2, the reverse recovery current from the diode flows through the low-side IGBT. The voltage curve is controlled by the capacitance of the IGBT, but the amount of current

overshoot in the IGBT is determined by the diode. A smaller diode Qrr reflects in a lower Eon for the IGBT, thereby improving the overall system efficiency. A higher Qrr has the inverse effect.

#### **Charge Balanced Devices**

As mentioned earlier, the individual characteristics of the devices used play a huge role in determining the overall efficiency of the circuit. For this reason, there has been an increased shift towards using superjunction or charge balanced devices.

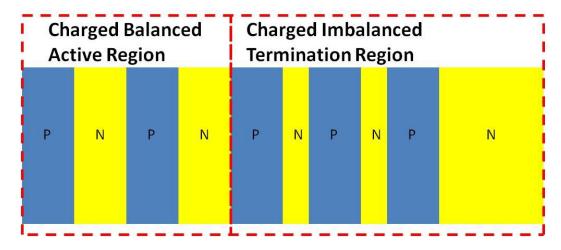

The concept of a charge balance is one that has been explored previously in [1]. The basic principle is to use alternating highly doped P and N columns to essentially generate a net intrinsic epi of negligible doping concentration. This way, the device can still support the requisite breakdown voltage, but due to the significantly higher N column doping concentration, can achieve significantly better performance specifications in most aspects.

The breakdown voltage is determined by the charge, depth of the drift region and the pitch of the alternating P and N columns. The basic structure is most commonly applied to MOSFETs, wherein they have the most benefit with regards to a BV-Rds-on trade-off, due to the increased N column doping concentration. The basic superjunction structure is as shown in Figure 1.3, along with the corresponding equation governing the charge distribution.

$$Net Q(y) = \int_{\mathbf{X}=\mathbf{O}} (N_D^+ - N_A^- + p - n) dx$$

$$\mathbf{X} = \mathbf{O}$$

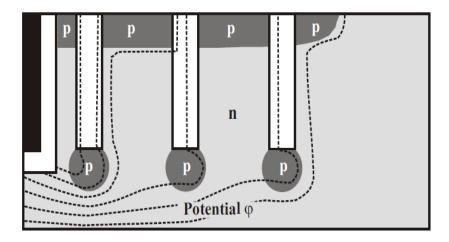

Figure 1.3. A conventional charge balance structure and the accompanying equation governing the net charge.

This concept can technically be extended to IGBT and FRD, but has a few issues which is outside the scope of this dissertation. The primary issue with using a superjunction structure in a diode is that increased P column doping would result in significantly higher carrier injection.

This increased carrier injection leads to a low diode forward voltage (Vf), but a severely degraded reverse recovery charge (Qrr).

We can still, however, apply the concept with a Trench MOS structure forming a partial charge balanced structure for the diode. The P column is replaced by a trench filled with heavily doped polysilicon and a thick liner oxide, with the polysilicon being connected to the ground. The

potential lines are supported by the liner oxide. This structure forms the basis for the diode and the termination scheme implemented for it. The basic cell structure is shown in Figure 1.4.

Figure 1.4. A partial superjunction epi with a Trench MOS structure on top.

This structure is also called the Trench MOS structure. The main idea being implementing a partial charge balance concept to the diode is to have the N region act as an injection control layer in the diode. This injection control is important because it helps achieve a better Vf-Qrr trade-off.

#### **High Voltage Edge Termination**

Since the diode makes use of the trench charge balance structure, the termination scheme follows suit. In a conventional vertical DMOS structure, the active area is biased at ground voltage, while the edge of die at the bus voltage. The purpose of an edge termination in a die is to help transition the voltage from the edge of the active area to the edge of the die, as shown in Figure 1.5.

Figure 1.5. Die layout in a package.

The high N concentration at the surface makes it difficult to implement a regular planar termination as mentioned above. For a conventional planar MOSFET, a simple structure like a guard ring termination is efficient. It alters the potential lines and terminates them at the surface. Given a peak silicon E-field on 3e5V/cm, the guard ring spacing can be adjusted to support the required BV. But in the proposed structure, as we showed earlier, this is more complicated. The high surface N charge makes it more difficult to implement a conventional edge termination where the field terminated in silicon because the electric field increases exponentially at the P-N junction. Also, a higher N charge can also punch-through the surface P concentration if the dose it low. While a higher P implant can prevent punch-through, it still cannot eliminate the higher electric field at the junction, and the field limitation of 3e5V/cm makes that more difficult.

Figure 1.6. Effect of highly doped topside N region on the potential lines around a surface field guard ring.

Most common terminations that involve the potential lines terminating in the surface are therefore hampered by the presence of the high surface N concentration and that electric field limit of Silicon. So, it is necessary to implement a novel termination scheme for the structure under consideration. As a result, a novel termination scheme for the same is studied and its enhanced reliability compared to a regular planar termination structure.

#### **Superjunction Ruggedness**

If the device used in the low side is a MOSFET, then the ruggedness of the device becomes critical. The measure of a MOSFET's ruggedness is made typically through its performance in an unclamped inductive switching circuit. In an unclamped inductive switching (UIS) circuit, the inductor is quickly turned off, and the resulting magnetic field causes the switch to sustain high

voltages. In the case of a MOSFET, this voltage buildup, coupled with the increased current flow, results in power dissipation which exceeds the rated value of the MOSFET. A commonly used circuit is shown in Figure 1.7.

Figure 1.7. (a) A UIS circuit and (b) the accompanying current and voltage waveforms seen in the DUT (MOSFET).

In the UIS test, the MOSFET can undergo two modes of failure, active and passive. While the active mode is caused by the latchup of the bipolar junction transistor (BJT) in the MOSFET, the passive mode is caused by external factors when the chip temperature reaches a very high value, causing thermal runaway. For the purposes of this dissertation, we focus exclusively on the active failure mode which is caused by the avalanche currents from the bipolar latchup.

During the UIS mode, the current flowing through the parasitic resistance from the p region causes a voltage drop from the conduction current, thus activating the parasitic BJT. If the P-base dose is low, then the effective dopant resistance is high, which in this case happens to be the base resistance of the BJT. As the current through the MOSFET increases during the UIS avalanche

period, the voltage drop across the parasitic base resistance triggers the parasitic BJT. Once the parasitic BJT is triggered, the BJT is on a self-sustaining mode wherein it results in a thermal runaway of the MOSFET, eventually causing MOSFET failure.

The maximum current allowed by the MOSFET before failure is dependent on the size of the inductor used in the circuit. So, based on the inductor used in the circuit, we can characterize both the maximum voltage seen by the MOSFET and the maximum energy dissipation in the MOSFET (Eas). The equations for the same are as given by the following:

$$V=L(di/dt)+V_{DD}$$

$$Eas=(1/2)*L*I^2$$

MOSFETs are generally characterized by the maximum energy dissipation in the UIS mode as a reflection of their ruggedness.

The peak energy dissipation occurs at time t=0, when the MOSFET experiences peak current and voltage levels. This peak energy point can be captured in the avalanche snapback curves of a MOSFET. The avalanche snapback property in a MOSFET has a similar trigger mechanism as the UIS failure, i.e. turn-on of the parasitic BJT.

If the MOSFET in question happens to be a superjunction MOSFET, then the robustness of the device becomes even more critical. While a fully charge balanced, superjunction MOSFET

offers many advantages, it does show degradation in a couple of areas, specifically the diode reverse recovery characteristics and its ruggedness. While the diode characteristics can be somewhat controlled through some sort of lifetime control, a pure SJ device has inherently weak ruggedness due its structure.

In the superjunction MOSFET, the superior Rdson of a unit cell due to higher N column doping concentration results in a lower effective Rds\*A figure of merit. So, for the same Rds-on, the superjunction MOSFET has a smaller chip size compared to a planar MOSFET. A smaller chip area results in a lower energy handling capability. Another detail to consider is that the increased doping concentration of the N column leads to a much higher carrier density at the surface. The increased carrier density leads to a higher current when the device avalanches during the UIS test, leading to a larger IR drop across the parasitic resistor triggering the intrinsic bipolar transistor.

While the UIS test is one common way to test the ruggedness of the MOSFET, another approach for verifying the same is the BV avalanche test. If current is continually pushed through the MOSFET even after it enters the avalanche mode, the avalanche current will eventually trigger the bipolar BJT. This can however be influenced by the column charge. By introducing a charge imbalance in the SJ structure, we can alter the electric field and the carrier density profile to alter the avalanche breakdown property of the MOSFET.

# CHAPTER 2 FAST RECOVERY DIDOE

#### Introduction

While the previously mentioned inductive switching circuit is the common topology, it is usually component of the half-bridge rectifier. Half-bridge rectifiers usually form the back-bone of modern power electronic systems. In most of these applications, the circuit is hard-switched, where the forced commutation of the diode is crucial in determining the switching losses.

The rectifier usually has two semiconductor switches which conduct alternately. The previously mentioned inductive switching circuit is predominantly controlled by the switches used in the circuit. The device used and the corresponding topology greatly determines the efficiency of the system. The low and high side switches are most commonly implemented in one of two ways.

- MOSFET: This is usually the case if the low side device is a MOSFET too. In this case, the anti-parallel diode of the MOSFET is the diode on the high side. The MOSFET is gradually being replaced by the IGBTs at the higher voltage ranges (>600V).

- <u>IGBT + Fast Recovery Diode</u>: This is usually the solution if the low side device is an IGBT. Since IGBTs structurally do not have an internal body diode, they are usually copackaged with an external diode to allow for current conduction when the low side is switched off. The exception in this case is when an RC-IGBT, but there is a severe drop-off in the diode performance in this instance, as explained in detail later. This solution usually applies to applications with voltage ranges >600V.

The reason why IGBTs are the preferred choice for higher voltage ranges is because of the advantageous operating principle. Due to the fact that the IGBT is a bipolar device compared to the unipolar nature of the MOSFET, the conduction energy of the IGBT at higher operating voltages is lower. Beyond an operating voltage of typically 600V, the Vce(sat) of the IGBT has a better performance trade-off compared to the Rds-on of a comparable MOSFET.

The issue with using an IGBT however is the lack of an anti-parallel diode. In a MOSFET, the P+ source and the N+ drain inherently form a diode. The diode is basic and will have high injection and consequently a large Qrr. While this is a by-product of the MOSFET structure, the IGBT unfortunately does not have the same advantage due to the P+ drain in the structure. This creates a problem when the IGBT replaces the MOSFET in a switching circuit for the higher voltage applications. To address this, the IGBT is usually co-packaged with a standalone fast recovery diode (FRD), which forms the basis of this chapter.

In case of the MOSFET, as mentioned earlier, the injection characteristics are difficult to modify since they are set based on the MOSFET design. In case of the IGBT, since the diode characteristics can now be de-coupled from the main switching device, the diode can be engineered individually for much better switching characteristics and increased efficiency. A diode's performance is ideally characterized by the Vf-Qrr trade-off. A lower Vf leads to a higher Qrr, and vice-versa. This can best be explained using the Vf-Qrr curve.

Figure 2.1. Performance Curve illustrating the Vf-Qrr trade-off.

For ideal diode characteristics, we would like to have minimum  $V_f$  to go with minimum  $Q_{rr}$ . The  $V_f$  of the diode comes into play during the conduction mode of the diode, while the  $Q_{rr}$  is essential during the switching mode. Both these characteristics are controlled by the amount of carrier injection in the diode, both from the cathode and anode, due to the FRD being bipolar in nature.

There is a way to introduce diode characteristics in an IGBT. This structure is commonly known as the Reverse Conducting IGBT (RC-IGBT) [2]. In an RC-IGBT, there is an anode short on the cathode side wherein some of the P+ region is killed in favour of an N+ contact. This once again introduces the anti-parallel diode structure into the IGBT. The basic structure of an RC-IGBT as shown in Figure 2.2 [2].

Figure 2.2. RC-IGBT Structure.

The RC-IGBT has its share of advantages and disadvantages. On the plus side, the RC-IGBT is more compact than an IGBT+FRD combinations, and consequently more economical and cost effective. It however has limitations. As seen with the MOSFET, the injection is largely dictated by the IGBT design criteria, so optimizing the diode performance in the structure has limitations with regards to the IGBT parameters. When designing the anode short, the ratio of N+/P+ contact directly impacts both the IGBT and FRD characteristics. Also, if the N+ contact dose is insufficient or is not sufficiently activated, it adversely affects the Vf of the device. For industrial motor drives which require optimum Vf and Qrr, targeting the ideal Vf-Qrr trade-off point becomes difficult.

It is for this reason that a standalone FRD is preferred for applications where the efficiency is paramount. The diode specifically comes into play when the low side IGBT is turned off. At this point, the current path needs to be maintained. So, the current cycles through the diode. When

the low side IGBT is turned on again, the diode needs to turn off as soon as possible so that the current can flow through the IGBT again.

The switching losses in the circuit are calculated when the devices transition between states. The high side current which commutes through the diode now flows through the low side device when it turns on. Since the diode is bipolar, the switching mechanism inside the diode is a function of how the P-N junctions are designed. The commonly used application circuit which forms the basis for the half bridge rectifier is the inductive switching circuit, as shown in Fig 2.3.

Figure 2.3. Application circuit for the diode.

The high side diode in this application supports the inductor current when the low side IGBT is switched off. This means the diode is in the ON state, and conducts the current. When the low-side IGBT is turned on again, the diode is forced to change to an OFF-state, but the current being conducted takes a little longer to reduce to 0 because the carriers need to deplete from the drift

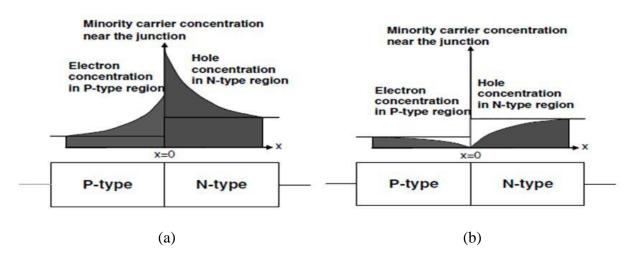

region. A pictorial representation the device physics which form the operating principle behind the diode commutation property is shown in Figure 2.4 [3].

Figure 2.4. Device theory behind (a) conduction and (b) blocking modes of the diode [3].

For the diode to switch from the On to Off state, the charge distribution in the device needs to change. As shown above, the density of the minority carriers is the main parameter governing the charge distribution in the structure, as well as the rate it dissipates. The carrier density itself is a function of the background doping concentration of the N-region and the area of the diode.

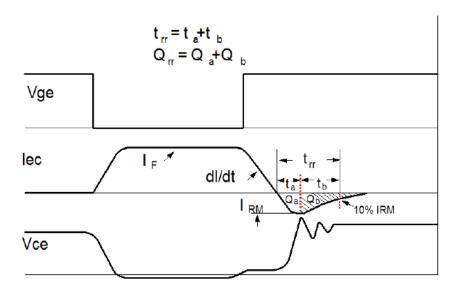

The breakdown in the current flow is shown in Figure 2.5. When the low side FET is turned on, the current in the FET starts rising once the gate voltage exceeds the threshold voltage (Vth). This increase in current corresponds with the decrease in diode current, maintaining the constant inductor load current at all times.

Figure 2.5. A typical diode reverse recovery curve.

The different circuits used to characterize the diode performance is mentioned in [4], and the diode behaviour duing the reverse recovery stage is explained in [5]-[8]. The total reverse recovery time (Ta+Tb) determines the total switching losses during reverse recovery. The smaller the net charge, the lower the switching losses. While the di/dt parameter is a circuit characteristic, the Irm, ta and the are determined by the diode structure. A lower carrier injection leads to a smaller Irm, leading to a smaller ta, and inturn results in a faster discharge of the carriers during the the phase. The theof the curve can also be influenced by the adding a buffer region, which tends to act as a carrier layer and delays the removal of carriers form the drift region. This increases the softness factor (tb/ta), which increases the switching losses slightly, but at the same time greatly reduces the probability of voltage ringing during switching. Ringing due to a fast di/dt slope during the the phase can cause device failure if the overshoot exceeds the rated avalanche breakdown voltage.

Conventionally, the easiest way to control this reverse recovery charge is through carrier lifetime control. This can be achieved through multiple methods, but the core purpose of this approach is to affect the natural lifetime of the carriers so as to control the amount of carriers that need to be depleted from the drift region when the diode enters a reverse bias state. The lower the amount of carriers to be flushed out, the faster the diode depletes during turn off. This results in a reduction of the net Qrr.

#### **Prior Art**

Given the proliferation of high power systems and the increased need for their efficiency, various concepts for improving the diode performance have been studied before. These can be broadly classified into two primary groups:

- External Lifetime Control: Under this category, the diode structure used is mostly a

regular planar structure, but uses external lifetime control techniques like electron

radiation and proton radiation to control the recombination rates of the carriers.

- Injection Control: Under this category, the diode structure itself serves to control carrier injection and improve the Vf-Qrr trade-off.

The earliest innovations in improving the diode characteristics pertain to external lifetime control, while the structural improvements are a lot more recent. While both display markedly improved characteristics at room temperature (RT), external lifetime control techniques do not hold at high temperatures since the defects are annealed away, causing the carrier lifetime control to revert to normal.

# External Lifetime Control

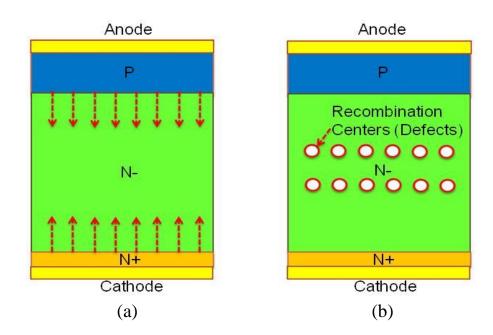

There are multiple ways to implement lifetime control in a diode. Some of the common methods include electron radiation, proton radiation and heavy metal (gold) radiation [9]-[13]. The basic concept involves introduction of defects into the silicon which act as recombination centers for the carriers, as shown in Figure 2.6

Figure 2.6. Device structure indication carrier flow for both a non-lifetime controlled and a lifetime controlled device.

#### Electron Radiation

The most common method of lifetime control is electron irradiation. In this method, the device is bombarded with electrons at high energy. This introduces physical defects in the silicon, which usually occur in the drift region. The defects in turn act as recombination centers for the carriers, thus limiting the amount of uncombined carriers in the region. The higher the energy at which the electrons are irradiated, the more defects formed in the Silicon, leading to an even larger

decrease in the carrier lifetime and the reverse recovery charge. This can be shown in the following figure.

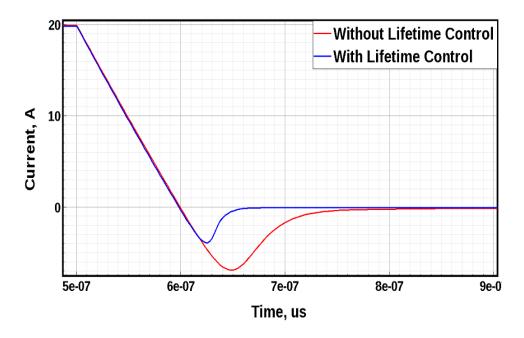

Figure 2.7. Effect of carrier lifetime control on the reverse recovery charge.

As clearly seen in Figure 2.7, carrier lifetime control leads to a faster recombination of the holes and electrons in the drift region. A faster recombination results in a lower Irm, and a lower Tb. This significantly lowers the Eon of the low side MOSFET, thereby increasing the system efficiency.

While this approach is quite common and widely used, there are many issues with electron irradiation. Firstly, the amount of defects introduced leads to higher leakage level. Secondly, at higher temperatures, some of the defects get annealed away, returning the carrier lifetimes closer to their intrinsic values. The Qrr respectively increases as the defects get annealed away, leading

to higher Qrr at higher operating temperatures. This is especially an issue for applications which require the device to operate at higher temperature ranges exceeding 150C.

Figure 2.8. Effect of electron radiation on leakage current of a conventional planar device.

Figure 2.9. Effect of electron radiation on the reverse recovery charge of a conventional planar device

Thirdly, while the electron irradiation decreases the Qrr at room temperature, there is a corresponding increase in the Vf. While this does not play a role in the switching losses, it does

play a role when the diode conducts, increasing the heat dissipation within the device. This again harms the overall efficiency of the system.

The higher the electron radiation energy, the more the change in the Vf and the Qrr specs, but the more severe the degradation in the leakage and the high temperature characteristics

## Gold Diffusion

Another approach to lifetime control is through gold diffusion. This approach was commonly used previously, but has multiple issues associated with it [9]. Gold being heavier does not diffuse deep enough in the silicon, so the defects tend to be localized close to the contacts. Also, the recombination centers arising from the Gold diffusion is in the center of the silicon energy gap, causing a significantly higher leakage current.

# Platinum Diffusion

Platinum diffusion is another option for lifetime control using heavy metals. While it does show better leakage characteristics, it demonstrates much more degraded high temperature reverse recovery characteristics [9].

There are other lifetime control processes used to varying degrees, which are explained in detail in [14]-[22]. All the above mentioned lifetime control techniques operate on the same principle, that of introducing physical defects into silicon which act as recombination centers for the carriers, hence reducing their lifetime and the net charge during commutation. They show varying degrees of improvement with regards to the reverse recovery characteristics of the diode,

but with invariably similar penalties of higher leakage current and forward voltage, Vf. The effect of a process like electron radiation is explained in [23].

# **Injection Control**

While the above mentioned methods address the carrier density using external lifetime control techniques, they don't actually improve the Vf-Qrr trade-off. They only change the operating point along the Vf-Qrr curve. Diode structures with inherent injection control, on the other hand, seek to limit the actual amount of carriers which are modulated in the device, thereby greatly reducing or completely eliminating the need for any extra lifetime control.

Reducing the Qrr in the diode through injection control is described in [24]-[28]. The operating principle for this category of diodes is essentially similar. A form of localized injection control, implemented either on the anode or cathode side, controls the amount of carriers injected into the drift region. Some of the popular ones are as listed below:

# Schottky Controlled Injection Diode

This structure controls carrier injection though schottky contacts on both the anode and cathode side. By killing parts of the P-anode injection through P-schottky regions, the diode sees reduced hole injection form the anode side. On the cathode side of the diode, the structure uses a transparent anode structure, again by killing some of the N+ cathode injection by replacing parts of it with a P-schottky contact. The structure is shown below in Figure 2.10 [24].

Figure 2.10. Schottky Controlled Injection Diode [24].

While this structure helps realize a flat carrier profile, it still requires significant backside engineering. Also, the N+ contact might have activation issues, which means the backside contact might have a few issues. Also, while schottky diodes offers great trade-offs with Vf and Qrr due to almost instantaneous recovery, they are generally not very compatible with high power systems.

## Hydrogen Implant

A commonly used method is that of Hydrogen Implant, as mentioned in [28]. In this approach, a multi-step hydrogen implant helps form the buffer and the backside collector implant. The basic structure for a device with Hydrogen implant is as shown below in Figure 2.11

Figure 2.11. Buffer formation and backside injection control using hydrogen implant.

This approach is beneficial for multiple reasons. Apart from the injection control afforded by the hydrogen implants, the three-tiered hydrogen implants are different energies also act as the buffer for the structure. This is also used for IGBT structures, where the backside implant for contact purposed is a P-type implant. While efficient and popular, this approach is more expensive. Hydrogen implants are more expensive to implement, and usually have restrictions with regards to the wafer handling capabilities for the equipment.

# CIBH Diode

Another form of injection control was also implemented in a structure called the CIBH diode [25]. In this structure, the injection control is performed by patterned implants of a P type dopant like boron on the backside to control any injection from the N type cathode. The structure is shown in Figure 2.12 [25].

Figure 2.12. Construction of the CIBH Diode [25].

While extremely effective, the CIBH diode again comes with its share of issues. The CIBH structure also needs a thin wafer due to backside processing involved. So the structure is extremely sensitive to the backside process conditions, including variations in the backgrind thickness of the wafer and the amount of N+ concentration required to form a good ohmic contact with the backside metal.

Other structures used for injection control are mentioned in [29-[39], including the commonly used Merged PiN Schottky Diode, Static Shielding Diode, Soft and Fast Recovery Diode and the SPEED Diode. All these diodes seek to improve the Vf-Qrr trade-off inside the diode by directly addressing the carrier injection within the diode. They offer improved performance of the diode at room temperature, without the side-effects of degraded leakage and increased Qrr at high temperatures.

# **Trench Shielded Fast Recovery Diode**

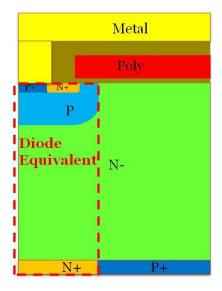

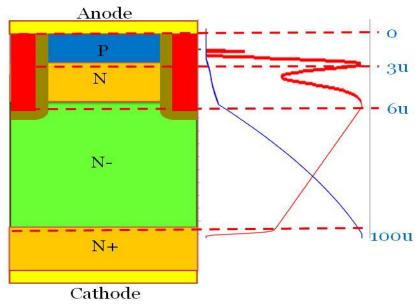

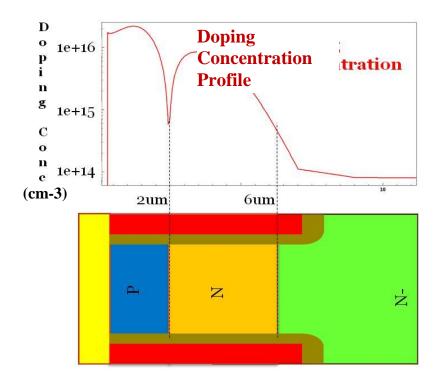

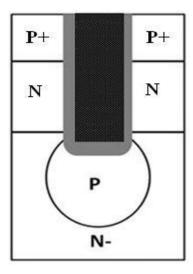

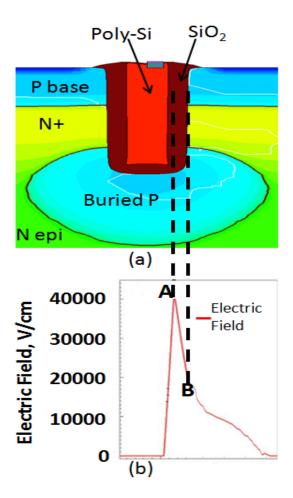

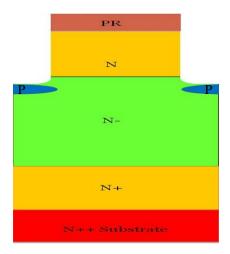

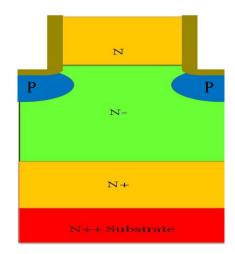

Along the same lines, a Trench Shielded Fast Recovery Diode [40], [41] is proposed. The basic structure for this is as shown below in Figure 2.13. The basis of the structure is the topside injection control. In this case, the N+ region as shown in the figure helps control the injection from the topside P implant. If used as a standalone concept, this would lead to a punch-through effect. So to achieve this, we have to use a trench MOS, charge balance structure where the grounded polysilicon filled trench helps charge balance the heavy N+ region. In essence, this is similar to trench based super junction structure on top.

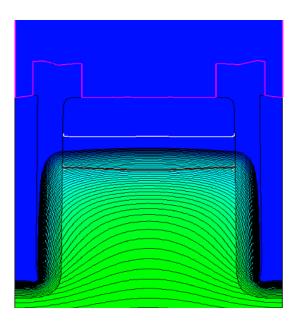

Figure 2.13. Basic cell structure of the proposed trench shielded fast recovery diode.

If we did not have the super junction structure on top, the N+ concentration required to achieve the desired level of injection control would easily deplete the P region and punch-through, leading to almost instant breakdown. This can clearly be illustrated in the following Figure 2.14. By inserting a polysilicon filled trench extending unto the depth of the N+ region at regular intervals (determined by the amount of charge in the N+ region), we can extend the ground

potential deeper into silicon. This helps maintain a higher breakdown potential of the device while enabling the N+ region help suppress injection from the P without punching through.

Figure 2.14. Effect of the polysilicon filled trench on the device avalanche capability compared to a conventional planar structure.

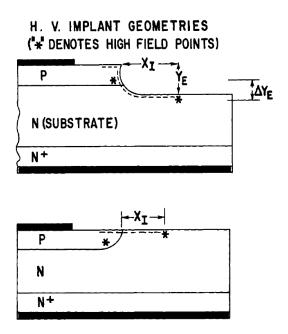

Our initial design is for an application voltage of 1350V. This however can easily be implemented for lower breakdown regions like 650V applications. The higher or lower voltage rating is achieved by changing the N- drift region thickness and resistivity. Meanwhile the topside partial superjunction is the same. This means all diodes with this structure share similar electric filed profiles and impact ionization points. The electric potential lines and impact ionization points for the structure are as shown in Figures 2.15 and 2.16.

Figure 2.15. Distribution of electrostatic potential lines around the trench and in the trench liner oxide.

Figure 2.16. Impact Ionization point in the proposed structure which shows the region where avalanche occurs.

The initial step involved in designing this diode was the decision to use a soft punch through diode. This would involve adding a buffer at the backside to help terminate the electric field.

This buffer also serves the additional purpose of adding a bit of softness to the Qrr curve of the diode. The next step was to determine the resistivity and thickness of the diode required to support this high a voltage. Considering a tolerance of an additional 20% for a 1350V diode, the design would have to support a voltage in excess of 1620V. Through simulation, a thickness of 105um with a resistivity of 85ohm-cm was arrived at. The electrostatic potential and electric field for this is shown below in Figure 2.17.

Figure 2.17. Electric Field distribution in the structure.

Focussing exclusively on the charge balance region on top, we observe that the trench MOS structure successfully helps shift the peak electric field deeper into silicon, thus alleviating the stress at the P-N junction and helps achieve the intended injection control without sacrificing the breakdown. The peak electric field at the base of the trench is supported by the thickness of the liner oxide used. The liner oxide needs to be thick enough to support the potential lines in the

structure because this is the region where the maximum impact ionization takes place in the structure.

It is critical that the trench extend at least till the depth of the N+ region. If the trench is not as deep, the heavier N+ underneath the trench bottom will result in impact ionization before the desired breakdown voltage is reached. The width of the trench, thickness of the liner oxide and charge in the N+ determine the pitch of the structure. This again was arrived at 6um through simulation. If the N+ charge is increased, the liner oxide thickness is increased accordingly to accommodate the additional potential lines. But for a given trench width, the thickness of the liner oxide has an upper limit. In this case, the pitch would have to decrease to allow for the same.

Through simulation, the thickness of the topside N+ region was arrived at 4.5um for the desired amount of injection control. Accounting for the diffusion of the N+ charge into the N- drift region, a trench depth of 6um, with a width of 2.5um and a liner oxide thickness of 6.5um was deemed to be optimal.

Even though the trench MOS structure supports a majority of the diode breakdown, the P base still needs to have a minimal charge to prevent punch-through. The resulting doping profile is shown in Figure 2.18.

Figure 2.18. Doping Concentration Profile showing the effect the topside N heavy region has on the injection from the P-base.

## **Fabrication**

The process steps involved in creating this structure are as follows:

## Step 1: Epi Growth

The first step is to grow the drift region epitaxial layer as decided through design. The starting material is an Arsenic substrate with resistivity <.003 ohm-cm. The subsequent epitaxial growth for the drift region is carried out in a high pressure chamber at a temperature of 1100C. The first layer to be grown is the buffer region. There are two ways to design the buffer as desired in the structure:

• Implant from the backside and apply a thermal cycle to diffuse the N type dopant deep enough to form the desired buffer layer.

• Grow the N+ buffer as part of the drift region growth.

Implanting the buffer from the backside would involve using a thin wafer without the substrate. For our purposes, we retain the substrate on the backside. So, we grow the buffer region, with a thickness of 10um and resistivity of 0.5ohm-cm. The thickness and resistivity of the buffer region are decided based on the amount of softness required in the Qrr curve.

After the buffer region is grown, the drift region epitaxial layer is then grown, based on the design target for the breakdown voltage. For a higher breakdown voltage characteristic, the drift region needs to be thicker and have a lower resistivity since it supports the bulk of the electric field. This is worked out to be around 105um thick with a resistivity of 55 ohm-cm.

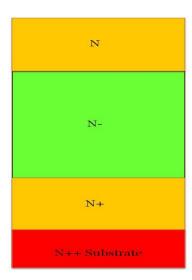

Figure 2.19. Starting epi structure profile for the diode.

Once the drift region is grown, the topside N region is grown. The thickness and resistivity of this region is dictated by the depth and width of the trench, and more critically the thickness of

the liner oxide in the trench. The principle behind this was discussed in the previous chapter. For this structure, the specifications of the topside N heavy region are 4.5um thickness and 0.5 ohm-cm resistivity. The resulting epi structure is as shown in Figure 2.19:

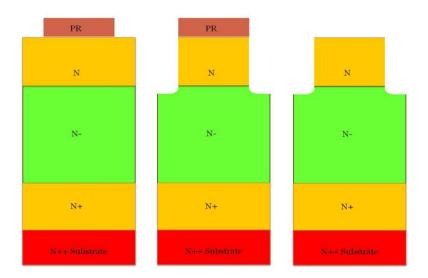

# Step 2: Trench Etch

The next step is to form the trench. This is done by first covering the epi structure by Photo-Resist. Following that, we use a patterned mask to expose selective areas where we need to etch the trench. The exposed PR is then chemically washed away and we implement a chemical etch process wherein a 6um deep etch is made in Silicon. After the etch is completed, the remaining PR is washed away. This results in a structure as shown in Figure 2.20.

Figure 2.20. Process steps involved in forming the trench.

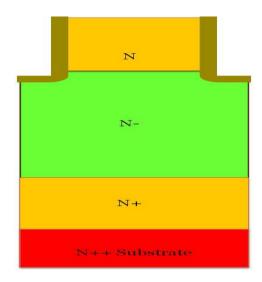

#### Step 3: Thermal Drive

Once the trench etch is completed, the next step is for a thermal cycle. This step is required for two reasons:

1. Grow the trench liner oxide to support the required breakdown voltage. The thickness of the liner oxide depends on the resistivity of the N+ top epi region grown and the pitch of the device structure. The optimum oxide thickness for this application was found to be ~6700A. The liner oxide thickness is essential for the charge balance region in the diode. A smaller liner oxide thickness is insufficient to support the electric field at that location. On the other hand, if the oxide is much ticker than expected, the amount of polysilison required for shielding is reduced. This again would reduce in a BV drop. This is shown in Figure 2.21.

Figure 2.21. Process steps showing formation of the trench liner oxide.

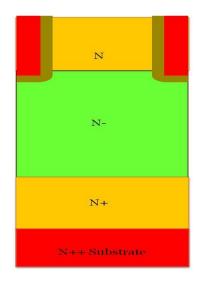

## Step 4: Polysilicon Deposition

After the trench liner oxide is grown, the N++ doped polysilicon is then deposited on the wafer. Since the polysilicon is desired only in the trench, after deposition, the surface polysilicon is etched away. After the etch step, a CMP (Chemical Mechanical Polarization) step is down to smooth out the silicon surface. This removes any surface irregularities that occurred as a result of the etching process. The final structure looks as shown in Figure 2.22:

Figure 2.22. Process steps showing deposition of the heavily N-doped polysilicon in the trench.

# Step 5: P-Base Implant

Once the basic epic structure is grown, the next step is to implant the P-base dose. The dose is dictated by 3 factors:

- The target forward voltage of the diode, Vf. The implant dose controls the amount of hole injection into the drift region.

- The target breakdown voltage of the diode. The resulting P base concentration should be enough to prevent the topside heavy N region from punching through and maintain the target breakdown voltage, which in this case exceeds 1600V.

- The contact resistance of the topside Metal contact. The amount of Boron at the surface plays a huge role in determining the contact resistance after metallization.

A higher P concentration at the surface results in a much lower resistance, thereby leading to faster injection.

Taking the above-mentioned factors into consideration, the boron implant specification of 6.5e12 @ 480 KeV was arrived at through TCAD simulations, followed by a thermal cycle @1150C for 60 minutes to diffuse the boron enough to support the required BV. Figure 2.23 shows the structure at the end of this process step.

Figure 2.23. Structure after P-Base implant and diffusion.

# Step 6: Topside Metallization

The next step is to form the metal contacts to the P base (Anode). To do this, we first need to use a mask layer to establish where the metal will contact the silicon. In this case, we will form a metal contact to both the silicon between the polysilicon filled trenches, and the polysilicon in the trench itself. But we cannot form a blanket metal contact because that could create some of the liner oxide to get etched away and cause a metal spike in the silicon-oxide junction. If the metal spikes into the junction and goes deeper into the silicon, the current flow will bypass the P-base and go through the metal, which would lead to a reduced breakdown. So the contact

opening is to be established only at the silicon and the polysilicon regions. Figure 2.24 illustrates this process step.

Following this, the Metal is then deposited. In this case, the metal would be an Aluminum mixed with Silicon so as to form a good low resistivity contact with the silicon surface. The low resistivity is important, because if the metal contact to the silicon is insufficient, the injection from P-base is minimal, resulting in a much higher Vf.

This is also a consideration for deciding on the P-base dose. The P doping concentration at the surface where the metal contacts the silicon is also critical in determining the quality of the contact. A low P concentration reduces the contact resistivity. The energy of the P-implant also plays a role in this scenario. A higher energy implant shifts the profile deeper into the silicon, reducing the amount of P in the silicon. So there is a trade-off between the depth of the P-N+ junction and the doping concentration of the P at the surface.

Figure 2.24. Structure after topside metallization.

## Step 7: Backside Metallization

Once the topside is processed, the wafer is flipped and background to a thickness of ~200um. Since the wafer around that thickness is usually just the substrate, any variation in the backgrind would not cause a major issue. After the backgrind, we implant an N+ dose to help ensure a good, low resistivity contact with the back-metal. The metal used for the backside drain contact is usually a combination of Ti+Ni+Ag. The final structure is then showed in Figure 2.25.

Figure 2.25. Structure after backside metallization.

# **Impact of Injection Control**

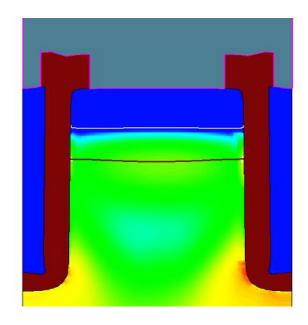

As mentioned earlier, the whole reason for injection control was to avoid the pitfalls associated with electron irradiation. The proposed structure seeks to address that. The N+ region acts as a suppressant for any injection from the P base region, thus enabling a lower catenary profile in the drift region. Figure 2.26 shows the difference in the carrier density profiles between the different structures.

Figure 2.26. Effect of lifetime and injection control on the catenary profile in the diode drift region.

As seen above, when electron irradiation is used, the catenary dips in the middle of the drift region. As mentioned earlier, this is due to the defects created in the region. This dip in the profile is what results in the performance enhancement in the device. However, at higher temperatures, the defects get annealed out, and the profile starts trending towards that of the non-irradiated device, thereby neutralizing any effect on the carrier lifetimes.

By implementing a form of localized lifetime control, we can reduce the net carrier density close to levels post electron irradiation. This means we can achieve a flat catenary at room temperature and maintain it at higher temperatures. This greatly improves the Vf-Qrr trade-off of the device. The effect of this can clearly be seen when the device is applied to the inductive switching circuit mentioned in Figure 2.3.

#### **Results**

The proposed structure was implemented in Silicon and the results obtained were pretty close to what was expected. For this diode, we used a current density of 500A/cm2. The device was designed for a BV of 1600V with a target  $V_F=1.4V$ . The FRD easily met the desired specifications, as seen in Figure 2.27.

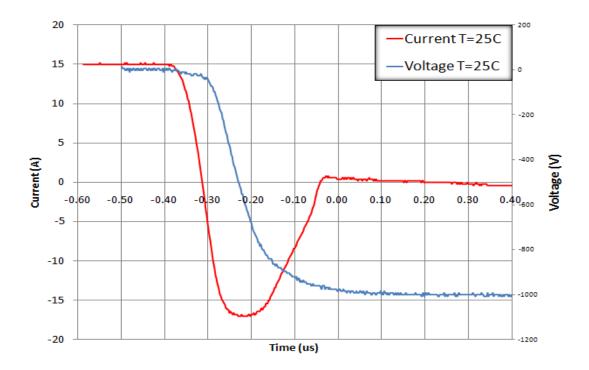

Figure 2.27. Measured Voltage and Current waveforms of the FRD during reverse recovery phase.

The above figure shows the Voltage and Current waveforms of the fabricated device during reverse recovery at room temperature. The test was conducted at a  $V_R$ =1000V, with an  $I_F$ =15A and a Di/Dt=400A/us.

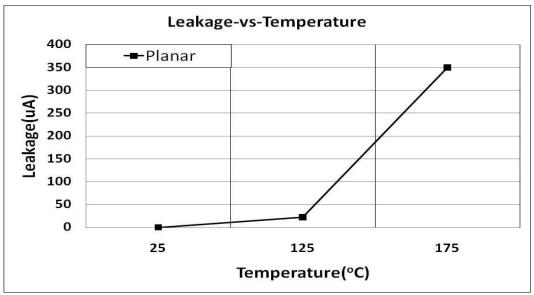

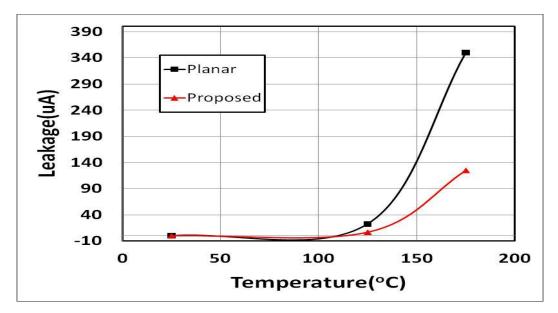

We then compared the performance of the fabricated diode with that of a regular lifetime controlled planar device with similar specifications. As seen in Figure 2.28, we compare the

leakage of the device across the desired temperate range. It is clearly observed that the fabricated device shows minimal degradation at higher temperatures which is critical for industrial applications such as Induction Heating cookers and motor drives. In comparison, due to the presence of induced defects from ER, the planar diode shows significantly worse leakage at 175°C.

Figure 2.28. Measured Idss values of conventional Electron Radiated Device and proposed structure at room temperature and higher temperatures.

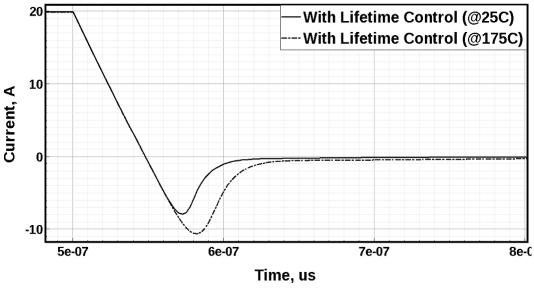

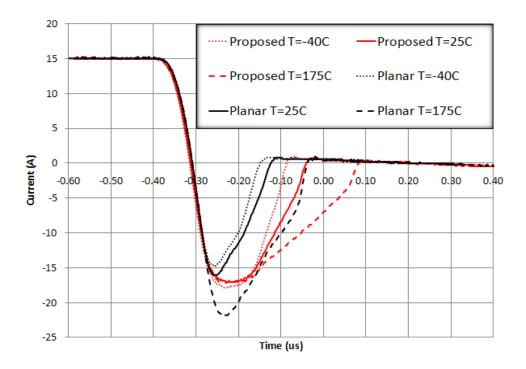

Next, we compare the reverse recovery curve of the FRD with that of a lifetime controlled planar diode. All comparisons were made at a  $V_R$ =1000V, with an  $I_F$ =15A and a Di/Dt=400A/us. As seen in Figure 2.29, the proposed FRD displays similar reverse recovery characteristics to that of the planar FRD at room temperature. But at 175°C, the lifetime controlled planar device showed degraded reverse recovery characteristics.

Figure 2.29. Measured Qrr curves of proposed structure compared with a conventional Electron Radiated Device at -40, 25 and 175°C.

As observed in the above figure, the trench FRD maintains the peak reverse recovery current from -40-175°C. This is critical because the typical temperature during industrial applications is between 90-100°C. This greatly helps reduce the conductions losses in the co-packaged device during reverse conduction.

It is also observed from Figure 29 that the proposed figure without lifetime control also has better softness than the planar structure. Table 2.1 lists the  $I_{RM}$  and softness factors of the two devices measured from the curves from the previous figure.

Table 2.1. I<sub>RM</sub> and softness values of compared devices

| Device   | Temperature (°C) | I <sub>RM</sub> (A) | S    |

|----------|------------------|---------------------|------|

|          | -40              | 17.8                | 1.5  |

| Proposed | 25               | 17.2                | 2.32 |

|          | 175              | 17                  | 3.78 |

| Planar   | -40              | 14.8                | 2.16 |

|          | 25               | 16                  | 2.83 |

|          | 175              | 22                  | 2.65 |

#### **Conclusion**

The results support our claim that the proposed structure displays significantly improved performance over traditionally electron radiated devices, especially at high temperatures. This expands the scope for designing diodes for industrial applications which require stability at temperatures rated as high as 175°C. A couple of things are to be noted here:

- Both diodes were designed to have similar forward voltage of 1.6V.

- At Room Temperature (25°C), the Irm of the trench diode is similar to that of a planar diode which undergoes electron irradiation. However, at a higher operating temperature (175°C), the Irm increases significantly for the planar diode, which the trench diode maintains the Irm current level. This clearly shows the benefit of an injection control mechanism as opposed to an external lifetime control approach.

- Another thing to be noted is the softness of the curve. External life time control reduces the Irm current tail during the tb phase. For the trench diode, at room temperature, the

softness if quite significant. This is mostly due to improper Epi design. By adjusting the drift layer resistivity and the buffer layer characteristics.

Both devices show increased softness at higher temperatures, because higher temperatures naturally increase the carrier lifetime, increasing the time it takes to remove them from the drift region.

Advances are also being made in designing fast recovery diodes in alternate materials like SiC, GaN and GaAs [42]-[47]. These structures show various improvements over the conventional Silicon technology, especially in terms of reverse recovery. But given the still relatively nascent stages of development for these technologies, and the issues regarding cost and compatibility with Silicon structures in the circuit, the adoption of these technologies for conventional applications is still further down the road.

# CHAPTER 3 HIGH VOLTAGE EDGE TERMINATION

#### Introduction

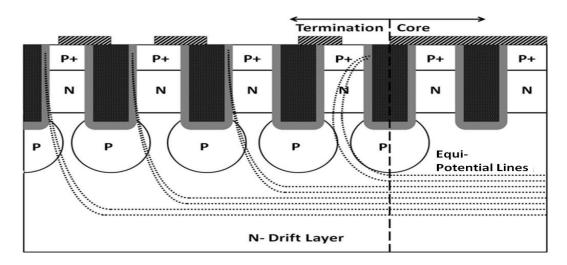

High voltage power semiconductor devices are used in a wide range of applications. These include the high voltage power MOSFETs in power supplies for Flyback, PFC and LLC topologies, insulating gate bipolar transistors (IGBTs) and fast recover diodes (FRDs) for motor drives, induction heating and solar inverters. As mentioned in the previous chapter, the trench MOS structure is a commonly used technique for improving the performance of these high voltage devices. It has been demonstrated for and injection control in an FRD [41]. With the addition of a buried P-type guard ring though the trench, this technology is extended to a MOSFET [48] and an IGBT [49]. The increased N doping concentration is used to lower the on resistance of the MOSFET and increase the injection enhancement of the IGBT.

One of the major challenges in the design of these high voltage devices is their edge termination. The purpose of the termination region is to avoid premature avalanche breakdown due to electric field crowding near the device edge. It achieves this by spreading out the depletion region at the device surface in order to support the full voltage from drain to source. This also results in high surface electric field in the termination region, in silicon and the passivation layer. The presence of the high surface N concentration makes it difficult to implement most conventional edge termination schemes. This necessitates a novel termination for that very reason.

#### **Prior Art**

The most commonly used termination techniques include the abrupt parallel plane junction [50], junction termination edge (JTE) [51]-[54], field rings [55], planar junction [56], metal plates [57], [58] etc. There is a comparative review of the above mentioned schemes along with a few others in [59]. Some of the most common schemes used in high voltage vertical power devices are listed below.

## Junction Termination Edge

A Junction Termination Edge Structure was one of the earliest structures used for high voltage edge termination. The concept behind this approach was simply to appropriately counter-dope the surface to shape the electric field as it transitions towards the edge. The JTE is simple to implement, and a very convenient way to implement edge termination. A conventional JTE structure is shown in Figure 3.1 [51].

Figure 3.1. JTE Termination schemes in a plane and planar p-n junctions [51].

# Field Rings

Field Rings based edge termination structure is the most commonly used termination scheme for vertical power structures. The concept of a field ring is extremely similar to that of a JTE, in that it helps shape the electric field in an efficient manner, but differs in the implementation. While the JTE is just one large cylindrical junction, field rings are multiple in number, helping spread the electric field efficiently along the termination scheme, as shown in Figure 3.2.

Figure 3.2. A conventional field limiting ring structure.

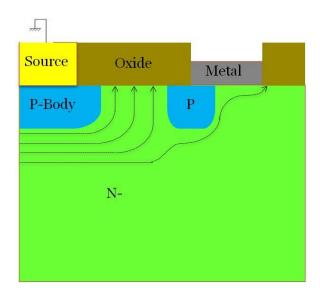

#### **Metal Plates**

Metal plates are used at the surface to prevent the field from collapsing at that point. The potential lines are shaped by the length of the plates, and terminate at the end of the metal plates. The metal plates are usually biased to shape the field accordingly. An example implementation is shown in Figure 3.3.

Figure 3.3. An edge termination scheme combining a field limiting ring and a field plate.

Since superjunction structures have a higher drift region doping concentration, conventional termination schemes don't work very well. So, the terminations schemes for charge compensated structures need to be slightly modified for the same. One of the major limitations of these termination techniques is their high surface electric field in silicon. This makes these termination techniques more susceptible to mobile charges during reliability tests. During high temperature, high voltage bias burn-in tests, mobile ions from packaging mold compound and outside sources can accumulate in the termination region and alter its electric field shape, which can increase leakage and lower breakdown voltage (BV) of the device. The silicon region is more susceptible compared to SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> films because of the higher order of magnitude of lower critical electric field strength compared to these passivation films.

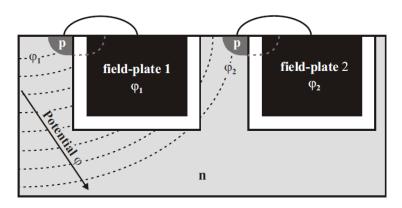

# Field Plate Based Edge Termination Structures