# STARS

University of Central Florida

STARS

Electronic Theses and Dissertations, 2004-2019

2017

# Energy-Aware Data Movement In Non-Volatile Memory Hierarchies

Navid Khoshavi Najafabadi University of Central Florida

Part of the Computer Engineering Commons Find similar works at: https://stars.library.ucf.edu/etd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

## **STARS Citation**

Najafabadi, Navid Khoshavi, "Energy-Aware Data Movement In Non-Volatile Memory Hierarchies" (2017). *Electronic Theses and Dissertations, 2004-2019.* 5604. https://stars.library.ucf.edu/etd/5604

## ENERGY-AWARE DATA MOVEMENT IN NON-VOLATILE MEMORY HIERARCHIES

by

## NAVID KHOSHAVI NAJAFABADI M.S. University of Central Florida, 2016 M.S. Amirkabir University of Technology, 2012

A dissertation submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Summer Term 2017

Major Professor: Ronald F. DeMara

© 2017 Navid Khoshavi Najafabadi

## ABSTRACT

While technology scaling enables increased density for memory cells, the intrinsic high leakage power of conventional CMOS technology and the demand for reduced energy consumption inspires the use of emerging technology alternatives such as eDRAM and Non-Volatile Memory (NVM) including STT-MRAM, PCM, and RRAM. The utilization of emerging technology in Last Level Cache (LLC) designs which occupies a significant fraction of total die area in Chip Multi Processors (CMPs) introduces new dimensions of vulnerability, energy consumption, and performance delivery. To be specific, a part of this research focuses on eDRAM Bit Upset Vulnerability Factor (BUVF) to assess vulnerable portion of the eDRAM refresh cycle where the critical charge varies depending on the write voltage, storage and bit-line capacitance. This dissertation broaden the study on vulnerability assessment of LLC through investigating the impact of Process Variations (PV) on narrow resistive sensing margins in high-density NVM arrays, including on-chip cache and primary memory. Large-latency and power-hungry Sense Amplifiers (SAs) have been adapted to combat PV in the past. Herein, a novel approach is proposed to leverage the PV in NVM arrays using Self-Organized Sub-bank (SOS) design. SOS engages the preferred SA alternative based on the intrinsic as-built behavior of the resistive sensing timing margin to reduce the latency and power consumption while maintaining acceptable access time.

On the other hand, this dissertation investigates a novel technique to prioritize the service to 1) Extensive Read Reused Accessed blocks of the LLC that are silently dropped from higher levels of cache, and 2) the portion of the working set that may exhibit distant re-reference interval in L2. In particular, we develop a lightweight Multi-level Access History Profiler to efficiently identify ERRA blocks through aggregating the LLC block addresses tagged with identical Most Significant Bits into a single entry. Experimental results indicate that the proposed technique can reduce the L2 read miss ratio by 51.7% on average across PARSEC and SPEC2006 workloads.

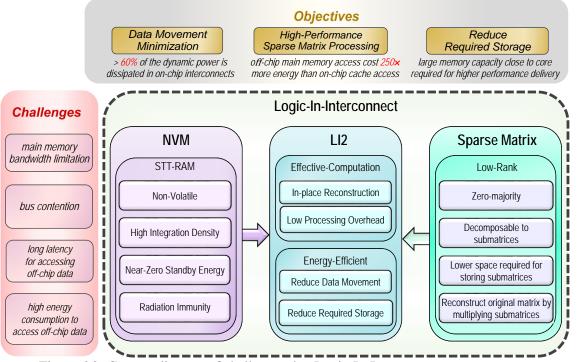

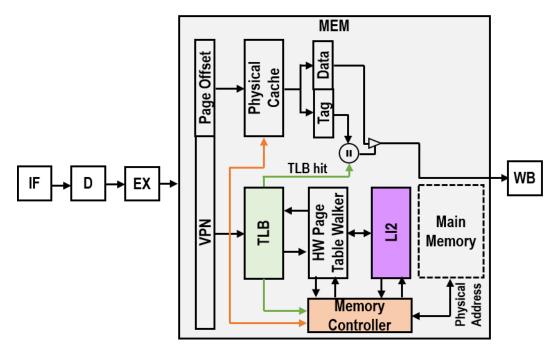

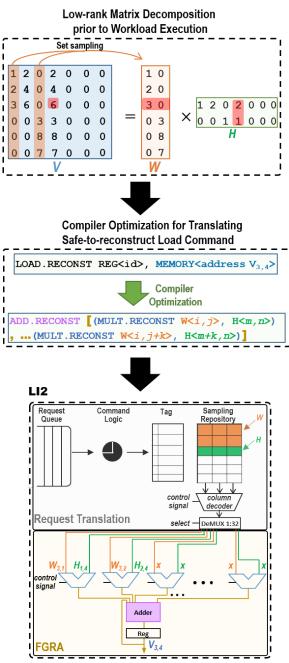

In addition, this dissertation will broaden and apply advancements in theories of subspace recovery to pioneer computationally-aware in-situ operand reconstruction via the novel Logic In Interconnect (LI2) scheme. LI2 will be developed, validated, and refined both theoretically and experimentally to realize a radically different approach to post-Moore's Law computing by leveraging low-rank matrices features offering data reconstruction instead of fetching data from main memory to reduce energy/latency cost per data movement. We propose LI2 enhancement to attain high performance delivery in the post-Moore's Law era through equipping the contemporary micro-architecture design with a customized memory controller which orchestrates the memory request for fetching low-rank matrices to customized Fine Grain Reconfigurable Accelerator (FGRA) for reconstruction while the other memory requests are serviced as before. The goal of LI2 is to conquer the high latency/energy required to traverse main memory arrays in the case of Last Level Cache (LLC) miss, by using in-situ construction of the requested data dealing with low-rank matrices. Thus, LI2 exchanges a high volume of data transfers with a novel lightweight reconstruction method under specific conditions using a cross-layer hardware/algorithm approach.

I dedicate my dissertation work to my family and friends. A special feeling of gratitude to my wife, Sahar, whose affection, love, encouragement make me able to get such success and honor. A special feeling of thankful to my parents whose unlimited support either financially or intellectually made this work possible. I dedicate this work and special thanks to not only my advisor, but also one of my friends for sharing his knowledge about how I can become a successful researcher.

## ACKNOWLEDGMENTS

I owe my gratitude to many people who made this thesis possible even only my name will be appeared on the cover of this thesis. I have been amazingly fortunate to work under supervision of Dr. DeMara who patiently supported me even in tough situations and continuously motivated me to become a successful student. His insightful comments and immense knowledge helped me to shape my ideas at different stage of my research which leads to publishing several papers in the well-known conferences and journals. I would like to extend special thanks to Dr. Jun Wand, Dr. Mingjie Lin, Dr. Cliff Zou, and Dr. Damian Dechev for serving in my dissertation committee.

# TABLE OF CONTENTS

| LIST OF FIGURES                                                       | xiii          |

|-----------------------------------------------------------------------|---------------|

| LIST OF TABLES                                                        | xviii         |

| CHAPTER 1: INTRODUCTION AND MOTIVATION                                | 1             |

| 1.1 Soft Error Impacts on eDRAM-based LLC Design                      | 1             |

| 1.2 Process Variation Impact on NVM-based LLC Design                  | 3             |

| 1.3 The Impact of Data Movement on Overall Performance and Energy Con | nsumption . 4 |

| 1.4 The Impact of Big Data Processing on Memory Throughput            | 6             |

| CHAPTER 2: RELATED WORK                                               | 10            |

| 2.1 Soft Error Vulnerability Analysis in Memory Storage Organization  | 10            |

| 2.2 Exploration of Hybrid Cache Design                                | 11            |

| 2.3 In-Memory Data Management to Minimize Data Movement               | 15            |

| CHAPTER 3: BIT-UPSET VULNERABILITY FACTOR ANALYSIS FOR ED             | RAM-BASED     |

| LLC                                                                   |               |

| 3.1 eDRAM Cell Organization and Operation                             |               |

|      | 3.1.1  | eDRAM Retention Time for Different Technology Node           | 20 |

|------|--------|--------------------------------------------------------------|----|

|      | 3.1.2  | Single Event Effect                                          | 21 |

|      | 3.1.3  | LLC Reference Characteristics                                | 22 |

| 3.2  | The Pr | oposed eDRAM Vulnerability Estimation Algorithm              | 24 |

|      | 3.2.1  | A general Lifetime Model for Data Array                      | 24 |

|      | 3.2.2  | The Proposed Lifetime Model for eDRAM Data Array             | 25 |

|      | 3.2.3  | Bit-Upset Vulnerability Factor Analysis of eDRAM Data Array  | 27 |

| 3.3  | Experi | mental Setup                                                 | 28 |

| 3.4  | Conclu | isions                                                       | 30 |

| СНАР | TER 4: | VARIATION-IMMUNE NVM-BASED SYSTEM DESIGN                     | 32 |

| 4.1  | The Sp | oin-Transfer Torque Magnetic Random Access Memory (STT-MRAM) | 33 |

|      | 4.1.1  | Process Variation in STT-MRAM                                | 34 |

|      | 4.1.2  | Extracting the PV Parameters                                 | 35 |

|      | 4.1.3  | Power-On Self-Test (POST)                                    | 36 |

| 4.2  | Self-O | rganized Sub-banks (SOS)                                     | 37 |

|      | 4.2.1  | SOS Schematic for SAs Array Assignment to each Sub-bank      | 37 |

|      | 4.2.2  | Distribution of Bit Errors in a Sub-banks                    | 41 |

|      | 4.2.3  | Fault Models Associated with Sensed Data             | 42 |

|------|--------|------------------------------------------------------|----|

|      | 4.2.4  | The Proposed PV/Energy -aware Cache Migration Policy | 43 |

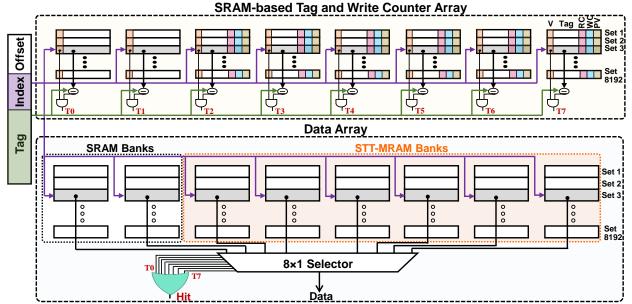

|      |        | 4.2.4.1 Hybrid SRAM and STT-MRAM LLC Design          | 43 |

|      |        | 4.2.4.2 PV/Energy -aware Cache Migration Policy      | 45 |

| 4.3  | Experi | mental Results                                       | 49 |

|      | 4.3.1  | Circuit-Level Simulation Results                     | 49 |

|      | 4.3.2  | Architecture-Level Simulation Results                | 52 |

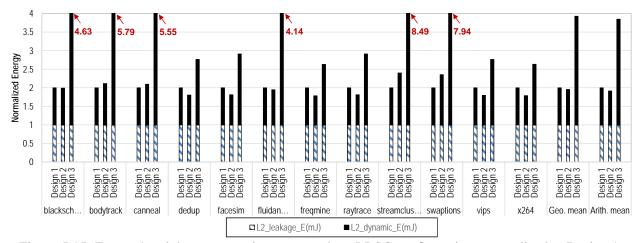

|      |        | 4.3.2.1 Energy Usage Comparison                      | 53 |

|      |        | 4.3.2.2 Write Performance Analysis                   | 54 |

|      |        | 4.3.2.3 Empirical Fault Model Analysis               | 55 |

| 4.4  | Conclu | isions                                               | 57 |

| СНАР | TER 5: | ACCELERATE SERVICE TO CRITICAL LOADS                 | 58 |

| 5.1  | Backg  | round on Technology Trends for Cache Organization    | 60 |

| 5.2  | Motiva | tion                                                 | 61 |

|      | 5.2.1  | Analysis of Memory Access Pattern to Shared LLC      | 62 |

|      | 5.2.2  | Analysis of Clean Victims Eviction in Private L2     | 64 |

| 5.3  | Techni | cal Approach                                         | 65 |

|     | 5.3.1  | Read Reference Activity Persistent (RRAP) Cache Hierarchy              | 66 |

|-----|--------|------------------------------------------------------------------------|----|

|     | 5.3.2  | RRAPclusive: Efficient Cache Configuration to Maximize RRAP Through-   |    |

|     |        | put                                                                    | 68 |

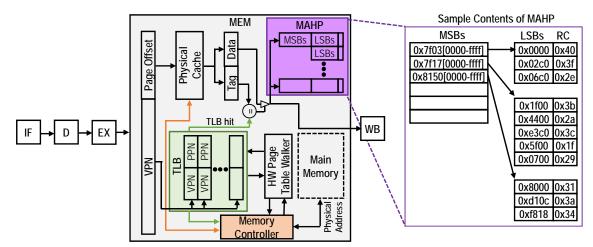

|     | 5.3.3  | Multi-level Access History Profiler                                    | 69 |

|     |        | 5.3.3.1 Spatial Locality at Page-Level Granularity                     | 71 |

|     |        | 5.3.3.2 Implementation of Multi-level Access History Profiler          | 72 |

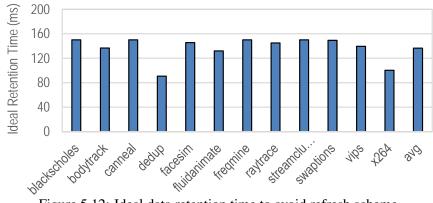

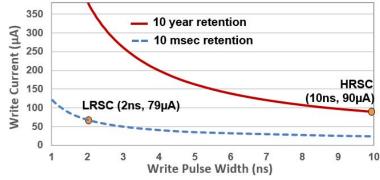

|     | 5.3.4  | Refresh Scheme for LRSC                                                | 75 |

|     | 5.3.5  | Retention Relaxation in LRSC Design                                    | 81 |

| 5.4 | Experi | mental Evaluation                                                      | 84 |

|     | 5.4.1  | Simulator Configuration                                                | 84 |

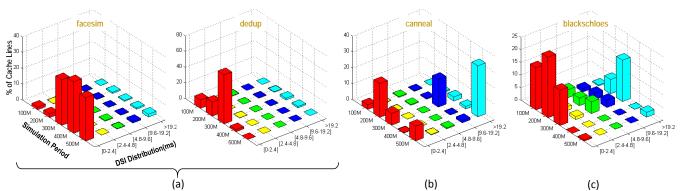

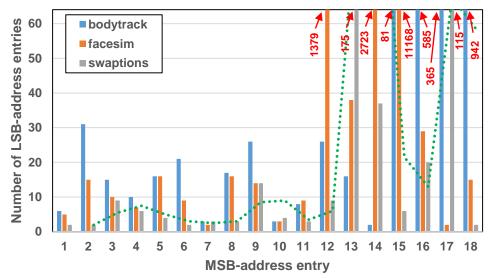

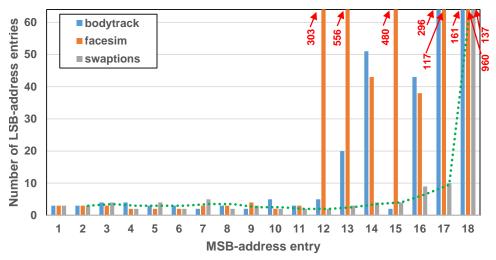

|     | 5.4.2  | Workload Characterization for Estimating the Ratio of MSB/LSB-addresse |    |

|     |        | entries                                                                | 85 |

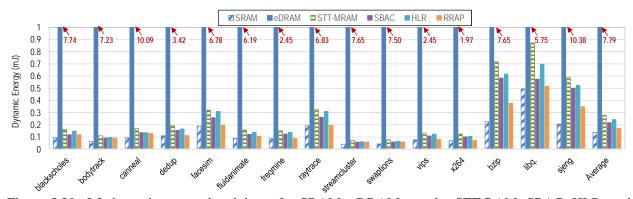

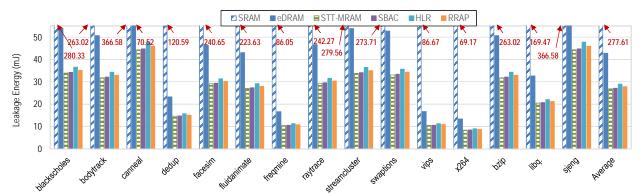

|     | 5.4.3  | Energy Usage Comparison                                                | 87 |

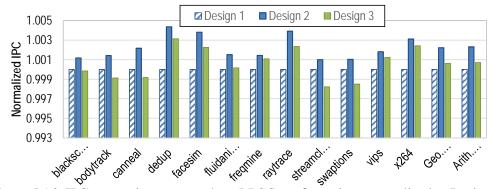

|     | 5.4.4  | Read Miss Ratio Comparison                                             | 89 |

|     | 5.4.5  | Read Service Time Comparison                                           | 90 |

|     | 5.4.6  | Performance Comparison                                                 | 91 |

| 5.5 | Conclu | isions                                                                 | 93 |

|     |        |                                                                        |    |

CHAPTER 6: LOGIC-IN-INTERCONNECT (LI2) COMPUTING: ENERGY-AWARE LOW-

|      | ]      | RANK MATRIX DATA IN-TRANSIT RECONSTRUCTION                      |

|------|--------|-----------------------------------------------------------------|

| 6.1  | Backg  | round on Memory Subsystem Design                                |

| 6.2  | Backg  | round on Sparse Low-rank Matrix                                 |

| 6.3  | Appro  | aches and Algorithms for Low Rank Matrix Recovery               |

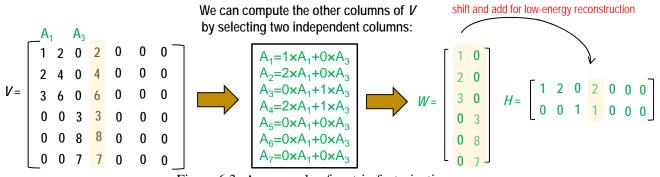

|      | 6.3.1  | Saving Low Rank Matrices                                        |

|      | 6.3.2  | Recovering Low Rank Matrices                                    |

| 6.4  | LI2 Sc | heme to Realize Data Reconstruction                             |

|      | 6.4.1  | ISA Extension for LI2 Realization                               |

|      | 6.4.2  | LI2 Implementation Steps                                        |

|      | 6.4.3  | Fine Grained Reconfigurable Array (FGRA)                        |

|      | 6.4.4  | LI2 Cache Coherence Protocol                                    |

| 6.5  | Prelim | inary Results                                                   |

| 6.6  | Conclu | usions                                                          |

| CHAP | TER 7: | CONCLUSION                                                      |

| 7.1  | Techni | cal Summary                                                     |

|      | 7.1.1  | Bit-Upset Vulnerability Factor Analysis for eDRAM-based LLC 117 |

|      | 7.1.2  | Variation-Immune NVM-based System Design                        |

|        | 7.1.3   | Accelerate Service to Critical Loads                               |

|--------|---------|--------------------------------------------------------------------|

|        | 7.1.4   | LI2 Computing: Energy-aware Low-Rank Matrix Data In-transit Recon- |

|        |         | struction                                                          |

| 7.2    | Techni  | cal Insights Gained                                                |

| 7.3    | Future  | Works                                                              |

| LIST C | )F REFI | ERENCES                                                            |

# **LIST OF FIGURES**

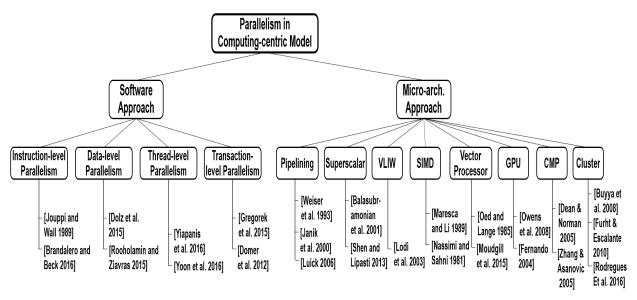

| 1.1 | Taxonomy of parallelism techniques in the traditional computing-centric model,   |    |

|-----|----------------------------------------------------------------------------------|----|

|     | which illustrates opportunities to redesign the location, plurality, and role of |    |

|     | memory along with its interfaces.                                                | 8  |

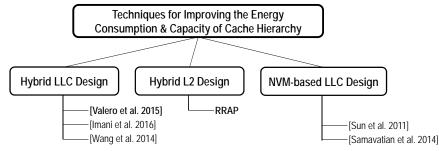

| 2.1 | Taxonomy of techniques utilizing the emergent technologies for improving         |    |

|     | the performance and energy consumption. Approaches using eDRAM high-             |    |

|     | lighted in bold face font.                                                       | 13 |

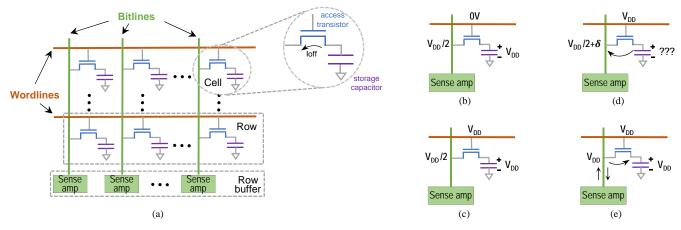

| 3.1 | Typical eDRAM system organization, (a) eDRAM bank structure, (b) Precharged      |    |

|     | state, (c) Wordline raised, (d) Charge sharing, (e) Sensing                      | 19 |

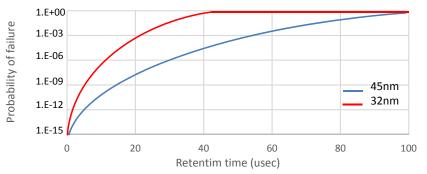

| 3.2 | eDRAM retention time distribution for 45nm and 32nm technology nodes             | 21 |

| 3.3 | The impact of ionizing particle in a reverse-biased p-n junction                 | 22 |

| 3.4 | LLC memory access for canneal.                                                   | 23 |

| 3.5 | LLC memory access for streamcluster.                                             | 23 |

| 3.6 | The lifetime of eDRAM cell. (a) the logic 1 is stored in the cell, (b) the logic |    |

|     | 0 is stored in the cell                                                          | 26 |

| 3.7 | Distribution of the proportion of data items in vulnerable sequence              | 30 |

| 3.8 | The sequence distribution of data items                                          | 31 |

| 3.9 | Measured BUVF behavior for the workloads of the PARSEC suite                     | 31 |

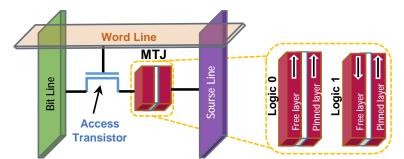

| 4.1  | An illustration of a 1T1R STT-MRAM cell embedded in the cache organization.                                                                                                                              | 34 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

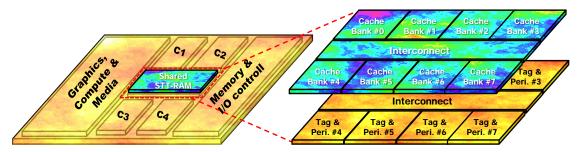

| 4.2  | PV map of a 4-core CMP die                                                                                                                                                                               | 35 |

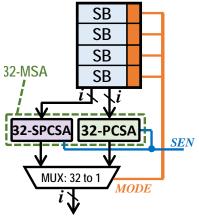

| 4.3  | Determining the preferred SA circuit based on post-fabrication sub-bank re-<br>siliency assessment to PV                                                                                                 | 36 |

| 4.4  | Proposed SOS.                                                                                                                                                                                            | 39 |

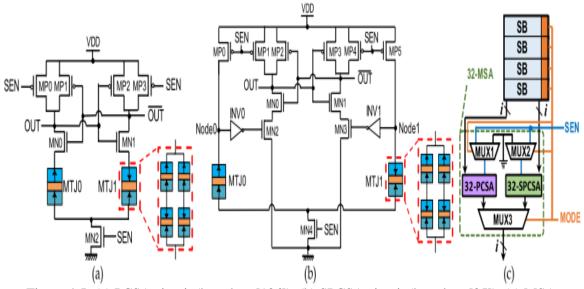

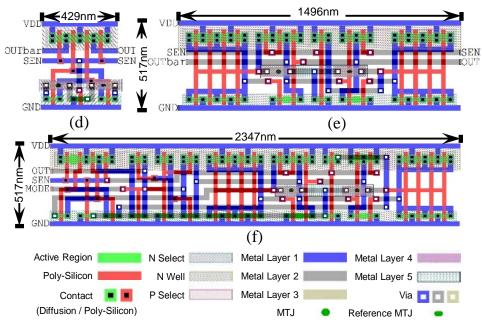

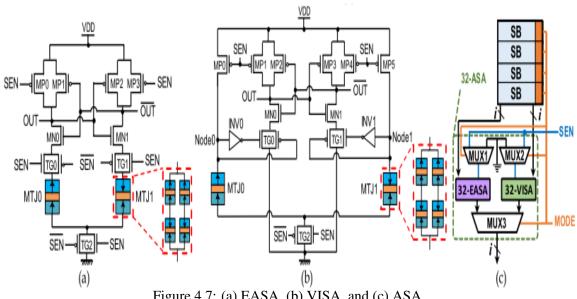

| 4.5  | (a) PCSA circuit (based on [186]), (b) SPCSA circuit (based on [85]), (c) MSA.                                                                                                                           | 39 |

| 4.6  | PCSA, SPCSA, and MSA Layout.                                                                                                                                                                             | 40 |

| 4.7  | (a) EASA, (b) VISA, and (c) ASA                                                                                                                                                                          | 40 |

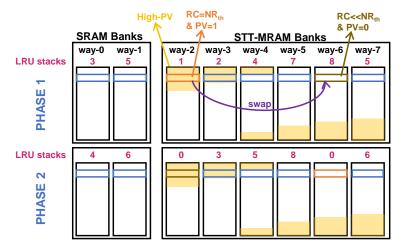

| 4.8  | The scheme of hybrid 8-way set associative SRAM and STT-MRAM cache design, whereby each bank stores a way. In the above configuration, two SRAM-based banks and six STT-MRAM based banks are illustrated | 47 |

| 4.9  | The migration policy to swap a read-intensive block resided in high-PV im-<br>pacted region with not access intensive block located in low-PV impacted<br>region.                                        | 47 |

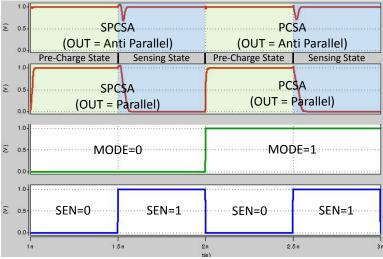

| 4.10 | Transition waveforms of PCSA and SPCSA                                                                                                                                                                   | 50 |

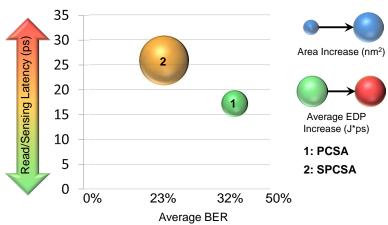

| 4.11 | PCSA and SPCSA design space for TMR=100%                                                                                                                                                                 | 50 |

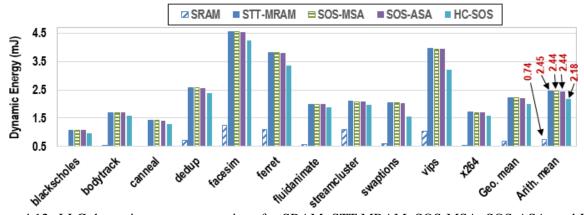

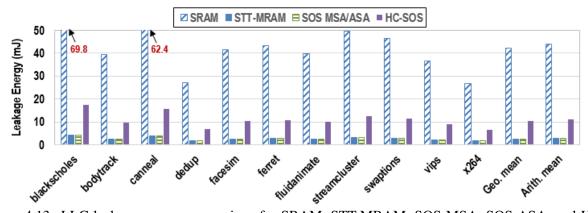

| 4.12 | LLC dynamic energy comparison for SRAM, STT-MRAM, SOS-MSA, SOS-ASA, and HC-SOS, respectively.                                                                                                            | 54 |

| 4.13 | LLC leakage energy comparison for SRAM, STT-MRAM, SOS-MSA, SOS-ASA, and HC-SOS, respectively.                                                                                                            | 54 |

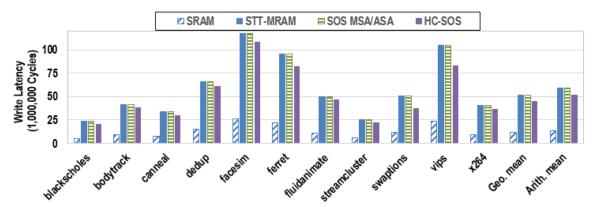

| 4.14 | Write performance comparison for SRAM, STT-MRAM, SOS MSA/ASA,                           |        |

|------|-----------------------------------------------------------------------------------------|--------|

|      | and HC-SOS.                                                                             | 55     |

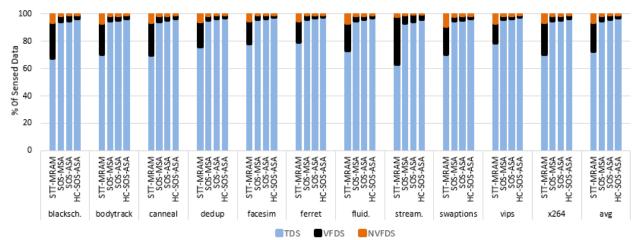

| 4.15 | Distribution of sensed data. SOS is equipped with $MTJ_{Ref}$ =4.8K $\Omega$ , TMR=150% | ,<br>, |

|      | and 10% variation in TMR                                                                | 56     |

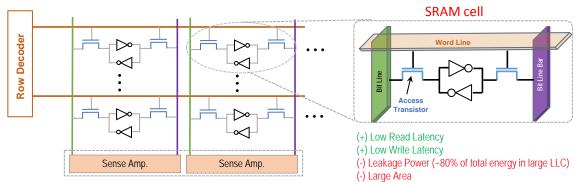

| 5.1  | LLC organization based on SRAM                                                          | 59     |

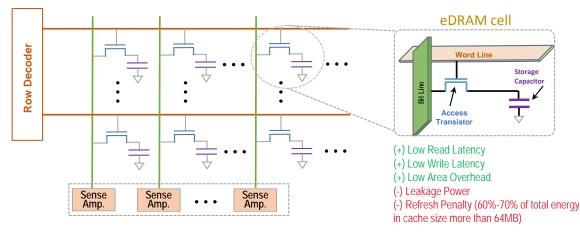

| 5.2  | LLC organization based on eDRAM                                                         | 60     |

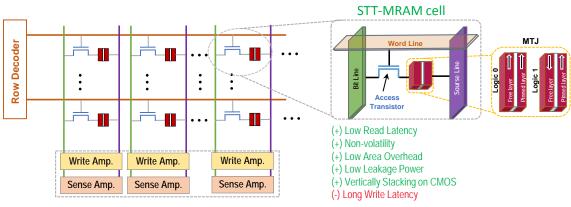

| 5.3  | LLC organization based on STT-RAM.                                                      | 60     |

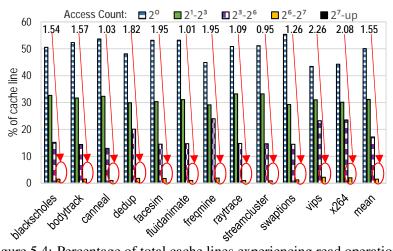

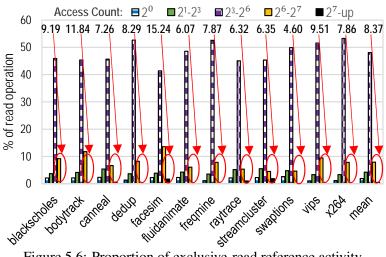

| 5.4  | Percentage of total cache lines experiencing read operation                             | 63     |

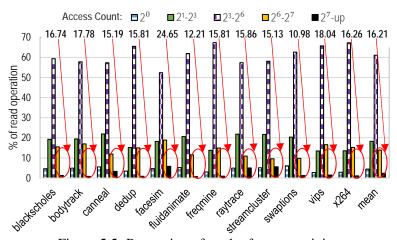

| 5.5  | Proportion of read reference activity.                                                  | 63     |

| 5.6  | Proportion of exclusive-read reference activity.                                        | 64     |

| 5.7  | Proportion of the frequently re-referenced clean victim blocks after their evic-        |        |

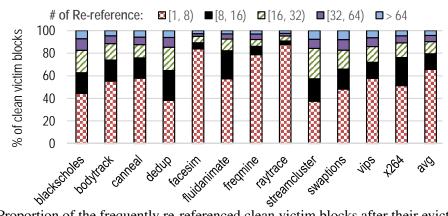

|      | tion from L2                                                                            | 65     |

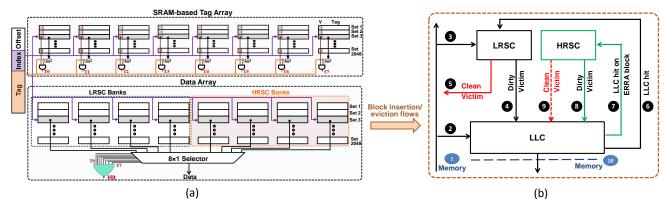

| 5.8  | RRAP scheme: (a) Heterogeneous split cache architecture, (b) Block inser-               |        |

|      | tion/eviction flows.                                                                    | 68     |

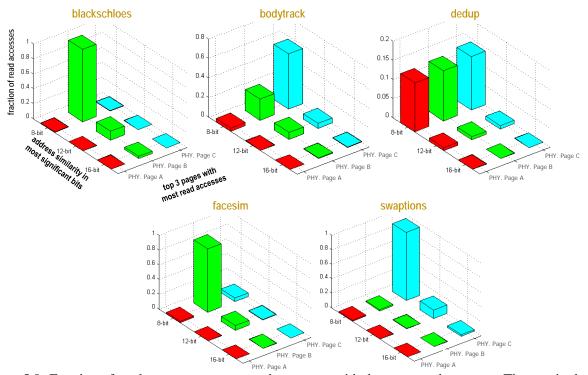

| 5.9  | Fraction of read accesses among top three pages with the most read accesses.            |        |

|      | The x-axis shows the bin of block addresses having different number of iden-            |        |

|      | tical MSBs within a selected page. The y-axis shows the fraction of total               |        |

|      | read accesses during the entire simulation interval. The z-axis characterizes           |        |

|      | the top three pages with the most read accesses.                                        | 74     |

| 5.10 | MAHP implementation in a virtual-physical cache configuration.                          | 74     |

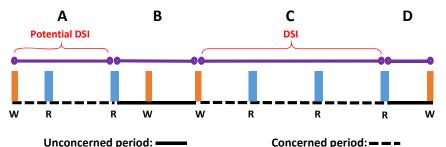

| 5.11 | DSI equals to the sequence C which is largest interval between a write and       |     |

|------|----------------------------------------------------------------------------------|-----|

|      | the final subsequent read operation                                              | 77  |

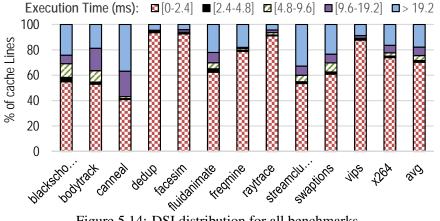

| 5.12 | Ideal data retention time to avoid refresh scheme.                               | 78  |

| 5.13 | Three classes of DSI distribution: (a) unimodal, (b) bimodal, and (c) symmetric. | 79  |

| 5.14 | DSI distribution for all benchmarks.                                             | 79  |

| 5.15 | Energy breakdown comparison among three LRSC configurations normal-              | 0.1 |

|      | ized to Design 1                                                                 | 81  |

| 5.16 | IPC comparison among three LRSC configurations normalized to Design 1            | 82  |

| 5.17 | Write current vs. write pulse width for LRSC and HRSC                            | 84  |

| 5.18 | Number of required LSB-address entries per each MSB-address entry for            |     |

|      | selected LLC blocks having identical 12 MSBs                                     | 86  |

| 5.19 | Number of required LSB-address entries per each MSB-address entry for            |     |

|      | selected LLC blocks having identical 16 MSBs                                     | 87  |

| 5.20 | L2 dynamic energy breakdown for SRAM, eDRAM, regular STT-RAM, SBAC,              |     |

|      | HLR, and RRAP.                                                                   | 89  |

| 5.21 | L2 leakage energy breakdown for SRAM, eDRAM, regular STT-RAM, SBAC,              |     |

|      | HLR, and RRAP.                                                                   | 89  |

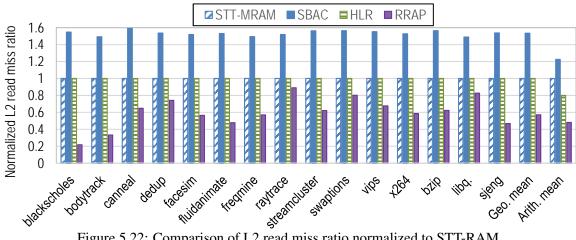

| 5.22 | Comparison of L2 read miss ratio normalized to STT-RAM                           | 92  |

| 5.23 | Comparison of read service time for the entire memory hierarchy normalized       |     |

|      | to STT-RAM.                                                                      | 92  |

| 5.24 | Comparison of RRAP's performance with other technologies 93                                                                                        |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.1  | Schematic of DRAM organization                                                                                                                     |

| 6.2  | Context diagram of challenges that Logic-In-Interconnect can overcome 101                                                                          |

| 6.3  | An example of matrix factorization                                                                                                                 |

| 6.4  | LI2 implementation feasibility in a virtual-physical cache configuration. LI2 is responsible for reconstructing data via the memory controller     |

| 6.5  | Illustrative example of LI2 processing                                                                                                             |

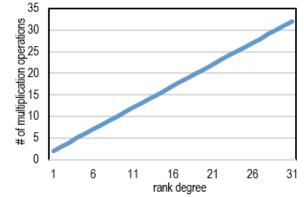

| 6.6  | Linear relation of rank degree and multiplication operations                                                                                       |

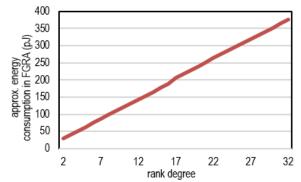

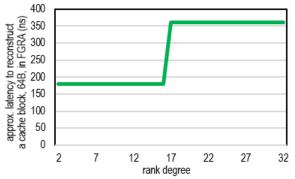

| 6.7  | Energy consumption estimation for data reconstruction where energy per FP MUL and per FP ADD considered to be 11.3 pJ and 7.1 pJ, respectively 114 |

| 6.8  | Latency estimation for data reconstruction where latency per FP MUL and per FP ADD considered to be 5 ns and 6.25 ns, respectively                 |

| 7.1  | The modified tracefile to include bank id                                                                                                          |

| 7.2  | A part of under-develop python parser script to analyze cache line access pattern                                                                  |

## LIST OF TABLES

| 2.1 | Comparison of hybrid cache design techniques.                                                                                                                                        | 14  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | Comparison of state-of-the-art techniques for reducing off-chip data transfer                                                                                                        | 17  |

| 3.1 | Simulator configuration                                                                                                                                                              | 30  |

| 4.1 | Evaluation parameters                                                                                                                                                                | 51  |

| 4.2 | Simulation Results for Ideal State (MTJ <sub>Ref</sub> = $5.7$ K $\Omega$ )                                                                                                          | 51  |

| 4.3 | MONTE CARLO SIMULATION 10,000 RUN RESULTS (MTJ <sub>Ref</sub> = $5.7$ K $\Omega$ , MTJ <sub>P</sub> = $3.2$ K $\Omega$ , and MTJ <sub>AP</sub> = $6.4$ K $\Omega$ for TMR=100%)      | 52  |

| 4.4 | MONTE CARLO SIMULATION 10,000 RUN RESULTS (MTJ <sub>Ref</sub> = $4.8$ K $\Omega$ , MTJ <sub>P</sub> = $3.2$ K $\Omega$ , and MTJ <sub>AP</sub> = $6.4$ K $\Omega$ for TMR= $100\%$ ) | 52  |

| 5.1 | STT-RAM cell retention time configurations for LRSC design                                                                                                                           | 80  |

| 5.2 | Detailed characteristics of private L2 cache bank configuration (32nm, tem-<br>perature=350K)                                                                                        | 85  |

| 5.3 | Memory subsystem                                                                                                                                                                     | 85  |

| 6.1 | Illustrative example of ISA extension to support LI2 realization.                                                                                                                    | 110 |

## **CHAPTER 1: INTRODUCTION AND MOTIVATION**

The CMOS technology advancements over past decades has introduced more accurate and costefficient techniques for manufacturing the electronic devices. The demand for delivering greater performance in a smaller chip area has motivated the International Technology Roadmap for Semiconductors (ITRS) community to significantly investigate the challenges of entering the nanometer scale CMOS technology era [24]. Even though the reduction of transistors gate length size in the early stage of CMOS microprocessor design process has promised the continued process of doubling the quantity of transistors in a single die with Moors Law [137], the power wall challenge [146] has enforced CMOS microprocessor designers to shift towards develop of multi-core processors. This design paradigm has made the researchers to confront new design and implementation obstacles where we find a way to turn them into opportunities for developing cost-effective and energy efficient high performance system designs. In the remaining of this chapter, we will discuss about these challenges and opportunities.

#### 1.1 Soft Error Impacts on eDRAM-based LLC Design

Large Last Level Cache (LLC) consumes a large fraction of the die in modern CMPs. High bandwidth demands of memory-intensive applications utilizing large working sets require larger LLC to (1) facilitate the residency of the working set to remain in cache, (2) prevent data replacement due to continual communication between cores. As the technology goes down toward sub-micron feature size, more cache lines can fit on the same LLC area which increases the cache capacity resulting in delivery of reduced miss rate to all cores. However, this approach is coupled with vulnerability increase of LLC against Single Event Upset (SEU) and Multi-Bit Upsets (MBUs). Soft errors induced by energetic particles penetrate the silicon substrate and generate electron-hole pairs along their tracks. If the generated electrons collected into cell junction is larger than critical charge ( $Q_C$ ), it can flip the cell state and generate soft error in memory cell [153]. Even though the probability of Soft Error Rate (SER) per bit is small, the large density of LLC unacceptably increases the SER per chip. In particular, given roughly 50% of chip is occupied by cache memory structure, high-dense large-scale LLC counterpart, becomes highly susceptible to soft errors [158]. Moreover, the high potential of residing a data block in LLC for millions of cycles between two consecutive accesses has significantly increased the vulnerability of LLC cache blocks to soft errors [111].

Recently, large embedded Dynamic Random Access Memory (eDRAM) cache has been introduced as the LLC or L3 cache between L2 SRAM cache and main memory to alleviate further the core-memory speed gap [111][103]. The employment of on-chip L3 eDRAM offers higher cache capacity compared to SRAM [111][110][170] and provides faster on-chip communication through on-chip high bandwidth [17][37]. The eDRAM requires periodic refresh operation less than *retention time* to prevent data loss due to the leakage of capacitors over time. The eDRAM cell's retention time is defined as the amount of time that eDRAM cell can preserve data before data loss occurs [145][29]. As the feature size continues to decrease, the eDRAM cell size reduction imposes serious problems to eDRAM design because it not only decreases the retention time of eDRAM cell, but also leads to reduced reliability in terms of increasing the susceptibility of eDRAM cell to the soft errors [16][57][4][47].

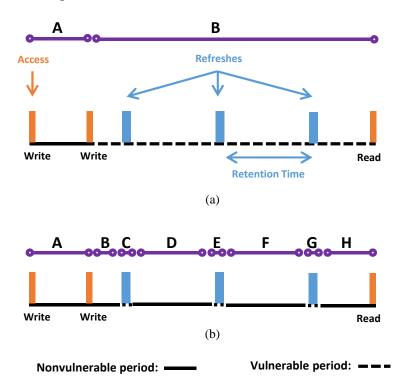

In order to preserve data integrity in eDRAM, the charge in each capacitor must be refreshed periodically. This means the data stored in eDRAM is required to be read out and written back into cell by each refresh operation. This new lifetime sequence needs to be investigated to accurately reveal how different lifetime sequences of cache data contribute to vulnerability. Thus, despite the fact that the most previous works studied the trade-offs between performance, energy consumption and achieved cache reliability, more systematic study of cache vulnerability is still needed to present a detailed lifetime model for data arrays in eDRAM LLC. Given these challenges, we propose a more accurate and application-relevant lifetime model in Chapter 3 while taking the refresh operation scheme for LLC into consideration. The proposed lifetime model distinguishes among six lifetime sequences for each data item located in eDRAM LLC according to the previous activity and current one. These sequences are further categorized into two groups, *vulnerable* and *nonvulnerable* sequences. A vulnerable sequence is characterized by the fact that any error that is encountered during this sequence has the potential to be either consumed by the CPU or committed to memory by a write. However, if the exposure occurs during nonvulnerable sequence, no program failure will result.

#### 1.2 Process Variation Impact on NVM-based LLC Design

Recently, the emerging Non-Volatile Memory (NVM) technologies such as Resistive RAM (RRAM), Phase Change Memory (PCM) and Spin Transfer Torque Magnetic RAM (STT-MRAM) have received significant attention as promising approaches to overcome the CMOS-based memory storage challenges such as volatility and high static power consumption. Even though the utilization of NVM technology in the overarching system can significantly reduce the leakage power issue, the Process Variation (PV) effect has still remained as a limiting factor for NVM applicability and scalability. In particular, the PV in Magnetic Tunnel Junction (MTJ) devices utilized in STT-MRAM organization, manifests itself as variation in MgO thickness and MTJ geometry which in turn results in deviation of MTJ resistance [159]. Furthermore, the threshold voltage,  $V_{th}$ , and gate length,  $L_{eff}$ , of CMOS access transistors in STT-MRAM organization exhibit delay and driving current variations under PV, which negatively impacts the performance consistency of memory operation [43]. As the results of PV effect on both conventional and emerging semiconductor technologies, the difference between the sensed bit-line voltage and the reference voltage which is referred as *sense margin* can severely fluctuate, resulting in possible false detection scenario and increased bit error rate [184]. This issue has increased the demand for designing advanced low-power and reliable sensing circuits which can be integrated into PV-resilient system architectures while providing required sensing margin. To provide reliable sensing operation while taking the energy budget into consideration, we propose a circuit-architecture cross-layer solution suitable for multi-core processors as well as IoT devices.

Our proposed technique, referred to as *Self-Organized Sub-bank (SOS)*, partitions STT-MRAM data arrays into several sub-banks to directly access requested data while introducing individualized sensing resolution. Sub-banks are evaluated and tagged during an initial *Power-On Self-Test* (*POST*) phase to identify the preferred SA for that particular sub-bank. Hence, SOS reduces the risk of contaminating the application's data structure by fault propagation.

#### 1.3 The Impact of Data Movement on Overall Performance and Energy Consumption

Apart from reliability concerns for correctly sensing data from LLC, the increasing bandwidth demand of current memory-intensive applications incurs significant data movement that negatively impacts off-chip bandwidth, on-chip memory access latency, and energy consumption [19] [102] [30] [6]. To reduce data transfer between on-chip and off-chip memory components, commercial multi-core systems utilize multi-level cache methodology [20] [93] [74] whereby fast, lowcapacity, and high leakage power SRAM arrays are employed in the upper-levels of cache, i.e. L1 and L2, while large, low leakage power and high refresh demand eDRAM is placed in LLC. The employment of relatively spacious SRAM arrays as L2 cache design in the middle of cache hierarchy results in two major challenges: 1) *leakage*: the high leakage power characteristic of SRAM cells results in excessive power budget [79], and 2) *area*: capacity constraints induced by the SRAM cell footprint prevent favorable residency of the working set to reside close to the active core [75] [72]. The negative effect of aforementioned issues is exacerbated with the high dynamic power dissipation incurred to drive on-chip interconnects while exchanging data [18][165].

On the other hand, the cache memory shortage to maintain continuously expanding working sets close to the core causes the performance degradation or increased miss ratio. This degradation is exacerbated by introducing more cache levels with larger LLC capacity. For instance, the transfer latency for a cache block from L2 to L1 in hyper-threaded Pentium IV is 18 cycles, while this latency goes up to 360 cycles for data movement between main memory and L2 [164]. Furthermore, the existing cache replacement policies are ineffective to deal with continuously growing large memory-intensive workloads that typically are greater than available cache size [138]. In particular, a fraction of working set that exhibit distant re-reference interval may repeatedly be evicted and be brought back from/to L2 prior to contributing sufficient hits to L2. Thus, the processor may stall for a long time to access the data stored in the cache blocks in LLC if there are no independent instructions to execute.

While other recent works have made significant advancement to optimize eDRAM LLC (L3 in this work) [112, 11], in Chapter 5, we introduce new insights regarding working set behavior to optimize L2 cache using a heterogeneous STT-MRAM. Various hybrid cache designs have been presented in the past to maintain the read-intensive cache blocks in the high-retention region while write-intensive blocks are allocated to low-retention regions of cache [161, 81]. The same strategy is adopted in our design for prioritizing the service to 1) Extensive Read Reused Access (ERRA) blocks that remain unchanged during their residency in LLC, and 2) frequently reused blocks which may exhibit distant re-reference intervals in L2. An efficient block allocation/replacement policy is introduced to maximize the throughput of the adopted hybrid cache design. To minimize the overhead of finding and labeling the potential blocks that must be prioritized to copy into high-

retention regions of the adopted hybrid L2 cache, we propose a novel Multi-level Access History Profiler (MAHP) inspired by observing the high spatial locality at page-level granularity among different class of workloads. To be specific, we observed that more than 50% of read accesses are from one of the three pages with the most accesses in the selected workloads, indicating that the majority of cache block accesses are from the same physical page. MAHP aggregates the LLC block addresses tagged with identical Most Significant Bits (MSBs) into a single entry while their remaining Least Significant Bits (LSBs) of the addresses are stored into distinct LSB-address entries.

#### 1.4 The Impact of Big Data Processing on Memory Throughput

The increasing demand for Big Data processing often requires the parallel execution of vast number of servers to employ multifaceted analytical methods for extracting meaningful value from data. Nowadays, around 80 percent of the large data-sets are unstructured data exhibiting no specified format which makes the datum access, arrangement, and processing extremely formidable [70]. To be specific, the large volume of unstructured data are analyzed with data structures that often incur random access patterns, which in turn cause cache underutilization, high memory access conflict, increased power dissipation for driving on-chip interconnects and activating off-chip main memory components (row/column address strobe, bit line pre-charge, sensing operation), and reduced memory-level parallelism. Therefore, research into addressing the computational challenges associated with unstructured data has significant potential to transform scalable parallelism using a cross-layer computation fashion from the application layer down to the micro-architecture.

Over the past few decades, the focus of researchers were mostly on speeding up the computational capabilities in traditional computing-centric model which is based on moving large volume of data from/to memory storage to/from processing nodes for execution/store. To maximize the efficacy of

computing-centric model, many fine/coarse -grain parallelism paradigms from software approach, i.e. instruction/data/thread/transaction -level parallelism [180, 84, 22, 39, 178, 64, 144, 38], to micro-architecture domain, i.e. pipelining [172, 77, 113], superscalar [15, 152], VLIW [109], Single Instruction Multiple Data (SIMD) instructions [118, 122], vector processors [125], Graphic Processor Unit (GPUs) [128, 53], chip-multiprocessors [35, 183], clusters [23, 56, 34], have been proposed in the past as illustrated in Figure 1.1, that facilitate the concurrent execution of numerous fine-grained threads on multiple functional units for arithmetic execution and logical calculation. For example, recently Nvidia company has released Tesla P100(SXM2) GPU accelerator that consumes about 56pJ per double-precision floating point operation derived from max power consumption of 300W for 5.3 Tflops operations [2]. Even though this achievement is approximately close to the anticipated 20pJ energy cost for targeted power envelop which was projected on 2008 for contemporary supercomputers [96], the simultaneous activation of multiple functional units has faced the power wall challenge which is referred as the dark silicon effect. This phenomenon stems from the failure of Dennard scaling where the aggressive CMOS technology scaling is no longer in line with voltage scaling, resulting in sharp increase of power density [162].

Figure 1.1: Taxonomy of parallelism techniques in the traditional computing-centric model, which illustrates opportunities to redesign the location, plurality, and role of memory along with its interfaces.

This encourages the computer architecture designers to shift the paradigm of computation from computing-centric model towards data-centric architecture for further parallelism and minimizing the energy cost per computation operation. The processing nodes in data-centric model are arranged to be placed close to the location of data, resulting in remarkable reduction of the cost for data movement [14]. These achievements have been coupled with the advancements in technology and manufacturing for 3D die stacking, and custom memory interfaces such as High Bandwidth Memory (HBM) and Hybrid Memory Cube (HMC) which have enabled the efficient implementation of data-centric models. In particular, direct data Processing-In-Memory (PIM) [44, 62, 126, 65, 66, 7, 9, 42, 88, 116], near memory processing [49, 50, 10, 171, 48, 182, 188, 149], and processing in memory controller [46, 179] have received significant attention for implementing data-centric architecture. However, means for continuing scalable parallelism especially in scientific applications will be through the development of a software-architecture cross-layer approach which is orthogonal to the recent data-centric model based techniques. The proposed method must reduce further the on/off -chip interferences for accessing shared resources while eliminating un-

necessary multiple round-trip to main memory for fetch and update of the data, which in turn results in the reduced orchestration workflow and data movement.

To attain this urgent goal, we target a category of matrices that are widely observed in Big Data processing, i.e. dimension reduction, signal processing, compression, clustering, regression, and classification, called the *low rank matrix*, as a high-payoff strategy to reduce data movement across the entire system stack. In particular, the low rank matrices exhibit specific characteristics that enable computationally-efficient reconstruction of the required column using two decomposed matrices which have significantly fewer elements than the original matrix, at the cost of a slight storage overhead. We argue that these two matrices are updated rarely in our target applications, which means that the overhead for extracting them from original matrix is correspondingly small.

## **CHAPTER 2: RELATED WORK**

#### 2.1 Soft Error Vulnerability Analysis in Memory Storage Organization

Asadi et al. [12] proposed algorithms of vulnerability computation for both L1 and L2 caches. The authors indicated the vulnerability breakdown of data, tag-addresses, and status bits. Tag error is analyzed in detail and classified into three categories. Whereas Asadi's research is forced on L1 and L2 private cache, Maghsoudloo et al. [114] analyzed the influence of coherence protocol on the susceptibility of shared LLC. Two prediction schemes are proposed to provide correction ability for dirty data.

The authors of [168] conducted a study to assess the reliability behavior of cache memories in order to provide insight into the cache design for manufacturing highly efficient reliable on-chip cache. Meanwhile, an analytical framework is a proposed by Suh et al. [158] to measure the failure rate in L2 SRAM cache under any soft error protection scheme. However, these two works are not specifically designed for eDRAM.

In terms of eDRAM and DRAM reliability analysis work, Fang et al. [47] developed an efficient method to predict scaling trends for both neutron- and alpha- soft error rate. However, our scheme is suitable for a wide range of soft errors. Shin [153] proposed a unified model for alphaparticle-induced charge collection. For soft error concerns outside of cache broader treatments are presented in [115][58].

### 2.2 Exploration of Hybrid Cache Design

Hybrid cache design approaches have received significant attention over past years. These techniques leverage the benefits of utilized technologies to maximize the performance and minimize the energy consumption. In [166], both SRAM and eDRAM technologies are employed in the second-level cache to offer area savings and reduced energy consumption while the performance is increased by 5.9 percent on average. The proposed LLC design leverages the fast SRAM device to store the most likely referenced blocks in the future while the high-dense and low-leakage eDRAM is utilized to reduce the overall energy consumption [166]. In other words, the larger SRAM banks can provide the higher performance while the deployment of larger area-efficient eDRAM requires lower energy for operation. Thus, the ratio of utilizing these technologies in the LLC has been optimized to provide the sufficient performance and reduce energy consumption. However, this design does not explicitly consider the critical load behavior.

The proposed work in [73] leverages the asymmetric write power associated with storing 'ones' and 'zeros' to place data blocks having majority 'zero' data into STT-RAM while the remained data blocks are stored in the SRAM. The less energy is required to write 'zero' in STT-RAM compared to writing 'one'. This asymmetric write power of the STT-RAM motivated the authors to place data blocks having majority 'zero' data into STT-RAM while the remained data blocks having majority 'zero' data into STT-RAM while the remained data blocks are stored in the SRAM. Since the data block is updated several times during its lifetime, it is possible that the majority of data changes over time. Accordingly, a two-bit counter has been considered for each cache line to track the status of the majority. The migration policy swap the data blocks according to the pace of majority-data changes. In other word, it does not immediately move the data by observing the changes in the majority-data to avoid write overhead associated with the unnecessary migration. Thus, the migration policy transfers the data between two partitions in favor of reducing the write energy overhead. This design limits the performance of multi-core chip

to the efficiency of the module which determines the majority of the data. Namely, each data block should be given to the dispatcher module before placement in the LLC which incurs significant overhead for memory-intensive applications imposing significant pressure on the placement policy.

The proposed hybrid LLC design proposed in [169] utilizes an intelligent adaptive data block placement by taking each cache line future access pattern into consideration. The write accesses are categorized into three main classes: prefetch-write, core-write and demand-write. Around 26% of all prefetch blocks are not accessed by the core after initial prefetch [169]. Furthermore, the data blocks moved to the LLC due to cache burst phenomenon are not accessed again until the eviction occurs [169]. The data blocks with the aforementioned characteristics are considered to be placed in the SRAM. On the other hand, the data blocks which experience long interval between consecutive reads are placed into the STT-RAM to benefit from the low leakage power cost of long-residency offered by non-volatile devices [169]. This design may incur prediction design overhead which incurs extra energy consumption for tracking the access pattern to each cache line and making the decision for placement.

In [161], Low-Retention (LR) and High-Retention (HR) STT-RAM arrays are utilized simultaneously to balance the performance versus the energy consumption. To accomplish this, the retention time of the STT-RAM is relaxed for LR architecture to improve the write operation speed. On the other hand, the HR cache offers the long-term residency of data block while incurring very small leakage power. Regarding to the features that each cache design offers, the proposed method manages the write-intensive cache blocks to be placed into the LR cache in favor of performance, while the read-intensive cache blocks are kept in the HR arrays to meet the required power budget limits. Furthermore, the migration policy is devised to transfer the data blocks to the proper cache design by continuously monitoring the access pattern to each cache line. Since the lifespan of the cache lines in the L1 arrays is limited to the retention time which is deliberated at the design time, a refresh mechanism is designed to periodically refresh cache lines for preventing data loss. RRAP utilizes the same refresh approach to maintain the stability of data in LRSC design.

In [147], the similar idea is utilized in the LLC design for GPU. The small-sized LR cache is employed to keep the write-intensive data blocks by considering the fact that the re-write interval time of blocks is typically lower than  $100\mu s$ . Again, the large HR arrays is considered to maintain the less-frequently written data blocks [147]. The proposed technique uses a write threshold on HR to determine whether to keep the data in HR or move it to the LR. To achieve this goal, the correlation between the threshold value and the performance has been accurately analyzed, and the optimum value has been selected as the threshold value. In addition, different degrees of associativity are considered for LR and HR designs to maximize the write utilization in LR and to improve the data migration policy. The taxonomy of the discussed techniques are presented in Fig. 2.1 and the contribution of our technique which will be presented in Chapter 5, compared to other techniques is highlighted in Table 2.1.

Figure 2.1: Taxonomy of techniques utilizing the emergent technologies for improving the performance and energy consumption. Approaches using eDRAM highlighted in bold face font.

Besides proposing hybrid cache designs to enhance performance and energy consumption, the bypass methods [63, 120, 141, 95] have received significant attention for their efficiency to improve the temporal locality. Gonzalez et al. [63] proposed a data cache organization to improve both spatial and temporal locality through *locality prediction table*. Essentially, the history of recently referenced instructions is considered to bypass branches that can cause cache pollution. McFarling [120] proposed to dynamically exclude cache lines that contribute to the conflict misses in a direct-

mapped cache. Rathi et al. [141] proposed to bypass STT-RAM based LLC while hooking up directly upper level caches to the memory if the LLC is susceptible to Denial of Service (DoS) or any other attacks. Kim et al. [95] proposed a bypass method for inclusive NVM-based LLC to reduce the write operations overhead which in turn results in the improved performance and efficient energy consumption. However, both replacement policy and the available cache capacity determine the efficiency of the aforementioned techniques. For example, suppose the working set cannot fit into L2 due to the insufficient cache capacity. If the access sequences of the running application to the L2 blocks discard a portion of resided blocks whose will be accessed at the end of reference pattern, most of the newly inserted blocks will be dead before contributing sufficient hit to L2. This scenario may also occur in the applications that exhibit the burst reference pattern to non-temporal blocks [76]. Thus, even though bypass methods mitigate the poor locality in most of scenarios, in this case maintaining a highly read accessed fraction of the working set in the upper level caches for a long-enough period aids to improve the temporal locality.

| Approach                | multi-retention<br>STT-RAM | Response time<br>to write operation | Energy<br>consumption | Service to<br>critical loads | Cache<br>configuration | Technique's<br>overhead |

|-------------------------|----------------------------|-------------------------------------|-----------------------|------------------------------|------------------------|-------------------------|

|                         | employment                 |                                     | resolution            |                              |                        |                         |

|                         |                            | fast                                | low-leakage STT-RAM   |                              |                        | periodic refresh+       |

| Sun et al.[161]         | yes                        | (volatile STT-RAM)                  | & data migration      | no                           | N/A                    | exhaustive data         |

|                         |                            |                                     |                       |                              |                        | migration               |

|                         |                            | fast                                | Hybrid SRAM &         |                              |                        | periodic refresh+       |

| Valero et al.[166]      | no                         | (SRAM banks)                        | eDRAM banks           | no                           | N/A                    | swap between            |

|                         |                            |                                     | design                |                              |                        | SRAM & eDRAM            |

| samavatian et al.[147]  | yes                        | fast                                | low-leakage STT-RAM   | no                           | N/A                    | periodic refresh+       |

|                         |                            | (volatile STT-RAM)                  | & data migration      |                              |                        | data migration          |

|                         |                            | fast                                | low-leakage STT-RAM   |                              |                        | write back dirty        |

| Jog et al.[79]          | yes                        | (volatile STT-RAM)                  | & buffering-based     | no                           | N/A                    | blocks+ buffering       |

|                         |                            |                                     | refresh scheme        |                              |                        |                         |

| RRAP                    |                            | fast                                | low-leakage STT-RAM   |                              |                        |                         |

| (approach in Chapter 5) | yes                        | (volatile STT-RAM)                  | & data movement       | yes                          | RRAPclusive            | periodic refresh        |

|                         |                            |                                     | reduction             |                              |                        |                         |

Table 2.1: Comparison of hybrid cache design techniques

#### 2.3 In-Memory Data Management to Minimize Data Movement

The continuous demand for accelerating the analysis and process of Big Data has shifted the paradigm of conventional computing-centric model towards data-centric architecture. This transition is driven by the aggressive CMOS technology scaling trends and advancements in fabrication process which enable the integration of billions of transistors into a small-scale die area to elevate the performance. These achievements are coupled with the advent of many-core processors that provides numerous number of computation nodes to schedule and perform multitasking workloads. The employment of ultra-fast many-core processors in the modern computers has significantly accelerated the arithmetic execution and calculation of logic which were bottleneck of computation in the past. Thus, the nature of computing-centric model which is based on moving large volume of data from/to memory storage to/from processing nodes for execution/restore has become ineffective. In contrast, the data-centric model has received significant attention in which the processing nodes are arranged to be placed close to the location of data, resulting in remarkable reduction of the cost for data movement [14].

Apart from the advancements in designing high performance many-core processors, the progress of tightly stacking logic and memory elements in a package has enabled the researchers to redesign the conventional Processing-In-Memory (PIM) concept for in-memory big-data processing [8]. Ahn et al. [8] tuned a PIM accelerator for large-scale graph processing called Tesseract. Tesseract is equipped with efficient communication scheme to hide long access latency between different cores and to assure the atomic memory update operation. Regarding to the specialized memory access characteristics of graph processing workloads, new hardware prefetchers are utilized in Tesseract to enhance the utilization of memory bandwidth. Tesseract can improve the delivered performance by around one order of magnitude compared to the baseline system while reducing the energy consumption by 87% on average.

The Rollback-Free Value Prediction (RFVP) technique is one of the approximation techniques that alleviates the memory wall through approximation of the load value [176]. However, due to the nature of prediction methodologies in which the predicted value can be inaccurate, thus a sensitive applications data structure can be contaminated.

Farmahini-Farahani et al. [51] proposed to apply 3D-stack technology for connecting Coarse-Grain Reconfigurable Accelerators (CGRAs) on top of off-chip DRAM units using Through-Silicon Vias (TSVs). This schematic, referred as DRAMA, aims to offload data-intensive operations to CGRAs while the processor executes the remaining parts of the program. The main reason is that the processing of data will be taken place much closer to memory units which results in significant reduction of the cost required for data movement. The Near-DRAM Acceleration (NDA) architecture proposed by Farmahini-Farahani et al. [52] also enables processing data using CGRAs which are 3D-stacked atop DRAM devices. NDA architecture requires trivial change in DRAM device's I/O circuit while host processor design remains unchanged. NDA can achieve 1.67X higher performance than the existing accelerators within the processor while consuming 68% lower energy for data transfer.

Guo et al. [67] proposed a novel PIM-based architecture, referred as AC-DIMM, to employ associative search engine along with processing in memory. To maximize the AC-DIMM throughput, associative TCAM accelerator implemented by STT-MRAM devices are used while the store of key-value pair is optimized to be located in the same TCAM row. These considerations enable AC-DIMM to outperform conventional RAM-based system by around 4.2X while consuming 6.5X lower energy.

The comparative advantages of the different approaches to tackle the memory performance bottleneck by leveraging techniques such as near-memory processing [132, 133], accelerator-based hardware architectures [59], and approximate computing [45] to reduce data transfer cost are listed in Table 2.2.

| Methodology   | Data Quality | 3D-stacked Memory Subsystem |                     | Beneficial for Irregular        |  |

|---------------|--------------|-----------------------------|---------------------|---------------------------------|--|

|               |              | Integration                 | Overhead            | Access Pattern                  |  |

| RFVP [176]    | approximate  | N/A                         | prediction stage    | no                              |  |

| PEI [9]       | exact        | yes, with DRAM              | dedicated processor | restricted to temporal locality |  |

| NDA [49]      | exact        | yes, near-DRAM              | coarse-grained      | yes                             |  |

| Tesseract [8] | exact        | yes, with DRAM              | fixed bank design   | yes, for graph-structured data  |  |

Table 2.2: Comparison of state-of-the-art techniques for reducing off-chip data transfer.

# CHAPTER 3: BIT-UPSET VULNERABILITY FACTOR ANALYSIS FOR EDRAM-BASED LLC

In order to preserve data integrity in eDRAM, the charge in each capacitor must be refreshed periodically. This means the data stored in eDRAM is required to be read out and written back into cell by each refresh operation. This new lifetime sequence needs to be investigated to accurately reveal how different lifetime sequences of cache data contribute to vulnerability. Thus, despite the fact that the most previous works studied the trade-offs between performance, energy consumption and achieved cache reliability, more systematic study of cache vulnerability is still needed to present a detailed lifetime model for data arrays in eDRAM LLC.

Given these challenges, we propose a more accurate and application-relevant lifetime model while taking the refresh operation scheme for LLC into consideration. The proposed lifetime model distinguishes among six lifetime sequences for each data item located in eDRAM LLC according to the previous activity and current one. These sequences are further categorized into two groups, *vulnerable* and *nonvulnerable* sequences. A vulnerable sequence is characterized by the fact that any error that is encountered during this sequence has the potential to be either consumed by the CPU or committed to memory by a write. However, if the exposure occurs during nonvulnerable sequences has the potential to be either consumed by the sequence, no program failure will result.

The proposed model relies on LLC ensemble behavior analysis using trace files obtained from PARSEC benchmark suites running on an extended version of MARSSx86 [29]. The results of our analysis can be used to develop efficient protection techniques for high reliable eDRAM cache design.

Figure 3.1: Typical eDRAM system organization, (a) eDRAM bank structure, (b) Precharged state, (c) Wordline raised, (d) Charge sharing, (e) Sensing.

# 3.1 eDRAM Cell Organization and Operation

The eDRAM cells are organized in a two-dimensional arrays called *bank* as illustrated in Fig. 3.1 (a). Each eDRAM cell consists of a dedicated transistor which connects the *bitline* wire to its associated capacitor. The access transistor in a *row* are connected and controlled by a wire called *wordline*.

The following steps are required to access the data stored in each *row*:

- First, all bitline wires in the bank need to be *precharged* to V<sub>DD</sub>/2 as illustrated in Fig. 3.1 (b).

- As shown in Fig. 3.1 (c), the row is activated with wordline overdriven to  $V_{DD}$  which follows by connecting all capacitors in the row to their corresponding bitlines.

- In the *Charge Sharing* process, the charge either flows from capacitor to bitline or vice versa according to the amount of charge stored in capacitor.

- The voltage change in the bitline is detected and enlarged using the respective connected

sense amplifier. As the final step shown in Fig. 3.1 (e), the sense amplifier drives the bitline entirely either to  $V_{DD}$  or 0 V.

Therefore, the cells of the enabled row can be read by sensing or be written by driving the voltage on the associated bitlines.

# 3.1.1 eDRAM Retention Time for Different Technology Node

The charge of capacitor is lost overtime through access transistor which makes the refresh operation inevitable for eDRAM celsl. The threshold voltage ( $V_{th}$ ) of access transistor plays an important role to determine the retention time of eDRAM cell. The high  $V_{th}$  leads to lower leakage which means the eDRAM cell retains state for longer time while low  $V_{th}$  provides less retention time due to higher leakage power. The retention time of an eDRAM cell is defined as the leakage time at which the capacitor loses  $\alpha$  portion of the stored charge [98] and can be defined as below:

$$T_{ret} = \frac{\alpha}{\beta} \tag{3.1}$$

where  $\alpha$  is the allowable amount of storage charge which capacitor can lose and  $\beta$  is the off drain current through access transistor. Kong et al. [98] showed that the eDRAM cell can stay operational while  $\alpha$  equals to 6/10th of the stored charge. The  $T_{ret}$  can also be expressed in Eq. 3.2 which comes from [98] and [4].

$$T_{ret} = \alpha \times \frac{L}{W} \times 10^{V_{th}/S_{th}} \times 10^9/300 sec$$

(3.2)

where W and L are the width and length of the access transistor channel, and  $S_{th}$  is subthreshold slope. The detail of Eq. 3.2 can be found in [4].

As the technology scales down, the  $V_{th}$  of access transistor reduces accordingly. Hence, if the  $V_{th}$  is substituted with a smaller  $V_{th}$  in Eq. 3.2, the eDRAM retention time is reduced. This phenomenon has been shown in Fig. 3.2 in which the probability of a retention failure in eDRAM cell fabricated by 32nm technology node is higher than 45nm eDRAM cell (derived from Figure 3 in [98]).

Figure 3.2: eDRAM retention time distribution for 45nm and 32nm technology nodes.

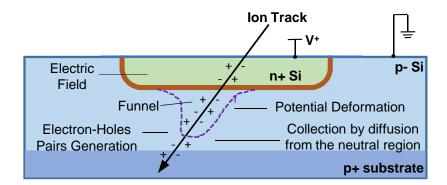

### 3.1.2 Single Event Effect

The Single Event Effect (SEE) is induced by the interaction of the high-energy particles with electronic components as illustrated in Fig. 3.3. The generated electron and hole pairs are collected into cell junctions through the so-called funneling mechanism. Most of the charge is obsorbed at the junction via a deformation of the junction potential. The remaining charge is diffused and collected in the substrate. The access transistors in eDRAM module are sensitive to the particle's radiation because the stored data is required to be blocked when no read or write is operated. A particle can induce a SEU when it strikes at the drain region of an off-MOSFET. The voltage at the struck node drifts and turn the radiation-induced current into a voltage transient because the released charge is collected at the reverse-biased drain p-n junction. If the drain potential is smaller than the cell switching voltage, the current decreases the potential at the drain node and likely

changes the initial state [16][175]. Radiation-induced Soft Error Rate (SER) can be expressed as:

$$SER \approx Area \times exp^{Q_C/Q_{Coll}}$$

(3.3)

where Area is diffusion area of collected charges which is linearly proportional to the cell size of eDRAM,  $Q_C$  is the minimum collected charges incurring soft error and  $Q_{Coll}$  is the collected charges compiled by drift ( $Q_{drift}$ ) in depletion layer and diffusion ( $Q_{diff}$ ) from the silicon substrate. As the size of cell junctions shrinks in eDRAM, the amount of charge collected decreases due to lowered-depth of sensitive depletion region. However, the amount of  $Q_C$  decreases even more rapidly due to the power supply reduction that is used for increasing the performance of succeeding generation of eDRAM. Thus, the SER exponentially increases for a new generation device activated by lowered power supply. Empirical data is presented in [47].

Figure 3.3: The impact of ionizing particle in a reverse-biased p-n junction.

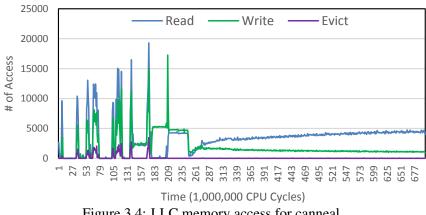

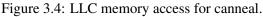

# 3.1.3 LLC Reference Characteristics

The eDRAM LLC is shared by all on-die cores to offer worthwhile benefits for such workloads exhibiting significant data-sharing. As illustrated in Fig. 3.4 and 3.5, the time varying behavior of each benchmark shows multiple sequences of cache reliability issue where some sequences are

vulnerable and some sequences that are not. For example, the *streamcluster* benchmark is a read intensive workload in which a high proportion of shared cachelines are accessed by consecutive read memory operations. Such a cache line generation information can be exploited to show the correlation among the LLC access pattern and the cacheline vulnerability factor.

Figure 3.5: LLC memory access for streamcluster.

# 3.2 The Proposed eDRAM Vulnerability Estimation Algorithm

# 3.2.1 A general Lifetime Model for Data Array

A cache line is brought into LLC on a read or write miss. Then, it will be accessed either by reads or writes for a couple of times, and finally, it will be replaced by a new cache line. According to the existing LLC reliability analysis methodologies [168][114], the lifetime of a cacheline can be categorized into the following sequences:

- Read-Read (RR): the lifetime between two consecutive reads

- Write-Read (WR): the lifetime of a write operation up until its first read

- Write-Evict (WE): the lifetime between the last write and the cache line replacement by a new cacheline

- Read-Evict (RE): the lifetime between the last read before cache line replacement

- Read-Write (RW): the lifetime between the last read before the write operation

- Write-Write (WW): the lifetime between two consecutive writes

A *lifetime sequence* is defined as *vulnerable sequence* if an error may propagate out of cache, either to the CPU or to the lower level of memory hierarchy. Apparently, the first four intervals, RR, WR, WE, and RE can be considered as vulnerable sequences. The reason for this is that if any error occurs in aforementioned sequences, it has this potential to be either read by CPU or committed to the memory. On the other hand, the RW and WW sequences are *nonvulnerable sequence* in which if an error occurs, it is simply masked off through overwritten operation, presenting no program failure.

# 3.2.2 The Proposed Lifetime Model for eDRAM Data Array

The critical charge of eDRAM is dependent on write voltage, storage and bit-line capacitance and the minimum voltage difference required by the sense amplier [153]. These factors make eDRAM cell vulnerable against soft error for a particular portion of lifetime sequence unlike SRAM cell which is vulnerable for the entire sequence period. There are three kinds of SER modes for eDRAM cell wherein, if any exposure occurs it may result in potential errors:

- Memory mode: This SER mode is the consequence of the injection of a high-energy particle into an eDRAM cell when logic 1 is stored in the storage capacitance.

- Bit mode: The soft errors are produced in this mode if SEU strikes a bit-line junction during the bit/bit-bar floating time and logic 1 is stored in the cell to be read.

- Bit-bar mode: If a SEU is injected into bit-bar junction during bit/bit-bar floating time and logic 0 is stored in the cell to be read, it can produce bit-bar mode soft errors.

The error produced is vulnerable exclusively if it occurs in abovementioned general lifetime sequences because it is either consumed by CPU or committed to the memory. Thus, to estimate the vulnerable sequence of eDRAM, it is necessary to integrate the existing lifetime model with the SER modes for eDRAM. In order to estimate the BUVF, all three kinds of SER modes for eDRAM cell must be considered. The memory and bit modes soft errors are taken place when the storage node has a logic 1 value while bit-bar mode occurs when the eDRAM cells contains logic 0 value.

To estimate BUVF for eDRAM cell containing logic 1 value, the entire lifetime sequence can be considered as vulnerable sequence if the second memory operation in two consecutive accesses to that data item is either read or evict. As shown in Fig. 3.6 (a), the *sequence A* is a WW sequence which is not vulnerable against soft errors. The *sequence B* represents the vulnerable

WR sequence in which the last write operation is following by three refresh operations and then by a read operation.

On the other hand, the BUVF for eDRAM cell containing logic 0 value is estimated according to the bit/bit-bar floating time allocated in vulnerable sequence. As shown in Fig. 3.6 (b), *sequence* C, E and G are vulnerable sequences where the eDRAM cell is in its refresh mode when logic 0 is stored in it. Even though this vulnerable sequence may seem negligible, it shares a significant portion of BUVF when we take the large size of eDRAM and number of refresh operations originating within each vulnerable sequence into consideration.

Figure 3.6: The lifetime of eDRAM cell. (a) the logic 1 is stored in the cell, (b) the logic 0 is stored in the cell.

# 3.2.3 Bit-Upset Vulnerability Factor Analysis of eDRAM Data Array

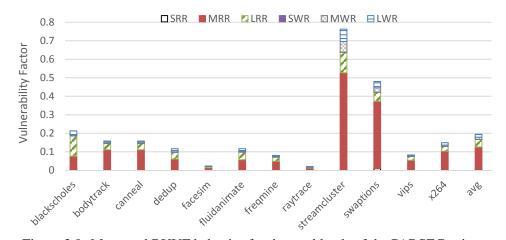

The cache BUVF introduced in this work is defined as the average rate of data items in vulnerable sequences over the total data items that cache can accommodate during the execution. BUVF can be calculated as follows:

$$BUVF = \frac{(vdi(0) + vdi(1))}{\sum(data\_items \times exec\_time)}$$

(3.4)

where vdi(0) and vdi(1) are the vulnerable period for eDRAM cell containing logic value 0 and 1, respectively. Thus, BUVF can be calculated as the summation of  $BUVF_0$  and  $BUVF_1$  for eDRAM cell storing logic value 0 and 1, respectively. The  $BUVF_0$  can be calculated as:

$$BUVF_{0} = \frac{\sum_{i=1}^{n} (data\_item(0)_{i} \times ref\_dur \times \sum_{j=1}^{l} vul\_sequence_{j})}{\sum (data\_items \times exec\_time)}$$

(3.5)

where  $data_item(0)_i$  is the  $i^{th}$  eDRAM cell storing logic 0 value,  $ref_dur$  is the period time for each refresh operation and l represents the number of refreshes occurring in the duration time of  $j^{th}$  vulnerable sequence for  $data_item(0)_i$ . Meanwhile, the  $BUVF_1$  is:

$$BUVF_{1} = \frac{\sum_{i=1}^{n} (data\_item(1)_{i} \times \sum_{j=1}^{k} vul\_sequence_{j})}{\sum (data\_items \times exec\_time)}$$

(3.6)

where  $data_i item(1)_i$  is the  $i^{th}$  eDRAM cell containing logic 1 value,  $vul\_sequence_j$  is the duration time of  $j^{th}$  vulnerable sequence for  $data_i item(1)_i$  and k represents the boundary which is the end of memory access to  $data_i item(1)_i$ .

A high value of BUVF for a data item located in eDRAM LLC indicates reduced resiliency to soft errors. Therefore, we recast the problem of reliable eDRAM LLC design as a straightforward

search for reduced BUVF.

#### 3.3 Experimental Setup

We analyze LLC ensemble behavior using traces from an extended version of MARSSx86 [29]. The traces capture access type to LLC which are typically read, write, and evict. We model a Chip MultiProcessor (CMP) with eight single-threaded x86 cores. Each core has private L1 and L2 caches and the LLC is shared among all the cores to increase the performance. The detail of our model can be found in Table 5.3. Twelve applications from the PARSEC benchmarks suite are selected and executed 500 million instructions starting at the Region Of Interest (ROI) after warming up the cache for 5 million instructions. Furthermore, the simsmall input sets are used for all PARSEC applications.

We evaluate the proposed scheme for all vulnerable sequences. However, RR and WR are the dominant contributors to the BUVF of LLC data array because the large size of LLC provides long-term residency for data items in LLC which results in the remained vulnerable sequences to be less active during program execution. Accordingly, the results of data vulnerability analysis in two major contributors to the BUVF are described in this paper.

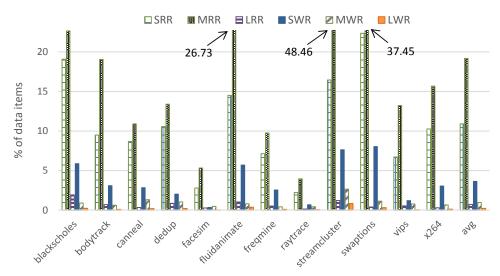

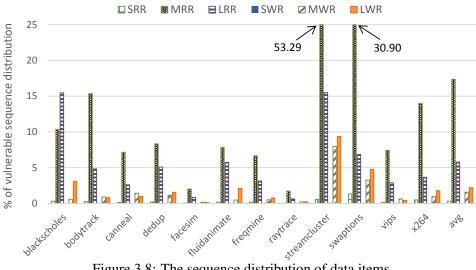

Fig. 3.8 (a) shows the proportion of data pieces resided in vulnerable sequences. We categorized each vulnerable sequence into three lengths based on the time interval between two consecutive accesses to data: *1) Short, 2) Medium, 3) Long*, denoted as SRR/SWR, MRR/MWR, or LRR/LWR, respectively. The short duration sequence indicates data instances with an interval less than 1 million cycles while this interval increases from 1 million to 50 million cycles for medium sub-vulnerable sequence. The data elements with intervals exceeding 50 million cycles are considered as long duration sequence. For example, the rightmost orange column for each benchmark repre-

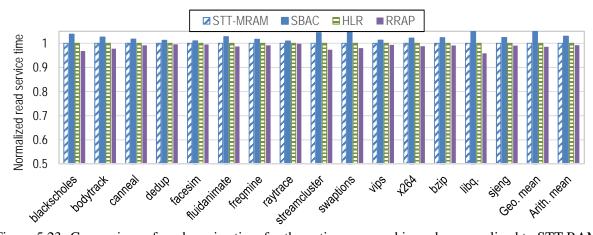

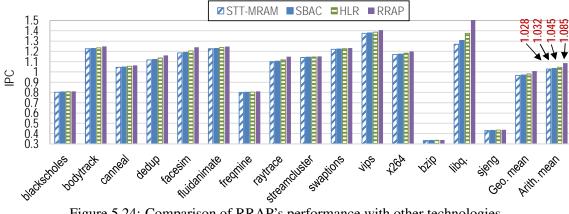

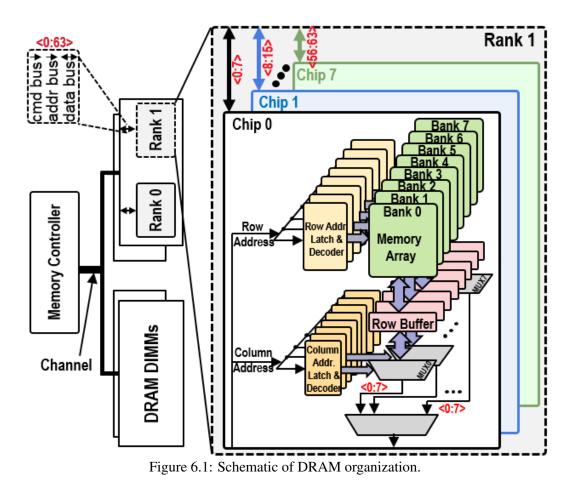

sents the long-term WR sequence which averages 0.23% across the suite. The second green column from the left shows the RR elements with medium duration interval contributing the largest share to the BUVF.