University of Central Florida

Electronic Theses and Dissertations, 2004-2019

2015

## Design of Novel Devices and Circuits for Electrostatic Discharge Protection Applications in Advanced Semiconductor Technologies

Zhixin Wang University of Central Florida

Part of the Electrical and Electronics Commons Find similar works at: https://stars.library.ucf.edu/etd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS Citation**

Wang, Zhixin, "Design of Novel Devices and Circuits for Electrostatic Discharge Protection Applications in Advanced Semiconductor Technologies" (2015). *Electronic Theses and Dissertations, 2004-2019.* 1436. https://stars.library.ucf.edu/etd/1436

# DESIGN OF NOVEL DEVICES AND CIRCUITS FOR ELECTROSTATIC DISCHARGE PROTECTION APPLICATIONS IN ADVANCED SEMICONDUCTOR TECHNOLOGIES

by

ZHIXIN WANG B.S. South China University of Technology, 2009 M.S. University of Central Florida, 2012

A dissertation submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Spring Term 2015

Major Professor: Juin J. Liou

© 2015 Zhixin Wang

#### ABSTRACT

Electrostatic Discharge (ESD), as a subset of Electrical Overstress (EOS), was reported to be in charge of more than 35% of failure in integrated circuits (ICs). Especially in the manufacturing process, the silicon wafer turns out to be a functional ICs after numerous physical, chemical and mechanical processes, each of which expose the sensitive and fragile ICs to ESD environment. In normal end-user applications, ESD from human and machine handling, surge and spike signals in the power supply, and wrong supplying signals, will probably cause severe damage to the ICs and even the whole systems.

Generally, ESD protections are evaluated after wafer and even system fabrication, increasing the development period and cost if the protections cannot meet customer's requirements. Therefore, it is important to design and customize robust and area-efficient ESD protections for the ICs at the early development stage. As the technologies generally scaling down, however, ESD protection clamps remain comparable area consumption in the recent years because they provide the discharging path for the ESD energy which rarely scales down. Diode is the most simple and effective device for ESD protection in ICs, but the usage is significantly limited by its low turn-on voltage. MOS devices can be triggered by a dynamic-triggered RC circuit for IOs operating at low voltage, while the one triggered by a static-triggered network, e.g., zener-resistor circuit or grounded-gate configuration, provides a high trigger voltage for high-voltage applications. However, the relatively low current discharging capability makes MOS devices as the secondary choice. Silicon-controlled rectifier (SCR) has become famous due to its high robustness and area efficiency, compared to diode and MOS. In this dissertation, a comprehensive design methodology for SCR based on simulation and measurement are presented for different advanced commercial technologies. Furthermore, an ESD clamp is designed and verified for the first time for the emerging GaN technology.

For the SCR, no matter what modification is going to be made, the first concern when drawing the layout is to determine the layout geometrical style, finger width and finger number. This problem for diode and MOS device were studied in detail, so the same method was usually used in SCR. The research in this dissertation provides a closer look into the metal layout effect to the SCR, finding out the optimized robustness and minimized side-effect can be obtained by using specific layout geometry. Another concern about SCR is the relatively low turn-on speed when the IOs under protection is stressed by ESD pulses having very fast rising time, e.g., CDM and IEC 61000-4-2 pulses. On this occasion a large overshoot voltage is generated and cause damage to internal circuit component like gate oxides of MOS devices. The key determination of turn-on speed of SCR is physically investigated, followed by a novel design on SCR by directly connecting the Anode Gate and Cathode Gate to form internal trigger (DCSCR), with improved performance verified experimentally in this dissertation. The overshoot voltage and trigger voltage of the DCSCR will be significantly reduced, in return a better protection for internal circuit component is offered without scarifying neither area nor robustness.

Even though two SCR's with single direction of ESD current path can be constructed in reverse parallel to form bidirectional protection to pins, stand-alone bidirectional SCR (BSCR) is always desirable for sake of smaller area. The inherent high trigger voltage of BSCR that only fit in highvoltage technologies is overcome by embedding a PMOS transistor as trigger element, making it highly suitable for low-voltage ESD protection applications. More than that, this modification simultaneously introduces benefits including high robustness and low overshoot voltage.

For high voltage pins, however, it presents another story for ESD designs. The high operation voltages require that a high trigger voltage and high holding voltage, so as to reduce the false trigger and latch-up risk. For several capacitive pins, the displacement current induced by a large snapback will cause severe damage to internal circuits. A novel design on SCR is proposed to minimize the snapback with adjustable trigger and holding voltage. Thanks to the additional a PIN

diode, the similar high robustness and stable thermal leakage performance to SCR is maintained.

For academic purpose of ESD design, it is always difficult to obtain the complete process deck in TCAD simulation because those information are highly confidential to the companies. Another challenge of using TCAD is the difficulty of maintaining the accuracy of physics models and predicting the performance of the other structures. In this dissertation a TCAD-aid ESD design methodology is used to evaluate ESD performance before the silicon shuttle.

GaN is a promising material for high-voltage high-power RF application compared to the GaAs. However, distinct from GaAs, the leaky problem of the schottky junction and the lack of choice of passive/active components in GaN technology limit the ESD protection design, which will be discussed in this dissertation. However, a promising ESD protection clamp is finally developed based on depletion-mode pHEMT with adjustable trigger voltage, reasonable leakage current and high robustness.

To my wife Jiaqi Tan, my parents Shikun Wang and Cuilian Guo, my parents in law Guozao Tan and Fengyi Yu.

#### ACKNOWLEDGMENTS

Ph.D career is a long journey during which the problems and stress from both the academic research and the routine life must be overcome. However, when I retrospect this period, I am not alone on the path towards the degree. This is because my families, mentors, colleagues and friends offer me with kind supports physically and mentally. Without their helps and encouragements it will be impossible for me to achieve the academic success and pursue the Ph.D degree. Dr. Juin J. Liou (UCF) is the 1st person I want to thank and appreciate to. He creates a very good platform and environment for academic research at UCF. He is good at inspiring research enthusiasm and bringing in brain storm, which are very important for innovation. Dr. Liou's enriched experience in ESD makes the research and paper preparation enjoyable. It is his professional supervision and strong back-up that make my creativities become true.

I thank Dr. James E. Vinson (Intersil), who is the mentor in the Intersil Project. Dr. Vinson is always patient to answer my question and feedback to me with very professional suggestions on the high voltage ESD protection design and EOS simulation. He tries not to tell me what to do, but instead, lead me to the proper path so that I can find myself with correct answers. I thank Jean-Michel Tschann (Intersil) for his kind support on the layout and tapeout.

I thank Dr. Maxim Klebanov (Allegro) for the useful discussion and sufficient support on the high voltage ESD protection design proposal, layout and tapeout, for his kind assistance on the Boston trip. I thank Dr. Richard Cooper (Allegro) for his valuable opinions on improving the ESD design, and Mr. Sebastian Courtney (Allegro) for his help on TCAD simulation and device characterizations.

I thank Dr. Michael Chain (Micron) and Dr. Xiaofeng Fang (Apple), who are my mentors at Micron Technology for providing me invaluable instructions and freedom to perform the Machine Model upgrade on the traditional TLP system.

I thank Dr. Yuan-Jiann Sun (UCF) and Dr. Kalpathy B. Sundaram (UCF) for their supports on the important research discussions and measurement equipments.

I thank my dissertation committee, including Dr. Juin J. Liou, Dr. James E. Vinson, Dr. Yuan-Jiann Sun, Dr. Ye Jin (UCF), and Dr. Xun Gong (UCF) for spending their time on reviewing my dissertation and their critical suggestions about improving my research.

I express my gratefulness to Mr. Ruei-Cheng Sun (Feng Chia University) for the exciting discussion of innovative ideas of ESD clamp and sharing me with his wisdom, to Mr. Kuan-Liang Cho (Chang Gung University) and and Mr. Alex Yang (Chang Gung University) for the valuable discussion and the layout support on the low-voltage and GaN ESD protects. Thank Dr. Don-Gey Liu and Dr. Hsien-Chin Chiu (Chang Gung University) for the cooperation opportunities.

I acknowledge all my friends and colleagues who join my life in this period and share with me their wonderful time, experience and knowledge. It is my pressure to have chance working with great people at Dr. Liou's lab, including Javier Salcedo (ADI), Slavica Malobabic (Maxim), David Ellis (Uber), Blerina Aliaj (Maxim), Qiang Cui (RFMD), Wen Liu (IBM), You Li (IBM), Brain Chang (Lockheed Martin), Xiang Liu (Microchip), Sirui Luo (UCF), Yunfeng Xi (UCF), Meng Miao (UCF), Wei Liang (UCF), Aihua Dong (UCF), and colleagues including Haiyuan Zhang, Xirong Liu, Wanling Deng, Karthik Padmanabhan.

Furthermore, I thank Don Harper and Denise Tjon Ket Tjong for their help of maintaining the lab servers.

Moreover, I thank my supervisors, Dr. Bin Li, Dr. Zhaohui Wu, Dr. Yurong Liu, Dr. Guoyuan Li and Dr. Quanlong Ding at South China University of Technology for their training that helps me establish solid knowledge and preparations for my success in Ph.D career. Finally, special thank my lovely wife Jiaqi Tan, my parents Shikun Wang and Cuilian Guo, and my parents in-law Guozao Tan and Fengyi Yu, for your love and forgiveness. Thank you to enter my life and make it wonderful!

## TABLE OF CONTENTS

| LIST ( | OF FIGU | JRES                                   |

|--------|---------|----------------------------------------|

| LIST ( | OF TAB  | LESxxi                                 |

| СНАР   | TER 1:  | INTRODUCTION                           |

| 1.1    | ESD N   | Nature and Protection for ICs          |

| 1.2    | ESD C   | Characterization Standards             |

|        | 1.2.1   | Human Body Model (HBM)                 |

|        | 1.2.2   | Machine Model (MM)                     |

|        | 1.2.3   | Charged Device Model (CDM)             |

|        | 1.2.4   | System Level IEC 61000-4-2             |

|        | 1.2.5   | Human Metal Model (HMM)                |

|        | 1.2.6   | Transmission Line Pulsing (TLP) Tester |

|        | 1.2.7   | ESD Test Methods                       |

| 1.3    | ESD F   | Protection Performance Criteria        |

|        | 1.3.1   | Static Performance                     |

|        | 1.3.2   | Dynamic Performance                    |

| 1.4  | ESD Protection Strategy                                                    | 16 |

|------|----------------------------------------------------------------------------|----|

|      | 1.4.1 Rail-based ESD Protections                                           | 17 |

|      | 1.4.2 Localized ESD Protections                                            | 17 |

| 1.5  | Conclusion and Remark                                                      | 18 |

| СНАР | TER 2: LAYOUT OPTIMIZATION FOR SILICON-CONTROLLED RECTIFIER .              | 19 |

| 2.1  | Introduction                                                               | 19 |

| 2.2  | Geometry and Metal Pattern of LSCR                                         | 20 |

| 2.3  | Results and Discussions                                                    | 22 |

| 2.4  | Conclusion and Remark                                                      | 26 |

| СНАР | TER 3: HIGH SPEED ESD PROTECTION DESIGN FOR LOW-VOLTAGE CMOS<br>TECHNOLOGY | 28 |

| 3.1  | Introduction                                                               | 28 |

| 3.2  | Direct-connected SCR                                                       | 32 |

| 3.3  | TLP Measurement                                                            | 35 |

| 3.4  | vf-TLP Measurement                                                         | 38 |

| 3.5  | Thermal Stability of Leakage Current                                       | 39 |

| 3.6  | ESD Performance Comparisons                                                | 41 |

| 3.7  | Conclusion and Remark                                         | 42 |

|------|---------------------------------------------------------------|----|

| CHAF | PTER 4: BIDIRECTIONAL ESD PROTECTION DESIGN FOR LOW-VOLTAGE   |    |

|      | CMOS TECHNOLOGY                                               | 43 |

| 4.1  | Introduction                                                  | 43 |

| 4.2  | Design and Operation of PTBSCR                                | 44 |

| 4.3  | Result and Discussion                                         | 46 |

|      | 4.3.1 TLP Results and Turn-On Mechanism                       | 46 |

|      | 4.3.2 Layout Parameters                                       | 49 |

|      | 4.3.3 Leakage Current                                         | 55 |

|      | 4.3.4 vf-TLP Results                                          | 58 |

|      | 4.3.5 Comparisons                                             | 59 |

| 4.4  | Conclusion and Remark                                         | 60 |

| CHAP | TER 5: NO-SNAPBACK ESD PROTECTION DESIGN FOR HIGH-VOLTAGE BCD |    |

|      | TECHNOLOGY                                                    | 63 |

| 5.1  | Introduction                                                  | 63 |

| 5.2  | NS-SCR Structure and Operation                                | 64 |

| 5.3  | Measurement and Discussion                                    | 66 |

| 5.4    | Thermal Stability of Leakage Current            | 69 |

|--------|-------------------------------------------------|----|

| 5.5    | Conclusion and Remark                           | 70 |

| CHAP   | TER 6: ESD PROTECTION DESIGN FOR GAN TECHNOLOGY | 72 |

| 6.1    | Introduction                                    | 72 |

| 6.2    | ESD Clamp Structure                             | 73 |

| 6.3    | Measurement Results and Discussions             | 76 |

| 6.4    | Failure Analysis                                | 79 |

| 6.5    | Conclusion and Remark                           | 80 |

| CHAP   | TER 7: CONCLUSION                               | 81 |

| LIST C | OF REFERENCES                                   | 84 |

## **LIST OF FIGURES**

| Figure 1.1: Equivalent HBM Simulator Circuit with Loads.                           | 3  |

|------------------------------------------------------------------------------------|----|

| Figure 1.2: Equivalent MM Simulator Circuit with Loads.                            | 4  |

| Figure 1.3: Conceptual Schematic of the CDM tester.                                | 5  |

| Figure 1.4: Equivalent diagram of the IEC 61000-4-2 generator.                     | 6  |

| Figure 1.5: Equivalent circuit of TDR TLP tester with 50 ohm impedance             | 9  |

| Figure 1.6: TLP-measured voltage waveform with 20V pre-charged voltage on an OPEN. | 9  |

| Figure 1.7: TLP-measured current waveform with 20V pre-charged voltage on an OPEN. | 10 |

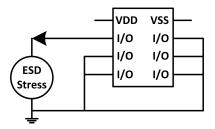

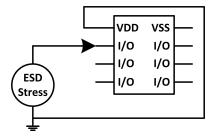

| Figure 1.8: Positive pin-to-pin ESD test mode                                      | 11 |

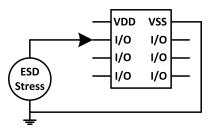

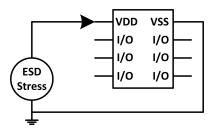

| Figure 1.9: Negative pin-to-pin ESD test mode                                      | 11 |

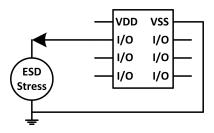

| Figure 1.10Positive-pin-to-VSS ESD test mode                                       | 11 |

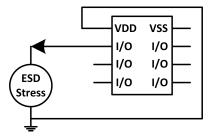

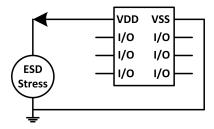

| Figure 1.11Negative-pin-to-VSS ESD test mode                                       | 12 |

| Figure 1.12Positive-pin-to-VDD ESD test mode                                       | 12 |

| Figure 1.13Negative-pin-to-VDD ESD test mode                                       | 13 |

| Figure 1.14Positive-VDD-to-VSS ESD test mode                                       | 14 |

| Figure 1.15Negative-VDD-to-VSS ESD test mode                                       | 14 |

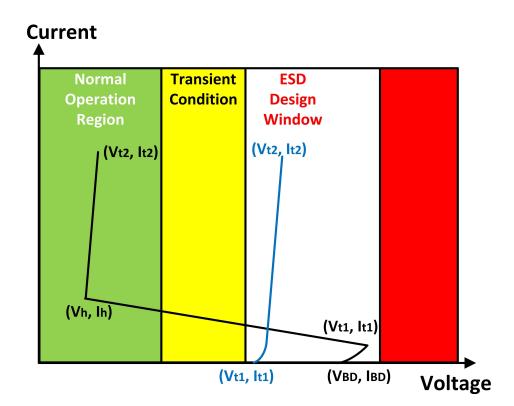

| Figure 1.16Typical ESD Design Window.                                              | 15 |

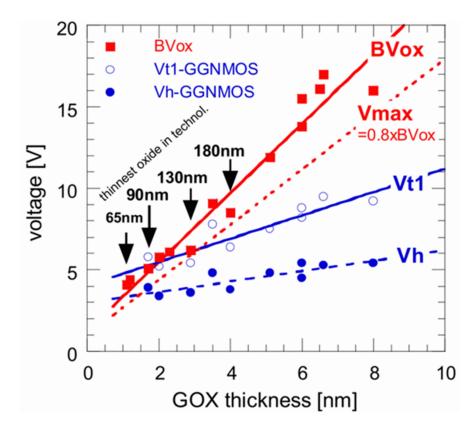

| Figure 1.17Transient breakdown of MOS gate oxide versus oxide thickness                  | 16 |

|------------------------------------------------------------------------------------------|----|

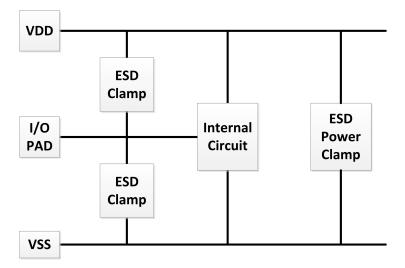

| Figure 1.18Conceptual diagram of rail-based ESD protection                               | 17 |

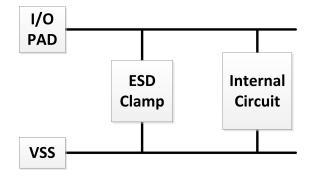

| Figure 1.19Conceptual diagram of localized ESD protection.                               | 18 |

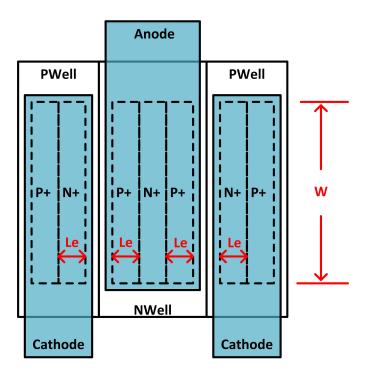

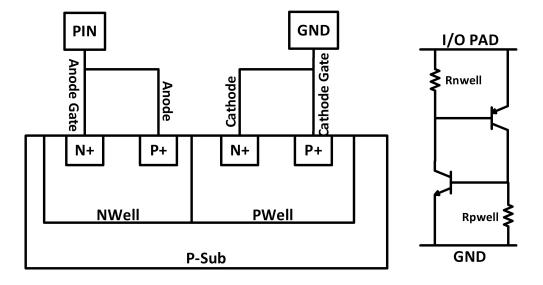

| Figure 2.1: Cross-section view of traditional LSCR                                       | 21 |

| Figure 2.2: Metal routing of SCR for parallel topology. W denotes the finger width. Le   |    |

| denotes the emitter lengths of bipolar transistors in SCR. Patterns in blue              |    |

| denote metal connections between SCR and Pads                                            | 22 |

| Figure 2.3: Metal routing of SCR for crossing topology. W denotes the finger width.      |    |

| Le denotes the emitter lengths of bipolar transistors in SCR. Patterns in blue           |    |

| denote metal connections between SCR and Pads                                            | 23 |

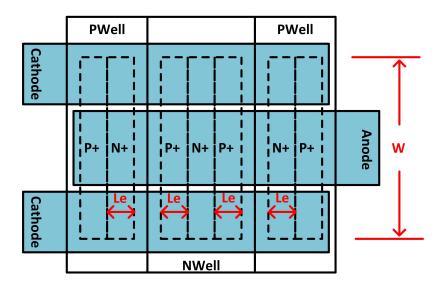

| Figure 2.4: TLP I-V curves with leakage current measurement for parallel and crossing    |    |

| topologies with W=40 $\mu$ m, N=2 and Le=0.9 $\mu$ m                                     | 24 |

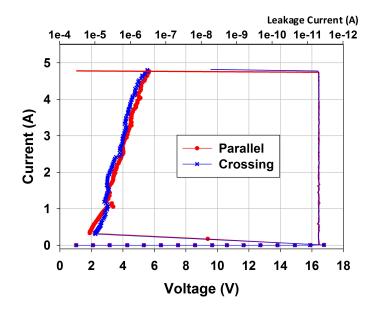

| Figure 2.5: Robustness and Current Density versus Device Width W for parallel and        |    |

| crossing topologies. Finger number N=2 and emitter length Le=0.9 $\mu$ m                 | 25 |

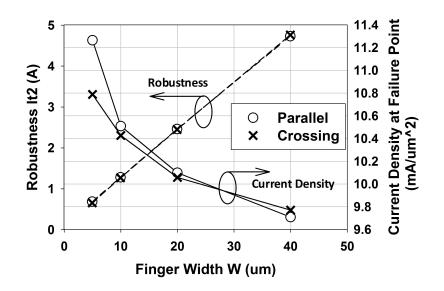

| Figure 2.6: Robustness and Current Density versus Finger Number N for parallel and       |    |

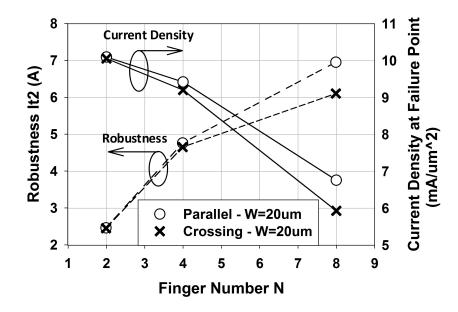

| crossing topologies. Device width W=20 $\mu$ m and emitter length Le=0.9 $\mu$ m.        | 26 |

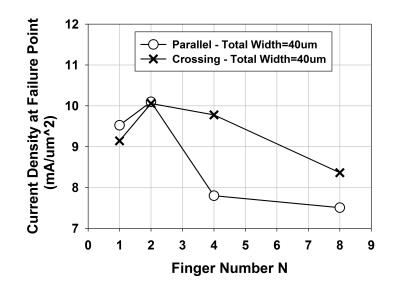

| Figure 2.7: Current Density versus Finger Number N for parallel and crossing topologies. |    |

| Total width (W*N) is fixed at 40 $\mu$ m when changing the finger number                 | 27 |

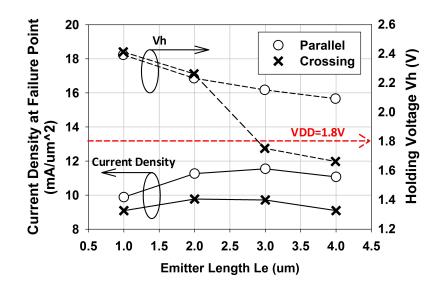

| Figure 2.8: Current Density and Holding Voltage versus Emitter Length Le for parallel    |    |

| and crossing topologies                                                                  | 27 |

| Figure 3.1: Cross-section view and equivalent circuit of traditional SCR                                                                     | 29 |

|----------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.2: Equivalent circuit of diode-triggered SCR                                                                                        | 31 |

| Figure 3.3: Cross-section view and equivalent circuit of traditional SCR                                                                     | 33 |

| Figure 3.4: Top view of the layout of DCSCR                                                                                                  | 34 |

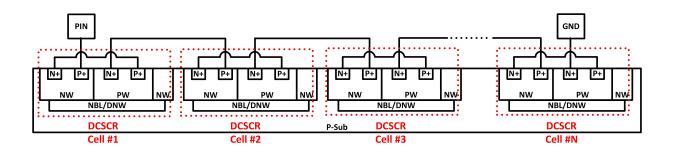

| Figure 3.5: Concept of stacking DCSCR cells for low-to-medium voltage ESD applications.                                                      | 34 |

| Figure 3.6: Cross-section view of stacking of multiple DCSCR cells for low-to-medium voltage ESD applications                                | 35 |

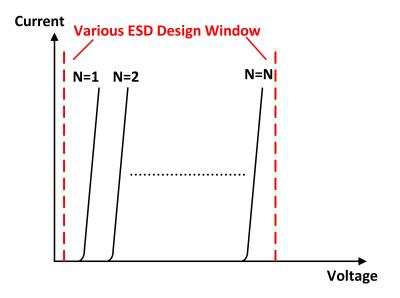

| Figure 3.7: Conceptual IV curves of stacked structure having different numbers of DC-SCRs                                                    | 35 |

| Figure 3.8: Cross-section view of DCSCR with dummy gate technique                                                                            | 36 |

| Figure 3.9: Comparison of TLP IV curves measured from the DCSCR with STI, DCSCR with dummy gate technique, traditional SCR, diode, and DTSCR | 37 |

| Figure 3.10Measured TLP IV curves of proposed stacking structures having different stacking numbers.                                         | 38 |

| Figure 3.11Measured transient waveforms of LSCR, DTSCRs, diode, the proposed DC-SCR, and the DCSCR with dummy gate structures.               | 40 |

| Figure 3.12DC sweep of the DCSCR, 2-stacked DCSCR, diode and DTSCR with three external diodes at 25 deg-C and 125 deg-C.                     | 41 |

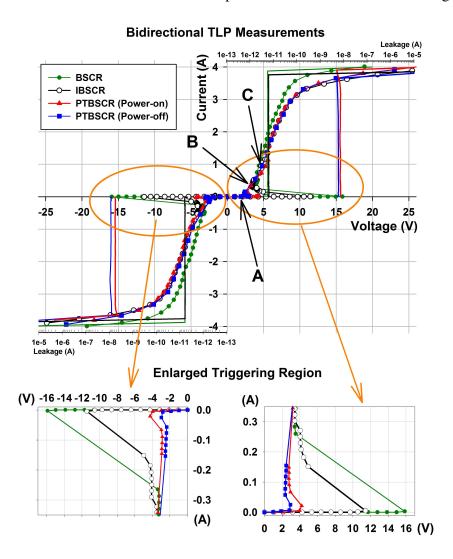

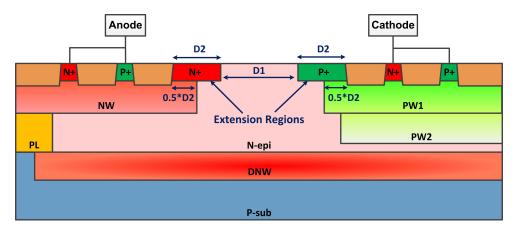

Figure 4.1: Cross-sectional view and equivalent circuit of the proposed PTBSCR. Red region: pMOS channel serving as the triggering path during ESD stress. . . . 45

|    | Figure 4.2: TLP I-V curves and leakage currents for the BSCR, IBSCR, and PTBSCR |

|----|---------------------------------------------------------------------------------|

|    | with gate floating (power-OFF) and gate biased at VDD=1.8 V (power-ON).         |

|    | Enlarged figures: detailed triggering behaviors for these devices. Lg=0.18      |

| 47 | $\mu$ m, D1 =0.9 $\mu$ m, and D2=1.3 $\mu$ m for the PTBSCR under measurement   |

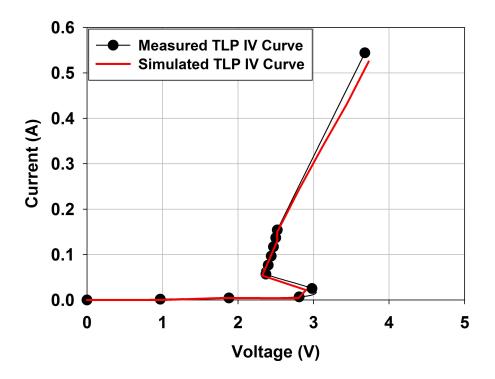

| Figure 4.3: Simulated and measured I-V curves of PTBSCR under power-off condition. |    |

|------------------------------------------------------------------------------------|----|

| Lg=0.18 $\mu$ m, D1=0.9 $\mu$ m, and D2= 1.3 $\mu$ m.                              | 48 |

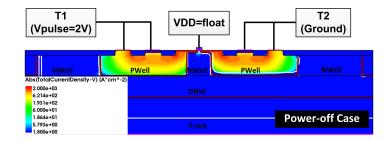

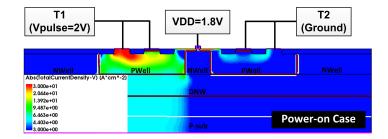

| Figure 4.4: TCAD-simulated current distribution of PTBSCT at pre- and post-snapback              |    |

|--------------------------------------------------------------------------------------------------|----|

| points. Lg=0.18 $\mu$ m, D1=0.9 $\mu$ m, D2=1.3 $\mu$ m. Vpulse = 2 V with floating gate, $^{2}$ | 19 |

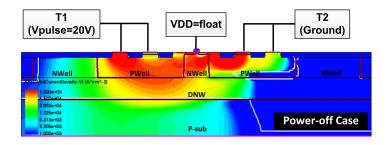

| Figure 4.6: TCAD-simulated current distribution of PTBSCT at pre- and post-snapback    |    |

|----------------------------------------------------------------------------------------|----|

| points. Lg=0.18 $\mu$ m, D1=0.9 $\mu$ m, D2=1.3 $\mu$ m. Vpulse = 2 V with gate biased |    |

| at VDD=1.8 V                                                                           | 50 |

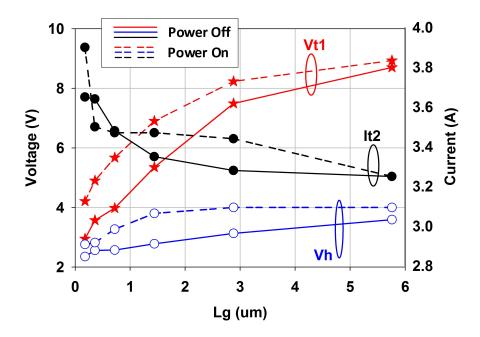

- Figure 4.8: Trigger voltage, holding voltage, and failure current of PTBSCR versus D1 in both power-OFF and power-ON conditions. Lg=0.18  $\mu$ m, and D2=1.3  $\mu$ m. 52

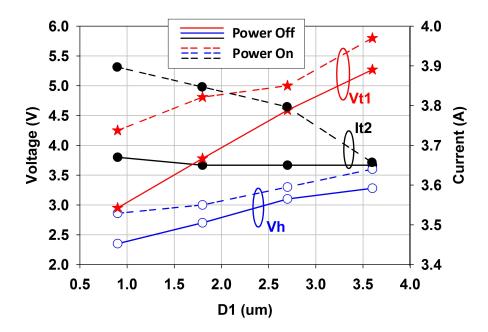

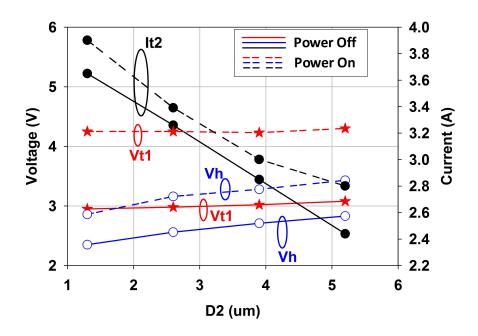

| Figure 4.9: Trigger voltage, holding voltage, and failure current of PTBSCR versus D2 |    |

|---------------------------------------------------------------------------------------|----|

| in both power-OFF and power-ON conditions. Lg=0.18 $\mu m$ and D1=0.9 $\mu m.$ .      | 53 |

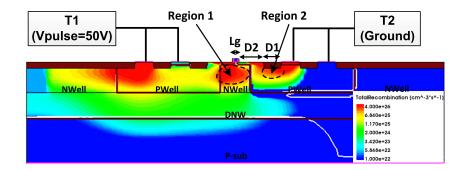

| Figure 4.10TCAD-simulated recombination rate contours in PTBSCR subject to a stress   |    |

| of Vpulse=50 V for Lg=0.18 $\mu$ m, D1=0.9 $\mu$ m and D2=1.3 $\mu$ m                 | 54 |

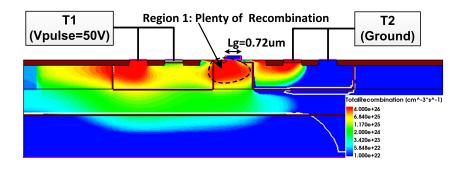

| Figure 4.11TCAD-simulated recombination rate contours in PTBSCR subject to a stress   |    |

| of Vpulse=50 V for Lg=0.72 $\mu$ m, D1=0.9 $\mu$ m and D2=1.3 $\mu$ m                 | 54 |

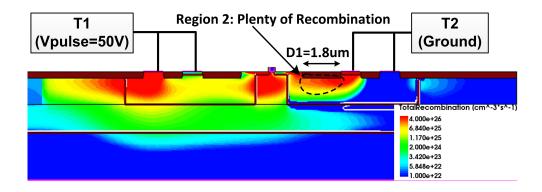

| Figure 4.12TCAD-simulated recombination rate contours in PTBSCR subject to a stress   |    |

| of Vpulse=50 V for Lg=0.18 $\mu$ m, D1=1.8 $\mu$ m and D2=1.3 $\mu$ m                 | 55 |

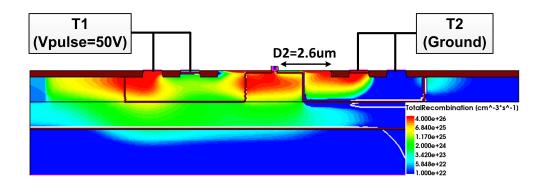

| Figure 4.13TCAD-simulated recombination rate contours in PTBSCR subject to a stress   |    |

| of Vpulse=50 V for Lg=0.18 $\mu$ m, D1=0.9 $\mu$ m and D2=2.6 $\mu$ m                 | 55 |

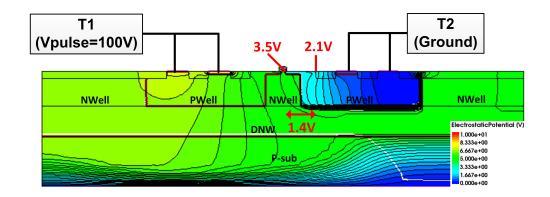

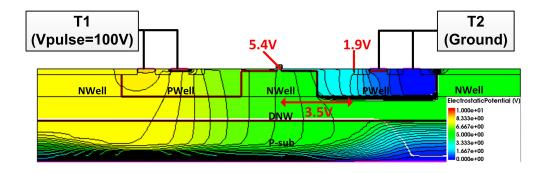

| Figure 4.14TCAD-simulated voltage contours in the PTBSCR under the same stress con-   |    |

| dition with D2=1.3 $\mu$ m. Lg=0.18 $\mu$ m, D1=0.9 $\mu$ m, and Vpulse=100 V for     |    |

| both cases.                                                                           | 56 |

| Figure 4.15TCAD-simulated voltage contours in the PTBSCR under the same stress con-   |    |

| dition with D2=3.9 $\mu$ m. Lg=0.18 $\mu$ m, D1=0.9 $\mu$ m, and Vpulse=100 V for     |    |

| both cases                                                                            | 56 |

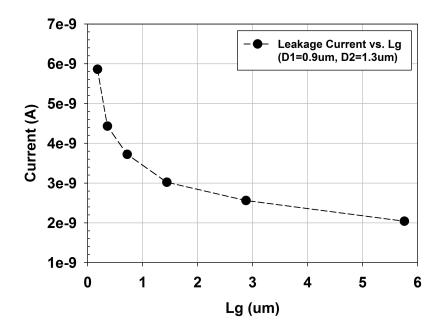

| Figure 4.16Leakage current versus Lg under the power-on condition                     | 57 |

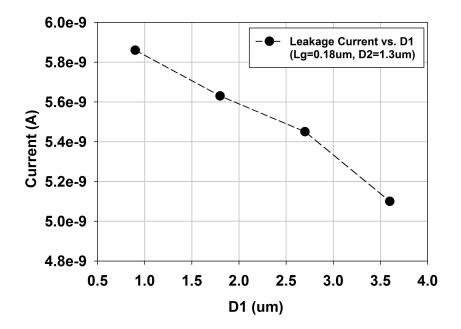

| Figure 4.17Leakage current versus D1 under the power-on condition.                    | 58 |

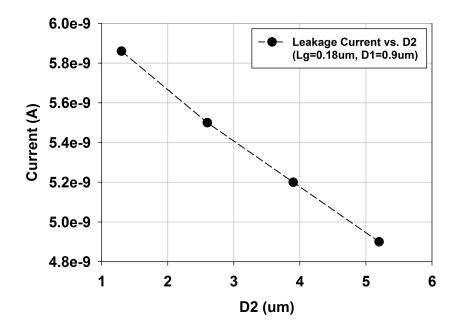

| Figure 4.18Leakage current versus D2 under the power-on condition.                    | 59 |

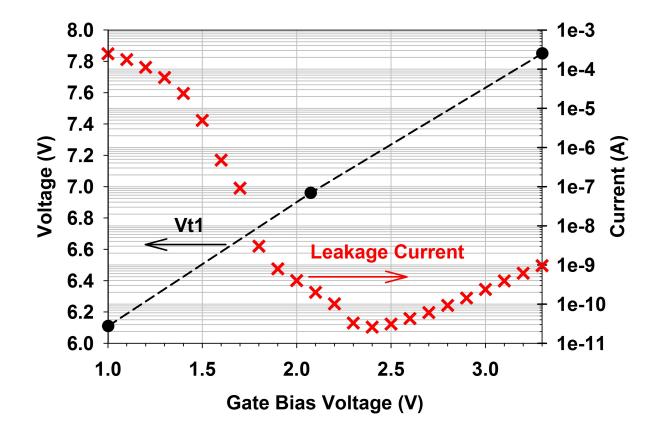

| Figure 4.19Measured leakage current and trigger voltage versus gate bias voltage (or      |    |

|-------------------------------------------------------------------------------------------|----|

| VDD). Lg=1.44 $\mu$ m, D1=0.9 $\mu$ m, D2=1.3 $\mu$ m. T1=1.8 V, T2=0 V for leakage       |    |

| current measurement.                                                                      | 60 |

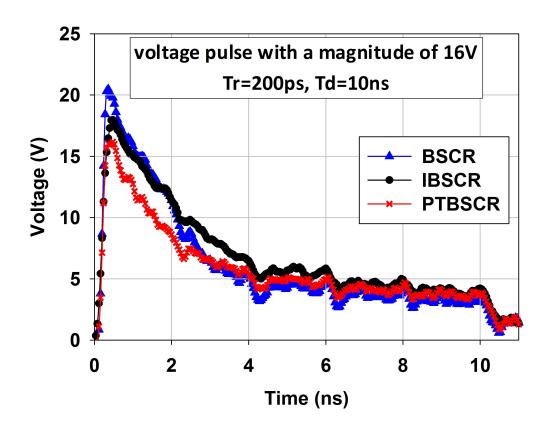

| Figure 4.20vf-TLP transient voltage waveforms of BSCR, IBSCR and PTBSCR. Lg=0.18          |    |

| $\mu$ m, D1=0.9 $\mu$ m, D2=1.3 $\mu$ m                                                   | 61 |

| Figure 5.1: Cross-section view of the left-hand half of 2-finger NS-SCR                   | 64 |

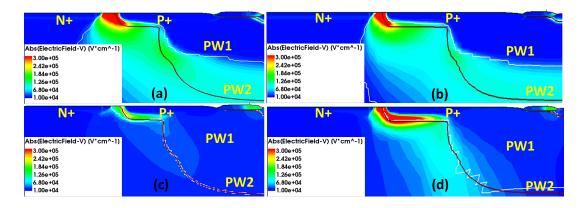

| Figure 5.2: TCAD-simulated pre-trigger ((a) and (b)) and post-trigger ((c) and (d)) elec- |    |

| tric field contours for the NS-SCR. D2 = 2 $\mu$ m in (a) and (c), and D2 = 4 $\mu$ m     |    |

| in (b) and (d). TLP-like pulse voltages of 15 and 250 V were employed for                 |    |

| the pre- and post-trigger cases, respectively.                                            | 65 |

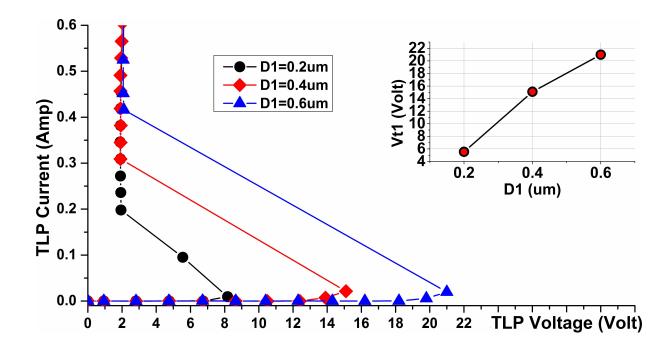

| Figure 5.3: TLP I-V characteristics for the NS-SCR's with D1 changing from 0.2 $\mu$ m to |    |

| 0.6 $\mu$ m. Insert shows the effect of D1 on the trigger voltage. D2 is fixed at         |    |

| 0.5 $\mu$ m for all cases                                                                 | 67 |

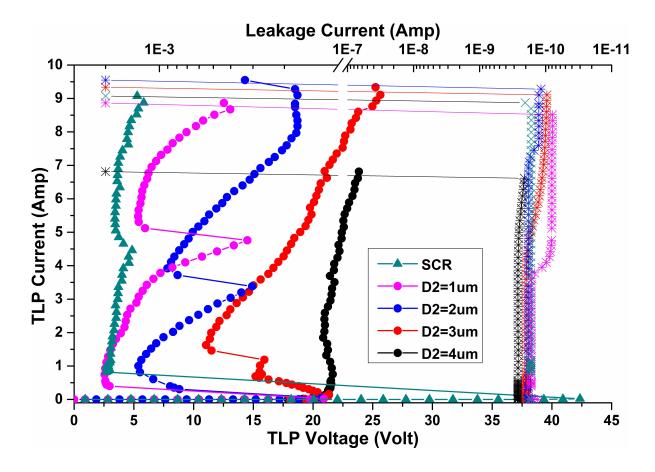

| Figure 5.4: TLP I-V characteristics for the traditional SCR and NS-SCR's with D2 chang-   |    |

| ing from 1 $\mu$ m to 4 $\mu$ m. D1 is fixed at 0.6 $\mu$ m for all cases                 | 68 |

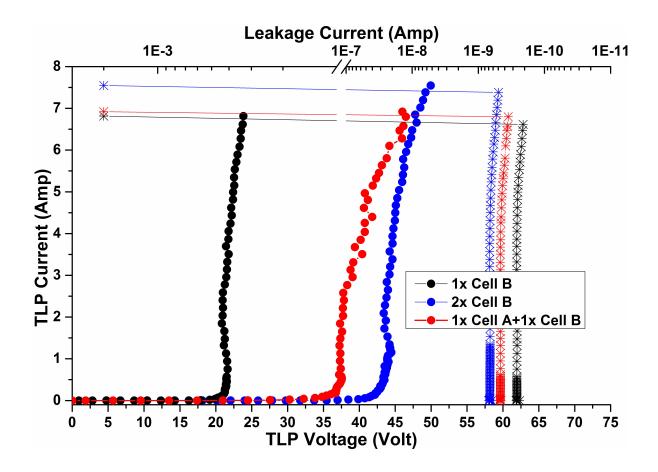

| Figure 5.5: TLP I-V characteristics for stacked Cell A and Cell B                         | 69 |

| Figure 5.6: Leakage current vs. DC voltage characteristics of SCR, Cell A and Cell B at   |    |

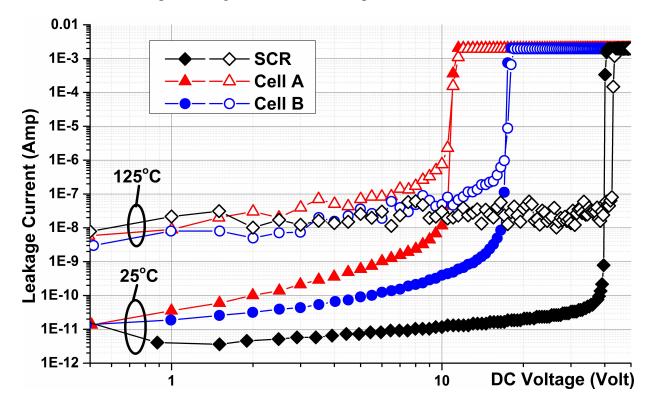

| temperatures of 25 and 125 deg-C                                                          | 70 |

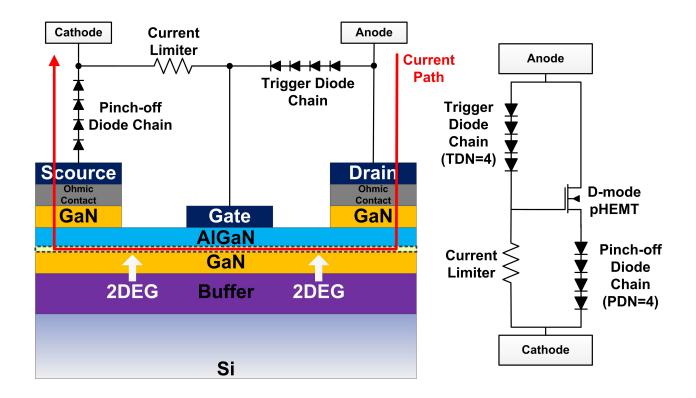

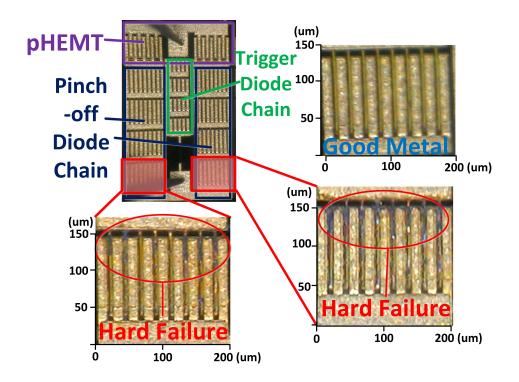

| Figure 6.1: Cross-sectional view and equivalent circuit of the proposed ESD protection |

|----------------------------------------------------------------------------------------|

| clamp, consisting of a single-gate D-mode GaN pHEMT, a trigger diode                   |

| chain, a pinch-off diode chain, and a resistor (current limiter). Red line:            |

| the current path after the clamp is turned on                                          |

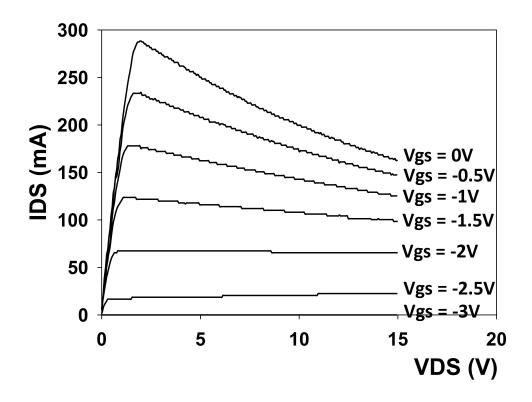

| Figure 6.2: Measured steady-state Formula curves of the pHEMT used in the proposed     |

| ESD clamp                                                                              |

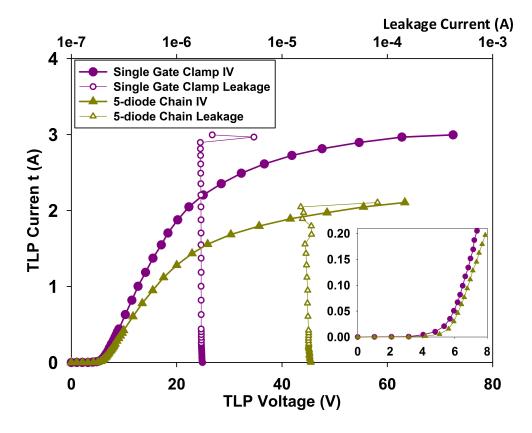

| Figure 6.3: Comparison of TLP IV curves measured from the GaN pHEMT clamp and          |

| five-diode chain                                                                       |

| Figure 6.4: Photograph of the GaN pHEMT clamp, with enlarged pictures showing hard     |

| failures on the pinchoff diode chain.                                                  |

### LIST OF TABLES

| Table 1.1: | HBM ESD Component Classification Levels.                                                                                              | 3  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 1.2: | CDM ESD Component Classification Levels.                                                                                              | 5  |

| Table 1.3: | IEC 61000-4-2 Test Levels                                                                                                             | 7  |

| Table 3.1: | ESD Performance Comparisons of Diode, LSCR, DTSCR with three diode connecting to NPN base, DCSCR with STI, and DCSCR with dummy gate. | 42 |

| Table 4.1: | ESD Parameters of PTBSCR with Respect to D1 and D2 Increase (Lg=0.18 $\mu$ m).                                                        | 50 |

| Table 4.2: | ESD Performance of PTBSCR and Existing Bidirectional SCRs                                                                             |    |

| Table 5.1: | Layout Parameters for Cell A and Cell B                                                                                               | 66 |

| Table 6.1: | Comparisons of Trigger Voltage, Leakage Current, On-state Resistance, and<br>Failure Current using different TDNs And PDNs.           | 78 |

#### **CHAPTER 1: INTRODUCTION**

#### 1.1 ESD Nature and Protection for ICs

Electrostatic Discharge (ESD) is a common phenomenon in the nature. It is regarded as a subset of Electrical Overstress (EOS) in reliability, comprising discharging stress with pulse widths from sub-microsecond to nanosecond. ESD event drives charges between two objects with various electrical potential or imbalanced charges, mainly resulting from triboelectrification, induction or conduction. Compared to normal switching signals in electronic systems, these discharging events can be extremely fast (in the order of nanoseconds) and contain high energy (with voltage up to a few kilovolts), leading to fatal failure in semiconductor devices and circuits. Major failures from ESD events include current induced damages such as thin film fusing, filamentation and junction spiking, and voltage induced damages such as charge injection and dielectric rupture [1]. Generally, it is nontrivial to diagnose and analyze the ESD-induced failures because one or more damages can be simultaneously active during the ESD event.

In order to protect the electronic systems from the ESD event, two types of design are widely adopted in semiconductor industry. On one hand, the protections are pre-developed along with the technologies, focusing on specific on-wafer design of devices and circuits that are placed on I/O pins and power supply pins domain. On the other hand, system level of protections are considered based on on-board components. No matter which one is applied, the key mechanism is to create a low-resistance path to bypass ESD energy in the form of current when ESD event happens.

#### 1.2 ESD Characterization Standards

ESD events are considered as the most significant factor to the early life failure and breakdown throughout the lifetime of ICs. Although specific protection circuits and devices are integrated in ICs, the effectiveness and robustness of the protections should be determined in a manner of guarantee for given applications. The ESD events could discharge amperes of current in a short period, typically from hundreds of picoseconds to hundreds of nanoseconds. For the purpose of repeatable and controllable ESD stress, four categories are broadly used for the ESD testing and characterization, according to the pulse rise and fall time, peak current, amount of energy, and the pulse duration.

#### 1.2.1 Human Body Model (HBM)

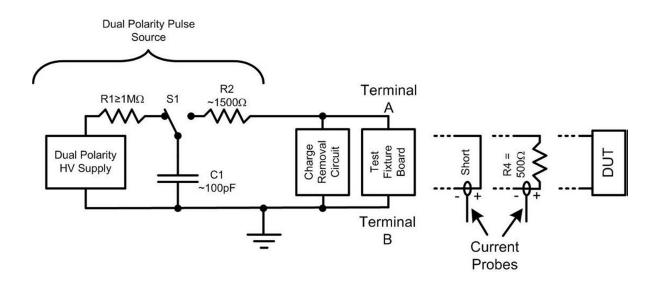

HBM represents an ESD stress caused by a charged human discharging the current into the grounded ICs. Because the internal resistance of human is large (1.5 Kohm in average), the ESD event discharges relatively slow with low peak current. Such current pules normally rises in 2 to 10 ns, and falls in 150 to 200 ns. The peak current is typically 1.2 to 1.48 A for 2 kV HBM ESD stress. Different organizations, such as MIL-STD, JEDEC, ESDA, etc, will have their own standard models for HBM testing, and the parasitic parameters in the circuit will vary. Figure 1.1 represent the equivalent circuit of HBM, and Table 1.1 lists the common HBM ESD Component Classification Levels from ANSI/ESDA joint standard [2]. R=1500 ohm and C=100 pF are chosen in the equivalent circuit.

Figure 1.1: Equivalent HBM Simulator Circuit with Loads.

| Classification | Voltage Range (V) |

|----------------|-------------------|

| 0A             | <125              |

| 0B             | 125 to <250       |

| 1A             | 250 to <500       |

| 1B             | 500 to <1000      |

| 1C             | 1000 to <2000     |

| 2              | 2000 to <4000     |

| 3A             | 4000 to <8000     |

| 3B             | >8000             |

Table 1.1: HBM ESD Component Classification Levels.

1.2.2 Machine Model (MM)

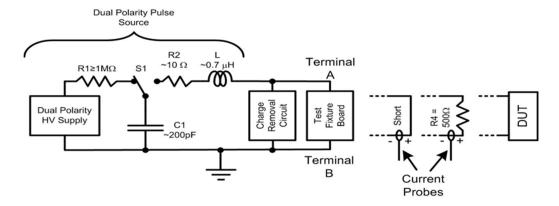

MM represents an ESD stress from a charged machine into the grounded ICs, which usually happens in automotive assembly lines. Due to the small parasitic resistance and large parasitic capacitance of metal, such kind of event discharges stress with similar rising time but much higher peak current, compared to HBM. One special characteristic of MM current waveform is the damped oscillation due to the parasitic inductance, whose negative portion may cause fatal failure in ICs. Same as HBM, the parameters of the equivalent circuit are distinct in various standard organizations. Figure 1.2 shows the equivalent circuit of the MM from ANSI standard [3].

Figure 1.2: Equivalent MM Simulator Circuit with Loads.

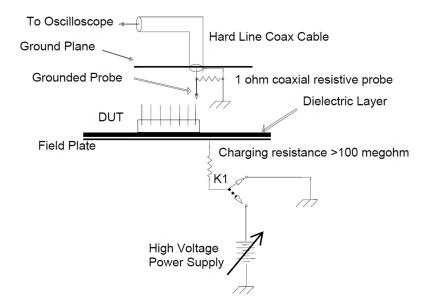

#### 1.2.3 Charged Device Model (CDM)

CDM describes an ESD stress from a self-charged IC during the manufacturing process when it contacts with ground or grounded equipments. Different from HBM and MM, the charge of CDM generally comes from contact-separation electrification and electric-field-induced electrification. With quite small internal resistance, the CDM event can discharge stress with very fast rising time and very high peak current. Theoretically, the rise time and hold time of CDM event can be 0.2 to 0.4, and 60 to 80 ns respectively, and the peak current can be up to 15-20 times more than those of HBM. Figure 1.3 shows the conceptual schematic of CDM tester, and Table 1.2 lists the common HBM ESD Component Classification Levels based on the ANSI standard [4].

Figure 1.3: Conceptual Schematic of the CDM tester.

| Class | Voltage Range (V) |  |  |

|-------|-------------------|--|--|

| C1    | <125              |  |  |

| C2    | 125 to <250       |  |  |

| C3    | 250 to <500       |  |  |

| C4    | 500 to <1000      |  |  |

| C5    | 1000 to <1500     |  |  |

| C6    | 1500 to <2000     |  |  |

| C7    | $\geq 2000$       |  |  |

Table 1.2: CDM ESD Component Classification Levels.

1.2.4 System Level IEC 61000-4-2

HBM, MM and CDM are standards specifically developed for component level ESD sensitivity testing so as to ensure effective and robustness ESD protection. However, these testing could be misunderstood and sometimes interchangeably used for system level ESD protection characterization. As a result, a protected system based on these standards fails later in consumer's applications.

Theoretically, component level ESD standards are designed for manufacturing environment, while system level one is mostly used to investigate ESD protection in end user environment. As the scale down of advanced technologies, the manufacturing geometries and stress levels that can cause ESD failures are decreasing. Since system level ESD stress usually carry large peak voltage and energy, it has been recommended to reduce the levels of on-chip ESD protection that is not sufficient for system protection, and to improve system reliability by using external ESD protection circuits.

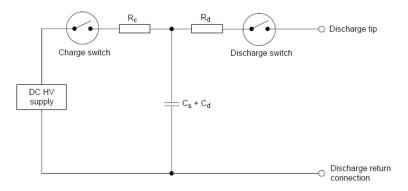

IEC 61000-4-2 standard replicates the electrostatic discharge into a system in end user environment from a charged person. It defines two different testing methodologies: contact discharge and air discharge. Figure 1.4 shows the equivalent diagram of the ESD generator that generate the IEC 61000-4-2 compatible stress. Cd is a distributed capacitance between the generator and its surroundings. The typical value of Cd+Cs is 150 pF, while the one for Rd is 330 ohm. Table 1.3 lists the test levels for both contact and air discharges. "x" can be any level, and the corresponding special test voltage can be determined in the dedicated equipment specification [5].

Figure 1.4: Equivalent diagram of the IEC 61000-4-2 generator.

| Co    | Contact Discharge |       | Air Discharge     |  |

|-------|-------------------|-------|-------------------|--|

| Level | Test Voltage (kV) | Level | Test Voltage (kV) |  |

| 1     | 2                 | 1     | 2                 |  |

| 2     | 4                 | 2     | 4                 |  |

| 3     | 6                 | 3     | 8                 |  |

| 4     | 8                 | 4     | 15                |  |

| X     | Special           | X     | Special           |  |

Table 1.3: IEC 61000-4-2 Test Levels.

#### 1.2.5 Human Metal Model (HMM)

Nowadays, increasing number of customers will request system level classification, such as IEC 61000-4-2 rating for component level electronic products. However, system level ESD standard only defines how to test the system as a whole such as mobile phones and laptops. Therefore, ESDA released the HMM, replicating IEC 61000-4-2 waveform and it is completely compatible for component level ESD measurement. The ability of surviving in the system level IEC 61000-4-2 test of different components can be evaluated at an earlier development stage, such that the cost of re-design and re-manufacturing can be effectively minimized.

HMM simulates the ESD situation where the grounded IC is touched by a charged person via a metal objects. The typical waveform of HMM contains an initial current spike with 800+-200 ps rising time, followed by a current pulse with much long fall time of about 50 ns. Such initial current spike stems from the very low resistance in the metal, while the larger resistance in human body generates the broader current pulse. The pulse source of HMM can be the general IEC 61000-4-2 compliant ESD gun. However, due to the different design of circuit board and manufacturing variation, the IEC 61000-4-2 compliant pulse waveforms from distinct manufacturers exhibit deviations from each other. Therefore, it is critical to use the same ESD gun during the whole measurement period for repeatable test result [6] and [7].

#### 1.2.6 Transmission Line Pulsing (TLP) Tester

Traditional extraction of IV characteristic from semiconductor devices are based on DC measurement. Thermal degradation and even breakdown happens in ESD investigation because of the self-heating effect from the inherent low-resistive current path created in ESD devices under DC condition. TLP, instead, provides the ability for accurate measurement and closer investigate at higher current level by using the short pulse (50 ns to 200 ns) measurement [8]. Furthermore, such short TLP pulses simulate the short ESD threats in the real world, resulting in good correlation of robustness to ESD model such as HBM.

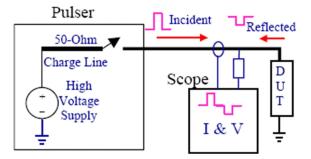

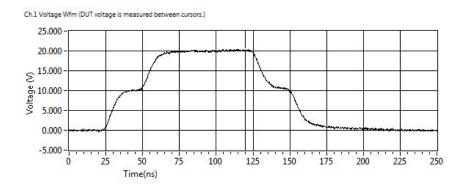

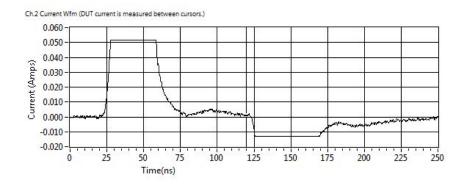

Figure 1.5 shows the equivalent circuit for the most popular TLP tester. It uses the constant impedance transmission line in the pulse source to reduce the degradation in the pulse rise time [9]. Time Domain Reflection (TDR) technique is commonly used in the commercial TLP tester, where the current and voltage signals are measured at the same location. Improved version of TLP using Time Domain Reflection-Transmission (TDRT) technique is proposed for flexible adjustment in the impedance, which should be increased from 50 ohm to higher value, e.g., 500 ohm, for closer illustration of the snapback behavior of high voltage ESD devices in static IV characteristic [10]. The charged capacitor discharge energy via the transmission cable with 50 ohm impedance and generate a flat-top rectangular pulse. As shown in Figures 1.6 and 1.7 are the square voltage and current pulses with 100 ns width and 20V pre-charged voltage captured from TLP system on an OEPN. The TDR technique overlaps the transmission and reflection pulses and a certain calibration will be applied by the system to generate the accurate data. A portion of data points on the flat-top region are averaged so that the static IV points are calculated to plot the static TLP IV curve.

Figure 1.5: Equivalent circuit of TDR TLP tester with 50 ohm impedance.

Figure 1.6: TLP-measured voltage waveform with 20V pre-charged voltage on an OPEN.

#### 1.2.7 ESD Test Methods

The ESD robustness of IC products are investigated using the ESD characterization standards before delivered to customers, such that their ESD protection capabilities are guaranteed. HBM, MM and CDM are three traditional standards that are widely used and accepted in the market. A typical set of requirement have the product under test 2000V, 200V and 750V for HBM, MM and CDM respectively.

In the fabrication and delivery process, the ESD damage can be caused by positive or negative

charges, requiring that the pins in the product are clearly evaluated by positive and negative ESD stresses. Due to the distinctions of pulse generation and discharging, HBM and MM tests are classified to three categories (pin-to-pin, pin-to-power and power-to-power). However, direct discharge and field-induced discharge are the two major categories for CDM test, performed on the CDM tester shown in Figure 1.3.

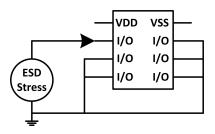

In pin-to-pin test, the ESD stress is injected to one I/O pin of the product, while another I/O pin is grounded. Therefore, two types of test modes, which are the positive mode and negative mode, are consequently classified. During the test, all the I/O pins are also grounded so as to reduce testing time, even though the discharge usually happens between one single pin to another. However, power pins are configure to be floating since such ESD events take place when the products are un-powered. Figures 1.8 and 1.9 show the equivalent testing diagrams.

In pin-to-power test, considering the two power supply (VDD and VSS), four types of testing modes, which are positive-to-VDD, negative-to-VDD, positive-to-VSS, negative-to-VSS, must be evaluated individually. Shown in Figures 1.10, 1.11, 1.12 and 1.13 are the equivalent testing diagrams. It should be noted that all the other I/O and power pins are configured to be floating.

Figure 1.7: TLP-measured current waveform with 20V pre-charged voltage on an OPEN.

Figure 1.8: Positive pin-to-pin ESD test mode

Figure 1.9: Negative pin-to-pin ESD test mode

In power-to-power pins, only VDD and VSS are considered, resulting in positive and negative modes shown in Figures 1.14 and 1.15. During the test, all the I/O pins are configured to be floating.

Figure 1.10: Positive-pin-to-VSS ESD test mode

Figure 1.11: Negative-pin-to-VSS ESD test mode

Figure 1.12: Positive-pin-to-VDD ESD test mode

#### 1.3 ESD Protection Performance Criteria

#### 1.3.1 Static Performance

In order to characterize the performance of the on-chip ESD protection, the typical ESD design window for the device operations is shown in Figure 1.16 based on TLP measurement. In voltage regime,  $V_{MAXOP}$  is the maximum operation voltage of the power supply line, while the  $V_{MAXABS}$ is considered as the absolutely maximum voltage, which takes account of the overlap of the voltage spike and noisy signals.  $V_{FAILURE}$  is equal to the upper voltage limit of the pins under protected, over which the internal circuits will be damaged.

According to the operation behavior, the ESD protections can be classified into two types: no-

snapback versus snapback. On the I-V plane, the black line curve represents the I-V characteristics of traditional snapback ESD device such as grounded-gate MOS (ggMOS) and Silicon-controlled Rectifier (SCR) with important performance matrix, including breakdown point (breakdown voltage  $V_{BD}$ , breakdown current  $I_{BD}$ ), trigger point (trigger voltage  $V_{t1}$ , trigger current  $I_{t1}$ ), holding point (holding voltage  $V_h$ , holding current  $I_h$ ), and the thermal-induced secondary breakdown point ( $V_{t2}$ ,  $I_{t2}$ ). The blue line, instead, represents the no-snapback IV characteristic from ESD devices such as diode with key ESD matrix of rigger point ( $V_{t1}$ ,  $I_{t1}$ ) and and the thermal-induced secondary breakdown point ( $V_{t2}$ ,  $I_{t2}$ ). For both cases,  $I_{t2}$  is considered as the robustness of the on-chip ESD protection.

Technically, four criteria must be completely satisfied for a successfully on-chip ESD protection design.

1)  $V_{BD}$  and  $V_{t1}$  should be larger than  $V_{MAXABS}$  to limit the occurrence of false trigger and reasonable leakage current under normal circuit operations.

2)  $V_{t1}$  and  $V_{t2}$  should be smaller than  $V_{FAILURE}$  to protect internal circuits.

3)  $V_h$  for snapback devices should be larger than  $V_{MAXABS}$  to immune latch-up effect.

4)  $I_{t2}$  should be reach specific values so that the ESD protections meet industrial standards.

Figure 1.13: Negative-pin-to-VDD ESD test mode

Figure 1.14: Positive-VDD-to-VSS ESD test mode

Figure 1.15: Negative-VDD-to-VSS ESD test mode

#### 1.3.2 Dynamic Performance

While the TLP tester offers the capability to evaluate the static performance and good correlation to the HBM level, its measurement mechanism and relatively-slow rising time limit to illustrate the dynamic performance of the ESD protection. VF-TLP, instead, measures the real transient waveforms from the separated transmitted and reflected pulse. It can generate pulse with very fast rising time in sub-nanosecond regime to simulate real-world stress like CDM. In such situation, the turn-on behavior of the ESD protection can be clearly studied, by using dynamic design matrix including turn-on time  $T_{on}$  and overshoot voltage  $V_{overshoot}$ .

Similar to TLP measurement, four criteria must be completely satisfied for a successfully on-chip ESD protection design.

Figure 1.16: Typical ESD Design Window.

1)  $T_{on}$  should be small enough to ensure the quick response to fast pulse like CDM.

2)  $V_{overshoot}$  should be smaller than the  $V_{FAILURE}$  defined specially by the technology.

The dynamic performance of ESD protection becomes very important as the development of the advanced manufacturing technologies scales down the oxide thickness of the MOS devices, which mainly determine the  $V_{FAILURE}$  in ESD design window. Figure 1.17 clearly shows the continuous decrease of  $V_{FAILURE}$  of the gate oxide and the slower reduction of the circuit operation voltage, dramatically shrinking the ESD design window [11]. Additional consideration should be taken although the ESD protection has good enough HBM immunity.

## 1.4 ESD Protection Strategy

A single IC contains multiple I/O and power supply pins for different application purpose, so the ESD protection should be considered ad planned not only on device level but also on chip level. Since the basic idea of ESD protection is to form a low-resistive path for discharging between the stressed pin and ground, rail-based and localized pin-based ESD protections are verified to the effective.

Figure 1.17: Transient breakdown of MOS gate oxide versus oxide thickness.

## 1.4.1 Rail-based ESD Protections

The rail-based ESD protections utilize the power supply rail (VDD and VSS) to assist the ESD discharge. As shown in Figure 1.18 is an example of such method, in which the ESD discharging path includes two clamps between I/O pins and power supplies, and one major clamp between the two power supplies. Therefore, a close loop connecting I/O and power pins is formed for effective ESD protection. The clamps between power supplies are usually placed across the whole chip. A larger rail resistance will hurt the ESD performance if the clamp is distributed far away from I/O pins. Therefore, the trade-off between the its placement and the area should be carefully considered.

Figure 1.18: Conceptual diagram of rail-based ESD protection.

### 1.4.2 Localized ESD Protections

The ESD clamp can also be placed beside or under the PAD for localized and effective protection, as shown in Figure 1.19. This is usually used in chip with small pin number. A bidirectional clamp in this protection is capable of further reducing the area but at the same time increase the design

difficulties of the clamp.

Figure 1.19: Conceptual diagram of localized ESD protection.

## 1.5 Conclusion and Remark

This chapter briefly discusses the industrial ESD standards and fundamental knowledge of successfully ESD protection design for semiconductor technologies. Due to the difference between various technologies, ESD protection designs are still quite customized and specialized.

## CHAPTER 2: LAYOUT OPTIMIZATION FOR SILICON-CONTROLLED RECTIFIER

We investigate the geometry layout and metal pattern in order to seek robust and optimized electrostatic discharge (ESD) performance for the silicon controlled rectifier (SCR). Parallel and crossing topologies, and different emitter lengths of the parasitic bipolar transistors, finger widths, and finger numbers are shown to significantly affect not only the ESD robustness but also the holding voltage of SCR. This paper provides useful guidelines to ameliorate the SCR performance for ESD protection applications.

#### 2.1 Introduction

Silicon-controlled rectifier (SCR) has been thoroughly investigated and verified to be a promising candidate for constructing effective electrostatic discharge (ESD) protection solutions because of its high area efficiency and robustness, compared to the other counterparts such as ggMOS. Plenty of research work were done on the improvement of its triggering technique [12], latch-up immunity [13] and [14], uniform trigger [15] and [16], and high turn-on speed [17]. It was commonly performed that the similar layout mechanism can be also applied to SCR based on previous research results of diode and ggMOS. Therefore, very limited work has been done about the influence of geometry layout and metal pattern to SCR's ESD performance. Parallel and crossing metal patterns of SCR were compared in [18], but no geometry-related issue nor the optimization of robustness were covered. The work in [19] discovered that the incorrect allocation of anode and cathode in the the individual finger of SCR would cause dramatic degradation on the current distribution and even robustness. Other research in [20], [21] and [22] just studied the geometry and metal pattern effect of diode on ESD protection capability. Therefore, a general instruction about how to draw the layout for optimum performance is expected to be very specific and unique for SCR, because its operation mechanism is completely distinct from the other counterparts.

In this chapter, we conduct a comprehensive study geometry layout and metal pattern based on the most typical lateral SCR (LSCR), and find out how they affect it's ESD protection capability. The findings reveal an interesting consequence and thus very useful optimization guidelines for ESD applications of SCR can be given finally, which will be applied to the research of SCR in the next two chapters.

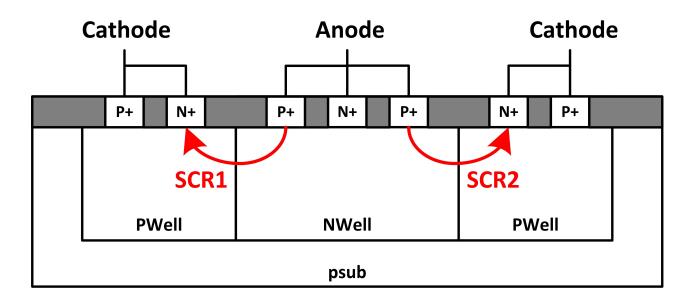

#### 2.2 Geometry and Metal Pattern of LSCR

LSCR devices fabricated in a 0.18  $\mu$ m CMOS technology are used to this work. According to [19], cathode-anode-cathode configuration are used in these devices to minimize the current nonuniformity effect, as shown in Figure 2.1 is the cross-section view of transitional LSCR. As a result, two parallel SCR current paths exist in such configuration. Since it is a twin-well based technology, no deep well/region is needed for substrate isolation. Metal 1 covers The active regions of SCR are fully covered by Metal 1 via the plugs, while Metal 2 to Metal 4 are used to connect the Anode and Cathode of the LSCR to PADs, such that the series metal resistance in the current path can be minimized.

The parallel and crossing topologies for metal routing are compared to each other in Figures 2.2 and 2.3. They lead to different current flow direction between the bulk and the back-end metal of LSCR. As shown in Figure 2.2, after trigger, the current flow of LSCR in the Anode and Cathode metals is perpendicular to that in the SCR bulk region. Instead, for the crossing topology, the current shown in Figure 2.3 will flow in the same direction in the Anode and Cathode Metals as that in the SCR bulk region.

Figure 2.1: Cross-section view of traditional LSCR.

Three critical parameters, the length of parasitic bipolar transistors in LSCR, defined as Le, the width of each finger, defined as W, and the total number of finger, defined as N, will be investigated and optimized for the SCR's ESD protection performance. It should be noted that N is also equivalent to the number of current paths in the SCR. For example, in Figure 2.1, two SCR current paths exist and hence N=2 for this case. A Barth 4002 TLP tester generating square pulses with a 10 ns rising time and a 100 ns pulse width was utilized to evaluate the ESD performance of SCR devices. The robustness, or the failure current It2, and related current density Jt2 of the measured devices were extracted when the leakage current increases more than three orders of from its original magnitude.

Figure 2.2: Metal routing of SCR for parallel topology. W denotes the finger width. Le denotes the emitter lengths of bipolar transistors in SCR. Patterns in blue denote metal connections between SCR and Pads.

#### 2.3 Results and Discussions

Figure 2.4 shows the TLP I-V curves with leakage currents from Barth 4002 TLP tester. 1.8V DC voltage is applied between Anode and Cathode for post-stress DC leakage current measurement. Both parallel and crossing topologies have the same parameters of W=40  $\mu$ m, N=2, and Le=0.9  $\mu$ m. From the Figure 2.4, very little variation can be observed on the important ESD matrix, including trigger voltage, holding voltage, robustness, and leakage current. However, when the parameters change, the ESD performances of SCR for these two different topologies are distinct from each other. Figure 2.5 compares the robustness It2 and the corresponding failure current density as a function of W for both parallel and crossing topologies with a finger number N=2

and an emitter length Le=0.9  $\mu$ m. It clearly shows that the robustness depends linearly on W for both topologies, because the larger the device's width, the higher the heat dissipation and thus the current conduction capability. However, it is interesting that the failure current density actually degrades when increasing W for both cases. Such a degradation indicates that all the fingers in the SCR may not be simultaneously triggered on when a relatively large W is used. Another interesting phenomenon is also illustrated in Figure 2.5, suggesting that the parallel topology can sustain a higher current density than the crossing topology when W is less than 20  $\mu$ m. However, this advantage is diminished if W is larger than 20  $\mu$ m.

Results in Figure 2.6 indicate that increasing N increases the SCR robustness for both topologies with W=20  $\mu$ m and Le=0.9  $\mu$ m. However, a current degradation trend for both topologies is observed when increasing the finger number. This is due to the non-uniform current distribution within the various fingers when a relatively large N is employed.

Figure 2.3: Metal routing of SCR for crossing topology. W denotes the finger width. Le denotes the emitter lengths of bipolar transistors in SCR. Patterns in blue denote metal connections between SCR and Pads.

Figure 2.4: TLP I-V curves with leakage current measurement for parallel and crossing topologies with W=40  $\mu$ m, N=2 and Le=0.9  $\mu$ m.

Figure 2.7 shows the failure current density for both parallel and crossing topologies having the same total width (equal to W\*N=40  $\mu$ m) but various N and W combinations. Obviously with the fixed total width of SCR, the current densities peak for both topologies in the case of using two fingers, which is exactly the same cathode-anode-cathode configuration shown in Figure 2.1. For the case of N larger than 2, the non-uniform current distribution in multiple fingers becomes prominent, which results in the current density degradation. Furthermore, the parallel topology has a larger degradation than the crossing topology, but the difference tends to become smaller when increasing N. On the other hand, when N is reduced from 2 to 1, which is the single anode-cathode configuration, the current densities for both topologies also degrade. This is a result of the fact that there is only one current path in the SCR. Therefore, for a fixed total width, the use of two fingers in cathode-anode-cathode configuration will be beneficial to obtain the highest robustness/area efficiency.

Figure 2.5: Robustness and Current Density versus Device Width W for parallel and crossing topologies. Finger number N=2 and emitter length Le=0.9  $\mu$ m.

When the SCR enters the snapback region, the emitter length Le affects the SCR's conductivity modulation and thus the holding voltage [23]. A similar effect can be observed and depicted in Figure 2.8. The parallel topology shows a linear dependency of holding voltage Vh on Le. However, there is a risk of inducing the latch-up when using the crossing topology if Le is larger than 3  $\mu$ m, due to the fact that Vh is lower than the power supply VDD which is 1.8V. Moreover, we also found Le will greatly affect the current density. The larger the Le, the larger the current densities for both topologies, but such trends tend to saturate when Le is larger than 3  $\mu$ m. Beyond this, increasing Le will degrade the current density. Therefore, when optimizing the current density and holding voltage, using Le=2  $\mu$ m would be a good choice, and it corresponds to two contact columns in the active region in this technology. Trigger voltage and leakage current are another two important figures of merit for evaluating the ESD protection performance of SCR. However, no significant influence is found on them when varying the layout geometry or the metal pattern. It should be pointed out that the measured leakage current for all devices are at the typical pA level.

## 2.4 Conclusion and Remark

Geometry and metal pattern effects on the ESD robustness of SCR were investigated. Both parallel and crossing topologies showed similar robustness dependencies on the geometric parameters. For a relatively small finger width W, the parallel topology demonstrated a higher robustness and better latch-up immunity than the crossing topology. However, the crossing topology yielded a higher robustness when using a relatively large finger width, but at the expense of a smaller holding voltage. Moreover, increasing the finger width W and finger number N will actually degrade the current density at the failure point for both topologies. It was concluded that a geometry of two fingers, cathode-anode-cathode configuration, and two contact columns can offer the optimized ESD performance of SCR.

Figure 2.6: Robustness and Current Density versus Finger Number N for parallel and crossing topologies. Device width W=20  $\mu$ m and emitter length Le=0.9  $\mu$ m.

Figure 2.7: Current Density versus Finger Number N for parallel and crossing topologies. Total width (W\*N) is fixed at 40  $\mu$ m when changing the finger number.

Figure 2.8: Current Density and Holding Voltage versus Emitter Length Le for parallel and crossing topologies.

# CHAPTER 3: HIGH SPEED ESD PROTECTION DESIGN FOR LOW-VOLTAGE CMOS TECHNOLOGY

An electrostatic discharge protection structure constructed by the stacking of multiple anode gatecathode gate directly connected silicon controlled rectifiers, called the DCSCRs, fabricated in a 0.18  $\mu$ m CMOS technology is studied in this chapter. Two parasitic diodes in the DCSCR dictate the turn-on mechanism and hence give rise to a trigger voltage equal to twice the diode's turn-on voltage. This approach enables the DCSCR to offer a diode-like TLP IV characteristic with a minimal snapback and at the same time improves the voltage step-up capability and offers a SCRlike high ESD robustness. This internal-triggering mechanism simultaneously turn on the parasitic bipolar transistors in SCR, booting up the SCR's speed of response to fast-rising pulses, as a consequence the overshoot voltage can be dramatically reduced. Finally, an ESD clamp constructed by stacking a selected number of DCSCRs can offer a flexible trigger/holding voltage and is highly suitable for low and medium voltage ESD protection applications.

## 3.1 Introduction

Electrostatic Discharge (ESD) induced failure is a major concern for the Metal-Oxide-Semiconductor (MOS) transistor based integrated circuits in main-stream technologies. This reliability issue is further worsened in advanced technology including sub-micron Complementary-Metal-Oxide-Semiconductor (CMOS) with very low operation voltage. Nowadays, there has been a growing demand for the availability of robust ESD protection solutions for advanced and main-stream technologies that are capable of operating in a very narrow ESD design window. Silicon Controlled Rectifier (SCR) is a typical apparatus for ESD protection. Figure 3.1 shows the cross-section view and equivalent circuit of the traditional SCR. It is an old fashion to name the four nodes, which are

SCR's electrical terminals, to be "Anode Gate" (AG), "Anode", "Cathode Gate" (CG), "Cathode". In this typical SCR, AG and Anode are tied together and connected to pin under protected. On the other hand, CG and Cathode are tied together and connected to GND.

Figure 3.1: Cross-section view and equivalent circuit of traditional SCR.

When the ESD event happens on the pin subject to the ground, voltage builds up and the middle NWell/PWell junction sustain the major electric field, where the impact ionization starts to generate electrons and holes that are able to move freely. When it reaches a critical electric field value, a chain-effect, which is called avalanche breakdown, gives born to large quantity of such free excess carriers. Electrons flow to pin and holes flow to ground, creating voltage drops in the well regions, and thus the SCR is turned on as the parasitic bipolar transistor operations dominate. Since this triggering mechanism relies on the junction breakdown, a relatively high trigger voltage is required (e.g., in 0.18  $\mu$ m technology, the junction breakdown voltage equals to 10-16V, depending the combination and doping concentration). However, at the specific point when SCR is triggered, the voltage drop between pin and ground, which is called holding voltage, is a combination of a saturation voltage between collector and emitter in a bipolar transistor, and a threshold voltage of

a diode (e.g., VCE of PNP and VBE of NPN in Figure 3.1). Therefore, a snapback region always exists in the usual TLP IV curve.Such triggering mechanism also limits the turn-on speed of SCR because of its complicated processes, which can be divided into four steps.

STEP 1: Impact ionization and avalanche breakdown in the middle revere bias junction. In Figure3.1 it is NWell/PWell junction.

STEP 2: Free carriers flow thought well regions and generate voltage dorp.

STEP 3: One of the parasitic bipolar transistors (typically it is NPN) start to inject carriers into well regions, modulating their conductivity and start the SCR operation.

STEP 4: Another parasitic bipolar transistors (typically it is PNP) is triggered and start to inject carriers into well regions, strongly modulating their conductivity and start the SCR operation.

These characteristics of SCR will introduce two critical problems. On one hand, the ESD in the environment will not scale down even though size of ICs keep decreasing, following the famous Moore's Law nowadays. The thinner gate oxide set up a lower gate oxide breakdown voltage, which significantly decrease the upper limit of available ESD design window. On the other hand, the ICs with small scales become very fragile and sensitive to the electrical overstress, e.g., overshoot voltage, which can be generated simply by the ESD protection device in ESD event due to its low turn-on speed.

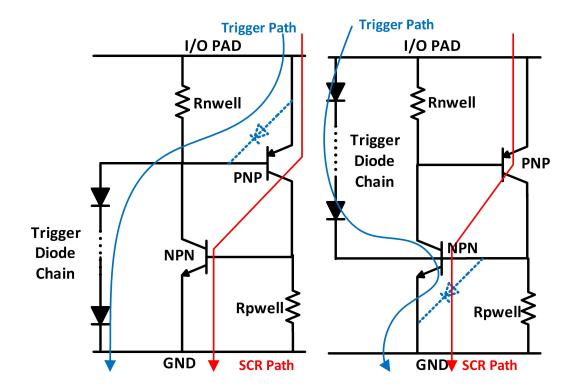

Plenty of works have been done to improve the triggering performance of SCR, and the major concept is to use external triggering techniques. For example, the work in [12] summarized various techniques for reducing the SCR's trigger voltage, but this come at the expense of a larger area. A typical realization is to use diode to trigger the SCR [24], and its equivalent circuits are shown in Figure 3.2. In this structure the trigger voltage is determined by the number of diode that are used in the external diode string. However, this method do little help on improving the turn-on speed

in fast-rising pulse because only one bipolar transistor is triggered at a time. Substrate trigger technique was proposed to trigger both parasitic bipolar transistors at the same time in [25] but it also needs a complicated design of external trigger circuit. Recently a gate-bounded structure is used to increase the turn-on speed of SCR, in which a high-K metal gate is required to compress the leakage current [17].

Figure 3.2: Equivalent circuit of diode-triggered SCR.

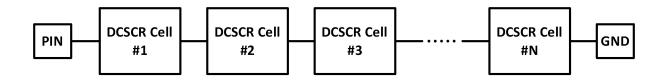

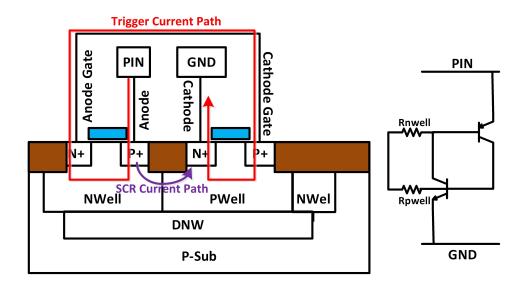

In this chapter an SCR-like device, called the direct-connected SCR (DCSCR), with the anode gate and cathode gate terminals connected together, is studied to fulfill objectives of the low-trigger voltage and fast turn-on speed. Meanwhile, Absence of a sizable snapback, the structure's trigger and holding voltages can be easily tuned by stacking a different number of DCSCRs, giving rise to an attractive ESD clamp with a proper trigger voltage, proper holding voltage, near-zero snapback window, high robustness, and minimal number of cells required for low and medium voltage ESD applications.

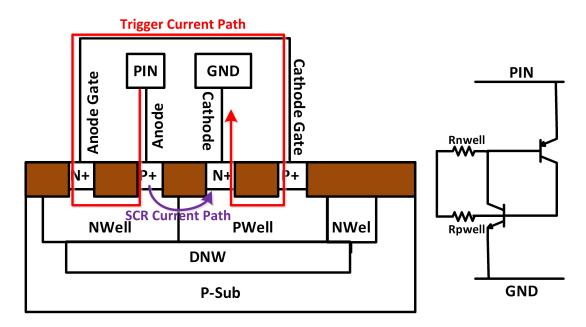

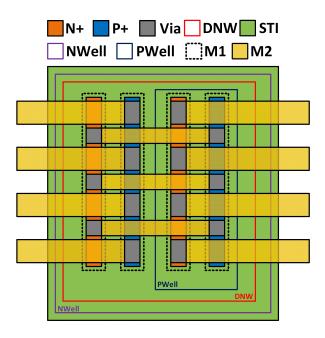

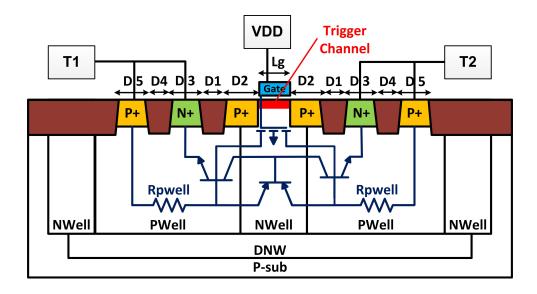

#### 3.2 Direct-connected SCR

Figure 3.3 shows the cross-section view and equivalent circuit of the DCSCR unit cell, whose top view of layout is represented in Figure 3.4. It can be easily realized in advanced and main-stream low-voltage semiconductor technologies with simple modification on the back-end layers. Like the traditional SCR (see Figure 3.1), the A and C terminals of DCSCR are connected to the pin and ground, respectively. In addition, the AG and CG terminals of the DCSCR are connected together using a metal layer. Such a connection gives rise to two internally connected PWell/N+ and NWell/P+ diodes. On top of that, the parasitic NPN and PNP transistors can be simultaneously triggered. Note that the PWell is not grounded and thus the deep NWell (DNW) is needed and used for substrate isolation. The DNW also increase the effective base width of the vertical parasitic PNP transistor, so that the carriers injected into the substrate can be greatly reduced. The red arrow in Figure 3.3 illustrates the internal trigger current, which flows through the two parasitic diodes in the DCSCR. When the voltage at the A terminal is larger than twice of the diode's turn-on voltage, the P-emitter connected to the A terminal and the N-emitter connected to the C terminal start to inject free carriers into the base regions (i.e., PWell and NWell) of the parasitic NPN and PNP bipolar transistors and consequently trigger the DCSCR without a snapback (see purple arrow in Figure 3.3). To the turn-on speed point of view, the DCSCR can be switched on quicker following two steps to trigger the internal SCR operation, one steps fewer than that of traditional SCR.

STEP 1: The two internally connected PWell/N+ and NWell/P+ diodes are turned on and start to inject carriers into well regions when voltage increases.

STEP 2: SCR operation is triggered and dominate the major ESD current discharge.

Figure 3.3: Cross-section view and equivalent circuit of traditional SCR.

In order to effectively raise the trigger and holding voltages needed for the low or medium ESD protection solutions, a number of DCSCRs can be stacked together. Figure 3.5shows the concept of implementing novel SCR cell in high voltage technologies. This approach is to stack several novel SCR cells to achieve a desirable high trigger and high holding voltages. The stacking number depends on the required trigger voltage, or the ESD design window. Since a single DCSCR cell does not possess a snapback behavior, the stacking of multiple cells also lacks snapback, thus providing an excellent ESD design window with adequate trigger and holding voltages for immunity of potential latch-up and core circuit damage. Figure 3.6 and Figure 3.7 shows the schematic and conceptual IV characteristics of the proposed stacking structure. It is turned on once the voltage applied to the structure's anode terminal exceeds the value of  $2 \times N \times V$ , where V is the diode's turn-on voltage and N is the DCSCR stacking number.

Figure 3.4: Top view of the layout of DCSCR.

Figure 3.5: Concept of stacking DCSCR cells for low-to-medium voltage ESD applications.

Dummy gate technique has been proved to be an effective way to increase the turn-on speed of ESD protection devices, examples of this usage includes the applications on diode and SCR [26], [17] and [27]. Under the dummy gate region, the trench isolation (e.g., STI and DTI) and the field oxide (FOX) will be removed, making the current path shorter. Figure 3.8 shows the cross-section view of the DCSCR with dummy gate technique. Clearly, the trigger current denoted by the red line flow closer to the silicon surface.

Figure 3.6: Cross-section view of stacking of multiple DCSCR cells for low-to-medium voltage ESD applications

Figure 3.7: Conceptual IV curves of stacked structure having different numbers of DCSCRs.

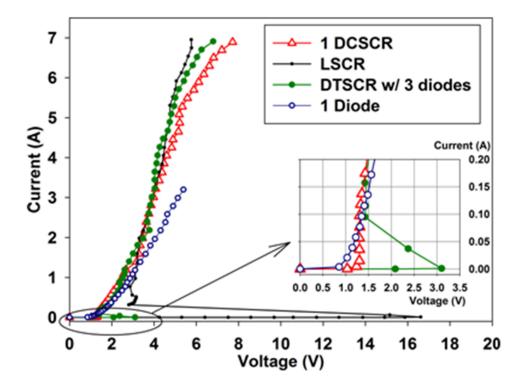

## 3.3 TLP Measurement

DCSCR with STI, DCSCR with dummy gate, diode, traditional SCR and DTSCR were fabricated in a 0.18  $\mu$ m CMOS technology and measured using the Barth 4002 transmission line pulsing (TLP) tester. Cathode-Anode-Cathode configuration was used for all the devices to improve the current uniformity [19]. Figure 3.9 compares the measured TLP IV curves of a DCSCR, a DCSCR with dummy gate, a diode, a traditional SCR, and a DTSCR with a string of 3 diodes. The diode has 60  $\mu$ m. while the other devices have the total width of 120  $\mu$ m. As expected, the DCSCR demonstrates a minimal snapback window with the same trigger voltage Vt1 and holding voltage Vh of 1.3 V (see inset in Figure 3.9). For the dummy gate version, its trigger voltage is increased from 1.3 V to 1.75 V, because the emitter lengths of it is half of that of DCSCR with STI, resulting in a smaller carrier injections and thus a higher holding voltage [23]. After the triggering, the SCR element carries out the current conduction, and the DCSCR behaves similarly to the traditional SCR. Furthermore, while the DCSCR has a similar robustness as the other SCR-based structures, but a small degradation on robustness is seen on dummy gate version. These, together with the fact that Vt1 of DCSCR is twice of that of diode, indicates that the DCSCR is a better cell than the diode when building a stacking ESD structure for low voltage applications. For example, designing a power clamp for a circuit with a VDD = 3 V would require 5 diodes but take only 3 DCSCR's.

Figure 3.8: Cross-section view of DCSCR with dummy gate technique.

As such, the DCSCR-based clamp would occupy a smaller area and offer a higher robustness over its ESD-based counterpart.

Figure 3.9: Comparison of TLP IV curves measured from the DCSCR with STI, DCSCR with dummy gate technique, traditional SCR, diode, and DTSCR.

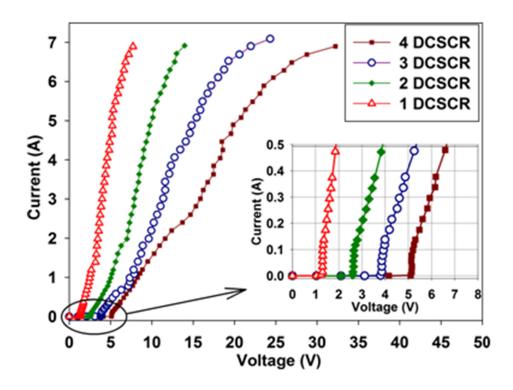

Stacking technique is a common method to increase the voltage compatibility of ESD clamp in high voltage pins. Figure 3.10 shows the measured TLP IV curves of the proposed stacked DC-SCR clamps (with STI) having N=1, 2, 3 and 4. Clearly, with the absence of the snapback, the trigger and holding voltages can be flexibly and coordinately increased with increasing the stacking number. It should be noted that the on-resistance also increase when stacking up, but it can be reduced if large device width and/or more metal connection are used.

Figure 3.10: Measured TLP IV curves of proposed stacking structures having different stacking numbers.

### 3.4 vf-TLP Measurement

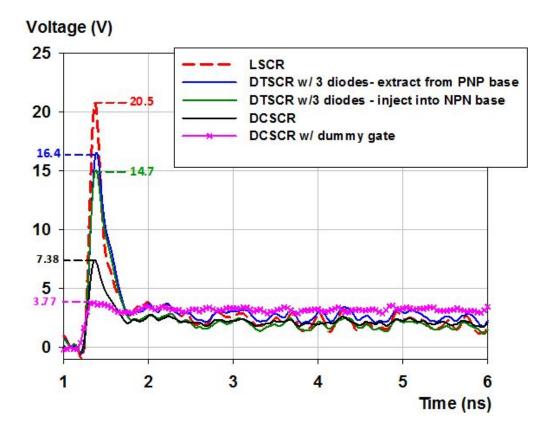

As the technology scaling down, advanced ICs becomes more and more fragile to sustain damages from ESD events with fast-rising pulse due to the overshoot voltage if the ESD clamps cannot turn on in time. DCSCR (with STI and dummy gate) is specifically designed for low voltage ESD applications, in return its turn on performance is an important ESD matrix. A Barth 4012 vf-TLP is used as the pulse source, which generates very-fast rising pulse having 100 ps rising time, and the pulse witdth is chosen to be 10 ns so as to simulate the worst ESD case. Figure 3.11 compares the voltage waveform versus transient time of diode, traditional SCR, DTSCR with three external diodes connecting to PNP base, DTSCR with three external diodes connecting to NPN base, DCSCR with STI and DCSCR with dummy gate. According to [24], the transient gate

oxide breakdown voltage is 10 V, indicating that the overshoot voltage must be clamped under 10 V. Diode, LSCR and DTSCRs are verified not to be suitable for such kind of protection even though they have similar robustness as DCSCR. However, an interesting result is observed for DTSCRs, showing that it is slightly effective to connect the external diode string to NPN base compared to PNP base (14.7 V vs. 16.4 V), due to the fact that electrons, the major carriers in NPN, has higher mobility than that holes, the major carriers in PNP. Oppositely, the overshoot voltages of DCSCR with STI is compressed to 7.38 V, thanks to the direct connection between AG and CG. It is interesting to observe that the dummy gate technique further reduce the overshoot voltage ot 3.77 V, which is similar to the transient voltage at the steady state. Therefore, a no-snapback behavior also exists in the transient voltage waveform, indicating that DCSCR type of devices are high suitable for constructing protection solutions for a high-speed ESD event, such as CDM.

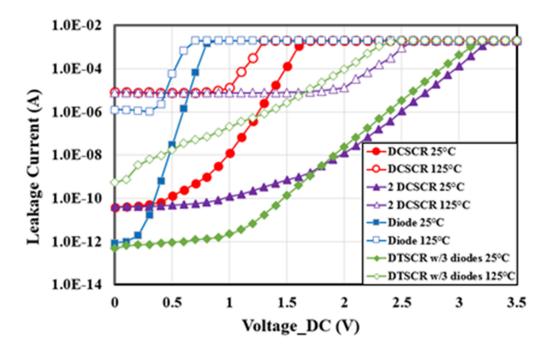

#### 3.5 Thermal Stability of Leakage Current

It is very critical to evaluate the leakage current of DCSCRs at high temperature environment, because it is triggered on by two embedded diodes, whose leakage current increase exponentially when temperature goes up. Large leakage current is dangerous to ICs because it not only increases power consumption but also induce risk of false triggering and latch-up. Figure 3.12 compares the DC sweep of diode, DTSCR with three external diodes, DCSCR with STI and 2-stacked DCSCR with STI at 25 and 125 deg-C respectively. The results indicate that the DCSCR has an acceptable nA-level leakage current at 25 deg-C when it is biased below 1 V. A smaller leakage current is found for the DTSCR due to the presence of several external diodes added to the structure. The leakage current performance of DCSCR with dummy gate has similar result as the STI versions. The diode has the fastest increase in the leakage current when the voltage goes up, followed by the DCSCR and the 2-stacked DCSCR.

Figure 3.11: Measured transient waveforms of LSCR, DTSCRs, diode, the proposed DCSCR, and the DCSCR with dummy gate structures.

At an elevated temperature of 125 deg-C, the leakage currents of these devices are jumped to the  $\mu$ A level at relatively small voltages. As the voltage increases, the diode's leakage current again increases much more rapidly than the DCSCR devices. This illustrates that the DCSCR and its stacked structure are superior to the diode in term of the leakage current performance.

Figure 3.12: DC sweep of the DCSCR, 2-stacked DCSCR, diode and DTSCR with three external diodes at 25 deg-C and 125 deg-C.

#### 3.6 ESD Performance Comparisons

Table 3.1 lists the trigger voltages, holding voltages, areas, failure currents It2, failure current densities Jt2, overshoot voltage and parasitic capacitances of the DCSCR with STI, DCSCR with dummy gate technique, diode, traditional SCR, and DTSCR. The DCSCRs and traditional SCR have the same robustness and area, but the DCSCRs with trigger voltages of 1.3 V and a near-zero snapback window is far more suitable for low and medium voltage ESD applications than the traditional SCR. Comparing to the diode, the DCSCRs demonstrate a much higher robustness and an improved voltage step-up capability. With regard to the DTSCR, the DCSCR is superior in terms of the snapback window and area. In addition, the DCSCR possesses the smallest capacitance among all devices considered, measured by AC signal with 1MHz frequency, thanks to the

novel direct connection. However, the capacitance slightly increase when dummy gate technique is applied due to the gate parasitic capacitance.

| Device                | Diode | LSCR | DTSCR (NPN) | DCSCR (STI) | DCSCR (dummy gate) |

|-----------------------|-------|------|-------------|-------------|--------------------|

| TLP It2 (A)           | 3.2   | 7    | 6.9         | 7           | 7                  |