Electronic Theses and Dissertations, 2004-2019

2012

# Design And Characterization Of High Temperature Packaging For Wide-bandgap Semiconductor Devices

Brian Grummel

University of Central Florida

Part of the Electrical and Electronics Commons

Find similar works at: https://stars.library.ucf.edu/etd

University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### STARS Citation

Grummel, Brian, "Design And Characterization Of High Temperature Packaging For Wide-bandgap Semiconductor Devices" (2012). *Electronic Theses and Dissertations, 2004-2019.* 2495. https://stars.library.ucf.edu/etd/2495

## DESIGN AND CHARACTERIZATION OF HIGH-TEMPERATURE PACKAGING FOR WIDE-BANDGAP SEMICONDUCTOR DEVICES

by

#### BRIAN J. GRUMMEL B.S.E.E. University of Central Florida, 2007 M.S.E.E. University of Central Florida, 2008

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida

Orlando, Florida

Fall Term 2012

Major Professor: Z. John Shen

© 2012 Brian J. Grummel

#### **ABSTRACT**

Advances in wide-bandgap semiconductor devices have increased the allowable operating temperature of power electronic systems. High-temperature devices can benefit applications such as renewable energy, electric vehicles, and space-based power electronics that currently require bulky cooling systems for silicon power devices. Cooling systems can typically be reduced in size or removed by adopting wide-bandgap semiconductor devices, such as silicon carbide. However, to do this, semiconductor device packaging with high reliability at high temperatures is necessary. Transient liquid phase (TLP) die-attach has shown in literature to be a promising bonding technique for this packaging need. In this work TLP has been comprehensively investigated and characterized to assess its viability for high-temperature power electronics applications. The reliability and durability of TLP die-attach was extensively investigated utilizing electrical resistivity measurement as an indicator of material diffusion in gold-indium TLP samples. Criteria of ensuring diffusive stability were also developed. Samples were fabricated by material deposition on glass substrates with variant Au-In compositions but identical barrier layers. They were stressed with thermal cycling to simulate their operating conditions then characterized and compared. Excess indium content in the die-attach was shown to have poor reliability due to material diffusion through barrier layers while samples containing suitable indium content proved reliable throughout the thermal cycling process. This was confirmed by electrical resistivity measurement, EDS, FIB, and SEM characterization. Thermal and mechanical characterization of TLP die-attached samples was also performed to gain a newfound understanding of the relationship between TLP design parameters and die-attach properties. Samples with a SiC diode chip TLP bonded to a copper metalized silicon nitride

substrate were made using several different values of fabrication parameters such as gold and indium thickness, Au–In ratio, and bonding pressure. The TLP bonds were then characterized for die-attach voiding, shear strength, and thermal impedance. It was found that TLP die-attach offers high average shear force strength of 22.0 kgf and a low average thermal impedance of 0.35 K/W from the device junction to the substrate. The influence of various fabrication parameters on the bond characteristics were also compared, providing information necessary for implementing TLP die-attach into power electronic modules for high-temperature applications. The outcome of the investigation on TLP bonding techniques was incorporated into a new power module design utilizing TLP bonding. A full half-bridge inverter power module for low-power space applications has been designed and analyzed with extensive finite element thermomechanical modeling. In summary, TLP die-attach has investigated to confirm its reliability and to understand how to design effective TLP bonds, this information has been used to design a new high-temperature power electronic module.

This dissertation is dedicated to my family.

#### **ACKNOWLEDGMENTS**

I would like to first thank my incredible advisor Dr. Z. John Shen who has mentored me since I knocked on his door as an undergraduate looking for research work after taking his semiconductor devices class. He welcomed me in and has guided, advised, and supported me through the field of power semiconductors ever since.

I would also like to thank Dr. Habib Mustain who has also advised me and directed me toward SiC devices and TLP die-attach. He has been invaluable in assisting me in my research.

Also, I would also like to thank Dr. Allen Hefner whom I have worked with since he asked me to come and work with him at the National Institute of Standards and Technology on power devices some years ago and has supported me since.

I also thank my committee members Dr. Ali Gordon, Dr. Kalpathy Sundaram, and Dr. Jiann-Shiun Peter Yuan who have provided me value invaluable feedback and guidance.

Thank you also to the many talented people I have worked with at the University of Central Florida and NIST including Patrick Shea, Boyi Yang, Karthik Padmanabhan, Gourab Sabui, Shan Sun, Jian Lu, Xuexin Wang, Matt Landowski, Yali Xiong, Madelaine Hernandez-Mora, Jose Ortiz, Colleen Hood, Tam Duong, and many others.

Finally, my family has been unwavering in their support of me over the many years I have been pursuing my degrees and I am eternally thankful for them all, including my fiancé Brittany, my Mom, my Dad, my Sister Jill, Jason, Darlene, Marsha, and many, many others. Every day they have stood behind me and pushed me and motivated me and I cannot think of where I would be without them nor can I thank them enough. Thank you all.

## TABLE OF CONTENTS

| LIST OF F | IGURES                                               | X     |

|-----------|------------------------------------------------------|-------|

| LIST OF T | ABLES                                                | xvii  |

| LIST OF A | ABBREVIATIONS                                        | xviii |

| LIST OF V | ARIABLES                                             | xix   |

| CHAPTER   | 1: INTRODUCTION                                      | 1     |

| 1.1       | Motivation                                           | 1     |

| 1.2       | Statement of Benefit                                 | 3     |

| 1.3       | Wide-Bandgap Semiconductors                          | 4     |

| 1.4       | High-Temperature Power Electronic Applications       | 15    |

| CHAPTER   | 2: REVIEW OF HIGH-TEMPERATURE PACKAGING PRIOR ART    | 21    |

| 2.1       | Conventional Power Module                            | 21    |

| 2.2       | Advanced Power Module Designs                        | 33    |

| 2.3       | Electronic Cooling Systems                           | 38    |

| 2.4       | High-Temperature Die-Attach                          | 42    |

| 2.5       | Summary                                              | 48    |

| CHAPTER   | 3: INTRODUCTION TO TRANSIENT LIQUID PHASE DIE-ATTACH | 49    |

| 3.1       | TLP Bonding Process Overview                         | 49    |

| 3.2       | Material System Requirements                         | 54    |

| 3.3       | Advantages and Limitations of TLP Die-Attach                                    |

|-----------|---------------------------------------------------------------------------------|

| CHAPTER   | 4: OBJECTIVES66                                                                 |

| 4.1       | Investigation of Thermal and Mechanical Properties of TLP Die-Attach 67         |

| 4.2       | Resistive, Diffusive, and Thermal Analysis of TLP Reliability and Durability 67 |

| 4.3       | Design and Simulation of High-Temperature Power Electronic Module 67            |

| CHAPTER   | 5: INVESTIGATION OF THERMAL AND MECHANICAL PROPERTIES OF                        |

| TLP DIE-A | TTACH69                                                                         |

| 5.1       | TLP Fabrication Parameters                                                      |

| 5.2       | Sample Fabrication Process                                                      |

| 5.3       | Die-Attach Percentage                                                           |

| 5.4       | Thermal Impedance                                                               |

| 5.5       | Shear Strength and Force 81                                                     |

| 5.6       | Thermo- Mechanical Investigation Summary                                        |

| CHAPTER   | 6: RELIABILITY AND DURABILITY STUDY OF TLP DIE-ATTACH                           |

| 6.1       | TLP Diffusion Experiment                                                        |

| 6.2       | Diffusion Detection through Electrical Resistivity90                            |

| 6.3       | Diffusion Sample Fabrication                                                    |

| 6.4       | Diffusion and Electrical Resistivity Results                                    |

| 6.5       | Surface EDS Characterization                                                    |

| 6.6       | Thermal Impedance Durability                                                    |

|       | 6.7     | TLP Reliability and Durability Summary               | 105 |

|-------|---------|------------------------------------------------------|-----|

| СНАР  | TER 7:  | DESIGN AND MODELING OF POWER ELECTRONIC MODULE BASED | ON  |

| TLP D | IE-AT   | ГАСН                                                 | 107 |

|       | 7.1     | Design Concept                                       | 107 |

|       | 7.2     | Finite Element Analysis                              | 112 |

|       | 7.3     | Module Fabrication Approach                          | 115 |

|       | 7.4     | Module Design Summary                                | 119 |

| СНАР  | TER 8:  | CONCLUSION AND FUTURE WORK                           | 120 |

|       | 8.1     | Summary and Conclusion                               | 120 |

|       | 8.2     | Future Work                                          | 121 |

| APPE  | NDIX: ( | COPYRIGHT PERMISSIONS                                | 123 |

| REFEI | RENCE   |                                                      | 127 |

## LIST OF FIGURES

| Figure 1.1 – Energy band diagram of 4H-SiC material                                         | 7    |

|---------------------------------------------------------------------------------------------|------|

| Figure 1.2 – Intrinsic carrier concentration versus temperature in silicon and SiC material | 9    |

| Figure 1.3 – SiC oxide reliability shown by mean time to failure (MTTF)                     | . 10 |

| Figure 1.4 - Relationship of electric field strength to energy bandgap in semiconductor     |      |

| materials [23]                                                                              | . 11 |

| Figure 1.5 – DMOS device structure [24]                                                     | . 13 |

| Figure 1.6 – Breakdown voltage versus doping concentration in silicon and SiC materials [1] | . 13 |

| Figure 1.7 – Specific on-resistance of semiconductors vs. breakdown voltage [25]            | . 14 |

| Figure 1.8 – Diagram of EGS geothermal plant and well [29]                                  | . 18 |

| Figure 1.9 – Comparison of normalized energy costs for multiple sources as a culmination of |      |

| capital costs, operations, maintenance, and transmission [32]                               | . 20 |

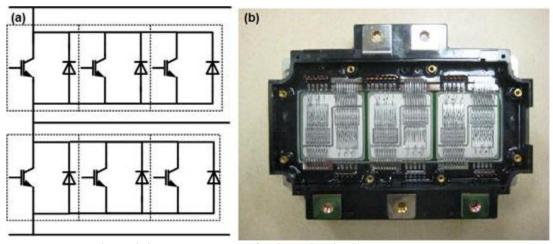

| Figure 2.1 – Conventional IGBT power module                                                 | . 22 |

| Figure 2.2 – Half-bridge circuit diagram                                                    | . 23 |

| Figure 2.3 – Half-bridge switching waveform [34]                                            | . 23 |

| Figure 2.4 – Three phase half-bridge circuit diagram and module                             | . 25 |

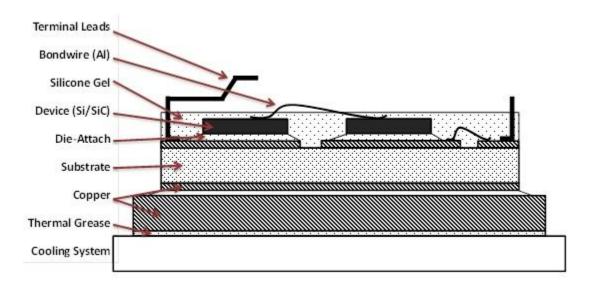

| Figure 2.5 – Conventional power module cross section [38]                                   | . 26 |

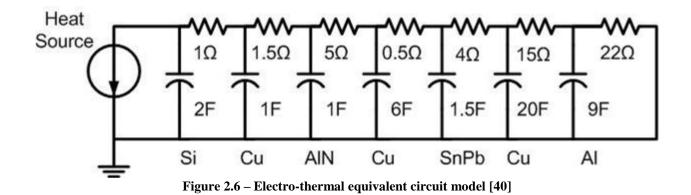

| Figure 2.6 – Electro-thermal equivalent circuit model [40]                                  | . 29 |

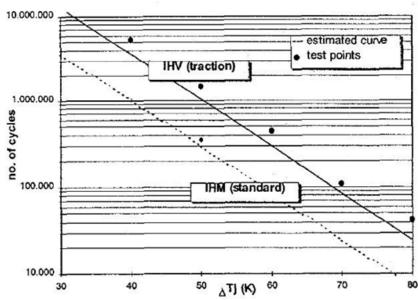

| Figure 2.7 – Module cycles to failure vs. temperature rise reliability [41]                 | . 30 |

| Figure 2.8 – SEM cross section of solder cracking failure [43]                              | . 31 |

| Figure 2.9 – Non-uniform current in parallel devices within power module [37]               | . 32 |

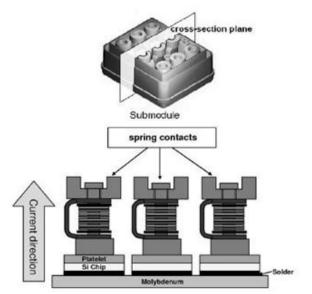

| Figure 2.10 – Standard press pack module design cross section [47]                          | 33   |

| Figure 2.11 – ABB press pack sub-module [49]                                                | . 34 |

|---------------------------------------------------------------------------------------------|------|

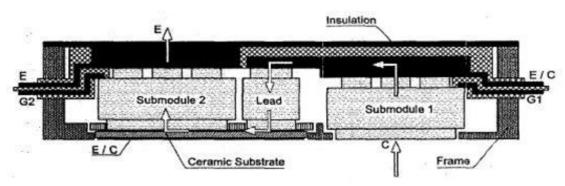

| Figure 2.12 – ABB system module conceptualization [50]                                      | . 34 |

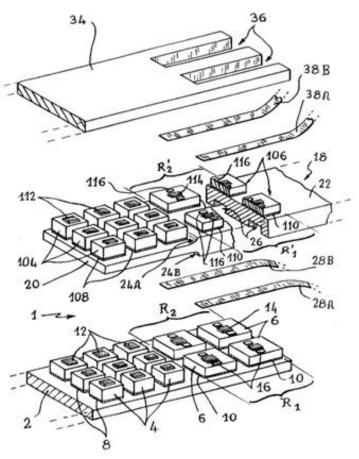

| Figure 2.13 – Alstom double lead frame module design [53]                                   | . 35 |

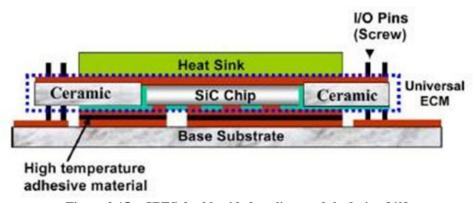

| Figure 2.14 – APEI hybrid module design [57]                                                | . 37 |

| Figure 2.15 – CPES double-sided cooling module design [60]                                  | . 37 |

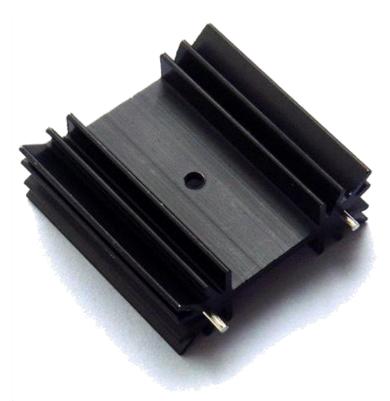

| Figure 2.16 – Conventional heat sink for passive air cooling                                | . 39 |

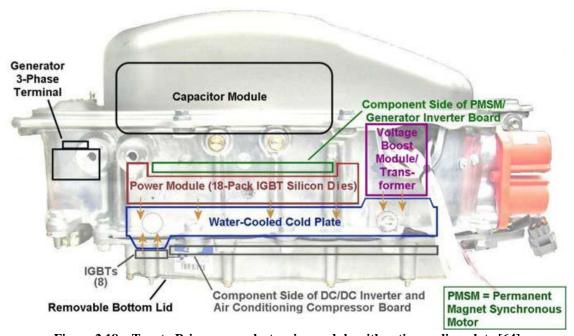

| Figure 2.17 – Ford Focus power electronics with cooling system                              | . 41 |

| Figure 2.18 – Toyota Prius power electronics module with active cooling plate [64]          | . 41 |

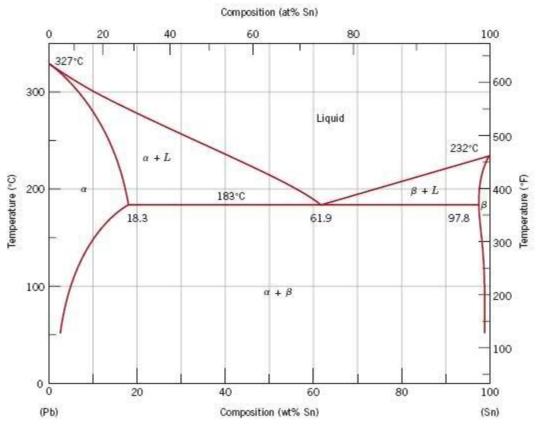

| Figure 2.19 – Tin-lead (Sn-Pb) phase diagram.                                               | . 44 |

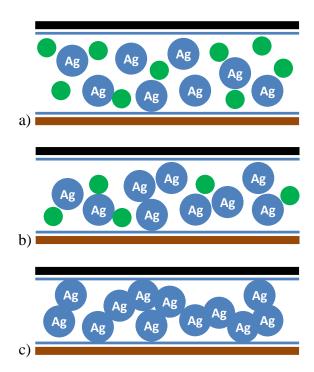

| Figure 2.20 - Silver sinter die-attach with silver sinter paste in which organic binders    |      |

| (green) evaporate and burnout with heat, leaving silver particles (blue) to sinter          |      |

| together and to silver material layers.                                                     | . 47 |

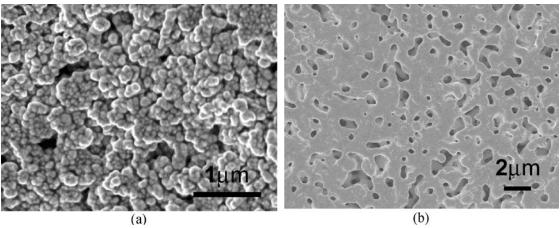

| Figure 2.21 – Surface morphology of nano-silver paste before and after high-pressure sinter |      |

| [82]                                                                                        | . 47 |

| Figure 2.22 – Silver sinter paste fabrication process [81]                                  | . 48 |

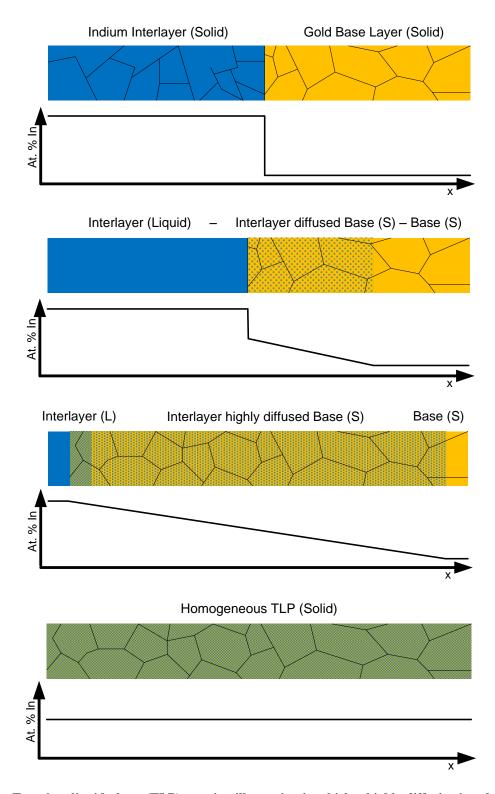

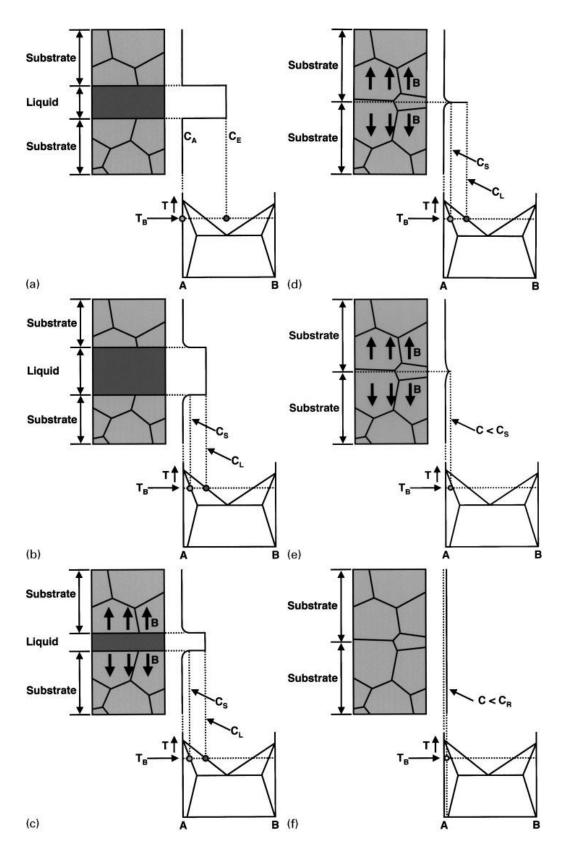

| Figure 3.1 – Transient liquid phase (TLP) reaction illustration in which a highly diffusive |      |

| interlayer diffuses into the high melting temperature base material, indium and gold,       |      |

| respectively, in this work. The In composition is plotted as it diffuses through the        |      |

| sample until complete. This composition solidifies into one homogenous composition          |      |

| while the reflow temperature is constant below the base melting point.                      | . 51 |

| Figure 3.2 – TLP reaction process by Gale et al. with the associated material phase of the  |      |

| two materials during the reaction until they are fully homogenized after isothermal         |      |

| solidification [88]                                                                         | 52   |

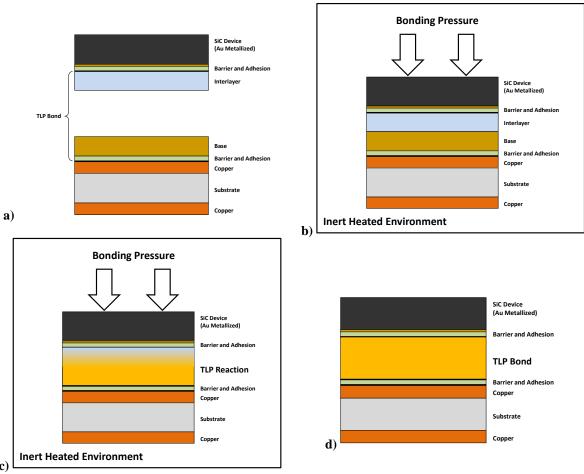

| Figure 3.3 – TLP die-attach bonding process in which SiC device and copper metallized       |      |

|---------------------------------------------------------------------------------------------|------|

| silicon nitride substrate are bonded in which the necessary TLP material are applied,       |      |

| the components are compressed in an inert heated environment, and they become               |      |

| bonded together.                                                                            | . 53 |

| Figure 3.4 – Select diffusion rates of indium into thin films                               | . 55 |

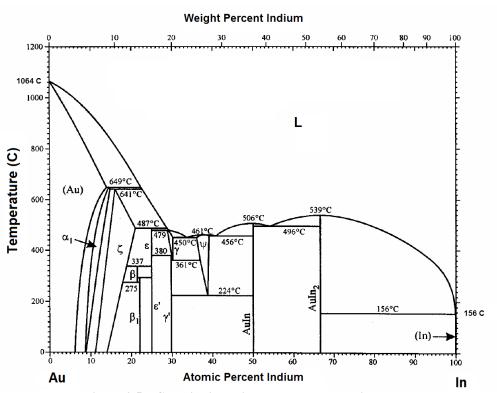

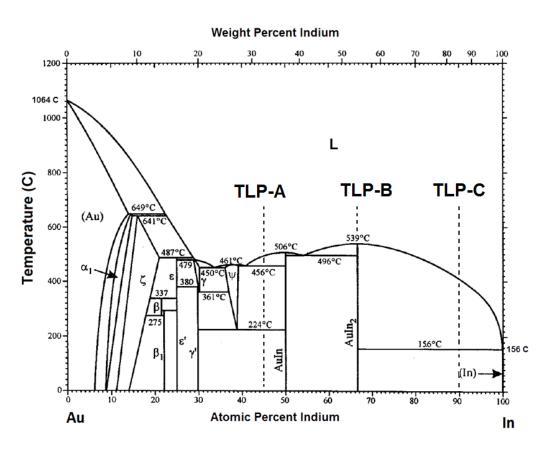

| Figure 3.5 – Gold–indium binary system phase diagram [7]                                    | . 59 |

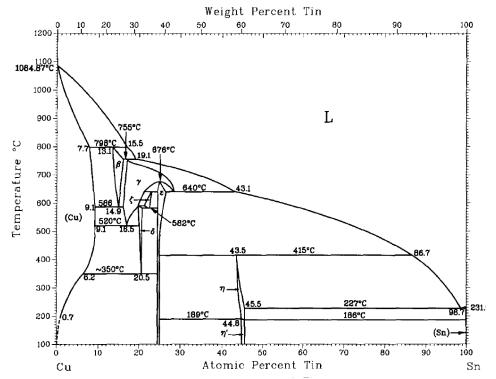

| Figure 3.6 – Copper–tin (Cu–Sn) phase diagram [142]                                         | 61   |

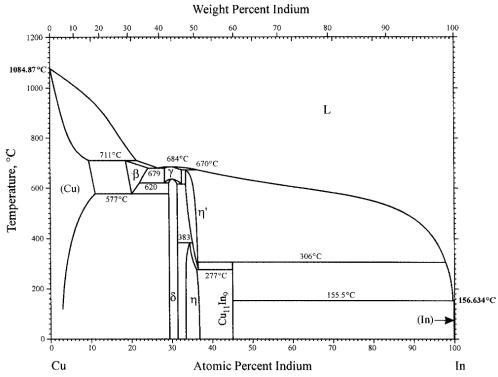

| Figure 3.7 – Copper–indium (Cu–In) phase diagram [145]                                      | 61   |

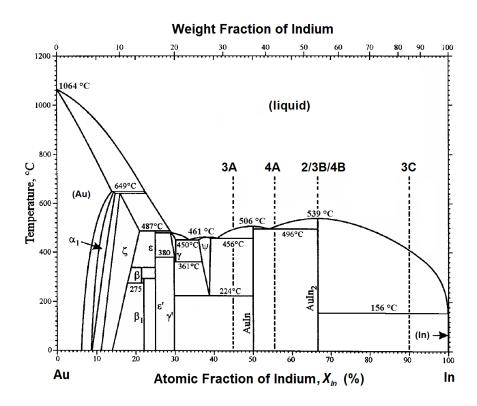

| Figure 5.1 – Binary phase diagram of the gold-indium (Au–In) system with TLP diffusive      |      |

| reliability test sample concentrations denoted from Table 5.1 [7]                           | . 70 |

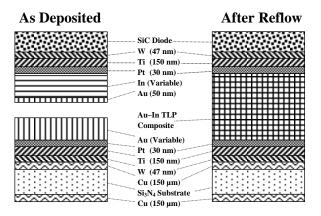

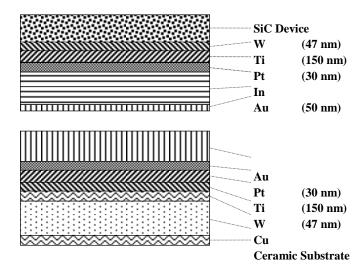

| Figure 5.2 – Material stack of a TLP die-attach sample joining a SiC power semiconductor    |      |

| diode to a copper metallized silicon nitride substrate before and after TLP bonding         |      |

| reaction.                                                                                   | . 73 |

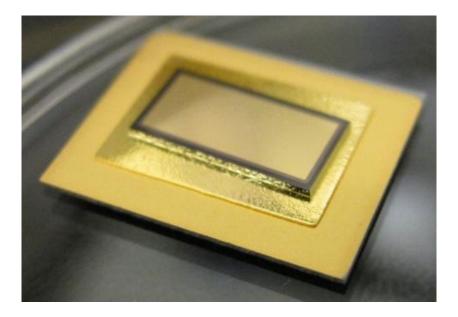

| Figure 5.3 - Fully constructed TLP sample featuring a SiC diode and silicon nitride         |      |

| substrate bonded by gold-indium (Au-In) TLP die-attach for thermo-mechanical                |      |

| characterization.                                                                           | . 73 |

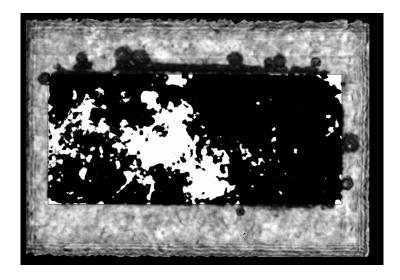

| Figure 5.4 – TLP die-attach C-SAM image showing a typical voiding pattern beneath the die   |      |

| in which voids occur evenly distributed                                                     | .74  |

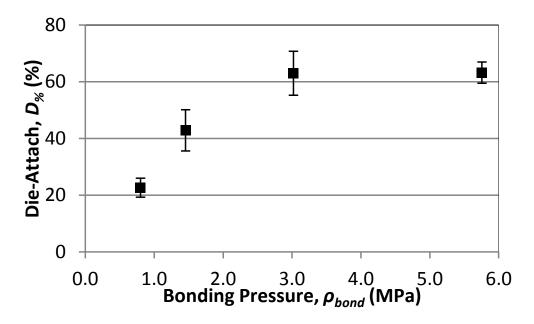

| Figure 5.5 – Die-attach percentage of TLP samples indicating a strong correlation to the    |      |

| fabrication bonding pressure. (Error bars indicate one standard deviation.)                 | .75  |

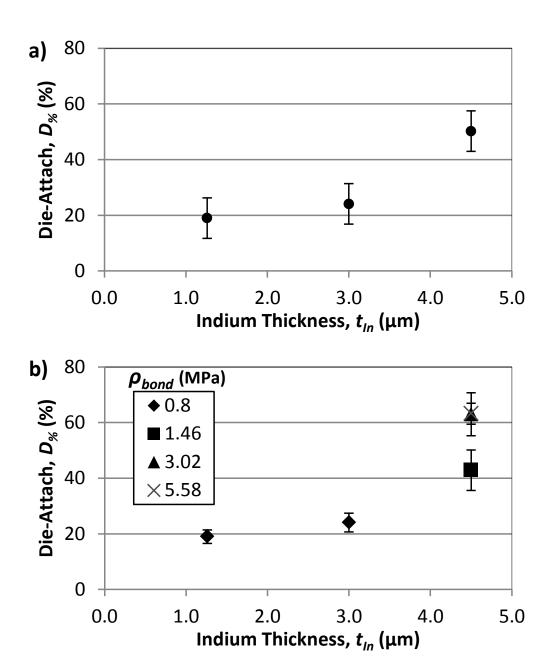

| Figure 5.6 – Die-attach percentage of TLP samples showing a positive correlation to thicker |      |

| indium interlayers. Fabrication bonding pressure is indicated in data of lower plot (b)     | . 76 |

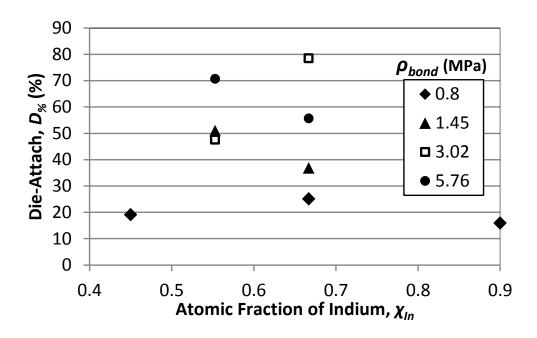

| Figure 5.7 - Die-attach percentage data plotted against the atomic fraction of indium            |

|--------------------------------------------------------------------------------------------------|

| showing no correlation of the two properties in the TLP bonds. The samples are                   |

| segregated by bonding pressure to separate its influence from the indium fraction77              |

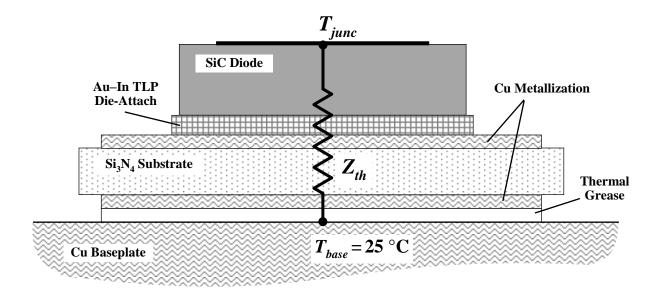

| Figure 5.8 – Diagram of thermal impedance $Z_{th}$ from the peak junction temperature $T_{junc}$ |

| through the device, TLP die-attach, metallized substrate, and thermal grease to the              |

| fixed temperature baseplate $T_{base}$ . Junction temperature is derived from the measured       |

| diode forward voltage drop $V_F$ which is a function of junction temperature                     |

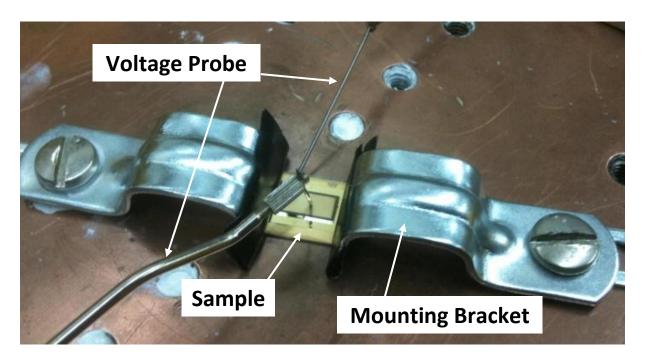

| Figure 5.9 – Thermal impedance mounting for characterization of a sample on a cooling            |

| baseplate held by two mounting brackets for mounting pressure uniformity. The                    |

| forward voltage drop is measured through two probing needles and used to extrapolate             |

| the peak junction temperature in the SiC diode in response to a heating power pulse              |

| during a unique customizable procedure                                                           |

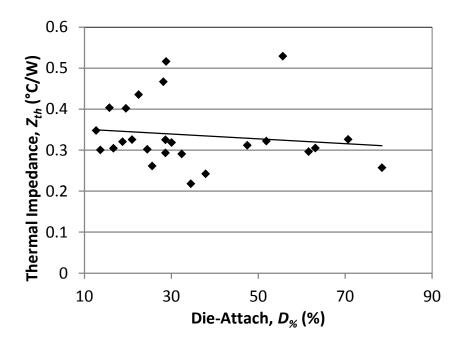

| Figure 5.10 – Thermal impedance of each TLP sample plotted against die-attach percentage         |

| comparison showing a subtle increase of impedance with decreasing die-attach area                |

| percentage80                                                                                     |

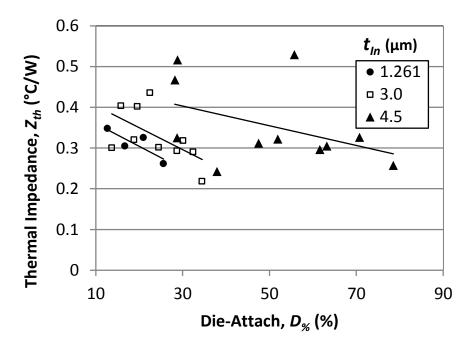

| Figure 5.11 – Thermal impedance of each TLP sample plotted against die-attach percentage         |

| comparison segregated by indium thickness with linear trends of each thickness                   |

| shown, indicating lower thermal impedance with thinner indium interlayer                         |

| independent of die-attach.                                                                       |

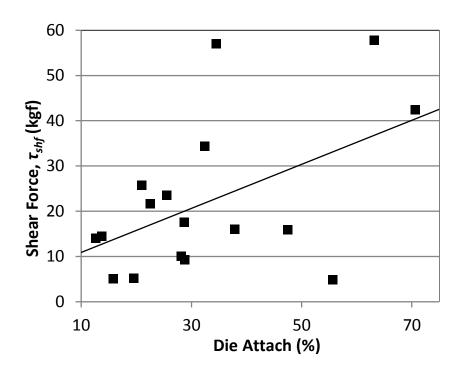

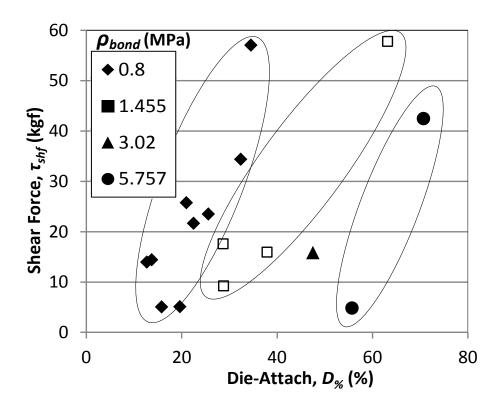

| Figure 5.12 – Dependence of TLP die-attach ultimate shear force on die-attach percentage 83      |

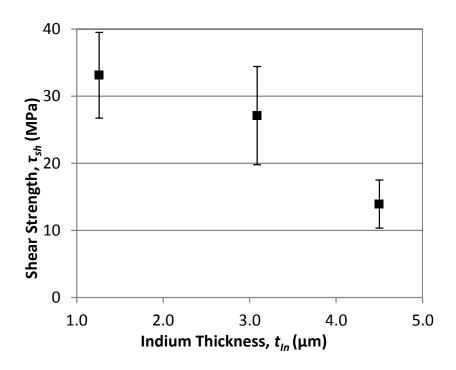

| Figure 5.13 – Dependence of TLP die-attach ultimate shear strength on indium thickness 84        |

| Figure 5.14 – TLP die-attach sample ultimate shear force data plotted against die-attach       |

|------------------------------------------------------------------------------------------------|

| percentage identified by samples' bonding pressure. Results show higher pressure               |

| bonded samples require higher die-attach percentage for comparable strength                    |

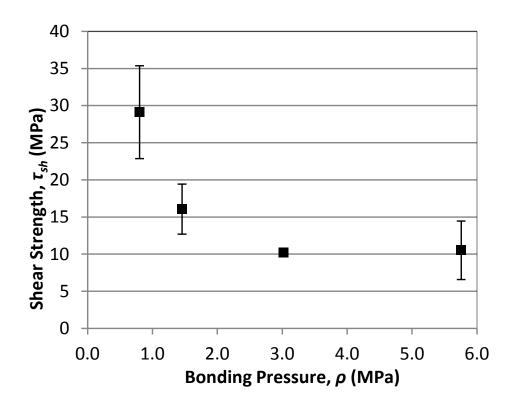

| Figure 5.15 - TLP die-attach sample ultimate shear strength versus bonding pressure,           |

| showing decreasing strength with increased pressure                                            |

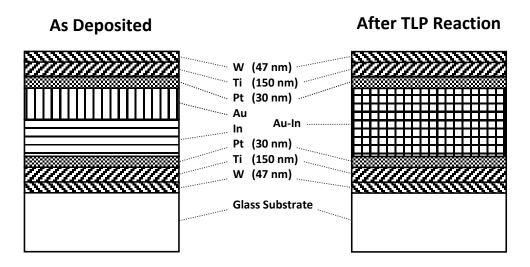

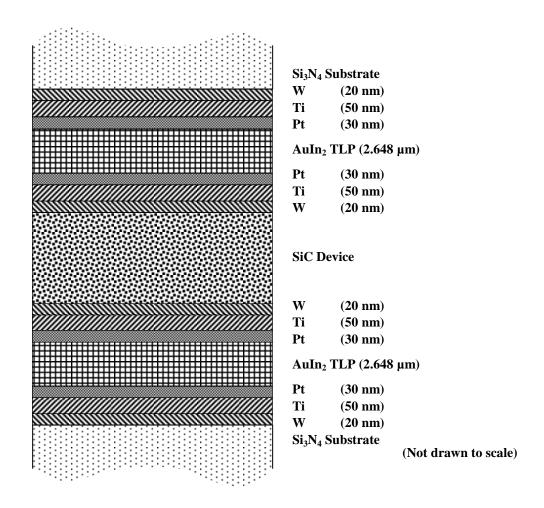

| Figure 6.1 – Material stack of TLP samples fabricated in this chapter emulating actual TLP     |

| bonds as they are before and after reflow. Gold and indium layer thicknesses vary by           |

| sample to create different material ratios seen in Table 6.1                                   |

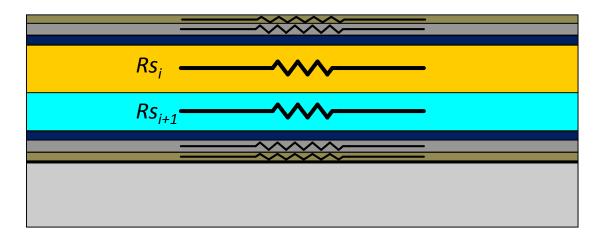

| Figure 6.2 – Representation of parallel sheet resistances in a thin film structure whose total |

| effective resistivity changes in the presence of material diffusion between them               |

| Figure 6.3 – Material stack of a TLP bond attaching a SiC power semiconductor device to a      |

| metalized substrate which this diffusion reliability work is designed to emulate94             |

| Figure 6.4 – Binary phase diagram of the gold-indium (Au–In) system with three test sample     |

| concentrations denoted at indium atomic fractions of 0.45, 0.67, and 0.90 within               |

| Samples TLP-A, B, and C, respectively [7]                                                      |

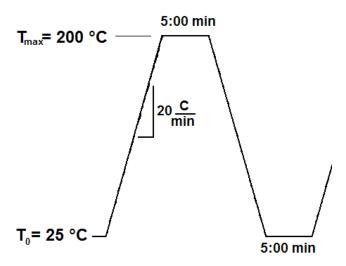

| Figure 6.5 - Representation of thermal cycles used to degrade samples and analyze              |

| durability and reliability95                                                                   |

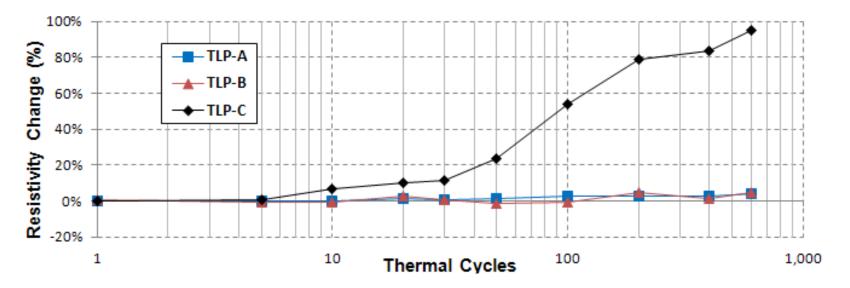

| Figure 6.6 – Measurement of resistivity change in Samples TLP-A, B, and C versus thermal       |

| cycling degradation showing excellent durability in higher gold concentration Samples          |

| TLP-A and B whereas Sample TLP-C, containing excessive indium, exudes poor                     |

| durability with increasing resistivity, indicating diffusion                                   |

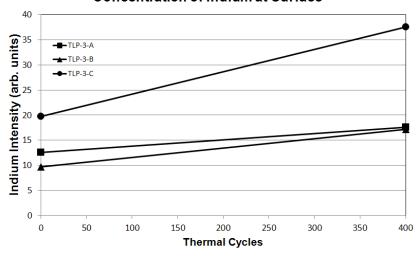

| Figure 6.7 – EDS surface characterization of TLP samples showing stability in Samples     |     |

|-------------------------------------------------------------------------------------------|-----|

| TLP-A and B and detrimental indium diffusion towards the sample surface through           |     |

| Pt/Ti/W barrier layers.                                                                   | 102 |

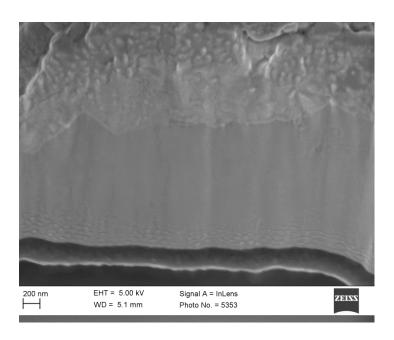

| Figure 6.8 - FIB cross section SEM image of Sample TLP-A showing multiple phases          |     |

| present and EDS characterization indicating AuIn <sub>2</sub> compound near the surface   | 102 |

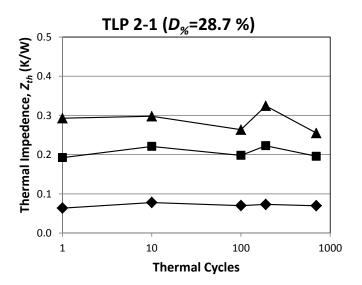

| Figure 6.9 - Thermal impedance durability in response to thermal cycling degradation of   |     |

| sample TLP 2-1.                                                                           | 104 |

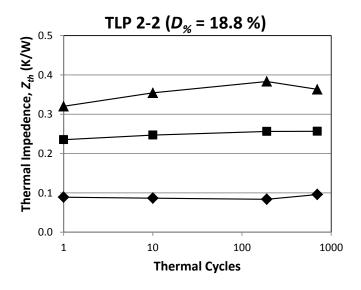

| Figure 6.10 – Thermal impedance durability in response to thermal cycling degradation of  |     |

| sample TLP 2-2.                                                                           | 104 |

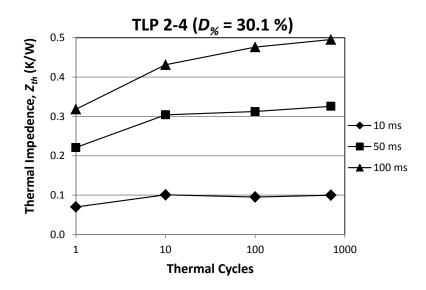

| Figure 6.11 – Thermal impedance durability in response to thermal cycling degradation of  |     |

| sample TLP 2-4.                                                                           | 105 |

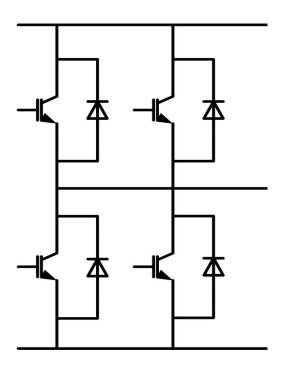

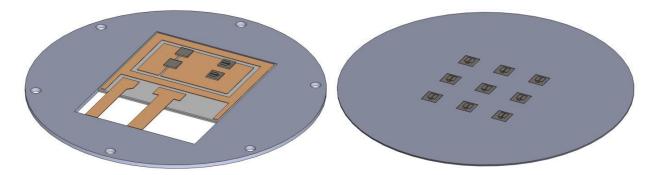

| Figure 7.1 – Half-bridge circuit design of high-temperature TLP power module featuring    |     |

| four SiC power MOSFETs                                                                    | 109 |

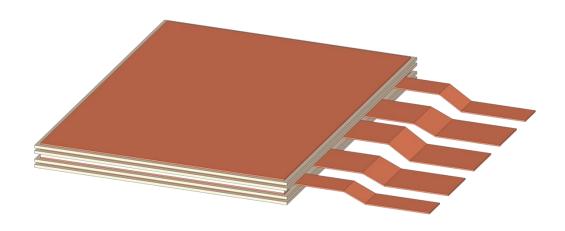

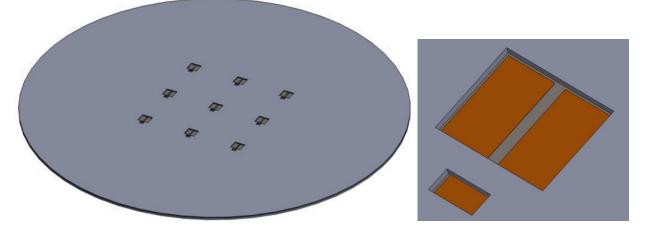

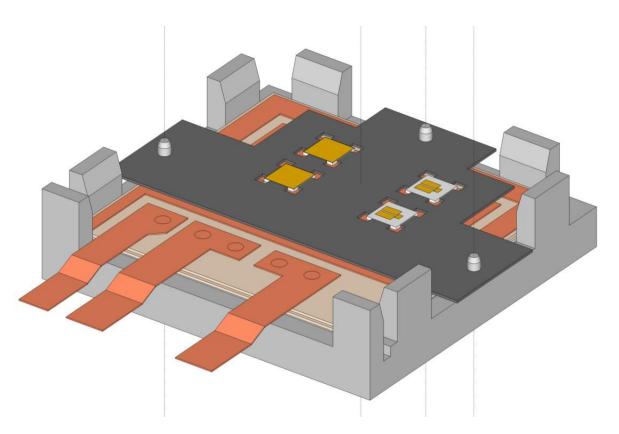

| Figure 7.2 – TLP power module design model                                                | 109 |

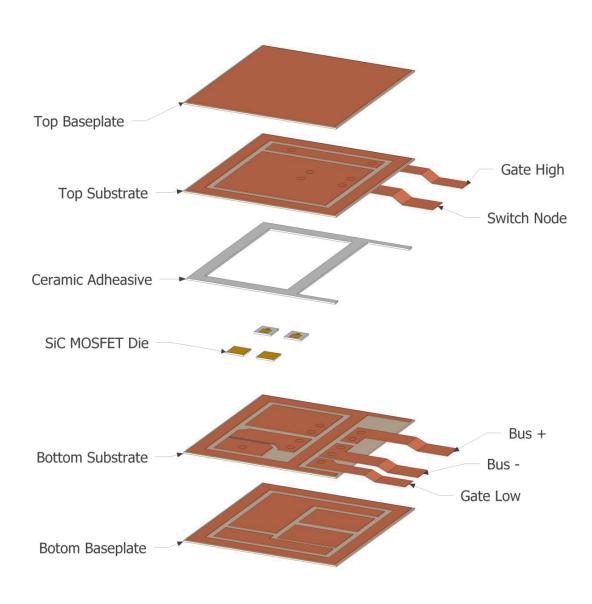

| Figure 7.3 – TLP power module exploded view showing all internal components               | 110 |

| Figure 7.4 – Material stack of a TLP die-attach in new module design surrounding SiC die  |     |

| between substrates                                                                        | 111 |

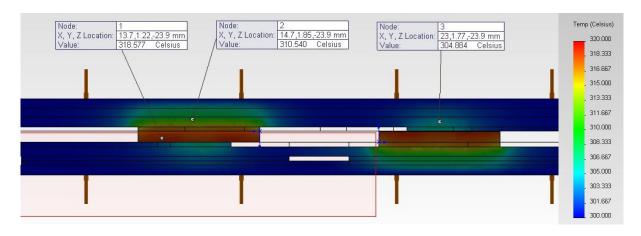

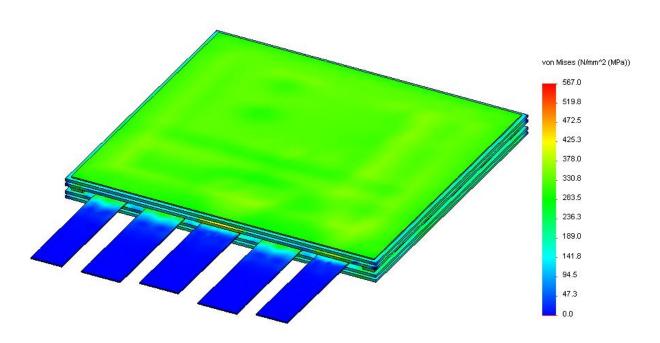

| Figure 7.5 – Thermal simulation of TLP power module given normal operating conditions in  |     |

| 300 °C ambient                                                                            | 112 |

| Figure 7.6 – Mechanical stress simulation of TLP module at 400 °C ambient temperature in  |     |

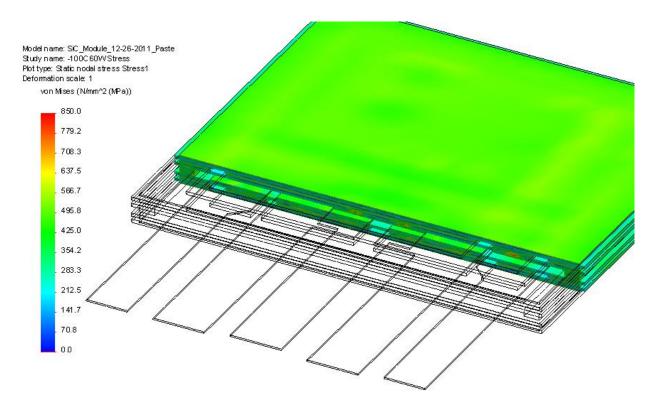

| operation                                                                                 | 114 |

| Figure 7.7 – Mechanical stress simulation of TLP module at -100 °C with sectioned view of |     |

| internal stress levels.                                                                   | 114 |

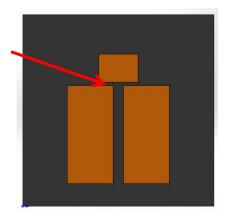

| Figure 7.8 – SiC MOSFET model showing 70 μm gap between source and gate pads              |

|-------------------------------------------------------------------------------------------|

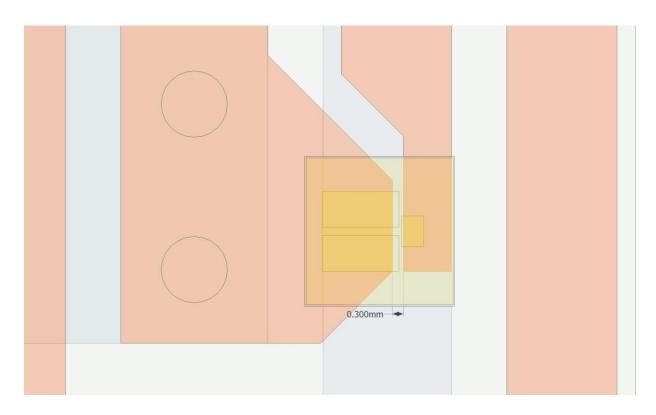

| Figure 7.9 – Modeled gap width between source and gate pad upon the MOSFET devices        |

| overlaid upon the specialty copper metallization traces                                   |

| Figure 7.10 - Deposition masks for holding MOSFET devices and substrates within           |

| deposition systems                                                                        |

| Figure 7.11 – Deposition masks allowing for deposition of material only on MOSFET gate    |

| and source pads without short circuiting passivation areas                                |

| Figure 7.12 – Assembly jig designed to constrain module components during fabrication and |

| align TLP bonds and device terminal pads                                                  |

### LIST OF TABLES

| Table 1.1 – Wide-Bandgap Semiconductor Properties                                             |

|-----------------------------------------------------------------------------------------------|

| Table 2.1 – Thermal Properties of Traditional Power Module Materials                          |

| Table 2.2 – Common High-Temperature Solder and Braze Materials                                |

| Table 3.1 – Comparison of Select Solder and TLP Die-Attach Properties                         |

| Table 3.2 – Select Material Diffusion Properties                                              |

| Table 5.1 – TLP Sample Fabrication Properties for Mechanical Characterization                 |

| Table 5.2 – Correlation of TLP Fabrication Parameters with Results                            |

| Table 6.1 – TLP Sample Design Parameters                                                      |

| Table 6.2 – Summation of Diffusion Effects on Total Resistivity in a Multi-Layer Thin Film 91 |

| Table 6.3 – Effective Resistivities and Calculation Properties of TLP Material Layers 100     |

| Table 6.4 – Concentration of Indium at Sample Surfaces                                        |

## LIST OF ABBREVIATIONS

| AC                             | Alternating Current                               |

|--------------------------------|---------------------------------------------------|

| AES                            | Auger Electron Spectroscopy                       |

| AlN                            | Aluminum Nitride                                  |

| DBC                            | Direct Bonded Copper                              |

| DC                             | Direct Current                                    |

| EDS                            | Energy Dispersive Spectroscopy                    |

| IGBT                           | Insulated Gate Bipolar Transistor                 |

| JBS                            | Junction-Barrier Schottky                         |

| MOSFET                         | Metal-Oxide-Semiconductor Field Effect Transistor |

| MPS                            | Merged PiN Schottky                               |

| RF                             | Radio Frequency                                   |

| SEM                            | Scanning Electron Microscope                      |

| Si <sub>3</sub> N <sub>4</sub> | Silicon Nitride                                   |

| SiC                            | Silicon Carbide                                   |

| SLID                           | Solid Liquid Inter-Diffusion                      |

| TLP                            | Transient Liquid Phase                            |

| WBG                            | Wide-Bandgap                                      |

## LIST OF VARIABLES

| χ <sub>In</sub> | Atomic Fraction of Indium   |

|-----------------|-----------------------------|

| $ ho_{bond}$    | Bonding Pressure            |

| D%              | Die-Attach Percentage       |

| $V_F$           | Forward Voltage             |

| $\lambda_0$     | Mean Free Path              |

| $ ho_T$         | Resistivity, Total          |

| $t_{In}$        | Thickness, Indium           |

| Z <sub>th</sub> | Thermal Impedance           |

| $	au_{sh}$      | Ultimate Die Shear Strength |

| $	au_{shf}$     | Ultimate Die Shear Force    |

#### **CHAPTER 1: INTRODUCTION**

#### 1.1 Motivation

Wide-bandgap power semiconductor devices, such as silicon carbide (SiC) diodes and MOSFETs, are now beginning to enter the power electronics marketplace which allow for improved power electronics performance. These wide-bandgap devices differ from silicon devices because of a wider energy bandgap which reduces the intrinsic carrier concentration and increases dielectric strength. These traits allow for lower power losses, higher efficiency, higher thermal conductivity, and much higher temperature operation capabilities than silicon [1–3]. Higher temperature capability is a critical improvement, with it there is increased potential for high-temperature applications that were previously impractical due to the low heat tolerance of silicon devices which must operate below 175 °C. A low temperature constraint requires the use of large cooling systems and bulky packaging modules for keeping the devices and critical packaging components cool so that they may operate reliability. Even still, they typically have short module life spans when operating in extreme environments where even possible. Widebandgap devices, however, demonstrate high-temperature capability with prolonged 500 °C operation demonstrated [3].

The benefits of these devices will allow for new applications of power electronics in a variety of applications. Exploration into deeper, higher-temperature down-hole well locations is now possible in the energy industry due to increasing access to difficult-to-reach natural resources. Geothermal energy will become more feasible to harness also, as it has been difficult to capture to date because it is inherently in the highest-temperature locations within the earth's

crust [4]. Overall system efficiency can increase in renewable energy power conversion and in electric vehicles by allowing for device operation at higher temperatures and reducing the power electronics' cooling systems to simple passive cooling methods. Wide-bandgap devices can also extend space exploration possibilities by reducing the need for warming and cooling boxes to house sensitive electronic components on satellites [5], [6].

Advanced packaging techniques are required, however, to implement high-temperature wide-bandgap devices into these and other applications. To transition to new packaging and allow the temperature to rise, the packaging must evolve using advanced packaging techniques to utilize wide-bandgap devices' full temperature range. Standard packaging technology is designed for silicon device temperatures and thus confines high-temperature device capabilities. Dieattach technology, which bonds the semiconductor device to a metalized substrate, is a critical need in the development of any new advanced packaging.

To achieve this, transient liquid phase (TLP) bonding is promising for die-attach due to its high-temperature capability equal to those of wide-bandgap devices [7–10]. There are many advantages of TLP bonding over alternative high-temperature die-attach techniques (e.g., brazing and silver sintering paste) including low thermal resistance due to its micrometer scale thickness and high thermal conductivity, lead-free capability, high mechanical strength, low mechanical stresses, and a simple bonding procedure with no binders to remove. TLP bonding die-attach and modern wide-bandgap power modules must be further investigated before major advances in packaging reliability, system reliability, and power electronic system size reduction becomes a reality.

#### 1.2 Statement of Benefit

This work is unique because it advances TLP die-attach research and understanding to assist wide-bandgap semiconductor devices, such as SiC, for their inclusion into high-temperature applications such as electric vehicles and renewable energy. This is primarily accomplished by the first known comparison and assessment of important TLP design parameters. This is unlike from any other previously done TLP analysis because a critical analysis of the fabrication of TLP die-attach bonds has been done and compares the fabrication parameters used in their design. This analysis is then used to realize dependencies and relationships of the success and failure of the bonds to their design to draw conclusions on creating better TLP bonds. This information will be invaluable to research and industry in the high-temperature packaging field by providing a greater understanding of how to design TLP bonds aside from already known information such as which materials can be used to create them.

Most TLP investigation prior to this one in the growing field of electronic packaging has amounted to "proof of concept" works in which the authors design and create a TLP bond then present a single characterization proving only that a bond was created. This leaves the reader to know only that a TLP bond was made but little more, and without any detailed knowledge of what contributed to the success or failure of the bond. This work highlights the design process as well as the characterization of several completed bonds in multiple designs to give a strong understanding of the role of important fabrication parameters. This is done by creating several bonds using the same design process with variation of only important parameters that are under inspection. Each of the design parameters are characterized for that particular parameter's importance to the design process and it is learned and shown how each of them affects TLP dieattach properties. This analysis has never before been seen.

Previous works typically used only one of a multitude of different characterization techniques, which again leaves the reader confused as to which bonds are actually of higher quality. In this work, several characterization of each design parameter are done so that the importance of each design parameter is known both mechanically and thermally through the use of scanning acoustic microscopy (C-SAM) for voiding analysis, die shear testing to measure shear strength, and peak junction temperature measurement for thermal impedance characterization. This work also performs several reliability inspections of TLP die-attach unlike any work prior. This includes a unique detection of unwanted diffusion within the bond in response to degradation using measurement of electrical resistivity. The durability of TLP thermal properties are investigated as well for the first known time.

TLP die-attach is in need of a refocus to lead it to implementation in high-temperature packaging and unleash wide-bandgap devices into important high-temperature applications. This work advances TLP die-attach past proof of concept work with a roadmap to design refinement and application.

#### 1.3 Wide-Bandgap Semiconductors

Wideband-gap semiconductors are defined by having a wider gap between the conduction and valence bands in the energy band diagram of the material than silicon. This typically results in more favorable material and device properties such as a lower intrinsic carrier concentration, higher dielectric voltage strength, and higher electron saturation velocity. This causes higher temperature operation ability, higher breakdown voltage, lower on-resistance, and faster switching for the devices created within them, which have the same basic structures as silicon such as diodes, MOSFETs, and IGBTs.

There are several wide-bandgap semiconductor materials that can be used for devices and among them SiC is the most well developed for power device. SiC devices have been in production for decades with improvement demonstrated in the early 1990s by North Carolina State University researchers who went on to found today's preeminent SiC substrate and device manufacturer Cree, Inc. (who supplied this project with SiC devices) [11]. It took many years for the devices to show reliability after initial proof-of-concept demonstrations but they improved in the mid-2000s with continuous high-temperature operation of first MESFETs then later diodes and MOSFETs. Development delays were rooted in substrate improvement to create pure single crystal substrates without micro-pipes or stacking faults which made devices unreliable. Eventually, low current power diodes were released in 2001 by Infineon to much fanfare and a decade later SiC MOSFETs entered the marketplace in January 2011 by Cree [12], [13].

There remain many other wide-bandgap materials which feature several key differences in material and device property from traditional silicon devices. Those properties are detailed in this section.

#### 1.3.1 Material

There are a several wide-bandgap semiconductor materials each with unique properties making some better for certain application, some less. Table 1.1 gives a succinct overview of the material properties of each major wide-bandgap material. It contains promising new materials, current ones, and past technologies such as germanium, the first semiconductor prototype ever produced [14]. Gallium arsenide (GaAs) may be the most common wide-bandgap device material in use today owing to its high electron mobility  $\mu_n$  which allows for very high switching speeds. This makes it very useful for high frequency communications such as mobile phones and

other communication industries. There are several different material properties each having distinct changes on the operation of a device built in that material [15].

Table 1.1 – Wide-Bandgap Semiconductor Properties

| Material | Bandgap, $E_g$ (eV) | Intrinsic<br>Carrier Con.,<br>$n_i$ , 300K(cm <sup>-3</sup> ) | Perm., $\varepsilon_r$ | Electron Mobility, $\mu_n (\text{cm}^2/\text{Vs})$ | Field Strength, $E_c$ (MV/cm) | Elec. Sat.<br>Velocity, v <sub>s</sub><br>(10 <sup>7</sup> cm/s) | Thermal Cond., λ (W/cm-K) | Bandgap<br>Type |

|----------|---------------------|---------------------------------------------------------------|------------------------|----------------------------------------------------|-------------------------------|------------------------------------------------------------------|---------------------------|-----------------|

| Si       | 1.1                 | 1.5E10                                                        | 11.8                   | 1350                                               | 0.3                           | 1.0                                                              | 1.5                       | I               |

| SiC (4H) | 3.26                | 8.2E-9                                                        | 10                     | ~700                                               | 2.0                           | 2.0                                                              | 4.5                       | I               |

| GaAs     | 1.4                 | 1.8E6                                                         | 12.8                   | 8500                                               | 0.4                           | 2.0                                                              | 0.5                       | D               |

| GaP      | 2.3                 | 7.7E-1                                                        | 11.1                   | 350                                                | 1.3                           | 1.4                                                              | 0.8                       | I               |

| InN      | 1.86                | ~1E3                                                          | 9.6                    | 3000                                               | 1.0                           | 2.5                                                              | -                         | D               |

| GaN      | 3.39                | 1.9E-10                                                       | 9.0                    | 900                                                | 3.3                           | 2.5                                                              | 1.3                       | D               |

| C        | 5.45                | 1.6E-27                                                       | 5.5                    | 1900                                               | 5.6                           | 2.7                                                              | 20                        | I               |

| BN       | 6.0                 | 1.6E-31                                                       | 7.1                    | 5                                                  | 10                            | 1.0                                                              | 13                        | I               |

| AlN      | 6.1                 | ~1E-31                                                        | 8.7                    | 110                                                | 11.7                          | 1.8                                                              | 2.5                       | D               |

| Ge       | 0.66                | 2.4E13                                                        | 16.0                   | 3900                                               | 0.1                           | 0.5                                                              | 0.6                       | I               |

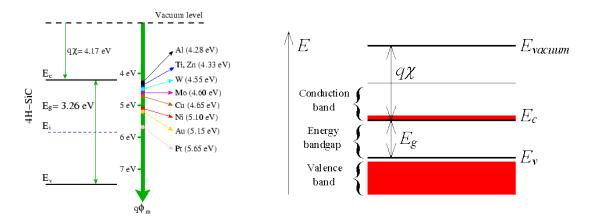

#### 1.3.2 Bandgap

The bandgap  $E_g$  describes the separation of the valance and the conduction band in the semiconductor energy band diagram. For an electron-hole pair of free carriers to be created, an electron must cross the bandgap from the valance band  $E_v$  to the state of higher energy the conduction band  $E_c$ . The bandgap is described in electron volts as the amount of energy that an electron must gain to cross the energy bandgap. This energy commonly arrives thermally, thus for a wider bandgap at an equal temperature fewer electron hole pairs will be formed and there will be fewer mobile charge carriers formed in the semiconductor. These are intrinsic carriers which are described in the next section.

Figure 1.1 – Energy band diagram of 4H-SiC material

Bandgap may be described as direct or indirect. This corresponds to the valence and conduction bands versus the wave number k by taking the energy band diagram into the third dimension. Regardless of  $E_V$  or  $E_C$  vs. k, the bandgap is measured typically from the lowest energy of  $E_C$  to the highest magnitude of  $E_V$ , if these points happen to be at the same wave number then the material is known to have a direct bandgap and the electrons and hole transfer

more directly at the same wave number. These materials have lower carrier lifetimes leading to faster devices [16]. Direct bandgap semiconductors also emit energy as a photon thus releasing light when electrons cross the bandgap. Silicon and SiC are both indirect bandgap semiconductors thus alternative wide-bandgap semiconductors are needed in the area of lasers and optics [17].

#### 1.3.3 Intrinsic Carrier Concentration

Intrinsic carrier concentration  $n_i$  is the average amount of electron hole pairs in an unbiased semiconductor per unit volume. It is a function of  $E_g$  and temperature by

$$n_i = \overline{N_c N_v} \exp^{-E_g} 2kT \frac{1}{cm^3}, \tag{1.1}$$

where

$$N_c = 2 \frac{2\pi m_e^* kT}{h^2}^{3}$$

(1.2)

and

$$N_{v} = 2 \frac{2\pi m_{h}^{*} kT}{h^{2}}^{3}$$

(1.3)

in which  $m_e^*$  and  $m_h^*$  are the effective mass of an electron and hole, respectively [16]. It can be assumed  $m_e^*=m_h^*$  for simplification, thus,

$$n_i = 2 \frac{m^* kT}{2\pi h^2}^{3} \exp \frac{-E_g}{2kT} \frac{1}{cm^3}.$$

(1.4)

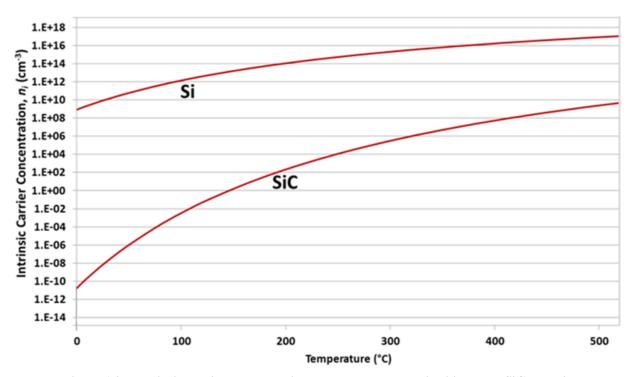

It can be seen in Table 1.1 that as the bandgap increases,  $n_i$  begins to reduce drastically, which is desirable. SiC carrier concentration is observed to be 18 orders of magnitude lower than silicon at  $n_i = 8.2\text{E-9 cm}^{-3}$ . A few electron volts have a dramatic impact on its value in silicon and SiC because  $n_i$  has an exponential relationship to  $E_g$  [18]. Carrier concentration is dependent on also temperature, as defined by (1.4), thus devices become ineffective at higher temperatures because of excess free carriers. SiC maintains  $n_i$  much lower than silicon up to very high temperatures, within the range of most high-temperature electronic applications, as seen in Figure 1.2 [19]. This constraint limits silicon device operation to 125 °C before the intrinsic carriers dominate, but SiC devices have been demonstrated to constant operation at 500 °C [3].

Figure 1.2 – Intrinsic carrier concentration versus temperature in silicon and SiC material

#### 1.3.4 High-Temperature Capability

Lower intrinsic carrier concentrations in wide-bandgap materials facilitate higher temperature operation. Lower  $n_i$  equates to fewer minority carriers in devices which often contribute to loss due to increased body currents and also can trigger BJT latch-up within the device. These losses increase with temperature until operation is no longer possible, however with a lower  $n_i$ , peak temperature increases several hundred of degrees Celsius, depending on device type and failure mechanism.

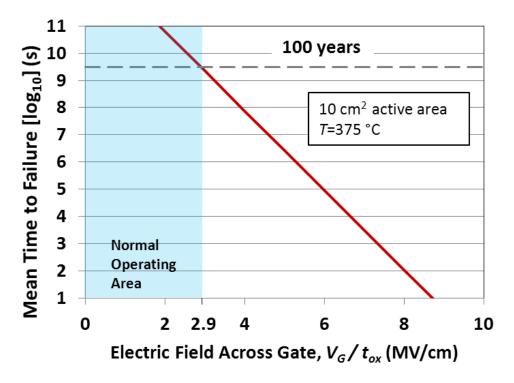

Figure 1.3 – SiC oxide reliability shown by mean time to failure (MTTF)

Poor reliability of the gate oxide has been one of the principal impediments to the implementation of WBG devices, specifically SiC, at high temperature. SiC has the benefit over other WBG materials of the capability to grow native SiO<sub>2</sub> on the surface. However, it has a lower conduction band offset than Si–SiO<sub>2</sub>, also the effective barrier height of this junction is reported to lower with temperature and increase leakage. Altogether, SiC devices were not

thought to be reliable over 250 °C [20]. This understanding has changed with new experimental data of increased oxide quality on SiC showing that gate oxides can withstand 375 °C for 100 years at up to 2.9 MV/cm of field across it as shown in Figure 1.3 [21].

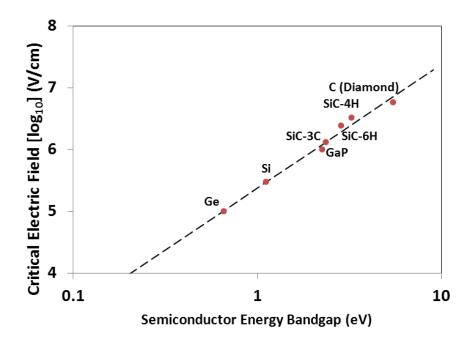

#### 1.3.5 Electric Field Strength

A material's dialectic, or electric field, strength  $E_C$  is the greatest determinant of its voltage blocking capability. For silicon,  $E_C = 0.3$  MV/cm and in SiC  $E_C$  is an order of magnitude higher at 3.18 MV/cm [22]. This is due to the dependence of  $E_C$  on the bandgap as described by

$$E_c = 1.02 \times 10^7 \frac{q}{\epsilon} N_B^{1/8} E_g^{3/4}.$$

(1.5)

This relationship is presented in Figure 1.4 showing increasing  $E_C$  with  $E_g$  for multiple wide-bandgap semiconductor materials [23]. Increased electric field strength directly relates to the breakdown voltage of a device fabricated in it.

Figure 1.4 – Relationship of electric field strength to energy bandgap in semiconductor materials [23]

#### 1.3.6 Breakdown Voltage

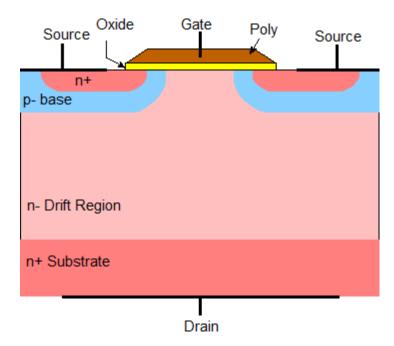

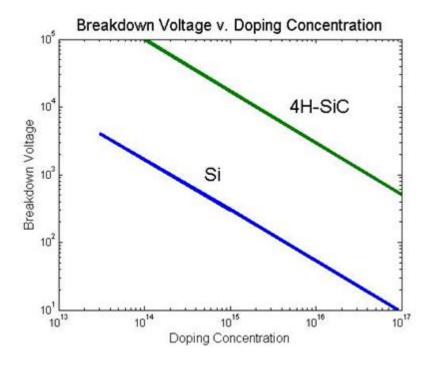

The breakdown voltage  $V_{BV}$ , or blocking voltage, is the voltage up to which a device blocking junction will block the in reverse bias, preventing current flow in the opposing direction or when off. This is typically a PN junction as in MOSFETs, IGBTs, and JBS diodes, however it maybe a metal semiconductor junction as in a Schottky or JBS rectifier. The breakdown is determined by two important factors; one is a static material property, the  $E_C$ , the other is a design dimension, the background doping concentration  $N_A$  of the drift region, as seen in Figure 1.5 [24]. A depletion region predominantly forms in the lightly doped drift region as voltage is applied to the junction, more so than in the N or P well where the inversion channel is formed. Lower  $N_A$  causes a greater depletion region width leading to a lower voltage gradient  $\binom{dV}{dx}$ . This gradient must be higher than the  $E_C$  or the device will no longer block current. There is a direct relationship between blocking voltage and doping concentration in non-punch through devices as shown in Figure 1.6. Devices with higher rated blocking voltages have wider more lightly doped drift regions. Because wide-bandgap materials have much higher  $E_C$ , they may have much higher  $V_{BV}$  across a thinner drift region than silicon [1].

Figure 1.5 – DMOS device structure [24]

Figure 1.6 – Breakdown voltage versus doping concentration in silicon and SiC materials [1]

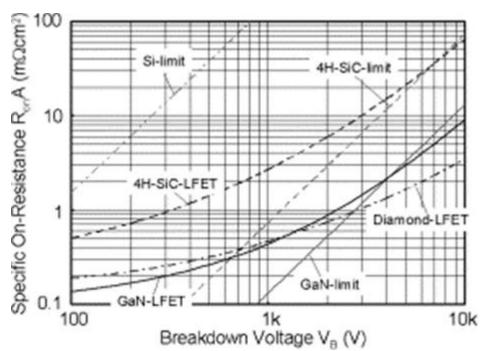

#### 1.3.7 Specific On Resistance

High electric field strength is a great advantage to specific on resistance  $SpR_{DS,on}$  of wide-bandgap devices as well.  $SpR_{DS,on}$  is the resistance, normalized by area, through an on state device at a certain gate voltage. The high electric field strength allows for manipulation of the two primary design dimensions that determine  $SpR_{DS,on}$ :  $N_A$  and the drift region width. Decreasing  $N_A$  to increase  $V_{BV}$  also increases  $SpR_{DS,on}$ . However, since  $E_C$  is higher in wide-bandgap material,  $N_A$  may be increased with much higher  $V_{BV}$  than silicon devices. This is because greater depletion doping keeps the region thinner with an equal or higher breakdown voltage. Thus the drift region may be designed much thinner which causes a reduction in  $SpR_{DS,on}$  since majority carriers pass through a shorter distance from drain to source. Similar to Figure 1.6, the  $SpR_{DS,on}$  is linked to  $N_A$  as seen in Figure 1.7 [25]. SiC devices have shown  $R_{DS,on}$  up to 200 X smaller for comparable silicon devices with the same  $V_{BV}$  [26].

Figure 1.7 – Specific on-resistance of semiconductors vs. breakdown voltage [25]

#### 1.3.8 Mobility

Electron mobility  $\mu_n$  also varies in wide-bandgap material from silicon. It is lower in some wide-bandgap semiconductors, including SiC, which is a disadvantage unlike so many other wide-bandgap material properties. The lower mobility in SiC and GaN does raise  $SpR_{DS,on}$  for comparably designed silicon devices, however the effect is largely neutralized because in actual devices the  $SpR_{DS,on}$  is lower by the shortened drift region. This makes bipolar devices less practical in SiC because of the decreased mobility of the minority carriers in addition to the already low  $R_{DS,on}$  of single carrier devices [16]. SiC suffers less from mobility degeneracy at high doping concentrations, however, where it is actually higher than silicon for  $N_D > 3$ E17 [1].

#### 1.4 <u>High-Temperature Power Electronic Applications</u>

There are several applications for power electronics that must endure high temperatures that can be enhanced by wide-bandgap devices and new packaging. All power electronics are inherently associated with high temperatures because the high currents and voltages they operate at in conjunction with their higher on-resistances create a great deal of heat loss which must be removed from the device. This is difficult for some applications however due to a high ambient temperature around the system such as in space applications or because the cooling system required to keep the devices cool is a large hindrance to overall system performance such as in an electric vehicle.

The benefits of these devices will allow for new applications of power electronics in a variety of fields. Exploration into deeper, higher-temperature well locations is now possible in the energy industry due to increasing access to difficult-to-reach natural resources. Geothermal energy will become more feasible to harness also, as it has been difficult to capture to date

because it is inherently in the highest-temperature locations within the earth's crust [4]. Overall system efficiency can increase in renewable energy power conversion and in electric vehicles by allowing for device operation at higher temperatures and reducing the power electronics' cooling systems to simple passive cooling methods. Wide-bandgap devices can also extend space exploration possibilities by reducing the need for warming and cooling boxes to house sensitive electronic components on satellites [5], [6].

#### 1.4.1 High Power, High Ambient Temperature Limitation

Some power electronics are required to operate in harsh environments which have no ambient environment available to base a cooling system in that can keep silicon devices below their 175 °C rating. Eqn. (1.6) shows the maximum power loss  $P_{loss}$  of a device based on  $T_{j,max}$  of the device, the ambient temperature of the cooling environment  $T_{amb}$ , and the total thermal resistance from device to ambient  $R_{\theta JA}$  by [27]

$$P_{loss} = \frac{T_{j,max} - T_{amb}}{R_{\theta IA}},\tag{1.6}$$

which gives  $T_{i,max}$  as a function of  $T_{amb}$  by

$$T_{j,max} = P_{loss} \cdot R_{\theta JA} + T_{amb}. \tag{1.7}$$

This suggests that  $T_{amb}$  cannot exceed a device's maximum temperature rating nor can it approach it without considering the temperature rise due to  $P_{loss}$ . This type of situation is excellent to employ wide-bandgap devices such as underground energy exploration, geothermal

energy, or oil well logging. Space based electronics also lack a cool ambient environment which inhibits satellites' ability to house sensitive electronic components.

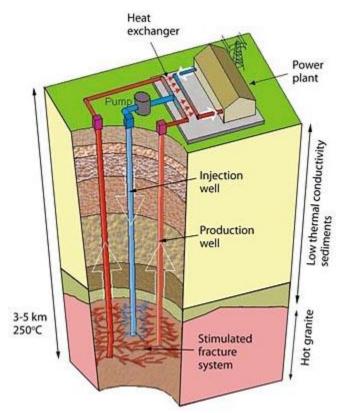

#### 1.4.2 Down-Hole Energy Extraction

Geothermal energy is a very promising energy source which only requires very high underground temperatures and has been aided in development by oil well drilling. It is a stable renewable energy supply that does not fluctuate in weather and has the potential to provide over 10 % of the country's total energy demands with 100 GW of capacity. The process of geothermal energy harvesting is simple. Instead of traditional energy production techniques where a heat source is created to heat water to drive steam through turbines which create energy; the heat source is natural underground heat present within the earth where temperatures reach thousands of degrees Celsius. There is enough geothermal energy to heat water to the required temperatures of 250–300 °C if one digs up to 10 km down anywhere in the United States [28].

To harness this energy, two wells are dug, one is the injection well which pumps water down into the earth, the second well is the production well from which the heated water rises into turbines which produce electricity [29]. This simple system has been advanced in recent years to enhanced geothermal systems (EGS) in which the heated rocks in the ground are intentionally cracked and fractured. This creates more surface area on them to more efficiently heat water pumped in to produce steam. New geothermal systems are typically closed systems where the extracted hot water is pumped back down to keep output water temperatures high and water consumption down, as seen in an EGS well is shown in Figure 1.8. Temperature typically need to be 250 °C or higher, depending on depth, for geothermal plants to be practical with higher temperatures at shallow depths best. The western United States is largely more practical than the

eastern region, along with areas near tectonic fault lines or historic volcanic areas. However with the advent of more durable high-temperature devices and packaging this would no longer be a prerequisite [30].

Figure 1.8 – Diagram of EGS geothermal plant and well [29]

Underground rock formations must be well characterized for geothermal extraction and well digging, and also to properly asses the area's capability for geothermal energy. This is similar in the oil industry, in a process known as oil well logging. This is where the opportunity for high-temperature devices and packaging are greatest. Many sensors are required which draw a sizable power supply to operate in these extreme temperatures for extended periods of time to characterize wells. Electronics are required during the drilling of the wells also. Although oil

wells do need to be in high-temperature rock formations, as required for geothermal, newly tapped oil wells are typically in higher and higher temperature locations since oil in shallow low temperature locations is being depleted. Increased temperature capability of oil discovery and collection would be very beneficial.

Currently, most electronics are protected by Dewar flasks that provide a heat shielded environment around electronic though the use of a vacuum for a fixed period of time. They have a maximum temperature of 400 °C and can protect electronics at 300 °C for 4-12 hours before failure or a return to the surface. There are currently no long term monitoring sensors to operate continuously in all parts of wells [31]. Silicon-On-Insulator (SOI) is a common high-temperature resilient fabrication and design technique with silicon electronics that has been necessary for existing higher temperature technologies. SOI incorporates a buried insulator, such as SiO<sub>2</sub>, to block the increased leakage current that rises with temperature, however it does not match SiC and other wide-bandgap semiconductor's capabilities.

#### 1.4.3 Reduced Cooling Capacity Systems

A need to reduce overall system size and weight can be accomplished by reducing the cooling system mass. Transportation vehicles of all kinds, such as hybrid-electric automobiles and airplanes, are relatively small working environment for high density high power electronics which make cooling a challenge. Also, transportation power electronics must be physically carried by the vehicle thus the weight of the electronics and the cooling system is a factor in overall system efficiency. There are two cooling loops in some hybrid vehicles, one for the engine and a separate loop just for active cooling electronics. By reducing the cooling system or removing it in favor of passive cooling the load can be lightened considerably [27].

# 1.4.4 Higher Efficiency Systems

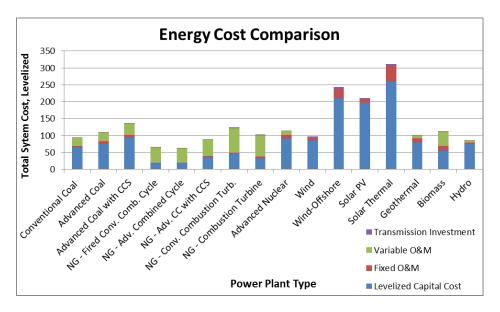

Most renewable power electronic systems require all efficiency and power system capital cost savings possible. Wide-bandgap devices in high-temperature packaging are attractive for this reason because they offer the efficiency improvements of SiC and the reduced system capital cost of high-temperature ability by not utilizing a cooling system. Unlike high-temperature environment applications or those with reduced cooling capability, renewable energies often are able to have a cooling system easily installed. However, they are competing fiercely in the marketplace with existing energy sources as they develop and would benefit by shedding a potentially sizable cooling system considering the large amount of power electronics required to perform a host of energy conditioning tasks in converting their variable DC power into grid-ready 120 V AC. By removing their cooling system this will reduce the high initial capital costs that currently plague renewable energies, as seen in

Figure 1.9, [32]. This would likely also reduce operations and maintenance costs and further increasing the competitiveness of renewable energies.

Figure 1.9 – Comparison of normalized energy costs for multiple sources as a culmination of capital costs, operations, maintenance, and transmission [32].

# CHAPTER 2: REVIEW OF HIGH-TEMPERATURE PACKAGING PRIOR ART

This work strives for advancement in the field of high-temperature power packaging. A focus of prior work in the field is on large conventional half-bridge power modules containing only a few high-current, high-powered devices which are still the primarily power module used today. With SiC device beginning to enter the marketplace, these modules typically contain silicon devices and are built for the low temperature range of silicon electronics (< 150 °C). Another packaging focus has been for high-temperature transportation applications, and other demanding environments which are also discussed, but not always used for high-power devices. This packaging employs other high-temperature die-attach materials that prelude TLP bonding along with high-temperature silicon devices.

#### 2.1 Conventional Power Module

The conventional power module contains two switching devices, typically IGBTs, and two anti-parallel diodes to form a half-bridge circuit. Although the circuitry is simple, the packaging design is not because it must withstand large temperature changes over its lifecycle and allow for the removal of large amounts of energy losses with a high thermal conductivity design.

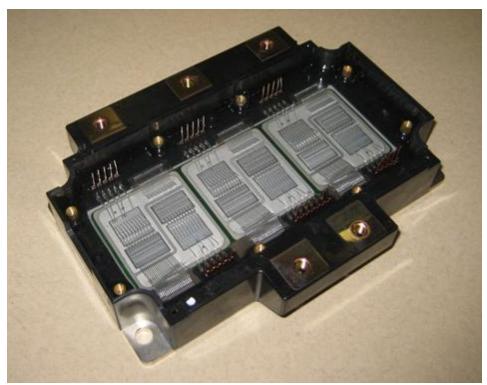

The insulated gate bipolar transistor (IGBT) power module is an extremely popular component in power applications. There is currently an industry standard design for the half-bridge power module with silicon IGBT devices as the switching device and freewheeling anti-parallel diodes seen in Figure 2.1. The design became common in the early 1990s as the IGBT

became more popular in the market place [33]. The IGBT can be used in much greater power densities than the MOSFET at low frequencies due to its low conduction losses.

The half-bridge design is designed to produce a sinusoidal output wave with an inductive load from a DC supply voltage. It is useful for motor control applications and it is typically found in trains, electric vehicles, and other traction devices. These fields are expected to grow for the foreseeable future with rising demand for electric powered transportation due to its environmentally friendly potential. This places an added importance on packaging design. The circuit is also used in high voltage power transmission and can be used to produce a DC voltage output in a buck or boost convert.

Figure 2.1 – Conventional IGBT power module

#### 2.1.1 Half-Bridge Circuit Design and Operation

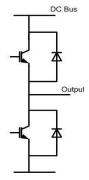

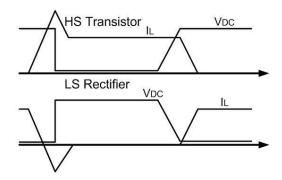

A common half-bridge circuit consists of a high and low side switch with freewheeling diodes and is seen in Figure 2.2. In motor control operation and DC to AC voltage inversion the output voltage will be sinusoidal. The device switching frequency is orders of magnitude higher than the output frequency thus each switch cycle is only infinitesimally different from the previous with an approximately constant output current. A switch cycle is seen in Figure 2.3, where a switch and its opposite rectifier are in conjunction. As the high side IGBT switch turns on, the output current  $I_L$  transfers from the low side diode to the high side IGBT. As the diode approaches  $I_L = 0$  A, the diode suffers reverse recovery current and causes additional strain on the transistor at IGBT turn on as a current spike. The IGBT current and the diode blocking voltage stabilize as excess charge carriers diminish within the diode. The IGBT current, which is the output current of the circuit at this time, rises over this time period infinitesimally due to the higher DC bus voltage of the transistor input charging the inductive load by  $\frac{di}{dt} = \frac{v \ t}{L}$ . When the IGBT turns off, excess carriers exit it while its blocking voltage rises, exactly similar to the diode. This again leads to switching power loss in the device and system. The system is again

Figure 2.3 – Half-bridge switching waveform [34]

in discharging state at  $I_L = 0$  A in the switch where the current is actually lowering by  $\frac{-di}{dt} = \frac{v \ t}{L}$  as in the beginning of the waveform figure [34].

The gate control of the module is pulse width modulated (PWM) for a sinusoidal output or a more constant duty cycle corresponding to a single DC output voltage depending on the application. On times of the devices must adjust dynamically since the output current  $I_L$  is always slightly fluctuating due the charging or discharging of the load. This is why the switching frequency is much higher than the output frequency. Both the IGBT and p-i-n diodes are dominated by switching losses, therefore the circuit is bound by a reasonable operating frequency which is typically around 20 kHz [1]. These switching losses produce heat which dominates packaging designs for these power circuits leading to robust thermal consideration examined at in the following section.

The half-bridge may be modified without freewheeling diodes in which an inductive DC motor is connected to the high voltage DC, parallel to the high side switch. The low-side switch acts as a drive switch MOSFET and when it is switched on the current will flow through the motor and voltage source. The high side switch acts as a freewheeling switch when the drive switch is off to allow the inductive motor current to flow through the freewheeling switch and back to the motor [35].

The half-bridge circuit configuration can also be expanded to serve a similar role for three phase current, where three identical half-bridges are placed in parallel on the DC bus to produce three AC voltages of the same frequency and amplitude but each 120 degrees out of phase. This circuit configuration and module topography is seen in Figure 2.4.

In CHAPTER 1 it is seen that wide-bandgap semiconductors can improve circuit performance. There are much few minority carriers in bipolar devices due to the lower intrinsic

carrier concentration of SiC, nearly eliminating minority charge reverse recovery [36]. Also, the lower  $SpR_{DS,on}$  makes it possible to use unipolar SiC MOSFETs instead of bipolar IGBTs. This leads to much lower conduction and switching losses compared to silicon IGBTs.

Figure 2.4 – Three phase half-bridge circuit diagram and module

# 2.1.2 Conventional Power Module Design

Construction of conventional modules has remained similar for over two decades, indifferent to the exact circuit configuration or the number of phases or switches. The cross sectional view is seen in Figure 2.5 [37]. There are many components of the module for both electrical and thermo-mechanical reasons. The design is robust and its fabrication begins with the placement of direct bonded copper (DBC) substrate. DBC is a sandwich structure of a ceramic material with copper layer on either side, aluminum nitride (AlN) is a common ceramic insulator because of its high thermal conductivity although aluminum oxide may also be used because of their lower cost. Silicon nitride (Si<sub>3</sub>N<sub>4</sub>) is also a less common option which features higher strength and allows for the insertion of conducting copper vias through the ceramic. Power semiconductor devices are then soldered to the top side of the DBC typically with tin-lead solder.

The DBC is then soldered to a heat spreader or baseplate with a lower melting point solder so as not to reflow the die-attach solder material. The DBC and baseplate are then attached to a semi-heat resistant, plastic enclosure which typically has rigid power interconnects built into it extruding from the plastic while the copper baseplate is still exposed. Wirebonding or ribbon attachment is then done to connect the DBC traces to the top-side device pads, typically gate, collector, and anode connections, and also the traces to the power interconnects. After which, the plastic enclosure is filled with a silicone based encapsulant gel for protection from debris, dielectric insulation, and additional thermal conductance from the devices [38]. This process makes for large modules with a mass upwards of 3 kg primarily due to the thick plastic packaging and the thick copper baseplate, none of which is necessary but for thermo-mechanical ruggedness.

Figure 2.5 – Conventional power module cross section [38]

#### 2.1.3 Power Module Thermal Design Considerations

The power module is designed to bridge the need for electrical, thermal, and mechanical demands. Design methodology dictates that once electrical connection demands are met, thermomechanics dominate leading to a large form factor. This is because when the module is in use, devices can produce over 270 W of power loss per device at 10 kHz with 114 W from conduction and an additional 164 W from switching losses, these amounts only increase with faster switching [39]. A fundamental design goal of the modules is to remove the power loss to keep  $T_{j,max}$  of the device below the 175 °C silicon device limit. Also, power loss leads to mechanical stress from material expansion because materials expand with higher temperatures as determined by their coefficient of thermal expansion (CTE).

Each material has two primary steady state thermal performance characteristics: CTE and thermal conductivity. These properties are listed for each common power module material in Table 2.1 and are carefully considered in module design.

**Table 2.1 – Thermal Properties of Traditional Power Module Materials**

| Material         | CTE<br>(µm/m-K) | Conductivity (W/m-K) |

|------------------|-----------------|----------------------|

| Copper           | 16.4            | 385                  |

| Aluminum         | 24              | 210                  |

| Silicon          | 3.0             | 124                  |

| SnPb40 Solder    | 24              | 50                   |

| Aluminum Nitride | 4.5             | 83                   |

| Thermal Grease   |                 | 0.75                 |

### 2.1.3.1 Coefficient of Thermal Expansion

CTE is the rate at which a material expands in response to heat. Typically ceramics and non-ductile material have low CTE, although some metals also have a low CTE. Every material has a CTE and it is measured in parts per million per Kelvin (µm/m/K). This is an important

material property because two joined materials that do not expand identically when heated will inflict force and stress on each other until a failure occurs. This process is the basis of nearly every single mechanical failure type in power modules. Larger CTE mismatches between joined materials cause larger stress per Kelvin.

Silicon and SiC have relatively low CTEs compared to most metals at 3.0 µm/m/K and 3.6 µm/m/K, respectively. Therefore this low CTE is the benchmark for every other material CTE to be used in any power module because the devices cannot be removed. Every material should have as similar CTE to silicon or SiC as possible to avoid large CTE mismatch. Unfortunately, some common materials of conventional modules do not have low CTEs and cause stress. This can often be because of price or complication of changing the module manufacture process. It may be because the other material has a low thermal resistance which is also desirable.

#### 2.1.3.2 Thermal Resistance and Specific Heat Capacity

Thermal conductivity k is a measure of a material's ability to transfer heat power efficiently and is the reciprocal of thermal resistivity  $\rho_{th}$ . Lower resistivity imposed on heat flow causes a lower thermal gradient across it and lower peak temperature. Thermal resistance is exactly similar to electrical resistance except for heat flow instead of current. Therefore, like CTE, each material should have as low of thermal resistivity as possible.

Electrical capacitance is emulated by thermal capacitance, or specific heat capacity  $c_p$ . This property is most important when considering switching; heat capacity resists temperature change like a capacitor and maintains temperature after the device is turned off. The effect of these two thermal properties is seen in Figure 2.6 which gives a thermal model of a power module with heat resistance and specific heat capacity of each material. They are in series with

each other where voltage is analogous to temperature and heat power flow to current [40]. Improving thermal performance reduces module temperature which also decreases CTE expansion, therefore reducing stress can be achieve through temperature reduction or improved CTE matching.

#### 2.1.4 Power Module Reliability Issues

Power modules endure a great deal of thermo-mechanical stress from the CTE mismatches causing several types of failures and reliability degradation issues. Figure 2.7 displays the relationship between the average amount of module usage cycles before failure and the rise in  $T_{j,max}$  during each cycle [41]. Module reliability is commonly expressed this way because a change in temperature brings about a proportionate amount of stress depending on CTE. A smaller  $\Delta T$  each cycle produces less stress, thus identical modules should operate more cycles on average with a lower  $\Delta T$  than with a greater  $\Delta T$ . More importantly, since power modules are used heavily in traction devices there is a great deal of thermal cycling because of the constant starting and stopping of vehicles. Constant thermal cycling leads to several reoccurring reliability issues including die cracking, DBC delamination, and wirebond failure.

Figure 2.7 – Module cycles to failure vs. temperature rise reliability [41]

© 1998 IEEE

# 2.1.4.1 Direct Bonded Copper Delamination

There is good adhesion between DBC and AlN, the highest thermal conductivity ceramic insulator. This is achieved by oxidizing copper which forms a copper oxide bond layer and then annealing the oxidized surface upon AlN at 1070 °C [38]. This bond combats the 11.9  $\mu$ m/m/K CTE mismatch between the two, however, give enough thermal cycles it will eventually fail. When doing so, DBC lifts off the ceramic substrate and curls causing solder and devices to break off. If the devices do remain after copper delamination, it will cause the heat flow to bottleneck into whatever contact remains between the copper and ceramic, raising the effective thermal resistance several orders of magnitude. This will lead to a huge temperature rise in  $T_{j,max}$ , solder, and wirebonds which quickly leads to device burnout or causes another interface to succumb to CTE stress failure [42].

#### 2.1.4.2 Die Cracking of Device

Conventional tin–lead solder (SnPb40) is sandwiched between silicon and copper which have CTE differences with the solder of 21  $\mu$ m/m/K and 7.6  $\mu$ m/m/K, respectively. Because of this, it is a common reliability issue point. This sometimes results in the solder itself cracking, as seen in Figure 2.8, or in the die itself cracking or breaking [43]. This sort of failure is less common than others due to the ductile nature of tin-lead solder.

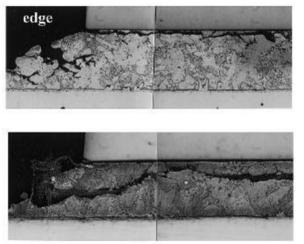

Figure 2.8 – SEM cross section of solder cracking failure [43]

© 2003 IEEE

#### 2.1.4.3 Wirebond Issues

Semiconductor wirebonding is the cause of 70 % of IGBT power module failures. Their problems cause two common types of failures, one is liftoff due to CTE mismatch. There is no ductile buffer between silicon die and aluminum wirebonds direction upon it leaving a 21  $\mu$ m/m/K CTE mismatched interface, a difference matched within the module only by the more ductile solder and silicon interface [44]. This wirebond connection is also the interface that experiences the highest temperature rise since it is directly at  $T_{j,max}$ , leading to the greatest expansion of those materials which leads to even higher CTE stress [45].

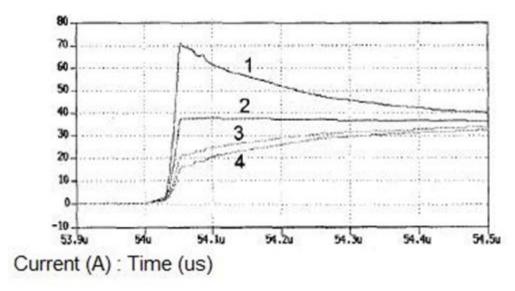

The other concern for wirebonds is inductance, their mutual inductance and high current acts upon other wirebonds within the module which causes non-uniform current sharing between devices. There is already concern of reverse recovery currents from power diodes and IGBTs in play. The addition of parasitic inductance has the potential to destroy the devices by further exceeding their current ratings. This phenomenon is especially true on the devices further from the center of the module because there is likely to be a balance of electromagnetic forces acting on the inner wires. Outer wires, however, are not typically as inductively balanced thus they are more prone to burnout [46]. This phenomenon is seen in a graph of the transient currents of parallel devices in a module in Figure 2.9 [37]. The lower numbered devices are on the periphery of the module while the higher numbered devices are in the center. It is seen that for several dozen microseconds the current can be at severe imbalance with some devices 100 % higher than the steady state current and others 66 % below it, easily pushing some devices above their current ratings.

Figure 2.9 – Non-uniform current in parallel devices within power module [37] © 1998 IEEE

# 2.2 Advanced Power Module Designs

There are many ideas and designs in power module packaging which attempt to introduce new high-temperature wide-bandgap semiconductors into modules while also attempting to address traditional problems with current modules.

#### 2.2.1 Press Pack Module