University of Central Florida

STARS

Electronic Theses and Dissertations, 2004-2019

2006

# On-chip Spiral Inductor/transformer Design And Modeling For Rf Applications

Ji Chen University of Central Florida

Part of the Electrical and Electronics Commons Find similar works at: https://stars.library.ucf.edu/etd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS Citation**

Chen, Ji, "On-chip Spiral Inductor/transformer Design And Modeling For Rf Applications" (2006). *Electronic Theses and Dissertations, 2004-2019.* 1024. https://stars.library.ucf.edu/etd/1024

## ON-CHIP SPIRAL INDUCTOR/TRANSFORMER DESIGN AND MODELING FOR RF APPLICATIONS

by

# JI CHEN B.S. Fudan University, 2001

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical Engineering in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Fall Term 2006

Major Professor: Juin J. Liou

© 2006 Ji Chen

## ABSTRACT

Passive components are indispensable in the design and development of microchips for high-frequency applications. Inductors in particular are used frequently in radio frequency (RF) IC's such as low-noise amplifiers and oscillators. High performance inductor has become one of the critical components for voltage controlled oscillator (VCO) design, for its quality factor (Q) value directly affects the VCO phase noise. The optimization of inductor layout can improve its performance, but the improvement is limited by selected technology. Inductor performance is bounded by the thin routing metal and small distance from lossy substrate. On the other hand, the in-accurate inductor modeling further limits the optimization process.

The on-chip inductor has been an important research topic since it was first proposed in early 1990's. Significant amount of study has been accomplished and reported in literature; whereas some methods have been used in industry, but not released to public. It is of no doubt that a comprehensive solution is not exist yet. A comprehensive study of previous will be first address. Later author will point out the in-adequacy of skin effect and proximity effect as cause of current crowding in the inductor metal. A model method embedded with new explanation of current crowding is proposed and its applicability in differential inductor and balun is validated. This study leads to a robust optimization routine to improve inductor performance without any addition technology cost and development.

## ACKNOWLEDGMENTS

Both this dissertation and the author myself have benefited from many people over the years. This work would have been impossible without their help and encouragement.

Foremost, I thank my advisor, Dr. Juin J. Liou, whose insights and advice are the strongest support and guidance of the accomplishment of this research. Working with him in the past five years has been a challenging and joyful experience. I would also thank my committee members for their willingness to evaluate this work and for their valuable comments and suggestions.

Special thanks to Dr. Yun Yue, Dr. Thomas Wu and Dr. Xun Gong. They are intelligent and diligent researchers. The discussion with them gives me practical and theoretical direction of this research, which are unobtainable from any textbooks.

Thanks to all the members in Dr. Liou's lab for their help in many ways: Xiaofang Gao, Zhi Cui, Yue Fu, Hao Ding (best tennis and travel partner), Lifang Lou, Zhiwei Liu, Daniel Osborne, Brian Chang and You Li. They are great people to work with, and I feel so lucky to have these lab-mates. Thanks also go to my friends in Orlando. Life without you would be unbearable.

Last but certainly not least, I would like to thank my parents who have been overcoming all difficulties to offer my sister and I good education and better life. Thanks for their love and support.

# **TABLE OF CONTENTS**

| LIST OF FIGURES                              |

|----------------------------------------------|

| LIST OF TABLES xiv                           |

| LIST OF ACRONYMS/ABBREVIATIONS xv            |

| CHAPTER ONE: INTRODUCTION 1                  |

| 1.1 Motivation                               |

| 1.1.1 Need for Inductors 1                   |

| 1.1.2 The Effect of Inductor Quality Factor  |

| 1.2 Description of Problems                  |

| CHAPTER TWO: LITERATURE REVIEW               |

| 2.1 Modeling Concept and Design Guideline    |

| 2.1.1 Series Inductance                      |

| 2.1.2 Resistances                            |

| 2.1.3 Capacitances                           |

| 2.1.4 Q Factor and Substrate Loss            |

| 2.1.5 Modified $\pi$ Models                  |

| 2.2 Advanced Structures                      |

| 2.2.1 Structures to Reduce Substrate Loss    |

| (a) Ground Shield                            |

| (b) Substrate Removal                        |

| (c) Horizontal Inductors                     |

| 2.2.2 Structures to Reduce Series Resistance |

| (a) Vertical Shunt                                              | 31 |

|-----------------------------------------------------------------|----|

| (b) Horizontal Shunt                                            | 32 |

| (c) Line Width Optimization                                     | 33 |

| 2.2.3 Structures to Increase Inductance                         | 34 |

| (a) Stacked Inductor                                            | 34 |

| (b) Miniature 3-D Inductor                                      | 35 |

| 2.2.4 Symmetrical Inductor                                      | 37 |

| 2.2.5 Alternative Patterns                                      | 40 |

| CHAPTER THREE: MODELING METHODOLOGY                             | 44 |

| 3.1 Introduction                                                | 44 |

| 3.2 Model Development of Symmetrical Inductor                   | 46 |

| 3.2.1 Nonuniform Current Distribution in Metal Lines            | 49 |

| 3.2.2 Modeling the Segment Box                                  | 53 |

| (a) Series Inductance                                           | 53 |

| (b) Series Resistance                                           | 56 |

| (c) Substrate Parasitics                                        | 57 |

| 3.2.3. Modeling Components Outside Segment Box                  | 59 |

| (a) Coupling Capacitance Between Metal Lines                    | 59 |

| (b) Overlap Parasitics                                          | 61 |

| 3.3 Model Development of Asymmetrical Inductor                  | 63 |

| 3.4 Model Verification                                          | 64 |

| 3.5 Conclusions                                                 | 71 |

| CHAPTER FOUR: APPLICATION IN DIFFERENTIAL INDUCTORS AND BALUNS. | 72 |

| 4.1 Introduction                                      | 72  |

|-------------------------------------------------------|-----|

| 4.2 Model Development                                 | 74  |

| 4.2.1 Nonuniform Current Distribution                 | 74  |

| 4.2.2. Differential Inductor                          |     |

| 4.2.3. Transformer/Balun                              | 79  |

| 4.3 Model Verification and Discussions                | 81  |

| 4.4 Conclusions                                       | 87  |

| CHAPTER FIVE: APPLICATION IN METAL WIDTH OPTIMIZATION | 88  |

| 5.1 Introduction                                      | 88  |

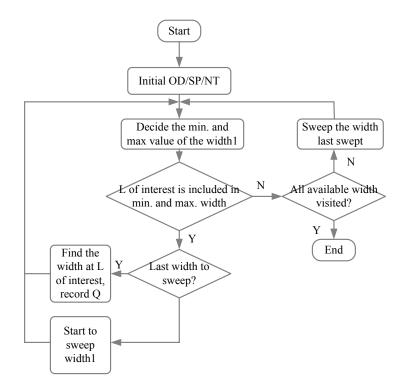

| 5.2 Optimization Approach Development                 | 91  |

| 5.3. Experimental Verification                        | 94  |

| 5.4. Conclusion                                       | 98  |

| CHAPTER SIX: SUMMARY AND FUTURE WORK                  | 99  |

| 6.1 Summary                                           | 99  |

| 6.2 Future Work                                       | 100 |

| LIST OF REFERENCES                                    | 102 |

# **LIST OF FIGURES**

| Figure 1 Topology and cross section of a typical on-chip square shaped spiral inductor. (after [4]). |

|------------------------------------------------------------------------------------------------------|

|                                                                                                      |

| Figure 2 Equivalent circuit of a basic gyrator                                                       |

| Figure 3 Schematic of a bond wire inductor (after [6])                                               |

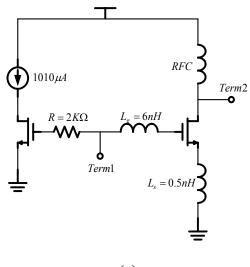

| Figure 4(a) A typical low-noise amplifier, (b) simulated noise figures, and (c) simulated            |

| small-signal current gains. In the simulations, the two active inductors were assumed having         |

| the same Q factors and the Q factors were increased from 5 to 25                                     |

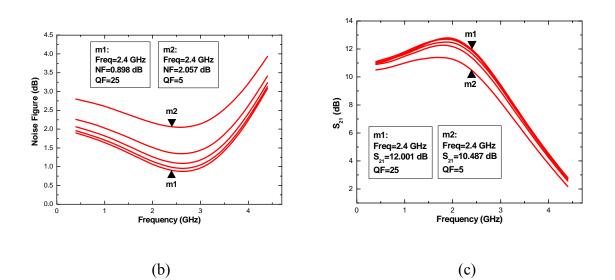

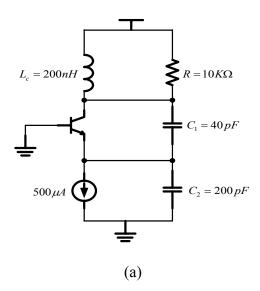

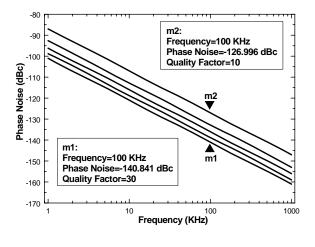

| Figure 5(a) An RF oscillator circuit, and (b) simulated phase noises of the circuit with the         |

| inductor's Q factor increasing from 10 to 30                                                         |

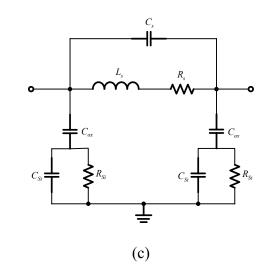

| Figure 6 Lumped $\pi$ models for spiral inductors developed by (a) Nguyen and Meyer [9]; (b) Ashby   |

| et al. [10]; and (c) Yue and Wong [11]                                                               |

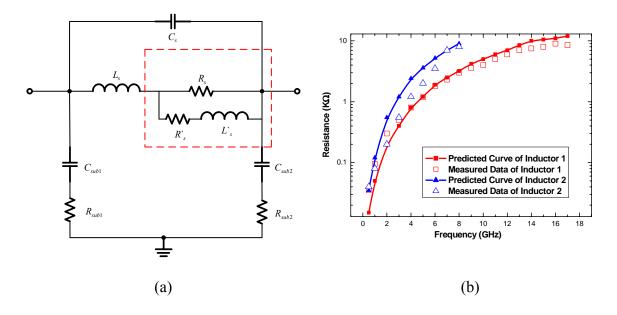

| Figure 7 (a) Model with improved series resistance (dashed line box) developed by Ooi et al. and     |

| (b) resistances measured and simulated for two different inductors (after [21])14                    |

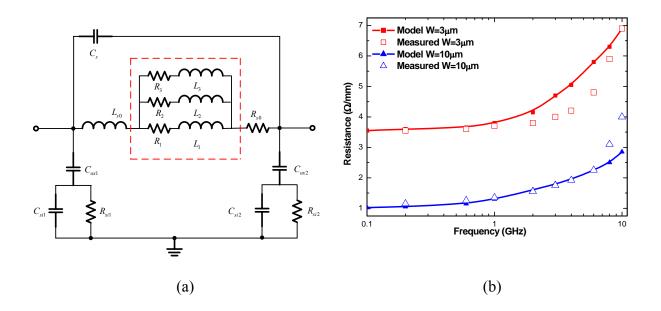

| Figure 8(a) Model with improved series resistance (dashed line box) developed by Rotella et al.      |

| and (b) resistances measured and simulated for two different inductors (after [23])                  |

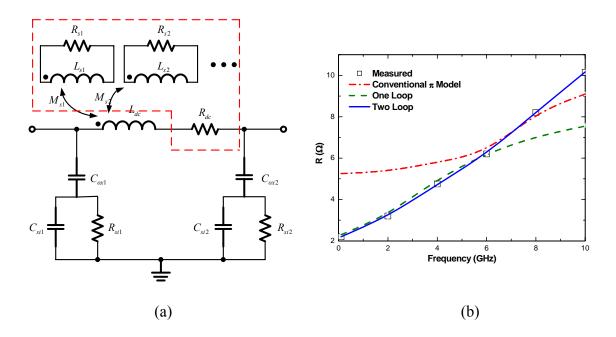

| Figure 9 (a) Model with improved series resistance (dashed line box) developed by Melendy et al.     |

| and (b) resistances measured and simulated from the conventional model and improved                  |

| model with one and two R/L loops in the dashed line box (after [24])                                 |

| Figure 10 Equivalent circuit of spiral inductor developed by Wu et al. [26]                          |

| Figure 11 Equivalent circuit of one terminal grounded inductor for modeling the Q factor 20          |

| Figure 12 Eddy and displacement currents in the substrate induced by the current flow in inductor        |

|----------------------------------------------------------------------------------------------------------|

| spiral                                                                                                   |

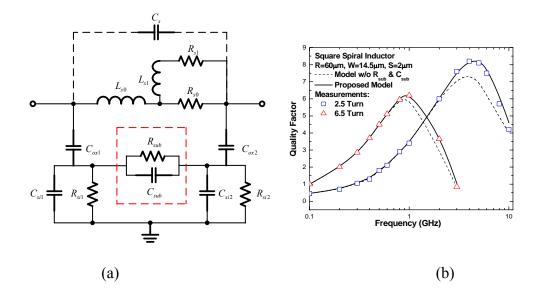

| Figure 13(a) Improved inductor model with horizontally coupled resistance and capacitance ( $R_{sub}$    |

| and $C_{sub}$ ) and (b) Q factors measured and simulated with and without $R_{sub}$ and $C_{sub}$ (after |

| [29])                                                                                                    |

| Figure 14(a) Improved double $\pi$ model to more accurately account for the frequency-dependent          |

| series resistance and inductance and (b) Q factors measured and simulated from the                       |

| conventional and improved models (after [19])23                                                          |

| Figure 15(a) Modified $\pi$ model with RLC laddered network and (b) Q factors measured and               |

| calculated from the modified model (after [30])24                                                        |

| Figure 16(a) Quality factors measured and calculated from model in Figure 7(a); (b) Inductances          |

| and quality factors measured and calculated from model in Figure 8(a)                                    |

| Figure 17(a) Schematic of patterned ground shield (PGS) and (b) quality factors of solid ground          |

| shield (SGS), PGS, and no ground shield (NGS) (after [28])                                               |

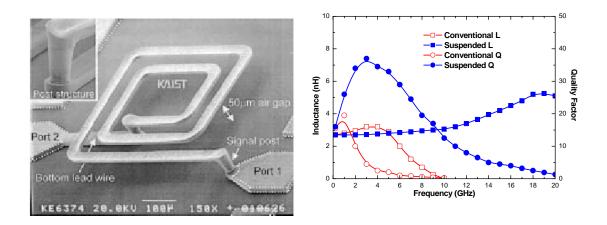

| Figure 18(a) Topology of the suspended inductor and (b) comparison of inductances and Q factors          |

| of conventional and suspended inductors (after [37])                                                     |

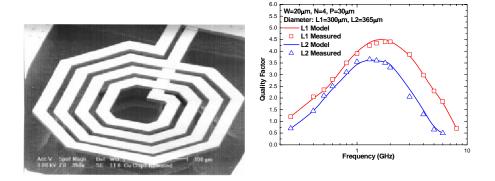

| Figure 19(a) Topology of the micromachined inductor and (b) Q factors of such an inductor with           |

| two different diameters (after [30])                                                                     |

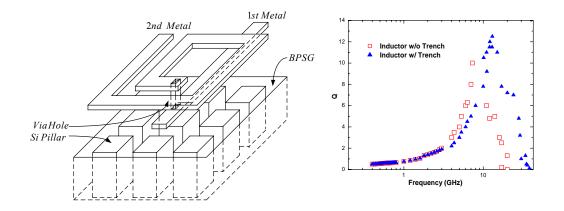

| Figure 20(a) Inductor with substrate removed by a deep trench technology and (b) Q factors of            |

| conventional and trenched inductors (after [39])                                                         |

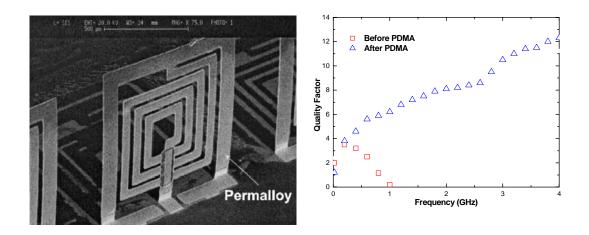

| Figure 21(a) Topology of the horizontal inductor based on the PDMA process and (b) Q factors of          |

| conventional and horizontal inductors (after [43])                                                       |

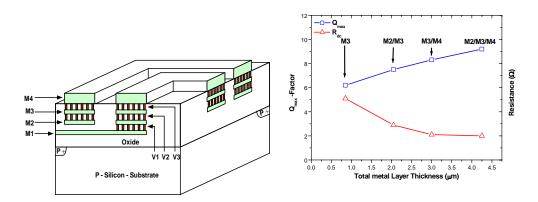

| Figure 22(a) Inductor with multiple metal layers and vertical shunt and (b) maximum Q factors and      |

|--------------------------------------------------------------------------------------------------------|

| resistances for the inductor having different numbers of vertical shunt (after [44])                   |

| Figure 23(a) Inductor with metal line split into shunt current paths and (b) Q factors of horizontally |

| shunt inductor with one, two, and three splits in the metal line (after [45])                          |

| Figure 24(a) Topology of a tapered inductor and (b) Q factors of a tapered inductor and three          |

| non-tapered inductors (after [47])                                                                     |

| Figure 25(a) Stacked inductor with six metal layers and (b) Q factor and inductance of the stacked     |

| inductor (after [48])                                                                                  |

| Figure 26(a) Structure of the miniature 3-D inductor, (b) capacitances of typical stacked and 3-D      |

| inductors, and (c) Q factors of typical stacked and 3-D inductors (after [49])                         |

| Figure 27 Spiral pattern of (a) non-symmetrical inductor and (b) symmetrical inductor                  |

| Figure 28 Comparison of (a) Q factor [50], (b) self-resonant frequency [27], and (c) capacitance       |

| [27] of non-symmetrical and symmetrical inductors                                                      |

| Figure 29(a) Structure of the dual-layer symmetrical inductor and (b) Q factors of single and          |

| dual-layer symmetrical inductors (after [51])                                                          |

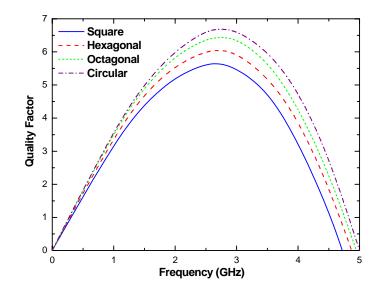

| Figure 30 Q factors of different shaped inductors with a fixed inductance of 5 nH (after [15]). 41     |

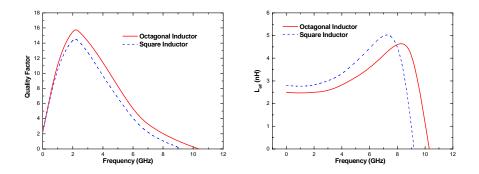

| Figure 31(a) Q factor and (b) inductance of octagonal and square inductors having the same             |

| inner-diameter of 100 $\mu$ m, number of turns of 3.5, and line width of 6 $\mu$ m (after [52]) 42     |

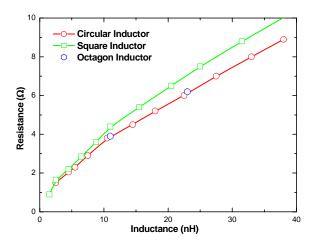

| Figure 32 Resistance comparison on square, octagon and circular inductors                              |

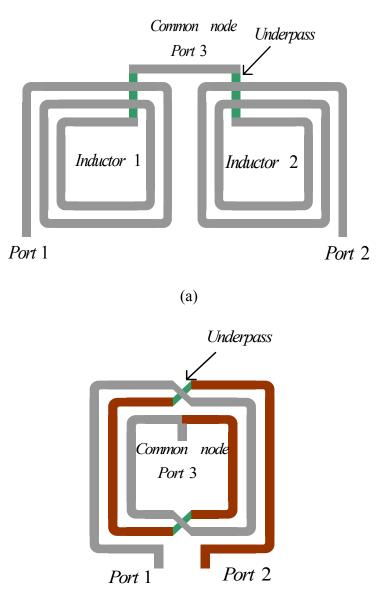

| Figure 33 Schematic of (a) asymmetrical inductor and (b) symmetrical inductor with a square            |

| pattern for differential driven applications                                                           |

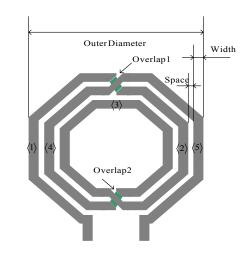

| Figure 34 (a) Schematic of an octagon symmetrical inductor with 3 turns, (b) overall equivalent      |

|------------------------------------------------------------------------------------------------------|

| circuit for the inductor including segmental and overlap components, and (c) equivalent              |

| circuit for the segment in (b)                                                                       |

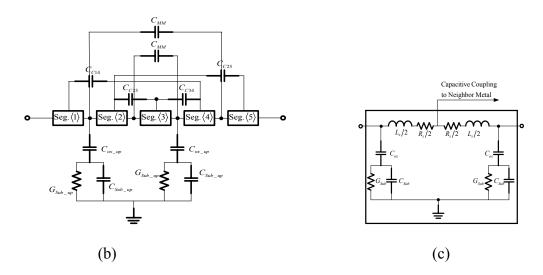

| Figure 35 Current density contours in the three metal lines at three different frequencies simulated |

| from an EM simulator                                                                                 |

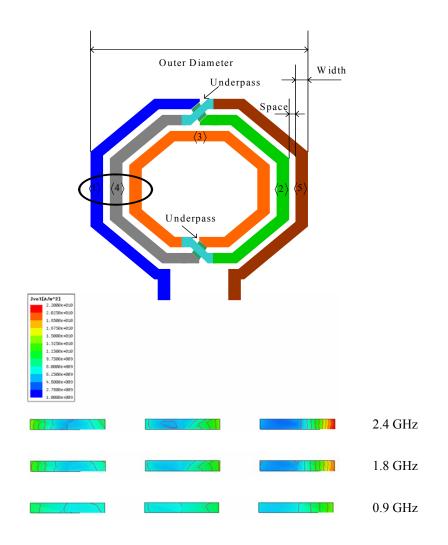

| Figure 36 Comparison of current density distributions in the three metal lines calculated from the   |

| present model (lines) and obtained from EM simulations (symbols)                                     |

| Figure 37 Different possible filament alignments for the mutual inductance calculations 55           |

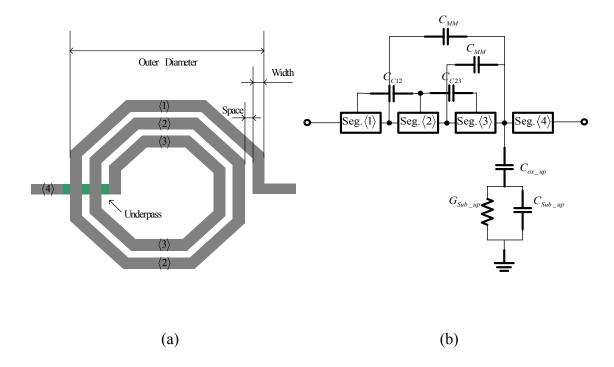

| Figure 38 Cross-section showing the different thicknesses associated with the overlap parasitics     |

| modeling                                                                                             |

| Figure 39 (a) Schematic of an octagon, 2.5-turn asymmetrical inductor and (b) overall equivalent     |

| circuit for the inductor including segment, capacitive coupling, and overlap components 63           |

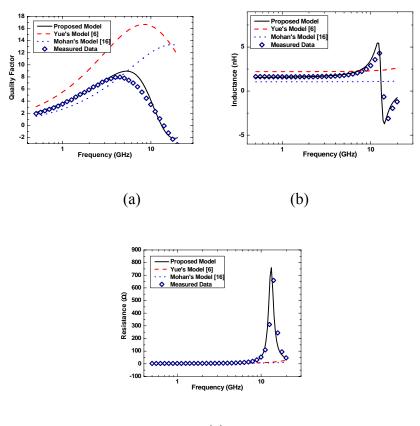

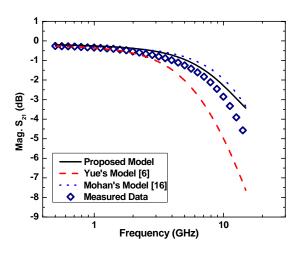

| Figure 40 Comparisons of the present model, existing models, and measurements of (a) quality         |

| factor (b) inductance and (c) series resistance for the 3-turn symmetrical inductor                  |

| Figure 41 Comparisons of the present model, existing models, and measurements of (a) magnitude       |

| and (b) phase of $S_{21}$ for the 3-turn symmetrical inductor                                        |

| Figure 42 Comparisons of the present model and measurements of (a) quality factor (b) inductance     |

| and (c) series resistance for the 5-turn symmetrical inductor                                        |

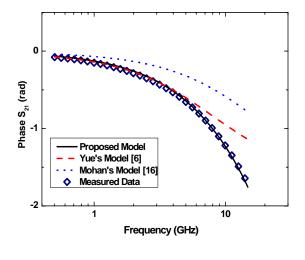

| Figure 43 Comparisons of the present model, existing models, and measurements of (a) quality         |

| factor (b) inductance and (c) series resistance for the 2.5-turn asymmetrical inductor 69            |

| Figure 44 Comparisons of the present model, existing models, and measurements of (a) magnitude       |

| and (b) phase of $S_{21}$ for the 2.5-turn asymmetrical inductor                                     |

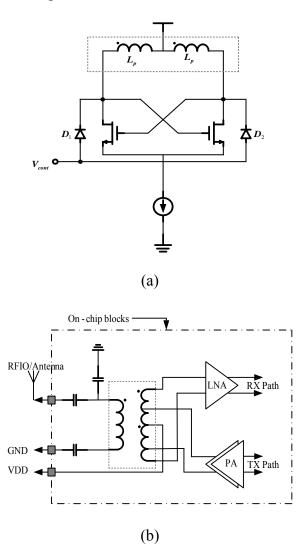

| Figure 45 Examples of differential inductor and transformer applications: (a) voltage control        |

|------------------------------------------------------------------------------------------------------|

| oscillator (VCO) with a differential inductor, (b) RF front-end circuit with a transformer for       |

| Bluetooth applications                                                                               |

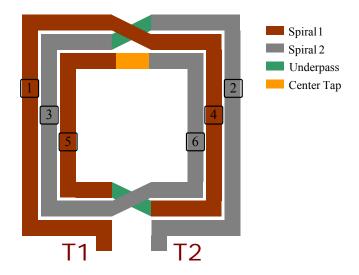

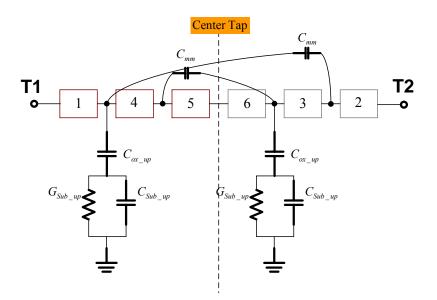

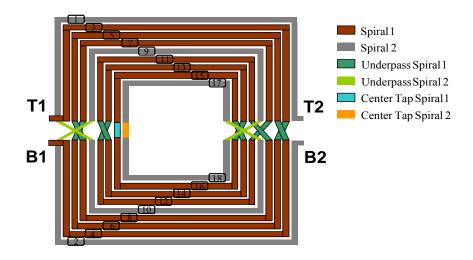

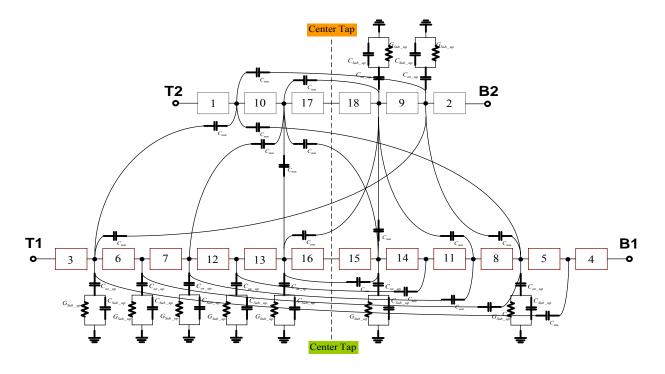

| Figure 46 Pattern of a three-turn square differential inductor, with six metal-line segments divided |

| by the underpasses and center tap77                                                                  |

| Figure 47 Equivalent circuit of each segment in Figure 46                                            |

| Figure 48 Complete equivalent circuit for the differential inductor in                               |

| Figure 49 Pattern of a nine-turn square transformer/balun                                            |

| Figure 50 Complete equivalent circuit for the transformer/balun in Figure 49                         |

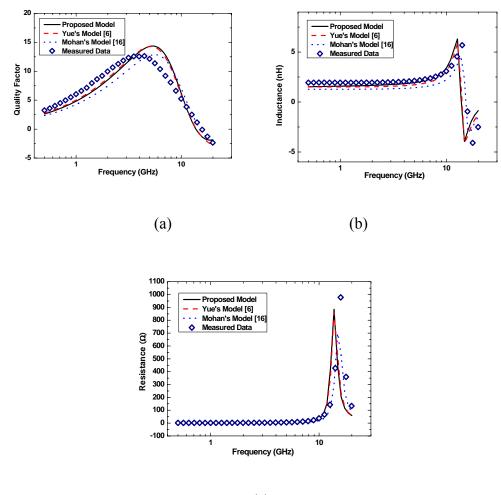

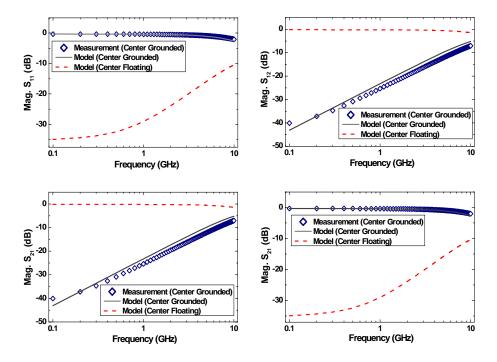

| Figure 51 Magnitude of two-port S-parameters for the inductor shown in                               |

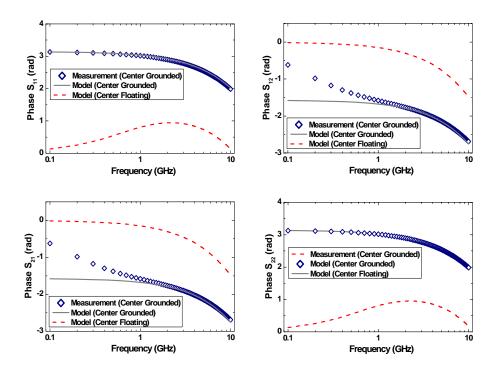

| Figure 52 Phase of two-port S-parameters for the inductor shown in Figure 46                         |

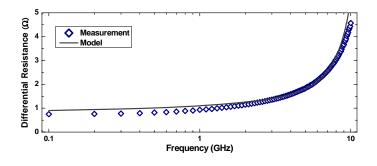

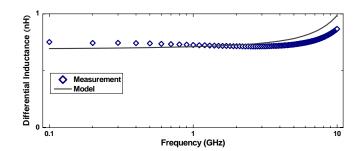

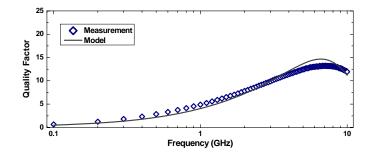

| Figure 53 (a) Inductance, (b) resistance, and (c) quality factor for the inductor shown in Figure 46 |

|                                                                                                      |

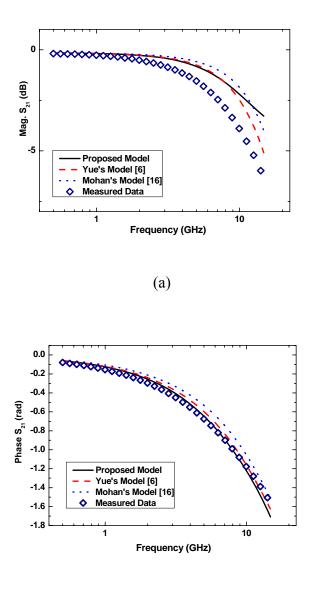

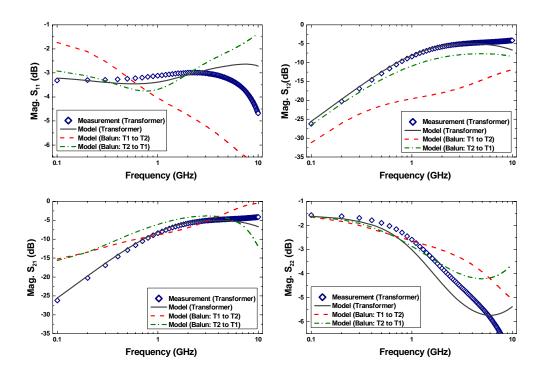

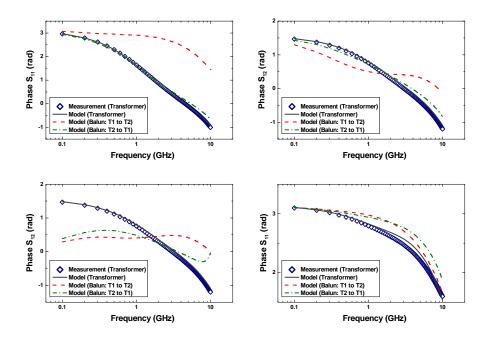

| Figure 54 Magnitude of two-port S-parameters for the transformer/balun shown in Figure 49 84         |

| Figure 55 Phase of two-port S-parameters for the transformer/balun shown in Figure 49 85             |

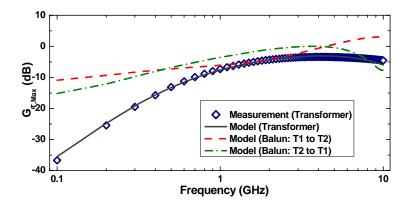

| Figure 56 Best available (with both ports matched) transducer gain (insertion loss) for the          |

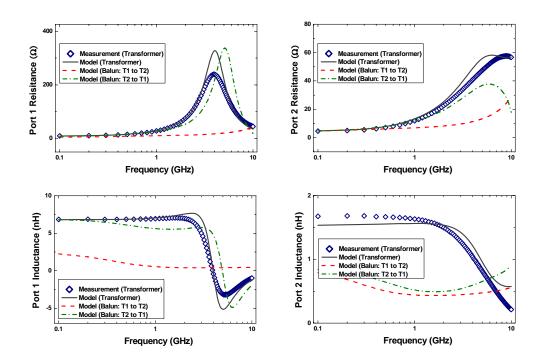

| transformer/balun shown in Figure 49                                                                 |

| Figure 57 Resistance and inductance of the transformer with both ports matched                       |

| Figure 58 (a) An RF oscillator circuit, and (b) simulated phase noises of the circuit with the       |

| inductor's Q factor increasing from 10 to 30                                                         |

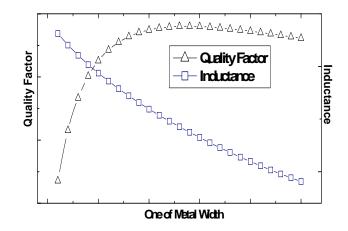

| Figure 59 Typical variation of inductance and quality factor with sweep of metal line width 92       |

| Figure 60 Optimization flow graph                                                                    |

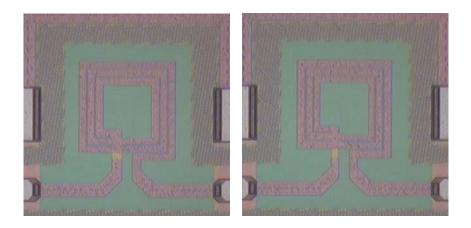

| Figure 61 Layout topology of (a) Inductor 1 (b) Inductor 2                                           |

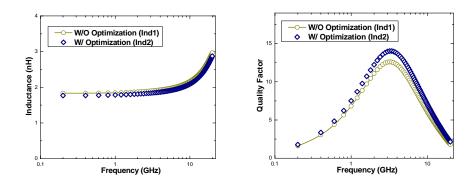

| Figure 62 (a) The inductance and (b) quality factor of Inductors 1 and 2 | 96 |

|--------------------------------------------------------------------------|----|

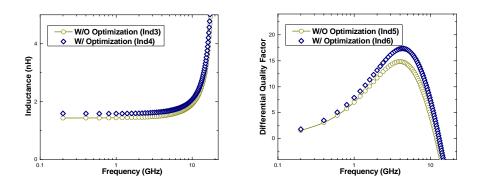

| Figure 63 (a) The inductance (b) and quality factor of Inductors 3 and 4 | 97 |

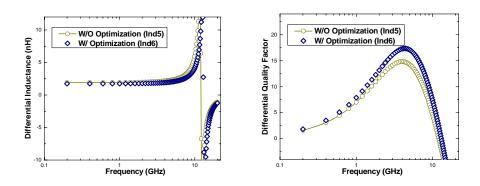

| Figure 64 (a) The inductance and (b) quality factor of Inductors 5 and 6 | 97 |

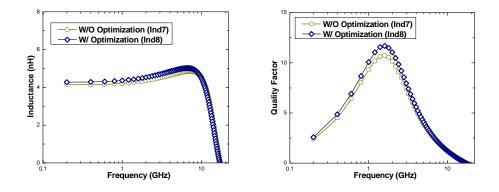

| Figure 65 (a) The inductance and (b) quality factor of Inductors 7 and 8 | 98 |

# LIST OF TABLES

| Table 1 Values of Fitting Parameters for the Three Inductors Considered | 68 |

|-------------------------------------------------------------------------|----|

| Table 2 Parameters for the inductors considered and fabricated          | 82 |

| Table 3 Layouts of optimized and non-optimized inductors                | 95 |

# LIST OF ACRONYMS/ABBREVIATIONS

| EM   | Electro-magnetic                 |

|------|----------------------------------|

| IC   | Integrated Circuit               |

| MEMS | Micro Electron-Mechanical System |

| Q    | Quality Factor                   |

| RF   | Radio Frequency                  |

| VCO  | voltage controlled oscillator    |

## **CHAPTER ONE: INTRODUCTION**

#### **1.1 Motivation**

#### **1.1.1 Need for Inductors**

In contrast with digital circuits which use mainly active devices, on-chip passive components are necessary and imperative adjuncts to most RF electronics [1-2]. These components, which include inductors, capacitors, varactors, and resistors, have been known as performance as well as cost limiting elements of radio frequency (RF) integrated circuits. While all of these components can be realized using MOS technology, their specific designs necessitate special consideration due to the requirement of high quality factor Q at relatively high frequencies. Inductors in particular are critical components in oscillators and other tuned circuits. For low-frequency applications, passive devices can be connected externally, but as the frequency increases, the characteristics of the passive devices would be overwhelmed by parasitic effect [3]. For instance, a voltage-controlled oscillator (VCO) of 10 MHz needs a tank inductance on the order of several µH, whereas at 10 GHz the inductance is around 1 nH. It's impossible to access such a small inductance externally, since the inductance associated with the package pin and bond wire can exceed 1 nH. As a result, on-chip passive components are commonly used in RF applications.

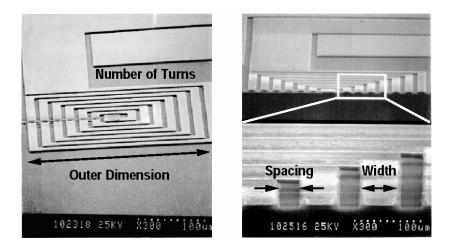

This chapter will focus on the on-chip inductors. Basically there are three types of on-chip inductors. The most widely used type is the planar spiral inductor, and a square shaped spiral inductor is shown in Figure 1 [4]. Although a circular shaped inductor may be more efficient and yield better performance, the shape of inductor is often limited to the availability of fabrication

processes. Most processes restrict all spiral angles to be 90°, and a rectangular/square pattern (hereafter called square pattern) is a nature choice, but a polygon spiral inductor can serve as a compromise between the square and circular shaped inductors. Structural parameters such as the outer dimension, number of turns, the distance between the centers of lines (or pitch), and substrate property are all important factors in determining the performance of on-chip inductors.

Figure 1 Topology and cross section of a typical on-chip square shaped spiral inductor. (after [4]).

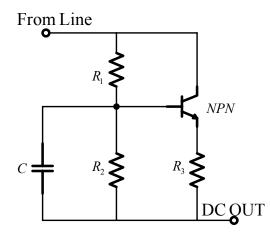

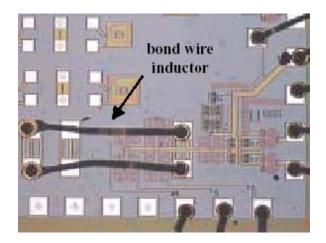

Besides the spiral inductor, two other kinds of on-chip inductors have been used. Gyrator, or active inductor, utilizes active components (i.e., transistors) to transform the impedance of a capacitor to inductance [5]. Figure 2 shows the basic gyrator circuit. The active device and capacitor required in the gyrator can be easily fabricated and occupy minimal space, but they consume relatively large power and introduce additional noise. The third on-chip inductor type is constructed with the bond wire [6], as shown in Figure 3. It can offer a very high quality factor (30~60, typically), but

such an approach is likely to cause unwanted coupling to other devices and may not be sufficiently robust for some RF applications. Only spiral inductors are covered in this dissertation.

Figure 2 Equivalent circuit of a basic gyrator.

Figure 3 Schematic of a bond wire inductor (after [6]).

#### 1.1.2 The Effect of Inductor Quality Factor

One of most frequently mentioned figure of merit of the on-chip inductor is its Q (quality factor). It has be often questioned what is quality factor and how it relates with the performance of an inductor.

Although describing the roll of an inductor in a RF circuit is not the purpose of this dissertation, two example circuits below, with simulation results, explain the importance of Q factor. Figs. 4(a) shows a typical low-noise amplifier (LNA) with two active inductors and an ideal inductor with infinite inductance serving as RF choke (RFC). Figs. 4(b) and (c) show the simulated noise figure and current gain, respectively, for the LNA when the Q factors of the two inductors are assumed equal and changed from 5 to 25. Clearly, the RF performances of the LNA are degraded when the inductors' Q factor is reduced. Figure 5(a) shows an RF oscillator circuit having one inductor, and the simulation results given in Figure 5(b) indicate that the phase noise of the circuit is again degraded as the Q factor of the inductor is reduced.

Figure 4(a) A typical low-noise amplifier, (b) simulated noise figures, and (c) simulated small-signal current gains. In the simulations, the two active inductors were assumed having the same Q factors and the Q factors were increased from 5 to 25.

(b)

Figure 5(a) An RF oscillator circuit, and (b) simulated phase noises of the circuit with the inductor's Q factor increasing from 10 to 30.

#### **1.2 Description of Problems**

As studied in the previous section, inductance quality factor is a limiting factor of RF front end circuits. High performance on-chip magnetic device design method is highly demanded for both academic study and industrial development.

This dissertation is constructed with six chapters. The first chapter introduces the application of inductor and describes the aim of this dissertation. The second chapter reviews significant amount of most updated literatures related to the topic, and offers a clear clue about on-chip inductor physics and modeling. Chapter three discovers the current crowding phenomena from a new angle of view, and proposes a new model structure to address this discovery. Chapter four further fulfill the proposed model in differential inductor and balun, and chapter five proposed an algorithm in optimizing inductor layout without any additional technology modification. Silicon data is measured and presented in the related chapters. At last, chapter six concludes the dissertation, and lead to the future work.

## **CHAPTER TWO: LITERATURE REVIEW**

#### 2.1 Modeling Concept and Design Guideline

Traditionally, spiral inductors are made in square shape due to its ease of design and support from drawing tools [7]. From the performance point of view, however, the most optimum pattern is a circular spiral because it suffers less resistive and capacitive losses. But the circular inductor is not widely used because only a few commercial layout tools support such a pattern. Hexagonal and octagonal structures are good alternatives, as they resemble closely to the circular structure and are easier to construct and supported by most computer-aided design tools. It has been reported that the series resistance of the octagonal and circular shaped inductors is 10% smaller than that of a square shaped spiral inductor with the same inductance value [8].

In 1990, Nguyen and Meyer [9] first developed a planar inductor on silicon using the interconnect technology, and they proposed a simple  $\pi$  model to describe the inductor's behavior (see Figure 6(a)), which can be considered as a section of the ladder model for interconnects. An improved model, shown in Figure 4(b), was later developed by Ashby et al. [10]. This model accounts for more physical mechanisms taking place in the inductor. However, the model parameters need to be extracted from empirical curve fitting rather than physical means. More recently, Yue and Wong [11] reported an inductor model similar to that in Figure 6(b), as shown in Figure 6(c), but with models parameters more relevant to inductor geometry and processing.

In the following subsections, we will consider the square shaped spiral inductor and use the model in Figure 6(c) as a benchmark to discuss the important issues associated with such a device,

including the series inductance (LS), resistances (RS and RSi), capacitances (CS, CSi, and COX), and quality factor and substrate loss. Note that these issues strongly correlate with the components in the equivalent circuit given in Figure 6(c) for modeling the on-chip inductor.

Figure 6 Lumped  $\pi$  models for spiral inductors developed by (a) Nguyen and Meyer [9]; (b) Ashby et al. [10]; and (c) Yue and Wong [11].

#### 2.1.1 Series Inductance

It is quite obvious that the knowledge of series inductance is critical to engineers who develop and utilize on-chip inductors for RF IC's. The inductance represents the magnetic energy stored in the device, although parasitic components may store energy as well. Numerical simulators computing the electromagnetic field distribution can be used to calculate the inductance, but our focus here is to determine such a parameter through analytical means, as the latter is less complicated and provides more physical insights.

In 1946, Grover derived formulas for the inductance of various inductor structures [12]. Greenhouse later applied the formulas to calculate the inductance of a square shaped inductor [13]. He divided the inductor into straight-line segments, and calculated the inductance by summing the self inductance of the individual segment and mutual inductance between any two parallel segments. The model has the form of

$$L_{S} = L_{0} + M_{+} - M_{-} \tag{1}$$

where LS is the total series inductance, L0 is the sum of the self inductance of all the straight segments, M+ is the sum of the positive mutual inductances and M- is the sum of the negative mutual inductances. Self inductance L'0 of a particular segment can be expressed as

$$L'_{0} = 2l \left( \ln \frac{2l}{w+t} + 0.5 + \frac{w+t}{3l} \right)$$

(2)

L'0 is the inductance in nH, l is the length of a segment in cm, w is the width of a segment in cm, and t is the metal thickness in cm. The mutual inductance between any two parallel wires can be calculated using

$$M = 2lQ' \tag{3}$$

where M is the mutual inductance in nH and Q' is the mutual inductance parameter

$$Q' = \ln\left[\frac{l}{GMD} + \sqrt{1 + \left(\frac{l}{GMD}\right)^2}\right] - \sqrt{1 + \left(\frac{l}{GMD}\right)^2} + \frac{l}{GMD}$$

(4)

GMD denotes the geometrical mean distance between the two wires. When two parallel wires are of the same width, GMD is reduced to

$$\ln GMD = \ln d - \frac{w^2}{12d^2} - \frac{w^4}{60d^4} - \frac{w^6}{168d^6} - \frac{w^8}{360d^8} - \frac{w^{10}}{660d^{10}} - \dots$$

(5)

d is the pitch of the two wires. Note that the mutual inductance between two segments that are perpendicular to each other is neglected. As the number of segments increases, the calculation complexity is increased notably because it is proportional to (number of segments)<sup>2</sup>. Another drawback of the model is its limitation to only square shaped inductors.

The above model could be simplified using an averaged distance for all segments rather than considering the segments individually [14]. Based on this approach, the self and mutual inductances are calculated directly as

$$L_{0} = \frac{\mu_{0}}{4\pi} l \left( \ln \frac{l_{T}}{n(w+l)} - 0.2 \right)$$

(6)

$$M_{-} = \frac{\mu_{0}}{4\pi} l_{T} \frac{n}{214}$$

(7)

$$M_{+} = \frac{\mu_{0}}{4\pi} l_{T} \left( n - 1 \right) \left[ \ln \left( \sqrt{1 + \left( \frac{l_{T}}{4nd} \right)^{2}} + \frac{l_{T}}{4nd} \right) - \sqrt{1 + \left( \frac{4nd}{l_{T}} \right)^{2}} + \frac{4nd}{l_{T}} \right]$$

(8)

where  $\mu_0$  is the permeability of vacuum,  $l_T$  is the total inductor length, n is the number of turns, and d' is the averaged distance of all segments:

$$d' = \left(w + s\right) \left(\sum_{i=1}^{(n-i)>0} i(n-i) / \sum_{i=1}^{(n-i)>0} (n-i)\right)$$

(9)

Mohan developed another method which further simplifies the calculations based on the current sheet concept [15]. His method serves as an adequate approximation for geometries where the conductor thickness is dwarfed by the length and width, and has the advantage of easily extendable to other geometries (i.e., octagonal and circular).

The methods mentioned above offer various solutions to estimate the inductance of a square shaped inductor. Some empirical techniques based on curve fitting have also been reported in [16]-[18], however models derived in this way cannot be scaled to reflect changes in the inductor's layout or fabrication technology.

#### 2.1.2 Resistances

Series resistance  $R_S$  (see Figure 6(c)) arises from the metal resistivity in the inductor and is closely related to the quality factor. As such, the series resistance is a key issue for inductor modeling. When the inductor operates at high frequencies, the metal line suffers from the skin and proximity effects, and  $R_S$  becomes a function of frequency [19]. As a first-order approximation, the current density decays exponentially away from the metal-SiO<sub>2</sub> interface, and  $R_S$  can be expressed as [11]:

$$R_{s} = \frac{\rho \cdot l_{T}}{w \cdot t_{eff}} \tag{10}$$

Where  $\rho$  is the resistivity of the wire, and  $t_{eff}$  is given by

$$t_{eff} = \delta \cdot \left(1 - e^{-t/\delta}\right) \tag{11}$$

t is the physical thickness of the wire, and  $\delta$  is the skin depth which is a function of the frequency:

$$\delta = \sqrt{\frac{\rho}{\pi\mu f}} \tag{12}$$

where  $\mu$  is the permeability in H/m and f is the frequency in Hz.

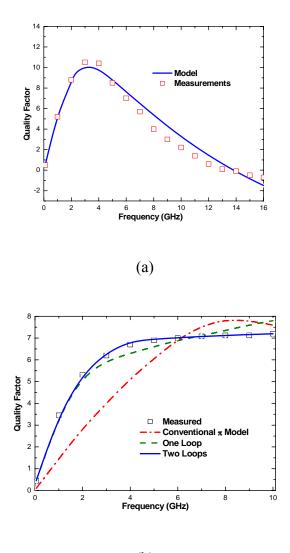

The most severe drawback of a frequency-dependent component, such as  $R_S$ , in a model is that it cannot be directly implemented in a time domain simulator, such as Cadence Spectre. Researchers have proposed to use frequency-independent components to model frequency-dependent resistance [19]-[25]. Ooi et al. [21] replaced  $R_S$  with a network of 2 R's and 1 L, where R and L are frequency-independent components, in the inductor equivalent circuit, as shown in the dashed line box in Figure 7(a). The total equivalent resistance  $R_{total}$  of the box is

$$R_{total} = R_0 \left[ 1 + \frac{\omega^2 \left( 0.035 \,\mathrm{w}^4 t^2 \sigma^2 \,\mu_0^2 \right)}{P^2} \sum_{n=1}^N \left( \frac{n-M}{N-M} \right)^2 \right]$$

(13)

Figure 7 (a) Model with improved series resistance (dashed line box) developed by Ooi et al. and (b) resistances measured and simulated for two different inductors (after [21]).

where  $R_{\theta}$  is the steady-state series resistance,  $\omega$  is the radian frequency, *P* is the turn pitch, *t* is the inductor thickness, *w* is the inductor width,  $\sigma$  is the conductivity, *N* is the total number of turns, and *M* is the turn number where the field falls to zero. This expression coincides with the approach based on the square-law relationship proposed in [22]. Figure 7(b) compares the measured and simulated series resistances of two different inductors. Another approach [23] used an R-L ladder to model the frequency-dependant resistor, which gives better flexibility and accuracy. Figs. 8(a) and (b) show the equivalent circuit of R-L ladder model and the series resistance results, respectively. Melendy et al. [24] used a series of R-L loops to represent the effect of series resistance, see Figs. 9(a) and (b). Another method is to average the different parameter values associated with R over the frequency [25].

Figure 8(a) Model with improved series resistance (dashed line box) developed by Rotella et al. and (b) resistances measured and simulated for two different inductors (after [23]).

Coupling resistance  $R_{Si}$  associated with the Si substrate (see Figure 6(c)) also degrades the inductor performance. A simple model to describe the substrate resistance is given by [11]

$$R_{Si} = \frac{2}{l \cdot \mathbf{w} \cdot G_{sub}} \tag{14}$$

where l is total length of all line segments,  $G_{sub}$  is the conductance per unit area of the substrate.

Figure 9 (a) Model with improved series resistance (dashed line box) developed by Melendy et al. and (b) resistances measured and simulated from the conventional model and improved model with one and two R/L loops in the dashed line box (after [24]).

#### 2.1.3 Capacitances

There are basically three types of capacitances in an on-chip inductor: the series capacitance  $C_S$  between metal lines, the oxide capacitance  $C_{OX}$  associated with the oxide layer, and the coupling capacitance  $C_{Si}$  associated with the Si substrate. Traditionally, they are modeled using the parallel-plate capacitance concept [11]:

$$C_s = n \cdot w^2 \cdot \frac{\varepsilon_{ox}}{t_{oxM1-M2}}$$

(15)

$$C_{ox} = \frac{1}{2} \cdot l_T \cdot \mathbf{w} \cdot \frac{\varepsilon_{ox}}{t_{ox}}$$

(16)

$$C_{Si} = \frac{1}{2} \cdot l_T \cdot \mathbf{w} \cdot C_{sub} \tag{17}$$

where *n* is the number of overlaps, *w* is the spiral line width,  $C_{sub}$  is the capacitance of the substrate,  $t_{ox}$  is the oxide thickness underneath the metal, and  $t_{oxM1-M2}$  is the oxide thickness between the spiral. An improved method [26], which evaluates the voltage and energy stored in each turn, leads to the equivalent capacitances of  $C_p$  and  $C_{sub}$ , as shown in Figure 10. Compared to the model in Figure 6(c),  $C_p$  and  $C_{sub}$  in this model are equivalent to  $C_s$  and the combination of  $C_{ox}$  and  $C_{Si}$ , respectively,

$$C_{p} = \sum_{k=1}^{n-1} \frac{1}{4} C_{mm} l_{k} [d(k+1) - d(k-1)]^{2}$$

(18)

$$C_{sub} = \sum_{k=1}^{n} \frac{1}{4} C_{ms} A_k [2 - d(k-1) - d(k)]^2$$

(19)

$$d(k) = h_1 + h_2 + \dots + h_{k-1} + h_k$$

(20)

$$h_k = \left(l_k / l_T\right) \tag{21}$$

Figure 10 Equivalent circuit of spiral inductor developed by Wu et al.

#### [26].

where  $C_{ms}$  represents the capacitance per unit area between the  $m^{th}$  metal layer and the substrate,  $C_{mm}$  represents the capacitance per unit length between adjacent metal tracks,  $A_k$  is the track area of  $k^{th}$  turn and  $l_k$  is the length of k<sup>th</sup> turn. The model also implies that  $C_s$  is a function of the index difference of each adjacent segment pair. This means that the larger the index difference between the two adjacent lines, the higher the capacitance [27]. This concept can be used to improve the inductor structure to be discussed in Section III.

#### 2.1.4 Q Factor and Substrate Loss

The quality factor Q is an extremely important figure of merit for the inductor at high frequencies. For an inductor, only the energy stored in the magnetic field is of interest, and the quality factor is defined as [28]

$$Q = 2\pi \cdot \left(\frac{Peak\ Magnetic\ Energy - Peak\ Electric\ Energy}{Energy\ Loss\ in\ One\ Oscillation\ Cycle}\right)$$

(22)

Basically, it describes how good an inductor can work as an energy-storage element. In the ideal case, inductance is pure energy-storage element (Q approaches infinity), while in reality parasitic resistance and capacitance reduce Q. This is because the parasitic resistance consumes stored energy, and the parasitic capacitance reduces inductivity (the inductor can even become capacitive at high frequencies). Self-resonant frequency  $f_{SR}$  marks the point where the inductor turns to capacitive and, obviously, the larger the parasitic capacitance, the lower the  $f_{SR}$ .

If the inductor has one terminal grounded, as in typical applications, then the equivalent circuit of the inductor can be reduced to that shown in Figure 11. From such a model, the quality factor Q of the inductor can be derived as [28]:

$$Q = \frac{\omega L_s}{R_s} \cdot \frac{R_p}{R_p + \left[ (\omega L_s / R_s)^2 + 1 \right] R_s} \cdot \left[ 1 - \frac{R_s^2 (C_s + C_p)}{L_s} - \omega^2 L_s (C_s + C_p) \right]$$

$$= \frac{\omega L_s}{R_s} \cdot \text{Substrate Loss Factor} \cdot \text{Self Resonance Factor}$$

(23)

Figure 11 Equivalent circuit of one terminal grounded inductor for modeling the Q factor.

where  $\omega$  is the radian frequency,  $L_S$  is the series inductance,  $R_S$  is the series resistance,  $R_P$  is the coupling resistance, and  $C_P$  is the coupling capacitance.  $R_P$  and  $C_P$  in Figure 11 are related to  $R_{Si}$ ,  $C_{Si}$ , and  $C_{OX}$  in the model in Figure 6(c) as

$$C_{p} = C_{ox} \cdot \frac{1 + \omega^{2} (C_{ox} + C_{Si}) C_{Si} R_{Si}^{2}}{1 + \omega^{2} (C_{ox} + C_{Si})^{2} R_{Si}^{2}}$$

(25)

Note that Q increases with increasing  $L_S$  and with decreasing  $R_S$ . Moreover, it appears from (23) that Q should increase monotonically with the frequency. This is not the case, however, as the substrate loss becomes a dominant factor for Q at high frequencies. The last two terms on the right-hand side of (23) denote the substrate loss factor and self-resonant factor. On-chip inductors are normally built on a conductive Si substrate, and the substrate loss is due mainly to the capacitive and inductive coupling [7]. The capacitive coupling (represented by  $C_P$  in the model in Figure 11) from the metal layer to the substrate changes the substrate potential and induces the displacement current. The inductive coupling is formed due to time-varying magnetic fields

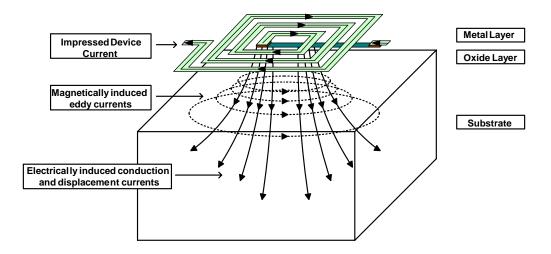

penetrating the substrate, and such a coupling induces the eddy current flow in the substrate. Both the displacement and eddy currents give rise to the substrate loss and thereby degrade the inductor performance. Figure 12 illustrates schematically the eddy and displacement currents in the substrate induced magnetically and electrically, respectively, by the current flow in the inductor spiral.

Figure 12 Eddy and displacement currents in the substrate induced by the

current flow in inductor spiral.

An important conclusion can be drawn from (23), that is when  $R_P$  approaches infinity, the substrate loss factor approaches unity. Since  $R_P$  approaches infinity when  $R_{Si}$  goes to zero or infinity, Q can be improved by making the silicon substrate either a short or an open [28].

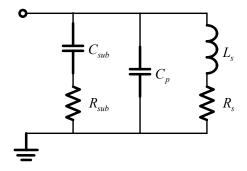

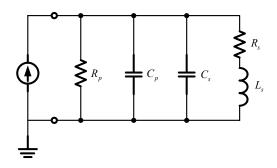

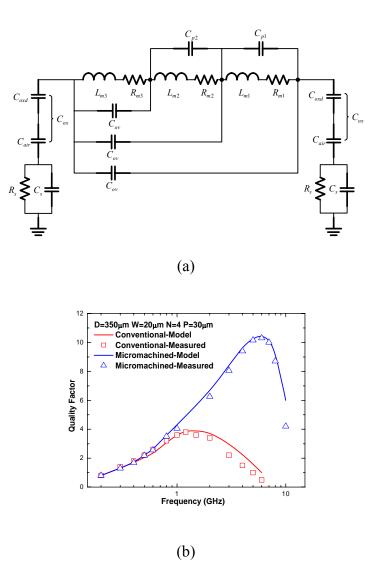

### 2.1.5 Modified $\pi$ Models

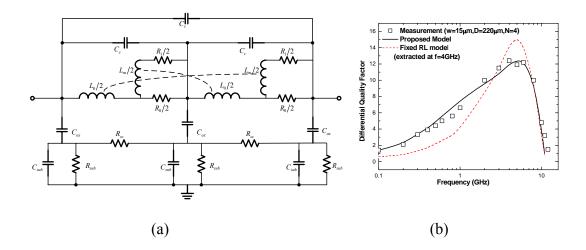

Some studies have been conducted to improve the accuracy of the simple lumped models shown in Figure 6. Gil and Shin [29] modified the simple  $\pi$  model by adding the horizontally coupled substrate resistor and capacitor, and the equivalent circuit and results of Q factor are given in Figures. 13(a) and (b). Cao et al. [19] proposed a double  $\pi$  model to account for the frequency-dependant resistance and inductance, in which the frequency-independent resistance components follow the square-law relationship suggested in [21]-[22] and the frequency-independent inductance components are derived based on mutual inductances and calculated from empirical equations. The equivalent circuit and model results are given in Figures. 14(a) and (b). Lakdawala et al. [30], on the other hand, used an RLC laddered network to describe the frequency-dependent resistance and inductance, as shown in Figure 15(a). The measured and calculated Q factors of conventional and micromachined inductors are given in Figure 15(b). The models in Figures. 8(a) and Figure 9(a) could also yield good predictions for *Q*, and the results are shown in Figures. 16(a) and (b), respectively.

Figure 13(a) Improved inductor model with horizontally coupled resistance and capacitance ( $R_{sub}$  and  $C_{sub}$ ) and (b) Q factors measured and simulated with and without  $R_{sub}$  and  $C_{sub}$  (after [29]).

Figure 14(a) Improved double  $\pi$  model to more accurately account for the frequency-dependent series resistance and inductance and (b) Q factors measured and simulated from the conventional and improved models

(after [19]).

Figure 15(a) Modified  $\pi$  model with RLC laddered network and (b) Q factors measured and calculated from the modified model (after [30]).

(b)

Figure 16(a) Quality factors measured and calculated from model in Figure 7(a); (b) Inductances and quality factors measured and calculated from model in Figure 8(a).

#### 2.2 Advanced Structures

The preceding section has addressed the design concept and modeling of a typical square shaped spiral inductor. The performance of such an inductor can be improved with the following advanced structures.

### 2.2.1 Structures to Reduce Substrate Loss

### (a) Ground Shield

As mentioned earlier, the substrate loss can be reduced with decreasing the substrate resistance  $R_{SI}$ . To achieve this, one can insert a metal or ploy-Si layer between the inductor and substrate, and connect this layer to the ground. This approach, called the ground shielding, reduces the effective distance between the spiral metal and ground and thereby reduces the substrate coupling resistance. Another purpose of the shield is that it can truncate the electric field in the substrate and thus reduce the noise. For a solid ground shield (SGS), however, the varying electromagnetic field in the inductor could induce the eddy current with the presence of ground plane, and the reflected image in the ground plane serves as a counteractive inductor [31]. Hence, it's necessary to pattern the shield to cut the eddy current loop [28], [32]. It has been found that poly-Si is a good material for the patterned ground shield (PGS). Chen et al. [33] reported the use of an n<sup>+</sup>-diffusion Si patterned ground shield to improve the quality factor. Since the substrate current mainly concentrates at the Si-SiO<sub>2</sub> surface due to the proximity effect, the n<sup>+</sup>-diffusion Si PGS can effectively break the current loop and thus eliminate the eddy current effect [34]. Figs. 17(a) and

(b) show a typical PGS and the results of quality factor Q with SGS and PGS. Clearly, the presence of PGS improves Q considerably.

Figure 17(a) Schematic of patterned ground shield (PGS) and (b) quality factors of solid ground shield (SGS), PGS, and no ground shield (NGS) (after [28]).

The most significant drawback of ground shielding is the fact that it reduces the distance between inductor and ground and thereby introduces additional capacitance. This effect may sometimes adversely decrease the quality factor of ground-shielding inductors [35].

## (b) Substrate Removal

Another way to enhance Q is to increase the substrate resistance. In order to elevate  $R_{Si}$  to approaching infinity, one idea is to use insulator as substrate. Quartz or glass shows better Q and higher self-resonant frequency than Si [35]. For Si technology, however, it is not possible to use a high resistive substrate as an effective RF ground, and via contacts through the chip to define RF grounds on both the chip front side and back side is usually not available. In other words, for CMOS-based on-chip inductors, we cannot avoid using a low resistive Si substrate. Nonetheless, instead of building the whole circuit on a low resistive substrate, we can make a region with high resistivity for placing the inductor [36]. This can be accomplished by using the proton implantation, and Chan et al. [36] achieved a 7% higher self-resonant frequency and 61% higher *Q* through this approach.

Researchers have come up with other novel ideas to keep the inductor away from substrate so that substrate coupling and loss can be greatly reduced. Using an advanced micromachinary process, an inductor can be built above the silicon surface [30], [37]-[38], as shown in Figs. 18 and 19, or the silicon underneath the inductor can be removed using the deep-trench technology [39], as shown in Figure 20.

Figure 18(a) Topology of the suspended inductor and (b) comparison of inductances and Q factors of conventional and suspended inductors (after [37]).

Figure 19(a) Topology of the micromachined inductor and (b) Q factors of such an inductor with two different diameters (after [30]).

# (c) Horizontal Inductors

An alternative way to reduce magnetic field coupling to substrate is to have the magnetic field parallel to the substrate. To this end, research works have been done to fabricate horizontal inductors with multilayer of interconnects [40]-[41]. Using this layout, the magnetic field is parallel to the substrate surface and the magnetic coupling to the substrate is minimal. This structure nevertheless gives rise to an increased in the coupling capacitance. Since a large metal is needed for the bottom layer of the horizontal inductor, the inductor-substrate capacitance increases tremendously if the inductor is on silicon. Again, researchers tried to use high resistive substrate [41], suspend the inductor in air [42], or even rectify the inductor with the so-called plastic deformation magnetic assembly (PDMA) [43]. Figs. 21(a) and (b) show the topology and performance of a horizontal inductor using the PDMA.

Figure 20(a) Inductor with substrate removed by a deep trench technology and (b) Q factors of conventional and trenched inductors (after [39]).

Figure 21(a) Topology of the horizontal inductor based on the PDMA process and (b) Q factors of conventional and horizontal inductors (after

[43]).

### 2.2.2 Structures to Reduce Series Resistance

Metal resistivity gives rise to the series resistance  $R_s$ , and it is always desired to reduce the resistance in order to improve the quality factor. One simple idea is to increase the line width. This method may work at low frequencies where the current density in a wire is uniform; however, as the frequency increases, the skin effect pushes the more current to the outer cross section of the metal wire and the so-called skin depth (i.e., the depth in which the current flows) is reduced with increasing frequency (see Eq. (12)). Thus, the skin effect increases the series resistance at high frequencies, and the approach of increasing the line width would not be effective. According to an earlier study, the larger the cross section, the lower the onset frequency at which the skin effect dominates the series resistance. Furthermore, a wider metal line would occupy more area, which increases the fabrication cost. Several possible solutions to this problem are given below.

## (a) Vertical Shunt

In this approach, the inductor is made of multiple metal layers and the neighboring metal layers are shunted through via arrays, so the effective thickness of the spiral inductor is increased, the skin effect is weakened, and the series resistance is reduced. A detailed study and comparison on the multilayer inductors are presented in [44]. The inductors are fabricated with multiple metal layers (M1 to M4), and these layers can be shunted through via arrays, as shown in Figure 22(a) for the case of shunting M2, M3 and M4. The results in Figure 22(b) show a reduced series resistance and thus an improved Q as the number of shunts is increased (i.e., the case of M3 has no vertical shunt). The performance of the inductor is therefore optimized with the increment of total metal thickness without occupying more area. One important aspect the inductor in Figure 22 did not address is

that the inductor may experience a lower self-resonant frequency with the utilization of lower metal layers. This is because 1) the reduction of metal-substrate distance could cause a significant increase in  $C_{ox}$ , and 2) the capacitance among the metal lines would also increase.

Figure 22(a) Inductor with multiple metal layers and vertical shunt and (b) maximum Q factors and resistances for the inductor having different numbers of vertical shunt (after [44]).

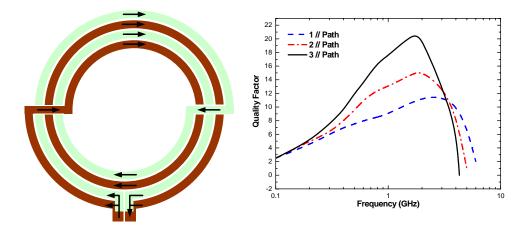

## (b) Horizontal Shunt

Instead of shunting vertically, the spiral inductor can be split into several shunting current paths, each with an identical resistance and inductance. This approach, called the horizontal shunt, can suppress the current crowding and increase the Q factor [45]. Figs. 23(a) and (b) show such an inductor and its Q factor, respectively. It is shown that for the same line width, the Q factor increases with increasing number of splits.

Figure 23(a) Inductor with metal line split into shunt current paths and (b) Q factors of horizontally shunt inductor with one, two, and three splits in the metal line (after [45]).

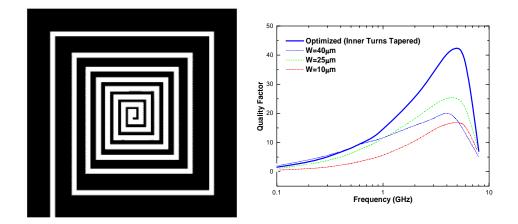

### (c) Line Width Optimization

For inductors fabricated with a constant line width, the influence of magnetically induced losses is much more significant in the inner turns of the spiral, where the magnetic field reaches its maximum. To avoid this effect, one method is to employ the so-called tapered inductor, in which the line width decreases toward the center of the spiral [46], as shown in Figure 24(a). A reduced series resistance can also be achieved from this approach. Detailed study was performed in [47] regarding the optimization of line width in order to enhance the RF performance. The frequencyand position-dependent optimum width  $W_{opt}$  is given by:

$$W_{opt,n} = \sqrt[3]{\frac{r_s(f)}{2 \cdot C \cdot g_n^2 \cdot f^2}}$$

(26)

where  $r_s(f)$  is the sheet resistance of the metal strip, f is the frequency, C is a fitting constant, and  $g_n$  is a geometric dependent parameter. As can be seen in Figure 24(b), the Q factor of a spiral inductor is much improved when the line width is not uniform and is optimized.

Figure 24(a) Topology of a tapered inductor and (b) Q factors of a tapered inductor and three non-tapered inductors (after [47]).

# 2.2.3 Structures to Increase Inductance

Since the quality factor is directly proportional to the series inductance, approaches to increase the inductance have also been suggested for on-chip inductor performance enhancement.

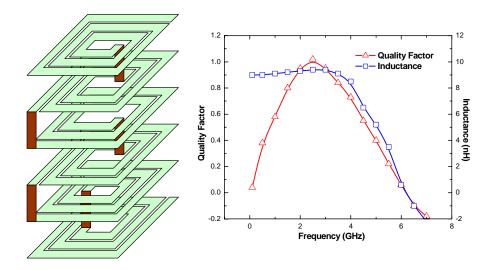

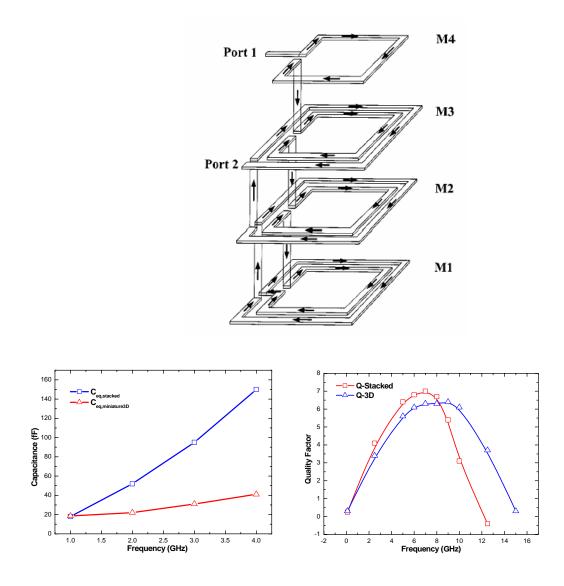

### (a) Stacked Inductor

A stacked inductor is a set of series inductors made from different metal layers, as illustrated in the schematic in Figure 25(a). This method maximizes the inductance per unit area. It has been reported that a 10 nH inductor can be achieved with an area of 22  $\mu$ m × 23  $\mu$ m, as opposed to several hundreds  $\mu$ m by several hundreds  $\mu$ m for regular inductors [48]. This is the main advantage

that this technology can offer. Shortcomings are relatively low Q factor and self-resonant frequency, due to the increased substrate capacitance and line to line coupling capacitance. The Q factor and inductance of such an inductor are illustrated in Figure 25(b).

Figure 25(a) Stacked inductor with six metal layers and (b) Q factor and inductance of the stacked inductor (after [48]).

## (b) Miniature 3-D Inductor

A high-performance stack-like inductor, called the miniature 3-D inductor, was proposed in [49]. Figure 26(a) shows such an inductor, which consists of at least two or more stacked inductors by series connections, and every stacked inductor has only one turn in every metal layer. The miniature inductor, while quite complicated, possesses a minimal coupling capacitance. This leads to a much higher self-resonant frequency and a wider frequency range for high quality factor. Comparisons of capacitances and Q factors obtained from this inductor and a typical stacked inductor are given in Figs. 26(b) and (c), respectively.

Figure 26(a) Structure of the miniature 3-D inductor, (b) capacitances of typical stacked and 3-D inductors, and (c) Q factors of typical stacked and 3-D inductors (after [49]).

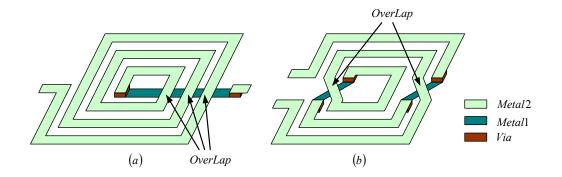

### **2.2.4 Symmetrical Inductor**

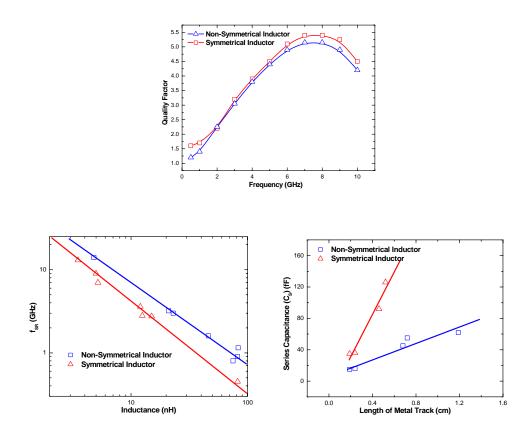

Traditionally, the winding of an inductor spiral starts from the outer turn to inner turn and then goes back out through an underpass. This is called the non-symmetrical inductor, as shown in Figure 27(a). An improved structure with a symmetrical winding, called the symmetrical inductor shown in Figure 27(b), will yield better performances [50]. This is because in the symmetrical inductor the geometric center of the symmetrical inductor is exactly the magnetic and electric center, which increases the mutual inductance and consequently the total inductance. Performances of the symmetrical and non-symmetrical inductors are illustrated in Figs. 28(a), (b) and (c). While the Q factor and series resistance of the symmetrical inductor are improved, the self-resonant frequency (i.e., frequency at which the inductance is zero) of such an inductor is reduced. This is due to an increased ac potential difference between the neighboring turns in the symmetrical inductor, a mechanism that increases the coupling capacitance and degrades the self-resonant frequency [26].

Figure 27 Spiral pattern of (a) non-symmetrical inductor and (b) symmetrical inductor.

Figure 28 Comparison of (a) Q factor [50], (b) self-resonant frequency [27], and (c) capacitance [27] of non-symmetrical and symmetrical inductors.

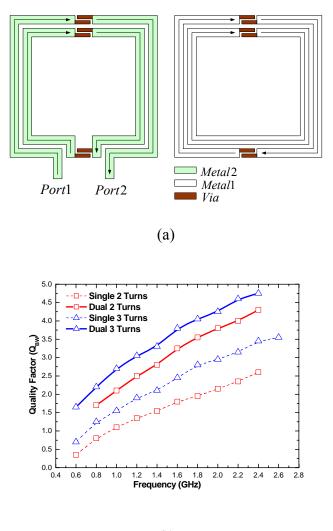

The symmetrical inductor can be further enhanced with a dual-layer structure, as shown in Figure 29(a) [51]. The results in Figure 29(b) suggest that this structure possesses a much higher Q factor over its single-layer counterpart.

(b)

Figure 29(a) Structure of the dual-layer symmetrical inductor and (b) Q factors of single and dual-layer symmetrical inductors (after [51]).

### 2.2.5 Alternative Patterns

The preceding discussions have focused mainly on square shaped spiral inductors. As mentioned earlier, while the circular shaped inductor yields better performance, such a pattern is more difficult to realize than its square counterpart. On the other hand, alternatives like the hexagonal and octagonal patterns are more feasible and good compromises. For these inductors, as the number of sides is increased, less metal length is needed to achieve the same number of turns. Thus series resistance is compressed and Q factor improved. On the other hand, the square shaped inductor is more area efficient. For example, for a square area on the wafer, square shape utilizes 100% of the area, whereas hexagonal, octagonal and circular shapes use 65%, 82.8% and 78.5%, respectively. As a result, square inductor can accommodate more metal line, thus yielding a larger inductance, within the same square area.

Selection of the pattern shape is a compromise between quality factor and area. Mohan [15] studied inductors with different shapes having a fixed inductance of 5 nH. As shown in Figure 30, the quality factor is improved with increasing number of sides (note that circular pattern can be considered as having infinite number of sides). The study further suggested that an octagonal spiral inductor suffers a 3~5% lower Q factor but achieves a 3~5% smaller effective chip area than the circular spiral inductor [15].

40

Figure 30 Q factors of different shaped inductors with a fixed inductance of 5 nH (after [15]).

The quality factor and inductance of square and octagonal shaped inductors having the same inner diameter are compared in Figs. 31(a) and (b) [52]. The square inductor possesses a higher peak inductance but a lower self-resonant frequency. This is because the longer metal line of square inductor induces a larger metal to substrate coupling capacitance, which reduces the inductance at high frequencies. For low frequencies, the inductor performance depends mainly on the length of the spiral wire, and the square pattern possesses a larger inductance in this region. Experiments of other research works also indicated an up to 10% resistance reduction of circular and octagonal inductor over the square inductor with the same inductance [8], as illustrated in Figure 32.

Figure 31(a) Q factor and (b) inductance of octagonal and square inductors having the same inner-diameter of 100  $\mu$ m, number of turns of 3.5, and line width of 6  $\mu$ m (after [52]).

Figure 32 Resistance comparison on square, octagon and circular

inductors

The dynamic growth in RF electronics has demanded and vitalized the need of high-performance on-chip passive components. One of these components, the on-chip spiral inductor, has been considered and reviewed in this chapter. Many aspects of the design and modeling of the on-chip inductor have been presented, and their impacts on RF performance addressed. It is demonstrated that while it is cost effective and technology reliable to fabricate such devices on Si substrate, the conductive nature of Si material gives rise to a large substrate loss and consequently relatively poor RF performance. The spiral pattern and geometry can also be optimized to enhance the quality factor, but these alternatives often come with trade-offs or compromises. This work should provide a useful and sufficient breath to researchers and engineers who are interested in the design and development of RF IC's involving passive components.

# **CHAPTER THREE: MODELING METHODOLOGY**

Recent growth in RF applications has increased the use of spiral inductors and thus demanded a more accurate model for such devices. In this dissertation, we focus on the model development of spiral inductors with symmetrical and asymmetrical terminals. Relevant and important physics such as the current crowding in metal line, frequency-dependent permittivity in oxide, and overlap parasitics are accounted for. Experimental data and results calculated from the existing inductor models are included in support of the model development.

### **3.1 Introduction**

Wireless communications is already part of our daily life. To reduce the cost of monolithic microwave integrated circuits (MMICs), passive devices are frequently integrated with active components on the same chip. Spiral inductors are particularly important and widely used in MMICs such as low-noise amplifiers, oscillators, and mixers [8].

Spiral inductors with asymmetrical and symmetrical terminals have been used in RF IC's, and their configurations for the widely used differential driven applications are shown in Figs. 1(a) and (b), respectively. For such applications, the symmetrical inductor yields better performance [53]. This is due to the presence of a shorter underpass metal line and smaller number of overlaps in the symmetrical inductor, which decrease the capacitance and consequently improve the quality factor

(Q factor) of the inductor [50]. In addition, the symmetrical inductor occupies a smaller chip area than its asymmetrical counterpart [53].

(b)

Figure 33 Schematic of (a) asymmetrical inductor and (b) symmetrical inductor with a square pattern for differential driven applications

Many spiral inductors models have been reported in the literature [15][9][11], and all these models were developed intended for asymmetrical inductors but nonetheless sometimes used for symmetrical inductors. To the best of our knowledge, an accurate and compact symmetrical inductor model is not yet available and urgently needed. Empirical technique based on curve fitting for symmetrical inductors has been reported in [16], but models derived this way cannot be scaled to reflect changes in the inductor's layout or fabrication technology and cannot be implemented into a circuit simulator. Commercial electromagnetic field solver may also be used to predict the inductor's performance accurately, but the computation time can be too extensive to be practical.

In this paper, a physics-based model applicable for both symmetrical and asymmetrical inductors will be developed. Model development and the proposed equivalent circuit for symmetrical inductors will first be given in Section II. This is followed by the model development of asymmetrical inductors in Section III. In Section IV, results obtained from the present model, existing models, and measurements are compared. Finally, conclusions are given in Section V.

## **3.2 Model Development of Symmetrical Inductor**

Our model development will first focus on symmetrical inductors. In addition, an octagonal spiral pattern will be considered, but the approach applies generally to other non-circular patterns. It has been suggested that the octagonal spiral provides a higher Q factor and lower series resistance than

the square pattern [8] and is more area efficient and easier realized than the circular spiral [15]. The consideration of the octagonal in fact makes the model more comprehensive than most existing models which consider only square or hexagonal patterns.

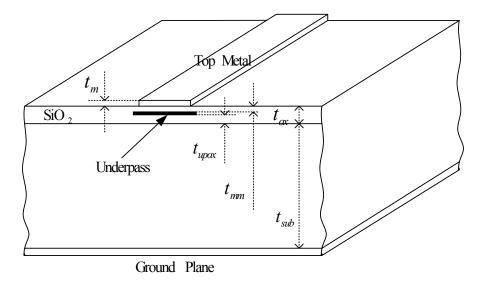

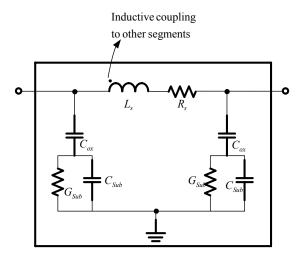

Figure 34 (a) Schematic of an octagon symmetrical inductor with 3 turns,(b) overall equivalent circuit for the inductor including segmental and overlap components, and (c) equivalent circuit for the segment in (b).

Figure 34(a) shows a symmetrical, octagon spiral inductor with 3 turns. For such an inductor, the metal track can be divided into 5 segments and 2 overlaps (see Figure 34(a)), and the improved equivalent circuit for the inductor is given in Figure 34(b). In Figure 34(b), each segment box is represented by a lumped model shown in Figure 34(c). In addition, coupling capacitances between the metal lines and parasitics associated with the overlaps need to be considered. These are accounted for with all the other components besides the segment boxes in Figure 34(b), where  $C_{C,ij}$ is the coupling capacitance between two particular metal lines i and j,  $C_{mm}$  represents the capacitance associated with the overlap,  $C_{ox up}$  and  $C_{sub up}$  model the capacitances associated with the oxide and substrate of the underpass metal, respectively, and  $G_{sub\_up}$  models the substrate conductance of the underpass metal. Note that there are two sets of the overlap parasitic components, and the subscripts 1 and 2 denote the components pertinent to overlaps 1 and 2, respectively. It is worth mentioning that the lumped equivalent circuit in Figure 34(c) is the sole framework used in the conventional modeling of spiral inductors. The improved version suggested in Figure 34(b) allows for the inclusion of the distributed nature of the spiral inductor and thus an increase in the model accuracy.

We want to point out that horizontal coupling in the substrate (horizontal coupling underneath the adjacent metal lines in the substrate) may affect the inductor performance, but such an effect is rarely included in the inductor compact modeling because of the complexity associated with its distributed nature. To the best of our knowledge, only the work by Gil and Shin [29] included the horizontal substrate coupling, but the model considered only the lump components for the horizontal substrate coupling, and all the model parameters were obtained from fitting schemes. To keep the present model compact and the parameters physics-based, this coupling effect will not

48

be considered. The eddy current is another mechanism for substrate loss. However, a recent work [19] has suggested that the loss due to eddy current is negligible in a relatively low conductive substrate with a resistivity larger than 10  $\Omega$ -cm. Because all the inductors considered in our work have a substrate resistivity of larger than 15  $\Omega$ -cm, such an effect will be neglected in this work.

### **3.2.1 Nonuniform Current Distribution in Metal Lines**

A difficult issue in modeling the spiral inductor is the fact that the current distribution in a metal line is not uniform and is a strong function of its location and operating frequency. Such a nonuniform current distribution is an important mechanism affecting the inductor performance. Traditionally, the current density in a metal line is considered to be governed by the skin and proximity effects [19]. It is more realistic, however, to consider the subject metal line lies in midst of electromagnetic field generated by all the other metal lines. According to the partial-element-equivalent-circuit (PEEC) simulation [54] and 3-D electromagnetic simulation [55], the current distribution in a metal line in general exhibits an exponential decay from the inner edge (side of metal line closer to the center of spiral) to the outer edge (side of metal line farther away from the center of spiral). Furthermore, this exponential-decay distribution is more prominent in the inner turns (i.e., segments 2, 3, and 4) and as the frequency is increased. Figure 35 shows the current density distributions in segments 1, 4, and 3 (circled in Figure 35) simulated from an EM simulator. The frequency and location dependencies of the current distribution in the metal lines are clearly illustrated.

49

We now introduce the concept of the effective line width  $W_{eff}$  in which the majority of the current density exists (the region where the first exponent of current density exists). Once  $W_{eff}$  is in place, then the nonuniform current distribution effect can be accounted for by replacing the physical line width in the model parameters with  $W_{eff}$ . The following expressions are proposed to describe the effective line width as a function of the frequency and the segment number:

$$w_{eff} = W_{0,i} \left( 1 - \exp\left(-\frac{w}{W_{0,i}}\right) \right)$$

(1)

$$W_{0,i} = c1 \cdot c2^{i-1} \sqrt{\frac{1}{f}}$$

(2)

where *w* is the physical width of metal line, *f* is frequency in Hz, *i* is turn index (i.e., for segments 1 and 5, *i*=1; segments 2 and 4, *i*=2; segments 3, *i*=3), and *c*1 and *c*2 are fitting parameters to make the inductance and resistance match with measurements. A systematic method to determine the values of *c*1 and *c*2 will be developed and discussed later.

Figure 35 Current density contours in the three metal lines at three different frequencies simulated from an EM simulator.

Figure 36 shows the normalized current distributions in segments 3, 2, and 5 (see Figure 36) obtained from an EM simulator and the effective line width model. The model results were calculated by first integrating the current distribution simulated from the EM simulator over the physical line width, normalizing it with the current integrated over the effective line width, and then using it as the peak value followed by an exponential decay function. The good agreement

demonstrates the soundness of using the effective line width for modeling the frequency- and location-dependent natures of the spiral inductors.

Figure 36 Comparison of current density distributions in the three metal lines calculated from the present model (lines) and obtained from EM

simulations (symbols).

#### **3.2.2 Modeling the Segment Box**

We will now first discuss the modeling of the components in the segment box (see Figure 34(c)), and later discuss the modeling of the overlap components in Figure 34(b). As shown in Figure 34(c), the model components in the segment box include the series inductance  $L_S$ , series resistance  $R_S$ , and substrate parasitics.

### (a) Series Inductance

The metal track in each segment can be further divided into several straight metal lines (for example, 5 straight metal lines for segment 4, see Figure 34(a)), so that the inductance  $L_{S\_lines}$  of each straight metal line can be expressed as the self inductance  $L_{line\_self}$  plus the mutual inductance M from all other metal lines [13]:

$$L_{S\_line} = L_{line\_self} + \sum M \tag{3}$$

The self inductance of a straight metal line can be written as [12]:

$$L_{line\_self} = 2l \left( \ln \frac{2l}{w_{eff} + t} - 0.5 \right)$$

(4)

where *l* is the length of the straight line, and *t* is the line thickness. Note that the current crowding effect has been accounted for and the self inductance is frequency dependent because of the introduction of  $w_{eff}$  in (4).

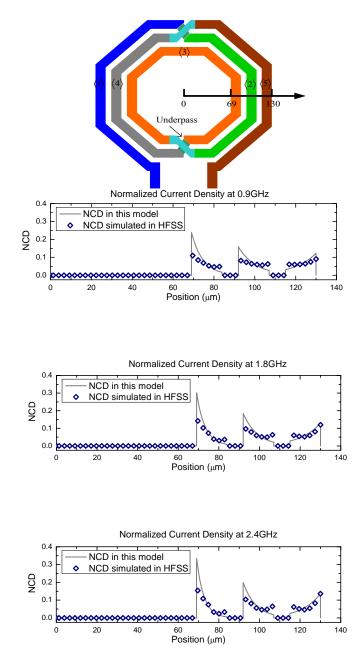

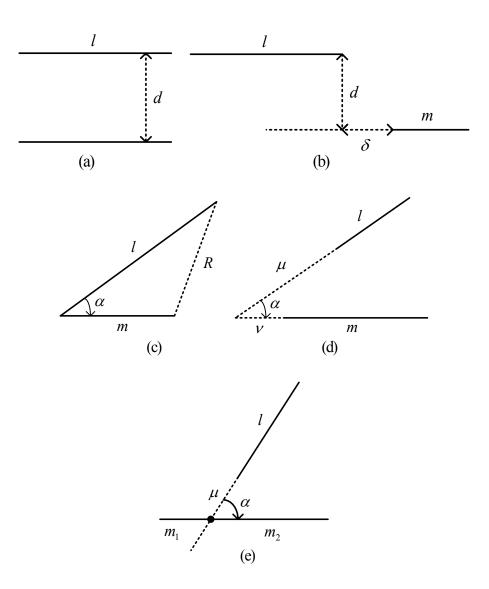

At low frequencies where the current distribution in a metal line is fairly uniform, mutual inductance of two parallel metal lines can be calculated using the geometric mean distance (GMD) [12]. This approach becomes questionable for high frequencies because of the highly non-uniform current distribution. In this work, the line separation is more accurately determined by the distance *d* between the centers of the two effective line widths. Based on this concept, the mutual inductance  $M_p$  for two parallel filaments of equal length (see Figure 37(a)) is expressed as

$$M_{p}(l) = 2l \left[ \ln \left( \frac{l}{d} + \sqrt{1 + \frac{l^{2}}{d^{2}}} \right) - \sqrt{1 + \frac{d^{2}}{l^{2}}} + \frac{d}{l} \right]$$

(5)

For unequal parallel filaments (see Figure 37(b)), the mutual inductance  $M'_P$  is

$$2M'_{p} = \left[M_{p}(l+m+\delta) + M(\delta)\right] - \left[M(l+\delta) + M(m+\delta)\right]$$

(6)

Here, m is the length of the second line, and  $\delta$  is the misalignment of the two lines and  $\delta$  becomes negative when two filaments overlap. For filaments incline with an angle between them (see Figure 37(c)), the mutual inductance  $M_i$  is

$$M_{i}(m,l) = \cos(\alpha) \cdot \left[ l \cdot \ln\left(\frac{l+m+R}{l-m+R}\right) + m \cdot \ln\left(\frac{l+m+R}{m-l+R}\right) \right]$$

(7)

Figure 37 Different possible filament alignments for the mutual

inductance calculations.

For the other possible configurations shown in Figure 37(d) and (e), the mutual inductances  $M'_i$  and  $M''_i$  can be modeled as

$$M'_{i} = \left[M_{i}(\mu + l, \nu + m) + M_{i}(\mu, \nu)\right] - \left[M_{i}(\mu + l, \nu) + M_{i}(\nu + m, \mu)\right]$$

(8)

$$M''_{i} = [M_{i}(m_{1}, \mu + l) + M_{i}(m_{2}, \mu + l)] - [M_{i}(m_{1}, \mu) + M_{i}(m_{2}, \mu)]$$

(9)

The total series inductance of a segment is the sum of all the straight-line series inductances, including the self and mutual inductances, within the segment.

Note that because of the need of a terminal taken in the middle of the segment box to connect the coupling capacitance to the neighboring segment box, the series inductance is split into two, each with  $L_{s}/2$  and located on both sides of the terminal (see Figure 34(c)). The same applies to the series resistance.

#### (b) Series Resistance

Ohmic loss ( $I^2R$ ) caused by the series resistance in the metal line is a factor limiting the inductor performance. At low frequencies, where the current density in the metal line is uniform, the series resistance can be easily found from the metal line resistivity and geometry. For spiral inductors operating at high frequencies, the series resistance of a straight line is frequency dependent and can be modeled using the concept of the effective metal width:

$$R_{line}(f) = \frac{\rho \cdot l}{w_{eff} \cdot t_m} \tag{10}$$

where  $\rho$  represents the resistivity in  $\Omega$ -cm and  $t_m$  is the metal thickness. The total series resistance of a segment is the sum of all straight line resistances.

### (c) Substrate Parasitics

Substrate parasitics result from the electrical coupling between the metal track and substrate, as the metal track of a spiral inductor can be considered as a microstrip on substrate with waves passing through it. Three elements,  $C_{ox}$ ,  $G_{sub}$ , and  $C_{sub}$ , are used to model the substrate parasitics (see Figure 34(c)).

The frequency-dependent permittivity  $\varepsilon_{eff}(f)$  is needed to model the frequency-dependent capacitance. It can be written as [56]:

$$\varepsilon_{eff}(f) = \varepsilon_{ox} - \frac{\varepsilon_{ox} - \varepsilon'}{1 + (f/f_c)^2}$$

(11)

$$\varepsilon' = \frac{\varepsilon_{ox} + 1}{2} + \frac{\varepsilon_{ox} - 1}{2\left(1 + 10t_{ox}/w_{eff}\right)}$$

(12)

Here,  $t_{ox}$  is the thickness of oxide under the metal line,  $\varepsilon_{ox}$  is the relative permittivity of oxide, and the critical frequency  $f_C$  is given by

$$f_C = \frac{c^2 \varepsilon_0 Z_0 \varepsilon_{ox}}{2t_{ox}} \varepsilon^{1/2}$$

(13)

$$Z_{0} = \frac{120\pi \cdot F\left(w_{eff}, t_{ox}\right)}{\varepsilon^{1/2}}$$

(14)

with

$$F\left(w_{eff},t\right) = \begin{cases} \frac{1}{2\pi} \ln\left(\frac{8t}{w_{eff}} + \frac{w_{eff}}{4t}\right) & \text{for } t/w_{eff} > 1\\ \frac{1}{w_{eff}/t + 2.42 - 0.44t/w_{eff} + \left(1 - t/w_{eff}\right)^{6}} & \text{for } t/w_{eff} < 1 \end{cases}$$

(15)

Using the frequency-dependent permittivity, the oxide capacitance and substrate conductance can be expressed as

$$C_{ox}(f) = \frac{\varepsilon_0 \varepsilon_{eff}(f)}{2F(w_{eff}, t_{ox})} \cdot l$$

(16)

$$G_{sub} = \frac{\sigma_{sub} \left[ 1 + \left( 1 + 10 t_{sub} / w_{eff} \right)^{-1/2} \right]}{2F \left( w_{eff}, t_{sub} \right)} \cdot l$$

(17)

where  $\varepsilon_0$  is the permittivity of free space,  $\sigma_{sub}$  is the silicon substrate conductivity, and  $t_{sub}$  is the thickness of substrate. The substrate capacitance can be expressed using (16) with  $t_{ox}$  replaced by  $t_{sub}$ .

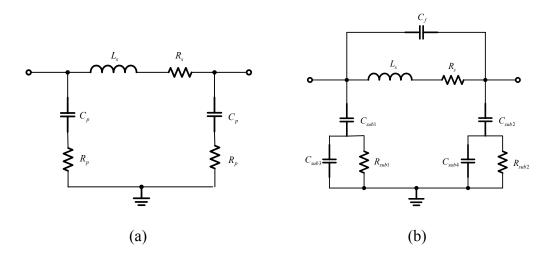

# 3.2.3. Modeling Components Outside Segment Box

Two types of components are located outside the segment boxes in Figure 34(b): the coupling capacitances between the metal lines and parasitics associated with the overlaps.

## (a) Coupling Capacitance Between Metal Lines

$C_{C,ij}$  in Figure 34(b) describes the coupling capacitance between segments *i* and *j*. Such a capacitance can be modeled using the method stated in [57]. For a conductor of width *w* centered at *b*, the even-symmetric potential at any point z = x + jy in the complex plane is given by

$$\phi_e(z,b,w) = q \left[ \frac{1}{\varepsilon_0} H_e(z,b,w) \right]$$

(18)