University of Central Florida

Electronic Theses and Dissertations, 2004-2019

2016

# Developing New Power Management and High-Reliability Schemes in Data-Intensive Environment

Ruijun Wang University of Central Florida

Part of the Computer Engineering Commons Find similar works at: https://stars.library.ucf.edu/etd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

## **STARS Citation**

Wang, Ruijun, "Developing New Power Management and High-Reliability Schemes in Data-Intensive Environment" (2016). *Electronic Theses and Dissertations, 2004-2019.* 5433. https://stars.library.ucf.edu/etd/5433

## DEVELOPING NEW POWER MANAGEMENT AND HIGH-RELIABILITY SCHEMES IN DATA-INTENSIVE ENVIRONMENT

by

## RUIJUN WANG M.S.Information Systems, Central Queensland University, 2009

A dissertation submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy of Computer Engineering in the Department of Electrical and Computer Engineering in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Summer Term 2016

Major Professor: Jun Wang

© 2016 Ruijun Wang

## ABSTRACT

With the increasing popularity of data-intensive applications as well as the large-scale computing and storage systems, current data centers and supercomputers are often dealing with extremely large data-sets. To store and process this huge amount of data reliably and energy-efficiently, three major challenges should be taken into consideration for the system designers. Firstly, power conservation-Multicore processors or CMPs have become a mainstream in the current processor market because of the tremendous improvement in transistor density and the advancement in semiconductor technology. However, the increasing number of transistors on a single die or chip reveals a super-linear growth in power consumption [4]. Thus, how to balance system performance and power-saving is a critical issue which needs to be solved effectively. Secondly, system reliability-Reliability is a critical metric in the design and development of replication-based big data storage systems such as Hadoop File System (HDFS). In the system with thousands machines and storage devices, even in-frequent failures become likely. In Google File System, the annual disk failure rate is 2.88%, which means you were expected to see 8,760 disk failures in a year. Unfortunately, given an increasing number of node failures, how often a cluster starts losing data when being scaled out is not well investigated. Thirdly, energy efficiency-The fast processing speeds of the current generation of supercomputers provide a great convenience to scientists dealing with extremely large data sets. The next generation of "exascale" supercomputers could provide accurate simulation results for the automobile industry, aerospace industry, and even nuclear fusion reactors for the very first time. However, the energy cost of super-computing is extremely high, with a total electricity bill of 9 million dollars per year. Thus, conserving energy and increasing the energy efficiency of supercomputers has become critical in recent years.

This dissertation proposes new solutions to address the above three key challenges for current large-scale storage and computing systems. Firstly, we propose a novel power management scheme

called MAR (model-free, adaptive, rule-based) in multiprocessor systems to minimize the CPU power consumption subject to performance constraints. By introducing new I/O wait status, MAR is able to accurately describe the relationship between core frequencies, performance and power consumption. Moreover, we adopt a model-free control method to filter out the I/O wait status from the traditional CPU busy/idle model in order to achieve fast responsiveness to burst situations and take full advantage of power saving. Our extensive experiments on a physical testbed demonstrate that, for SPEC benchmarks and data-intensive (TPC-C) benchmarks, an MAR prototype system achieves 95.8-97.8% accuracy of the ideal power saving strategy calculated offline. Compared with baseline solutions, MAR is able to save 12.3-16.1% more power while maintain a comparable performance loss of about 0.78-1.08%. In addition, more simulation results indicate that our design achieved 3.35-14.2% more power saving efficiency and 4.2-10.7% less performance loss under various CMP configurations as compared with various baseline approaches such as LAST, Relax, PID and MPC.

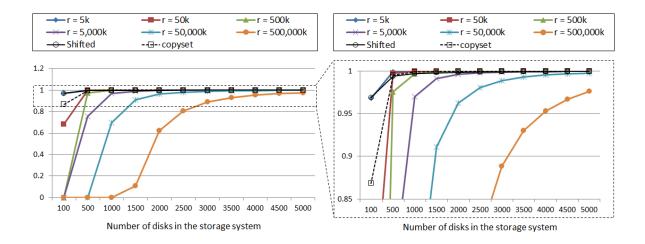

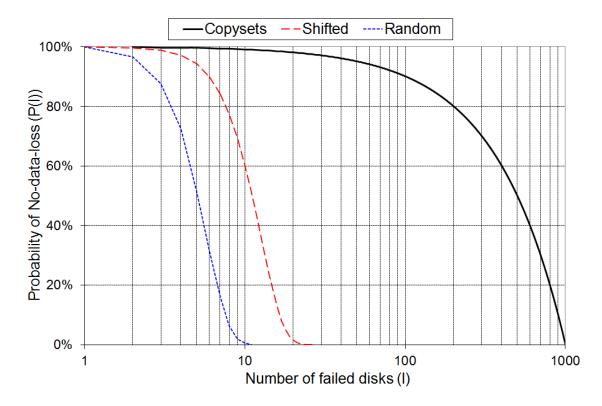

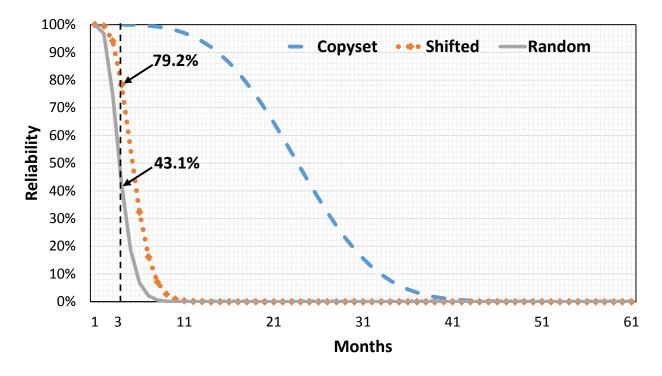

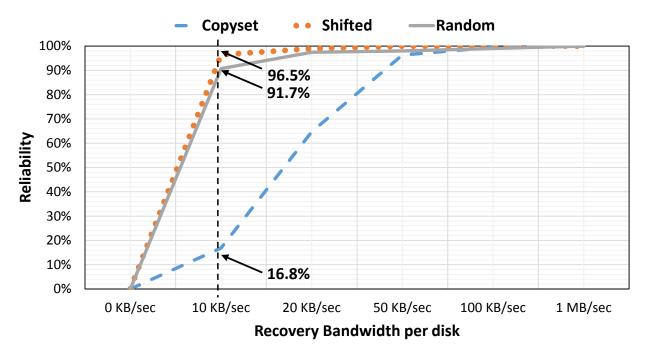

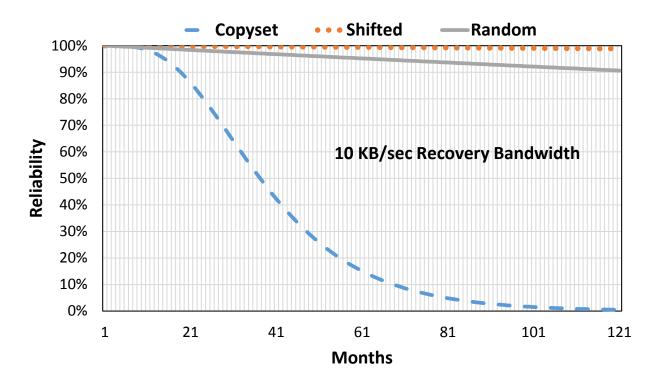

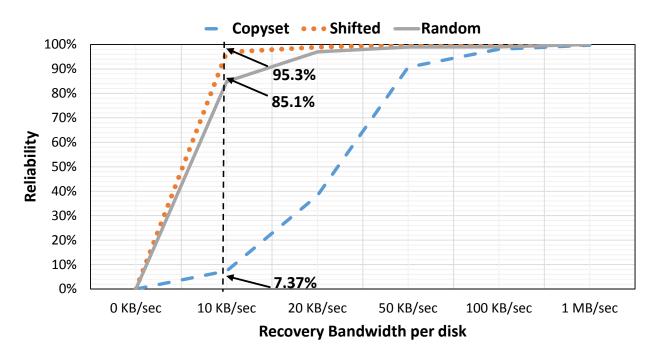

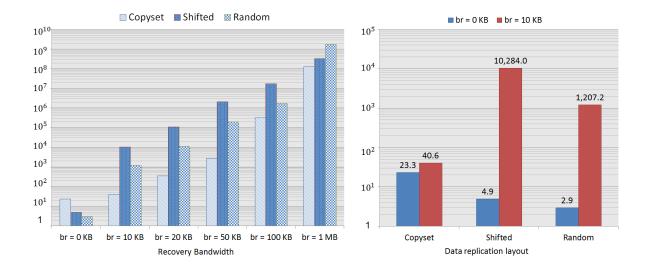

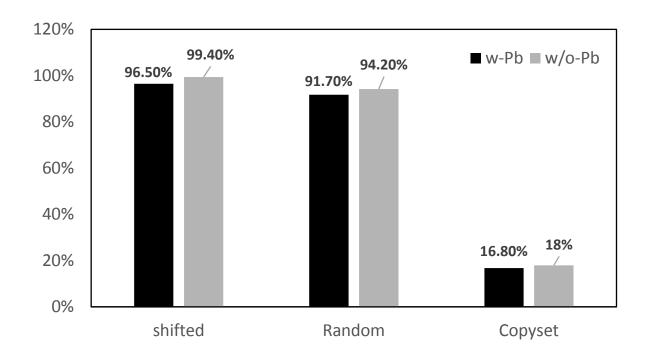

Secondly, we create a new reliability model by incorporating the probability of replica loss to investigate the system reliability of multi-way declustering data layouts and analyze their potential parallel recovery possibilities. Our comprehensive simulation results on Matlab and SHARPE show that the shifted declustering data layout outperforms the random declustering layout in a multi-way replication scale-out architecture, in terms of data loss probability and system reliability by upto 63% and 85% respectively. Our study on both 5-year and 10-year system reliability equipped with various recovery bandwidth settings shows that, the shifted declustering layout surpasses the two baseline approaches in both cases by consuming up to 79 % and 87% less recovery bandwidth for random layout.

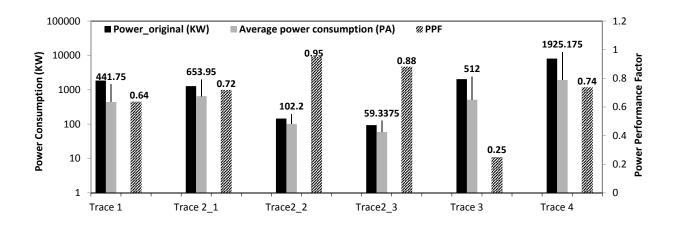

Thirdly, we develop a power-aware job scheduler by applying a rule based control method and taking into account real world power and speedup profiles to improve power efficiency while adhering to predetermined power constraints. The intensive simulation results shown that our proposed method is able to achieve the maximum utilization of computing resources as compared to baseline scheduling algorithms while keeping the energy cost under the threshold. Moreover, by introducing a Power Performance Factor (PPF) based on the real world power and speedup profiles, we are able to increase the power efficiency by up to 75%.

## ACKNOWLEDGMENTS

This dissertation would not been possible without the help and support of a number of people. First and foremost, I would like to express my sincerest gratitude to my adviser, Dr.Jun Wang, for the tremendous time, energy and wisdom he has invested in my graduate education. His inspiring and constructive supervision has always been a constant source of encouragement for my study. I also want to thank my dissertation committee members, Dr.Ronald DeMara, Dr.Yier Jin, Dr.Shaojie Zhang and Dr.Liqiang Ni, for spending their time to view the manuscript and provide valuable comments.

I would like to thank my past and current colleagues: Pengju Shang, Huijun Zhu, Jiangling Yin, Xuhong Zhang, Dan Huang and Xunchao Chen. I want especially thank to Xuhong, for the inspiring discussion and continuous support to improve the quality of each work. A special thanks to Jiangling, for tremendous help on my experiment setups. My gratitude also goes to Pengju Shang, whos previous work provides great inspirations of this dissertation.

I dedicate this thesis to my family: my parents Yunfu Wang and Mingxia Zong, my husband Chun Tang, for all their love and encouragement throughout my life. Last but not least, I would also like to extend my thanks to my friends, who have cared and helped me, in one way or another. My graduate studies would not have been the same without them.

Last but not least, my works are supported in part by the US National Science Foundation Grant CCF-1527249, CCF-1337244 and National Science Foundation Early Career Award 0953946.

# **TABLE OF CONTENTS**

| LIST OF FIGURES                          | xii |

|------------------------------------------|-----|

| LIST OF TABLES                           | cvi |

| CHAPTER 1: INTRODUCTION                  | 1   |

| MAR: A Novel power management scheme     | 2   |

| Reliability Analysis                     | 5   |

| Power-aware job scheduling               | 7   |

| CHAPTER 2: LITERATURE REVIEW             | 9   |

| Power Management Background              | 9   |

| Reliability Analysis in Storage systems  | 10  |

| Copyset replication                      | 10  |

| Random and shifted declustering approach | 11  |

| Muti-way Replication                     | 12  |

| Existing Reliability Models              | 13  |

CHAPTER 3: MAR: A NOVEL POWER MANAGEMENT SCHEME FOR CMP SYS-

| TEMS IN DATA-INTENSIVE ENVIRONMENT              |

|-------------------------------------------------|

| Learning Core's Behaviors                       |

| Per-Core                                        |

| Multi-Core                                      |

| Analysis and Preparation for MAR Design         |

| MAR's Design                                    |

| MAR Control model                               |

| Fuzzification without consideration of I/O wait |

| Fuzzification with consideration of I/O wait    |

| Fuzzy Rules                                     |

| Centroid Defuzzification method                 |

| Self-tuning Strategy                            |

| Methodology                                     |

| Processor                                       |

| Benchmark                                       |

| Core Statistics                                 |

| DVFS Interface                                  |

| Power Estimation                                                 | 37 |

|------------------------------------------------------------------|----|

| Baseline Control Methods                                         | 39 |

| Experiments                                                      | 39 |

| Fast Responsiveness                                              | 40 |

| Power Efficiency                                                 | 41 |

| Comparison with conventional governors                           | 47 |

| Conclusion                                                       | 49 |

| CHAPTER 4: A NEW RELIABILITY MODEL IN REPLICATION-BASED BIG DATA |    |

| STORAGE SYSTEMS                                                  | 55 |

| Extended Reliability Model                                       | 55 |

| Case 1:                                                          | 58 |

| Case 2:                                                          | 59 |

| Reliability Analysis                                             | 60 |

| Shifted Declustering Layout                                      | 60 |

| copyset Replication Layout                                       | 63 |

| Random Declustering Layout                                       | 66 |

| Aggrestive parallel recovery and the repair rate $\mu_l$         | 67 |

| Comparison between Copyset, Shifted and Random Declustering                       | 70 |

|-----------------------------------------------------------------------------------|----|

| Simulation Results                                                                | 73 |

| Methodology                                                                       | 73 |

| Sampling Procedures                                                               | 74 |

| Probility of No-data-Loss                                                         | 75 |

| System Reliability without Recovery                                               | 76 |

| System Reliability with Recovery                                                  | 77 |

| System reliability with and without considering probability of replica lost $\$ . | 81 |

| Mean Time to Data Loss                                                            | 83 |

| Conclusions                                                                       | 84 |

| CHAPTER 5: AN ENERGY-EFFICIENT JOB SCHEDULER FOR SUPERCOMPUTERS                   | 86 |

| Scheduler Design                                                                  | 86 |

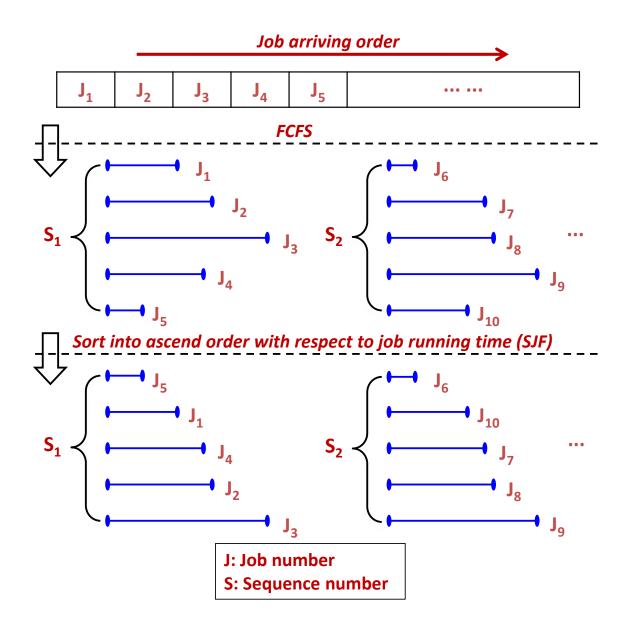

| Job scheduling polices                                                            | 86 |

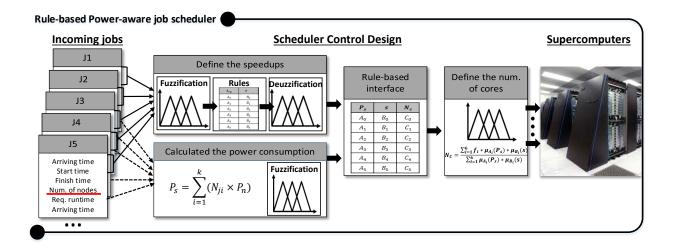

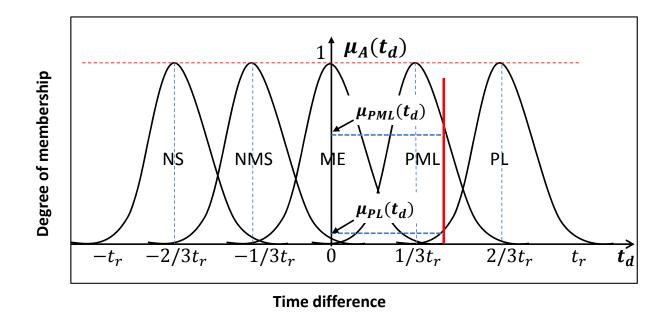

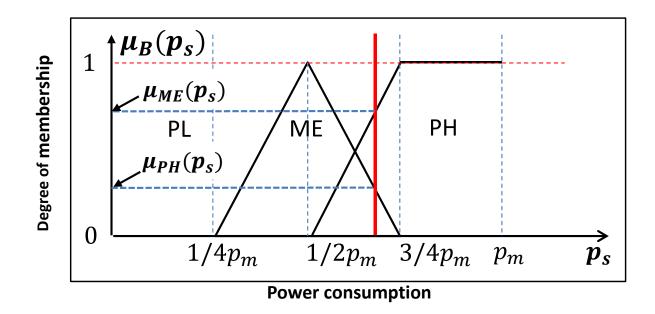

| Scheduler control model                                                           | 88 |

| Define the speedups                                                               | 91 |

| Fuzzification based on rules                                                      | 91 |

| Define the power consumption                                                      | 92 |

| Define the number of cores         | 94  |

|------------------------------------|-----|

| Methodology                        | 96  |

| Processor                          | 96  |

| Traces                             | 96  |

| Power estimation                   | 96  |

| Baseline algorithms                | 97  |

| Experiment                         | 98  |

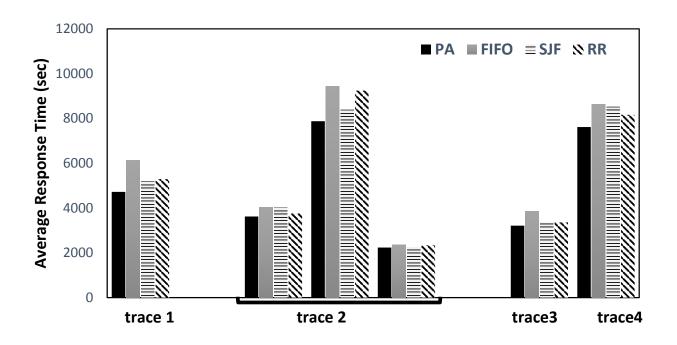

| Comparison of scheduling algorithm | 98  |

| Scheduling efficiency              | 98  |

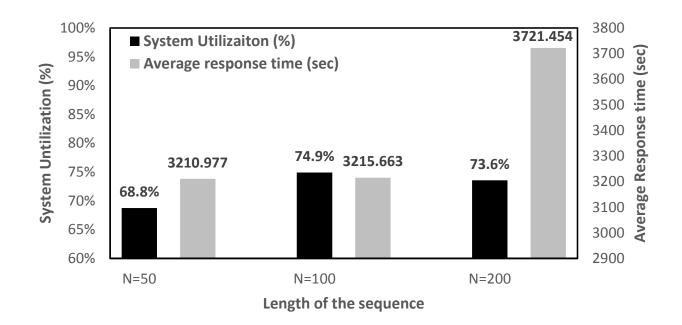

| Determine the length of a Sequence | 99  |

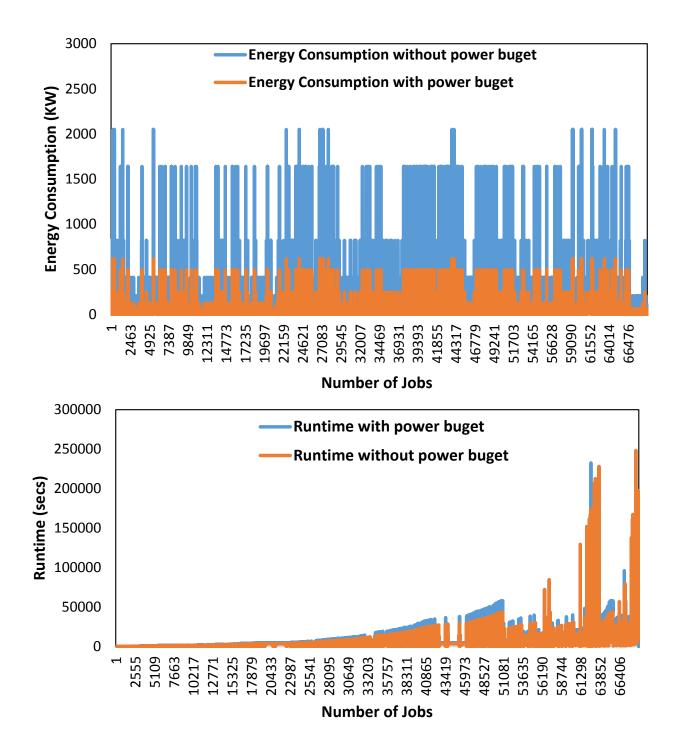

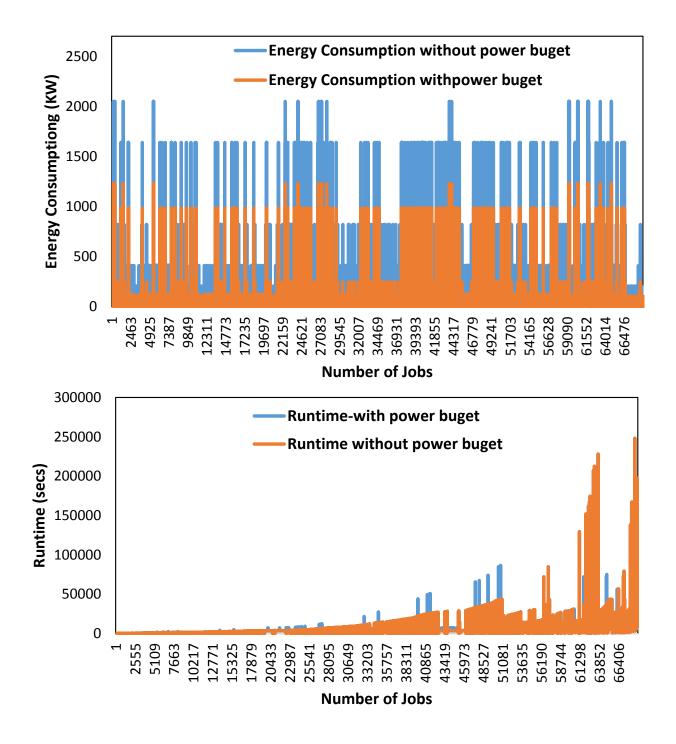

| Power and Speedup constraints      | 100 |

| CHAPTER 6: CONCLUSION              | 107 |

| LIST OF REFERENCES                 | 110 |

# **LIST OF FIGURES**

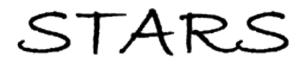

| Figure 1.1: Research work overview                                                      | 2  |

|-----------------------------------------------------------------------------------------|----|

| Figure 3.1: The relationship between CPU's frequency, power consumption and perfor-     |    |

| mance                                                                                   | 16 |

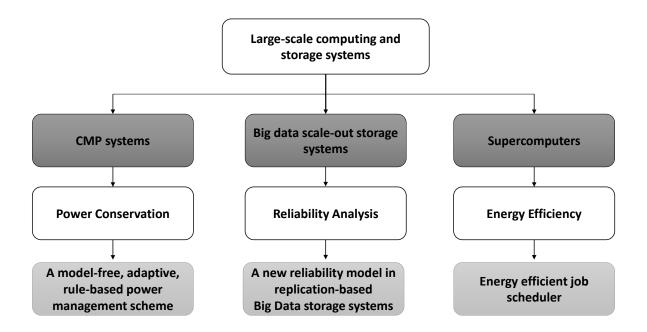

| Figure 3.2: Overall execution time of different workloads                               | 18 |

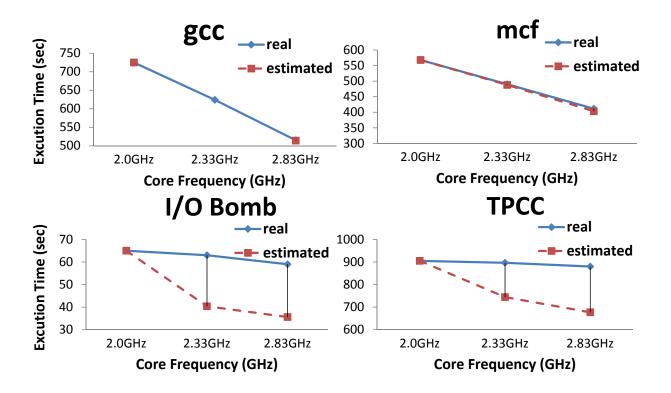

| Figure 3.3: Core's major statistics under different workloads                           | 20 |

| Figure 3.4: The trace of core0 under both high and low frequency; the overall execution |    |

| times are comparable for the two cases.                                                 | 21 |

| Figure 3.5: Two cases when I/O wait exits                                               | 22 |

| Figure 3.6: The architecture of MAR power management                                    | 27 |

| Figure 3.7: Mapping results for response time using Triangular Membership Function      | 28 |

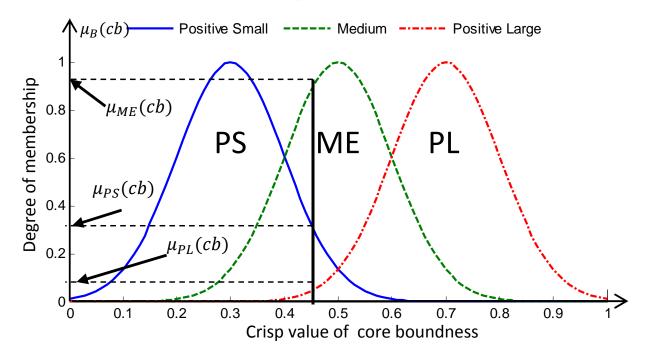

| Figure 3.8: Mapping results for core boundness using Gaussian Membership Function .     | 29 |

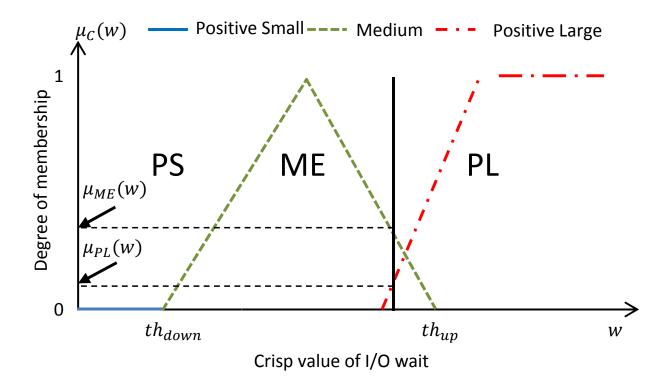

| Figure 3.9: Mapping results for I/O wait using Triangular Membership Function           | 30 |

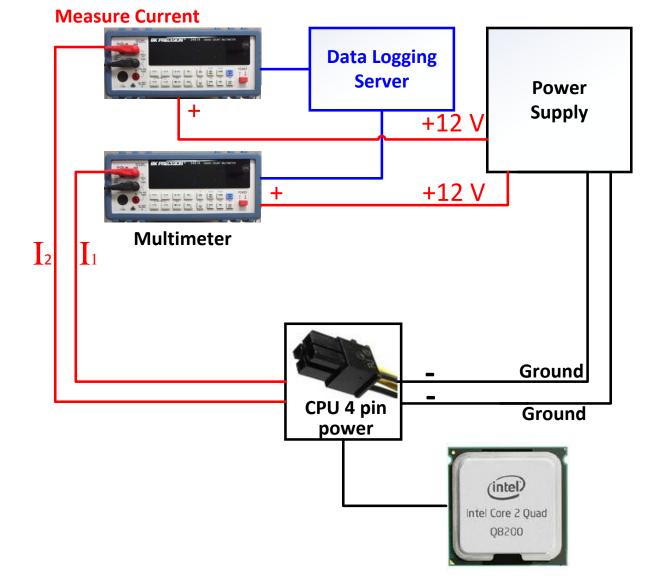

| Figure 3.10The Measurement setup: two multimeters are inserted between the power        |    |

| supply and CPU                                                                          | 38 |

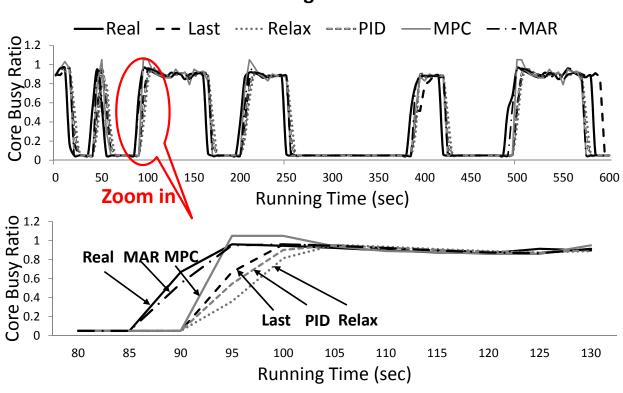

| Figure 3.11Comparison of workload prediction accuracy on a randomly picked core,        |    |

| SP=10s                                                                                  | 41 |

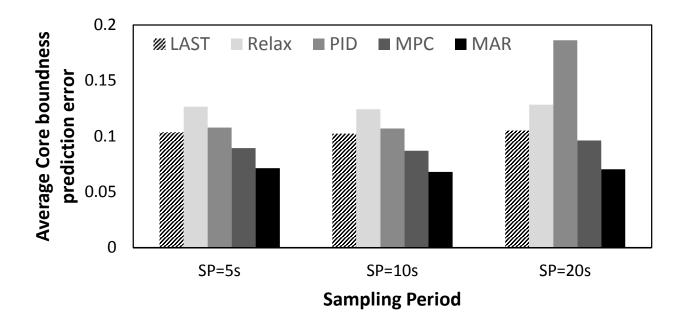

| Figure 3.12Average prediction errors for different sampling period                      | 43 |

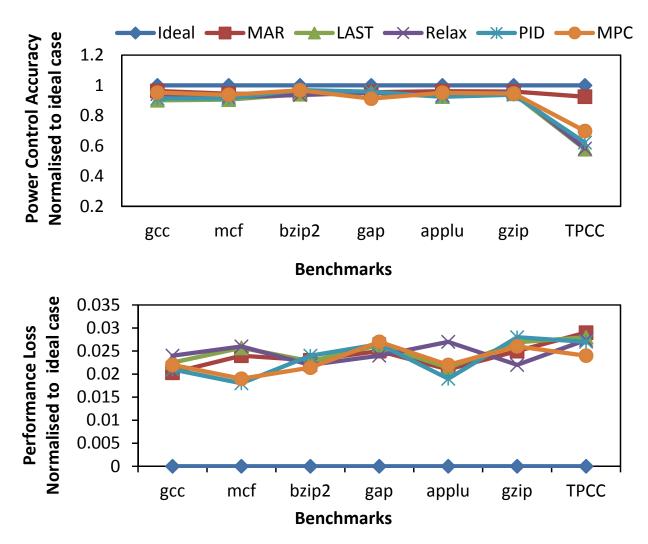

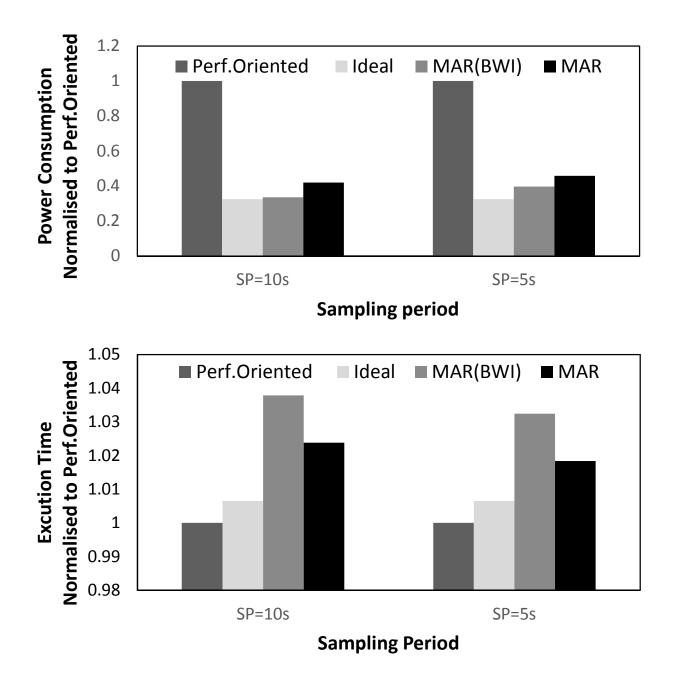

| Figure 3.13MAR's performance comparison under various benchmarks                                  | 44 |

|---------------------------------------------------------------------------------------------------|----|

| Figure 3.14Comparison of the power management efficiency of MAR with the baselines,               |    |

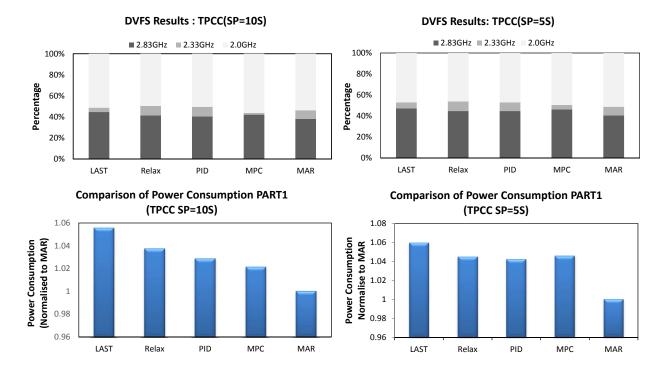

| SP = 10s/5s                                                                                       | 45 |

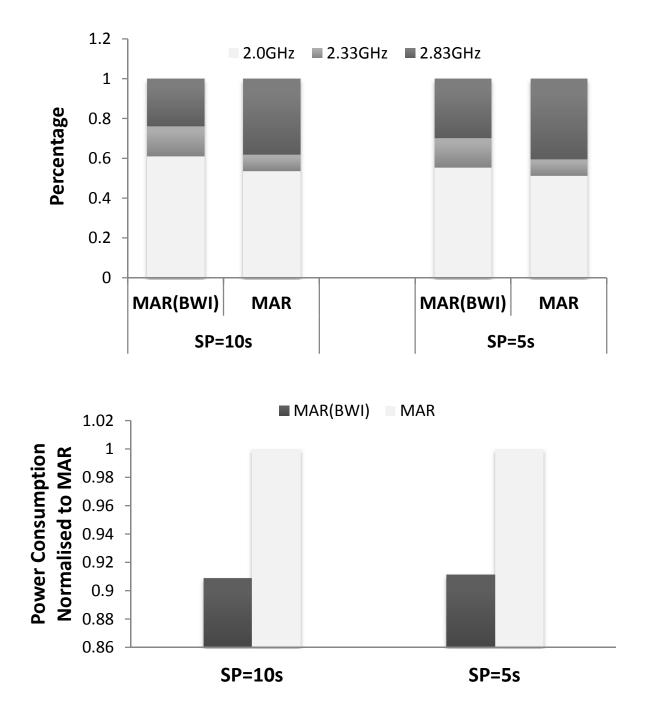

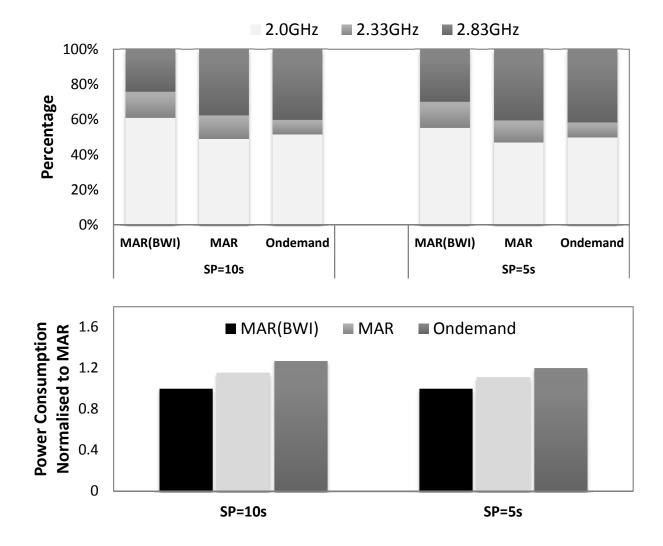

| Figure 3.15The DVFS and power consumption results of MAR (BWI) and MAR                            | 50 |

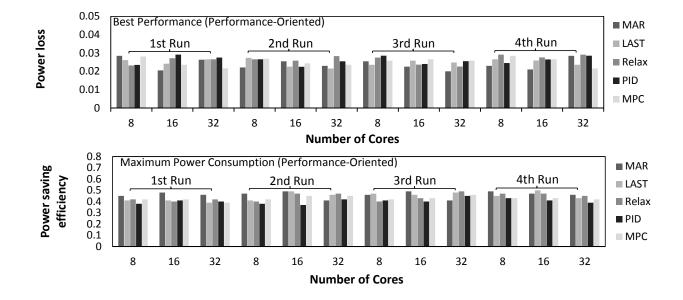

| Figure 3.16Comparison of Power-saving efficiency and performance loss, $SP = 10s/5s$ .            | 51 |

| Figure 3.17Scalability study of MAR and baselines under different number of cores in              |    |

| simulation                                                                                        | 52 |

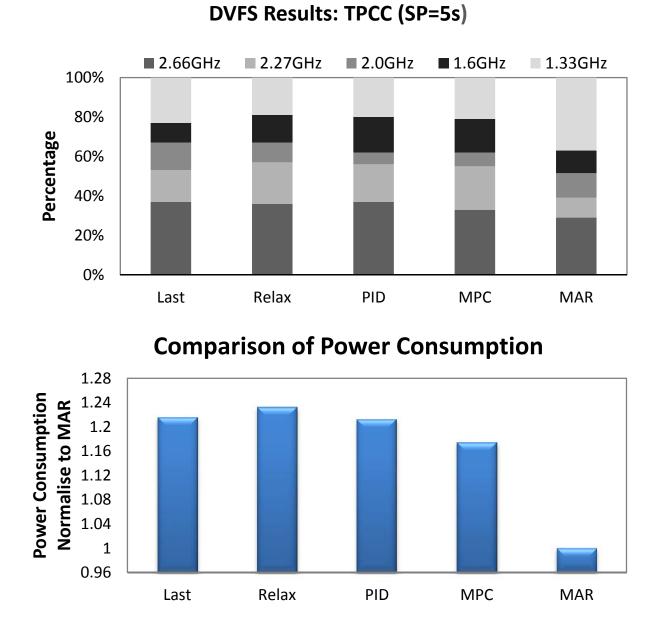

| Figure 3.18Comparison of DVFS Scaling results for MAR and baselines with 5 CPU                    |    |

| frequency levels                                                                                  | 53 |

| Figure 3.19Performance and Power Consumption Comparison between MAR and Linux                     |    |

| conventional governors in DVFS                                                                    | 54 |

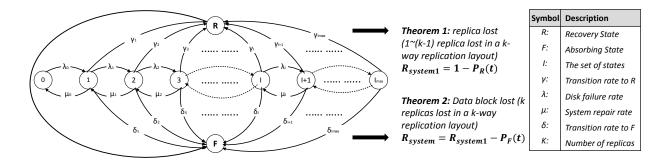

| Figure 4.1: State transition in declustered layouts                                               | 55 |

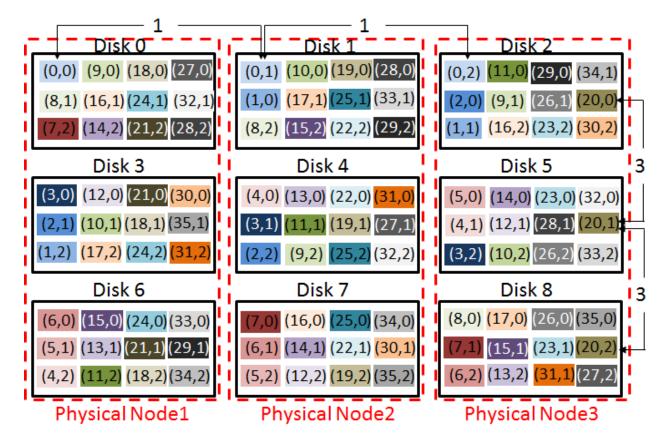

| Figure 4.2: Shifted declustering layout                                                           | 61 |

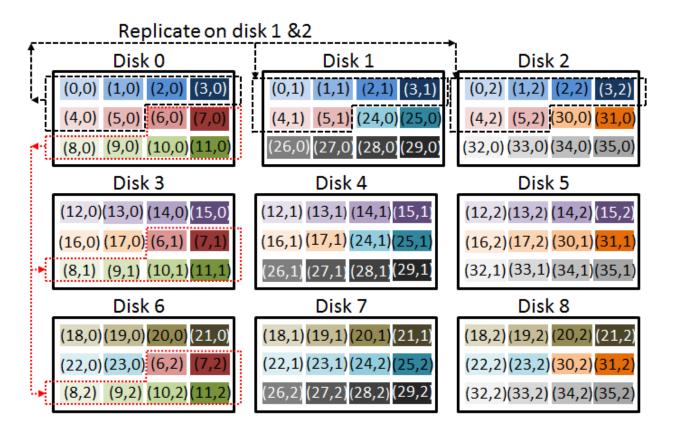

| Figure 4.3: Copyset Replication layout                                                            | 64 |

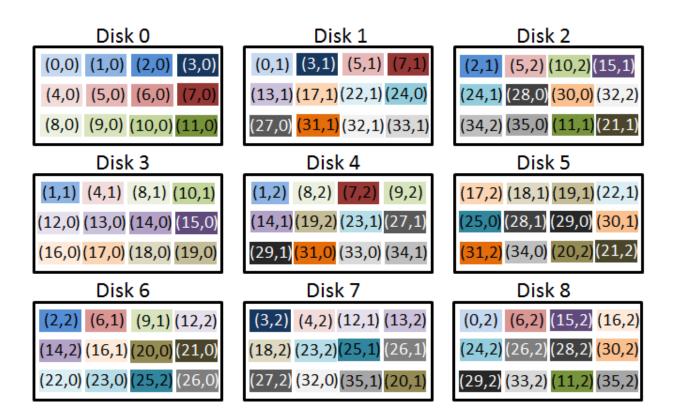

| Figure 4.4: Random Declustering layout                                                            | 65 |

| Figure 4.5: The comparison of $P^{(k)}$ between copyset, shifted and random declustering $\ldots$ | 71 |

| Figure 4.6: Probability of no data loss in a 999-disk system $(P^{(l)})$                          | 76 |

| Figure 4.7: System reliability of a 999-disk system without recovery                              | 77 |

| Figure 4.8: Reliability after 5 years                                                                                         | 78  |

|-------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.9: System reliability with 10 KB recovery bandwidth per disk                                                         | 79  |

| Figure 4.10Reliability after 10 years                                                                                         | 80  |

| Figure 4.11Mean Time to Data Loss                                                                                             | 81  |

| Figure 4.12Average system Reliability with and without considering probability of replica lost, recovery bandwidth = 10KB/sec | 82  |

| Figure 5.1: The illustration of our proposed scheduling algorithm                                                             | 87  |

| Figure 5.2: The architecture of our Rule-based Power-aware job scheduler                                                      | 89  |

| Figure 5.3: Gaussian membership function for mapping the time difference $(t_d)$ to linguistic terms                          | 92  |

| Figure 5.4: Triangular membership function for mapping the power consumption $(p_s)$ to linguistic terms                      | 93  |

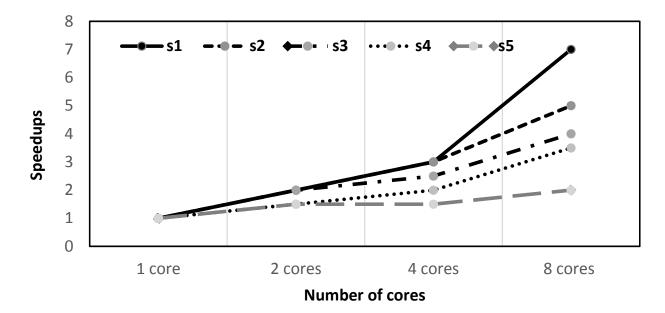

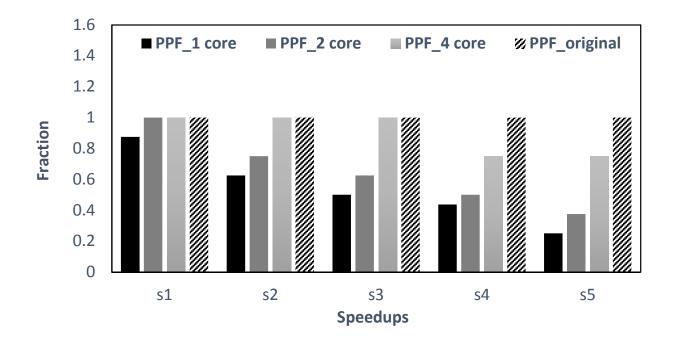

| Figure 5.5: The 5 level of speedup profiles                                                                                   | 94  |

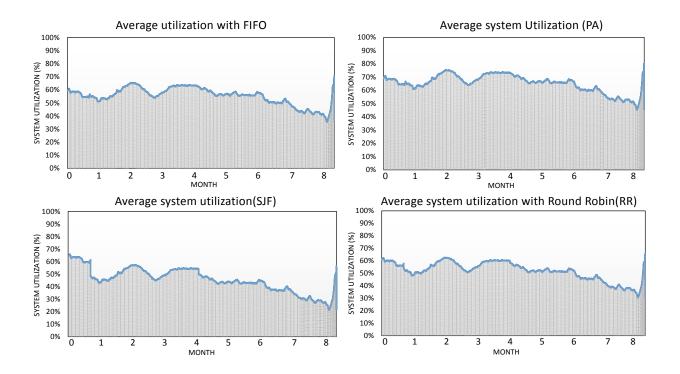

| Figure 5.6: Average system utilization compared with the baseline scheduling polices using trace 3                            |     |

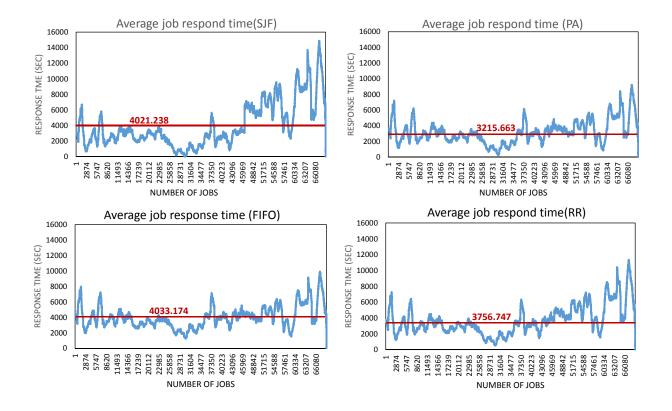

| Figure 5.7: Average system response time compared with the baseline scheduling polices using trace 3                          | 100 |

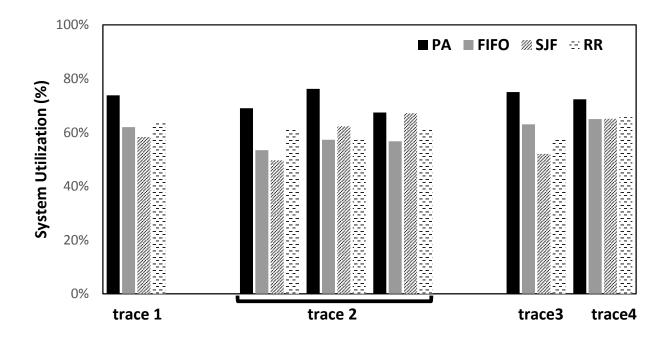

| Figure 5.8: Average system utilization for all 4 traces                                                                       | 101 |

| Figure 5.9: System utilization and response time with different settings of the length of         |

|---------------------------------------------------------------------------------------------------|

| Sequence $(L_s)$ by using trace 3                                                                 |

| Figure 5.10Average response time for all 4 traces                                                 |

| Figure 5.11Power consumption results with considering of the power constraints, P = 512KW         |

| Figure 5.12Power consumption results with considering of the power constraints, P = 1228.8KW      |

| Figure 5.13The result of Power Performance Factor for 5 different speedup levels by using trace 3 |

| Figure 5.14Average power consumption and PPF output for all 4 traces                              |

# LIST OF TABLES

| Table 3.1: | Cache Miss Rate                                                         | 20 |

|------------|-------------------------------------------------------------------------|----|

| Table 3.2: | Fuzzy Rule Base(Part I)                                                 | 31 |

| Table 3.3: | Fuzzy Rule Base(Part II)                                                | 34 |

| Table 3.4: | Comparison of the Overhead of Different Managements                     | 46 |

| Table 4.1: | Parameters in Simulation                                                | 74 |

| Table 5.1: | Rules for determine the Speedups                                        | 92 |

| Table 5.2: | Rules for determine of the core numbers                                 | 95 |

| Table 5.3: | Description of 4 traces                                                 | 97 |

| Table 5.4: | The breakdowns of the scheduling percentage on different core groups 10 | 03 |

## **CHAPTER 1: INTRODUCTION**

We are now entering the Big Data era, in which a huge amount of data are generated and analyzed by data-intensive applications as well as the large-scale computing and storage systems. These are reflected in the following three aspects. In the current processor market, multicore processors or CMPs have become a mainstream because of the tremendous improvement in transistor density and the advancement in semi-conductor technology. At the same time, the limitations in instruction level parallelism (ILP) coupled with power dissipation restrictions encourage us to enter the "CMP" era for both high performance and power savings [1], [2]. On the other hand, an increasing number of big data storage systems are turning to use multi-way replication based storage architecture for the sake of high availability and reliability [62, 60, 48, 54]. As the storage system scale up, it increases both capacity and bandwidth, but it also makes disk failures more common [79]. Thirdly, as the demand for high-performance computing on supercomputers and clusters continues to grow, there will be a substantial increase in the total power consumption. In the LiveScience report, the supercomputer "Titan" costs 100 million dollars and its electricity bill is expected to cost about 9 million dollars per year [100]. Therefore, even if scientists can benefit from the fast computing speeds provided by supercomputers, we cannot neglect the staggering electricity bill associated with these computing service.

In a computing or storage system like this, three important factors need to be taken into account for design considerations which are power conservation, reliability as well as the energy efficiency. More specifically, we propose three new approaches to improve the above three metrics in large-scale computing and storage systems as shown in Figure 1.1.

Figure 1.1: Research work overview

MAR: A Novel power management scheme

In recent years, many power management strategies have been proposed for CMP processors based on DVFS [5], [6], [7]. DVFS (Dynamic Voltage and Frequency Scaling) is a highly effective technique used to reduce the power dissipation. Previous research [8, 9, 10, 11] has successfully balanced the CPU power consumption and its overall performance by using chip-wide DVFS. However, this coarse-granular management cannot be directly applied to CMP chips where percore DVFS is available for more aggressive power-saving. Several recently proposed algorithms [12], [13] are based on open-loop search or optimization strategies, assuming that the power consumption of a CMP at different DVFS levels can be estimated accurately. This assumption may result in severe performance degradation or even power constraint violation when the workloads vary significantly from the one they used to perform estimations. There are also some closed-loop solutions based on feedback control theory [14, 15] which obtain power savings by using detected statistics of each core. The most widely adopted CPU statistics are CPU busy/idle times [16]. This busy/idle time approach referred as B-I model works well for non-I/O intensive applications. Unfortunately, data Intensive applications are mainly I/O bound, which becomes the main focus in this work. They often exhibit the unpredictable nature of I/O randomness and thus make the CPU utilization status hard to track. Consequently, the B-I model might not work well at this circumstance.

It may be noted that the I/O operations could actually affect the processor's both performance and power consumption, especially when we deal with data-intensive applications. More specifically, by taking I/O factors into consideration, we are able to make best use of CPU slack periods to save power more effectively and more efficiently. One example is when CPU is waiting for I/O operations to complete. Through our experiments, we found out several facts that can be utilized to conserve more power for a CMP processor. First of all, each core's waiting time for a completed I/O operation can be separated from its idle or working status. Secondly, appropriate scaling down the core's frequency during its I/O wait could provide more opportunities to save power without sacrificing overall system performance. Thirdly, the core frequency does not directly affect the I/O wait which means no relationship exists between these two factors. According to the above-mentioned observations, we develop our power management solutions for data-intensive applications using the following specific ways:

- 1. Considerations of each core's I/O wait status besides its working and idle status.

- 2. Accurately quantifying each status for accurate power-saving decisions.

- 3. A precise description of the relationship between frequency, performance and power consumption when the I/O wait factor is considered.

When we integrate the I/O wait into the power control system design, one challenge lies that the CPU workload is unable to be modeled because of the I/O randomness, which mainly results from

the diversity of I/O patterns and the internal characteristic of storage systems. In our experiment, we found that even with a comprehensive control policy, such as MPC, it is impossible to accurately predict the CPU workloads for I/O intensive applications. To resolve this issue, we employ a fuzzy logic control to simplify the model construction work, which incorporates a precise logic and approximate reasoning into the system design and obtains much more accurate representations [40, 41, 42, 43, 44].

We develop a multi-input-multi-output power management system named MAR (model-free, adaptive, and rule-based) for CMP machines. It adopts a fuzzy logic for the power management by considering the I/O wait rather than employing traditional B-I model. Our design could precisely control the performance of a CMP chip at the desired set point while save 12.3-16.1% more power at run-time. Moreover, we are able to save even more power if the loaded CPUs support more frequency levels, as detailed in the experimental results in Chapter 3.

There are four primary contributions of this work:

- Developing a model-free, adaptive and rule-based power management method named MAR.

- Achieving fast-responsiveness through fast detecting methods that adopted by MAR.

- Conducting extensive experiments to examine the impacts of the cores seven working status and proposing an accurate description about the relationship between frequency, performance and power consumption.

- Simplifying the power management method by introducing fuzzy control theory in order to avoid the heavy relying on precise system model.

#### **Reliability Analysis**

Today, an increasing number of big data storage systems are turning to use multi-way replication based storage architecture for the sake of high availability and reliability [62, 60, 48, 54].

Reliability is increasingly important in big data storage systems built from thousands of individual components. As the storage system scale up, it increases both capacity and bandwidth, but it also makes disk failures more common [79]. In petabyte-scale file systems, disk failures will happen in a daily bases. In the system with thousands machines and storage devices, even in-frequent failures become likely. Therefore, analyzing the system reliability through an analytic method is useful since they can provide a reference for developers to choose the best layout catering their requirements.

With regards to the modeling of system reliability, it should considers all the situations that will make the system unreliable. Intuitively, when people thinking about system reliability, they will tend to consider the data loss probability and the system recovery bandwidth [50, 51, 81]. However, in a replication-based storage systems, the loss of replicas will also have an influence on the system reliability which should not be neglected. This motivates us to create an effective and comprehensive analytic model to obtain an accurate reliability results.

It may be noted that it is not feasible to build a real testbed to evaluate the reliability of a large-scale redundancy storage system with different layout schemes. Once the block distribution scheme is selected, the layout can no longer be changed after the production storage system is up to work. Moreover, there is no systemic method which can be used to quantify the reliability for multi-way replication based data placement methods. This is especially true when the number of copies exceeding two. This is because the replicas of data on one failed disk are distributed among multiple disks in the declustered storage system, if either one of those disks fails before the failed disk

completely recovered, the data block will lost permanently. As a result, the data loss probability has increased. This motivates us to exploit the impact of data layouts on reliability in multi-way replication storage systems.

We propose a comprehensive reliability model to investigate the system reliability of multi-way declustering data layouts and analyzing their potential parallel recovery possibilities.

Specifically, we make the following contributions:

- 1. Propose a new reliability model to investigate the system reliability of multi-way declustering data layouts.

- 2. Utilize the reliability model for analyzing the data loss probability and system repair rate with different data layout schemes;

- Quantify the most important parameter used in the model, P<sup>(l)</sup>, which is the probability that the disk does not lose data with *l* failed disks in the system with either mathematical proof for copyset replication layout [46] or reasonable sampling techniques for shifted declustering [80] and random declustering<sup>1</sup>;

- 4. Analyze the possible optimal parallel recovery schemes for copyset replication, shifted declustering and random deccultering layouts;

- 5. Make specific comparison between these three layouts, which are the most widely used in current enterprise large-scale multi-way replication storage systems;

- 6. Simulate the reliability model, compare and explain the system reliability with considering of various recovery bandwidth.

<sup>&</sup>lt;sup>1</sup>Random declustering layout distributes data blocks according to given randomization algorithms, which map the key (or the index) of a data block to a position in the storage system.

## Power-aware job scheduling

Supercomputers and clusters today are usually managed by batch job scheduling systems, which partition the available set of compute nodes according to resource requests submitted through job scripts and allocate the partitions to parallel jobs [86]. As the demand for high-performance computing on supercomputers and clusters continues to grow, there will be a substantial increase in the total power consumption. In the LiveScience report, the supercomputer "Titan" costs 100 million dollars and its electricity bill is expected to cost about 9 million dollars per year [100]. Moreover, the computing and storage components of data centers consume around 61 billion kilowatt hours kWh of power per year, which costs about 4.5 billion U.S dollars. The power consumption of supercomputers and Data centers combined is about 1.5% of the total output of 15 typical power plants [101, 102]. Therefore, even if scientists can benefit from the fast computing speeds provided by supercomputers, we cannot neglect the staggering electricity bill associated with these computing service. In this case, it is necessary to apply a power-capping strategy for large-scale data storage or computing systems.

Job scheduling is a critical task for large-scale systems. Advanced schedulers can help to improve resource utilization and quality of service. Therefore, an advanced job scheduler should satisfy the following requirements. First, it must satisfy the user's requirements, such as job start time, requested number of processors, requested job finish time, and other priority constraints. Secondly, the scheduler should allocate the computation resources reasonably and effectively without exceeding the power limits. Thirdly, it should apply different speedup schemes while satisfying the user's requirements and saving as much power as possible. Finally, multiple power constraints should be introduced to adjust the power limit based on the characteristic of incoming jobs to explore further opportunities for energy conservation.

Many researchers are looking into this problem and trying to balance the energy conservation and

performance of supercomputers with various methods. For energy efficiency, some researchers attempt to schedule the job by applying Deadline Constraints on Data Grids or HPC systems [84, 89]. Some of them focus on developing energy-efficient multi-job scheduling models and algorithms for cloud computing [94, 93]. Others are proposed a technique to reduce the energy consumption by incorporating a predictive thermal model to select possible jobs to reduce the energy [87]. These algorithms are developed to conserve energy either by integrating the DVFS technique to examine the behavior of the workload or by introducing a thermal predictive model to minimize the energy needs. However, reducing energy consumption is not enough to alleviate the energy consumption issues of supercomputers. This work proposes to tackle the problem from the angle of improving the energy efficiency.

To the best of our knowledge, we present the first attempt to provide power efficient job scheduling on supercomputers by taking the power budget and speedup files into consideration. However, our method can provide opportunities to improve power conservation, which should not been neglected. In this work, we propose a novel rule-based power-aware job scheduler to efficiently schedule the incoming jobs while maintaining the power budget. The main contributions of this work are:

- 1. We develop a novel rule-based power-aware job scheduler to achieve the best system utilization while considering the power budgets and various speedup settings.

- 2. We generate a new scheduling algorithm to support our proposed job scheduler.

- 3. We create a series of rules to assist the scheduler with determining the appropriate power consumption as well as speedups.

- 4. We propose a new Power Performance Factor (PPF) to evaluate the power efficiency under a fixed power budget.

## **CHAPTER 2: LITERATURE REVIEW**

In this section, I would like to discuss the current research and their limitations with regards to the power management and the system reliability for large-scale computing and storage systems.

#### Power Management Background

In recent years, various power management strategies have been proposed for CMP systems. From the perspective of DVFS level, previous power management schemes could be divided into two categories which are chip-level and core-level power management. Chip-level power management uses chip-wide DVFS. In chip-level management [8, 9, 10, 11], the voltage and frequency of all cores are scaled to the same level during the program execution period by taking advantage of the application phase change. These techniques extensively benefit from application "phase" information that can pinpoint execution regions with different characteristics. They define several CPU frequency phases in which every phase is assigned to a fixed range of Mem/op. However, these task-oriented power management schemes do not take the advantage from per-core level DVFS. Core-level power management means managing the power consumption of each core. [12] and [13] collect performance-related information by an on-core hardware called performance monitoring counter (PMC). There are several limitations by using PMCs: Each CPU has a different set of available performance counters, usually with different names. Even different models in the same processor family can differ substantially in the specific performance counters available [38]; modern super scalar processors schedule and execute multiple instructions at one time. These "inflight" instructions can retire at any time, depending on memory access, cache hits, pipeline stalls and many other factors. This can cause performance counter events to be attributed to the wrong instructions, making precise performance analysis difficult or impossible. Some recently proposed

power management [16] approaches use MPC-based control model, which is derived from cluster level or large scale data centers level power management, such as SHIP [33], DEUCON [39], [15] and [16]. They make an assumption that the actual execution times of real-time tasks are equal to their estimated execution times, and their online-predictive model will cause significant error in spiky cases due to slow-settling from deviation. Moreover, their control architecture allows degraded performance since they do not include the performance metrics into the feedback. [35] tries to satisfy QoS-critical systems but their assumption is maintaining the same CPU utilization in order to guarantee the same performance. However, this is not true for the CPU unrelated works, such as the data-intensive or I/O-intensive workloads. Rule-based control theory [40] is widely used in machine control [41, 42], which incorporating the precise logic and approximation reasoning into the system design and obtaining much more accurate representations. More specifically, Rule-based control logic can be viewed as an attempt at formalization of the remarkable human capabilities. It is not "fuzzy" but a precise logic of imprecision and approximate reasoning with four distinguish features, which are graduation, granulation, precisiation and the concept of a generalized constraint [44]. It also reduces the development time/cycle, simplifies design complexity as well as implementation, and improves the overall control performance [43].

## Reliability Analysis in Storage systems

### Copyset replication

Copysets [46] replication technique is proposed to reduce the data loss frequency by introducing an near optimal trade off between number of nodes on which the data is scattered and the possibility of data loss. The problem is defined by several parameters R,N,S, which stand for number of replicas, number of nodes and the scatter width respectively. There are two phases of the copyset application technique which are permutation and replication. The first phase refers to an offline

activity that creates a number of permutations by randomly permuting the nodes into the system. The second phase executes when a chunk needs to be replicated. The number of permutation is depends on scatter width S, which is equal to S/(R-1). The primary replica can be placed on any node of the system, while others are placed on the nodes of a randomly chosen copyset that contains the first node. This design provides an optimal tradeoff between the scatter width and the number of copysets. Comparing with random replication method, copysets is able to reduce the probability of data loss form 99.99% to 0.15% under power outage in a 5000-node RAMCloud cluster.

#### Random and shifted declustering approach

Recently, A general multi-way replication-based declustering scheme has been widely used in enterprise large-scale storage systems to improve the I/O parallelism. Specifically, a random replication method [48] is widely used in large-scale storage systems due to its simple replication technique and strong protection against uncorrelated failures. Unfortunately, its high data loss rate and poorly handling of common correlated failures make the random replication method lose its generality in large-scale storage systems. There is also another copyset replication method [46] that has been proposed to obtain lower data loss frequency. Although the copyset replication technique is able to greatly reduce the probability of data loss, however it is trades off the data loss frequency with the amount of lost data in each incident, thus reliability issue remains a main concern. To improve the system reliability, a placement-ideal data layout–Shifted declustering [80] has been created to obtain optimal parallelism in wide variety of configurations and load balancing in both fault-free and degraded modes.

## Muti-way Replication

RAID is first introduced in the mid 80's for improving both the performance and reliability of storage systems by providing redundancy through replication or parity schemes. RAID-1 applies mirroring, the simplest policy for replication based redundancy. Declustered layout schemes for replication based disk arrays include chained declustering [67], group-rotational declustering [58], and interleaved declustering [59]. Among them, chained declustering can be generalized to multi-way replication, but to the best of our knowledge, no such implementation exists. Group-rotational declustering is used in media streaming servers configured with 3-way replication to improve the quality of Video On Demand services [57]. Interleaved declustering is difficult to leverage up to multi-way replication. shifted declustering is a scalable solution for multi-way replication storage over any number of disks achieving optimal parallel performance [80].

Due to the availability benefits and the ease of maintenance, the switch from parity to multi-way replication is being further encouraged by the wide adoption by such mission critical systems as Google's File System (GFS) [62], Amazon's Dynamo [60] used to power Amazon.com and Amazon's S3 service, Microsoft's FARSITE [54], projects using Apache's Hadoop File System (HDFS) [48], video on demand services [57], and Geographic Information Systems (GIS) [74].

There are also theoretical methods for replica distribution in a large data cluster. RUSH [66] was introduced for the replica placement issues in large distributed storage systems. RUSH is a family of algorithms that have excellent randomization performance and low conflict probabilities, so it can be used in distributed storage systems which allowed each node to distribute data objects. To-sun compared a series replicated declustering schemes for spatial data systems such as GIS, where majority queries obey some explicit patterns [74], for example, range queries cover a geometric shape of a spatial data set. However, decentralized systems have not been used in reality. Current enterprise systems such as the Google File System [62], are still centrally controlled due to the

ease of maintenance.

### Existing Reliability Models

Xin et al. [78, 79] analyzed the reliability in terms of MTTDL (mean time-to-data-loss) of largescale distributed storage systems configured with two-way and three-way replication. They apply Markov chains, where the state represents the failed number of data objects in a single redundancy group<sup>1</sup>. This model is based on the assumption that the data objects are independent, as well as redundancy groups. With this assumption, it makes sense to only model one redundancy group is enough, and if at time t, the reliability of one redundancy group is R(t), then the reliability of the whole system is simply  $1 - (1 - R(t))^r$ , where r is the number of redundancy groups in the system. In this model, single data object failure should be allowed. However, they take disk failure rate as the data object failure rate. With this failure rate, all data objects on a disk fail when the disk fails, accordingly the failure of data objects are no longer independent, and it is contradictory to the assumption. As long as the events of disk failure exist, it is not reasonable to view the redundancy groups as independent. We will also explain that disk failure is the dominant factor rather than data block failure to evaluate the impacts of data layouts on system reliability in Section 4. Gafsi et al. applied continuous time Markov chains (CTMC) to model the reliability of distributed video servers [61]. Their analysis is based on parity redundancy and two-way replication redundancy. They categorized the redundancy schemes into one-to-one, one-to-all and one-to-some, where oneto-all and one-to-some are declustering layout policies.

Currently, there is no systematic research on the reliability issues for redundancy systems with multi-way replication. Among reliability metrics, the most straightforward one to understand is

<sup>&</sup>lt;sup>1</sup>For replication based redundancy, a *redundancy group* includes all copies of a data unit. For parity based redundancy, a redundancy group includes all data stripe units as well as parity units of a data stripe.

the failure free period, during which the system provides services without any data loss.

# CHAPTER 3: MAR: A NOVEL POWER MANAGEMENT SCHEME FOR CMP SYSTEMS IN DATA-INTENSIVE ENVIRONMENT

#### Learning Core's Behaviors

In this section, we exploit the behaviors of each core in a CMP processor to learn the relationship between power consumption, performance, and frequency settings, as shown in Figure 3.1. As widely shown in previous works, CPU power consumption and performance are both highly related to CPU frequency [5], [19]. Our experiment results demonstrate that there exist a cubic relationship between power consumption and CPU frequency which is well documented and shown in Figure 3.1. However, the relationship between performance and frequency is difficult to be modeled: the same frequency setting may result in a different response time (rt) or execution time (et) for various types of applications. Hence, the performance is related to both the processor's frequency and the workload characteristics. On the other hand, the behavior of the CPU is able to illustrate the characteristics of the running workloads. More specifically, each core in a CMP has seven working statuses, which we denote as the "metrics" in the rest of this work:

- user: normal processes executing in user mode;

- nice: niced processes executing in user mode;

- system: processes executing in kernel mode;

- idle: idle times;

- I/O wait: waiting for the I/O operations to complete;

- irq: servicing interrupts;

• softirq: soft servicing interrupts;

Figure 3.1: The relationship between CPU's frequency, power consumption and performance

The duration of the cores seven statuses completely exhibit the composition of the running workload. As a result, the performance is determined by a function F with considering both of the CPU frequency and the workload characteristic. Since the workload can be formulated using  $\phi$  which is a function of the seven working statuses, the system performance can be present in Equation (4.9).

$$et = F(frequency, workload)$$

$$= F\{f, \phi(metrics)\}$$

$$= F\{f, \phi(user, nice, sys, idle, iowait, irq, softirq)\}$$

(3.1)

We launch various applications on our testbed to learn the curve of Equation (4.9), e.g. an I/O bomb from Isolation Benchmark Suite (IBS) [22], a gcc and a mcf benchmark from SPEC CPU2006 suite version 1.0 [23], and TPC-C running on PostgreSQL [24]. I/O bomb uses the IOzone benchmark tool to continuously read and write to the hard disk (by writing files larger than main memory to ensure that it is not just testing memory); mcf is the most memory bound benchmark in SPEC CPU2006 while gcc is a CPU-intensive application, as shown in Table 3.1. TPC-C is a standard On-Line-Transaction-Processing (data-intensive) benchmark. The configuration details of these benchmarks could be found in Section 3. We run these tests on a Quad-Core Intel Core2 Q9550 2.83 GHz processor with 12MB L2 cache and 1333 MHz FSB. The CPU supported frequencies are 2.0 GHz, 2.33 GHz, and 2.83 GHz.

Figure 3.2: Overall execution time of different workloads

## Per-Core

Because we are using per-core level DVFS for power management, it is necessary to understand the meanings of the 7 statuses of each single core. In previous works, the relationship between CPU behavior and estimated performance *et* is simply determined by the CPU busy/idle (B-I) time [14], [25]. This B-I model is defined as Equation (3.2):

$$et_{new} = et_{old} * \left(\frac{P_{busy} * f_{old}}{f_{new}} + P_{idle}\right)$$

$$P_{busy} = \frac{\left(\frac{rt_{new}}{rt_{old}} - P_{idle}\right) * f_{new}}{f_{old}}$$

(3.2)

where  $P_{busy}^{1}$  is the busy ratio of CPU while  $P_{idle}$  is the idle percentage of CPU;  $f_{old}$  and  $f_{new}$  are the two version of CPU frequency settings. We first enable only one core in the CMP processor and assign one process to run the benchmarks, so that we can avoid the noise from task switches among the cores. The upper two charts in Figure 3.2 illustrates that for the first two workloads, e.g. gcc (CPU-intensive) and mcf (memory-intensive), the B-I model is accurate enough with less than 3% deviation. However for the I/O intensive or data-intensive workloads, e.g. I/O bomb and TPC-C showing in the lower two charts in Figure 3.2, using the B-I model which does not consider the I/O impact will result in up to 39.6% modeling errors. The reason that B-I model works well for CPU-intensive and memory-intensive workloads is because of Instruction-Level Parallelism (ILP). The latency caused by cache misses, and mis-predictions will be eliminated by advancing the future operations. However, ILP is not always capable of eliminating the latency caused by I/O operations [3], which leads to the prediction errors for I/O bomb and TPC-C benchmarks.

We also show the statistics of the 3 main working statuses in Figure 3.3. For gcc and mcf, most of the execution time is in user mode; the cache misses and mis-predictions of mcf have negligible impact on the CMP's behavior due to ILP. For I/O bomb, I/O wait is the main latency; for dataintensive benchmark TPC-C, the lower frequency will hide some of the I/O wait latency because of ILP, but the latency in both user and iowait modes cannot be ignored. For all four cases, the irq and softirq latency are very small which only constitute about 0.2% of the total working status. Therefore, irq and softirq will not be taken into account in our experiments since the latency cause by them cannot affect the overall system performance comparing with other major latency. As a result, "user+nice+sys", "idle" and "I/O wait" are the three most important working statuses which could describe the CMP's behavior in general. Without considering I/O wait latency, the basic B-I model may result in non-trivial modeling errors for data-intensive or I/O intensive applications.

<sup>&</sup>lt;sup>1</sup>The "Busy Time" in previous works is usually calculated as the equation of *overall/timeidle/time* without the consideration of the cores other metrics [14], [25].

Table 3.1: Cache Miss Rate

| Benchmarks | L1 Data Miss | L2 Miss | Mispredictions |

|------------|--------------|---------|----------------|

| gcc        | 14.21        | 3.17    | 5.11           |

| mcf        | 130.15       | 36.73   | 15.79          |

Figure 3.3: Core's major statistics under different workloads

# Multi-Core

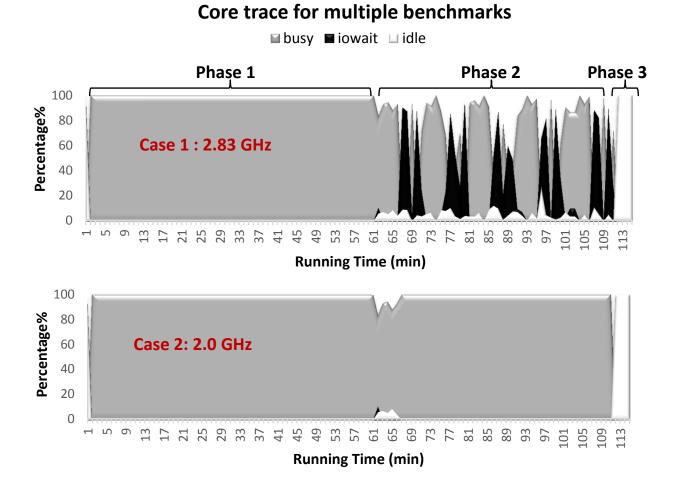

Because of the job scheduler in a CMP processor, one task in CMP processor may be switched among the cores during its run. In order to show whether this core-level task switches can eliminate the I/O wait latency, we run 7 processes on all 4 cores in our testbed. Each process will randomly run one of the following benchmarks: gcc, mcf, bzip2, gap, applu, gzip and TPC-C. Each core has 3 available frequency settings: 2.83 GHz, 2.33 GHz and 2.0 GHz.

Figure 3.4: The trace of core0 under both high and low frequency; the overall execution times are comparable for the two cases.

Figure 3.4 shows the traces for core0 under different frequency settings. We omit "irq" and "softirq" based on the results of section 3, and we treat "user, nice, sys" as a group denoting the real "busy" status. When the frequency is 2.83 GHz, all the workloads are processed in parallel in "phase 1"; the I/O wait latency could be hidden by the process-level parallelism. However in "phase 2", when there are not enough available processes to schedule, the I/O wait latency will emerge. After all processes are finished, the core will stay idle in "phase 3". The traditional B-I based power management scheme is only able to discover the chances to save power in "phase 3" by lowering the processor's voltage and frequency. However in fact, "phase 2" also provides opportunities to save more power. In this case, we can lower the frequency in order to parallel the CPU and I/O operations as much as possible.

Figure 3.5: Two cases when I/O wait exits

In Case 2, as shown in the lower part of Figure 3.4, we can use "2.0 GHz" to process all the workloads roughly at a comparable execution time while only consumes 35.3% power as compared to the Case 1 that runs at the 2.83 GHz frequency. We note that heavy disk utilization may not

necessarily result in I/O wait if there are enough parallel CPU-consuming tasks. Interestingly, the new data-intensive analyses and applications will incur long I/O wait latency [18, 26, 27, 28, 29]. As a result, I/O wait still needs to be taken into account in the big data era.

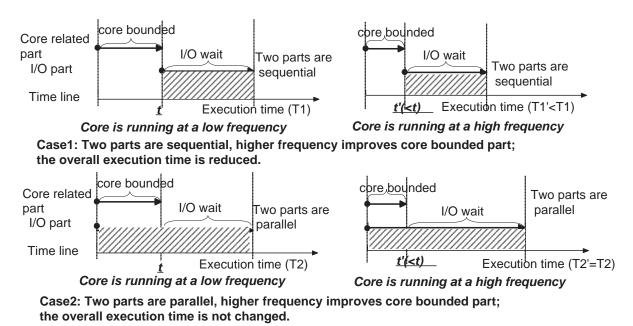

#### Analysis and Preparation for MAR Design

Although the I/O wait is the duration that the processor is waiting for the I/O operation to be finished, we cannot simply consider it as a sub-category of the idle time. Since if and only if CPU idle time exists, increasing the CPU frequency will linearly decrease the execution time. However, when I/O wait is present, there are two cases as shown in Figure 3.5. In Case 1 where the CPU-consuming tasks and I/O tasks are running asynchronously or blocking each other [30], the traditional B-I method can be utilized (discussed in Section 3) to model the relation between execution time and CPU frequency. In Case 2 where the two types of workloads are running in parallel but not well aligned, using the B-I model to scale CPU frequency will not affect the overall execution time. In other words, the traditional "B-I" model will not work precisely under this situation. In order to distinguish these two cases, we introduce two thresholds which are " $th_{up}$ " and " $th_{down}$ ". " $th_{up}$ " stands for the CPU scaling up threshold, and the " $th_{down}$ " stands for the CPU scaling down threshold. With their help, we can quantify the Equation (4.9) as the following Equation (3.3). In the Case 1, the core is either in busy-dominate ( $\omega < th_{up}$ ) or in idle-dominate  $(\omega > th_{down})$ , thus the traditional B-I model can be utilized. In the Case 2, the core is neither in busy nor in idle status, thus scaling the CPU frequencies will not affect the overall execution time. Therefore, the ratio of  $\frac{rt_{new}}{rt_{old}}$  will be set to "1".

$$if \omega > th_{down} \text{when scaling down:}$$

$$P_{busy} = \frac{\left(\frac{rt_{new}}{rt_{old}} - P_{idle}\right) * f_{new}}{f_{old}}$$

$$Case2: \quad Otherwise:$$

$$P_{busy} = \frac{\left(1 - P_{idle}\right) * f_{new}}{f_{old}}$$

$$(3.3)$$

where  $P_{busy}$  represents the busy ratio; rt stands for response time;  $P_{idle}$  means the idle ratio. The default value of " $th_{up}$ " and " $th_{down}$ " are based on our comprehensive experimental results. Note that these two thresholds are affected by the throughput of I/O devices, L1/L2 cache hit rates, network traffic, etc.. A self-tuning strategy for these two thresholds will explain in detail in Section 3. Equation (3.3) can be used to complete the relationship among performance, frequency and the various types of workloads that we try to present in Figure 3.1. Our rule-based power management controller MAR will be designed according to the two relationships in Equation 3.3.

$Case1: if \omega < th_{up}$  when scaling up OR

#### MAR's Design

In this section, we introduce the design, analysis, and optimization of our rule-based power management approach. In previous sections, we explain why I/O wait should be considered into powermanagement. One challenge is, when considering the I/O wait, the CPU workload will become unpredictable due to the I/O randomness. Therefore, the short sampling period that used to work well for the DVFS control might cause severe problems to the system, such as instability and noise. To attack this problem, we need to prolong the sampling period but not significantly stretch the response time under the variation of CPU utilization. There is a need for incorporating a thorough understanding of the control object and control system into MAR system design. Interestingly, a fuzzy logic control method is an ideal candidate solution here as it utilizes human's experience as input and enforce a precise logic in the control system to reflect the thorough understanding.

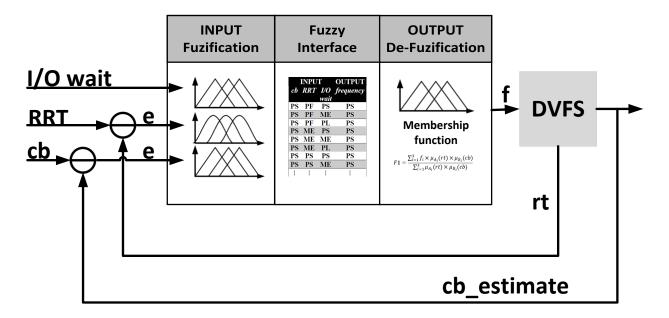

#### MAR Control model

The fuzzy logic has been used as the main base for the MAR's design, which includes fuzzification, rules evaluation and defuzzification. MAR is designed as a MIMO controller shown in Figure 3.6. In order to demonstrate that our control efficiency is better than any other control methods, we divide our control algorithm into two parts. In the first part, the I/O wait is not taken into account in order to prove that, the outcome of our control algorithm is more precise and the response time is faster. Secondly, as we define that the I/O wait is critical for power-saving strategy especially when running data-intensive tasks. Thus, I/O wait would be considered in the second part to show that our new "B-W-I" model can work accurately and efficiently. By introducing the I/O wait, Equation 3.3 can be further updated in the following equation (3.4):

$$\begin{array}{ll} Case1: & if \omega < th_{up} \text{when scaling up OR} \\ & if \omega > th_{down} \text{when scaling down:} \\ & cb = \frac{\left(\frac{rt}{RRT} - P_{idle}\right) * f_{new}}{f_{old}} \\ Case2: & Otherwise: \\ & cb = \frac{\omega * f_{new}}{f_{old}} \end{array} \tag{3.4}$$

where  $\omega$  stands for the I/O wait ratio. Let *SP* denote the sampling period, *RRT* means the required response time, which is a key factor used to determine whether the system performance has been achieved, *cb* is core boundness of the workloads (the percentage of core's busy time compared with

the sample time),  $\omega$  is I/O wait ratio and *ecb* is the tracking error of core boundness. One basic control loop is described as follows: at the end of each *SP*, *rt*, *cb*, and  $\omega$  vectors will feed back into the controller through an input interface. It should be noted that *rt*, *ecb*, and  $\omega$  could be directly measured from last *SP*. These inputs will be processed into the arguments  $P_{busy}$ ,  $\omega$ , *rt<sub>new</sub>* and *rt<sub>old</sub>* of the Equation (3.3) or Equation (3.4) based on whether the I/O wait has been taken into account or not. Now we show how to calculate the arguments.

#### Fuzzification without consideration of I/O wait

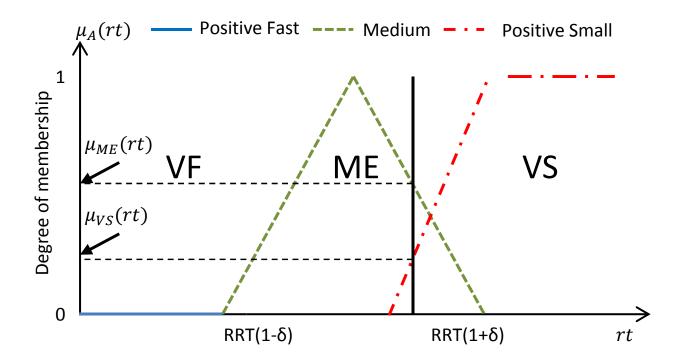

We first fuzzify the input values of cb and rt by performing a scale mapping using membership function to transfer the range of crisp values into the corresponding universe of discourse. The universe of discourse means linguistic terms especially in Fuzzy Logic, such as "PS", "ME" and "PL" represent for "positive short", "moderate" and "positive large" respectively. Membership function represents the degree of truth as an extension of valuation. The response time rt is one input of the system that used to determine the performance of the controller. In order to set a performance constraint, we denote  $0 < \delta < 1$  as the user-specified performance-loss constraint. We are using the symmetric triangular membership function that presented in Equation (3) for mapping between crisp value and linguistic terms. The reason that we apply a linear transformation to the response time is we have a specified minimum and maximum value in this case. Equation (3) present the membership function and Figure 3.7 plot of the function of rt.

$$\mu_A(rt) = \begin{cases} 1 - \frac{rt - RRT}{RRT * \delta} & \text{,if} \mid rt - RRT \mid \leq RRT * \delta \\ 1 & \text{,if} rt > RRT(1 + \delta) \\ 0 & \text{,Otherwise} \end{cases}$$

(3.5)

where A stands for the fuzzy set of response time, which including {PF, ME, PS} stands for positive fast, medium and positive small. For each crisp value of response time, we can compute a set of  $\mu$  that can be used in the defuzzification step by applying certain rules.

Figure 3.6: The architecture of MAR power management

Secondly, we fuzzify another input variable core boundness using Gaussian membership function because it transforms the original values into a normal distribution, which creates a smooth transformation rather than the linear functions. On the other hand, since the value of core boundness changes frequently, using Gaussian membership function can achieve the higher chances to detect the fluctuation and response accordingly. Equation (3.6) is the Gaussian membership function that used to map the crisp values for core boundness and Figure 8 shows the plot of the mapping.

$$\mu_B(cb) = \exp\left[-\frac{1}{2}\left(\frac{cb-cb_0}{\sigma}\right)^2\right]$$

(3.6)

Figure 3.7: Mapping results for response time using Triangular Membership Function

Where B represents the fuzzy set of core boundness that including {PS, ME, PL} represent "Positive Small", "Medium" and "Positive Large";  $cb_0$  is the position of the peak relative to the universe and  $\delta$  is the standard deviation. Figure 3.8 show that if we have a crisp value of core boundness falls between 0.4 and 0.5, we can calculate the degrees under each element of the fuzzy set.

#### Fuzzification with consideration of I/O wait

In the section, we will focus on the fuzzification of I/O wait. As we mentioned above, there are two thresholds in Section 3 that have been introduced to distinguish the parallelism of I/O wait and core boundness. Therefore, these two thresholds will be used as the minimum and maximum value for the mapping by utilizing symmetric triangular membership function. Equation (7) shows the relationship between crisp values and the membership degrees and Figure 3.9 present the plot

accordingly.

$$\mu_{C}(\omega) = \begin{cases} 1 - \frac{\omega - (th_{down} + th_{up})/2}{(th_{up} - th_{down})/2} & , \text{if} th_{down} < \omega < th_{up} \\ 1 & , \text{if} \omega > th_{up} \\ 0 & , \text{Otherwise} \end{cases}$$

(3.7)

where C represents the fuzzy set of I/O wait that including {PS, ME, PL} represent "Positive Small", "Medium" and "Positive Large";  $th_{up}$  and  $th_{down}$  denote for the two thresholds.

Figure 3.8: Mapping results for core boundness using Gaussian Membership Function

Figure 3.9: Mapping results for I/O wait using Triangular Membership Function

# Fuzzy Rules

In this section, we propose a set of rules for MAR which will guide MAR to find the frequencies to be set in next Sampling Period. The fuzzy rules can be presented in the following two tables, which are Table 3.2 and Table 5.2. The Table 3.2 is about the fuzzy rules without considering I/O wait, which aims at demonstrating that our MAR control method works better than other existing control approaches.

| INP            | OUTPUT        |           |

|----------------|---------------|-----------|

| core boundness | Response time | frequency |

| PS             | PF            | PS        |

| PS             | ME            | PS        |

| PS             | PS            | ME        |

| ME             | PF            | PS        |

| ME             | ME            | ME        |

| ME             | PS            | ME        |

| PL             | PF            | PS        |

| PL             | ME            | ME        |

| PL             | PS            | PH        |

Table 3.2: Fuzzy Rule Base(Part I)

Table 5.2 presents a set of fuzzy rules by taking I/O waits into account. The following paragraph provides a detailed explanation showing the procedure of generating the rules.

First, if  $RRT(1 + \sigma) \le rt \le RRT(1 + \sigma)$ : This is the ideal case from a performance perspective. Traditional solutions may not change the core's frequency setting. However MAR will do a further check whether  $\omega > th_{down}$ .

- If so, the frequency could be scaled down to a lower level to save more power without affecting the response time *rt*.

- If not, scaling the frequency will result in different response time *rt*, which is deviated from RRT. In this case, MAR will keep using the current frequency.

Secondly, if  $rt > RRT(1 + \sigma)$ : This means the real response time does not meet the requirement, MAR checks whether  $\omega > th_{up}$ .

• If  $\omega$  exceeds the scaling up threshold, changing to higher frequency will not improve the performance. Moreover, higher frequency will result in a higher I/O wait, which is a waste

of core resources. As a result, MAR will keep the current frequency setting.

• If  $\omega$  is within the threshold, a higher core frequency could improve response time rt in this case.

Finally,  $rt < RRT(1 - \sigma)$ : If the measured response time is unnecessarily better than the requirement, there is a chance to scale the frequency down to save more power.

- If ω > th<sub>down</sub>, MAR will only scale down the core frequency by one level. The reason for this "lazy" scaling is because it is difficult to know what ω will be when using one level lower frequency. The new ω decides whether we should further scale down the frequency or not.

- If ω ≤ th<sub>down</sub> we may be able to scale down the core frequency to just meet the performance requirement while saving more power.

#### Centroid Defuzzification method

As we introducing two different kinds of membership functions which are triangular and Gaussian. There are also exist two types of centroid defuzzification methods. In the previous paragraph we present two fuzzification approaches for our MAR controller, with the difference in whether considering I/O wait or not. Equation (4.4) and Equation (3.9) were generated to deal with these two cases by using two kinds of defuzzification solutions.

$$F1 = \frac{\sum_{i=1}^{3} f_i * \mu_{Ai}(rt) * \mu_{Bi}(cb)}{\sum_{i=1}^{3} \mu_{Ai}(rt) * \mu_{Bi}(cb)}$$

(3.8)

(3.9)

$$F1 = \frac{\sum_{i=1}^{3} f_i * \mu_{Bi}(\sum_{i=1}^{3} min[\mu_{Ai}(rt), \mu_{Ci}(\omega)])}{\sum_{i=1}^{3} \mu_{Bi}(\sum_{i=1}^{3} min[\mu_{Ai}(rt), \mu_{Ci}(\omega)])}$$

where  $f_i$  stands for the center of CPU frequencies. In our case,  $f_i = 2.0, 2.33, 2.83$ . Through Equation 4.4 and Equation 3.9, we are able to defuzzify the linguistic values that obtained in the output of the rule table by incorporating the various membership degrees. The output results will fall into three intervals which are 0 - 2.0 GHz, 2.0 - 2.33 GHz and 2.33 - 2.83 GHz. Since the CPU only supporting 3 DVFS levels, the value below the first interval will automatically set to 2.0 GHz, otherwise, MAR will decide which frequency level will be set based on the output of the rule table. For example, if linguistic term of the output frequency says "PB", 2.83 GHz would be set for the next sampling period.

# Self-tuning Strategy

There are several factors affecting the thresholds  $th_{up}$  and  $th_{down}$ , for example:

- Throughput of I/O devices. Higher I/O throughput means the same amount of data could be transferred in less "I/O wait" jiffies. As a result, the thresholds will become higher because the core needs more I/O wait jiffies to reach the time boundary, which defines whether core bounded part or I/O part is the determinant in execution time.

- on-chip L1/L2 cache hit rate. Lower cache hit rate results in higher memory access, which is much slower than cache access. Therefore, the overall processing speed of the core bounded part (including both cache and memory access) becomes slower.

| INPUT          |               |          | OUTPUT    |  |

|----------------|---------------|----------|-----------|--|

| Core boundness | Response time | I/O wait | frequency |  |

| PS             | PF            | PS       | PS        |  |

| PS             | PF            | ME       | PS        |  |

| PS             | PF            | PL       | PS        |  |

| PS             | ME            | PS       | PS        |  |

| PS             | ME            | ME       | PS        |  |

| PS             | ME            | PL       | PS        |  |

| PS             | PS            | PS       | PS        |  |

| PS             | PS            | ME       | PS        |  |

| PS             | PS            | PL       | PS        |  |

| ME             | PF            | PS       | PS        |  |

| ME             | PF            | ME       | PS        |  |

| ME             | PF            | PL       | PS        |  |

| ME             | ME            | PS       | PS        |  |

| ME             | ME            | ME       | PS        |  |

| ME             | ME            | PL       | PS        |  |

| ME             | PS            | PS       | ME        |  |

| ME             | PS            | ME       | ME        |  |

| ME             | PS            | PL       | PS        |  |

| PL             | PF            | PS       | PS        |  |

| PL             | PF            | ME       | PS        |  |

| PL             | PF            | PL       | PS        |  |

| PL             | ME            | PS       | ME        |  |

| PL             | ME            | ME       | ME        |  |

| PL             | ME            | PL       | PS        |  |

| PL             | PS            | PS       | PH        |  |

| PL             | PS            | ME       | ME        |  |

| PL             | PS            | PL       | PS        |  |

Table 3.3: Fuzzy Rule Base(Part II)

- 3. The noise in I/O wait, such as network I/O traffic file system journaling, paging swapping, etc.

- 4. Heat and heat dissipation. When processors run too hot, they can experience errors, lock, freeze, or even burn up. It is difficult to predict the thresholds in this case; hence we adopt

self-tuning methods based on the observed system behaviors. The self-tuning strategies are listed below:

When rt > RRT(1+σ), ω ≤ th<sub>up</sub>, in this case, the RRT is not met and the frequency need to be scaling up for improving the performance. However, if the rt<sub>new</sub> after the frequency scaling is same as the rt in last sampling period, we need to adjust it lower by Equation (3.10):

$$th_{up_new} = th_{up_old} - \frac{\omega}{2} \tag{3.10}$$

When rt < RRT, in this case, the RRT is met and the frequency may be scaled based on the rules presented in Section 3. Thus, if ω ≤ th<sub>down</sub>, RRT is over met and the frequency need to be scaled down, the th<sub>down</sub> also need to be adjusted to a lower level. Else if ω > th<sub>down</sub>, RRT is over met and rt<sub>new</sub> is changed which means ω should be lower than th<sub>down</sub>, hence we set th<sub>down</sub> to a higher level. Equation (3.11) can be used to set th<sub>down</sub> either to a higher or lower level.

$$th_{down_new} = th_{down_old} + \frac{\omega}{2} \tag{3.11}$$

#### Methodology

In this section, we show our experimental methodology and benchmarks, as well as the implementation details of each component in our MAR controller.

#### Processor

We use a Quad-Core Intel Core2 Q9550 2.83GHz processor, with 12 MB L2 cache and 1333MHz FSB. The four execution cores are in four sockets. We change the DVFS levels of the 4 cores in each group together in order to have a real impact on the processor power consumption. Each core in the processor supports 3 DVFS levels: 2.0 GHz, 2.33 GHz and 2.83 GHz. The operating system is Ubuntu 12.04.3(LTS) with Linux kernel 3.8.13. For the extended experiment in Section 3, we use an Intel(R) Core(TM) 6700 2.66 GHz processor with two execution cores. Each core in the processor supports 5 DVFS levels, which are 1.33GHz,1.6GHz, 2.0GHz, 2.33GHz and 2.66GHz respectively. The operation system is Ubuntu 12.04.3(LTS) with Linux kernel 3.8.13.

#### Benchmark

We use 3 stress tests (CPU-bomb, I/O-bomb, and memory-bomb) from Isolation Benchmark Suite [22]; SPEC CPU 2006 suite version 1.0 [23], and data-intensive benchmark: TPC-C running on PostgreSQL [24]. TPC-C incorporates five types of transactions with different complexity for online and deferred execution on a data-base system. Every single transaction consists of computing part and I/O part. Due to the database buffer pool, the updating records will not be flushed until the pool is full.

# Core Statistics

Various information about kernel activities are available in the /proc/stat file. The first three lines in this file are the CPU's statistics, such as usr,nice,sys,idle,etc.. Since we using the 3.8.13 version of Linus, the file includes three additional columns: iowait, irq, softiqr. These numbers identify the amount of time that the CPU has spent on performing different kinds of work. Time units are in

USER\_HZ or Jiffies. In our x86 system, the default value of a jiffy is 10*ms*, or 1/100 of a second. MAR needs to collect core boundness information as well as I/O wait latency. Each core's boundness is the sum of the jiffies in user, nice and sys mode divided by the total number of jiffies in last SP. Similarly, I/O wait latency is calculated based on the iowait column. The way to measure the real-time response time depends on the benchmarks. In Isolation Benchmark, the response time could be monitored by the I/O throughput. In TPC-C, the primary metrics, transaction rate (tpmC), could be used as the response time. However for SPEC CPU2006 benchmarks, it is difficult to find any metrics to denote response time because there is no "throughput" concept. Our previous experiments in Figure 2 show that these CPU-intensive and memory-intensive benchmarks have roughly linear relationships with core frequency. Hence we can calculate the number of instructions have been processed in the sampling period by multiplying the CPU time (first three fields in /proc/stat file) and the core frequency. The result could be used as the response time metrics.

### **DVFS** Interface

We enable the Intel's SpeedStep on BIOS and use cpufreq package to implement DVFS. When using root privilege, we can echo different frequencies into the system file /sys/devices/ system/cpu/cpu[X]/cpufreq-scaling\_setspeed, where [X] is the index of the core number. We test the overhead of scaling CPU frequencies on our platform, which is only 0.08 milliseconds on average.

#### **Power Estimation**

We measure the processor's power consumption by connecting two multi-meters into the circuit, as shown in Figure 3.10. Specifically, as the processor is connected by two +12V CPU 4 pin cables, we put one multi-meter in each cable to test the amperage (A). On the other side, the

Agilgent IntuiLink software logged data into the logging server using Microsoft Excel. After we collecting the measured amperage based on the sampling period, we are able to compute the average amperage accordingly, such that we could obtain the energy by multiplying the voltage, amperage as well as the time duration.

Figure 3.10: The Measurement setup: two multimeters are inserted between the power supply and CPU

#### **Baseline Control Methods**

PID controller [32] is a control loop feedback mechanism widely used in industrial control systems. A PID controller calculates an error value as the difference between a measured process variable and a desired setpoint. Model predictive control (MPC) [33] is an advanced method of process control that has been widely used in the process industries. It relies on dynamic models of the process, most often linear empirical models obtained by system identification. LAST [9] is the simplest statistical predictor, which assumes the next sample behavior is identical to its last seen behavior. Relax [25] is an algorithm which predicts the workload using both history values and run-time profiling.

#### Experiments

First, MAR is compared with four other baselines to illustrate the high responsiveness of MAR. Second, MAR is used to do the power control for different types of workloads, including CPUintensive, memory-intensive and I/O-intensive benchmarks. The purpose is to show MAR's performance under specific environment. Third, we compare the two versions of MAR (with/without considering I/O wait) by running data-intensive benchmarks, in order to highlight the impact of I/O wait in power management schemes. After that, we compare the overall efficiency of MAR and the baselines. In order to demonstrate MAR's efficiency in power management, we also compare MAR with conventional Linux governors solution (Ondemand). At the end, we briefly evaluate the overhead of our power management schemes.

#### Fast Responsiveness