University of Central Florida

Electronic Theses and Dissertations, 2004-2019

2009

# Adaptive Efficiency Optimization For Digitally Controlled Dc-dc Converters

Wisam Al-Hoor University of Central Florida

Part of the Electrical and Electronics Commons Find similar works at: https://stars.library.ucf.edu/etd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS Citation**

Al-Hoor, Wisam, "Adaptive Efficiency Optimization For Digitally Controlled Dc-dc Converters" (2009). *Electronic Theses and Dissertations, 2004-2019.* 4006. https://stars.library.ucf.edu/etd/4006

# ADAPTIVE EFFICIENCY OPTIMIZATION FOR DIGITALLY CONTROLLED DC-DC CONVERTERS

by

WISAM M. AL-HOOR

B.S. Princess Sumaya University for Technology, 2002 M.S. University of Central Florida, 2006

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the School of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Summer Term 2009

Major Professor: Issa Batarseh

© 2009 Wisam M. Al-Hoor

#### ABSTRACT

The design optimization of DC-DC converters requires the optimum selection of several parameters to achieve improved efficiency and performance. Some of these parameters are load dependent, line dependent, components dependent, and/or temperature dependent. Designing such parameters for a specific load, input and output, components, and temperature may improve single design point efficiency but will not result in maximum efficiency at different conditions, and will not guarantee improvement at that design point because of the components, temperature, and operating point variations.

The ability of digital controllers to perform sophisticated algorithms makes it easy to apply adaptive control, where system parameters can be adaptively adjusted in response to system behavior in order to achieve better performance and stability. The use of adaptive control for power electronics is first applied with the Adaptive Frequency Optimization (AFO) method, which presents an auto-tuning adaptive digital controller with maximum efficiency point tracking to optimize DC-DC converter switching frequency. The AFO controller adjusts the DC-DC converter switching frequency while tracking the converter minimum input power point, under variable operating conditions, to find the optimum switching frequency that will result in minimum total loss and thus the maximum efficiency.

Implementing variable switching frequencies in digital controllers introduces two main issues, namely, limit cycle oscillation and system instability. Dynamic Limit Cycle Algorithms (DLCA) is a dynamic technique tailored to improve system stability and to reduce limit cycle oscillation under variable switching frequency operation.

The convergence speed and stability of AFO algorithm is further improved by presenting the analysis and design of a digital controller with adaptive auto-tuning algorithm that has a variable step size to track and detect the optimum switching frequency for a DC-DC converter. The Variable-Step-Size (VSS) algorithm is theoretically analyzed and developed based on buck DC-DC converter loss model and directed towered improving the convergence speed and accuracy of AFO adaptive loop by adjusting the converter switching frequency with variable step size.

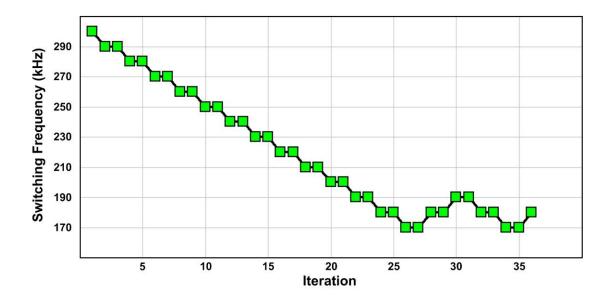

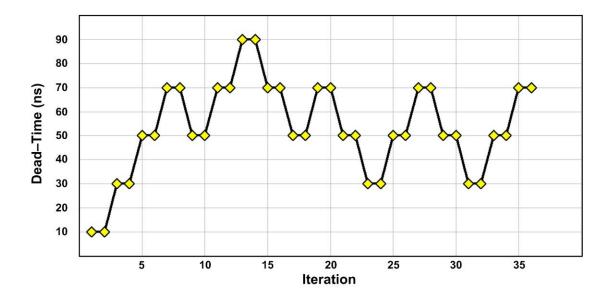

Finally, the efficiency of DC-DC converters is a function of several variables. Optimizing single variable alone may not result in maximum or global efficiency point. The issue of adjusting more than one variable at the same time is addressed by the Multivariable Adaptive digital Controller (MVAC). The MVAC is an adaptive method that continuously adjusts the DC-DC converter switching frequency and dead-time at the same time, while tracking the converter minimum input power, to find the maximum global efficiency point under variable conditions.

In this research work, all adaptive methods were discussed, theoretically analyzed and its digital control algorithm along with experimental implementations were presented. To my parents with love and gratitude.

#### ACKNOWLEDGMENTS

First, and foremost, all the praises and thanks are to Allah for his persistent bounties and blessings. Then, I would like to convey my deep gratitude and appreciation to my supervisor Dr. Issa Batarseh for his unwavering encouragement, guidance and support. I would like to express my sincere appreciation to: Dr. Wasfy Mikhael for his numerous discussions and support and Dr. Jaber Abu-Qahouq for his encouragement and thought provoking ideas that helped me in this work. Special thanks Dr. John Shen and Dr. Thomas Wu for serving on my dissertation committee and providing insightful comments and thoughts on my research.

I would like to express my sincere love and gratitude to my father Munier, my mother Huda, my lovely wife Rashaa, my brothers, Mouayad, Yazan, Anas and my sister Batool. Their love, encouragement and support have been the root of this success.

This work was partially supported by Intel Corporation.

Wisam M. Al-Hoor June, 2009

# TABLE OF CONTENTS

| LIST OF FIGURES                                                                   |

|-----------------------------------------------------------------------------------|

| LIST OF TABLES                                                                    |

| CHAPTER ONE: INTRODUCTION                                                         |

| 1.1 Background and motivation                                                     |

| 1.2 Adaptive Efficiency Optimization                                              |

| 1.3Variable Step Size auto-tuning algorithm                                       |

| 1.4 Multivariable adaptive digital controller                                     |

| CHAPTER TWO: ADAPTIVE DIGITAL CONTROLLER AND DESIGN                               |

| CONSIDERATIONS FOR A VARIABLE SWITCHING FREQUENCY VOLTAGE                         |

| REGULATOR                                                                         |

| 2.1 Introduction                                                                  |

| 2.2 Switching Frequency Effect on Losses                                          |

| 2.3 Adaptive Frequency Optimization (AFO) Digital controller                      |

| 2.3.1 Switching Frequency Minimum Increment/Decrement $f_{sw\_step}$ Selection 19 |

| 2.3.1.1 Sensitivity for conduction losses in CCM Mode:                            |

| 2.3.1.2 Sensitivity for switching (and driving) losses in CCM Mode 22             |

| 2.3.1.3 Sensitivity for conduction losses in DCM Mode                             |

| 2.3.1.4 Sensitivity for switching losses in DCM Mode                              |

| 2.3.2 $P_e$ Selection                                                             |

| 2.3.3 M Selection                                                                 |

| 2.4 Loop Gain-Phase Design Considerations                                         |

| 2.5 Limit-Cycle Considerations And Proposed Dynamic Algorithm            | 39  |

|--------------------------------------------------------------------------|-----|

| 2.6 Experimental Work                                                    | 48  |

| 2.7 Conclusion                                                           | 58  |

| CHAPTER THREE: ANALYSIS AND DESIGN OF A VARIABLE STEP SIZE               |     |

| AUTO-TUNING ALGORITHM FOR DIGITAL POWER CONVERTER WITH A                 |     |

| VARIABLE SWITCHING FREQUENCY                                             | 60  |

| 3.1 Introduction                                                         | 60  |

| 3.2 Variable Frequency Adaptive-Step-Size Algorithm and its Analysis     | 61  |

| 3.2.1 Gradient for conduction losses in CCM mode:                        | 64  |

| 3.2.2 Gradient for switching losses in CCM mode:                         | 66  |

| 3.2.3 Gradient for conduction losses in DCM mode:                        | 68  |

| 3.2.4 Gradient for switching losses in DCM mode:                         | 70  |

| 3.3 Convergence Stability and speed analysis for VSS adaptive controller | 73  |

| 3.3.1 Gradient Search using Steepest Descent Method                      | 74  |

| 3.3.2 Gradient Stability and Convergence                                 | 77  |

| 3.4 Variable Step-Size Adaptive Controller Flowchart                     | 79  |

| 3.5 Adaptive loop theoretical design and guidelines                      | 82  |

| 3.6 Proof of concept experimental results                                | 83  |

| 3.7 Conclusion                                                           | 89  |

| CHAPTER FOUR: MULTIVARIABLE ADAPTIVE EFFICIENCY OPTIMIZAT                | ION |

| DIGITAL CONTROLLER                                                       | 90  |

| 4.1 Introduction                                                         | 90  |

| 4.2 Effect of different PWM parameters on losses                         | 91  |

| 4.2.1 Switching frequency effect on lossesError! Bookmark not define | ed. |

|----------------------------------------------------------------------|-----|

| 4.2.2 Dead-time effect on losses Error! Bookmark not define          | ed. |

| 4.3 Multivariable adaptive digital controller                        | 99  |

| 4.4 MVAC Algorithm and its analysis 1                                | 03  |

| 4.4.1 Adaptive Dead-Time Optimization 1                              | 03  |

| 4.4.2 Gradient search using steepest descent method 1                | 05  |

| 4.4.3 Gradient stability and convergence                             | 07  |

| 4.4.4 Adaptive Dead-Time sensitivity analysis 1                      | 09  |

| 4.5 Experimental Results 1                                           | 11  |

| 4.6 Conclusion 1                                                     | 26  |

| CHAPTER FIVE: SUMMARY AND FUTURE WORK 1                              | 27  |

| 5.1 Summary 1                                                        | 27  |

| 5.2 Future Work 1                                                    | 30  |

| REFERENCES 1                                                         | 32  |

## LIST OF FIGURES

| Fig. 1.1: General block diagram for a digitally controlled power converter                |

|-------------------------------------------------------------------------------------------|

| Fig. 2.1: Non-isolated buck DC-DC converter with synchronous rectification                |

| Fig. 2.2: Switching and conduction power losses normalized to the total power loss vs.    |

| load current under fixed switching frequency operation for a given design                 |

| Fig. 2.3: Simulation efficiency curves vs. switching frequency: (a) DCM operation is      |

| allowed, and (b) DCM operation is not allowed (CCM only) 15                               |

| Fig. 2.4: The Adaptive-Frequency-Optimization (AFO) Digital Controller Flowchart 18       |

| Fig. 2.5: Block-diagram of a digitally controlled closed loop synchronous buck converter. |

|                                                                                           |

| Fig. 2.6: Conceptual Block-Diagram of the DPWM unit [32]                                  |

| Fig. 2.7: Digital variable switching frequency (by varying DPWM number of steps) effect   |

| in CCM mode                                                                               |

| Fig. 2.8: Digital variable switching frequency (by varying DPWM number of steps) effect   |

| in DCM mode                                                                               |

| Fig. 2.9: Dynamic Limit-Cycle controller algorithm flowchart                              |

| Fig. 2.10 (a): DPWM and ADC required resolution to avoid limit-cycle at different         |

| switching frequencies with nominal input voltage of 10V                                   |

| Fig. 2.10 (b): ADC required resolution to avoid limit-cycle at different input voltages   |

| with switching frequency = 250 kHz                                                        |

| Fig. 2.10 (c): ADC required resolution to avoid limit-cycle at different frequencies and  |

| input voltages                                                                            |

| Fig. 2.10 (d): DPWM required resolution to avoid limit-cycle at different frequencies and |

|-------------------------------------------------------------------------------------------|

| input voltages                                                                            |

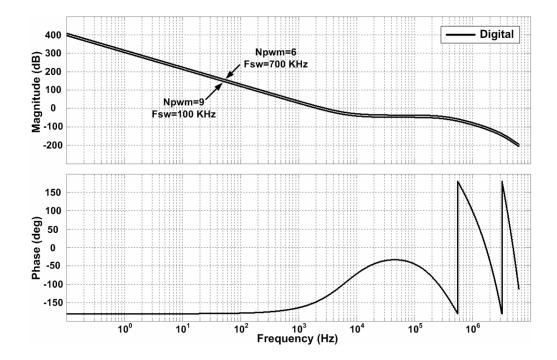

| Fig. 2.11: Bode-Plots in CCM with the DLCA controller                                     |

| Fig. 2.12: Bode-Plots in DCM with the DLCA controller                                     |

| Fig. 2.13: Complete proposed controller algorithm flowchart                               |

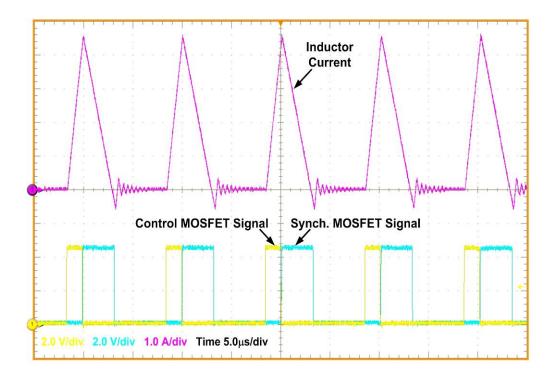

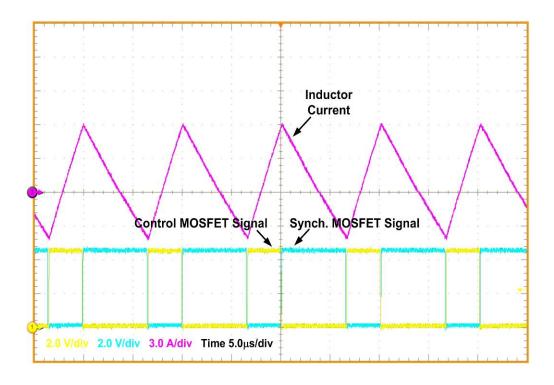

| Fig. 2.14: Experimental switching waveforms: (a) in DCM and (b) in CCM                    |

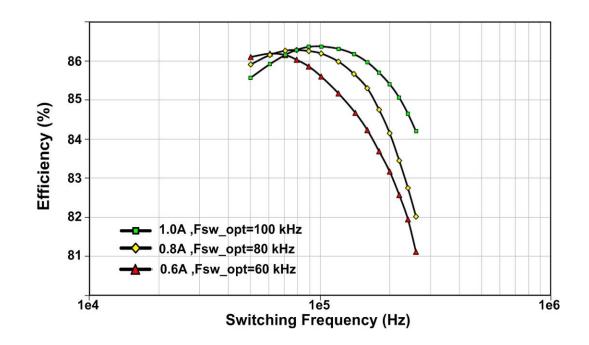

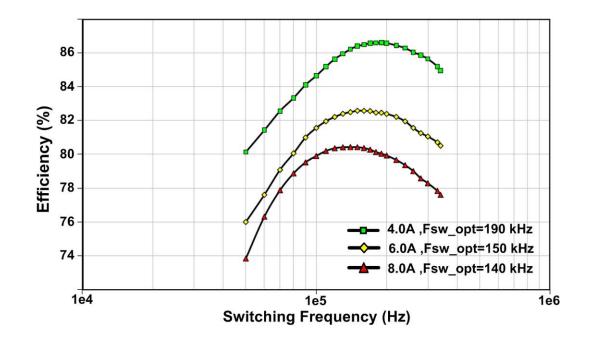

| Fig.2.15 (a): Efficiency vs. switching frequency at different loads when DCM is allowed.  |

|                                                                                           |

| Fig.2.15 (b): Efficiency vs. switching frequency at different loads in CCM when DCM is    |

| not allowed                                                                               |

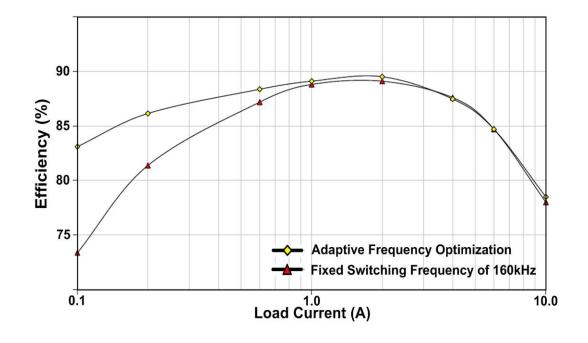

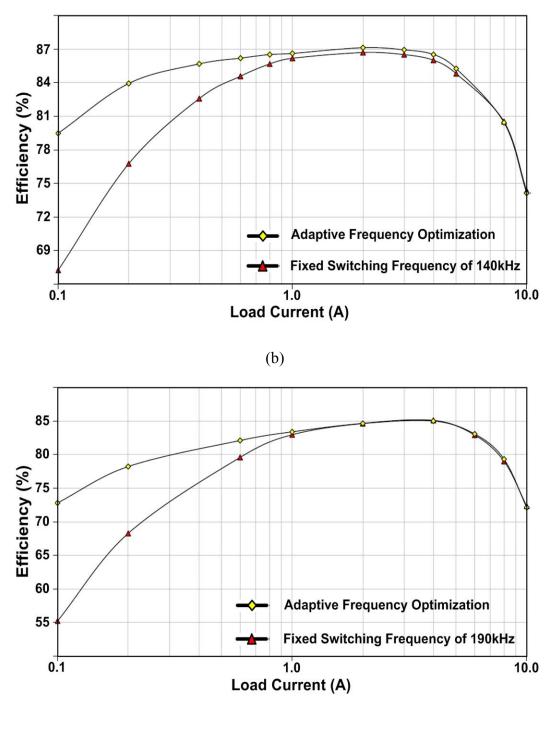

| Fig. 2.16 : Efficiency vs. Load using adaptive frequency Optimization (AFO) algorithm     |

| compared to operating at fixed switching frequency with CCM/DCM enabled at input          |

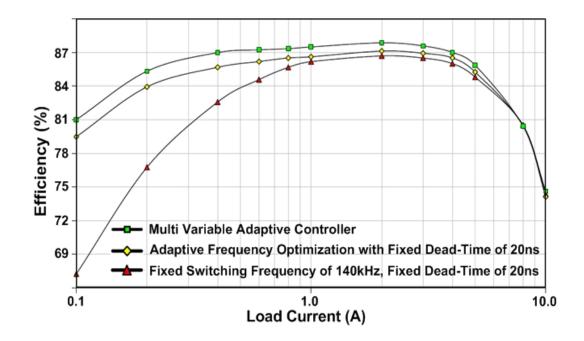

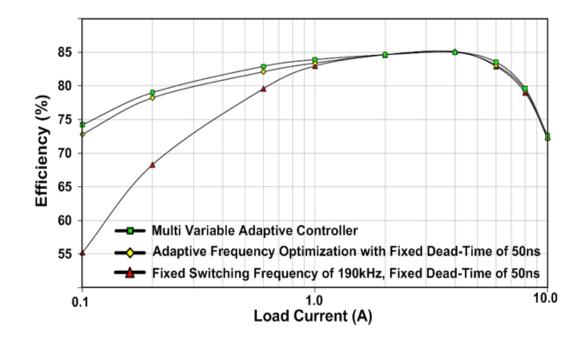

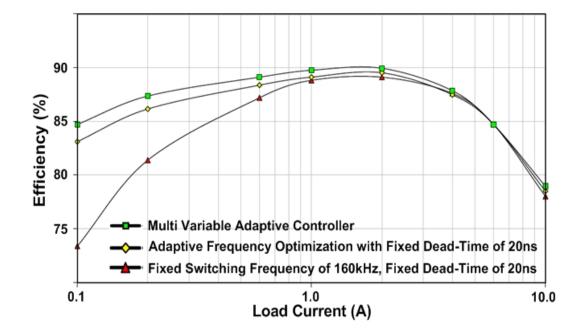

| voltage of (a) 8V (b) 10V (c) 12V                                                         |

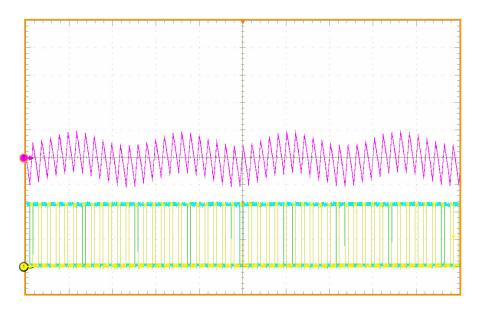

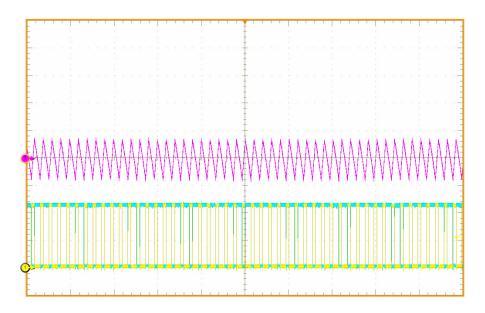

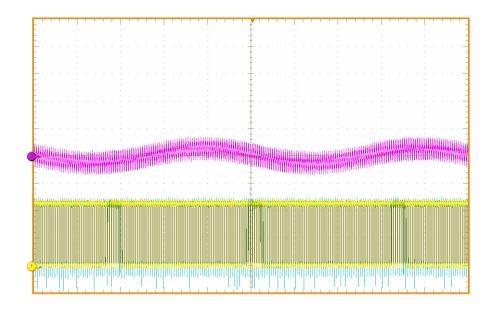

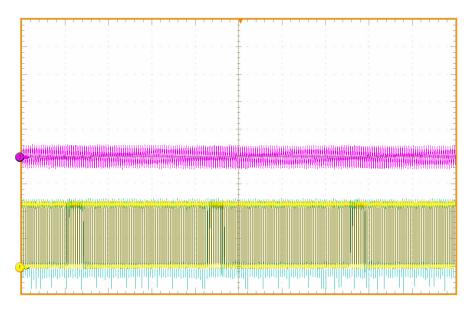

| Fig. 2.17: (a) Limit cycle oscillation at 100 kHz without the proposed DCLA, (b) No       |

| limit cycle oscillation at 100 kHz because of activating the DCLA part of the controller, |

| (c) Limit cycle oscillation at 200 kHz without the proposed DCLA, and (c) No limit cycle  |

| oscillation at 200 kHz because of activating the DCLA part of the controller              |

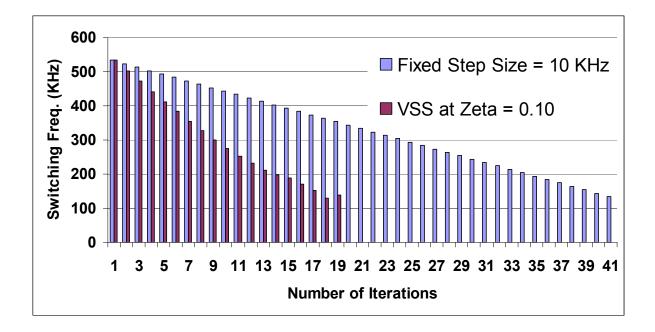

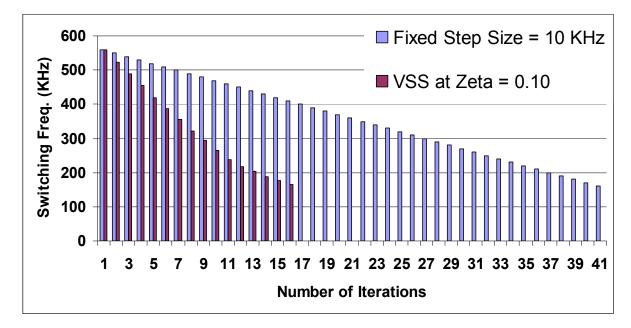

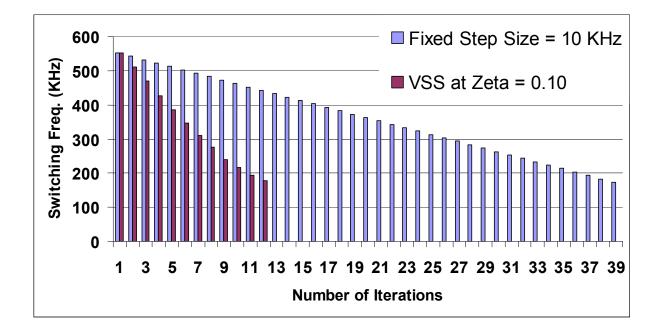

| Fig. 3.5 (a) Comparing variable step size with fixed step size at 5A load (start up          |

|----------------------------------------------------------------------------------------------|

| frequency 533 KHz)                                                                           |

| Fig. 3.5 (b) Comparing variable step size with fixed step size at 10A load (start up         |

| frequency 560 KHz)                                                                           |

| Fig. 3.5 (c) Comparing variable step size with fixed step size at 15A load (start up         |

| frequency 552 KHz)                                                                           |

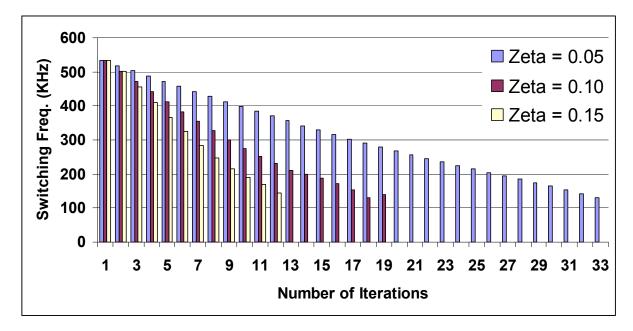

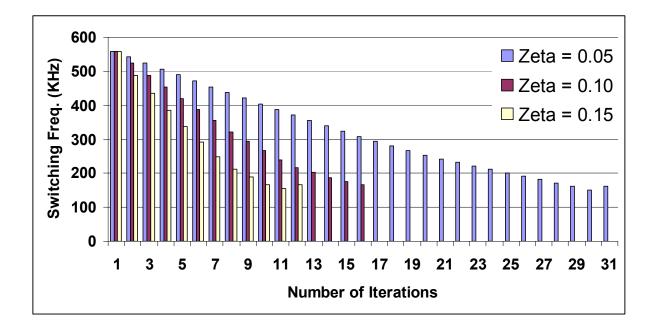

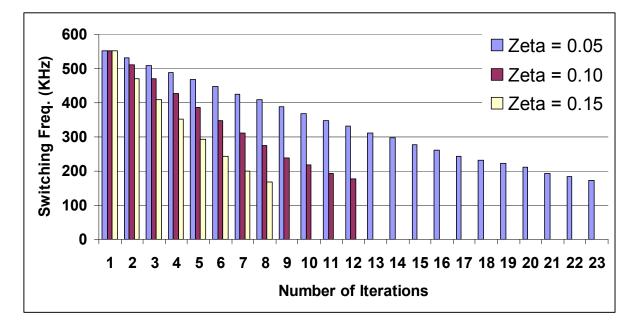

| Fig. 3.6 (a) Switching frequency at different iterations using different Zetas at 5A load 86 |

| Fig. 3.6 (b) Switching frequency at different iterations using different Zetas at 10A load   |

|                                                                                              |

| Fig. 3.6 (c) Switching frequency at different iterations using different Zetas at 15A load   |

|                                                                                              |

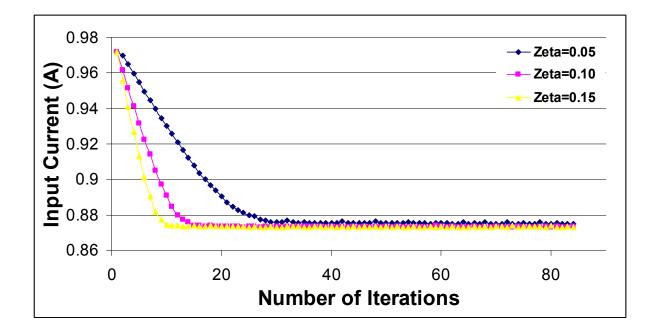

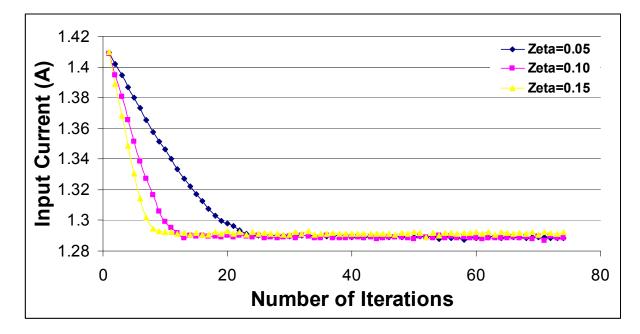

| Fig. 3.7 (a): Input Current at different iterations using different Zetas at 10A load 88     |

| Fig. 3.7 (b): Input Current at different iterations using different Zetas at 15A load 88     |

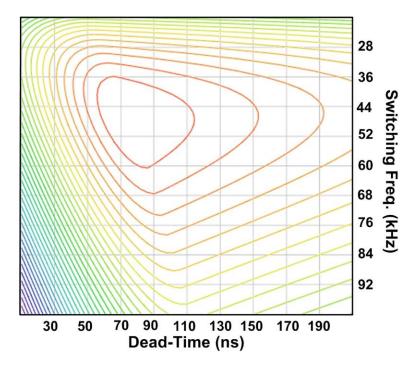

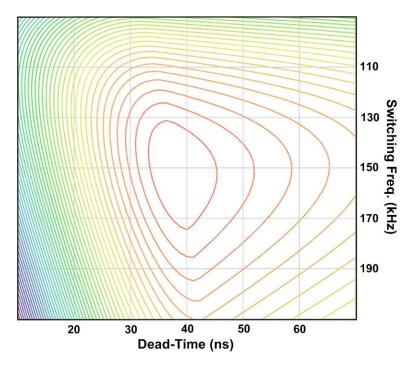

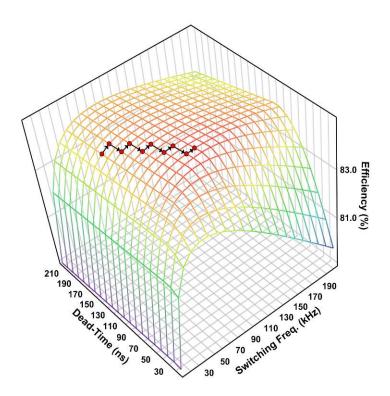

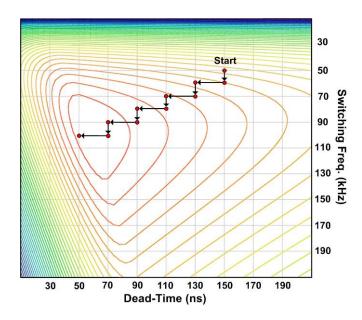

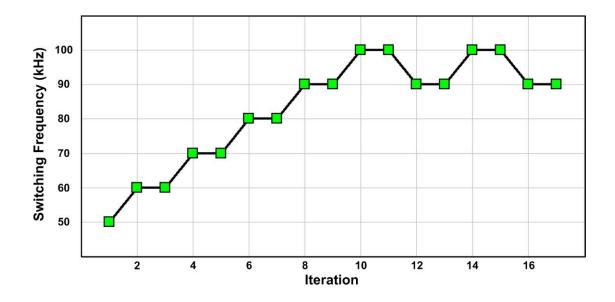

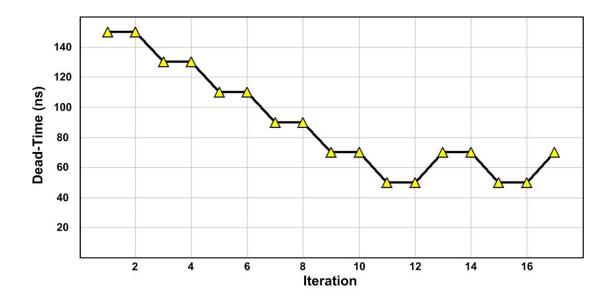

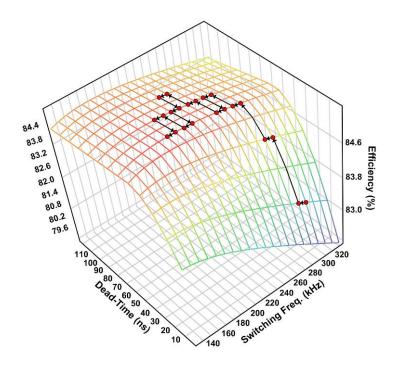

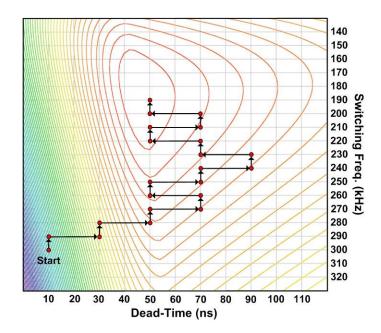

| Fig. 4.3 (d): Contour plot of Switching Frequency vs. Dead-Time vs. Efficiency at Load   |

|------------------------------------------------------------------------------------------|

| current = 1.0A, Optimum $F_{sw}$ = 100 kHz, Optimum Dead-Time = 60ns                     |

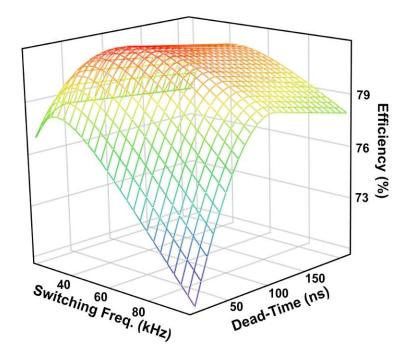

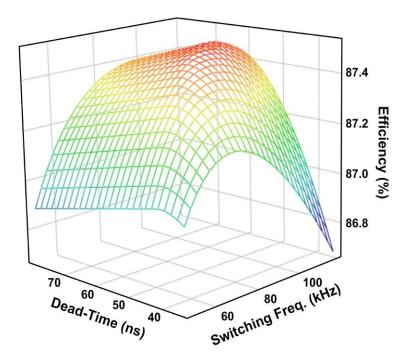

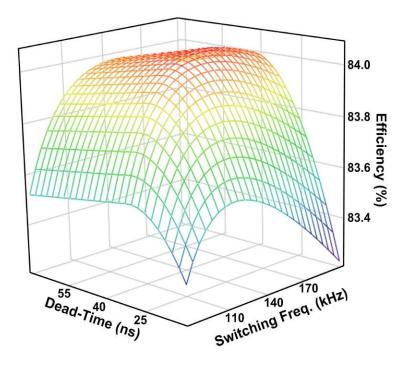

| Fig. 4.3 (e): 3D surface plot of Switching Frequency vs. Dead-Time vs. Efficiency at     |

| Load current = 6.0A, Optimum $F_{sw}$ = 150 kHz, Optimum Dead-Time = 40ns                |

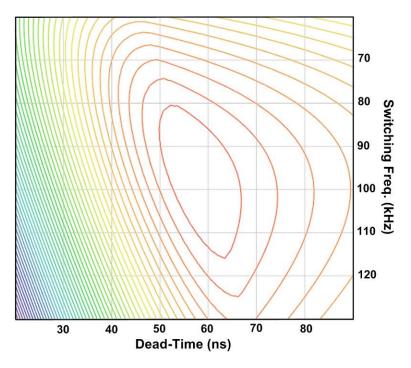

| Fig. 4.3 (f): Contour plot of Switching Frequency vs. Dead-Time vs. Efficiency at Load   |

| current = 6.0A, Optimum $F_{sw}$ = 150 kHz, Optimum Dead-Time = 40ns                     |

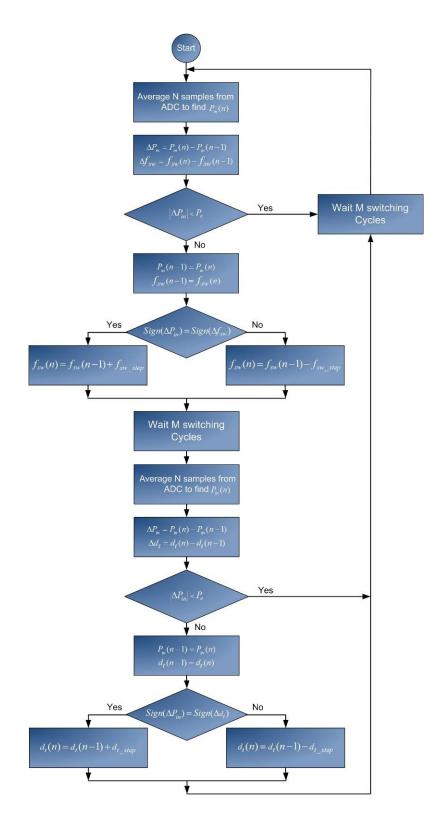

| Fig. 4.4: Multivariable Adaptive Controller (MVAC) flowcharts 102                        |

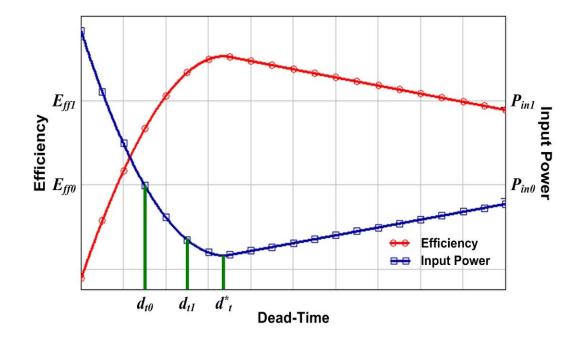

| Fig.4.5 Input Current as function of Dead-Time 104                                       |

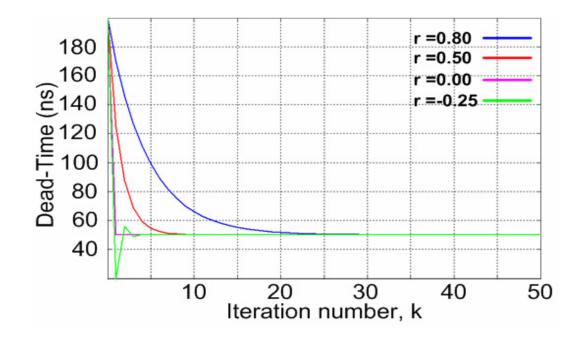

| Fig. 4.6 weight adjustment behavior for dead-time adaptive loop at different values of r |

|                                                                                          |

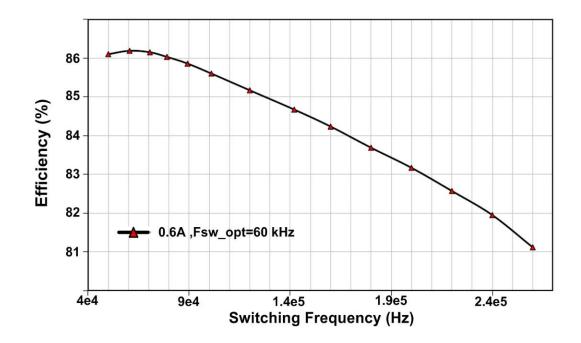

| Fig. 4.7 (a): Experimental Efficiency vs. switching frequency at 0.6A load at DCM mode.  |

|                                                                                          |

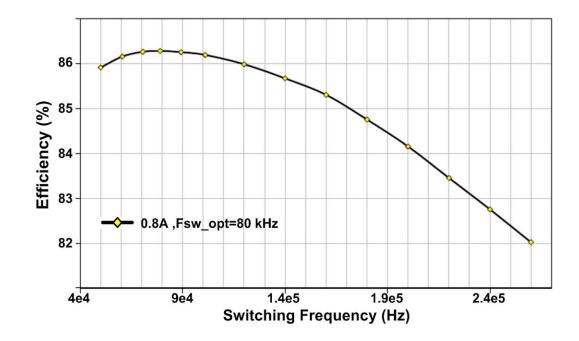

| Fig. 4.7 (b): Experimental Efficiency vs. switching frequency at 0.8A load at DCM mode.  |

|                                                                                          |

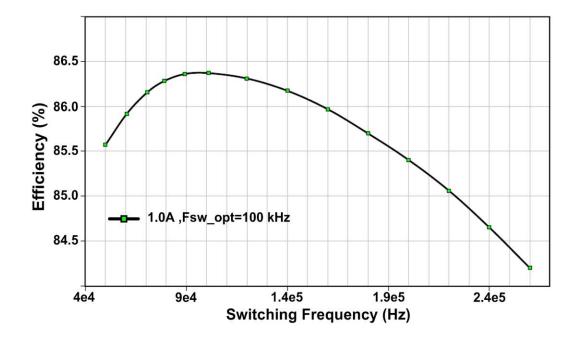

| Fig. 4.7 (c): Experimental Efficiency vs. switching frequency at 1.0A load at DCM mode.  |

|                                                                                          |

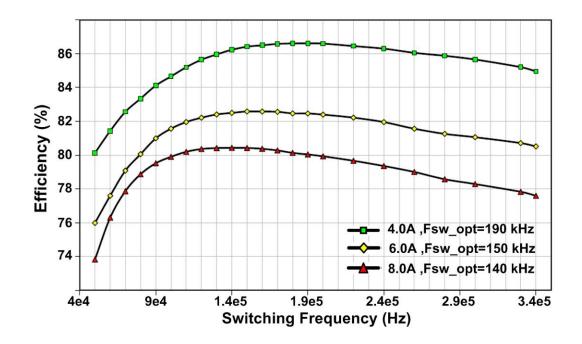

| Fig. 4.7 (d): Experimental Efficiency vs. switching frequency at different loads at CCM  |

| mode                                                                                     |

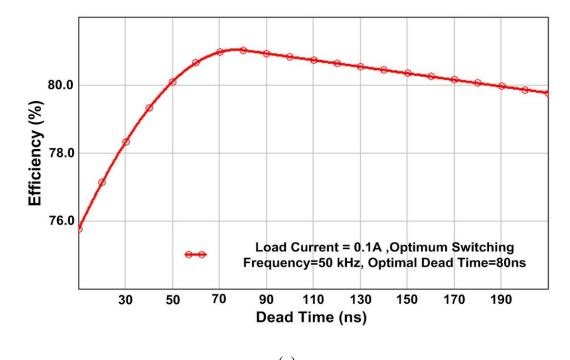

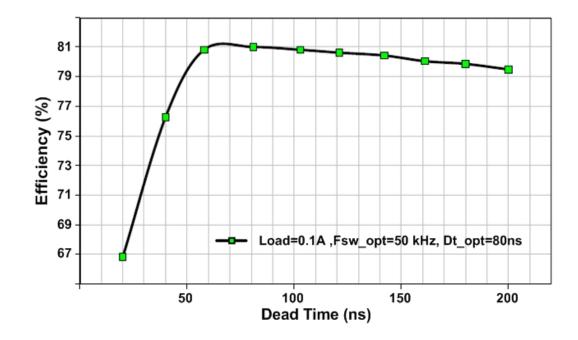

| Fig. 4.8 (a): Experimental Efficiency vs. Dead-Time at 0.1A load at DCM mode 115         |

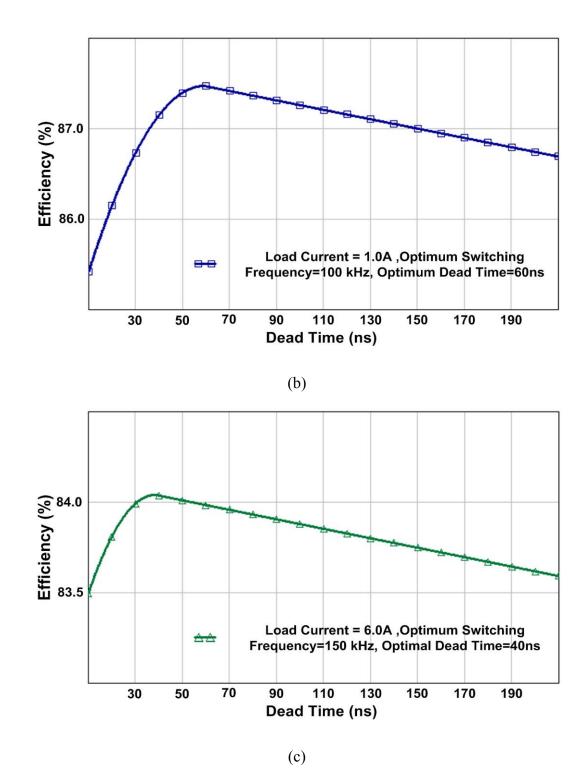

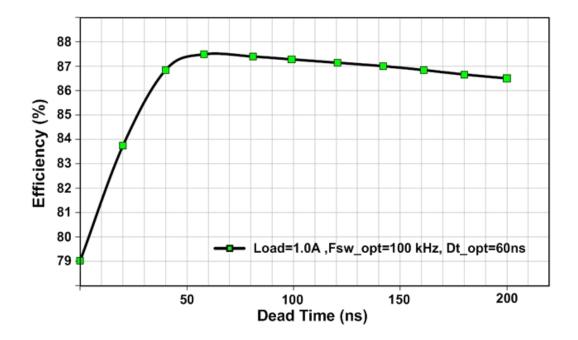

| Fig. 4.8 (b): Experimental Efficiency vs. Dead-Time at 1.0A load at DCM mode 115         |

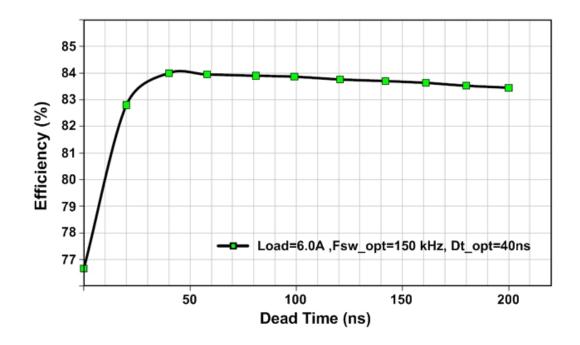

| Fig. 4.8 (c): Experimental Efficiency vs. Dead-Time at 6.0A load at CCM mode 116         |

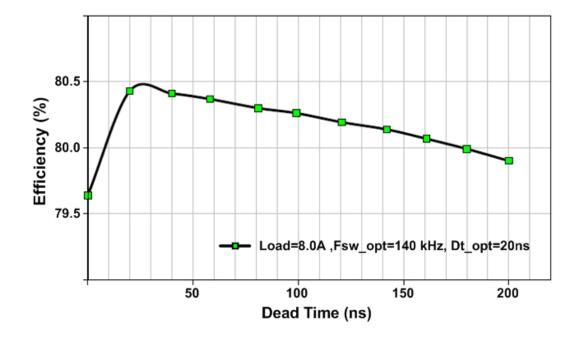

| Fig. 4.8 (d): Experimental Efficiency vs. Dead-Time at 8.0A load at CCM mode 116         |

| Fig. 4.9 (a): Efficiency comparison between different schemes working at Vin=10V 117     |

### LIST OF TABLES

| Table 2.1: A summary of continuous time models for different blocks of digitally      |

|---------------------------------------------------------------------------------------|

| controlled buck converter                                                             |

| Table 2.2: Optimum switching frequency and efficiency at different input voltages and |

| different load currents                                                               |

| Table 3.1. VSS Experimental Results                                                   |

| Table 4.1: Optimum switching frequency and Dead-Time and the resulted efficiency at   |

| different input voltages and different load currents                                  |

### CHAPTER ONE INTRODUCTION

#### **1.1 Background and Motivation**

The ever increasing demand for power converter systems with smaller size, higher efficiency and more tight output regulation place many challenges over the traditional analog control approach. Digital control is a new promising direction that offers many advantages over analog controllers [1-26]. One of the most important advantages is the ability to apply advanced non-linear control algorithms. Newer power converter systems may have two or more control loops that interact with each other to: control output variables, enhance dynamic response, and optimize certain system parameters. Building such control schemes using analog controllers is a very difficult and time consuming task, where it can be easily programmed using a digital controller. Reliability is another important advantage; digital controller's needs few passive components compared to analog controllers which make them less sensitive to components tolerances, aging and temperature variations. Finally digital controllers offers flexibility, where all the control laws and monitoring schemes can be programmed in a single digital controller, and can be easily changed in case of new design requirements [9].

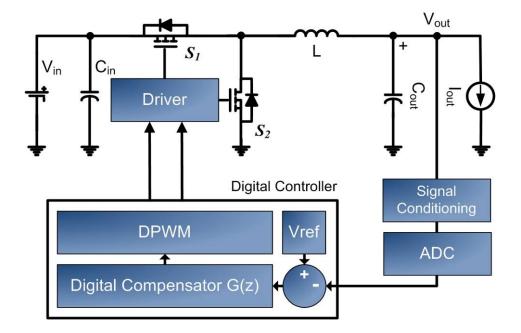

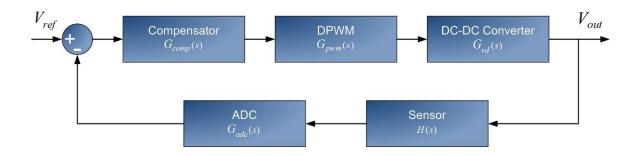

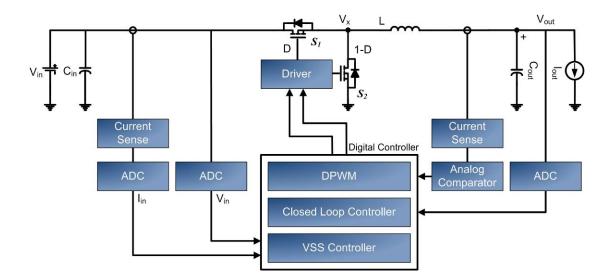

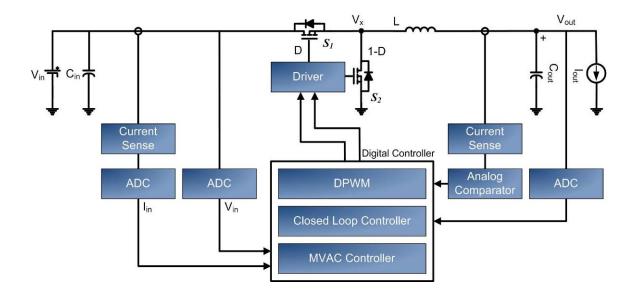

Fig. 1.1 shows typical digitally controlled synchronous buck DC-DC converter. The closed loop in Fig. 1.1 starts by measuring output voltage using a signal conditioning circuit that attenuates noise levels and convert the measured signal to a level appropriate for the Analog to Digital Converter (ADC). The measured signal is then sampled using the ADC and compared to a programmable reference inside the digital controller. The resultant error signal is then processed by the digital PID compensator that will calculate the required duty-cycle. Digital pulse width modulation (DPWM) unit works on the compensated error signal from the PID and generates a PWM signals with the correct frequency and duty cycle to the driver of the DC-DC converter. The sensed output voltage is not only used for voltage regulation, but can be also used to protect the DC-DC converter by shutting down the PWM signals when a faulty condition occurs [12].

Fig. 1.1: General block diagram for a digitally controlled power converter

According to control theory, there are two ways to design a digital controller [15]. The first method is the direct digital design, where a discrete time model of the system is first obtained then the controller is directly designed in the z-domain using traditional methods like frequency response bode plots, or root locus method. Direct digital design offers the advantages of better system response and the ability to achieve better phase and gain margins [15,16,19]. The other design method is the digital redesign, where the controller is first designed in continuous time domain (s-domain) then transformed to z-domain using well known discretization methods [15,16]. Digital redesign has the advantages of easier design process and the ability to apply known analog controller design techniques [15,22].

This work focuses on moving with power converters digital control beyond the conventional closed loop design into more advanced control schemes that will take the full advantage of digital controllers to harvest the benefits of improved efficiency and better converter dynamics. The following is the literature review and introduction of the work covered in this dissertation.

#### **1.2 Adaptive Efficiency Optimization**

Design optimization of the DC-DC converters requires the optimum selection of several parameters to achieve improved efficiency and performance. Some of these parameters are load dependent, input/output voltage dependent, components dependent, and/or temperature dependent. Designing such parameters for a specific load, input and output, components, and temperature may improve single design point efficiency but will

not result in maximum efficiency at different load and line conditions and will not guarantee improvement at that design point because of the components, temperature, and operating point variations [27-32]. As the processing power of digital controllers is becoming better at lower cost and lower power consumption, the ability to implement complex control law becomes easier and more practical for power conversion applications. One interesting type of control is adaptive control, where system parameters are dynamically adjusted in response to system changes in order to achieve better efficiency and dynamics [27,28].

One important parameter to be optimized for power converters is the switching frequency, in order to improve efficiency over wide range of operating conditions such as load conditions [31]. For example, for a wide load range low-output voltage DC-DC converter, selecting the optimized switching frequency is an important design parameter. Usually lower switching frequency means lower switching losses. Switching losses increase at higher switching frequencies while conduction losses become higher at heavier load currents [31,32]. Higher efficiencies are important at all operating conditions and at light load conditions to achieve energy savings and to extend battery life [27-44].

Variable switching frequency schemes have been used at light load in conjunction with DCM (Discontinuous Conduction Mode) to improve light load efficiency. For example, in [31], a synchronous buck converter is used to operate in the DCM with variable switching frequency that change according to the load current. Operating in DCM at light loads prevents the inductor current from going negative, which helps in reducing the conduction losses since there will be no circulating energy in the synchronous converter [31]. This will also result in lower switching losses since the synchronous rectifier is turned off at zero current. Moreover, operating at lower switching frequency reduces the switching losses. Operating in DCM with a lower switching frequency results in a converter that has higher efficiency at lighter loads. Since the converter operates in DCM and the switching frequency is reduced, a larger output capacitor may be needed to filter out the resulting large ripple current [35,38].

A peak current control method is used in [31], which may cause converter instability [35]. A modified approach to solve this issue was proposed in [32] and named hybrid control, where the DC-DC converter operates in the CCM (Continuous Conduction Mode) with fixed frequency at heavy loads, and in DCM with variable switching frequency that is also a function of the load current at light loads. In [39,40] and [43], a method is proposed that varies the switching frequency non-linearly, by tracking the peak inductor current in order to achieve efficiency at lighter loads while keeping maintained performance.

On the other hand, the optimum switching frequency value for the highest efficiency even in CCM fixed frequency operation is determined in conjunction with other design variables and assumptions. Usually, this optimum frequency is selected at nominal converter operating conditions (nominal input voltage, load range, temperature, inductor value, ...etc.) and for assumed components and parasitic values. Operating far from these nominal conditions and assumed design variables will result in not operating at the optimum switching frequency value for maximum conversion efficiency. The Adaptive Frequency Optimization (AFO) method starts by presenting an adaptive digital closed loop controller, with lower bandwidth than the output voltage regulation loop, to optimize and auto-tune the converter switching frequency on-the-fly under variable operating conditions. The proposed controller adaptively chooses the best switching frequency for the DC-DC converter, as operating conditions vary, by tracking the maximum efficiency point [28]. The Adaptive-Frequency-Optimization (AFO) changes the switching frequency to achieve lower combined switching and conduction losses, and as a result, achieves higher power conversion efficiency.

In the second part of the AFO method, design considerations that are related to variable switching frequency power digital controllers are summarized, and a dynamic technique that adjusts the system resolution to avoid the limit cycle oscillation problem is proposed [49-59]. This proposed dynamic technique alleviates some issues that result in digitally controlled variable frequency converters, which affect stability and dynamics. AFO algorithm along with improved controller designed is roughly studied and analyzed and simulation and experimental results to prove the concept are presented.

#### 1.3 Variable Step Size Auto-Tuning Algorithm

It is known that the power conversion efficiency of a DC-DC converters is typically a function of several design variables such as switching frequency, output inductance, switching devices characteristics, and dead-time and is a function of several other surrounding factors such as temperature and component aging [28,31-42]. Switching power converters designer optimize the efficiency based on given and assumed components characteristics and parasitics under a given set of pre-defined operating conditions and design specifications [31-42]. Usually, the efficiency-based design optimizations target at achieving the best tradeoff between different types of power losses including conduction losses, switching losses and gate drive losses at a certain load [37-40]. Such designs will only result in achieving the maximum efficiency degradation under different sets of operating conditions. This is true for on-board power converters that use discrete components and also true for on-chip integrated power converters [41, 42].

Digital controllers allow flexibility in realizing adaptive and advanced control schemes [27-29, 52-54]. Adaptive auto-tuning power controllers can adjust power converter parameters for maximized efficiency is under variable conditions [35,40,27-29]. However, the convergence stability, convergence speed, convergence error and simplicity/complexity are among the important characteristics of an adaptive auto-tuning controller, which need to be carefully studied and improved.

The switching frequency and Synchronous Rectifiers (SR) dead-time are two of the parameters which need to be optimized under variable conditions for maximum efficiency during the life time of the converter [27-29]. The SR dead-time can be optimized based on either the input current/power value minimization or based on the duty cycle value minimization as discussed in [28, 29]. In general, the method that is based on the duty cycle is suitable and accurate only for some of the non-isolated type converters, while the method that is based on the input current/power can be applied to both isolated and non-isolated converters. The later method can be used to auto-tune converter parameters such as switching frequency in addition to SR dead-time.

In previous work [27-29], the proposed algorithms were implemented using fixedstep-size (fixed increment and decrement of the variable value being auto-tuned). In fixed setp size algorithms, the designer has to choose either a small step-size (limited by the hardware resolution) that will result in longer controller convergence time to reach the optimum parameter value but with better accuracy, or he has to choose a large step-size that will result in shorter controller convergence time to the optimum parameter value but with lower accuracy.

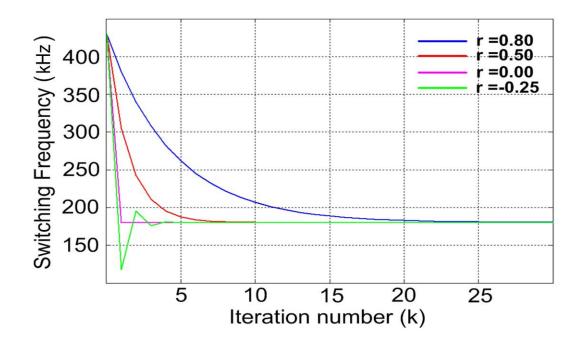

In this work, the effect of variable conditions on conversion efficiency is considered and a Variable Step Size (VSS) algorithm and the corresponding controller with good tradeoff between conversion speed, stability, and accuracy are proposed. The VSS control loop is theoretically analyzed and its design and stability criteria are developed. The developed algorithm and its theory are verified by a proof of concept experimental prototype results. While chapter three focus on analyzing and implementing the VSS to auto-tune the switching frequency of a power converter, the approach can be also extended to auto-tune the SR dead-time.

#### 1.4 Multivariable Adaptive Digital Controller

Optimizing the efficiency of DC-DC converters is one of top priorities for power electronics design engineer. Power converter losses, and the resultant power efficiency for

a given design varies at different loading conditions, line conditions, and it is impacted by the variations of temperature and aging effect [27-44]. From studying the power loss in DC-DC converter, it can be noted that there are two main kinds of losses, DC-DC converter switching losses and DC-DC converter conduction losses [31-38]. Switching losses are function of the switching frequency and conduction losses are function of the load current. Optimizing DC-DC converter switching frequency is one way to reduced switching losses [27,31,35]. While optimizing DC-DC converter dead time value can reduce conduction losses [31-38].

The ability of a digital controller to perform sophisticated algorithms makes it easy to apply adaptive control laws where system parameters can be dynamically adjusted in response to system behaviors in order to achieve better efficiency [28]. An adaptive controller and algorithm to optimize switching frequency of DC-DC converter is presented in [27] based on the efficiency tracking concept discussed in [28]. However, the controller in [27] optimizes one parameter: the switching frequency, while the controller in [28] optimizes another parameter only: the SR dead-time. Optimizing one parameter at a time may not result in maximum or global efficiency point and combined efficiency improvement.

Since the input power/current used in both [27] and [28] as the function to minimize, a single controller that optimize both variables and exhibits multivariable behavior can be used. In chapter 4, the analysis and experimental results for a multivariable adaptive controller that optimize DC-DC converter switching frequency and dead-time together is presented.

### CHAPTER TWO ADAPTIVE DIGITAL CONTROLLER AND DESIGN CONSIDERATIONS FOR A VARIABLE SWITCHING FREQUENCY VOLTAGE REGULATORS

#### **2.1 Introduction**

Power converter efficiency improvement is a major concern for power electronics design engineers. Higher efficiency values reveal better utilization of the available input power, and less stresses, and thus better reliability for the power converter system on hand. While the common approach for conversion efficiency improvement is using more optimized hardware components, a new approach, that utilize advanced control theory, to optimize converter operating parameters, proved to be effective in tackling the efficiency problems.

In this chapter an adaptive digital controller with maximum efficiency point tracking to optimize DC-DC converter switching frequency is presented. The Adaptive-Frequency-Optimization (AFO) controller adjusts the DC-DC converter switching frequency while tracking the converter minimum input power (maximum efficiency) point under variable conditions including variable load and variable input voltage. The AFO digital controller continuously finds the optimum switching frequency that will result in the minimum total loss while converter parameters and conditions vary. Moreover, the presented controller addresses issues that are associated with implementing variable switching frequencies in digital controllers, such as limit cycle oscillation and system

instability, using a dynamic algorithm to improve system stability under variable switching frequency operation.

Next section briefly discusses the switching frequency effects on losses. Section 2.3 presents the adaptive-frequency optimization controller and its algorithm to optimize the switching frequency to improve converter efficiency. Section 2.4 discusses the gain and phase considerations when designing a variable frequency digital controller. The limit cycle issue and the proposed dynamic algorithm to avoid it are discussed in Section 2.5. The experimental work is discussed in Section 2.6 while the conclusion is given in Section 2.7.

#### **2.2 Switching Frequency Effect on Losses**

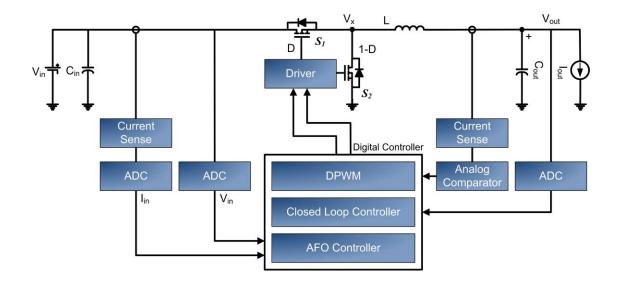

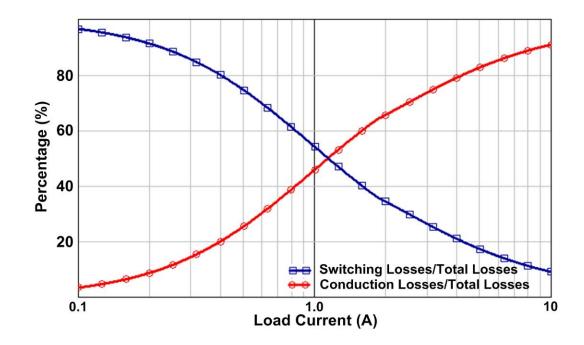

Fig. 2.1 shows a non-isolated buck DC-DC converter with synchronous rectification to be taken as a converter example to present the AFO and the Dynamic Limit Cycle Algorithms (DLCA) of this chapter. As stated earlier, switching losses are due to many reasons including the control and synchrnous MOSFETs output capacitances charge and discharge, the control and synchrnous MOSFET input capacitance charge and discharge (gate drive losses) and voltage-current turn off overlapping. Where as, conduction losses are mainly due to the components' parasitic resistances; which include the lower and upper MOSFET ON-resistance, the inductor winding DC resistance (DCR), the capacitor equivalent series resistance (ESR) and the sensing resistances [30-44]. Fig. 2.2 shows typical switching and conduction losses for the synchnous buck coverter discussed in section 2.6 at different load conditions with fixed switching frequency: it is

clear that the switching losses are dominant at light loads while conduction losses are dominant at heavy loads. A complete list of equations that summarizes the switching and conduction losses for a synchronous buck converter in both Discontinuous Conduction Mode (DCM) and continuous Conduction Mode (CCM) are discussed in [35,36,38].

Fig. 2.1: Non-isolated buck DC-DC converter with synchronous rectification.

Fig. 2.2: Switching and conduction power losses normalized to the total power loss vs. load current under fixed switching frequency operation for a given design.

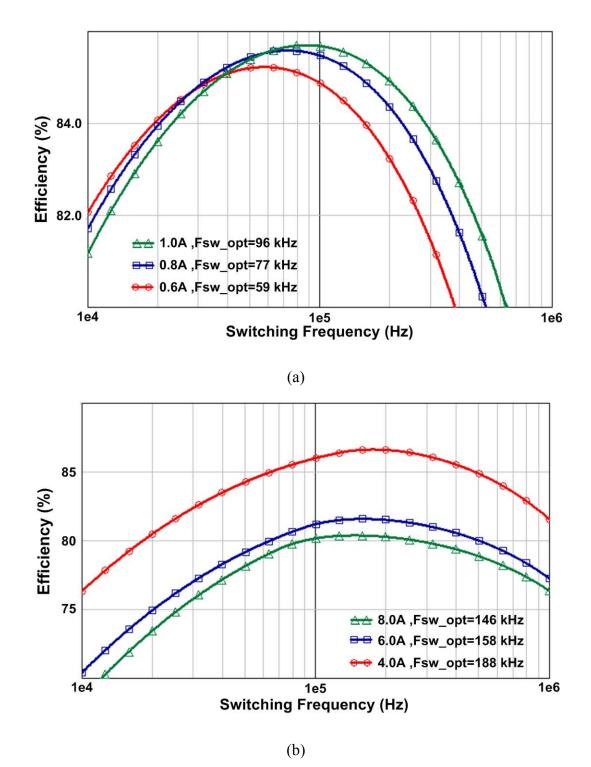

Lower switching frequency means lower switching and driving losses. Moreover, the switching and driving losses increase with the switching frequency while the conduction losses decrease because of lower ripple and *rms* currents. Also, the conduction losses increase with the load current increase. The optimized switching frequency that achieves the lowest total switching and conduction losses is related to many nonlinear parameters that makes the optimized switching frequency  $(f_{swO})$  different at different conditions. An adaptive controller that adaptively adjusts  $f_{sw}$  within a range depending on such nonlinear parameters variation can be used to achieve the optimum switching frequency. Fig. 2.3 shows efficiency simulation results curves at different load currents for synchronous buck converter discussed in section 2.6. From Fig. 2.6 it can be noted that there is a different optimized switching frequency where the efficiency is maximum for

both DCM and CCM operation. Fig. 2.3 (a) shows the simulation results when DCM operation is allowed and Fig. 2.3 (b) shows the simulation results when DCM is not allowed at all conditions (or in other words, while operating in CCM at all conditions). These curves shows that even in CCM, the optimum switching frequency is not necessarily fixed and it can vary. Moreover, as stated earlier, the optimum switching frequency will vary based on components parasitic variations resulted for example from aging and temperature variations.

Next section presents the Adaptive-Frequency-Optimization (AFO) method that tracks the optimum switching frequency  $(f_{swO})$  to achieve peak efficiencies under variable conditions. Even though the discussion of this chapter is based on a low power design example for the sake of concept demonstration, the method is applicable to higher power levels where its implementation is more justifiable and the power savings are larger.

Fig. 2.3: Simulation efficiency curves vs. switching frequency: (a) DCM operation is allowed, and (b) DCM operation is not allowed (CCM only)

#### 2.3 Adaptive Frequency Optimization (AFO) Digital Controller

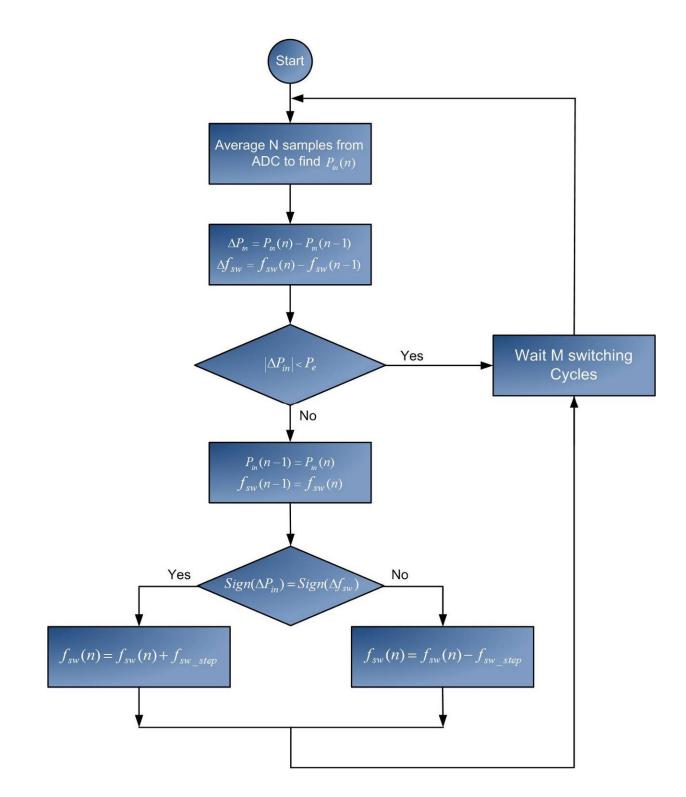

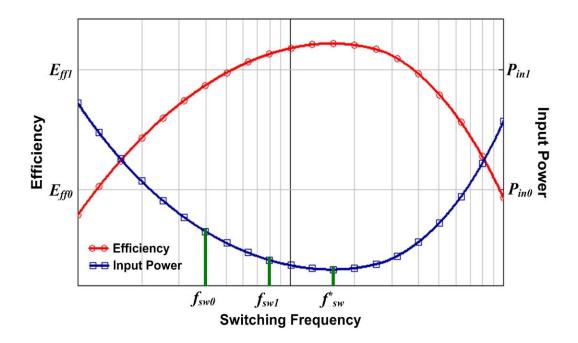

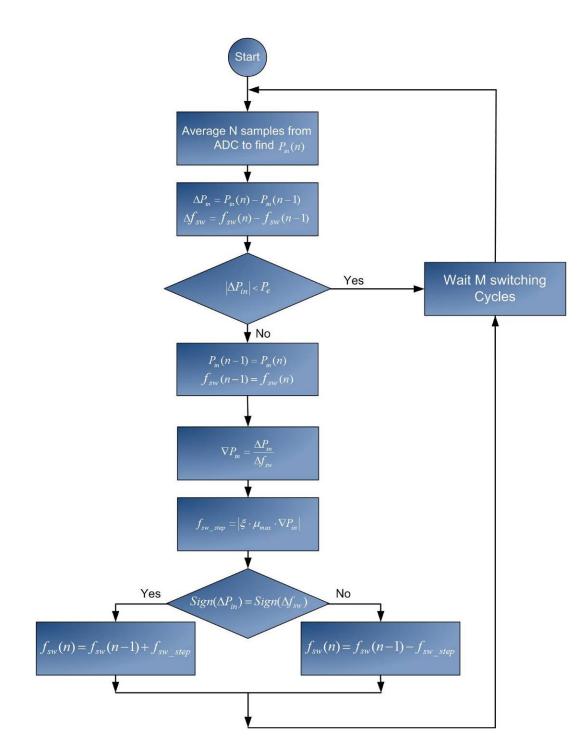

Fig. 2.4 shows an implementation flowchart for the AFO algorithm. The algorithm can be activated periodically or it can run in continuous manner with appropriate delay between iterations. *N* samples of  $P_{in}$  (converter sensed input power, or input current at a fixed input voltage) are taken by the ADC (Analog-to-Digital Converter) and averaged to generate  $P_{in}(n)$ .  $P_{in}(n)$  is used as an indication of the converter efficiency since the maximum efficiency occurs at the minimum input power. It is proved theoretically and experimentally that the switching frequency versus input power at a certain load current, has one local minimum [27]. So  $P_{in}$  can be used in the adaptive loop to decide the value of the digital controller switching frequency. Next, the AFO algorithm calculates the difference between the present and the previous values of  $P_{in}$  and the difference between the present and the previous values of  $f_{sw}$  as follows:

$$\Delta P_{in} = P_{in}(n) - P_{in}(n-1)$$

$$\Delta f_{SW} = f_{SW}(n) - f_{SW}(n-1)$$

(2.1)

(2.2)

Next, a check is performed to see if  $\Delta P_{in}$  has sufficient difference  $(p_e)$  to update  $f_{sw}$  or not. If this difference is sufficient, the program will proceed to the next step. Otherwise, it will start from the beginning by sampling  $P_{in}$  again. If the signs (positive or negative) of

Equations (2.1) and (2.2) are similar, this means  $f_{sw}$  should be incremented by  $f_{sw\_step}$  to move toward the maximum efficiency point (or minimum input power). Otherwise, if the signs of Equations (2.1) and (2.2) are not similar, this means  $f_{sw}$  should be decremented by  $f_{sw\_step}$  to move toward the maximum efficiency point. Increasing the converter efficiency by decreasing the input power indicates a reduction in the total losses to the minimum possible value (optimal switching frequency value). After storing the current values of  $P_{in}$  and  $f_{sw}$ , the program will decrement or increment  $f_{sw}$  and update it. Then, after several (*M*) switching cycles (enough to reach steady-state),  $P_{in}$  is sampled again and the AFO process is repeated. It must be noted that the compensated control signal  $D_c$  that regulates the converter output voltage is generated by a digital controller that also contains the AFO algorithm.

At a fixed input voltage, or with relatively very slow changing input voltage, it is sufficient to track the minimum input current value as discussed in [28]. The following discussion in this chapter will base in tracking the minimum input current rather than tracking the minimum input power.

Finally, it should be noted that the AFO loop bandwidth is much smaller than the output voltage regulation loop bandwidth. In practical implementation of the AFO algorithm in a digital controller, the following consideration should be taken into account:

Fig. 2.4: The Adaptive-Frequency-Optimization (AFO) digital controller flowchart

## 2.3.1 Switching Frequency Minimum step size f<sub>sw</sub> step Selection

Selecting the switching frequency increment/decrement step size  $(f_{sw\_step})$  depends on many parameters. This includes the minimum/maximum change in switching frequency that the DPWM can generate, the ADC resolution and the minimum change in switching frequency that will generate a descent and sufficient change in input current (or input power) that can be sensed. In the following, a detailed analysis for the effect of changing the switching frequency on input current is first introduced and then this analysis is used to design for the minimum  $f_{sw\_step}$  based on a given converter system design parameters.

The sensitivity of the input current,  $I_{in}$ , with constant input voltage (assuming the voltage is either constant or slow changing), to a change in switching frequency  $f_{sw}$  can be defined as the normalized change in  $I_{in}$  over the normalized change in  $f_{sw}$ :

$$S_{f_{SW}}^{I_{in}} = \frac{\frac{\Delta I_{in}}{I_{in}}}{\frac{\Delta f_{SW}}{f_{SW}}} = \frac{\Delta I_{in}}{\Delta f_{SW}} \cdot \frac{f_{SW}}{I_{in}}$$

(2.3)

For AFO process, where the switching frequency  $f_{SW}$  is varied in successive iterations, the sensitivity can be approximated as:

$$S_{f_{SW}}^{I_{in}} = \frac{\partial I_{in}}{\partial f_{SW}} \cdot \frac{f_{SW}}{I_{in}}$$

(2.4)

Equation (2.4) can also be rewritten as:

$$S_{f_{sw}}^{I_{in}} = \nabla I_{in} \cdot \frac{f_{sw}}{I_{in}}$$

(2.5)

Where  $\nabla I_{in}$  is the gradient of the input current. The expression for the input current gradient function  $\nabla I_{in}$  can be obtained as follows:

$$P_{in} = P_{out} + P_{Losses} = V_{out}I_{out} + P_{Losses}$$

(2.6)

The resulting expression for Iin,

$$I_{in} = \frac{V_{out}I_{out}}{V_{in}} + \frac{P_{Losses}}{V_{in}}$$

$$\nabla I_{in} = \frac{\partial I_{in}}{\partial f_{sw}} = \frac{\partial (\frac{V_{out}I_{out}}{V_{in}})}{\partial f_{sw}} + \frac{\partial (\frac{P_{Losses}}{V_{in}})}{\partial f_{sw}} = \frac{\partial (\frac{P_{Losses}}{V_{in}})}{\partial f_{sw}}$$

(2.7)

The sensitivity for each power loss type can be calculated using the gradient function and the total input current sensitivity as follows:

#### **2.3.1.1 Sensitivity for Conduction Losses in CCM Mode:**

The conduction losses in synchronous buck converter are the result of the *rms* current passing through the parasitic resistances of the different components. By computing the conduction losses and taking the derivative with respect to the switching frequency, the

sensitivity for conduction losses in Continuous Conduction Mode (CCM) using the gradient function can be given by:

$$S_{f_{SW}}^{I\Phi_1} = S_{f_{SW}}^{I\alpha} + S_{f_{SW}}^{I\beta} + S_{f_{SW}}^{I\chi} + S_{f_{SW}}^{I\delta}$$

$$(2.8)$$

Where  $S_{f_{SW}}^{I_{\Phi_1}}$ : is the change in the input current as a result of all conduction losses in CCM under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{\alpha}}$ : is the change in the input current as a result of control MOSFET conduction losses in CCM under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{\beta}}$ : is the change in the input current as a result of synchronous MOSFET conduction losses in CCM mode under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{\beta}}$ : is the change in the input current as a result of synchronous MOSFET conduction losses in CCM mode under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{\beta}}$ : is the change in the input current as a result of Inductor conduction losses in CCM mode under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{\beta}}$ : is the change in the input current as a result of Inductor conduction losses in CCM mode under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{\beta}}$ : is the change in the input current as a result of losses in CCM mode under one set in CCM mode under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{\beta}}$ : is the change in the input current as a result of losses in CCM mode under one set in the input current as a result of set in the input current as a result of losses in CCM mode under one  $f_{SW}$  step. The sensitivity for each conduction loss using the gradient is computed as:

$$S_{f_{SW}}^{I} = \frac{\partial (\frac{P_{\alpha}}{V_{in}})}{\partial f_{SW}} \cdot \frac{f_{SW}}{I_{in}} = -\frac{1}{6} \cdot \frac{V_{out}^3}{V_{in}^4} \cdot \frac{(V_{in} - V_{out})^2}{L^2 f_{SW}^2} \cdot \frac{R_{SW}}{I_{in}}$$

(2.9)

$$S_{f_{sw}}^{I_{\beta}} = \frac{\partial (\frac{P_{\beta}}{V_{in}})}{\partial f_{sw}} \cdot \frac{f_{sw}}{I_{in}} = -\frac{1}{6} \cdot \frac{V_{out}^2}{V_{in}^4} \cdot \frac{(V_{in} - V_{out})^3}{L^2 f_{sw}^2} \cdot \frac{R_{sr}}{I_{in}}$$

(2.10)

$$S_{f_{sw}}^{I} = \frac{\partial (\frac{P_{\chi}}{V_{in}})}{\partial f_{sw}} \cdot \frac{f_{sw}}{I_{in}} = -\frac{1}{6} \cdot \frac{V_{out}^{2}}{V_{in}^{3}} \cdot \frac{(V_{in} - V_{out})^{2}}{L^{2} f_{sw}^{2}} \cdot \frac{R_{DCR}}{I_{in}}$$

$$(2.11)$$

$$S_{f_{sw}}^{I} = \frac{\partial (\frac{P_{\delta}}{V_{in}})}{\partial f_{sw}} \cdot \frac{f_{sw}}{I_{in}} = -\frac{1}{6} \cdot \frac{V_{out}^{2}}{V_{in}^{3}} \cdot \frac{(V_{in} - V_{out})^{2}}{L^{2} f_{sw}^{2}} \cdot \frac{R_{sense}}{I_{in}}$$

(2.12)

Where  $P_{\alpha}$ : is the control MOSFET conduction power losses in CCM mode,  $P_{\beta}$ : is the synchronous MOSFET conduction power losses in CCM mode,  $P_{\chi}$ : is the inductor conduction power losses in CCM mode,  $P_{\delta}$ : is the sense resistor conduction power losses in CCM mode,  $R_{sw}$  is the ON resistance of a main switch,  $R_{sr}$  is the ON resistance of a synchronous switch,  $R_{DCR}$  is the inductor parasitic resistance, and  $R_{sense}$  is the sensing resistance.

## 2.3.1.2 Sensitivity for Switching (and Driving) Losses in CCM Mode

Switching losses (including driving losses) in synchronous buck converter are combinations of the turn ON and turn OFF losses of the main and synchronous switch, losses to charge the MOSFETs output capacitance and the driving losses. By computing the switching losses and taking the derivative with respect to the switching frequency, the gradient function for the switching losses in CCM can be given by:

$$S_{f_{SW}}^{I_{\Phi_{2}}} = S_{f_{SW}}^{I_{\varepsilon}} + S_{f_{SW}}^{I_{\phi}} + S_{f_{SW}}^{I_{\phi}} + S_{f_{SW}}^{I_{\gamma}} + S_{f_{SW}}^{I_{\kappa}} + S_{f_{SW}}^{I_{\lambda}}$$

(2.13)

Where  $S_{f_{SW}}^{I_{\Phi_2}}$ : is the change in the input current as a result of all switching losses in CCM under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{\mathcal{E}}}$ : is the change in the input current as a result of control MOSFET turn ON switching losses in CCM under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{\phi}}$ : is the change in the input current as a result of control MOSFET turn OFF switching losses in CCM under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{\varphi}}$ : is the change in the input current as a result of synchronous MOSFET turn ON switching losses in CCM under one  $f_{SW}$  step.  $S_{f_{ew}}^{I_{\gamma}}$ : is the change in the input current as a result of synchronous MOSFET turn OFF switching losses in CCM under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{\kappa}}$ : is the change in the input current as a result of MOSFET output capacitance switching losses in CCM under one  $f_{SW}$  step.  $S_{f_{cw}}^{I_{\lambda}}$ : is the change in the input current as a result of driving losses in CCM under one  $f_{SW}$  step. The sensitivity for each conduction loss using the gradient is computed as:

$$S_{f_{SW}}^{I_{\mathcal{E}}} = \frac{\partial (\frac{P_{\mathcal{E}}}{V_{in}})}{\partial f_{SW}} \cdot \frac{f_{SW}}{I_{in}} = \frac{1}{2} \cdot \frac{I_{out}}{I_{g_{on}}} \cdot \frac{f_{SW}}{I_{in}} \cdot \mathcal{Q}_{SW}$$

$$(2.14)$$

$$S_{f_{sw}}^{I_{\phi}} = \frac{\partial (\frac{P_{\phi}}{V_{in}})}{\partial f_{sw}} \cdot \frac{f_{sw}}{I_{in}} = \frac{1}{2} \cdot \frac{I_{out}}{I_{g_{off}}} \cdot \frac{f_{sw}}{I_{in}} \cdot \mathcal{Q}_{sw}$$

(2.15)

$$S_{f_{SW}}^{I_{\varphi}} = \frac{\partial (\frac{P_{\varphi}}{V_{in}})}{\partial f_{SW}} \cdot \frac{f_{SW}}{I_{in}} = -\frac{1}{4} \cdot \frac{V_{out}}{V_{in}^2} \cdot \frac{(V_{in} - V_{out})}{L} \cdot \frac{t_{rise\_sr} \cdot V_D}{I_{in}}$$

$$S_{f_{SW}}^{I_{\gamma}} = \frac{\partial (\frac{P_{\gamma}}{V_{in}})}{\partial f_{SW}} \cdot \frac{f_{SW}}{I_{in}} = \frac{1}{4} \cdot t_{fall\_sr} \cdot \frac{V_{out}}{V_{in}^2} \cdot \frac{(V_{in}-V_{out})}{L} \cdot \frac{V_{D}}{I_{in}}$$

$$S_{f_{SW}}^{I_{\kappa}} = \frac{\partial (\frac{P_{\kappa}}{V_{in}})}{\partial f_{SW}} \cdot \frac{f_{SW}}{I_{in}} = \frac{1}{2} (Q_{oss\_sw} + Q_{oss\_sr}) \cdot \frac{f_{SW}}{I_{in}}$$

(2.18)

$$S_{f_{SW}}^{I_{\lambda}} = \frac{\partial (\frac{P_{\lambda}}{V_{in}})}{\partial f_{SW}} \cdot \frac{f_{SW}}{I_{in}} = \frac{2Q_{gSW}V_g}{V_{in}} \cdot \frac{f_{SW}}{I_{in}}$$

(2.19)

Where  $P_{\varepsilon}$ : is the control MOSFET turn ON switching power losses in CCM,  $P_{\phi}$ : is the control MOSFET turn OFF switching power losses in CCM,  $P_{\phi}$ : is the synchronous MOSFET turn ON switching power losses in CCM,  $P_{\gamma}$ : is the synchronous MOSFET turn

OFF switching power losses in CCM,  $P_{\kappa}$ : is the MOSFET output capacitance switching power losses in CCM,  $P_{\lambda}$ : is the driving power losses in CCM.  $Q_{sw}$  is the main switch charge,  $I_{g_{on}}$  is the Driver ON current,  $I_{g_{off}}$  is the Driver OFF current,  $V_D$  is the forward voltage drop of the switch body diode,  $t_{rise\_sr}$  is the turn ON rise time of the synchronous switch,  $t_{fall\_sr}$  is the turn OFF fall time of the synchronous switch, and  $Q_{oss}$  is MOSFET output charge. From the above, the input current sensitivity for total losses in CCM is:

$$S_{f_{SW}}^{I_{\Phi}} total = S_{f_{SW}}^{I_{\Phi}} + S_{f_{SW}}^{I_{\Phi}}$$

$$(2.20)$$

Where  $S_{f_{SW}}^{I_{\Phi_{total}}}$ : is the change in the input current as a result of all switching and

conduction losses in CCM under one  $f_{_{SW}}$  step

### 2.3.1.3 Sensitivity for Conduction Losses in DCM Mode

Following the same procedure in CCM analysis above, start by computing the gradient for the conduction losses in Discontinuous Conduction Mode (DCM), by taking the derivative with respect to the switching frequency, the sensitivity for conduction losses in DCM can be given by:

$$S_{f_{SW}}^{I_{\Psi_{1}}} = S_{f_{SW}}^{I_{\mu}} + S_{f_{SW}}^{I_{\nu}} + S_{f_{SW}}^{I_{o}} + S_{f_{SW}}^{I_{o}}$$

(2.21)

Where  $S_{f_{sw}}^{I_{\Psi_1}}$ : is the change in the input current as a result of all conduction losses in DCM

under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{\mu}}$ : is the change in the input current as a result of control MOSFET conduction losses in DCM under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{\nu}}$ : is the change in the input current as a result of synchronous MOSFET conduction losses in DCM mode under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{o}}$ : is the change in the input current as a result of Inductor conduction losses in DCM mode under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{o}}$ : is the change in the input current as a result of Inductor conduction losses in DCM mode under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{o}}$ : is the change in the input current as a result of Inductor conduction losses in DCM mode under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{o}}$ : is the change in the input current as a result of Inductor conduction losses in DCM mode under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{o}}$ : is the change in the input current as a result of Inductor conduction losses in DCM mode under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{o}}$ : is the change in the input current as a result of Inductor conduction losses in DCM mode under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{o}}$ : is the change in the input current as a result of Inductor conduction losses in DCM mode under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{o}}$ : is the change in the input current as a result of Inductor conduction losses in DCM mode under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{o}}$ : is the change in the input current as a result of Inductor conduction losses in DCM mode under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{o}}$ : is the change in the input current as a result of  $f_{SW}$  step.  $S_{f_{SW}}^{I_{o}}$  is the change in the input current as a result of  $f_{SW}$  step.  $S_{f_{SW}}^{I_{o}}$  is the change in the input current as a result of  $f_{SW}$  step.  $S_{f_{SW}}^{I_{o}}$  is the change in the input current as a result of  $f_{SW}$  step.

the sense resistor conduction losses in DCM mode under one  $f_{SW}$  step. The sensitivity for each conduction loss using the gradient is computed as:

$$S_{f_{sw}}^{I\mu} = \frac{\partial (\frac{\mu}{V_{in}})}{\partial f_{sw}} \cdot \frac{f_{sw}}{I_{in}} = -\frac{\sqrt{2}}{3I_{in}} \cdot \frac{I_{out}^2 V_{out} R_{sw}}{\sqrt{\frac{I_{out}V_{in}^5 L f_{sw}}{V_{out}(V_{in} - V_{out})}}}$$

| $(\mathbf{r})$ | 22) |

|----------------|-----|

| (2)            |     |

$$S_{f_{SW}}^{I_{V}} = \frac{\partial(\frac{P_{V}}{V_{in}})}{\partial f_{SW}} \cdot \frac{f_{SW}}{I_{in}} = -\frac{\sqrt{2}}{3I_{in}} \cdot \frac{I_{out}^{2}(V_{in} - V_{out})R_{sr}}{\sqrt{\frac{I_{out}V_{in}^{5}Lf_{SW}}{V_{out}(V_{in} - V_{out})}}}$$

(2.23)

$$S_{f_{SW}}^{I_{O}} = \frac{\partial (\frac{P_{O}}{V_{in}})}{\partial f_{SW}} \cdot \frac{f_{SW}}{I_{in}} = -\frac{\sqrt{2}}{3I_{in}} \cdot \frac{I_{out}^{2} R_{L}}{\sqrt{\frac{I_{out}V_{in}^{3} L f_{SW}}{V_{out}(V_{in} - V_{out})}}}$$

$$(2.24)$$

$$S_{f_{SW}}^{I} = \frac{\partial (\frac{I_{\varpi}}{V_{in}})}{\partial f_{SW}} \cdot \frac{f_{SW}}{I_{in}} = -\frac{\sqrt{2}}{3I_{in}} \cdot \frac{I_{out}^2 R_{sense}}{\sqrt{\frac{I_{out}V_{in}^3 L f_{SW}}{V_{out}(V_{in} - V_{out})}}}$$

(2.25)

Where  $P_{\mu}$ : is the control MOSFET conduction power losses in DCM mode,  $P_{V}$ : is the synchronous MOSFET conduction power losses in DCM mode,  $P_{o}$ : is the inductor conduction power losses in DCM mode,  $P_{\overline{o}}$ : is the sense resistor conduction power losses in DCM mode.

#### 2.3.1.4 Sensitivity for Switching Losses in DCM Mode

By computing the gradient for the switching losses in DCM mode, the sensitivity for switching losses in DCM can be given by:

$$S_{f_{SW}}^{I_{\Psi_{2}}} = S_{f_{SW}}^{I_{g}} + S_{f_{SW}}^{I_{\rho}} + S_{f_{SW}}^{I_{\sigma}} + S_{f_{SW}}^{I_{\varsigma}}$$

(2.26)

Where  $S_{f_{sw}}^{I_{\Psi_2}}$ : is the change in the input current as a result of all switching losses in

DCM under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_g}$ : is the change in the input current as a result of control

MOSFET turn OFF switching losses in DCM under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{\rho}}$ : Is the change in

the input current as a result of synchronous MOSFET turn ON switching losses in DCM under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{\sigma}}$ : Is the change in the input current as a result of MOSFET output

capacitance switching losses in DCM under one  $f_{SW}$  step.  $S_{f_{SW}}^{I_{S}}$ : is the change in the input

current as a result of driving losses in DCM under one  $f_{SW}$  step. The sensitivity for each conduction loss using the gradient is computed as:

$$S_{f_{sw}}^{I_{g}} = \frac{\partial(\frac{P_{g}}{V_{in}})}{\partial f_{sw}} \cdot \frac{f_{sw}}{I_{in}} = \frac{1}{2\sqrt{2}I_{in}I_{g_{off}}} \sqrt{\frac{\mathcal{Q}_{sw}^{2}I_{out}f_{sw}V_{out}(V_{in}-V_{out})}{V_{in}L}}$$

(2.27)

$$S_{f_{sw}}^{I} = \frac{\frac{\partial (\frac{\rho}{V_{in}})}{\partial f_{sw}} \cdot \frac{f_{sw}}{I_{in}}}{\frac{\partial f_{sw}}{\partial I_{in}}} = \frac{t_{rise\_sr}}{2\sqrt{2}I_{in}} \cdot \sqrt{\frac{V_D^2 I_{out} f_{sw} V_{out} (V_{in} - V_{out})}{V_{in}^3 L}}$$

(2.28)

$$S_{f_{sw}}^{I} = \frac{\partial (\frac{P_{\sigma}}{V_{in}})}{\partial f_{sw}} \cdot \frac{f_{sw}}{I_{in}} = \frac{1}{2} (Q_{oss\_sw} + Q_{oss\_sr}) \cdot \frac{f_{sw}}{I_{in}}$$

(2.29)

$$S_{f_{SW}}^{I\varsigma} = \frac{\partial (\frac{P_{\varsigma}}{V_{in}})}{\partial f_{SW}} \cdot \frac{f_{SW}}{I_{in}} = \frac{2Q_{gSW}V_g f_{SW}}{V_{in}I_{in}}$$

(2.30)

Where  $P_g$ : is the control MOSFET turn OFF switching power losses in DCM,  $P_{\rho}$ : is the synchronous MOSFET turn ON switching power losses in DCM,  $P_{\sigma}$ : is the MOSFET output capacitance switching power losses in DCM,  $P_{\varsigma}$ : is the driving power losses in DCM. From the above, the input current sensitivity for total losses in DCM is:

$$S_{f_{SW}}^{I_{\Psi}} total = S_{f_{SW}}^{I_{\Psi}} + S_{f_{SW}}^{I_{\Psi}}$$

$$(2.31)$$

Where  ${}^{I}_{S_{f_{SW}}}$ : is the change in the input current as a result of all switching and

conduction losses in DCM under one  $f_{SW}$  step.

From the above analysis, the synchronous buck DC-DC converter, input current sensitivity to changes in input current can be calculated as:

$$S_{f_{SW}}^{I_{in}} = \begin{cases} S_{f_{SW}}^{I_{\Phi}} total , & CCM \\ \\ S_{f_{SW}}^{I_{\Psi}} total , & DCM \end{cases}$$

(2.32)

The minimum frequency change that can be used given certain hardware limitations can be calculated as follows: First, the minimum change the ADC can sense is given in Equation (2.33) as follow:

$$ADC_{LSB} = \frac{V_{ADC} MAX}{2^{N} ADC}$$

(2.33)

Where  $ADC_{LSB}$  is the minimum voltage change the ADC can sense,  $V_{ADC\_MAX}$  is the ADC maximum sensed voltage and  $N_{ADC}$  is the ADC number of bits. For the AFO experimental step of this chapter presented in Section 2.6, the input current is sensed using a 12 bits ADC with  $V_{ADC\_MAX} = 3.3$ V:

$$ADC_{LSB} = \frac{3.3}{2^{12}} = 0.806 \times 10^{-3} V$$

If the current sensing circuitry is using a  $5m\Omega$  sensing resistor with current sensing opamp gain set to 100 V/V, the minimum input current change that cause a 0.806mV change can be calculated as:

$$I_{in\_min} \times R_{sense} \times Gain = ADC_{LSB}$$

$$I_{in\_min} \times (5 \times 10^{-3}) \times 100 = 0.806 \times 10^{-3}$$

$$I_{in\_min} = 1.6 \times 10^{-3} A$$

The minimum switching frequency change that cause the minimum input current change  $I_{in \ min}$  can be calculated using Equation (2.34):

$$f_{sw\_min} = \frac{I_{in\_min}}{\nabla I_{in}}$$

(2.34)

Using Equation (2.34) and based on the power stage specifications that are given in the experimental work of Section 2.6, the minimum change in switching frequency is calculated to be 6.380 kHz. Therefore, the step size should be selected to be larger than 6.380 kHz. This value was selected to be 10 kHz for the experimental prototype.

# 2.3.2 $P_e$ Selection

$P_e$  is defined as the minimum input power change required to activate the AFO loop. As shown in Fig. 2.4, the difference in input power between two samples is first compared if this difference is greater than a certain threshold  $P_e$  the AFO adaptive loop is activated, else, the AFO algorithm will just wait and do nothing. This condition is optional and can be replaced by a delay time that periodically activates the AFO. This threshold comparison serves two purposes [26]: First it reduces oscillation between two values when there is no descent change in input power, and second, it minimizes the noise effect [2]. The selection of  $P_e$  depends on the selected step size:  $f_{sw\_step}$  and can be calculated from equation (2.35) as follow:

$$P_{e} = \nabla I_{in} \cdot f_{in} \min \cdot V_{in}$$

(2.35)

Using the power stage specification, and assuming that the input voltage  $V_{in} = 10V$  and that the switching frequency step-size is  $f_{sw\_step} = 10 \ kHz$ , the input power threshold  $P_e$  can be calculated from Equation (2.35) and is equal to 3.1 mW or 0.31mA at 10V fixed input voltage. It should be noted that the design equations discussed above are used as a guide line to find an initial value for the step size and Pe, more exact values was found through out the experiment.

#### 2.3.3 M Selection

A delay of M switching cycles between each increment/decrement of the switching frequency is required to ensure that the new input power/input current is sampled after the frequency change transient effect has passed. The closed loop compensator takes some time, the settling time, to settle the system to it new steady state condition. This transient settling time value is very negligible especially when the step size is small, however, it should be taken into account. The delay time (M switching cycles) is usually selected to be much larger than the settling time value. For the experimental setup described in Section 2.6, the settling time was selected to be M = 5 switching cycles, which was sufficient based on this chapter loop design (see Section 2.4 for bode-plots of the closed loop design). One important note here is that AFO algorithm will only work when the load is

changing at frequency less than M. In other words, AFO will work with slowly varying loads. It should be noted also that since the adaptive loop is running at much slower bandwidth than the closed loop, this means that the AFO effect on system stability is minimal.

#### 2.4 Loop Gain-Phase Design Considerations

Fig. 2.5 shows the block diagram of a digitally controlled synchronous Buck DC-DC converter. For a digitally controlled converter the output voltage is sampled using an ADC and compared to a programmable reference internal to the digital controller [12-26]. This is done before it is applied to the digital PID compensator that will generate the required duty-cycle to the digital pulse width modulation (DPWM) unit. The DPWM unit generates the PWM signals with the correct frequency and duty cycle to the driver of the DC-DC converter. The sensed output voltage can also be used to protect the DC-DC converter by shutting down the PWM signals when an over voltage condition occurs.

Fig. 2.5: Block-diagram of a digitally controlled closed loop synchronous buck converter.

According to control theory, there are two closed loop design methods that can be used to design the digital controller [15]: The first method is the direct digital design, where a discrete time model of the system is first obtained then the controller is directly designed in the z-domain using famous methods like frequency response bode plots, or root locus method. Direct digital design has the advantages of better system response and the ability to achieve better phase and gain margins [15,16,19]. The other design method is the digital redesign where the controller is first designed in continuous time domain (s-domain) then transformed to z-domain using well known discretization methods [15,16]. Digital redesign has the advantages of easier design process and the ability to apply known analog controller design techniques [15]. For both design methods an accurate model for the different systems blocks must be first obtained [14, 22].

Table 2.1 shows a summary of continuous time models for different blocks of digitally controlled buck converter, where  $V_{in}$  is the input voltage,  $R_o$  is the load resistance which equals to  $V_o/I_o$ , L is the output inductor,  $R_L$  is the output inductor equivalent series resistance (DCR),  $C_o$  is the output capacitance,  $R_C$  is the output capacitor equivalent series resistance (ESR),  $T_{samp}$  is the sampling time,  $K_{adc}$  is the ADC gain,  $T_{adc}$  is the delay caused by the ADC conversion time,  $V_{\max}_{adc}$  is the maximum voltage range that the ADC can sense,  $N_{adc}$  is the ADC resolution or number of bits,  $K_{pwm}$  is the DPWM gain,  $T_{pwm}$  is the delay caused by the DPWM,  $N_{pwm}$  is the DPWM resolution or number of bits, H(s) is the output voltage sensor gain, L(s) is

the system open loop gain, C(s) is the closed loop voltage reference to output voltage transfer function, and  $G_{comp}(s)$  is the conventional PID compensator transfer function. Matched Z transform [15] was used to get the discrete time model of the complete system. The equations summarized in Table 2.1 are used next in the discussion design example.

| Buck DC-DC converter<br>model working CCM                                                                                                                                            | $G_{vd}(s) = \frac{\bigwedge_{V_o}^{\wedge}(s)}{d} = \frac{\left(\frac{V_{in}R}{R+R_L}\right)(1+s\cdot R_C \cdot C)}{1+s\left[C\left(R_C + \frac{R\cdot R_L}{R+R_L}\right) + \frac{L}{R+R_L}\right] + s^2\left[\frac{LC\left(R+R_C\right)}{R+R_L}\right]}$ | (2.36)   |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|

| Buck DC-DC converter<br>model working DCM                                                                                                                                            | $G_{vd}(s) = \frac{\bigwedge_{o}^{\wedge}(s)}{d} = \frac{2V_o}{\sqrt{\frac{2 \cdot L \cdot f_s \cdot M^2}{R \cdot (1 - M)}}} \cdot \frac{(1 - M)}{(2 - M) + s \cdot R \cdot C \cdot (1 - M)}$                                                              | (2.37)   |  |  |

| Analog to Digital converter ADC model                                                                                                                                                | $G_{adc}(s) = K_{adc}e^{-sTadc} = \frac{1}{LSB} \cdot e^{-sTadc}$                                                                                                                                                                                          | (2.38)   |  |  |

| Pulse width modulation<br>PWM model                                                                                                                                                  | $G_{pwm}(s) = K_{pwm}e^{-sTpwm} = \frac{1}{2^{N}pwm} \cdot e^{-sTpwm}$                                                                                                                                                                                     | (2.39)   |  |  |

| Zero Order Hold                                                                                                                                                                      | $\frac{1 - e^{-sT_{samp}}}{sT_{samp}}$                                                                                                                                                                                                                     | (2.39.a) |  |  |

| Dealy                                                                                                                                                                                | $e^{-sT_{samp}}$                                                                                                                                                                                                                                           | (2.39.b) |  |  |

| output voltage $V_o$ sensor gain                                                                                                                                                     | $H(s) = \frac{V_{ref}}{V_{out}}$                                                                                                                                                                                                                           |          |  |  |

| System Open loop                                                                                                                                                                     | $L(s) = G_{adc}(s) \cdot G_{vd}(s) \cdot G_{pwm}(s) \cdot H(s)$                                                                                                                                                                                            |          |  |  |

| System closed loop<br>reference to output $C(s) = \frac{G_{comp}(s) \cdot G_{pwm}(s) \cdot G_{vd}(s)}{1 + G_{comp}(s) \cdot G_{pwm}(s) \cdot G_{vd}(s) \cdot G_{adc}(s) \cdot H(s)}$ |                                                                                                                                                                                                                                                            |          |  |  |

Table 2.1: A summary of continuous time models for different blocks of digitally controlled buck converter

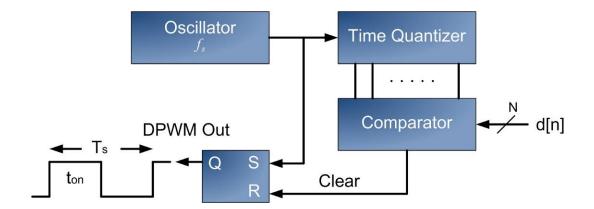

Fig. 2.6 shows a conceptual block diagram for a digital pulse width modulator (DPWM), in which an internal oscillator feeds a quantizer block where the oscillator frequency  $f_s$  or time  $T_s$  is divided into a discrete number of time slots each of length  $t_d$ . The selection of a particular time slot is made through the control word d[n] [45-49]. Changing the switching frequency of the DPWM can be performed by dividing the oscillator frequency by a number programmed in a register in the digital controller. This number also determines the total number of duty cycle steps over one switching cycle. The new switching frequency can be given by Equation (2.43) as follows [46]:

$$f_{PWM} = \frac{f_{osc}}{\text{Register}[0:N_{\text{steps}}]+1}$$

(2.43)

Where  $f_{PWM}$  is the DPWM switching frequency ( $f_{PWM} = f_{sw}$ ),  $f_{osc}$  is the DPWM oscillator clock frequency,  $N_{steps}$  is the number programmed the divider register. Note that it is assumed here that the DPWM is implemented in a counter-based architecture [45], for discussion purposes Other possible architectures are such as delay-line and hybrid architectures [23, 45-48].

Fig. 2.6: Conceptual block diagram of the DPWM unit [32].

Based on the Equation (2.43), in order to achieve higher switching frequencies, the total number of steps need to be reduced and hence the effective resolution of the DPWM,  $N_{pwm}$ , is reduced. Reducing the effective DPWM resolution increases the DPWM gain as given by Equation (2.39) in Table 2.1. Changing the DPWM gain,  $K_{pwm}$ , changes the total system gain, which results in performance change in the closed loop system, which may cause the system to run into instability. This effect does not exist in analog controllers since the PWM resolution does not change with switching frequency.

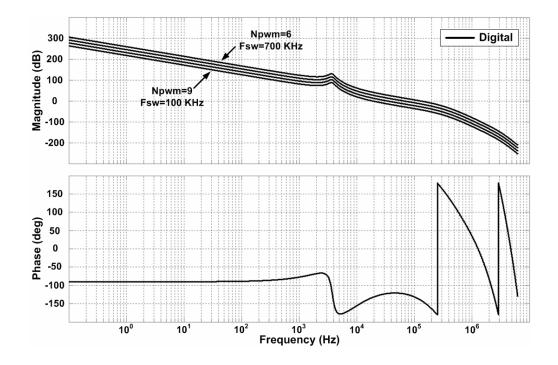

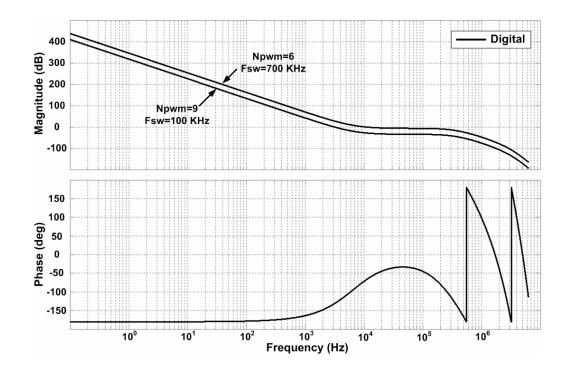

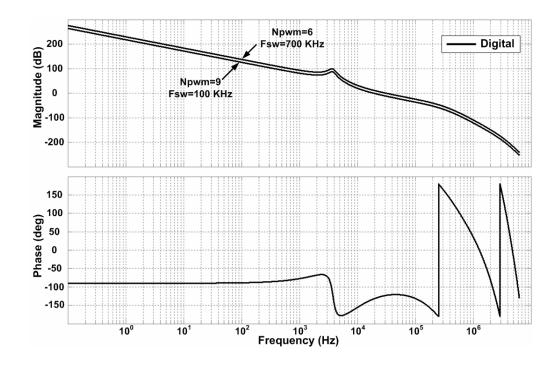

A synchronous buck converter closed loop is simulated (using Table 2.1 equations and Fig. 2.5 models), which has the same hardware specifications as in Section 2.6, to investigate the effect of variable switching frequency. The switching frequency is varied from 100 kHz to 700 kHz in digitally controlled buck converter. Fig. 2.7 shows the effect of changing the switching frequency in CCM and Fig. 2.8 shows the effect of changing the switching frequency in DCM. From Fig. 2.7, it can be noticed that varying the switching frequency in CCM using digitally controlled converter has changed the crossover frequency (from 18 kHz at  $f_{sw}$ =100 kHz to 106 kHz at  $f_{sw}$ =700 kHz for this design example) and also has changed the phase margin (from 48.5° at  $f_{sw}$ =100 kHz to 40.5° at  $f_{sw}$ =700 kHz).

From the above discussion, when designing a compensator for the variable switching frequency digital controller, the controller should also be designed to have a good phase margins that ensures stability over the entire switching frequency range, in addition to having a good phase and gain margins for different input voltages and loads. Next section discusses another issue resulting from varying the switching frequency digitally, the limit cycle oscillation issue, and an adaptive technique to alleviate these issues is presented.

Fig. 2.7: Digital variable switching frequency (by varying DPWM number of steps) effect in CCM mode

Fig. 2.8: Digital variable switching frequency (by varying DPWM number of steps) effect in DCM mode

## 2.5 Limit-Cycle Considerations and Proposed Dynamic Algorithm

Limit-cycle is undesired oscillation at the output of the DC-DC converter  $V_{out}$  at frequencies lower than the converter's switching frequency  $f_{sw}$  [19, 49-59]. The DPWM block generates a discrete number of duty cycle values, and if the output voltage does not correspond to one of those values, the feedback controller will oscillate between two or more discrete duty cycle values, which cause the output voltage to oscillate in what is known as limit cycle oscillation. For a fixed frequency DPWM, the limit cycle oscillation can be avoided by making sure that the output voltage change resulted from one LSB change in the duty cycle of the DPWM is smaller than the analog equivalent of the LSB of

the ADC [19]. In other words, the resolution of the DPWM should be always higher than the resolution of the ADC [53]. An exact relation for the minimum required resolution for the DPWM unit for a buck converter is given in Equation (2.44) [19]:

$$N_{PWM} \ge \operatorname{int} \left[ N_{adc} + \log_2 \left( \frac{V_{ref}}{V_{\max_{adc}} \cdot D} \right) \right]$$

(2.44)

Where  $V_{ref}$  is the closed loop reference voltage and the rest of parameters where defined earlier in the chapter. To achieve the output voltage regulation requirement, the ADC must sense voltage changes smaller than the variation in the output voltage  $\Delta V_o$ . The resolution of the ADC is given in Equation (2.45) [19]:

$$N_{adc} \ge \operatorname{int}\left[\log_2\left(\frac{V_{\max}_{adc}}{V_{ref}}, \frac{V_o}{\Delta V_o}\right)\right]$$

(2.45)

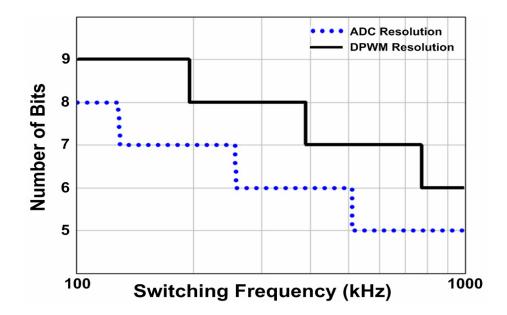

For a variable frequency digital controller that varies the switching frequency to achieve the optimum efficiency, the DPWM resolution will also vary since the total number of DPWM steps that controls the switching frequency changes. For example, when changing the switching frequency from 100 kHz to 800 kHz in a digital controller that uses a 50 MHz DPWM oscillator and a 9 bit DPWM register, the DPWM resolution changes from 9 bits to 6 bits. Therefore, optimizing the system resolution at switching frequency of 100 kHz to avoid limit cycle does not guarantee the elimination of limit cycle oscillation at all other switching frequencies.

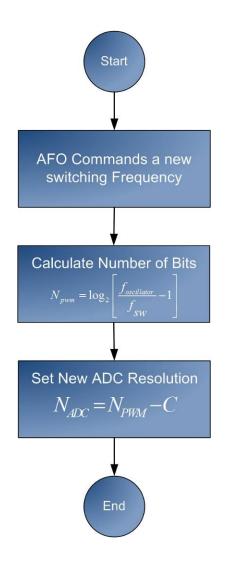

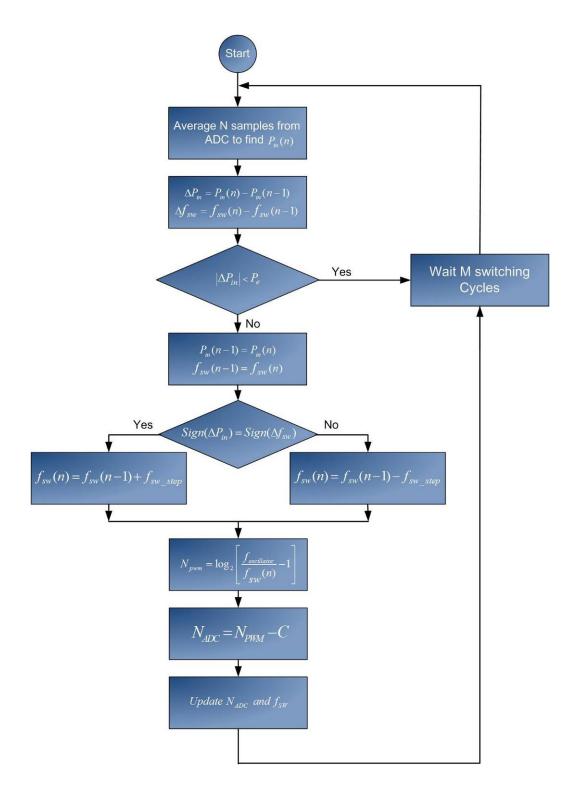

The need arises for adding another functionality to the AFO, and therefore, the Dynamic Limit Cycle Algorithm (DLCA) is presented in this section. The DLCA is a simple control algorithm that dynamically varies the ADC resolution as the switching frequency changes to avoid limit cycle oscillation, and at the same time, reduces the gain and phase changes discussed in the previous section [25]. Fig. 2.9 shows the dynamic limit cycle controller flowchart. Note that the algorithms of Fig. 2.4 and Fig. 2.9 form one completed algorithm as shown next in this chapter and in Fig. 2.13.

Fig. 2.9: Dynamic limit cycle controller algorithm flowchart.

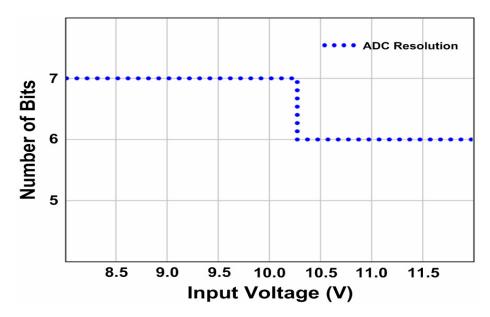

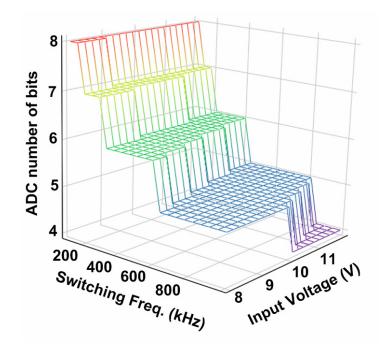

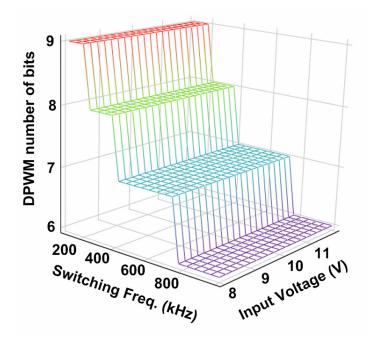

The DLCA algorithm starts by taking the new required switching frequency value from the AFO adaptive loop that determines the best switching frequency to optimize the efficiency. The first step is calculating the required number of steps and the DPWM resolution  $N_{PWM}$  to achieve the new commanded frequency at a certain PWM oscillator. From this value the algorithm calculates the new ADC resolution value to avoid the limit cycle as shown in Fig. 2.10 (a). Fig. 2.10 (b) shows the required ADC resolution to avoid the limit cycle problem at different input voltages and Fig. 2.10 (c) shows a surface plot of the switching frequency vs. the input voltage vs. the ADC required number of bits in order to avoid limit cycle. It can be noted from Fig. 2.10 that the required change in ADC resolution to avoid limit cycle over a wide frequency range is small, Maximum 2 bits in the frequency range 100 kHz to 500 kHz, and thus the effect of DLCA on dynamic behavior is minimal.