Electronic Theses and Dissertations, 2004-2019

2010

## Reconfigurable Architecture For H.264/avc Variable Block Size Motion Estimation Based On Motion Activity And Adaptive Search Range

Sumedha Kodipyaka University of Central Florida

Part of the Electrical and Electronics Commons

Find similar works at: https://stars.library.ucf.edu/etd

University of Central Florida Libraries http://library.ucf.edu

This Masters Thesis (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS Citation**

Kodipyaka, Sumedha, "Reconfigurable Architecture For H.264/avc Variable Block Size Motion Estimation Based On Motion Activity And Adaptive Search Range" (2010). *Electronic Theses and Dissertations*, 2004-2019. 1572.

https://stars.library.ucf.edu/etd/1572

# RECONFIGURABLE ARCHITECTURE FOR H.264/AVC VARIABLE BLOCK SIZE MOTION ESTIMATION BASED ON MOTION ACTIVITY AND ADAPTIVE SEARCH RANGE

by

#### SUMEDHA GUPTA KODIPYAKA B.E. Osmania University, 2007

A thesis submitted in partial fulfillment of the requirements

for the degree of Master of Science

in the Department of Electrical Engineering and Computer Science

in the College of Engineering and Computer Science

at the University of Central Florida

Orlando, Florida

Summer Term 2010

Major Professor Jooheung Lee @2010 Sumedha Gupta Kodipyaka

#### **ABSTRACT**

Motion Estimation (ME) technique plays a key role in the video coding systems to achieve high compression ratios by removing temporal redundancies among video frames. Especially in the newest H.264/AVC video coding standard, ME engine demands large amount of computational capabilities due to its support for wide range of different block sizes for a given macroblock in order to increase accuracy in finding best matching block in the previous frames.

We propose scalable architecture for H.264/AVC Variable Block Size (VBS) Motion Estimation with adaptive computing capability to support various search ranges, input video resolutions, and frame rates. Hardware architecture of the proposed ME consists of scalable Sum of Absolute Difference (SAD) arrays which can perform Full Search Block Matching Algorithm (FSBMA) for smaller 4x4 blocks. It is also shown that by predicting motion activity and adaptively adjusting the Search Range (SR) on the reconfigurable hardware platform, the computational cost of ME required for inter-frame encoding in H.264/AVC video coding standard can be reduced significantly.

Dynamic Partial Reconfiguration is a unique feature of Field Programmable Gate Arrays (FPGAs) that makes best use of hardware resources and power by allowing adaptive algorithm to be implemented during run-time. We exploit this feature of FPGA to implement the proposed reconfigurable architecture of ME and maximize the architectural benefits through prediction of motion activities in the video sequences ,adaptation of SR during run-time, and fractional ME refinement. The implemented ME architecture can support real time applications at a maximum frequency of 90MHz with multiple reconfigurable regions.

When compared to reconfiguration of complete design, partial reconfiguration process results in smaller bitstream size which allows FPGA to implement different configurations at higher speed. The proposed architecture has modular structure, regular data flow, and efficient memory organization with lower memory accesses. By increasing the number of active partial reconfigurable modules from one to four, there is a 4 fold increase in data re-use. Also, by introducing adaptive SR reduction algorithm at frame level, the computational load of ME is reduced significantly with only small degradation in PSNR (≤0.1dB).

#### **ACKNOWLEDGMENTS**

I would like to first thank my parents, Chandra Sekhar and Vishalakshmi, and my brother, Siddharth, who have been with me in every step of my life, helping me to succeed and instilling in me the confidence that I am capable of doing anything I put my mind to.

Special thanks to you my friend, Hari, for your practical and emotional support, helping me to consistently keep up to the competing demands of work, study and personal development.

I would also like to thank Dr. DeMara and Dr. Wang for their review and encouragement as Committee Members.

Most of all, I would like to thank Dr. Jooheung Lee for his excellent technical inspiration and editorial suggestions that helped me shape up this dissertation. Thank you for being a constant support as a mentor, right from the day one of my MS studies.

## TABLE OF CONTENTS

| A  | BSTRACT                                           | iii   |

|----|---------------------------------------------------|-------|

| A  | CKNOWLEDGMENTS                                    | vi    |

| T  | ABLE OF CONTENTS                                  | . vii |

| L  | IST OF FIGURES                                    | ix    |

| L  | IST OF TABLES                                     | X     |

| 1. | INTRODUCTION                                      | 1     |

|    | 1.1 Video Coding Standard                         | 1     |

|    | 1.2 Motion Estimation Technique                   | 2     |

|    | 1.3 Partial Reconfiguration and its Benefits      | 5     |

|    | 1.4 Motivation                                    | 7     |

|    | 1.5 Thesis Organization                           | 8     |

| 2. | BACKGROUND AND RELATED WORK                       | 9     |

|    | 2.1 Motion Estimation Algorithms                  | 9     |

|    | 2.1.1 Adaptive Search Locations                   | 9     |

|    | 2.1.2 Cost Reduction of Matching Criterion        | 10    |

|    | 2.1.3 Lossless Fast Full Search Algorithm         | 11    |

|    | 2.1.4 Mode Decision and Other Encoding Parameters | 12    |

|    | 2.1.5 Fractional Motion Estimation Algorithm      | 12    |

|    | 2.2 Motion Estimation Hardware Architectures      | 13    |

|    | 2.2.1 FSBMA Architectures                         | 13    |

|    | 2.2.2 Fast ME Architectures                       | 15    |

|    | 2.3 Summary                                       | 16    |

| 3. | MODULAR H.264/AVC VBSME APPROACH                  | . 17  |

|    | 3.1 Top Level Architecture                        | 17    |

|    | 3.2 Memory Management                             | 18    |

|    | 3.3 Partial Reconfigurable Module                 | 20    |

|    | 3.4 Data Flow                                     | 22    |

|    | 3.6 Block Mode Selector                           | 2/    |

|    | 3.6 Experimental Results                                                           | 26 |

|----|------------------------------------------------------------------------------------|----|

|    | 3.7 Summary                                                                        | 29 |

| 4. | ADAPTIVE SEARCH RANGE ALGORITHM AND IMPLEMENTATION                                 | 30 |

|    | 4.1 Video Coding Efficiency with Variable Search Range                             | 30 |

|    | 4.2 Search Range Reduction Algorithm                                               | 32 |

|    | 4.3 Proposed ME Architecture                                                       | 34 |

|    | 4.3.1 Top Level Architecture                                                       | 35 |

|    | 4.3.2 Memory Management                                                            | 36 |

|    | 4.3.3 Partial Reconfigurable Module                                                | 37 |

|    | 4.3.4 Data Flow                                                                    | 38 |

|    | 4.4 Experimental Results                                                           | 40 |

|    | 4.4.1 Simulation Results for Search Range Reduction Algorithm                      | 40 |

|    | 4.4.2 Proposed Partially-Reconfigurable ME Architecture Evaluation and Comparisons | 41 |

|    | 4.5 Hardware Implementation Results                                                | 43 |

|    | 4.6 Extended Approach for time multiplexing PRRs                                   | 45 |

|    | 4.7 Summary                                                                        | 46 |

| 5. | CONCLUSIONS                                                                        | 47 |

| 6. | REFERENCES                                                                         | 48 |

| 7  | PURUCATION                                                                         | 54 |

## LIST OF FIGURES

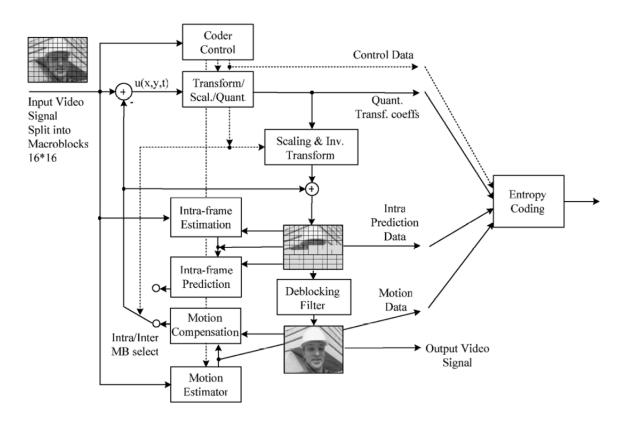

| Figure 1 Block diagram of hybrid encoding process for the H.264/AVC video coding standard [1]       | 1  |

|-----------------------------------------------------------------------------------------------------|----|

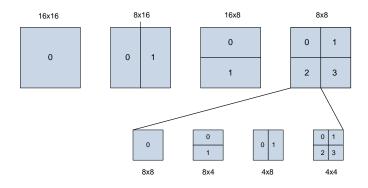

| Figure 2 Partitioning of macroblock in seven different block sizes                                  | 3  |

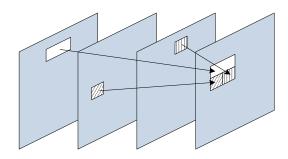

| Figure 3 Motion Estimation with multiple reference frames.                                          | 3  |

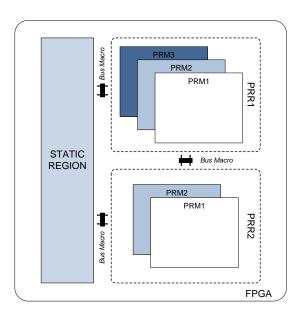

| Figure 4 Design layout of static and configurable regions in FPGA.                                  | 6  |

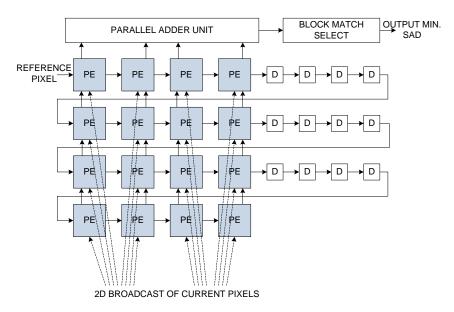

| Figure 5 Generalized 2D intra-level SAD hardware architecture supporting block size of 4x4          | 14 |

| Figure 6 Generalized 1D inter-level SAD architecture supporting SR of 8 horizontal direction        | 14 |

| Figure 7 Top level architecture of proposed VBSME.                                                  | 17 |

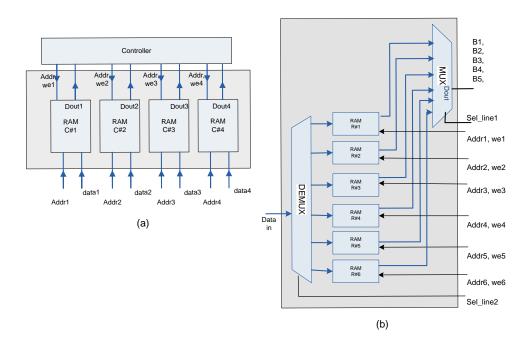

| Figure 8 (a) Current frame buffer structure (b) Reference frame buffer                              | 18 |

| Figure 9 Data scanning in the search window                                                         | 19 |

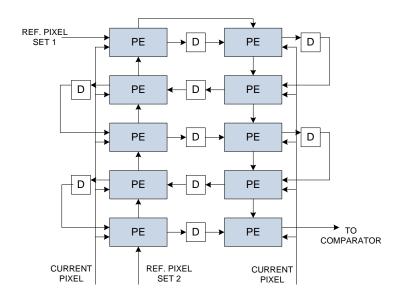

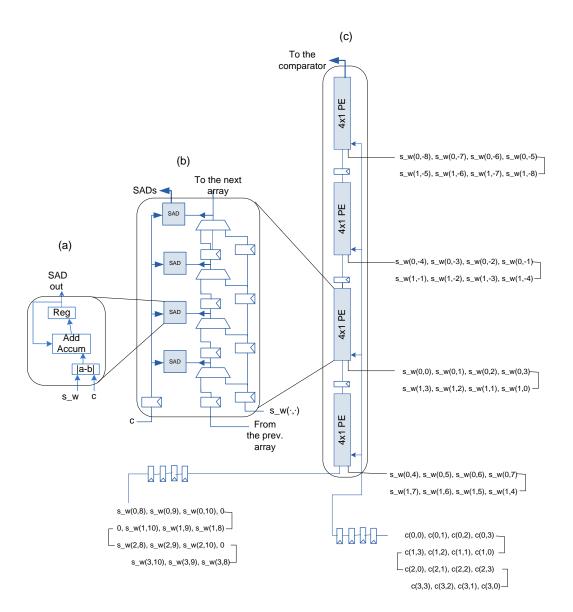

| Figure 10 (a) Structure of SAD block (b) Building block of one 41 PE                                | 20 |

| Figure 11 Number of blocks covered given the number of PRRs in active mode                          | 21 |

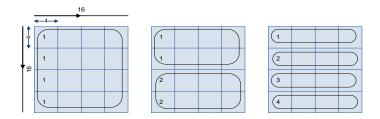

| Figure 12 Different configurations of 16x1 PE Arrays                                                | 21 |

| Figure 13 Variable Block Mode Selector for H.264/AVC Standard                                       | 24 |

| Figure 14 PSNR performance of H.264/AVC motion estimation for various video sequences               | 30 |

| Figure 15 SAD computations of H.264/AVC ME for various search ranges                                | 30 |

| Figure 16 Distribution of MVs for football video sequence (QCIF @30fps)                             | 31 |

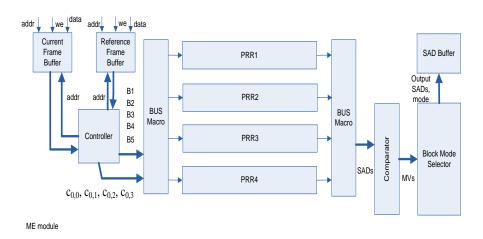

| Figure 17 Top level architecture for PRR ME supporting different search ranges                      | 35 |

| Figure 18 (a) General architecture of PR for 2-step SR (b) General architecture of PR for 4-step SR | 36 |

| Figure 19 Internal structure of 4x1 PE array                                                        | 37 |

| Figure 20 Data sharing among neighboring                                                            | 38 |

| Figure 21 Partitioning of SW into different 4 pixel width columns                                   | 38 |

| Figure 22 Top view of an integrated Integer-Fractional ME architecture on FPGA                      | 44 |

## LIST OF TABLES

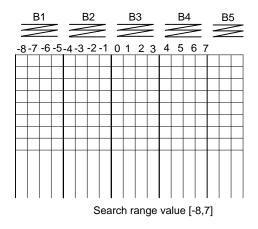

| Table 1 Dataflow for Proposed Reconfigurable Motion Estimation Algorithm, for SW[-8, +7]23        |

|---------------------------------------------------------------------------------------------------|

| Table 2 Bitrate and PSNR comparison of VBSD scheme25                                              |

| Table 3 Various Criteria of Different Architectures27                                             |

| Table 4 Comparison of Different H/W Architectures for ME Algorithm for SR [-8, 7], N=16, N=428    |

| Table 5 Various Criteria of Different Architectures                                               |

| Table 6 Various Reconfigurable Architectures to Support Different Image Resolutions28             |

| Table 7 Hardware Resources                                                                        |

| Table 8 Bitstream Information                                                                     |

| Table 9 Best matching MVs covered with different SRs for football video sequence (QCIF @30fps) 31 |

| Table 10 Data Flow for different PRRs39                                                           |

| Table 11 Simulation results of SR Reduction Algorithm                                             |

| Table 12 Performance results for different PRR structures44                                       |

| Table 13 Hardware resources and bitstream information44                                           |

#### INTRODUCTION

#### 1.1 Video Coding Standard

Digital video compression is widely used and plays an integral part in providing 'network friendly' video representation. The technology progress in the fields of digital multimedia and wireless communication systems has demanded the development of several video compression standards over past two decades. The main goal of these standards is to develop efficient video coding design with improved picture quality and high rate-distortion efficiency. The H.264/AVC is the latest video coding standard developed by the ITU-T Video Coding Experts Group and the ISO/IEC Moving Picture Experts Group in 2003 [1], [2].

Figure 1 Block diagram of hybrid encoding process for the H.264/AVC video coding standard [1].

Compared to previous video coding standards, such as H.261/3 and MPEG-1/2/4, H.264/AVC provides many advanced coding techniques, such as integer DCT transform, intra prediction in the spatial domain, multiple reference pictures, variable block size motion estimation and compensation, context adaptive variable length coding, and context adaptive binary arithmetic coding to achieve higher coding efficiency. The standard related documents and reference software can be found in [3].

The H.264/AVC technique is based on hybrid video coding process. The general block diagram for hybrid H.264/AVC encoding process is shown in Figure 1. A given video is encoded frame by frame and each input frame is divided into several macroblocks. Each macroblock consists of 16x16 pixel data which is coded in Intra or Inter mode. In inter mode, the macroblock is predicted using Motion Vectors (MVs) which correspond to the displacement of the current block from its corresponding position in already coded previous frame(s). In Intra mode, the frame is coded without reference frame. The prediction scheme for Intra mode uses information of previous blocks of the same frame. In inter mode, the predictions error is transformed using integer transform, quantized and then the calculated coefficients are encoded. For frame reconstruction, the quantized coefficients of each block are inverse transformed at the decoder side. Since the encoding is done block by block, the reconstructed frame will have visible block structures. In order to reduce this blockiness, H.264/AVC introduces an in-loop deblocking filter. After the filter, each macroblock is completely decoded and stored for further processes.

#### 1.2 Motion Estimation Technique

Motion Estimation (ME) is a part of Motion Compensation prediction which provides the best MV and distortion data of all possible modes of a given macroblock. The motion prediction of macroblock is performed using the information of already transmitted previous image as a reference.

Figure 2 Partitioning of macroblock in seven different block sizes

**Figure 3** Motion Estimation with multiple reference frames.

ME techniques play a key role in the video coding systems to achieve high compression ratios by removing temporal redundancies among video frames. Especially in the H.264/AVC standard, ME engine demands large amount of complex computational capabilities due to its support for wide range of different block sizes for given macroblock in order to increase accuracy in finding best matching block. The partitions of a macroblock and sub-macroblock are shown in Figure 2. Also, in H.264/AVC, it is possible to refer to multiple reference frames. Figure 3. shows the concept of motion compensated prediction with multiple reference frames. It is shown that more than 60% of the video encoders computational time is consumed by the ME module [4].

The macroblock is partitioned as 16x16, 16x8, 8x16, and 8x8 block sizes. The 8x8 sub-block, can be further divided into partitions with block sizes 8x4, 4x8, and 4x4. Introduction of such smaller

blocks can more accurately find the best matching block match in the previous frame and also reduce the resultant residual errors to be encoded [5]. Hence, Variable Block Size Motion Estimation (VBSME) can achieve higher coding performance at the cost of increase in computational complexity. Therefore, efficient and hardware-friendly VBSME architectures are critical for high-performance video encoder.

In Full Search Block Matching Algorithm (FSBMA), for each macro block (MB) in the current frame, the most similar MB within all possible locations in the Search Range (SR) in the reference frame is chosen. Sum of Absolute Differences (SAD) is a commonly used matching criterion for ME algorithm [6]. For a block-based ME, its basic functions are to calculate and compare the cost function used as a matching criterion between the current image block and all candidate blocks in the search range of reference frame. Let the block size be N×N and location of each block in the current frame (C) is represented by (i, j). This block must be matched with a block within the search window (h, v) in the reference frame (R). SAD of such searching candidate block is given by

$$SAD_{(i,j)}(x,y) = \sum_{x=0}^{N-1} \sum_{y=0}^{N-1} \left| C_{(i,j)}(x,y) - s_{-}w_{(i,j)}(x1+x+h,y1+y+v) \right| \tag{1}$$

Where, c(x,y) and  $s_w(x,y)$  represent pixel value in current block and search candidate block respectively. (x1, y1) represents center of the search range for the given macroblock in the reference frame. While computationally expensive, FSBMA offers high encoding efficiency, very regular computational algorithm, and hence good visual quality. In order to speed-up this process, data-adaptive ME algorithms have been introduced to modify the search center location by adaptively forming correlations among neighboring MVs.

#### 1.3 Partial Reconfiguration and its Benefits

Field Programmable Gate Arrays (FPGAs) are digital Integrated Circuits (ICs) that contain configurable logic blocks and interconnects. FPGAs are being targeted in many applications, such as high performance signal processing applications, to provide real-time computing capabilities. This is due to the fact that they incur very low-to-none Non-Recurring Engineering (NRE) costs and faster development time. Each generation of FPGAs are made significantly useful by introducing additional benefits and utilities with larger size and faster speed. Among such significant advancements is Dynamic Partial Reconfiguration [7]. Their main feature of partial reconfiguration process is to reconfigure a part of the device while the other parts of the FPGA are still active.

In SRAM-based FPGAs, initialization of device involves loading the device with configuration data or configuration bitstream in order to make FPGA perform some task. This configures all the logic blocks, interconnects and Input/Output (I/O) interfaces. FPGAs can be partially reconfigured by loading it with partial configuration bitstream file. The partial bitstreams can be generated by two methods: difference-based and modular-based processes [8]. In difference-based method, partial bitstreams contain information of the difference between original and new bitstream file so that only those logic blocks are modified. This method may not apply to real-time adaptive applications as both the original and the new configuration bitstream files may not be always available.

In modular-based partial reconfiguration, specific areas are assigned as Partial Reconfigurable Regions (PRRs) which can have several Partial Reconfigurable Modules (PRMs). Figure 4 shows the design layout of modular-based process. The static and reconfigurable regions communicate through I/O ports called Bus Macros (BMs). When FPGA is loaded with partial bitstreams, PRR region can be modified.

**Figure 4** Design layout of static and configurable regions in FPGA. This example consists of two PRRs with three and two PRMS respectively.

The main benefits of partial reconfiguration on FPGA are a) the unchanged part is not affected and, in some cases, may continue execution, and b) a partial bitstream size is smaller than a full bitstream and hence lower reconfiguration time. By time-to-time analysis, the modules which are not necessary can be detected and loaded with 'blank' bitstreams to reduce dynamic power consumption. Reconfigurable hardware of FPGA is one solution which can provide benefits of the performance of Application Specific Integrated Circuits (ASICs) and the flexibility of General Purpose Processors (GPPs). They now accommodate digital systems with more than 10 million equivalent gates in its reconfigurable fabric. Its capability to support various design configurations during run-time and dedicated hardware components, such as microprocessors, Digital Signal Processing (DSP) logics, memory blocks, and other specific modules, make FPGAs one of the ideal platforms to implement and test those computationally demanding real-time applications.

#### 1.4 Motivation

Firstly, ME is the most computationally intensive part in the entire video encoding system. In Full Search (FS) method, best MV with minimum SAD is calculated among HxV search positions as discussed in Section 1.2. For example, assuming each pixel undergoes 3 operations for given SR, i.e., absolute difference between current and reference pixel, adding the residues of all the pixels in given macroblock, and accumulate, ME for a QCIF (176x144), 30 frames per second (fps) video sequence with [-8, +7] SR takes 584 Mega operations per second (MOPS) and ME for SD (720x480), 30fps video sequence with [-16, +15], SR takes 32 Giga operations per second (GOPS). So, there is need to speed up ME process which can be done by methods like simplification of search criterion, data-adaptive algorithms, predictive search, etc, at algorithm level and enhanced data re-use, parallelizing SAD computations, etc, at architecture level. Keeping this thought, we develop an approach to gain algorithmic and architectural benefits through a) an adaptive search range reduction algorithm to reduce number of search candidates during run-time and b) a pipelined systolic SAD array architecture to improve performance and data reuse at intra 4x4 block level as well as inter block level.

Secondly, due to the ever increasing complexity of today's chip design, it becomes common to use pre-defined Intellectual Property (IP) cores to simplify the system design and meet the requirements such as manufacturing yield and time-to-market schedule. However, commercial IP cores available in the market are pre-constructed circuits with details of pre-determined area, power, and performance provided by the vendors, and typically target for both Application Specific Integrated Circuits (ASICs) and FPGAs markets. As a consequence, there is a need to develop IP cores which can be easily customizable to avoid mismatches of computing capability between users' applications and the IP cores, and run-time adaptable for time varying loads of computing while reducing design efforts from the users. These features are particularly desirable for real time video

processing systems involving dynamic adaptation to the characteristics of the target applications or other communication systems. Our design approach is towards developing a reconfigurable IP core to perform the computationally complex ME module, so that it can be used in diversified applications with user parameters passed to the control system in the IP core for adjustment of its architecture. We present in details hardware - reconfigurability strategy for development of IP core that can support block matching ME. It is also shown how our ME architecture can adapt with various search ranges (SR), video formats, and frame rates by designing efficient data sharing platform, memory organization, modular approach in hardware design, and different configurations of processing element (PE) arrays during run-time.

#### 1.5 Thesis Organization

Chapter 2 investigates various ME algorithms and architectures. The algorithms presented in this Chapter are mainly categorized as lossy and lossless methods. In lossy algorithms, the video quality is degraded when compared to FSBMA where in lossless methods the results are same as FSBMA. The various architectures discussed mainly consider memory organization, data flow, and latency issues. Chapter 3 presents a modular design strategy for ME hardware architecture to support different video formats and frame rates. This Chapter also discusses the implementation flow using partial reconfiguration on FPGA. As an extension, Chapter 4 presents search reduction algorithm to improve performance of FSBMA and hardware architecture with adaptive SR support. Also, we discuss an approach on time multiplexing reconfigurable area using dynamic partial reconfiguration by integrating the integer and fractional ME architectures. Finally, concluding remarks are given in Chapter 6.

#### BACKGROUND AND RELATED WORK

#### 2.1 Motion Estimation Algorithms

As discussed in Chapter 1, although its computations are costly, FSBMA is most accurate algorithm. Hence, it is taken as reference for best video quality. In this Chapter, various strategies to reduce the ME computational load and related work are discussed. The methods in Sections 2.1.1, 2.1.2, 2.1.4 are lossy and Section 2.2.3 is lossless [54].

#### 2.1.1 Adaptive Search Locations

In this class of lossy algorithm, ME is performed only on certain search points in order to reduce number of SAD computations. This approach can be classified into three types: a) Careful prediction of motion direction and selecting certain points for which ME is performed in given SR. b) Reducing the search window itself and perform ME in all locations of new SR. c) Hierarchical search with pyramid structure. All these algorithms are based on the assumptions that the motion in sequence of frames is regular and the distortion increases when the search locations move away from the minimum distortion position. Hence, by skipping such search points, computation load on ME is reduced significantly but with degradation of video quality. Some of the examples of type one are, three-step search developed in [9], [10], logarithmic search [11], [12], four step search [13], diamond search [14]. However, the search point selection is not regular and so is the data flow. Therefore, parallelizing the process of SAD computations and efficiency of memory access may not be feasible. The work of [15], considers these issues and shows an approach towards system optimization. For video sequences with large motion, these algorithms perform very poor and are sensitive to local minimum which further degraded ME accuracy.

The second type also called as Predictive Search, can be one of the solutions for the issues in type one algorithms. In this method, first the motion vector is predicted using the motion information of spatial or temporal neighboring blocks. This information along with the distortion (SAD) threshold, decides the final Motion Vector Prediction (MVP). In [16], MV of previous MBs on the top left, top, and top right are taken and their median is calculated. This result, zero MV block, and MV of corresponding MB in previous frames are considered to find MVP. In [17], the motion of MB is categorized as slow, medium, and fast mode to decide the search range.

In hierarchical ME algorithms, a pyramid structure of coarse to fine level search is adopted. First, ME is performed at coarse level and then refined by estimating around the initial MV. Two to three levels of hierarchy are used for finding final MV. The 3SS in [9], can be considered as hierarchical search. In the work of [18], a threshold for SAD value is introduced. The MV refinement is continued for several steps until an MV with SAD value less than the threshold is obtained. ME hardware architecture using hierarchical search method are given in [19], [20].

#### 2.1.2 Cost Reduction of Matching Criterion

In general, SAD block matching scheme involves matching of all pixel in a given block. One way to reduce this is sub-sampling scheme. In the work of [21], only every alternate pixel is considered for matching in both horizontal and vertical direction. This way, the computation load is reduced by four times than typical matching method. In the work of [22], only the edge pixels which are supposed to have important information are considered.

Pixel truncation is another lossy method to reduce hardware cost with small degradation in video quality. For example, 8-bit pixel can be reduce to 4-bits to reduce hardware resources to be used and can also reduce computations. The work of [23] presents an approach where pixel width can be changed adaptively.

#### 2.1.3 Lossless Fast Full Search Algorithm

One direct method of lossless algorithm is Partial Distortion Elimination (PDE) algorithm presented in [24]. If the accumulated partial distortion of candidate block is already larger than existing minimum SAD, the block can be skipped without any loss in image quality. Many other algorithms were developed based on partial distortion elimination method such as normalized PDE [25], probabilistic PDE [26], spiral PDE [27]. These algorithms find an approach to increase the early rejection process.

Successive Elimination Algorithm (SEA) is proposed in [28]. It is based on the mathematical fact that  $|A + B| \le |A| + |B|$  for all real values of A and B. If the absolute difference between sum of current block pixel sum and sum of reference (or candidate) block pixel is greater than existing minimum SAD value, then the corresponding block is eliminated. This is illustrated as

$$SAD(x,y) = \sum_{i=0}^{N} \sum_{j=0}^{N} |C(i,j) - R(i+x,j+y)| \ge |C_s - R_s| (SEA \ value)$$

(2)

Where  $C_s$  sum of is current block pixel and  $R_s$  is reference block pixel sum. Therefore, if SEA value is greater than minimum SAD, then it implies that its SAD value is greater than SADmin. SEA combined with good MVP method can increase the rejection ratio of SAD computations.

Winner Update algorithm presented in [29], [30] is based on the idea that we need not require to calculate the total sum in order to eliminate that candidate block. This can be explained by simple strategy employed in the game of poker. The winning player will have minimum sum of his cards. Each player shows one card initially and the player with lowest value card is allowed to show his second card and so on until the player with no cards left is the winner. The basic idea is if the intermediate sum of cards of a particular player already exceeds the total sum of the winning player then that particular player has no chance of winning. The same strategy can be applied to find minimum SAD of candidate blocks. However, implementation of sorting the SAD values is very

expensive in terms of hardware realization. All the algorithms explained in this Section have very minor difference in SAD calculation when compared to FSBMA. However, these minor differences do not cause noticeable effect on video quality.

#### 2.1.4 Mode Decision and Other Encoding Parameters

Mode decision is another important aspect which contributes towards increased computations of H.264/AVC ME. In the JM reference software, all the 16 sub-macroblocks starting with smallest 4x4 blocks are used and exhaustively searches for best mode. With this process, the encoding time for ME is increased significantly. The work in [31], presents a simplified version of mode decision strategy to use reduced number of sub-macroblock modes and effectively saves about 27% of bit-rate and significant computational time for ME with very little degradation in Peak Signal-to-Noise Ratio (PSNR) of the video sequence. In [32], Quantization Parameter (QP) is used for early detection of macroblocks with SKIP mode or with all-zero residue values and eliminates ME computations for that macroblock. Works in [33], [34] discuss about reduction in number of reference frames. All these algorithms are 'software-oriented' and become very complex to realize efficient hardware architectures.

#### 2.1.5 Fractional Motion Estimation Algorithm

The H.264/AVC VBSME consists of seven different block sizes ranging from 16x16 to 4x4. These sub-partitions lead to a large number of possible combinations within each macroblock. In general, large blocks are appropriate for homogeneous areas and small partitions are appropriate for textured and variant motion area. Especially in complex textured pictures, the accuracy of motion compensation is in quarter and half pixel resolution for H.264/AVC, which can provide better compression performance [3], [48]. The half-pixel MV refinements are performed around the best integer search positions, I, from IME results. The search range of half-pixel MV refinements is  $\pm 1/2$

pixel along both horizontal and vertical directions. This refinement has nine candidates, including the refinement center and its eight neighborhoods, for the best match. Then, quarter pixel refinement is performed in same fashion as half-pixel. The inter mode decision is done after all costs are computed in half-pixel and (or) quarter-pixel precision in all reference frames.

The reference pixels are interpolated to produce fractional pixels for each search candidate. Afterward, residues are generated by subtracting the corresponding fractional pixels from current pixels. Then, the absolute values of the 4×4-based residues are accumulated as distortion cost called SAD. The final matching cost is calculated by adding the SAD with the MV cost. The cost can be correctly derived only after prediction modes of the neighboring blocks are determined.

#### 2.2 Motion Estimation Hardware Architectures

#### 2.2.1 FSBMA Architectures

Integer pixel Full Search ME algorithm has an inherent property of common data dependency, which makes pipelining of such data possible in order to speed up the ME computations. Based on this algorithm, some efficient full search algorithms are proposed having 1-D and 2-D PE structures. In general, ME hardware architectures can be classified into two types: inter-level SAD architecture where each processing element (PE) is responsible for complete SAD for specific search location and intra-level SAD architecture where each PE is responsible for the partial absolute difference of a fixed current pixel location in the current MB, but for all search locations. In intra level architecture, the PE matrix size is confined to the MB size, hence occupies less area and further can be pipelined to design a faster ME engine.

Figure 5 Generalized 2D intra-level SAD hardware architecture supporting block size of 4x4.

**Figure 6** Generalized 1D inter-level SAD hardware architecture supporting SR of 8 horizontal direction.

Figure 5. shows generalized intra-level SAD architecture. In [35], [36], 2-D systolic PE array architecture was presented, where the number of PEs is equal to the MB size. The architecture has excess registers for the reference data to propagate and the search sequence is meander-like scanning.

Due to number of additional registers, this architecture has comparably low performance and latency is degraded. In [37], [38], intra level 2-D array architecture was proposed which satisfies H.264 requirements with high performance. However, their architecture is supported by a data flow where actually 16 different PEs are accessing 16 different reference pixel data simultaneously, which increases the memory access per clock cycle.

In inter-level SAD architecture, the PE matrix size is dependent on the search window (SW) size and with a regular data flow design, the architecture can be designed for a 1-D to a 2-D systolic structure. Figure 6. illustrates inter-level SAD architecture. In such architectures, reference frame data are broadcasted into corresponding PEs to compute SADs. Although it requires more hardware to have high parallelism, this type of approach effectively reduces the memory bit width. Hence, there is always a trade-off in ME engine performance, hardware area utilization, and most importantly memory bandwidth.

The work in [39] implements 1-D PE architecture which uses pipelining to improve the data reuse. However, it may not support the present ME which deals with various sub-blocks within each macroblock. The proposed works in [38], [40] have such 2-D array structures and can achieve high throughput. These architectures are scalable and have the scope for extending the level of parallelism. However, both of the works use ASIC design based on fixed hardware architecture.

#### 2.2.2 Fast ME Architectures

Architectures for fast ME algorithms can reduce the hardware cost and decrease the computation time with acceptable video quality. The main challenges include design of unpredictable data flow, memory access and sorting out systolic mapping. For example, a simplified architecture of three step search is presented in [41]. A real chip for 3SS is realized in [42] with 0.8um technology. Several architectures for other fast ME algorithms are also discussed. But in general, only the

simplified fast ME algorithms are chosen to facilitate the hardware realization such as the designs for Hierarchical Search [19], [20], Three Step Search [13], and Diamond Search [43]. In the work of [44], a hybrid model to support various algorithms is presented. The average computational cost reduction in this work is about 24%.

In this thesis, first reconfigurable PE arrays were designed to improve performance and data reuse at 4x4 block level, but for fixed SR. This can be used to extend the architecture from 1-D to a faster 2-D SAD architecture. Further, we show how this SAD array architecture can be modified and reconfigured to support various SRs. If there is few motion activities in the sequence (for example, video captured by the surveillance camera in the hall way during night time), SR can be reduced further, resulting in reduction of power and hardware resources used.

#### 2.3 Summary

Motion estimation engine is usually the most important module in the video encoding process. Significant amount of time is spent in software based module and demands good amount of hardware and memory bandwidth. In this Chapter, we made a detailed study of block matching algorithms and architectures during the past two decades. A lot of work has been done to reduce the computational load of ME through variety of software algorithms. However, hardware realization may not be feasible for each and every algorithm developed on software. The main challenge lies in developing hardware-oriented computational reduction algorithms, which can adapt different parameters and their corresponding adaptable hardware resources during run-time without turning-off the ME process for reconfiguration. The works discussed in this Chapter can be an inspiration for solving this challenge.

#### MODULAR H.264/AVC VBSME APPROACH

#### 3.1 Top Level Architecture

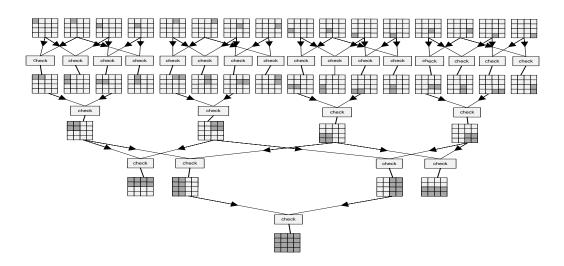

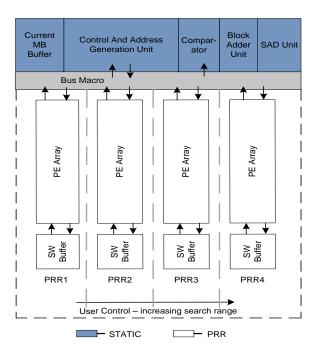

Figure 7 Top level architecture of proposed VBSME.

The top level architecture of proposed scalable ME design is shown in Figure 7. The ME module is divided into static region and reconfigurable region. The static region of ME module consists of current frame buffer, reference frame buffer, controller, comparator, block mode selector, and SAD buffer. These modules remain unchanged after initial configuration. Controller generates the address to fetch the data from current frame buffer and reference frame buffer. The results of 12 bit SAD value of 4x4 blocks from the reconfigurable region and 8 bit motion vector information from the comparator unit are propagated into the block mode selector unit where the best block size is determined. These final block modes, SADs, and corresponding MVs are stored in SAD buffer. In our implementation, 16 minimum SADs for each MB are computed and the best block mode and corresponding MV are stored into SAD buffer. The tracking range used for our implementation purpose is [-8, +7]. In this work, four modules, i.e., from PRR1 to PRR4, are included and tested to implement scalable ME computation. Each module is defined as a partial reconfigurable region

(PRR). Bus Macros (BM) are used to connect signals between static region and PRR. Each PRR can compute ME computation for 4×4 blocks within the search window.

#### 3.2 Memory Management

The current frame buffer stores all the 256 pixels of current MB in internal BRAM memory. In order to increase throughput of memory access, it is divided into 4 dual port BRAMs with data width of 8 bits and depth of 64 pixels as shown in Figure 8(a). Each BRAM stores pixel information of four 4×4 blocks in a row at a given current MB. Depending on the number of active PRRs, the data flows into each PRR through the controller. For example, if all four PRRs are active, then PRR1-PRR4 receives current pixel information from C#1 - C#4 respectively.

Figure 8 (a) Current frame buffer structure (b) Reference frame buffer

Figure 9 Data scanning in the search window

The design also includes six memories for reference frame buffer as shown in Figure 8(b). The search window is divided into five columns, having row size of 4 pixels, as shown in Figure 9. The column height is equal to the vertical size of search window. In our case, it is 31 pixel high. This information is stored in the BRAM with data width of 8 bits and depth of 31x4 pixels. The sixth BRAM is used as a temporary buffer for loading next search pixel values in parallel.

At the beginning of the motion estimation process, the first search window is stored in the reference buffer R#1 – R#5 as shown in Figure 8(b). While first round of SAD computations is taking place, the memory R#6 is loaded with next 31×4 pixels required for SAD computation of four 4×4 blocks of 2nd column of corresponding MB. Now, for this 2nd round of SADs, memories R#2 – R#6 are used, and simultaneously R#1 is updated with next pixel information. Therefore, bottle neck problem of memory accesses can be avoided in consecutive SAD iterations.

## 3.3 Partial Reconfigurable Module

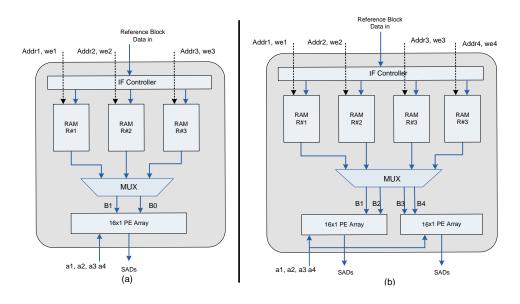

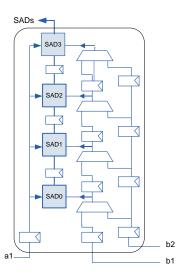

**Figure 10** (a) Structure of SAD block (b) Building block of one 4×1 PE (c) Architecture of one PRR with 16×1 PEs

Figure 11 Number of blocks covered given the number of PRRs in active mode.

More the number of divisions imply more the degree of parallelism.

Figure 12 Different configurations of 16x1 PE Arrays

Figure 10. shows the internal structure of a 16×1 PE array. This unit consists of 16 SAD Units, responsible for simultaneously calculating SADs of all the search locations of one row [-8, +7] (i.e., 16 pixels) in the search window. The four PRRs are responsible for calculating SADs of four 'different 4x4' blocks simultaneously. For this, 1, 2 or 4 PRRs can be configured for computation.

Now, by increasing number of 16×1 PE Arrays, for calculating SAD for the 'same 4x4' current block, data reuse and performance can be improved. This can be done by introducing PRR5, which contains additional 4 16x1 PE arrays, the data reuse for each block is improved and so is the SAD computation speed. Each 16x1 PE array here will compute SADs for the first column of four 4x4 blocks in Figure 11. While the PRR1-4 compute SADs of search candidates of a particular row, PRR5 computes SADs for search candidates of next row simultaneously but with initial latency of 4

clock cycles. The various types of modules that can be configured are shown in Figure 12. For implementation purpose, we use reconfigurable PRR1 – PRR4.

#### 3.4 Data Flow

The absolute difference (AD) of specific pixel in current block and reference block can be computed as shown below

$$AD_{(i,j)}^{(x,y)}(h,v) = |C_{(i,j)}(x,y) - s_{-}w_{(i,j)}(x+h,y+v)|$$

(3)

Here, (x, y) is pixel location within block, i.e.,  $0 \le (x, y) \le n-1$ . Part of search window  $(s_w)$  is observed to be common with neighboring blocks. So, this search window data can be exploited by using 4 PRRs where each PRR computes SAD of neighboring block. Hence, data reuse is improved by increasing number of PRRs from 1 to 2 and 2 to 4. From equation (2), it is clear that current pixel information c(x, y) is common for evaluating every SAD (h, v) where  $-8 \le (h, v) \le +7$ . So, this data can be shared with all search candidates row-wise (h) as well as column-wise (v). If we implement one  $16 \times 1$  PE Array, all search locations with common 'h' are computed in parallel. This parallelism can be extended to 2-D, i.e., for all 'h' as well as 'v' by implementing two  $16 \times 1$  (partial data reuse improvement) or four  $16 \times 1$  (full data reuse improvement) PE Arrays. These  $16 \times 1$  PE arrays share the current block data and search window data. Now each of PRR1 – PRR4 uses one PE array. If we introduce four more arrays (PRR5), two rows of pixel values in the search window can be processed simultaneously. Similarly, if we introduce PRR6, then four rows of pixel values in the search window can be processed simultaneously.

**Table 1** Dataflow for Proposed Reconfigurable Motion Estimation Algorithm, for Search Window [-8, +7]

|                     |               |                         | SADs of corresponding 4x4 Blocks, i.e., SAD <sub>(i, j)</sub> |                      |                      | Showing SAD flow of first current block | Showing SAD flow of first current block |

|---------------------|---------------|-------------------------|---------------------------------------------------------------|----------------------|----------------------|-----------------------------------------|-----------------------------------------|

| B5, B4, B3, B1, B2  | С             | SAD locations<br>(h, v) | (1PRR)                                                        | (2PRRs)              | (4PRRs)              | PRR(1-5)                                | PRR(1-6)                                |

| s_w(-8,-8)-(-8,10)  |               |                         |                                                               |                      |                      |                                         |                                         |

| s_w(-7,-7)-(-7,10)  | c(0,0)-c(0,3) |                         |                                                               |                      |                      |                                         |                                         |

| s_w (-6,-6)-(-6,10) | c(1,0)-c(3,3) |                         |                                                               |                      |                      |                                         |                                         |

| s_w (-5,-5)-(-5,10) | c(2,0)-c(3,3) |                         |                                                               |                      |                      |                                         |                                         |

| s_w (-4,-4)-(-4,10) | c(3,0)-c(3,3) |                         |                                                               |                      |                      |                                         |                                         |

| s_w (-3,-3)-(-3,10) | c(0,0)-c(3,3) | (-8,-8) - (-8,7)        | SAD <sub>(0,0)</sub>                                          | SAD <sub>(0,0)</sub> | SAD <sub>(0,0)</sub> | SAD(-8,-8) - (-8,7)                     | SAD(-8,-8) - (-8,7)                     |

| s_w (-2,-2)-(-2,10) | c(1,0)-c(3,3) |                         |                                                               |                      |                      | SAD(-7,-8) - (-7,7)                     | SAD(-7,-8) - (-7,7)                     |

| s_w (-1,-1)-(-1,10) | c(2,0)-c(3,3) |                         |                                                               |                      |                      |                                         | SAD(-6,-8) - (-6,7)                     |

| s_w (0,0)-(0,10)    | c(3,0)-c(3,3) |                         |                                                               |                      |                      |                                         | SAD(-5,-8) - (-5,7)                     |

| s_w (1,1)-(1,10)    |               | (-4,-8) - (-4,7)        | SAD <sub>(0,0)</sub>                                          | SAD <sub>(0,0)</sub> | SAD <sub>(0,0)</sub> | SAD(-4,-8) - (-4,7)                     | SAD(-4,-8) - (-4,7)                     |

| s_w (2,2)-(2,10)    |               | (-8,-8) - (-8,7)        |                                                               | SAD <sub>(1,0)</sub> | SAD <sub>(1,0)</sub> | SAD(-3,-8) - (-3,7)                     | SAD(-3,-8) - (-3,7)                     |

| s_w (3,-8)-(3,10)   |               |                         |                                                               |                      |                      |                                         | SAD(-2,-8) - (-2,7)                     |

|                     |               |                         |                                                               |                      |                      |                                         | SAD(-1,-8) - (-1,7)                     |

|                     |               | (0,-8) - (0,7)          | SAD <sub>(0,0)</sub>                                          | SAD <sub>(0,0)</sub> | SAD <sub>(0,0)</sub> | SAD(0,-8) - (0,7)                       | SAD(0,-8) - (0,7)                       |

|                     |               | (-4,-8) - (-4,7)        |                                                               | SAD <sub>(1,0)</sub> | SAD <sub>(1,0)</sub> | SAD(1,-8) - (1,7)                       | SAD(1,-8) - (1,7)                       |

| s_w (6,-8)(6,10)    |               | (-8,-8) - (-8,7)        |                                                               |                      | SAD <sub>(2,0)</sub> |                                         | SAD(2,-8) - (2,7)                       |

| s_w (7,-8)-(7,10)   | c(3,0)-c(3,3) |                         |                                                               |                      |                      |                                         | SAD(3,-8) - (3,7)                       |

|                     | c(0,0)-c(0,3) | (4,-8) - (4,7)          | SAD <sub>(0,0)</sub>                                          | SAD <sub>(0,0)</sub> | SAD <sub>(0,0)</sub> | SAD(4,-8) - (4,7)                       | SAD(4,-8) - (4,7)                       |

|                     |               | (0,-8) - (0,7)          |                                                               | SAD <sub>(1,0)</sub> | SAD <sub>(1,0)</sub> | SAD(5,-8) - (5,7)                       | SAD(5,-8) - (5,7)                       |

|                     |               | (-4,-8) - (-4,7)        |                                                               |                      | SAD <sub>(2,0)</sub> |                                         | SAD(6,-8) - (6,7)                       |

|                     |               | (-8,-8) - (-8,7)        |                                                               |                      | SAD <sub>(3,0)</sub> |                                         | SAD(7,-8) - (7,7)                       |

|                     |               | (-7,-8) - (-7,7)        | SAD <sub>(0,0)</sub>                                          | SAD <sub>(0,0)</sub> | SAD <sub>(0,0)</sub> | SAD(-6,-8) - (-6,7)                     |                                         |

|                     |               | (4,-8) - (4,7)          |                                                               | SAD <sub>(1,0)</sub> | SAD <sub>(1,0)</sub> | SAD(-5,-8) - (-5,7)                     |                                         |

|                     |               |                         |                                                               |                      |                      |                                         |                                         |

In the proposed architecture, the search window is divided into 5 columns and the pixel data are scanned simultaneously from these columns as shown in Figure 9. During initial 4 clock cycles, the pixel information of first row in the search window  $(s_w(0,0)(-8,v) - s_w(0,0)(7,v))$  is stored in the latches. In the next clock cycle, the current pixel information (c(0,0)) becomes available to each 16x1 PE array when it starts SAD computations. During this cycle, the next row pixel information in the search window is continuously read and pipelined into the latches. More precise details of data

flow into the latches are shown in Figure 10(c). These partial SADs are stored in each PE array After 16 clock cycles SADs are propagated into the comparator unit for MV generation. The detailed data flow for different PRRs architecture is shown in Table 1. According to the number of PRRs operating, the controller unit can efficiently have the data flow pipelined among the PRRs to increase data reuse.

#### 3.6 Block Mode Selector

Figure 13 Variable Block Mode Selector for H.264/AVC Standard

In the H.264/AVC standard, mode decision algorithm is left open to the developer. Given the quantization parameter (QP) and the Lagrange parameter,  $\lambda_{mode}$ , the mode decision can be performed by minimizing the following equation,

$$J_{mode} (MB_k, I_k | QP, \lambda_{mode}) = Distortion(MB_k, I_k | QP, \lambda_{mode}) + \lambda_{mode} \cdot Rate(MB_k, I_k | QP, \lambda_{mode})$$

(4)

Where  $I_k$  denotes all possible coding modes and their corresponding MVs. Due to the huge computation complexity and sequential issues in the high complexity mode of H.264/AVC, it is less suitable for real-time applications. In this Chapter, we discuss a low complexity mode decision [31].

The function of this unit is to merge SADs of 4x4 blocks that are exact matches. The resulting merge follows the rules of allowable block patterns for the H.264/AVC ME. For our implementation, merging decision is based on motion vectors of neighboring 4×4 blocks. If the MV displacements are exact match, then we merge the neighboring blocks [31]. The Variable Block Size Decision (VBSD) approach reduces the number of optimal sub-macroblocks for motion compensation operations and uses less hardware resources when compared to the technique used in JM software. Table 2. gives the comparison results of PSNR and bitrate with JM software. On an average, it reduces 5% of bitrate with only 0.04dB of PSNR degradation. In other words, data computational load is reduced and so is the ME computation time.

Figure 13. shows the block mode selector tree. The values of SADs and MVs are read from output of comparator unit. The comparator unit finds the best SAD for given block, by reading the output SADs from the PRR(s). The final resultant block mode and corresponding SADs are stored in the output SAD buffer unit.

Table 2 Bitrate and PSNR comparison of VBSD scheme

|        |               | Container | Carphone | Foreman | Football | Hall   | Suzie  |

|--------|---------------|-----------|----------|---------|----------|--------|--------|

|        | PSNR(dB)      | 36.348    | 37.398   | 36.711  | 36.560   | 37.711 | 37.568 |

| JM     | Bitrate(Kpbs) | 45.382    | 119.000  | 139.300 | 745.820  | 60.890 | 91.820 |

| [31]   | PSNR(dB)      | 36.319    | 37.345   | 36.655  | 36.472   | 37.676 | 37.555 |

| Scheme | Bitrate(Kpbs) | 44.007    | 117.020  | 124.350 | 696.330  | 58.059 | 90.440 |

|        | ΔPSNR         | -0.029    | -0.053   | -0.056  | -0.088   | -0.035 | -0.013 |

| VBSD   | Δbitrate      | -1.375    | -1.980   | -14.950 | -49.490  | -2.831 | -1.380 |

#### 3.6 Experimental Results

Table 5 gives the performance characteristics of our design when various reconfigurable structures are used. From this Table, it is clear that as the number of PRRs increases, the number of SADs that are computed in parallel also increases. This actually depicts the degree of parallelism and data reuse.

Table 6 shows the time required for SAD computations for each frame at a maximum clock frequency of 90MHz. Suppose the frame rate of a video sequence be 30fps, then the maximum allowable time that ME engine can take is 33ms for each frame. If the image resolution is either QCIF or CIF, we can reduce the hardware by using only 1 or 2 PRRs and still maintaining required ME time. However, if the image is of higher resolution, then a faster ME engine is needed. In that case, number of PRRs configured can be increased. Partial reconfiguration of these modules can allow best utilization of FPGA hardware resources.

At architecture level, the performance of our proposed architecture for different operating PRRs is compared with previous works of [45], [37], [46], [47]. Table 3 shows general characteristics of number of PEs, latency, operating cycles, bit width information summarizing the level of parallelism and data reuse. It also includes the scalability factor which plays important role in reconfigurable design methodology. The macro block size is taken as N×N and the smaller block as n×n. For block in the current frame, one reference block that is best match to it, in the search range of H×V, is selected. 'P' represents the number of 16x1 PE arrays present, i.e., P=1,2,4,8,16 for combination of PRRs(1), (1&2), (1-4), (1-5) and (1-6) respectively. 'q' represents number of current blocks accessed in parallel, i.e., q=1,2 or 4 for combination of PRRs(1), (1&2), [(1-4) or (1-5) or (1-6)] respectively. From the Table 5, it is clear that the ME engine speeds up with increase in PRRs and

at the same time only 1 PRR can be configured in applications where hardware resource and power consumption are critical criteria.

The memory bit width is defined as the number of bits the algorithm accesses from the memory in each cycle. It is one of the factors to determine efficient memory management and degree of parallelism. The works of [45], [37], and [47] compute 16 SADs in parallel hence have large bit width, but their data flow is not regular. Memory bandwidth is defined as the number of memory access to complete ME for one MB. It is the one to determine the efficient data reuse capability. From Table 4, it is shown that by increasing the number of PRRs, data reuse is significantly increased when compared to previous works.

Table 7 gives the synthesis result and Table 8 shows the partial bit stream size of each PRR module. The design is implemented on Xilinx Virtex2Pro (XC2VP30) FPGA development board. Synthesis is done using ISE Foundation Tool. The full and partial bit streams are generated using PlanAhead 10.1 Tool. Bitstreams obtained from the synthesized design are used to reconfigure the FPGA through JTAG.

**Table 3** Various Criteria of Different Architectures

| Architecture  | Latency     | Bit Width for ref. frame Operating Cycles |                                  | Scalability/<br>Modularity  |

|---------------|-------------|-------------------------------------------|----------------------------------|-----------------------------|

| [45]          | N           | 2 · N · 8                                 | [H·V]+N-1                        | Memory bitwidth constraints |

| [37]          | N           | (N + 1) · 8                               | $[H \cdot V] + N - 1$            | Memory bitwidth constraints |

| [46]          | N·(V+1)     | 2 · 8                                     | $[H \cdot V] + N \cdot (V+1)$    | -                           |

| [47]          | H + N       | N · 8                                     | $H \cdot (V + N)$                | -                           |

| Proposed work | n · (n + 1) | $[(H/n)+1]\cdot 8$                        | $[H\cdot V]\cdot (n^3/P\cdot R)$ | Yes                         |

**Table 4** Comparison of Different Hardware Architectures for VBSME Algorithm for Search Range [-8, 7], N=16, N=4

| Architecture (with r = 16x1) | Bit width for<br>ref. frame<br>(bits/cycle) | Bit width<br>for current<br>frame<br>(bits/cycle) | Bandwidth<br>for ref.<br>Frame<br>(Kbits/MB) |

|------------------------------|---------------------------------------------|---------------------------------------------------|----------------------------------------------|

| 1 PRR                        | 40                                          | 8                                                 | 184                                          |

| 2PRRs                        | 40                                          | 16                                                | 92                                           |

| 4PRRs                        | 40                                          | 32                                                | 46                                           |

| 8PRRs                        | 40                                          | 64                                                | 23                                           |

| 16PRRs                       | 40                                          | 128                                               | 11.5                                         |

| [45]                         | 256                                         | 1                                                 | 76                                           |

| [37]                         | 136                                         | -                                                 | 48                                           |

| [46]                         | 16                                          | -                                                 | 10.5                                         |

| [47]                         | 128                                         | -                                                 | 77.6                                         |

Table 5 Various Criteria of Different Architectures

| No. of PRRs | No. of SADs   | Buffer cycles<br>for each MB |

|-------------|---------------|------------------------------|

| 1           | 16/16 cycles  | 16                           |

| 2           | 32/16 cycles  | 32                           |

| 4           | 64/16 cycles  | 64                           |

| 5           | 128/16 cycles | 72                           |

| 6           | 256/16 cycles | 88                           |

Table 6 Various Reconfigurable Architectures to Support Different Image Resolutions

| Display Type   | Type of Reconfigurable architecture | Estimated time for SAD computation for each frame @ 90MHz |

|----------------|-------------------------------------|-----------------------------------------------------------|

| QCIF (174×144) | 1PRR                                | 5.5ms                                                     |

| CIF (352×288)  | 1PRR                                | 17.7ms                                                    |

|                | 2PRR                                | 9ms                                                       |

| 720×480        | 1PRR                                | 62ms                                                      |

|                | 2PRR                                | 31.7ms                                                    |

|                | 4PRR                                | 15.9ms                                                    |

| 1920×1080      | 1PRR                                | 366ms                                                     |

|                | 2PRR                                | 183ms                                                     |

|                | 4PRR                                | 92ms                                                      |

|                | 5PRR                                | 47.8ms                                                    |

|                | 6PRR                                | 24.6ms                                                    |

**Table 7** Hardware Resources

| Module                     | LUTs | UTs Slice Flip<br>Flops |   | BRAMs |

|----------------------------|------|-------------------------|---|-------|

| 16×1 PE Array              | 1109 | 871                     | - | -     |

| Static & Memory<br>Buffers | 874  | 327                     | 7 | 15    |

**Table 8** Bitstream Information

| Bitstreams | Size (Bytes) |

|------------|--------------|

| PRR1       | 90640        |

| PRR2       | 105472       |

| PRR3       | 90640        |

| PRR4       | 105472       |

#### 3.7 Summary

In this Chapter, we presented an approach to design integer pixel H.264/AVC variable block size scalable ME engine. Its regular structure, regular data flow, and memory management make it possible to implement IME-FSBMA. The Chapter includes all the modules like PE Array, mode selector, and memory unit. The proposed architecture has lower memory bandwidth and latency. Simulation results show that our design can increase data reuse significantly and thereby reduce the memory bandwidth overhead. Further through partial reconfiguration approach, depending on input image resolution, it can adopt suitable number of PRRs during runtime. In summary, our architecture presents an inherent capacity to adjust the hardware resources, which forms basis for a novel self adaptive full-search algorithm.

# ADAPTIVE SEARCH RANGE ALGORITHM AND IMPLEMENTATION

#### 4.1 Video Coding Efficiency with Variable Search Range

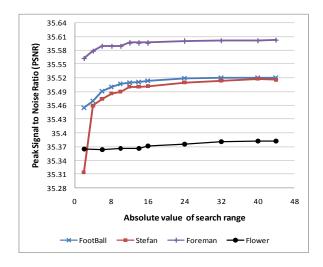

In video coding applications, the search range for motion estimation should be large enough to cover the motion displacements, but at the same time, increase in the SR also causes a problem of increasing computational overhead. Figure 14. shows the Peak Signal to Noise Ratio (PSNR) performance of H.264/AVC using motion estimation with different Search Ranges (SR), and 40 frames from different video sequences with CIF (352×288 pixels) resolution are encoded at 30fps.

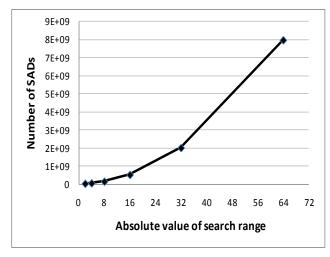

The results show that after SR ( $\pm$  32), the PSNR is saturated indicating significant increase in computational overhead. This is illustrated in Figure 15, where computational cost is calculated as the number of SAD evaluation for full search ME algorithm.

**Figure 14** PSNR performance of H.264/AVC motion estimation for various video sequences

**Figure 15** SAD computations of H.264/AVC ME for various search ranges

H.264/AVC standard introduces other new features, such as multiple reference frames and up to quarter pixel resolution ME. Applying these two methods for all the search points, further increases the computational load, making hardware implementation essential. In order to accelerate these computations, quarter pixel ME can be performed by using certain integer pixel points which have lowest coding cost. Therefore, the performance of integer pixel ME at the first round needs to be more accurate so that the following sub-pixel ME can produce the best results. Therefore, after an efficient motion vector prediction, the search range center can be set depending on surrounding motion vectors. This can be useful to reduce the SR size [JVT-P026]. There is a good chance that the search range can be reduced for the same video sequence depending on the behavior of motion vectors of neighboring blocks as well as previous frames without much degradation of PSNR and compression ratio.

**Table 9** Percentage of the best matching MVs covered with different search ranges for football video sequence (QCIF @30fps)

| SR  | PSNR   | Bitrate | % of vectors covered |  |  |

|-----|--------|---------|----------------------|--|--|

| ±8  | 36.545 | 738.75  | 87.61                |  |  |

| ±16 | 36.553 | 713.42  | 91.66                |  |  |

| ±24 | 36.596 | 705.67  | 98.49                |  |  |

| ±32 | 36.617 | 692.93  | 100.00               |  |  |

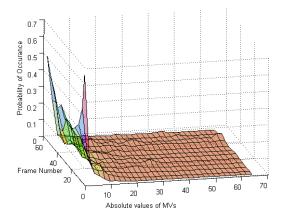

Figure 16 Distribution of MVs for football video sequence (QCIF @30fps)

Figure 16. shows the example of absolute motion vector displacements after applying prediction-based MV and re-evaluating center of search range. The x-axis gives the absolute value of motion displacement vector and the y-axis gives the probability of occurrence for different values of MVs. Table 9. gives the performance variation for different values of SRs. Analysis has been performed for various sequences and is derived that most of the best motion vectors are very near the predicted center of SR and hence by adaptively reducing the SR, we can achieve great reduction in computational complexity as well as hardware resources used.

From careful analysis of these plots for various video sequences, we conclude that more than 90% of the MVs fall under the search range of  $\pm 6$  to  $\pm 12$  (for QCIF resolution @30fps) with very small degradation in video quality. From the above analysis, it is derived that by reducing the SR further, we can reduce the computational complexity of ME.

# 4.2 Search Range Reduction Algorithm

Performing exhaustive search is computationally very expensive and adds great complexity to ME. A full search algorithm for each block candidate requires [(2R+1)·2] SAD computations where [+R,-R] is the search window size. We present an approach to reduce this search range (R) adaptively based on the correlation of the motion vectors as described in Section 4.1. This approach is based on the assumptions that motion field is smooth and changes slowly frame by frame. The correlation among MVs for the neighboring blocks is very high and hence current MV is likely to be near the search center which is predicted by using the previously encoded MVs of the neighboring blocks.

The adaptive search range algorithm can be described in the following steps:

- a) Initially set the SR for all the reference frames (for the case of multiple or single referenced frame algorithm) to maximum SR (i.e., [-32, +32]).

- b) Perform prediction algorithm as used in the JM software and obtain Motion Vector Prediction (MVP). Then, set the SR center in the reference frame accordingly. For simplicity in hardware implementation, all the block types for current macroblock share the same MVP (Fast Full Search in JM).

- c) Perform Fast Full Search ME and simultaneously store the number of MVs falling into different category of absolute displacement. (i.e., number of MVs with displacement 0,1,2, and so on). The averaged MV, MV<sub>avg</sub>, for a given macroblock in previous R reference frames is estimated by the equation below:

$$MV_{avg} = \frac{1}{R} \sum_{r=1}^{R} \frac{1}{M} \sum_{i=1}^{M} m v_{ri}$$

(5)

Where M is number of sub-blocks in each macroblock. The optimal SR can be estimated by using this  $MV_{\rm avg}$ .

- d) Set the search range for the next frame such that the SR covers at least Th (Threshold) % of total MVs. 'Th' can vary from 90-100% depending on the user requirement: higher performance/PSNR, less computational complexity or hardware resources utilized, and so on. There are some algorithms which update SR at macroblock level for software oriented implementations. In our approach, SR is updated at frame level. Hence, it is assumed that SR is fixed for all macroblocks in particular frame.

- e) Given minimum SAD threshold increase or maintain the new SR. The SAD threshold for given average MV of a frame is listed in [51].

- f) Continue from step (b) onwards.

#### 4.3 Proposed ME Architecture

As discussed in Chapter 1, the basic functions of a block-based ME are to calculate and compare the matching criterion between the current image block and all candidate blocks in the search range of reference frame. In H.264/AVC, seven different block sizes are specified for ME process as shown in Figure 2. Therefore, an ideal encoder has to examine all possible combinations of MB division modes to select the best mode among them. Hence, VBSME improves motion tracking over fixed block size algorithm especially by giving attention to highly active sub-block. A 4x4 block can be considered as a preliminary block. Using SAD of this sub-block, SADs of larger blocks can be computed by simply adding the corresponding sub-block SADs. A total of 41 sub-blocks including macroblock have to be evaluated for the motion vector selection. In SR reduction approach discussed earlier (Sections 4.1, 4.2), we consider MVs corresponding to all the 41 sub-blocks for setting suitable SR for the following frame.

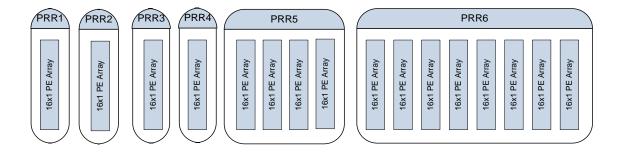

The ME architecture is separated into different Partial Reconfigurable Regions (PRRs). Each PRR consists of PE arrays, where each PE is responsible for computing SAD of a specific searching candidate. In the later Sections, we show how each PRR can be configured to support increasing or decreasing SR in steps of 2, 4 and 8 (in both X and Y directions). Increasing the number of PRRs: 1,2,3,4 can support SRs with  $\pm 2$ ,  $\pm 4$ ,  $\pm 6$ ,  $\pm 8$  respectively if the PRR is configured for 2-step SR. Similarly, to support set of SRs [ $\pm 4$ ,  $\pm 8$ ,  $\pm 12$ , and  $\pm 16$ ], the PRRs can be configured for 4-step SR.

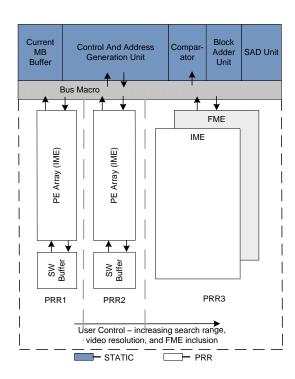

#### 4.3.1 Top Level Architecture

Figure 17 Top level architecture for partially reconfigurable ME supporting different search ranges

The modified top level architecture to support different SRs is shown in Figure 17. The architecture discussed in Chapter 3, forms the basis of this new architecture. In Section 3.2, it is discussed that the reference frame buffer size depends on the number of horizontal search range pixels. For example, if SR is ±8, we need five buffers; each one storing four column lengths of reference pixels. But now as SR is not fixed, the reference frame buffer also changes. Hence, it is desirable to move this buffer into reconfigurable area along with PE array. In our implementation, SADs for each 4x4 block are computed, sent to block mode selector unit, and the resultant MVs and corresponding SADs are stored in SAD buffer. For implementation purpose, we configured the PRRs for 2-step SR. In this work, four modules, i.e., from PRR1 to PRR4, are included and tested to implement scalable ME computation.

#### 4.3.2 Memory Management

**Figure 18 (a)** General architecture of partial reconfiguration module for 2-step SR (b) General architecture of partial reconfiguration module for 4-step SR

Memory management becomes an essential aspect for modular designs as the data flow into each module should be made regular and at the same time memory bandwidth should be at the minimum level. The current frame buffer architecture is discussed in Section 3.2. Its size is equal to MB size, i.e. 16x16 pixels. As all the sub-blocks in a macroblock are assumed to share same MVP, SR is overlapped between different 4×4 sub-blocks. In our PE design, we pipeline four 4×4 blocks to effectively re-use the SR data.

To support 2-step SR, the reference frame buffer includes 3 BRAMs as shown in Figure 18(a). Each BRAM stores 4×V pixels from the reference frame, where 'V' is the vertical height of SR covering one macroblock. R#1 stores these pixel data and R#2 stores the additional 3 pixel data needed for border 4×4 block positions in SR. Third BRAM is used as a temporary buffer for loading next search pixel values simultaneously. This can be one approach where the data flow is not interrupted and SAD computations can be performed continuously for different blocks.

## 4.3.3 Partial Reconfigurable Module

Figure 19 Internal structure of 4x1 PE array

Figure 19. shows the internal structure of 4×1 PE array, having 4 SAD units. Each PRR consists of four such PE arrays including total of 16 SAD units (SAD0-SAD15). The four sets of SAD array (SAD0-SAD3), (SAD4-SAD7), (SAD8-SAD11), and (SAD12-SAD15) are responsible for simultaneously calculating SADs of four 4×4 blocks corresponding to a column of particular macroblock.

Each PRR is responsible for SADs of  $\pm 2$  SR for four blocks and by increasing the PRRs from 1, 2, 3, and 4, the ME design can support  $\pm 2$ ,  $\pm 4$ ,  $\pm 6$ , and  $\pm 8$  SR respectively. Similarly, the PRR structure can be designed to support increasing/decreasing SR in steps of 4 (Figure 18(b)) and 8. This can be useful for video with very high motion activities and high resolution which require optimum SR to be greater than  $\pm 8$ . For implementation purpose, we use 4 PRRs which can support increasing/decreasing SR in steps of  $\pm 2$ .

Here from this work and also from work from Chapter 3, it can be shown that by rearranging the SAD units and with proper memory management unit, we can design a modular ME engine to support various requirements from the user, such as frame rate, video resolution, and search range,

and to maximize the benefits by fully utilizing the trade-offs among video signal characteristics, computing power, and reconfigurable hardware resources.

#### 4.3.4 Data Flow