University of Central Florida

Electronic Theses and Dissertations, 2004-2019

2005

# Analysis And Simulation Tools For Solar Array Power Systems

Nattorn Pongratananukul University of Central Florida

Part of the Electrical and Electronics Commons Find similar works at: https://stars.library.ucf.edu/etd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

### **STARS Citation**

Pongratananukul, Nattorn, "Analysis And Simulation Tools For Solar Array Power Systems" (2005). *Electronic Theses and Dissertations, 2004-2019.* 373. https://stars.library.ucf.edu/etd/373

# ANALYSIS AND SIMULATION TOOLS FOR SOLAR ARRAY POWER SYSTEMS

by

NATTORN PONGRATANANUKUL B.S. University of Central Florida, 2000 M.S. University of Central Florida, 2003

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Spring Term 2005

Major Professor: Takis Kasparis

© 2005 Nattorn Pongratananukul

## ABSTRACT

This dissertation presents simulation tools developed specifically for the design of solar array power systems. Contributions are made in several aspects of the system design phases, including solar source modeling, system simulation, and controller verification.

A tool to automate the study of solar array configurations using general purpose circuit simulators has been developed based on the modeling of individual solar cells. Hierarchical structure of solar cell elements, including semiconductor properties, allows simulation of electrical properties as well as the evaluation of the impact of environmental conditions.

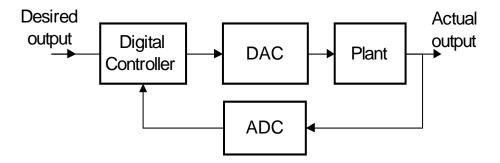

A second developed tool provides a co-simulation platform with the capability to verify the performance of an actual digital controller implemented in programmable hardware such as a DSP processor, while the entire solar array including the DC-DC power converter is modeled in software algorithms running on a computer. This "virtual plant" allows developing and debugging code for the digital controller, and also to improve the control algorithm.

One important task in solar arrays is to track the maximum power point on the array in order to maximize the power that can be delivered. Digital controllers implemented with programmable processors are particularly attractive for this task because sophisticated tracking algorithms can be implemented and revised when needed to optimize their performance. The proposed co-simulation tools are thus very valuable in developing and optimizing the control algorithm, before the system is built. Examples that demonstrate the effectiveness of the proposed methodologies are presented.

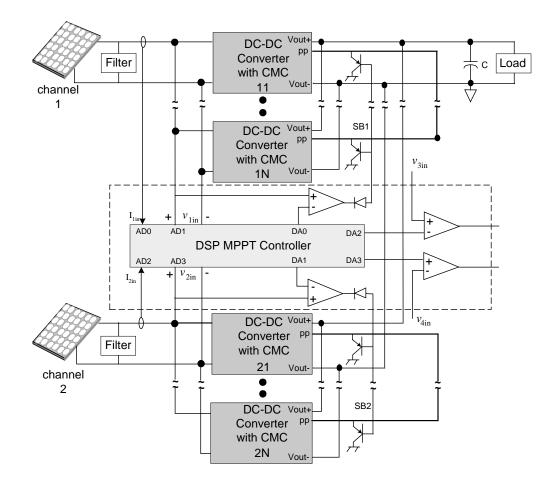

The proposed simulation tools are also valuable in the design of multi-channel arrays. In the specific system that we have designed and tested, the control algorithm is implemented on a single digital signal processor. In each of the channels the maximum power point is tracked individually. In the prototype we built, off-the-shelf commercial DC-DC converters were utilized. At the end, the overall performance of the entire system was evaluated using solar array simulators capable of simulating various I-V characteristics, and also by using an electronic load. Experimental results are presented. To my parents

### ACKNOWLEDGMENTS

I would like to thank my advisor Dr. Takis Kasparis for his guidance and encouragement throughout my study. I am grateful of his digital signal processing, electronics, and operational amplifier courses.

It would like to thank several individual who contribute to my research work. Dr. Issa Batarseh introduced me to power electronics and provided opportunities to gain various technical and non-technical experiences through various projects and discussion. Dr.Wenkai Wu developed the power stage used in this research and phase I of the Air Force project. Dr. Kasemsan Siri provided fruitful discussions on the subject of solar power system level and the simulation. I would like to extend my appreciation to my committee members for their help.

It was a pleasure to work with Florida Power Electronics colleagues, Jaber Abu-Qahouq, Dr. Weihong Qiu, Songquan Deng, Duy Bui, Yufang Jin, Dr. Mao Hong, Khalid Rustom, Dr. Christopher Iannello, Feng Tian, Yangyang Wen, Hussam Alatrash, Shilpa Kaluvala, Ehab Shoubaki, Adje Mensah, and Jia Luo for their help and cooperation.

I am indebt to my first two teachers, my parents, who always provide endless love and encouragement throughout my life.

This work was partially supported by Air Force SBIR Phase I grant # F29601-02-C-0075 and Phase II grant # F29601-03-C-0033 through APECOR.

# **TABLE OF CONTENTS**

| LIST OF FIGURES                                     | . X  |

|-----------------------------------------------------|------|

| LIST OF ABBREVIATIONS                               | ciii |

| CHAPTER 1 : INTRODUCTION                            | . 1  |

| 1.1 Digital Control                                 | . 1  |

| 1.2 Scalable Power System                           | . 5  |

| 1.3 Outline                                         | . 6  |

| CHAPTER 2 : PHOTOVOLTAIC SOURCE MODEL               | . 7  |

| 2.1 Solar Cell Modeling                             | . 8  |

| 2.2 Solar Array Structure                           | 13   |

| 2.3 Implementation                                  | 18   |

| 2.4 Application Examples                            | 21   |

| 2.5 System Consideration                            | 23   |

| CHAPTER 3 : MPPT ALGORITHMS                         | 24   |

| 3.1 Constant Voltage and Current                    | 28   |

| 3.2 Pilot Cell/Reference Array Measurement Approach | 29   |

| 3.3 Model-Based MPPT Algorithms                     | 30   |

| 3.4 Perturb-and-Observe                             | 31   |

| 3.5 Incremental Conductance                         | 33   |

| 3.6 Parasitic Capacitance                                                                                                                                                                                             | 35                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 3.7 Dither Signal Injection                                                                                                                                                                                           |                                        |

| 3.8 Analog Implementation                                                                                                                                                                                             | 40                                     |

| 3.9 Applications                                                                                                                                                                                                      | 44                                     |

| CHAPTER 4 : SYSTEM CONFIGURATION                                                                                                                                                                                      | 45                                     |

| 4.1 System Architecture Under Consideration                                                                                                                                                                           | 46                                     |

| 4.2 Parallel Current-mode-controlled DC-DC with Current Sharing                                                                                                                                                       | 47                                     |

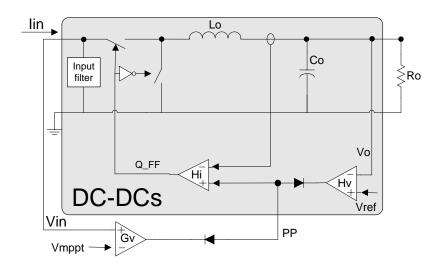

| 4.3 Single-channel Configuration                                                                                                                                                                                      | 50                                     |

| 4.4 Multi-channel Configuration                                                                                                                                                                                       | 57                                     |

| 4.5 Advantages of a MPPT Controller Per Channel Approach                                                                                                                                                              | 61                                     |

| 4.6 Advantages of DSP-based MPPT Controller                                                                                                                                                                           | 62                                     |

| CHAPTER 5 : SYSTEM SIMULATION AND VERIFICATION OF I                                                                                                                                                                   | DIGITAL                                |

| CONTROLLER                                                                                                                                                                                                            |                                        |

|                                                                                                                                                                                                                       | 63                                     |

| 5.1 System Modeling                                                                                                                                                                                                   |                                        |

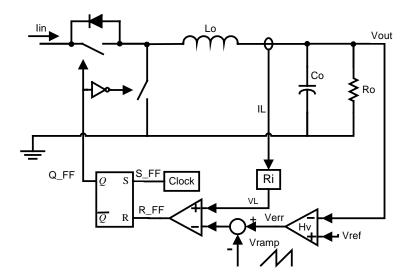

| <ul><li>5.1 System Modeling</li><li>5.1.1 Behavioral Modeling of Analog Power Stage</li></ul>                                                                                                                         | 65                                     |

|                                                                                                                                                                                                                       | 65<br>65                               |

| 5.1.1 Behavioral Modeling of Analog Power Stage                                                                                                                                                                       | 65<br>65<br>68                         |

| <ul><li>5.1.1 Behavioral Modeling of Analog Power Stage</li><li>5.1.2 Digital Control Portion</li></ul>                                                                                                               | 65<br>65<br>68<br>69                   |

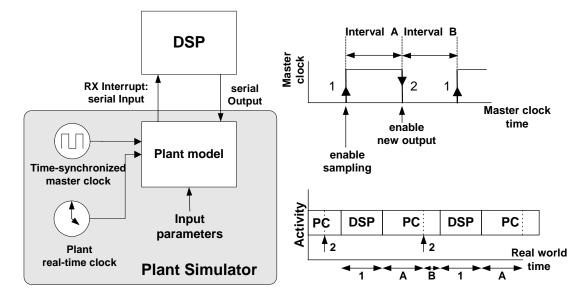

| <ul> <li>5.1.1 Behavioral Modeling of Analog Power Stage</li> <li>5.1.2 Digital Control Portion</li> <li>5.2 Proposed Co-simulators' Data and Time Synchronization</li> </ul>                                         | 65<br>65<br>68<br>69<br>74             |

| <ul> <li>5.1.1 Behavioral Modeling of Analog Power Stage</li> <li>5.1.2 Digital Control Portion</li> <li>5.2 Proposed Co-simulators' Data and Time Synchronization</li> <li>5.3 Implementation and Results</li> </ul> | 65<br>65<br>68<br>69<br>74<br>74       |

| <ul> <li>5.1.1 Behavioral Modeling of Analog Power Stage</li> <li>5.1.2 Digital Control Portion</li></ul>                                                                                                             | 65<br>65<br>68<br>69<br>74<br>74<br>76 |

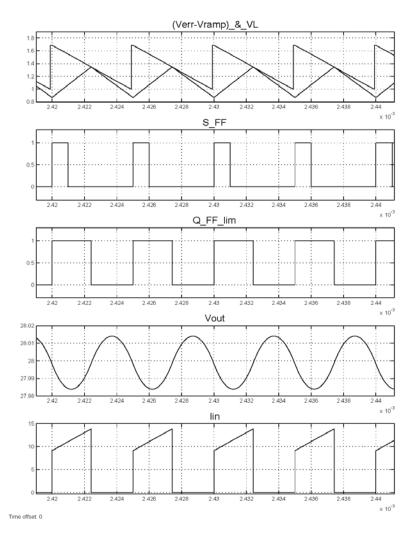

| 5.3.5 Key Waveforms                           |     |

|-----------------------------------------------|-----|

| 5.4 Towards Experimentation                   | 83  |

| CHAPTER 6 : IMPLEMENTATION AND EXPERIMENTS    |     |

| 6.1 DSP Hardware Implementation               | 85  |

| 6.2 MPPT Algorithm Implementation             | 91  |

| 6.3 Dither Signal Generation                  |     |

| 6.4 Power Stage Hardware Prototype            |     |

| 6.5 Solar Array Simulator                     | 96  |

| 6.6 System Setup and Experimental Results     |     |

| CHAPTER 7 : CONCLUSIONS AND FUTURE DIRECTIONS |     |

| LIST OF REFERENCES                            | 108 |

# LIST OF FIGURES

| Figure 2.1: Two-diode solar cell model                                   | 9  |

|--------------------------------------------------------------------------|----|

| Figure 2.2: Typical I-V and P-V characteristics of a solar cell          | 11 |

| Figure 2.3: I-V curves for various irradiance                            | 12 |

| Figure 2.4: I-V curves for various temperature                           | 12 |

| Figure 2.5: Generation characteristics for two parallel-connected cells  | 13 |

| Figure 2.6: Generation characteristics for two series-connected cells    | 15 |

| Figure 2.7: Various solar cells interconnection.                         | 17 |

| Figure 2.8: Implementation flow chart                                    | 19 |

| Figure 2.9: PSPICE subcircuit model and schematic equivalent             | 20 |

| Figure 2.10: I-V and P-V curve of partially shaded panel                 | 22 |

| Figure 2.11: Parameter variation (a) Rs (b) Rp                           | 23 |

| Figure 3.1: I-V characteristics under wide operating conditions          | 24 |

| Figure 3.2: Direct coupled method                                        | 25 |

| Figure 3.3: Basic components of a maximum power pointer tracker          | 26 |

| Figure 3.4: Constant voltage/current algorithm flowchart                 | 29 |

| Figure 3.5: Perturb & Observe (P&O) control action                       | 32 |

| Figure 3.6: Incremental conductance algorithm flow chart                 | 34 |

| Figure 3.7: Circuitry used to implement the parasitic capacitance method | 37 |

| Figure 3.8: Modified dither-based MPPT scheme                                           |

|-----------------------------------------------------------------------------------------|

| Figure 3.9: Solar array power change vs. voltage change                                 |

| Figure 3.10: Simulation results with dither signal added                                |

| Figure 3.11: Control mechanism of MPPT 42                                               |

| Figure 3.12: Regions of MPPT 42                                                         |

| Figure 3.13: Logic combinations that may occur and its associated movement              |

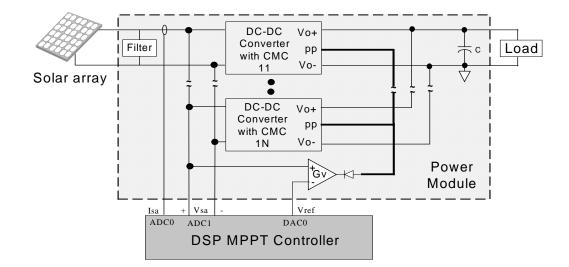

| Figure 4.1: Configuration of paralleled converters with MPPT control for a single solar |

| channel                                                                                 |

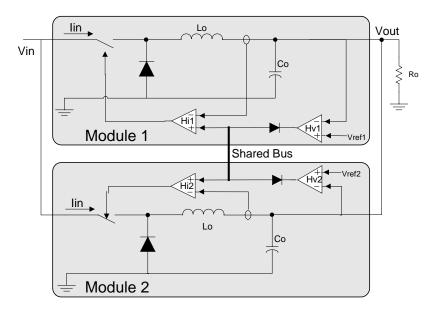

| Figure 4.2: Paralleled converters with current sharing bus                              |

| Figure 4.3: Two operating modes                                                         |

| Figure 4.4: Command to the current-loop compensator                                     |

| Figure 4.5: (a) Set point voltage and (b) Reference voltage from MPPT controller 55     |

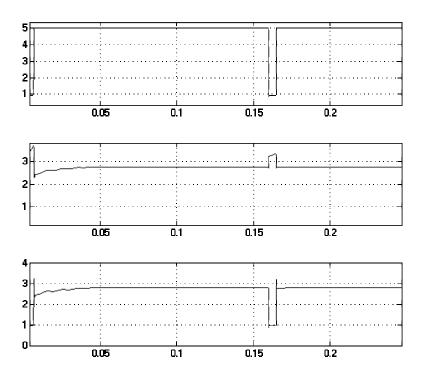

| Figure 4.6: Solar array (a) voltage and (b) current under transient load                |

| Figure 4.7: Output voltage under transient load                                         |

| Figure 4.8: Transient load current                                                      |

| Figure 4.9: Basic Configuration of Paralleled Converters with Multiple Peak Power       |

| Tracking Control                                                                        |

| Figure 5.1: Example of behavioral modeling                                              |

| Figure 5.2: Power stage peak-current controlled steady-state waveforms                  |

| Figure 5.3: Typical digital control configuration                                       |

| Figure 5.4: Timing details for co-simulation71                                          |

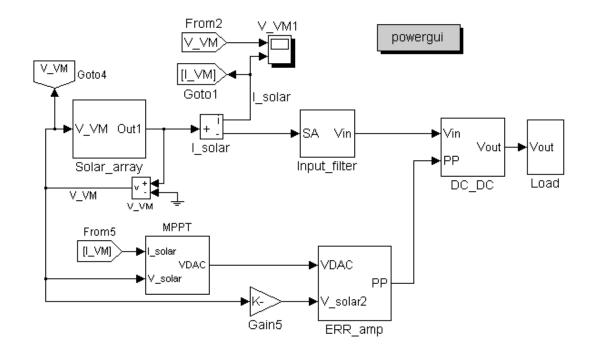

| Figure 5.5: SIMULINK system block diagram75                                             |

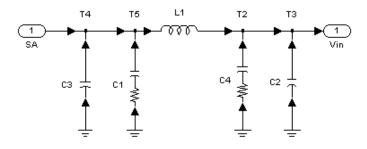

| Figure 5.6: Power stage modeling – input filter                                 | . 75 |

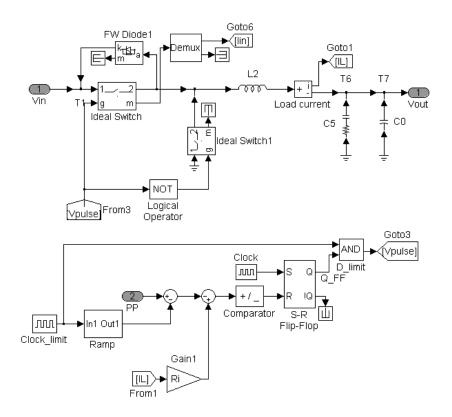

|---------------------------------------------------------------------------------|------|

| Figure 5.7: Power stage modeling – DC-DC                                        | . 76 |

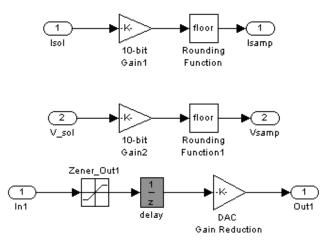

| Figure 5.8: Data converters modeling                                            | . 78 |

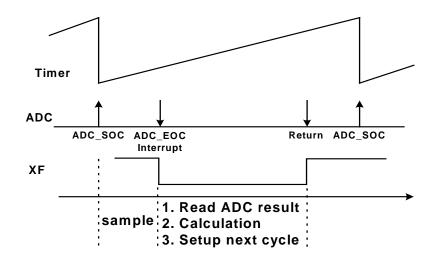

| Figure 5.9: ADC timing inside DSP                                               | . 79 |

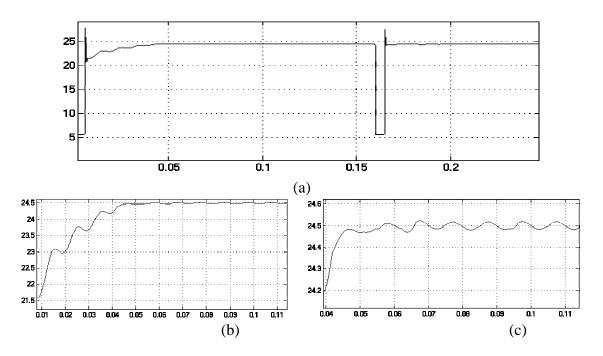

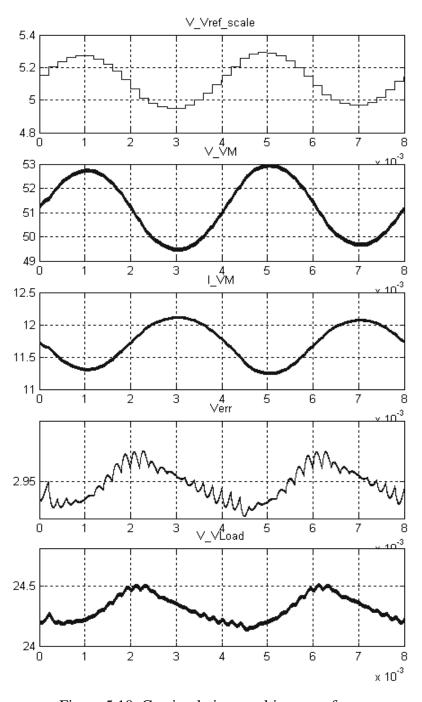

| Figure 5.10: Co-simulation resulting waveforms                                  | . 82 |

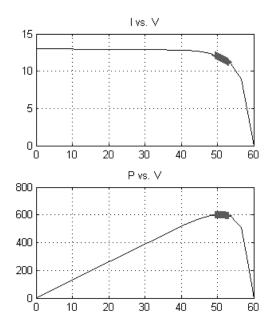

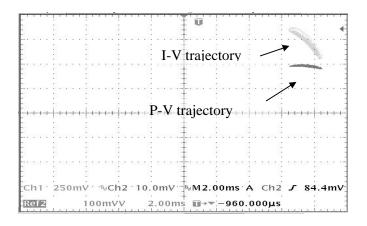

| Figure 5.11: Co-simulation resulting I-V and P-V traces                         | . 83 |

| Figure 6.1: DSP TMS320F24xxEVM evaluation board                                 | . 86 |

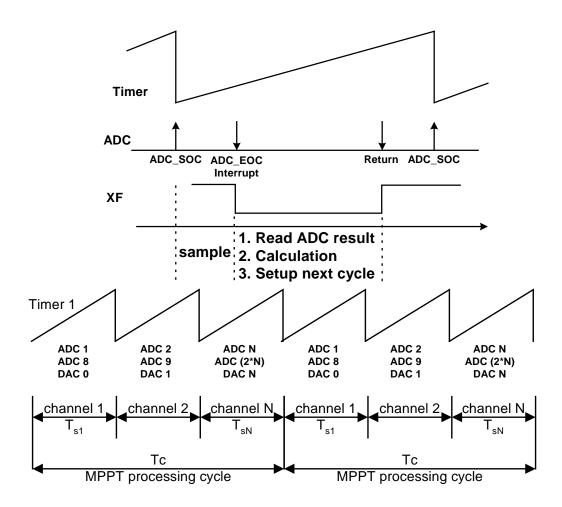

| Figure 6.2: Timing (a) Single channel and (b) Time-multiplexed multi-channel    | . 89 |

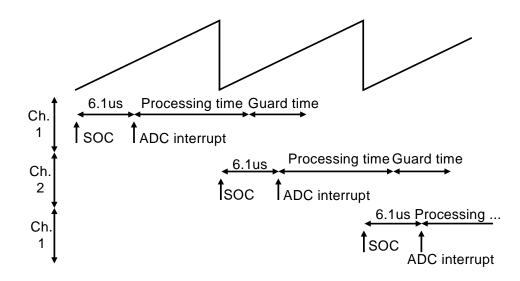

| Figure 6.3: Detail timing of interrupt service routine for 2 solar sources case | . 91 |

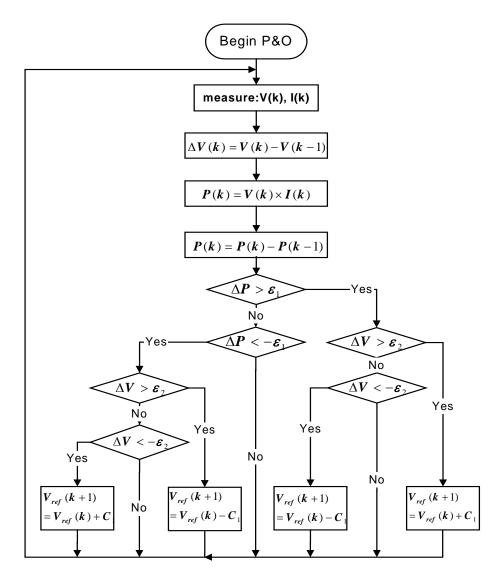

| Figure 6.4: Perturb-and-observe implementation                                  | 92   |

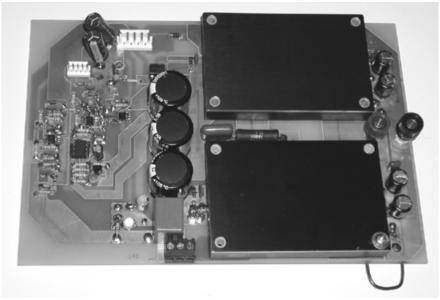

| Figure 6.5: Power modules and conditioning circuit                              | . 95 |

| Figure 6.6: Auxiliary board                                                     | . 95 |

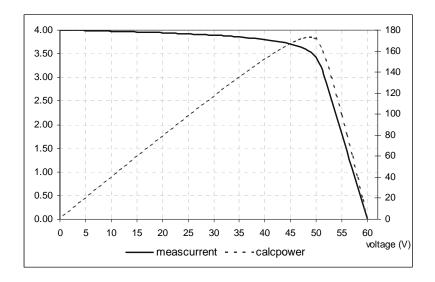

| Figure 6.7: I-V curve from Simulator mode                                       | . 97 |

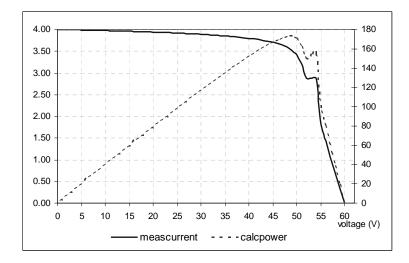

| Figure 6.8: I-V curve from Table mode                                           | . 97 |

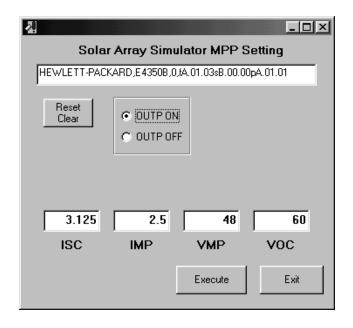

| Figure 6.9: GUI for SAS control in Simulator mode                               | . 98 |

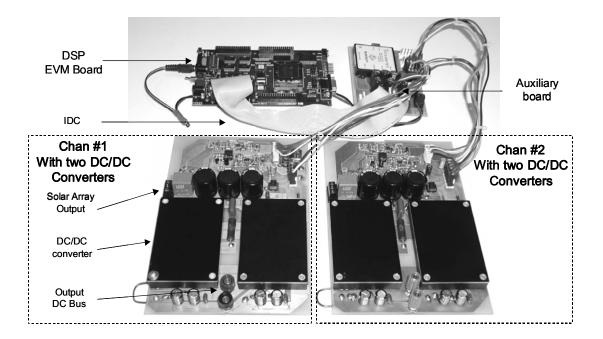

| Figure 6.10: 500W Two solar arrays power system with DSP-based MPPT control     | 100  |

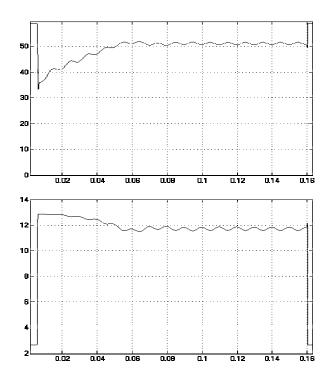

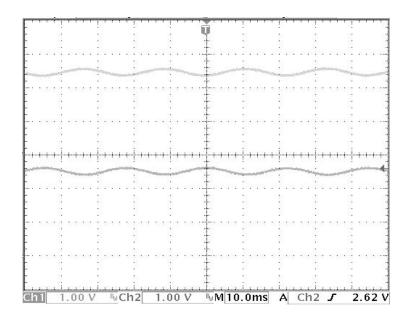

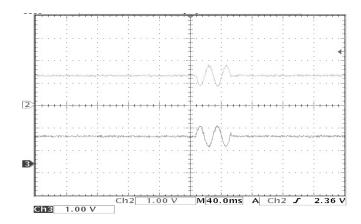

| Figure 6.11: Dither signals                                                     | 100  |

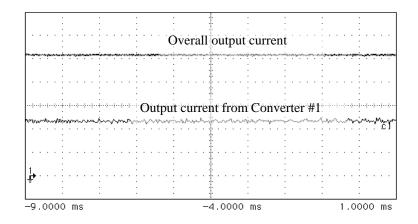

| Figure 6.12: Current sharing among the paralleled DC-DC converters (2A/Div)     | 101  |

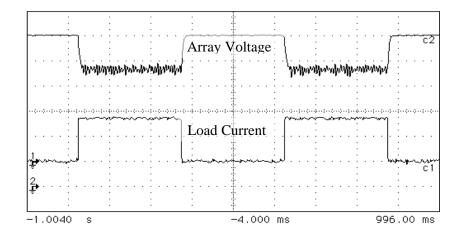

| Figure 6.13: Dynamic response of array voltage and current                      | 101  |

| Figure 6.14: Trajectories of array P-V and I-V                                  | 101  |

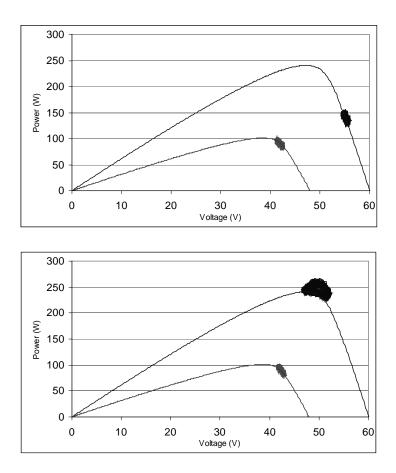

| Figure 6.15: Operating point for two solar arrays                               | 103  |

| Figure 6.16: Two solar array's P-V trajectory under different loads             | 103  |

# LIST OF ABBREVIATIONS

- A/D Analog-to-digital

- ADC Analog-to-digital converter

- BOL Begin-of-life

- CMC Current-mode control

- COTS Commercial-off-the-shelf

- D/A Digital-to-analog

- DAC Digital-to-analog converter

- DSP Digital signal processing/processor

- EOC End of conversion

- EOL End-of-life

- EVM Evaluation module

- GPIB General Purpose Interface Bus

- I-V Current vs. voltage

- IncCond Incremental conductance

- MPPT Maximum power point tracking

- OVR Output voltage regulation

- P&O Purturb-and-observe

- P-V Power vs. voltage

| PP    | Parallel pin                                        |

|-------|-----------------------------------------------------|

| PV    | Photovoltaic                                        |

| S/H   | Sample-and-hold                                     |

| SAS   | Solar array simulator                               |

| SB    | Shared-bus                                          |

| SNR   | Signal-to-noise ratio                               |

| SOC   | Start-of-conversion                                 |

| SPICE | Simulation program with integrated circuit emphasis |

## **CHAPTER 1: INTRODUCTION**

In recent years, the problem of energy crunch has become more and more aggravating, resulting in increased exploitation and research for new power energy resources around the world. In particular, the use of natural energy, especially the solar energy is increasingly emphasized and regarded as an important resource of power energy in the future.

As the power supplied by solar arrays depends upon the insolation, temperature and array voltage, it is necessary to implement a so-called maximum power point tracking (MPPT) technique to track the changes and extract the maximum power from the solar array. A MPPT for solar application is a control algorithm to force the impedance at the terminals of PV array to the value that produces maximum power out of the array. Some papers had proposed different maximum power point tracking control techniques in the past. The popularity of MPPT system was tempered to a large extent by operational problems, added complexity and unfavorable incremental costs.

### 1.1 Digital Control

The primary advantages of traditional analog controllers are high bandwidth, high resolution, are easy to understand and use, and they are relatively low in cost. Analog

controllers have some drawbacks such as component drift, they are hardwired and as a result they are not flexible. Large part count is also common for complex analog systems. Components age and change values over temperature and various environmental conditions. As far as predictability, one cannot obtain two components that are exactly alike. They have to be tweaked and trimmed. To modify a system one has to replace components. Board layouts become a consideration that we must take into account, and it is difficult, sometimes impossible, to implement some functions.

The innovation of DSP control into power electronic designs is an excellent example of the advantages provided by major technological advances. By replacing analog control with DSP control, the primary advantages are achieved by replacing hardware with flexible software.

A digital signal processing (DSP) controller is the combination of a high-speed mathematical core, memory, and a set of peripheral devices. With an appropriate set of peripherals for the application, it is possible to reach a single chip solution with minimum or even no external interface components. Today's DSP controllers created for complex motor speed and servo control are also ideally suited for renewable energy applications. The newly introduced low-cost, high performance DSPs, with features such as singlecycle multiplication and accumulation with on-chip pulse-width modulation (PWM) mechanism and analog to digital converters (ADCs), provide the Central Processing Unit (CPU) bandwidth and peripheral mix needed to implement sophisticated control techniques required for interfacing with various renewable energy sources. There are many advantages to digital control. For example, digital controllers are less sensitive to the environment, they are highly reliable, and they are software programmable, which translates to greater flexibility. Digital controllers are precise, and offer more predictable behavior. Advanced control is also possible – enabling non-linear and multi-variable control. Designers can also perform multiple loops, and other unique functions.

A digital controller has many advantages over its analog counterpart. There are no hardware adjustments, fewer components, less aging effects, and smaller temperature drifts. With a digital controller, adjustment of control parameters for adapting to different electrical environments is easy and flexible. DSP provides other advantages such as full digital control, fewer components, high noise/EMI immunity, high reliability, reduced heating of power switches, lower harmonics, less filtering, faster fault response, no dc components, and higher efficiency. Additionally, it is easy to include other system level functions such as battery charging, power factor correction, reactive power compensation, fuzzy logic control, parallel operation, and on-the-fly frequency change to adapt to different environments and applications. Secure remote communication, data acquisition and display, device overload protection, maximum power tracking, and state control can all easily be implemented.

With the improvement in math-intensive functions and high execution speed, faster control response and correction to achieve desired parameters yields a better performing system. The DSP software allows for automation of the testing process, thus reducing the labor content of the technical staff. The software within the DSP can be easily modified to optimize the application and provide diagnostic once in use in the field or if the application changes once the unit is installed. The application that the equipment addresses can be easily modified via software changes as opposed to hardware design changes. This also increases in-house design flexibility. Development time is reduced, since software is easier to revise than manufactured hardware. The same controller board can be used for different applications; thus economics are achieved by reducing the number of components in inventory across numerous product lines as well as the overhead associated with specifying and purchasing components.

With advanced DSP control, low frequency passive filter and high frequency filter damping circuits are not required. This results in a simple system configuration, high reliability, low cost, smaller footprint, and lighter weight. For example, the RFI (radio frequency interference) filter can be smaller and less costly. The controller will reduce the material cost of the customer's equipment, labor content, and overhead related to both materials and labor (purchasing transactions cost, accounting transactions costs, factory overhead). Technological advancements allow equipment to become smaller and lighter which translates into cost reduction, labor, transportation, and materials.

Digital controllers have drawbacks, however. Those include bandwidth limitations, numerical problems like quantization errors, data converter limitations, CPU performance limitations, and system cost concerns. More recently, many of the "traditional" negatives associated with digital controllers are disappearing. DSP controller technology is rapidly improving while prices are reaching levels where even cost-sensitive equipments benefit.

#### 1.2 <u>Scalable Power System</u>

As the need for flexible, scalable space-based power requirements increases, and in an effort to avoid redesign of spacecraft and electric propulsion power systems, a number of concepts have emerged to provide expandable, parallel-connected power converters employing techniques such as maximum peak power tracking. Such approaches then allow a variety of options with the rest of the power system such as employing standard, modular, power converters that can be connected in parallel. The goal of such structures is to provide a single power system design that can meet a range of power requirements for spacecraft and/or electric propulsion power systems. For such a flexible and scalable power system, a need exists for control of such functionality. Depending on the concept, risks of power system failures exist due to a variety of circumstances. Under any circumstance that causes the output voltage of the power system to lose regulation, MPPT techniques ensure that the power delivered to the load is at the maximum available from the solar arrays. Hence, the control prevents the complete drop out of the system output voltage. Under normal sun insolation and healthy array source conditions, the control will not interfere with the regulation of the system output voltage because the load demand is below the maximum available power of the array source. The expansion capability of the system with such a control provides long-term cost/schedule benefits to the electric propulsion and spacecraft power systems of the next generations. In many cases, Commercial Off-the-Shelf (COTS) power converters can be employed with such control circuitry to meet space needs.

## 1.3 Outline

In this dissertation we present simulation tools and experimental work for solar power system. Chapter 2 gives a review of the modeling of solar cell sources and analysis of simple interconnection. An automated simulation tool is developed to ease the complexity of the analysis of solar cells characteristics. Simulation examples are presented. Chapter 3 describes methodologies for extracting maximum power from solar cell sources, and outlines existing techniques. A focus on dynamic tracking of maximum power point based on dither signal injection is discussed. Chapter 4 presents a flexible and scalable power system configuration under consideration. Details of the underlying components and their operation are explained for a single channel, and then for multichannel arrangement. Chapter 5 describes a proposed co-simulation tool for system simulation. The tool is used to verify the digital-controlled implementation of the maximum power point tracking system, where a host computer simulates a modeled power stage and digital signal processor runs actual algorithms on-board. The communication and synchronization issues are discussed. Chapter 6 details the hardware and software implementation of the multi-channel power system. Various aspects of the embedded system implementation, such as timing and peripherals setup, are described. Descriptions of the power stage prototype and experimental results are shown. Chapter 7 provides conclusion and direction for future works.

## **CHAPTER 2: PHOTOVOLTAIC SOURCE MODEL**

The understanding of solar cell source behavior is necessary to specify the size of solar array system or to study the stability of regulators. Placing the solar panels in an optimal way is an effective measure to take to maximize the energy yield from a photovoltaic-installation. Shading can rarely be completely avoided, certainly not in urban or suburban environments. At higher latitudes the sun is often close to the horizon, which makes the shading problem more severe than at low latitudes. Therefore, especially for high-latitude locations and urban/suburban sites, a shading-tolerant system should be chosen. Furthermore, the direction south/north (azimuth) and elevation angle should also be considered. Any shading of the solar panels will lead to considerable reduction in energy yield, even if just a small fraction of the panels is shaded. Consequently, the case in which the solar cells in the generation system do not operate under uniform generation conditions should be examined.

The connection of photovoltaic modules with different operating currents and/or voltages characteristic may result in the performance of the array being less than the sum of the potential performances of individual modules. When connected in series, the current flowing through the lowest productive cell limits the entire array output. The problem arises when modules have different sizes, which may be a result of individual modules not exposed to the same lighting conditions, such as is the case with differently

oriented modules or irregular shading of the array. Mismatch is more likely in large systems than in independent arrays, because individual modules may be oriented differently or they may be subject to varying degrees of shading and heating.

Taking into account that real operating conditions of a solar array are difficult to reproduce during tests, simulations to determine electrical characteristics will allow the researcher to gain more insight for better understanding and design. Performance gain is beneficial and can find applications in numerous areas such as the one described in reference [1]. As the fine modeling of a cell's behavior is the basis for any solar generator, the solar cell model needs to be properly determined. Methods for simulation of general solar array configuration have been proposed; however, these implementations are associated with special-purpose simulation tools, and detailed modeling has not been performed [2], [3], [4]. Utilizing a circuit-simulator such as Simulation Program with Integrated Circuit Emphasis (SPICE), one can run many component models.

#### 2.1 Solar Cell Modeling

Solar cells are essentially a very large area p-n junction diode, where such a diode is created by forming a junction between the n-type and p-type regions. As sunlight strikes a solar cell, the incident energy is converted directly into electrical energy. Transmitted light is absorbed within the semiconductor by using the energy to excite free electrons from a low energy status to an unoccupied higher energy level. When a solar cell is illuminated, excess electron-hold pairs are generated by light throughout the material; hence the p-n junction is electrically shorted and current will flow.

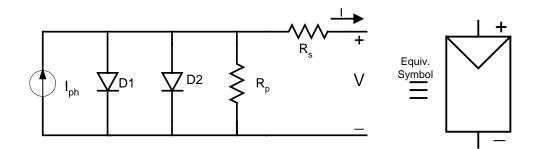

The equivalent circuit of a solar cell is represented by four components: a lightinduced current source, a diode parallel to the source, a series resistor and a shunt resistor. The light-induced current is due to the separation and drift of the photongenerated electron-hole pairs under the influence of the built-in field.

Figure 2.1: Two-diode solar cell model

The two-diode model of solar cell is shown in Figure 2.1. The corresponding current vs. voltage curves (I-V) equation is:

$$I = I_{ph} - I_{s_1} \left[ e^{\frac{q(V+IR_s)}{n_1 kT}} - 1 \right] - I_{s_2} \left[ e^{\frac{q(V+IR_s)}{n_2 kT}} - 1 \right] - \frac{V+IR_s}{R_p}$$

(2.1)

where, I and V are the solar cell output current and voltage,  $I_{ph}$  is the generated photocurrent, and  $I_{s1}$ ,  $I_{s2}$  are the reverse saturation currents of each diode. The parameters  $n_1$ ,  $n_2$  are diode ideality factors, T is the absolute temperature in Kelvin, k is the Boltzmann's constant (1.380 x 10<sup>-23</sup> J/K) and q is the elementary charge (1.602 x 10<sup>-19</sup> C). The two-diode model is derived from the physics of the p-n junction, especially those of poly crystalline silicon [5]. For amorphous silicon the single-diode model is more appropriate ( $I_{s2} = 0$ ). The first saturation current,  $I_{s1}$ , is due to diffusion mechanism of the minority carriers into depletion layer, and the second,  $I_{s2}$ , is due to recombination in space-charge layer. Series resistance  $R_s$  is the effect of the path that photo-generated electrons have to traverse a surface semiconductor region to reach the nearest finger electrode. The value of  $R_s$  can also further increase for a thin finger electrode. A small fraction of the photo-generated carrier can also flow through the crystal surfaces or through grain boundaries in polycrystalline devices instead of flowing though the external load. This leakage can be represented by an effective internal parallel resistance  $R_p$  [6].

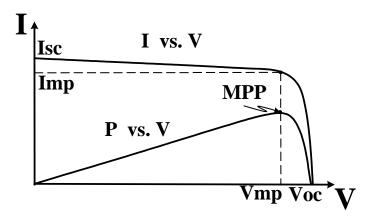

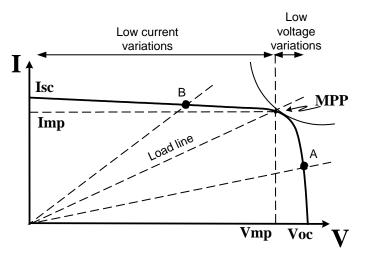

Consider a fixed environmental condition, a typical I-V characteristic of a solar cell is shown in Figure 2.2. The operating point on power vs. voltage curve (P-V curve) will depend on the solar array characteristic and the load. Assuming that initially there is no load, the operating point will be at the far right at the open-circuit voltage, Voc, of the solar array with zero current (V = Voc, I = 0). As the load increase, the operating point will move up and to the left, i.e. voltage at the solar array terminal decreased, while the power increases. As the load increases further, it will reach the maximum power point (MPP), where the power drawn from the solar cell is maximized. The voltage at this point is denoted by the maximum-power voltage (Vmp), and the current by maximum-power current (Imp). If the load increases beyond this point, the voltage decreases and

power drawn from the solar array decreases. Eventually, the operating point will reach the far left at the short-circuit current, Isc, with zero voltage output (V = 0, I = Isc).

Figure 2.2: Typical I-V and P-V characteristics of a solar cell

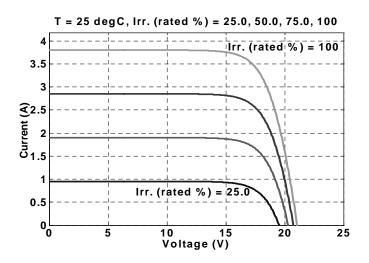

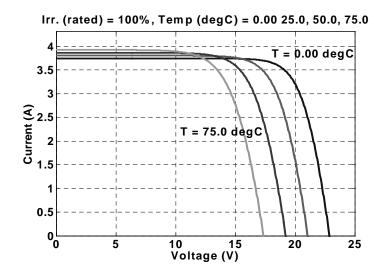

Solar cell model parameters vary with environmental conditions, the two most important effects being temperature and irradiance. Solar cell open-circuit voltage decreases with increasing temperature, and the short circuit current is proportional to the amount of irradiance. The current vs. voltage curves (I-V curves) for various irradiance and temperature are shown in Figure 2.3 and Figure 2.4, respectively.

The equations showing modeling effects of irradiance and temperature on model parameters [5] are:

$$\mathbf{I}_{ph} = \mathbf{I}_{ph}\Big|_{Tref} \left[1 + \mathbf{K}_0 \left(T - T_{ref}\right)\right]$$

(2.2)

$$\mathbf{I}_{s} = \mathbf{I}_{s} \Big|_{\mathrm{Tref}} \left( \frac{\mathrm{T}}{\mathrm{T}_{\mathrm{ref}}} \right)^{3} \exp \left\{ \frac{-\mathrm{qE}_{g}}{\mathrm{nk}} \left( \frac{1}{\mathrm{T}_{ref}} - \frac{1}{\mathrm{T}} \right) \right\}$$

(2.3)

$$\mathbf{R}_{s} = \mathbf{R}_{s} \Big|_{\text{Tref}} \left[ 1 - \mathbf{K}_{3} \left( T - T_{ref} \right) \right]$$

(2.4)

$$\mathbf{R}_{p} = \mathbf{R}_{p} \Big|_{\text{Tref}} \exp\{-K_{4}T\}$$

(2.5)

where  $T_{ref}$  is the cell reference temperature.  $E_g$  is the band gap energy of the semiconductor.  $K_0$  is the short-circuit temperature coefficient, and  $K_3$ ,  $K_4$  are the resistance temperature coefficients. Each parameter value is varied relative to the value at the cell reference temperature.

Figure 2.3: I-V curves for various irradiance

Figure 2.4: I-V curves for various temperature

### 2.2 Solar Array Structure

When solar cells are connected in parallel, the voltage is the uniform for each solar cell, and the current generated from each cell flows without restriction. In other words, the output voltage of the system becomes the voltage of a single cell, and the output current becomes the sum of the currents in each cell. In contrast, when solar cells are connected in series, the same current flows through each cell and the output voltage is the sum of the voltages across each of the cells. The voltage of each cell is determined according to the generation current, which depends on the generation conditions. Therefore, the optimal generation voltages are not always obtained for each cell. These behaviors can be generalized to the parallel/series connection of photovoltaic modules, provided the environmental condition is uniform on every cell in the modules.

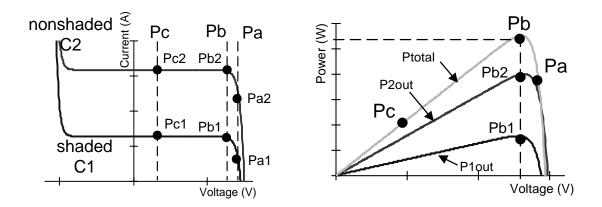

Figure 2.5: Generation characteristics for two parallel-connected cells. (a) I–V characteristics. (b) P–V characteristics.

Figure 2.5(a) shows the typical generation characteristics and I-V curve for two parallel-connected cells that have different generation conditions, mainly in the amount

of irradiance. In this figure, C1 and C2 represent of a shaded and a nonshaded cell, respectively. In parallel connection, the operating point of each cell is given by the point of intersection of the vertical operating lines,  $P_{a-c}$ , i.e. uniform cells' voltage, and the I-V curve of each cell. As the output current of the system increases from zero to the maximum current, the operation point of each cell moves as indicated in Figure 2.5(b),  $p_{a1} \rightarrow p_{b1} \rightarrow p_{c1}$  for C1 and  $p_{a2} \rightarrow p_{b2} \rightarrow p_{c2}$  for C2. This operation characteristic reveals that both the nonshaded cells and the shaded ones can operate in the area where each cell can generate power. Hence, the total output P-V characteristics of these cells are obtained as shown in Figure 2.5(b). Then, the total output power,  $P_{total}$ , is given by Equation (2.6), where, the generation power on C1 is  $P_{1out}$ , and the generation power on C2 is  $P_{2out}$ .

$$P_{\text{total}} = P_{1\text{out}} + P_{2\text{out}} \tag{2.6}$$

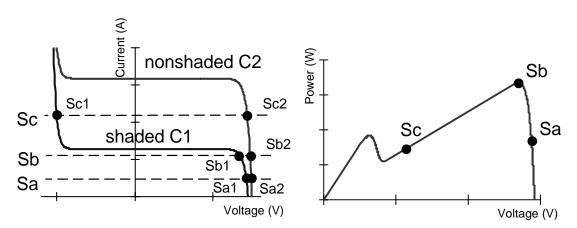

In series connection, the operating point of each cell is given by the point of intersection of the horizontal operation line, i.e. uniform cells' current, and the I-V curve of each cell. As the output current of the system increases from zero to the maximum current, the operation point of each cell moves as indicated in Figure 2.6(a),  $s_{a1} \rightarrow s_{b1} \rightarrow s_{c1}$  for C1 and  $s_{a2} \rightarrow s_{b2} \rightarrow s_{c2}$  for C2. On operation line S<sub>b</sub>, the shaded cell, C1, generates its maximum power, but the nonshaded cell, C2, does not generate its maximum power yet. When the operation line moves to Sc, the operation points of each cell C1 and C2 move to  $s_{c1}$  and  $s_{c2}$ , respectively, and the generation power on C2 increases. The unshaded cell, C2, will force the shaded cell, C1, to pass more current than its new short

circuit current. The shaded cell operates in reverse-bias region and causes a net voltage loss to the system. This is a point of breakthrough in the pn-junction when the externally applied electric field will overcome the intrinsic electric field, known as the avalanche effect. The product of the current and the negative voltage (avalanche voltage) gives the power dissipated by the shaded cell. In other words, the shaded cell will dissipate power as heat and cause "hot spots" [9]. Here the nonshaded cell, C2, generates power,  $P_{2out}$ , but the shaded cell, C1, causes a power loss,  $P_{1loss}$ . Hence, the output power,  $P_{out}$ , on this system is decreased to the following equation:

$$\mathbf{P}_{\text{total}} = \mathbf{P}_{\text{2out}} - \mathbf{P}_{\text{1loss}} \tag{2.7}$$

The total output power characteristic of this system, the P-V curve, is obtained in the same manner and is shown in Figure 2.6(b). Two peaks in power exist, but the output powers at these peak points are much smaller than that of the parallel-connected condition shown in Figure 2.5(b). Although only a two-cell connection is described here, the mechanism by which power reduction occurs for multiple cells that are connected in series is similar to that for two-cell connection.

Figure 2.6: Generation characteristics for two series-connected cells. (a) I–V characteristics. (b) P–V characteristics.

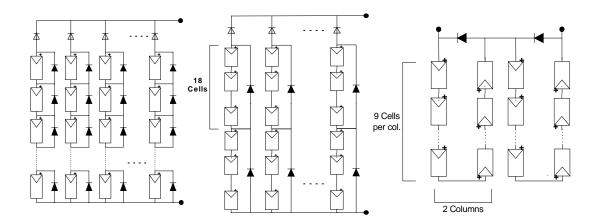

Solar cells are often connected together to form strings that produce a desirable voltage. In the string connection, the voltage is the sum of the device voltages and the string current is limited to the current of the least productive device in the string. Multiple strings are connected in parallel to form a panel. In practice, additional diodes are included for protection. Bypass diodes are depicted with black-filling, while grayfilled diode symbols represent blocking diodes. Diodes connected in series with cells perform a blocking function, preventing backflow of current back into the module string. When diodes are installed in parallel with cells/modules, they perform a bypass function allowing current to pass around a shaded area of a module. The configuration, including physical layout, will have impact on the system performance [7][8]. Figure 2.7 shows various solar cell interconnections. Figure 2.7(a) and (b) have blocking diode on every string before the positive array terminal. Bypass diode is connected across every cell in Figure 2.7(a), while across every 18 cells in Figure 2.7(b). Figure 2.7(c) has the same electrical configuration as in Figure 2.7(b), but each string is arranged as 2 columns with 9 cells per column.

To minimize the power loss and to prevent destruction of series-connected solar cells due to shading effect, we use bypass diodes over a group of cells. Bypass diodes allow current to pass around shaded cells and thereby reduce the voltage losses through the module. When a module becomes shaded its bypass diode becomes "forward biased" and begins to conduct current through itself. All the currents greater than the shaded cell's new short circuit current are "bypassed" through the diode, thus reducing drastically the amount of local heating at the shaded area. The energy from the by-passed substring is still lost, however. Bypass diodes should be connected across fewer solar cells to improve module's shade-tolerant.

Diodes placed in series with cells or modules can perform the function of blocking currents from flowing back to the modules; thus, preventing the modules from becoming loads. In battery charging systems, the module potential drops to zero at night, and the battery could discharge backwards through the module. Diodes placed in the circuit between the module and the battery can block any discharge flow. In the case that one string becomes severely shaded, or if there is a short circuit in one of the modules, the blocking diode prevents the other strings from loosing current backwards down the shaded or damaged string.

Figure 2.7: Various solar cells interconnection. (a) Bypass diode across every cell, (b) Bypass diode across a group of cells, (c) Same as (b) with different physical layout

#### 2.3 Implementation

Expression to describe solar cell characteristic is extremely nonlinear. The equation to describe their interconnection behavior is even more complex. Numerical techniques to solve for I-V curve have been proposed. To be able to obtain data for generalized solar cell structures under varying weather conditions, it is essential to have both programmability and circuit simulation capability. While circuit-oriented simulator, such as SPICE, is an excellent tool for solving circuit networks, existing schematic tools are not suitable for simulating photovoltaic system and data analysis functions for evaluating photovoltaic parameters are cumbersome. To this end, software with flexible coding feature will be utilized in addition to circuit simulator.

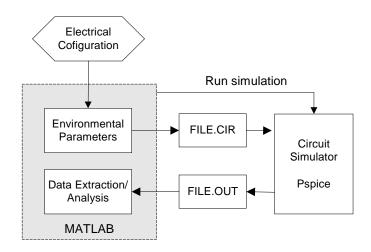

The implementation of the proposed tool is broadly consisted of four components. The first is an electrical configuration representing the interconnection of the elementary solar cells and protective diodes. Various models of photovoltaic devices and that of diodes can be applied to accommodate different types of solar cells. The second component is the environmental condition that account for climatic variation. These environmental conditions, such as short circuit current and temperature, can be incorporated into netlist as passing parameters to the solar cell elements via subcircuit parameterization. Circuit simulator solves the array circuit network, then a script file finally extracts data. A pictorial representation of the automated process is shown in Figure 2.8.

Figure 2.8: Implementation flow chart

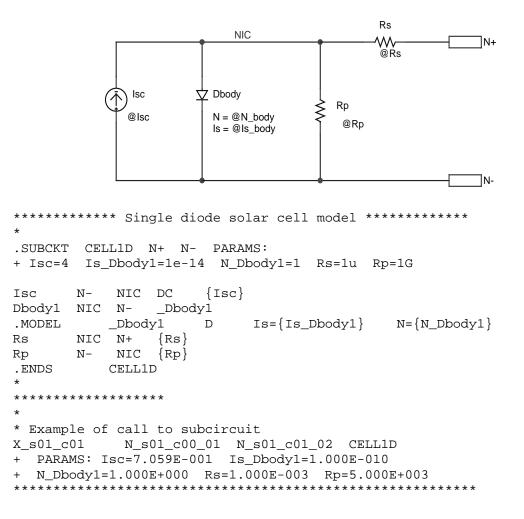

PSPICE's sub-circuit [10] is used to model the individual cell and allow variable input parameters to fine-tune the model. With the sub-circuit of a single-diode model solar cell shown in Figure 2.9, short circuit current, saturation current and ideality factor of the body diode, and equivalent series and parallel resistances are variables. A call to the sub-circuit is also shown.

The proposed method has been implemented using two general-purpose software: a simulator to obtain electrical measurements given varying environmental condition and/or electrical structure, and a scriptor to update the netlist file **FILE.CIR**, start the simulator, read simulation results from the output file **FILE.OUT**, and perform data analysis. MATLAB script file is developed to create PSPICE netlist of a selected electrical configuration composing of solar cell PSPICE's sub-circuit. Node name is automatically updated to represent the electrical connections between solar cells for such structure. One of the advantage for this implementation is the ability to create batches of simulations, so for example, the performance of the solar array can be simulated with varying illumination as it varies throughout a day. An important aspect of this batch mode is that the resulting I-V curves are automatically collected and analyzed, allowing large quantities of data to be handled with ease.

Figure 2.9: PSPICE subcircuit model and schematic equivalent

#### 2.4 <u>Application Examples</u>

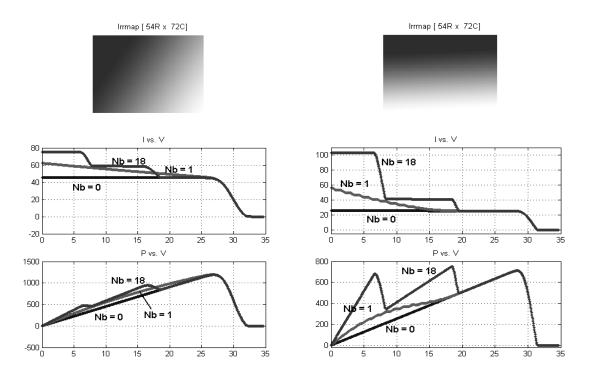

To demonstrate the proposed method, some applications examples are presented. Comparison of shading effect on different panel configurations are considered, namely 1) panel with bypass diode across every solar cells, and 2) with bypass diode across every Nb cells with the same physical layout. The physical layout considered is strings of vertically-aligned solar cells with blocking diode at the output terminal of the panel and top most cells as shown in Figure 2.7(a) and b with 54 rows by 72 columns dimension. Variation of various parameters can be represented by two-dimensional matrix, such as an image file. The dimension of the image N rows x M columns corresponds to the physical layout of a solar panel with NxM solar cells. Illumination of each image pixel provides a mapping to the amount of short circuit current, i.e. white area corresponds to full short circuit current, while darker area has less. For an 8-bit grayscale image, a pixel value of 255 can correspond to irradiance that produces the full short circuit current. By analogy, mapping of solar cells' temperature by a two-dimension image is also possible. For example, a high pixel value can correspond to high temperature. For a partially shaded cell, the parameter value is assumed constant and is equal to the corresponding averaged value [12]. For instance, cell illumination is set to the average solar irradiance over the entire cell.

In Figure 2.10(a) and (b), a gradual shadow is casted across the diagonal and along the vertical of the panel as represented with intensity levels shown. For simplicity, other parameters are kept constant in this case. A variable load across each solar array

configuration obtains I-V characteristic, and P-V is calculated and displayed. As it can be noticed, certain shading patterns produce local maxima in the power curve, and the proposed method provides a tool to study the severity of such shading effects.

Figure 2.10: I-V and P-V curve of partially shaded panel (a) Diagonal shade (b) Vertical shade

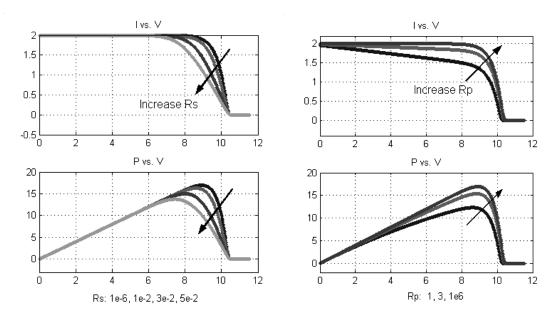

Even though, it is possible to assume that each cell in a module has the same semiconductor characteristic, another potential feature of the proposed method is that it allows distribution of the parameters statistically to account for manufacturing tolerances. As a result, all solar cells can be simulated together as a module, allowing the effects of cell mismatching to be evaluated. Example showing effects of resistances variation is shown in Figure 2.11.

Figure 2.11: Parameter variation (a) Rs (b) Rp

### 2.5 System Consideration

Unlike ideal voltage or current sources, solar arrays produce a limited electrical energy which related to the amount of sunlight they receive. As describe earlier, other environmental, such as temperature, also affects the solar array's electrical characteristics. For stand-alone application, it is necessary to incorporate backup battery to provide extra energy when load-demand energy exceeds that provided by the solar array sources, and both battery and arrays must be properly sized. Since the arrays also requires a large area for installation, then for optimal cost benefit it is desirable to extract the maximum power available from solar array sources, with minimum number of arrays installed.

# **CHAPTER 3: MPPT ALGORITHMS**

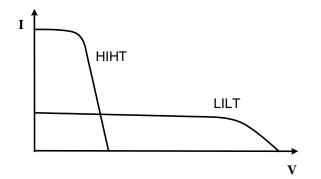

The environmental condition under which a solar power system operates can be wide, as shown in I-V curves in Figure 3.1. The current-voltage relation of a solar array is variable throughout the day, as it varies with environmental conditions such as irradiance and temperature. In terrestrial applications, Low Irradiance, Low Temperature (LILT) condition reflects morning condition where the sun just rises. A High Irradiance, High Temperature (HIHT) condition might represent a condition near high noon in a humid area. High Irradiance, Low Temperature (HILT) condition can represent a condition with healthy sunlight in the winter. Finally, condition near sunset can be described by Low Irradiance, High Temperature (LIHT) condition. For space application, LILT characterizes a deep space mission or aphelion period, while HIHT condition is when satellite orbits near the sun (perihelion).

Figure 3.1: I-V characteristics under wide operating conditions

For a uniformly illuminated array, there is only one single point of operation that will extract maximum power from the array. In a battery charging system where the load seen by the solar modules is a battery connected directly across the solar array terminals, the operating point is determined by the battery's potential. This operating point is typically not the ideal operating voltage at which the modules are able to produce their maximum available power.

Figure 3.2: Direct coupled method

In the direct coupled method [13], in which the solar array output power is delivered directly to the loads, as shown in Figure 3.2. To match the MPPs of the solar array as closely as possible, it is important to choose the solar array I-V characteristic according to the I-V characteristics of the load. A general approach for the power feedback control is to measure and maximize the power at the load terminal, and it assumes that the solar array maximum power is equal to the maximum load power. However, this maximizes the power to the load not the power from the solar array. The direct-coupled method cannot automatically track the MPPs of the solar array when the insolation or temperature changes. The load parameters or solar array parameters must be carefully selected for the direct coupled method

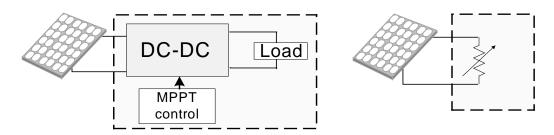

To be able to extract the maximum power from the solar array and to track the changes due to environment, therefore, a maximum power point tracking should be implemented. Devices that perform the desired function are known as Maximum Power Point Trackers, also called MPPTs or trackers. A tracker consists of two basic components, as shown in Figure 3.3: a switch-mode converter and a control with tracking capability. The switch-mode converter is the core of the entire supply. The converter allows energy at one potential to be drawn, stores as magnetic energy in an inductor, and then releases at a different potential. By setting up the switch-mode section in various topologies, either high-to-low (buck converter) or low-to-high (boost) voltage converters can be constructed. The goal of a switch-mode power supply is to provide a constant output voltage or current. In power trackers, the goal is to provide a fixed input voltage and/or current, such that the array is held at the maximum power supply, while allowing the output to match the load voltage.

Figure 3.3: Basic components of a maximum power pointer tracker

When properly applied, a maximum power point tracking control can prevent the collapse of the array voltage under excessive load demand, particularly when supplying a

constant-power type of load. One of the proper approaches is to operate the system in a solar array voltage regulation mode where the array voltage is clamped to a commanding set point, Vmp, which is dynamically updated by the MPPT control circuit. The control processes feedback signals, such as the array current and voltage, to determine a proper direction to move the operating point. Eventually, this continuously updated set point will fluctuate around the voltage corresponding to the array peak power point. By adjusting the operating point of the array to the point Vmp, power output of the array is maximized, and the most efficient use of the solar array may be realized.

For a system without MPPT, the voltage will quickly collapse to zero. This phenomenon can be understood from the I-V characteristic of a solar array. The flatness of the I-V curve on the left of the MPP implies that a small incremental increase in current demand leads to large voltage change. A system with MPPT avoids the voltage collapse by keeping the operating point near the MPP. On the I-V curve, the operating point corresponding to the maximum-power point is around the "knee" region. Therefore, unlike other power systems with stiff voltage sources, power conversion from solar array sources with MPPT requires more robust design due to risks of an array voltage collapse under peak load demand or severe changes in the array characteristics.

The location of the MPP of an I-V characteristic is not known a priori, and must be located. A number of MPPT control algorithms / methods have been proposed. In the subsequent sections, the algorithms will be reviewed. The MPPT method based on dither signal injection will be emphasized, and later applied in this dissertation.

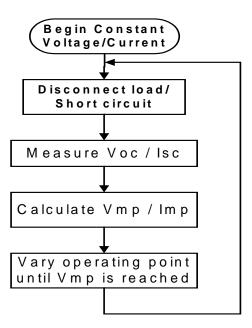

#### 3.1 Constant Voltage and Current

The constant voltage algorithm is based on the observation from I–V curves that the ratio of the array's maximum power voltage, Vmp, to its open-circuit voltage, Voc, is approximately constant:

$$Vmp / Voc = K < 1$$

(3.1)

The constant voltage algorithm can be implemented using the flowchart shown in Figure 3.4. The solar array is temporarily isolated from the MPPT, and a Voc measurement is taken. Next, the MPPT calculates the correct operating point using Equation (3.1) and the preset value of K, and adjusts the array's voltage until the calculated Vmp is reached. This operation is repeated periodically to track the position of the MPP. Although this method is extremely simple, it is difficult to choose the optimal value of the constant K. The literature reports success with K values ranging from 73 to 80%.[14]. Constant voltage control can be easily implemented with analog hardware. However, its MPPT tracking efficiency is low relative to those of other algorithms. Reasons for this include the aforementioned error in the value of K, and the fact that measuring the open-circuit voltage requires a momentary interruption of PV power.

It is also possible to use a constant current MPPT algorithm that approximates the MPP current as a constant percentage of the short-circuit current [15]. To implement this algorithm, a switch is placed across the input terminals of the converter and switched on momentarily. The short-circuit current is measured and the MPP current is calculated, and the PV array output current is then adjusted by the MPPT until the calculated MPP

current is reached. This operation is repeated periodically. However, constant voltage control is normally favored because of the relative ease of measuring voltages, and because open-circuiting the array is simple to accomplish, but it is not practically possible to short-circuit the array (i.e., to establish zero resistance across the array terminals) and still make a current measurement.

Figure 3.4: Constant voltage/current algorithm flowchart

# 3.2 Pilot Cell/Reference Array Measurement Approach

In the pilot cell MPPT algorithm, the constant voltage or current method is used, but the open-circuit voltage or short-circuit current measurements are made on a small solar cell, called a pilot cell, that has the same characteristics as the cells in the larger solar array. Alternative improvement can be achieved with I-V characteristics curve measurement by scanning reference solar cells located at strategic points on the array, but do not constitute a part of the array itself. The pilot cell measurements can be used by the MPPT to operate the main solar array at its MPP, eliminating the loss of PV power during the Voc or Isc measurement. However, the problem of a lack of a constant K value is still present. Also, this method has a logistical drawback in that the solar cell parameters of the pilot cell must be carefully matched to those of the PV array it represents. Thus, each pilot cell/solar array pair must be calibrated, increasing the cost of the system.

#### 3.3 Model-Based MPPT Algorithms

If the values of the parameters in the solar array I-V equation are known for a given solar cell, the solar cell current and voltage could be calculated from measurements of the light incident on and temperature of the solar cell. The maximum power voltage could then be calculated directly, and the PV array operating voltage could be simply set equal to Vmp. Such an algorithm is commonly called a model-based MPPT algorithm. Although appealing, model based MPPT is usually not practical because the values of the cell parameters are not known with certainty, and in fact can vary significantly between cells from the same production run. In addition, the cost of an accurate light sensor (pyranometer) can by itself make this MPPT scheme unfeasible.

#### 3.4 <u>Perturb-and-Observe</u>

As the name of the perturb-and-observe (P&O) states, this process works by perturbing the system by increasing or decreasing the array operating voltage and observing its impact on the array output power. The operating voltage is perturbed with every MPPT cycle. As soon as the MPP is reached, V will oscillate around the ideal operating voltage Vmp. Figure 3.5 summarized the control action of the P&O method. The value of the reference voltage, Vref, will be changed according to the current operating point. For example, for when the controller senses that the power from solar array increases (dP > 0) and voltage decreases (dV < 0), it will decrease (-) Vref by a step size C1, so Vref is closer to the MPP. The MPP represents the point where Vref and scaled down Vsa become equal.

The oscillation around a maximum power point causes a power loss that depends on the step width of a single perturbation. The value for the ideal step width is system dependent and needs to be determined experimentally to pursue the tradeoff of increased losses under stable or slowly changing conditions. In fact, since the AC component of the output power signal is much smaller than the DC component and will contain a high noise level due to the switching DC-DC converter, an increase in the amplitude of the modulating signal had to be implemented to improve the signal to noise ratio (SNR), however, this will lead to higher oscillations at the MPP and therefore increase power losses even under stable environmental conditions.

| Case | dP  | dV  | Action |

|------|-----|-----|--------|

| 1    | < 0 | < 0 | +      |

| 2    | < 0 | >0  | -      |

| 3    | >0  | < 0 | -      |

| 4    | >0  | >0  | +      |

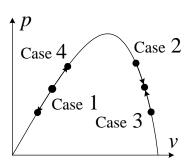

Figure 3.5: Perturb & Observe (P&O) control action

Several improvements of the P&O algorithm have been proposed. One of the simplest entails the addition of a 'waiting' function that causes a momentary cessation of perturbations if the algebraic sign of the perturbation is reversed several times in a row, indicating that the MPP has been reached. This reduces the oscillation about the MPP in the steady state and improves the algorithm's efficiency under constant irradiance conditions. However, it also makes the MPPT slower to respond to changing atmospheric conditions, worsening the erratic behavior on partly cloudy days. Another modification involves measuring the array's power P1 at array voltage V1, perturbing the voltage and again measuring the array's power, P2, at the new array voltage V2, and then changing the voltage back to its previous value and remeasuring the array's power, P1, at V1. From the two measurements at V1, the algorithm can determine whether the irradiance is changing. Again, as with the previous modifications, increasing the number of samples of the array's power slows the algorithm down. Also, it is possible to use the two measurements at V1 to make an estimate of how much the irradiance has changed between sampling periods, and to use this estimate in deciding how to perturb the

operating point. This, however, increases the complexity of the algorithm, and also slows the operation of the MPPT.

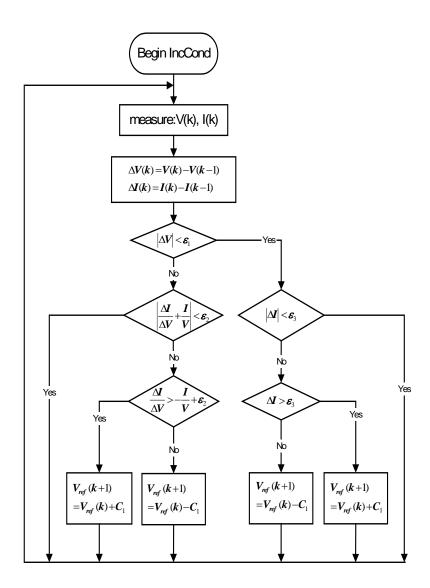

### 3.5 Incremental Conductance

The incremental conductance (IncCond) method [16] is based on comparing the instantaneous panel conductance with the incremental panel conductance. The input impedance of the DC-DC converter is matched with optimum impedance of PV panel. As noted in literatures, this method has a good performance under rapidly changing conditions. The algorithm uses the fact that the derivative of the output power P with respect to the panel voltage V is equal to zero at the maximum power point:

$$\frac{dP}{dV} = I \frac{dV}{dV} + V \frac{dI}{dV} = I + V \frac{dI}{dV} = 0$$

(3.2)

One of the advantages of the IncCond algorithm is that it does not oscillate around the MPP. The check of condition (1) and dI = 0 allows it to bypass the perturbation step and therefore maintain a constant operating voltage V once the MPP is found. Furthermore, conditions  $\left|\frac{dI}{dV} + \frac{I}{V}\right| > 0$  and dI > 0 make it possible to determine the relative location of the MPP. This leads to the advantage that an initial adjustment in the wrong direction, as with the "trial and error" P&O method, does not occur. A fast and correct system response to changing operating conditions should be the result – yielding high system efficiency. A small marginal error could be added to the maximum power condition (1) such that the MPP is assumed to be found if  $\left|\frac{dI}{dV} + \frac{I}{V}\right| < \varepsilon_2$ . The value of  $\varepsilon_2$

was determined with consideration of the tradeoff between the problem of not operating exactly at the MPP and the possibility of oscillating around it. It will also depend on the chosen perturbation step size C1.

Figure 3.6: Incremental conductance algorithm flow chart

#### 3.6 Parasitic Capacitance

The parasitic capacitance algorithm [17] is similar to incremental conductance, except that the effect of the solar cells' parasitic junction capacitance Cp, which models charge storage in the p–n junctions of the solar cells, is included. By adding this capacitance to the lighted diode equation, and representing the capacitance using i(t)=CdV/dt, Equation (3.3) is obtained.

$$I = I_{ph} - I_{s_1} \left[ e^{\frac{q(v_p + IR_s)}{n_1 kT}} - 1 \right] + C_p \frac{dv_p}{dt} = F(v_p) + C_p \frac{dv_p}{dt}$$

(3.3)

On the far right of Equation (3.3), the equation is rewritten to show the two components of I, a function of voltage  $F(v_p)$  and the current in the parasitic capacitance. Using this notation, the incremental conductance of the array  $g_p$  can be defined as  $dF(v_p)/dv_p$  and the instantaneous conductance of the array,  $g_L$  can be defined as  $-F(v_p)/v_p$ . The MPP is located at the point where  $dP / dv_p = 0$ . Multiplying Equation (3.3) by the array voltage  $V_p$  to obtain array power and differentiating the result, the equation for the array power at the MPP is obtained:

$$\frac{dF(v_p)}{dt} + C_p \left(\frac{\dot{V}}{V} + \frac{\ddot{V}}{\dot{V}}\right) + \frac{F(v_p)}{v_p} = 0$$

(3.4)

The three terms in Equation (3.4) represent the instantaneous conductance, the incremental conductance, and the induced ripple from the parasitic capacitance. The first and second derivatives of the array voltage take into account the AC ripple components generated by the converter. The reader will note that if  $C_P$  is equal to zero, this equation

simplifies to that used for the incremental conductance algorithm. Since the parasitic capacitance is modeled as a capacitor connected in parallel with the individual solar cells, connecting the cells in parallel will increase the effective capacitance seen by the MPPT. From this, the difference in MPPT efficiency between the parasitic capacitance and incremental conductance algorithms should be at a maximum in a high-power solar array with many parallel modules.

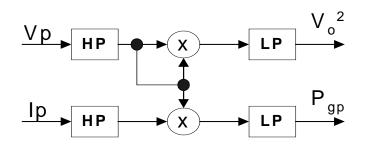

The array conductance is just the ratio of the instantaneous array current to the instantaneous array voltage. Obtaining the array differential conductance is more difficult, but it can be done using Equation (3.5):

$$g_{P} = \frac{P_{GP}}{V_{0}^{2}} = \frac{\frac{1/2}{2} \sum_{n=1}^{\infty} \left[ a_{n}^{i} \cdot a_{n}^{v} + b_{n}^{i} \cdot b_{n}^{v} \right]}{\frac{1/2}{2} \sum_{n=1}^{\infty} \left[ \left( a_{n}^{v} \right)^{2} + \left( b_{n}^{v} \right)^{2} \right]}$$

(3.5)

where  $P_{GP}$  is the average ripple power,  $V_0$  is the magnitude of the voltage ripple, and  $a_n^i$ ;  $a_n^v$ ;  $b_n^i$ ;  $b_n^v$  are the coefficients of the Fourier series of the PV array voltage and current ripples. The values of  $P_{GP}$  and  $V_0^2$  may be obtained from a circuit configuration like that seen in Figure 3.7. The inputs to the circuit are the measured array current and voltage. The high-pass filters remove the DC component of  $V_{PV}$ . The two multipliers generate the AC  $V_0^2$  and AC  $P_{gP}$ , which are then filtered by the low-pass filters, leaving behind the DC components of  $V_0^2$  and  $P_{gP}$ . From Equation (3.5), the ratio of these two values is equal to the array conductance, which can then be used in conjunction with Equations (3.2) until the array differential conductance and the array conductance are equal.

Figure 3.7: Circuitry used to implement the parasitic capacitance method

### 3.7 Dither Signal Injection

The MPPT control usually operates in a limiting cycle oscillation in which the array voltage contains an AC ripple component, while continually tracking the array peak power that varies with changes in environmental conditions. Several MPPT approaches rarely achieve stability in both amplitude and frequency of the oscillatory array voltage ripple. These MPPT controllers can lose their peak power tracking ability and lock up in a "trapped" state far from the array peak power point due to the insufficient strength of the feedback signal used for determining the proper control direction toward the maximum power point. Therefore, an improved MPPT control approach should take into account all the severe circumstances of solar source to achieve sufficient stability margin.

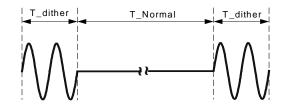

An MPPT approach employing a dither signal superimposed on the updated set point provides the controllability of the amplitude and frequency of the array voltage ripple with respect to the amplitude and frequency of the dither signal. Using the dither signal to properly perturb the MPPT control loop, the power system can operate without a trapped state in which the array voltage is settled far above or below the peak power voltage. In contrast, several other MPPT approaches, without dither signal injection, experience two major difficulties: The first is a trapped state in which the array voltage is undesirably settled down (far from the peak power point condition), and the second is that the operating amplitude and frequency of the array voltage ripple around the peak power point are not fixed and difficult to analyze because of their load dependency. Consequently, the improved MPPT controllers (for different array sources not connected in parallel) can be set to operate synchronously by sharing the same dither signal for which the frequency of the ac voltage ripple in steady-state is the same for all the DC-DC converters being controlled in tandem.

Figure 3.8: Modified dither-based MPPT scheme

Another approach is to vary the amplitude of the dither signal over time, as shown in Figure 3.8. In such an arrangement, a higher efficiency could be expected since the solar arrays primarily operate in near peak power point. Such operation could adopt larger modulation amplitude to increase the SNR and system dynamic performance. Furthermore, multiple local maxima problems could be overcome by finding the global maximum through scanning a wide control range MPPT operation. Since the percentage of large ripple is much smaller, the overall system efficiency will be improved. Dither signal in MPPT method and proposed hybrid MPPT method helps to increase the system stability; however, it also by-produces one drawback namely the output ripple. For multiple channel solar array power system, this issue could be mitigated by inversing the dither signal for the complimentary solar array source.

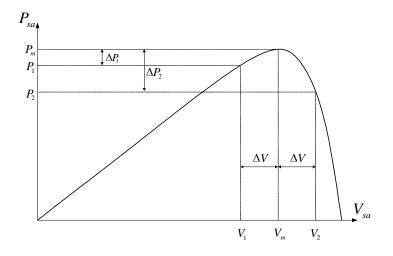

Figure 3.9: Solar array power change vs. voltage change

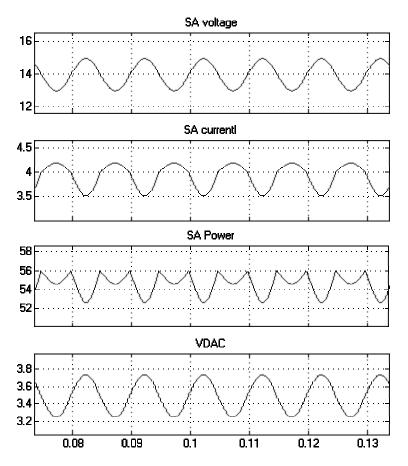

For a system with dither signal added to the setting voltage to generate the reference signal for solar array voltage compensator, the setting voltage is change slowly to keep the system stable. So the reference signal will include the dither signal. Since the solar array voltage will follow the reference signal, the solar array voltage will follow the dither signal changing. Here sinusoidal signal is chosen as dither signal. Figure 3.9 shows the power change according to the voltage change. We can find the power change is not symmetric even if the voltage change is symmetric around the maximum power point. For example, solar array voltage changes from maximum power point  $V_m$  to  $V_1$ , the power change from  $P_m$  to  $P_1$ . The solar array output power will change from  $P_m$  to  $P_2$ ,

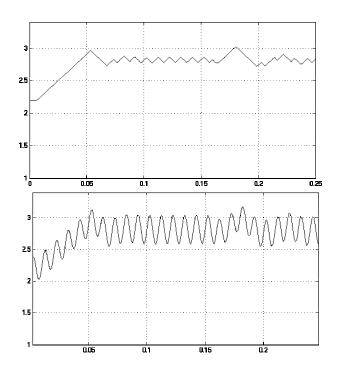

if the changes from maximum power point  $V_m$  to  $V_2$ . Although  $V_m$ - $V_1$  is equal to  $V_2$ - $V_m$  (= $\Delta V$ ), the power change is not the same, i.e.  $\Delta P_1$  is not equal to  $\Delta P_2$ . The simulation results of system with dither signal are shown in Figure 3.10.

Figure 3.10: Simulation results with dither signal added

## 3.8 Analog Implementation

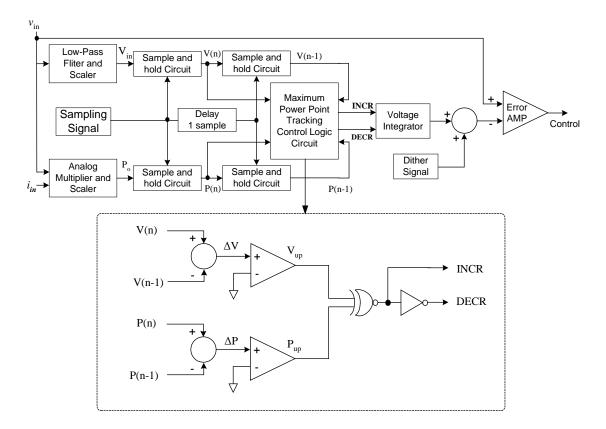

Figure 3.11 shows the detailed block diagram for the maximum power tracking system using discrete components. The description of how the maximum power tracking system automatically adjusts operation conditions of the converter to maximum power

point of the solar array is as follows. The maximum power point tracker receives  $i_{in}$ ,  $V_{in}$  sense signals, and the dither signal to calculate the control signal. The array voltage passes through a low pass filter (LPF) and scalar to provide appropriate signals to the two samples and hold (S/H) circuits. At the output of the sample and hold circuits the present state voltage signal V(n) and the previous state V(n-1) will be generated by sampling  $V_{in}$  at two adjacent sampling times with one sampling period apart. Likewise, the product of  $i_{in}$  and  $V_{in}$  will be processed to provide P(n) and P(n-1) since scaling the current will be correlated with the average output power change and consequently with the average change in the solar array power due to the slow varying output voltage. The sampling intervals are controlled by a sampling signal. The four signals V(n), V(n-1), P(n), and P(n-1) will provide the MPPT control algorithm with enough indications on the direction of voltage and power movements. At the output of the MPPT control circuit the increment INCR and decrement DECR signals will define two operation states; an increment and decrement in the array voltage, respectively.

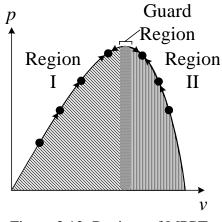

In Figure 3.12 we can notice that during maximum power point tracking process the operation point on the P-V curve can fall in two distinct regions. In region I the operation point will be to the left of the maximum power point and the voltage of the solar array should be increased to move this point up towards MPP. On the other hand when the operation point is to the right of the MPP the solar array voltage should be decreased.

Figure 3.11: Control mechanism of MPPT

Figure 3.12: Regions of MPPT

In order to trace the operation point to its related region, the algebraic difference between V(n) and V(n-1) is generated to produce true logic  $V_{up}$  when the input voltage is

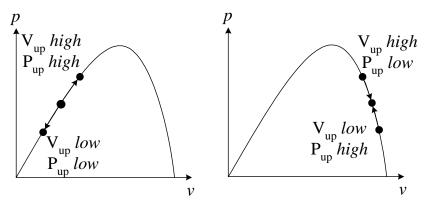

increasing and false  $V_{up}$  other wise. The same process will be applied to P(n) and P(n-1) to produce the logic  $P_{up}$ . Figure 3.13 shows all the logic combinations that may occur and the associated movement of the operation point. When  $V_{up}$  and  $P_{up}$  are either high or low the action should be increasing the array voltage to move the point to a higher position on the curve other. When  $V_{up}$  and  $P_{up}$  have different logic the array voltage should be decreased. Connecting  $V_{up}$  and Pup to an exclusive NOR gate with the direct output to INCR and inverted output to DECR with provide the described functionality.

Figure 3.13: Logic combinations that may occur and its associated movement

The voltage integrator at the output of this logic circuit will provide a linearly changing tracking signal that is clamped between minimum and maximum levels to a summer. This signal will be linearly increasing if only INCR is high and linearly decreasing if only DECR is high. The summer will sum up the tracking signal with the dither signal and provide a set point signal that is AC dithered above the DC level of the tracking signal and feed it to an error amplifier as shown in Figure 3.11. The difference between the summer signal and the input voltage will be amplified through the error amplifier to generate the output control signal that provides the negative feedback closed loop operation and controls the solar array voltage and power.

## 3.9 Applications

The MPPT techniques have much wider application than just photovoltaic alone, since similar functionality of power output versus loading can be seen in the I-V curves of other sustainable energy sources. Such sources are small water turbines and wind-power turbines; however, the actual physics behind the I-V curves for the various sources are different. The voltage, current, and power produced by such sources is variable in response to environmental conditions (insolation, pressure, or wind speed) and dependent on the electrical impedance of the load. Under any combination of environmental conditions, each of these sources is characterized by exactly one ideal load impedance, which will result in operation at  $V_{MPPT}$  and maximum power transfer.

## **CHAPTER 4: SYSTEM CONFIGURATION**