# STARS

University of Central Florida

STARS

Electronic Theses and Dissertations, 2004-2019

2012

# **Bst-inspired Smart Flexible Electronics**

Ya Shen University of Central Florida

Part of the Electrical and Electronics Commons Find similar works at: https://stars.library.ucf.edu/etd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

## **STARS Citation**

Shen, Ya, "Bst-inspired Smart Flexible Electronics" (2012). *Electronic Theses and Dissertations*, 2004-2019. 2483. https://stars.library.ucf.edu/etd/2483

## BST-INSPIRED SMART FLEXIBLE ELECTRONICS

by

## YA SHEN M.S. University of Central Florida, 2009

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

> Summer Term 2012

Major Professors: Xun Gong and Parveen Wahid

© 2012 Ya Shen

## ABSTRACT

The advances in modern communication systems have brought about devices with more functionality, better performance, smaller size, lighter weight and lower cost. Meanwhile, the requirement for newer devices has become more demanding than ever. Tunability and flexibility are both long-desired features. Tunable devices are 'smart' in the sense that they can adapt to the dynamic environment or varying user demand as well as correct the minor deviations due to manufacturing fluctuations, therefore making it possible to reduce system complexity and overall cost. It is also desired that electronics be flexible to provide conformability and portability.

Previously, tunable devices on flexible substrates have been realized mainly by dicing and assembling. This approach is straightforward and easy to carry out. However, it will become a "mission impossible" when it comes to assembling a large amount of rigid devices on a flexible substrate. Moreover, the operating frequency is often limited by the parasitic effect of the interconnection between the diced device and the rest of the circuit on the flexible substrate. A recent effort utilized a strain-sharing Si/SiGe/Si nanomembrane to transfer a device onto a flexible substrate. This approach works very well for silicon based devices with small dimensions, such as transistors and varactor diodes. Large-scale fabrication capability is still under investigation.

A new transfer technique is proposed and studied in this research. Tunable BST (Barium Strontium Titanate) IDCs (inter-digital capacitors) are first fabricated on a silicon substrate. The devices are then transferred onto a flexible LCP (liquid crystalline polymer) substrate using

iii

wafer bonding of the silicon substrate to the LCP substrate, followed by silicon etching. This approach allows for monolithic fabrication so that the transferred devices can operate in millimeter wave frequency. The tunability, capacitance, Q factor and equivalent circuit are studied. The simulated and measured performances are compared. BST capacitors on LCP substrates are also compared with those on sapphire substrates to prove that this transfer process does not impair the performance.

A primary study of a reflectarray antenna unit cell is also conducted for loss and phase swing performance. The BST thin film layout and bias line positions are studied in order to reduce the total loss. Transferring a full-size BST-based reflectarray antenna onto an LCP substrate is the ultimate goal, and this work is ongoing at the University of Central Florida (UCF).

HFSS is used to simulate the devices and to prove the concept. All of the devices are fabricated in the clean room at UCF. Probe station measurements and waveguide measurements are performed on the capacitors and reflectarray antenna unit cells respectively.

This work is the first comprehensive demonstration of this novel transfer technique.

iv

Dedicated to my parents.

## ACKNOWLEDGMENTS

I am deeply in debt to the people who have been with me during these years of my Ph.D study, people who have encouraged me in various ways at different times, and people who have shared my joys and tears. I simply cannot imagine myself facing life's challenges by myself.

Special thanks to my advisors and mentors, Dr. Wahid and Dr. Gong, for their continuous teaching and support all these years. Even during my days of self-doubt and uncertainty, they never gave up on me. I could not ask for more from any mentor.

Huge thanks to all the professors in my committee for their hard work and constructive advice for my research and my dissertation. I feel very sorry for having you all go through my first draft of the dissertation, which, when I look at it now, was kind of like a punishment.

Big thanks to all of my course professors who invested in me. I learned so much from all of you that will surely benefit me for the rest of my life.

Many thanks to all my coworkers who have been working with me for years, some more than the number of fingers on my hand. How can I forget those days when you guys generously offered your time to help me proofread my papers, to prepare me for various presentation occasions and even just to "chit-chat" to lower my stress?

A lot of thanks also go to all my friends from school, from my church family and everywhere else. There are just too many of you so I'm not going to spend pages to list all the names. Thanks for always being there for me whenever I needed you. It is such a blessing to have you all in my life!

vi

And of course, most importantly, I would like to thank my parents. You are the ones who have been there for me ever since I took my first breath. You are the ones who would still love me whether I succeed or fail. I would not have accomplished so much in my life without your teaching, encouragement and love. Hope this one more achievement will add in your collection of "things I'm proud of for my girl"!

# **TABLE OF CONTENTS**

| LIST OF F | FIGURES                                                         | xi    |

|-----------|-----------------------------------------------------------------|-------|

| LIST OF T | TABLES                                                          | xvii  |

| LIST OF A | ACRONYMS/ABBREVIATIONS                                          | xviii |

| CHAPTER   | RONE: INTRODUCTION                                              | 1     |

| 1.1       | Frequency-agile Technologies                                    | 1     |

| 1.1.1     | 1 Semiconductors                                                | 2     |

| 1.1.2     | 2 MEMS                                                          | 4     |

| 1.1.3     | 3 Ferroelectric Materials                                       | 8     |

| 1.1.4     | A Comparison of the Current Available Tunable Technologies      | 12    |

| 1.2       | Flexible Electronics                                            | 13    |

| 1.2.1     | 1 Materials and Fabrication Techniques for Flexible Electronics | 15    |

| 1.2.2     | 2 LCP State-of-the-art Applications                             | 16    |

| 1.3       | Tunable and Flexible – The Newly-mingled Field                  | 19    |

| 1.4       | Dissertation Outline                                            | 21    |

| CHAPTER   | R TWO: BST – A SMART MATERIAL                                   | 23    |

| 2.1       | BST Material Properties                                         | 23    |

| 2.1.1     | 1 Ferroelectric Phenomenology                                   | 23    |

| 2.1.2     | 2 Bulk vs. Thin Film BST                                        | 25    |

| 2.1.3     | BST Thin Film Electrical Properties                             | 26    |

| 2.2       | BST Deposition Techniques                                       | 29    |

| 2.2.1     | 1 RF Magnetron Sputter Deposition                               | 29    |

| 2.2.2     | 2 Pulsed Laser Deposition PLD                                   | 32    |

| 2.2.3     | 3 Sol-gel                                                       | 33    |

| 2.2.4     | 4 Chemical Vapor Deposition CVD                                 | 33    |

| 2.3       | BST Analytical Techniques                                       | 34    |

| 2.4       | BST Transfer Technique                                          |       |

| CHAPTER   | R THREE: BST CAPACITOR ON FLEXIBLE SUBSTRATE                    | 40    |

| 3.1       | Layout Design of BST capacitors                                 | 40    |

| 3.  | 2     | BST Thin Film on a Silicon Substrate                                           | 43  |

|-----|-------|--------------------------------------------------------------------------------|-----|

|     | 3.2.  | 1 Thermal Incompatibility between BST Thin Film and Silicon Substrate          | 44  |

|     | 3.2.  | 2 Deposition and Annealing Parameters for BST Thin Film on a Silicon Substrate | 46  |

|     | 3.2.  | 3 Material Characterization of the BST Thin Film on a Silicon Substrate        | 46  |

| 3.  | 3     | BST IDC on Flexible LCP Substrate – Simulation                                 | 48  |

| 3.  | 4     | BST IDC on Flexible LCP Substrate – Fabrication and Transfer                   | 54  |

| 3.  | 5     | BST IDC on Flexible LCP Substrate – Measurement Setup                          | 60  |

| 3.  | 6     | Measurement Results and Discussions                                            | 62  |

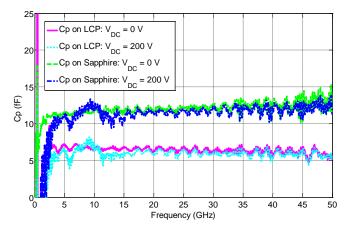

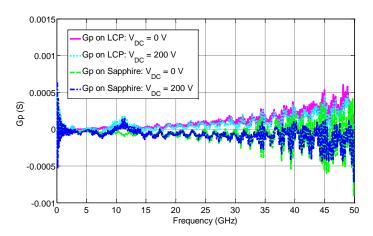

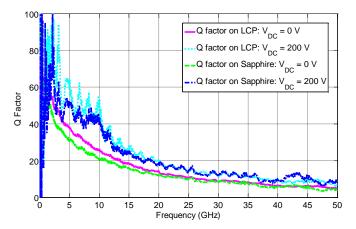

|     | 3.6.  | 1 Measured Results of BST IDC on LCP Substrate                                 | 62  |

|     | 3.6.  | BST IDC on an LCP substrate – Comparison of Measured and Simulated Results     | 67  |

|     | 3.6.  | BST IDC Comparison of Measured Results on an LCP and a Sapphire Substrates     | 72  |

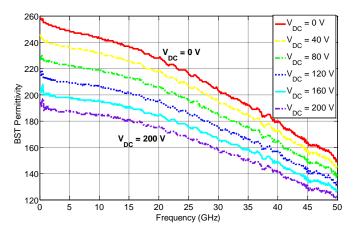

|     | 3.6.  | Extraction of BST Permittivity Values and Loss Tangent Values from measurement | 74  |

| СНА | PTE   | R FOUR: BST-BASED REFLECTARRAY ANTENNA UNIT CELL                               | 78  |

| 4.  | 1     | Why Reflectarray Antenna?                                                      | 79  |

|     | 4.1.  | Advantages and Disadvantages of Parabolic Reflector and Phased Array           | 79  |

|     | 4.1.  | 2 Reflectarray Antenna                                                         | 80  |

| 4.  | 2     | Available Technologies for the Tunable Microstrip Patch Reflectarray antenna   | 81  |

| 4.  | 3     | BST-thin-film-based Reflectarray Antenna Unit Cell Design                      | 84  |

|     | 4.3.  | 1 Patch Size Design                                                            | 84  |

|     | 4.3.  | 2 Proof of Concept: Lumped Capacitor vs. BST-loaded Gap                        | 89  |

|     | 4.3.  | BST thin film Layout Design                                                    | 92  |

|     | 4.3.  | Bias Line Layout Design                                                        | 93  |

| 4.  | 4     | X-band Reflectarray Antenna Unit Cell Simulation                               | 97  |

| 4.  | 5     | X-band Reflectarray Antenna Unit Cell Fabrication                              | 100 |

| 4.  | 6     | X-band Reflectarray Antenna Unit Cell Measurement Setup                        | 104 |

| 4.  | 7     | Results and Discussions                                                        | 105 |

| 4.  | 8 A F | urther Study of Bias Lines                                                     | 109 |

|     | 4.8.  | 1 Optimum Bias Line Position                                                   | 110 |

|     | 4.8.  | 2 X-band Unit Cell Simulation                                                  | 111 |

| 4.  | 9     | A Possible Upgrade – Ka-band Unit Cell Simulation                              | 113 |

| CHAPTER FIVE: CONCLUSION AND FUTURE WORK                         | . 117 |

|------------------------------------------------------------------|-------|

| APPENDIX A: SILICON ETCHING RATE BY KOH SOLUTION                 | . 119 |

| APPENDIX B: CONVERSION OF S-PARAMETERS TO Y-PARAMETERS           | . 121 |

| APPENDIX C: BST IDC ON LCP SUBSTRATE FABRICATION                 | . 123 |

| APPENDIX D: BST-BASED REFLECTARRAY ANTENNA UNIT CELL FABRICATION | . 126 |

| LIST OF REFERENCES                                               | . 129 |

# **LIST OF FIGURES**

| Figure 1 - 1 Varactor Diode                                                                        |

|----------------------------------------------------------------------------------------------------|

| Figure 1 - 2 RF MEMS switch and capacitor4                                                         |

| Figure 1 - 3 Electrical field dependent permittivity                                               |

| Figure 2 - 1 BST molecule structure 24                                                             |

| Figure 2 - 2 polarization of BST material (a) Ferroelectric and (b) paraelectric                   |

| Figure 2 - 3 An RF sputtering system, (a) diagram, (b) targets, and (c) the inside picture of a 3- |

| gun sputtering system                                                                              |

| Figure 2 - 4 Sample data of an RBS measurement                                                     |

| Figure 2 - 5 Sample data of an XRD measurement                                                     |

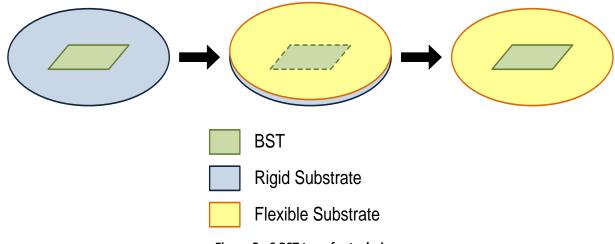

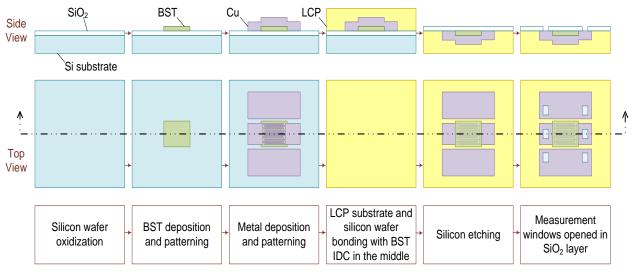

| Figure 2 - 6 BST transfer technique                                                                |

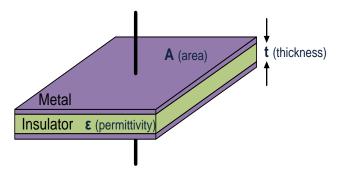

| Figure 3 - 1 Capacitor with MIM structure 41                                                       |

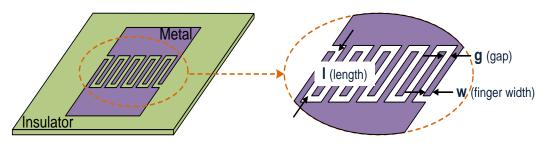

| Figure 3 - 2 Capacitor with IDC structure                                                          |

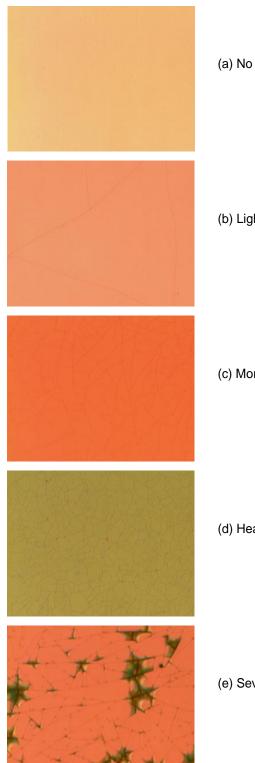

| Figure 3 - 3 Different BST thin film cracking observed under the microscope with the same          |

| magnification                                                                                      |

| Figure 3 - 4 RBS result of a BST thin film on a silicon substrate                                  |

| Figure 3 - 5 XRD result of a BST thin film on a silicon substrate                                  |

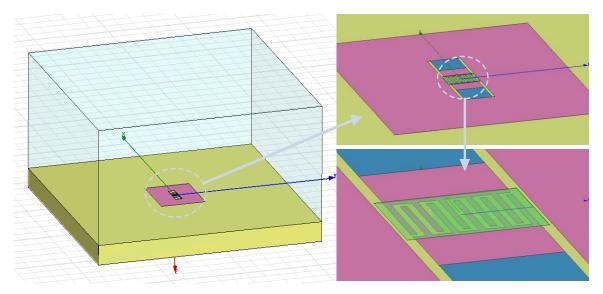

| Figure 3 - 6 HFSS simulation for BST IDC on LCP substrate                                          |

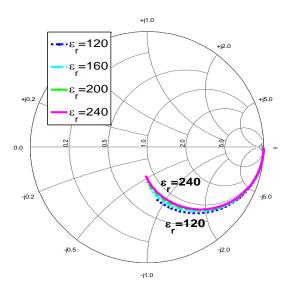

| Figure 3 - 7 Simulated variation of S11 with the BST permittivity $\epsilon_{\rm r}$               |

| Figure 3 - 8 BST IDC lumped element equivalent circuit                                             |

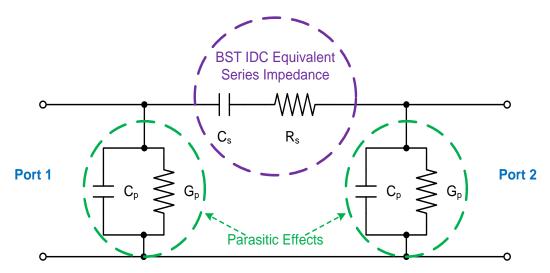

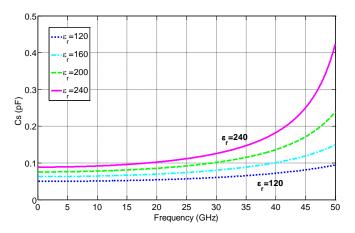

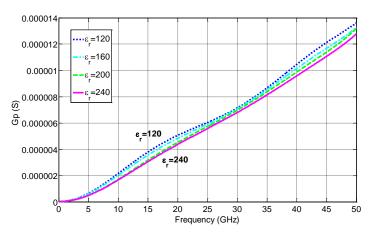

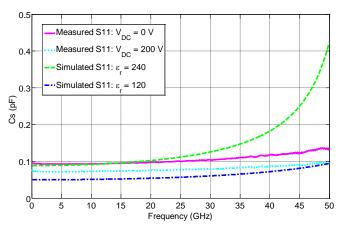

| Figure 3 - 9 Extracted series capacitance Cs from HFSS simulation                                  |

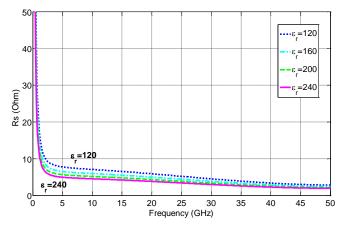

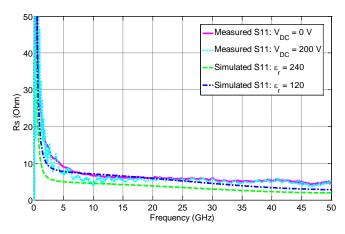

| Figure 3 - 10 Extracted series resistance Rs from HFSS simulation                                  |

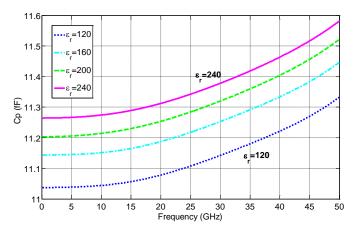

|----------------------------------------------------------------------------------------------------|

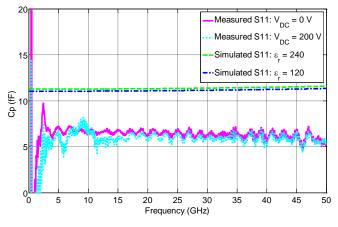

| Figure 3 - 11 Extracted parasitic capacitance Cp from HFSS simulation                              |

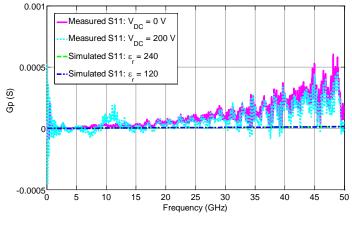

| Figure 3 - 12 Extracted parasitic conductance Gp from HFSS simulation                              |

| Figure 3 - 13 Extracted Q factor from HFSS simulation53                                            |

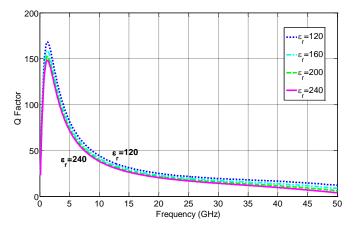

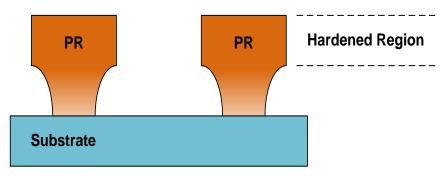

| Figure 3 - 14 PR overhanging or under-cutting effect                                               |

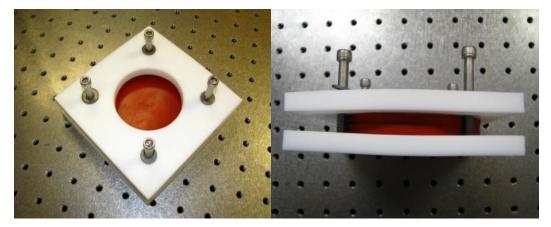

| Figure 3 - 15 A fixture used in silicon etching process to protect the LCP substrate from being    |

| etched by silicon etchant58                                                                        |

| Figure 3 - 16 Fabrication process for the BST IDC on LCP substrate                                 |

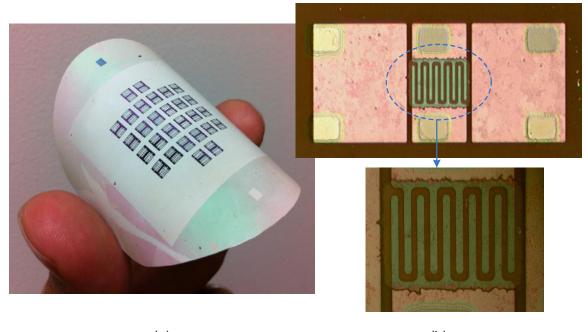

| Figure 3 - 17 BST IDC on an LCP substrate (a) bent (b) under the microscope                        |

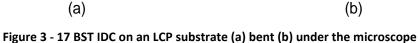

| Figure 3 - 18 Agilent 110 GHz N5250A PNA and Cascade Microtech M150 probe station 61               |

| Figure 3 - 19 Picosecond Pulse Labs model 5543 bias tee                                            |

| Figure 3 - 20 BST IDC being measured using Cascade Microtech GSG 150 probes                        |

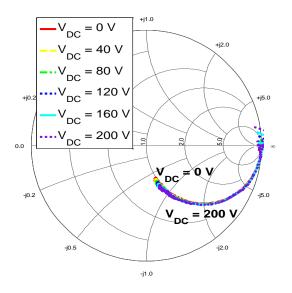

| Figure 3 - 21 S11 with DC bias voltage variation for the BST IDC on LCP substrate                  |

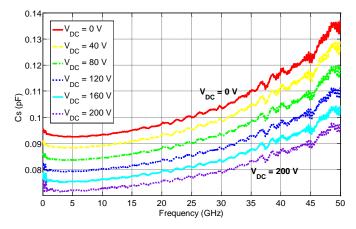

| Figure 3 - 22 Extracted series capacitance Cs with DC bias voltage variation for the BST IDC on    |

| LCP substrate                                                                                      |

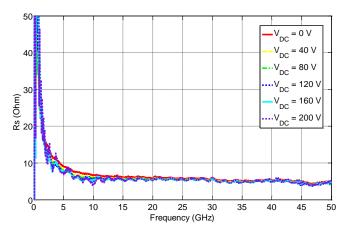

| Figure 3 - 23 Extracted series resistance Rs with DC bias voltage variation for the BST IDC on LCP |

| substrate64                                                                                        |

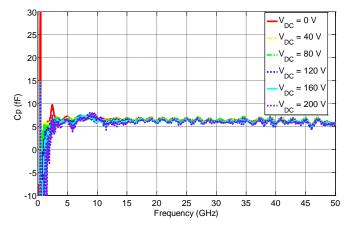

| Figure 3 - 24 Extracted parasitic capacitance Cp with DC bias voltage variation for the BST IDC    |

| on LCP substrate                                                                                   |

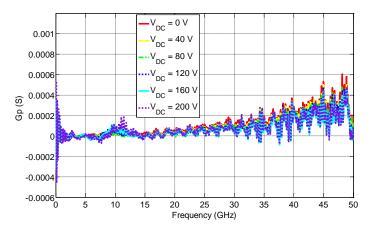

| Figure 3 - 25 Extracted parasitic Conductance Gp with DC bias voltage variation for the BST IDC    |

| on LCP substrate                                                                                   |

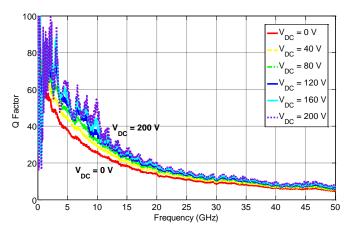

Figure 3 - 26 Extracted Q factor with DC bias voltage variation for the BST IDC on LCP substrate

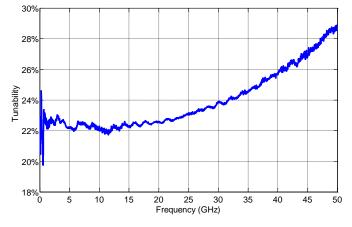

| Figure 3 - 27 Extracted tunability for the BST IDC on LCP substrate                   |

|---------------------------------------------------------------------------------------|

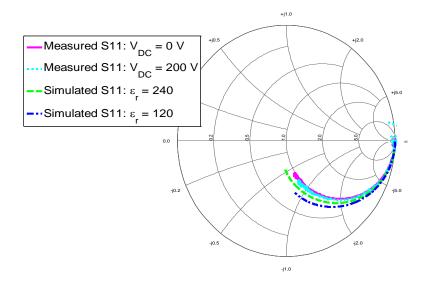

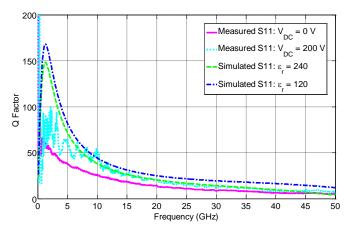

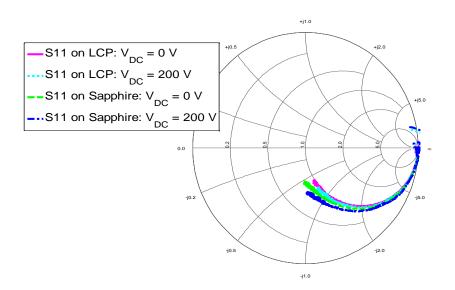

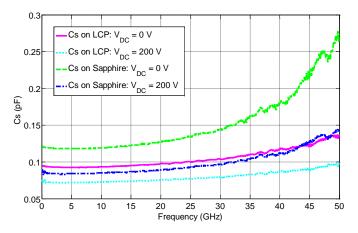

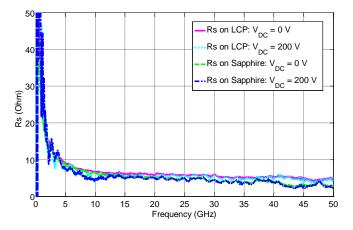

| Figure 3 - 28 Measured S11 vs. simulated S1168                                        |

| Figure 3 - 29 Measured Cs vs. simulated Cs 68                                         |

| Figure 3 - 30 Measured Rs vs. simulated Rs 69                                         |

| Figure 3 - 31 Measured Cp vs. simulated Cp70                                          |

| Figure 3 - 32 Measured Gp vs. simulated Gp70                                          |

| Figure 3 - 33 Measured Q factor vs. simulated Q factor71                              |

| Figure 3 - 34 S11 measured on an LCP substrate vs. on a sapphire substrate            |

| Figure 3 - 35 Cs measured on an LCP substrate vs. on a sapphire substrate             |

| Figure 3 - 36 Rs measured on an LCP substrate vs. on a sapphire substrate             |

| Figure 3 - 37 Cp measured on an LCP substrate vs. on a sapphire substrate             |

| Figure 3 - 38 Gp measured on an LCP substrate vs. on a sapphire substrate             |

| Figure 3 - 39 Q factor measured on an LCP substrate vs. on a sapphire substrate       |

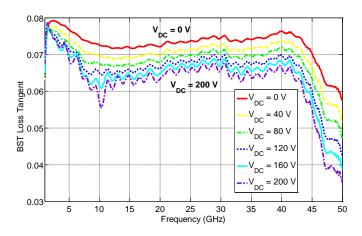

| Figure 3 - 40 Extracted BST permittivity vs. frequency for different DC bias voltages |

| Figure 3 - 41 Extracted BST loss tangent vs. frequency for different DC bias voltages |

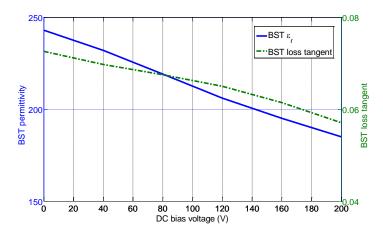

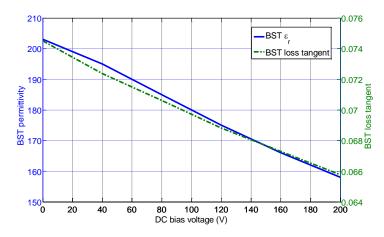

| Figure 3 - 42 Extracted BST permittivity and loss tangent vs. bias voltage at 10 GHz  |

| Figure 3 - 43 Extracted BST permittivity and loss tangent vs. bias voltage at 30 GHz  |

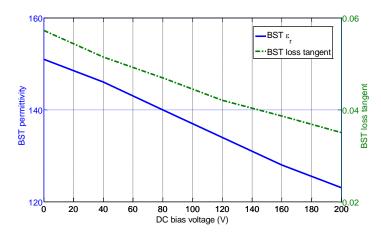

| Figure 3 - 44 Extracted BST permittivity and loss tangent vs. bias voltage at 50 GHz  |

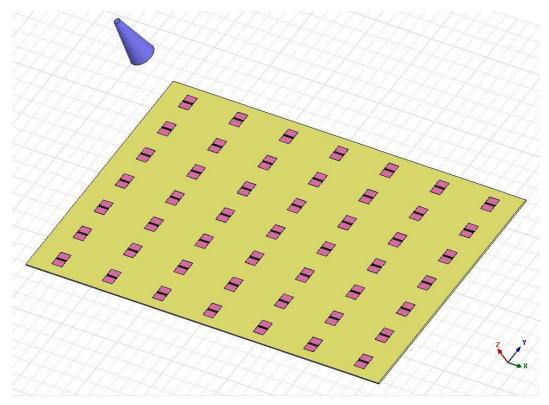

| Figure 4 - 1 A 7 by 7 microstrip-patch-antenna-based reflectarray antenna             |

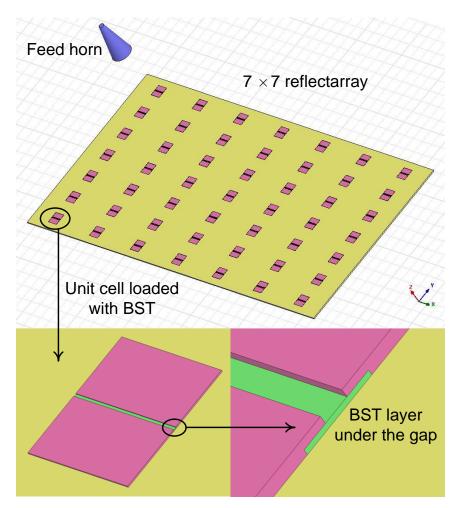

| Figure 4 - 2 A reflectarray antenna with BST-based capacitive loading                                 |

|-------------------------------------------------------------------------------------------------------|

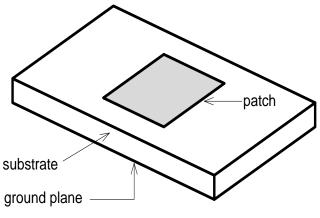

| Figure 4 - 3 Reflectarray antenna unit cell with a square patch                                       |

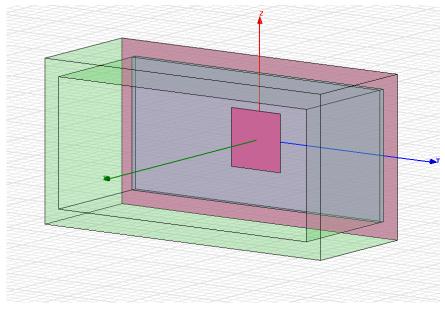

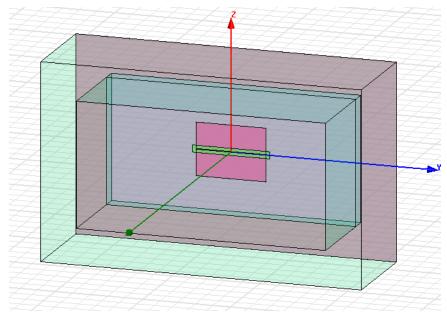

| Figure 4 - 4 HFSS waveguide simulation of a reflectarray antenna unit cell with a square patch 87     |

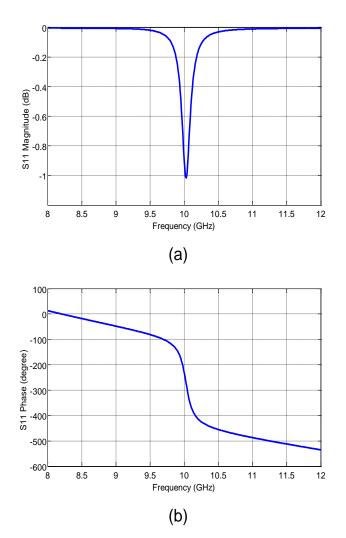

| Figure 4 - 5 HFSS simulation of a reflectarray antenna unit cell with a square patch (a) S11          |

| magnitude, (b) S11 phase88                                                                            |

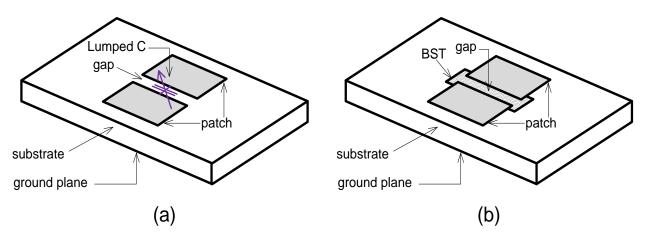

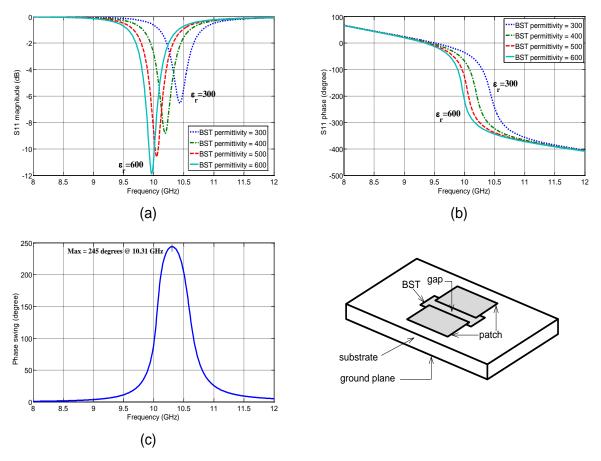

| Figure 4 - 6 Reflectarray antenna unit cell (a) lumped capacitor loading, (b) BST loading             |

| Figure 4 - 7 HFSS simulation results of a reflectarray antenna unit cell with lumped capacitor        |

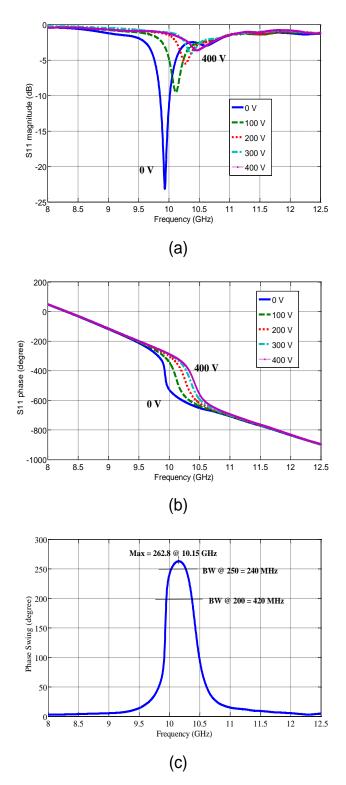

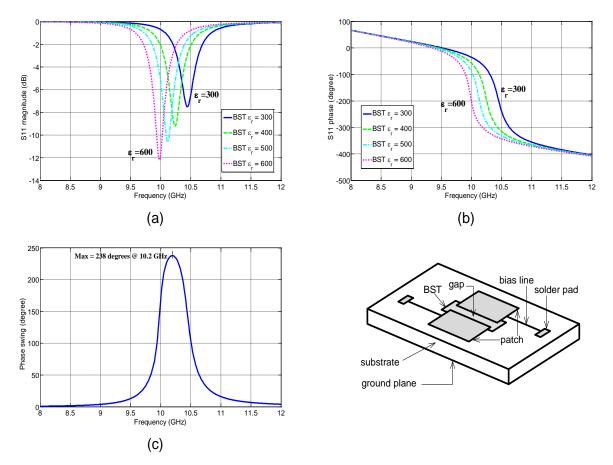

| loading. (a) S11 magnitude, (b) S11 phase, and (c) phase swing                                        |

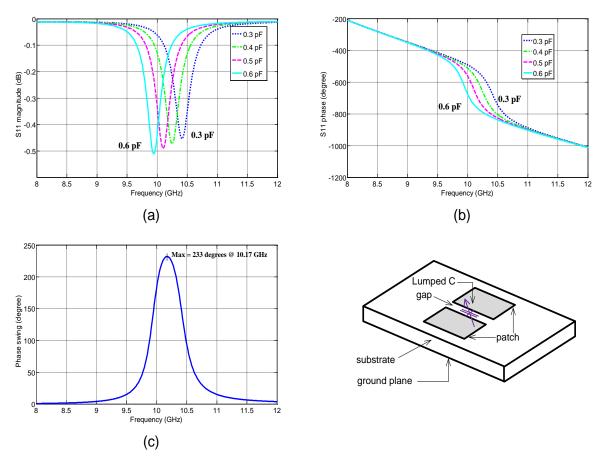

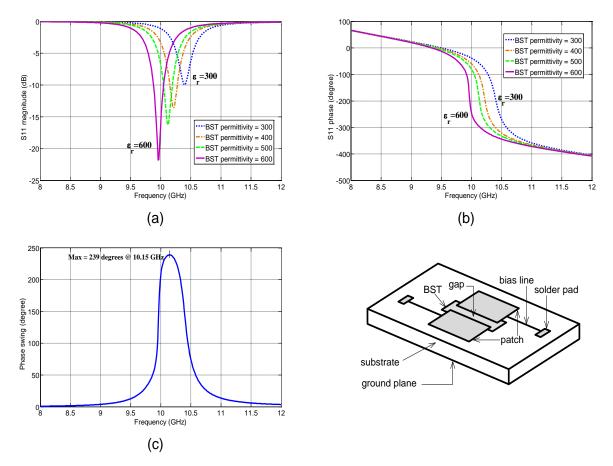

| Figure 4 - 8 HFSS simulation results of a reflectarray antenna unit cell with BST loading. (a) S11    |

| magnitude, (b) S11 phase, and (c) phase swing                                                         |

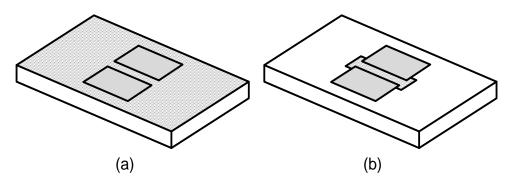

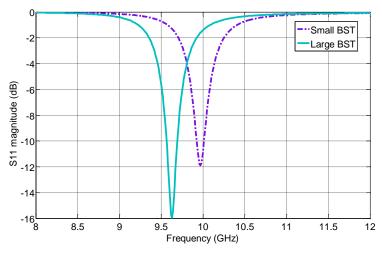

| Figure 4 - 9 Different designs of BST thin film layout (a) BST thin film covering the entire          |

| substrate, (b) BST thin film only under the gap area                                                  |

| Figure 4 - 10 S11 magnitude comparison of reflectarray antenna unit cells with small BST thin         |

| film and large BST thin film93                                                                        |

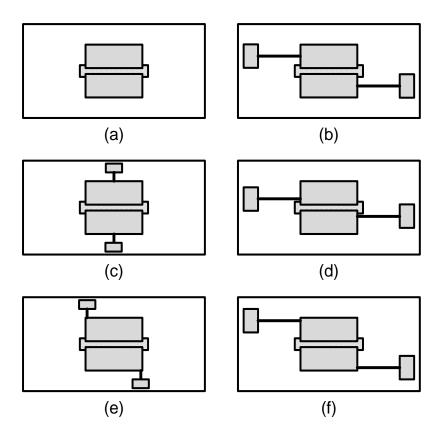

| Figure 4 - 11 Different bias line configurations for reflectarray antenna unit cell (a) no bias line, |

| (b) horizontal bias lines in the middle, (c) vertical bias lines in the middle, (d)                   |

| horizontal bias lines in the center, (e) vertical bias lines in the corner, (f) horizontal            |

| bias lines in the corner94                                                                            |

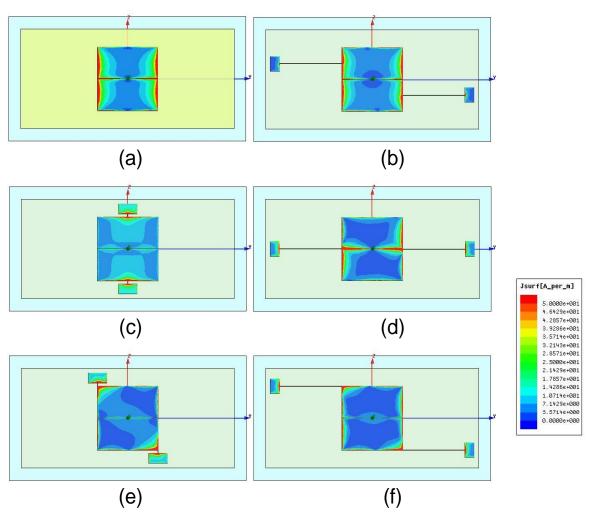

| Figure 4 - 12 Current distribution for reflectarray antenna unit cell with different bias lines (a)   |

| no bias line, (b) horizontal bias lines in the middle, (c) vertical bias lines in the                 |

| middle, (d) horizontal bias lines in the center, (e) vertical bias lines in the corner,             |  |  |  |

|-----------------------------------------------------------------------------------------------------|--|--|--|

| (f) horizontal bias lines in the corner95                                                           |  |  |  |

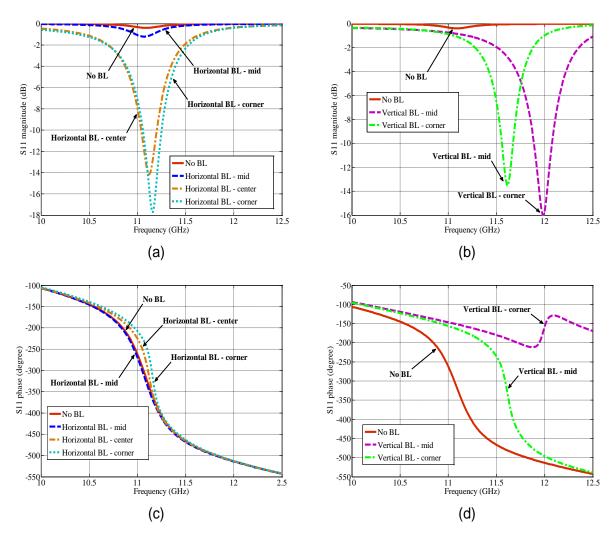

| Figure 4 - 13 HFSS simulation of S11 for different bias line configurations (a) S11 magnitude of    |  |  |  |

| unit cells with horizontal bias lines and without bias line, (b) S11 magnitude of unit              |  |  |  |

| cells with vertical bias lines and without bias line, (c) S11 phase of unit cells with              |  |  |  |

| horizontal bias lines and without bias line, (d) S11 phase of unit cells with vertical              |  |  |  |

| bias lines and without bias line96                                                                  |  |  |  |

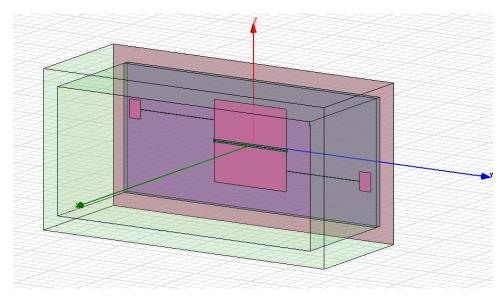

| Figure 4 - 14 HFSS waveguide simulation of a reflectarray antenna unit cell with BST loading and    |  |  |  |

| bias lines                                                                                          |  |  |  |

| Figure 4 - 15 HFSS simulation results of a reflectarray antenna unit cell with BST loading. (a) S11 |  |  |  |

| magnitude, (b) S11 phase, and (c) phase swing                                                       |  |  |  |

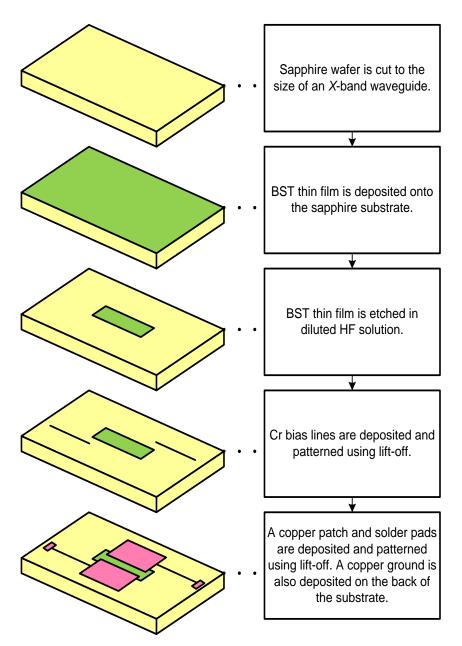

| Figure 4 - 16 Reflectarray antenna unit cell fabrication procedure for the front side 103           |  |  |  |

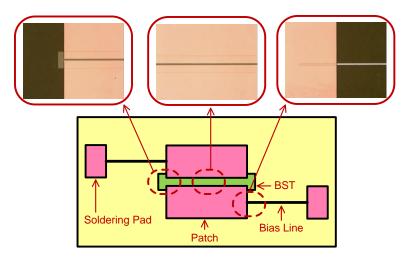

| Figure 4 - 17 Reflectarray antenna unit cell illustration and microscopic pictures                  |  |  |  |

| Figure 4 - 18 Reflectarray antenna unit cell measurement setup 105                                  |  |  |  |

| Figure 4 - 19 Reflectarray antenna unit cell measurement results (a) S11 magnitude, (b) S11         |  |  |  |

| phase, and (c) phase swing106                                                                       |  |  |  |

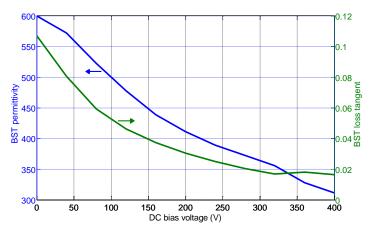

| Figure 4 - 20 Extracted BST permittivity and loss tangent                                           |  |  |  |

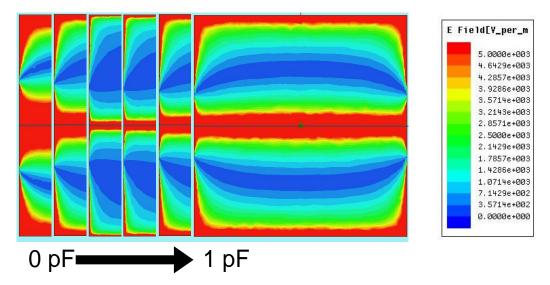

| Figure 4 - 21 E-field shifts with lumped capacitance variation                                      |  |  |  |

| Figure 4 - 22 HFSS simulation results of a reflectarray antenna unit cell with BST loading and      |  |  |  |

| optimized bias lines. (a) S11 magnitude, (b) S11 phase, and (c) phase swing 112                     |  |  |  |

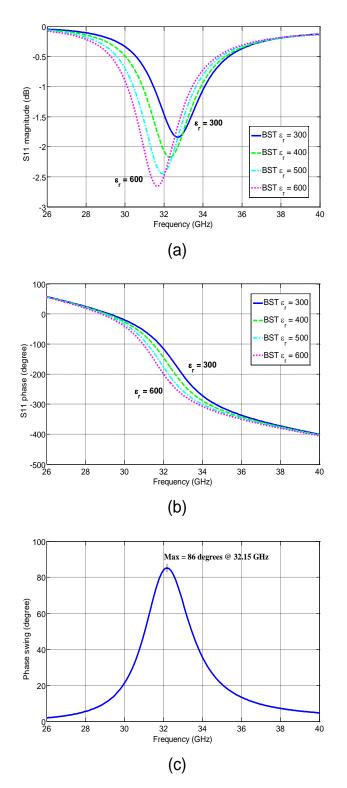

| Figure 4 - 23 HFSS waveguide simulation of a reflectarray antenna unit cell in Ka-band 114          |  |  |  |

Figure 4 - 24 HFSS simulation results of a reflectarray antenna unit cell in Ka-band (a) S11

| magnitude, (b) S11 phase, and (c | ) phase swing 1 | 115 |

|----------------------------------|-----------------|-----|

|----------------------------------|-----------------|-----|

# **LIST OF TABLES**

| Table 1 - 1 Comparison of current available tunable technologies    13                        |

|-----------------------------------------------------------------------------------------------|

| Table 4 - 1 Compare loss performance of reflectarray antenna unit cells with and without bias |

| lines                                                                                         |

| Table 4 - 2 Compare loss performance of measured and simulated reflectarray antenna unit      |

| cells                                                                                         |

| Table 4 - 3 Compare loss performance of reflectarray antenna unit cells with optimized bias   |

| lines and without bias lines 113                                                              |

| Table A - 1 Silicon wafer etching rate in KOH solution       120                              |

| Table A - 2 S-parameter to Y-parameter conversion for 2-port network with the same            |

| characteristic impedance for both ports                                                       |

| Table A - 3 BST IDC on LCP fabrication recipe                                                 |

| Table A - 4 BST-based reflectarray antenna unit cell fabrication recipe                       |

## LIST OF ACRONYMS/ABBREVIATIONS

BOX Buried Oxide BOE Buffered Oxide Etch BPF **Band-Pass Filter** BST Barium Strontium Titanate CCVD **Combustion Chemical Vapor Deposition** CNT Carbon Nanotube CPW Coplanar Waveguide CVD **Chemical Vapor Deposition** CTE **Coefficient of Thermal Expansion** DI Water Deionized Water DMTL Distributed Microelectromechanical Transmission Line DRAM **Dynamic Random Access Memories** EBG Electromagnetic-bandgap EDP Ethylene Diamine Pyrocatechol ΕM Electromagnetic FOM Figure of Merit Frequency-selective surfaces FSS GaAs Gallium Arsenide IDC Inter-Digital Capacitor LCP Liquid Crystalline Polymer

| LNA   | Low Noise Amplifier                     |

|-------|-----------------------------------------|

| LPF   | Low-Pass Filter                         |

| MEMS  | Micro-Electro-Mechanical Systems        |

| MIM   | Metal-Insulator-Metal                   |

| MMIC  | Monolithic Microwave Integrated Circuit |

| MMW   | Millimeter Wave                         |

| MOCVD | Metalorganic Chemical Vapor Deposition  |

| NEC   | Nantenna Electromagnetic Collector      |

| NWT   | Nanowire Transistor                     |

| OLED  | Organic Light-emitting Diode            |

| РА    | Power Amplifier                         |

| РСВ   | Printed Circuit Board                   |

| PLD   | Pulsed Laser Deposition                 |

| РРМ   | Parts-Per-Million                       |

| PR    | Photoresist                             |

| PVD   | Physical Vapor Deposition               |

| PZT   | Lead Zirconate Titanate                 |

| RBS   | Rutherford Backscattering Spectroscopy  |

| RF    | Radio Frequency                         |

| RFID  | Radio Frequency Identification          |

| RPM   | Revolutions Per Mnute                   |

xix

- SBT Strontium Bismutate Tantalate

- SCCM Standard Cubic Centimeter per Minute

- SiNM Silicon-nanomembrane

- SOP System-on-package

- SSP Single Side Polish

- TMAH Tetra Methyl Ammonium Hydroxide

- TMN Tunable Matching Network

- UHV Ultra High Vacuum

- UWB Ultra-wideband

- VCO Voltage Controlled Oscillator

- XRD X-Ray Diffraction

## CHAPTER ONE: INTRODUCTION

Advances in science and technology since the vacuum tube era have brought about the rapid evolution in electronic devices. While the ever-increasing demands of enhanced functionality, downscaled dimension and reduced cost have attracted the spotlight during the 20<sup>th</sup> century, tunability and flexibility are emerging needs for contemporary electronics. The driving force behind this recent focus of interest is indisputable. Tunable devices are 'smart' in the sense that they can adapt to the dynamic environment, varying user demands as well as correct the minor deviations due to manufacturing fluctuations. This favorable feature makes it possible to reduce system complexity and thus overall cost. On the other hand, flexible electronics are desired for their many virtues, such as conformability, portability – being light and able to be rolled up and deployed – and low-cost, thanks to the use of lightweight, flexible and inexpensive substrates.

A lot of research effort and progress has been made in the area of tunable radio frequency (RF) and microwave devices and in the field of flexible electronics respectively. Only during recent years has the possibility of combining the two wonderful properties become evident.

#### 1.1 Frequency-agile Technologies

Tunable RF and microwave devices are often referred to as frequency-agile devices because of their ability to quickly shift the operating frequency to accommodate different

needs. This category includes filters, phase shifters, matching networks, and voltage controlled oscillators (VCO), to name a few. The frequency band for RF and microwave devices generally covers anywhere from 20 kHz to 300 GHz. The three most frequently used technologies that are available in the commercial market are semiconductors, micro-electro-mechanical systems (MEMS) and ferroelectric materials [1] – [3].

### **1.1.1 Semiconductors**

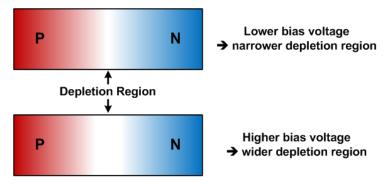

The semiconductor-based varactor diode is the earliest-matured technology among the three technologies mentioned above in the electronics industry. It utilizes a reversely biased PN junction to realize capacitance tuning, as shown in Figure 1 - 1 [4]. As the reverse bias voltage increases, the width of the depletion region grows, thus the capacitance decreases, and vice versa. This effect is equivalent to changing the distance between the plates of a metal-insulator-metal capacitor in order to adjust its capacitance [5].

Figure 1 - 1 Varactor Diode

Because of its tuning mechanism, the varactor diode offers fast and continuous tuning,

yet it is inexpensive for mass production. However, it has disadvantages that limit its

applications, such as low quality factor at microwave frequencies, nonlinear C/V characteristics and low power handling capacity.

Presently, varactor diodes are being used in two main areas: tunable filters and VCOs [6] – [10]. Their main operating frequencies are within several GHz.

The tunable filters have always been a popular research topic. An early study of a varactor-diode-based coplanar waveguide (CPW) slotline bandpass filter in the 1990's showed a tuning bandwidth of 600 MHz at the center frequency of 3 GHz (20% tuning) with a maximum insertion loss of 2.15 dB. This tuning was achieved with a maximum bias voltage of 25 V [6]. A later study of a varactor-diode-tuned filter using a suspended stripline showed a tuning range from 0.7 to 1.33 GHz (60% tuning) with less than 3 dB of insertion loss. The maximum bias voltage applied was 30 V [7]. More recent research results showed several resonator-based two-pole filters using varactor diodes as tuning elements with a tuning range of 0.85 to 1.4 GHz (50% tuning) with no more than 3.5 dB of insertion loss. A maximum bias voltage of 22 V was used [8].

The VCOs have also been studied extensively. Research in the 1990's showed a VCO utilizing a varactor diode achieved a tuning of 9% at 4 GHz with a control voltage of 1 - 3 V. The phase noise was measured at -106 dBc/Hz at 1 MHz and -85 dBc/Hz at 100 kHz [9]. A more recent study of a varactor-diode-tuned VCO showed an improved phase noise of -110.5 – 108 dBc/Hz at 100 kHz that can be tuned from 5.4 to 5.8 GHz with a maximum bias voltage of 26 V [10].

## 1.1.2 MEMS

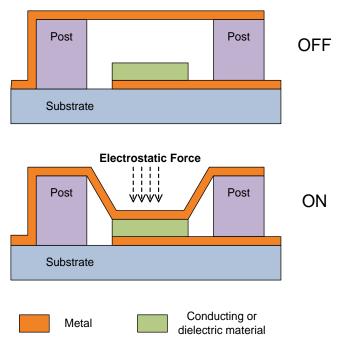

RF MEMS switches and capacitors belong to another popular category of frequencyagile technology. MEMS – from its name, micro-electro-mechanical systems – traditionally refer to miniature structures (usually sub-millimeter in dimension) that combine mechanical and electrical functions. A demonstration of a basic MEMS switch and capacitor is shown in Figure 1 - 2 [1]. Upon applying an electrostatic force, the device changes its state from isolating position (OFF) to conducting position (ON). Based on the type of dielectric material, this ON state can be either conductive – a switch – or capacitive – a capacitor, as the demonstration in Figure 1 - 2 shows. This mechanism means that the tuning of the basic MEMS devices is typically discrete: on and off [11] [12]. However, with some special designs, MEMS devices can be made to perform continuous tuning.

Figure 1 - 2 RF MEMS switch and capacitor

MEMS devices are generally small and light. They provide a very wide tuning range, high quality factor, high power handling capacity and low power consumption. However, because of the need of packaging and the integrated circuit (IC) foundry for microfabrication, MEMS devices are relatively expensive. The parasitic losses in the packages and other circuit connections create a limitation on the operation frequency. Additionally, their reliability has been an area of concern. Several failure mechanisms need to be studied in detail and taken into consideration during design and manufacturing, which include, but are not limited to, mechanical failures, electromechanical breakdown, material deterioration, excessive intrinsic stress, improper packaging techniques and environmental effects [13].

Recent research has shown a promising future for RF MEMS technologies. They can be used as switches or variable capacitors in antennas, phase shifters, tunable filters, etc.

RF MEMS switches with a figure of merit (FOM) of 2 THz were reported in the 1990's by Goldsmith et al. [14]. This FOM is comparable to that of PIN diodes, which are well-known for their excellent FOM performance. *W*-band RF MEMS switches were also reported in [15]. An isolation of 20 dB and an insertion loss of 0.25 dB were measured from a single and a T-match design. An isolation of 30 to 40 dB and an insertion loss of 0.4 dB were measured from a  $\pi$ -match design.

Although RF MEMS varactors are slower than other varactor types, their high level of performance is indisputable. A MEMS parallel plate varactor with discrete tuning was fabricated and measured by Chiao et al. [16], resulting in a maximum capacitance of 35 pF and a minimum capacitance of 0.5 pF, measured using a low frequency capacitance meter. Its breakdown

voltage, over 200 V, was much higher than that of a varactor diode. Another recent report of a MEMS tunable capacitor with a continuous tuning range of 8.4:1 showed a high Q factor of greater than 200 measured over the frequencies from 225 to 400 MHz [17]. Both of these devices showed an exceptional tuning capacity which is superior to either the varactor diode or the ferroelectric tunable capacitor.

RF MEMS switch or varactor based antennas require extra caution during design, since antennas are generally very sensitive to surrounding structures and feeding variations. An early effort of a tunable antenna integrating MEMS technology demonstrated a scanning angle of 48° at 17.5 GHz. Directivity was estimated to be around 38 [18]. A *V*-band 2-D beam-steering antenna applying MEMS technology was reported in [19]. This antenna was driven by magnetic force and reached a maximum scanning angle of 40°.

An RF MEMS phase shifter design can employ many different topologies, such as loaded-line phase shifters, reflection phase shifters, delay line phase shifters, etc. Although MEMS phase shifters provide much lower loss than those based on monolithic microwave integrated circuit (MMIC) technology, they suffer from slow tuning speed, normally in the order of microseconds ( $\mu$ s). A 0 – 60 GHz wide band loaded line phase shifter has been developed in [20], with a phase shift of 118° and an insertion loss of 2 dB when measured at 60 GHz. A phase shift of 84° and insertion loss of 1.8 dB was measured at 40 GHz. The return loss was better than 10 dB for both cases. Two other *W*-band loaded line phase shifters have also been demonstrated in [21]. For the 3-bit distributed microelectromechanical transmission line (DMTL) configuration, phase shifts of 45°, 90°, 135°, 180°, 225°, 270° and 315° were achieved,

and an average insertion loss of 2.7 dB and a return loss better than 10 dB were measured at 78 GHz. For the 2-bit DMTL configuration, phase shifts of 89°, 180° and 272° were achieved, and an average insertion loss of 2.2 dB and return loss better than 11 dB was measured at 81 GHz. A reflection phase shifter was reported in [22]. This 4-bit circuit provided a phase shift from 0 to 337.5° in 22.5° steps. An average insertion loss of 1.4 dB and a return loss better than 11 dB were measured for all 16 states. Two delay line phase shifters, one with 3-bit and the other with 4-bit, were reported in [23]. The 3-bit phase shifter had an average insertion loss of 1.7 dB and a return loss better than 13 dB for all 16 states from 0° to 337.5° with 22.5° increments. The 4-bit phase shifter had an average insertion loss of 2.25 dB and a return loss better than 15 dB for all 8 states from 0° to 315° with 45° increments.

RF MEMS tunable filters have been studied intensively for all frequency bands. A differential 4-bit MEMS band-pass filter designed from 6.5 to 10 GHz was reported in [24]. A 44% tuning range was achieved with return loss better than 16 dB for the whole frequency range. Insertion losses of 4.1 dB and 5.6 dB were measured at 9.8 and 6.5 GHz respectively. Fractional bandwidths of 4.7% and 5.5% were obtained. A *Ku*-band RF MEMS tunable band-pass filter was reported in [25]. A tunability of 44% (from 9.55 to 14.95 GHz), an insertion loss less than 3.2 dB, a return loss better than 15 dB and a fractional bandwidth of 5.3-5.8% were measured. A miniature three-pole slow-wave RF MEMS band pass filter at 18-22 GHz was developed in [26]. This filter exhibited a tuning range of 14% (from 18.6 to 21.4 GHz), an insertion loss of 3.85-4.15 dB and a fractional bandwidth of 7.5%.

In addition to RF and microwave applications, MEMS devices have made their way into numerous fields in the last half a century, for instance, fluidics, thermodynamics, acoustics, electromagnetics, chemistry, biology, optics, etc [27] – [29]. Therefore the name MEMS has also outgrown its classical definition as many MEMS devices nowadays do not involve mechanical movement anymore.

#### **1.1.3 Ferroelectric Materials**

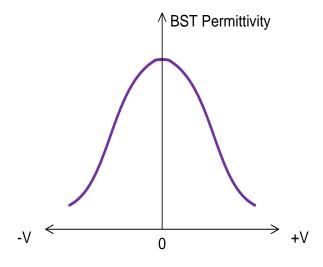

A tunable ferroelectric device is an electrical device whose principle of operation is based on the use and properties of ferroelectric materials with an electrical field dependent permittivity [30]. An illustration of the material dielectric constant being tuned by an external DC bias voltage is shown in Figure 1 - 3 [31]. This bell-shape curve indicates that, as the bias voltage increases (regardless of its polarity), the relative permittivity  $\varepsilon_r$  decreases.

Figure 1 - 3 Electrical field dependent permittivity

Ferroelectric materials have been studied in the RF and microwave realms since the 1950s, yet only during the past two decades has enormous development progress been made. Because of their material properties – high dielectric constant, good tunability, high breakdown voltage and monolithic processing compatibility – ferroelectric materials, such as BST (Ba<sub>x</sub>Sr<sub>1</sub>. <sub>x</sub>TiO<sub>3</sub>), PZT (PbZr<sub>x</sub>Ti<sub>1-x</sub>O<sub>3</sub>), SBT (SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>), etc, are being used in various RF and microwave devices [32]. Among those, BST is most frequently studied because of its overall advantages compared with other ferroelectric materials. Hence the focus of this dissertation is going to be placed on the BST material, specifically on its fabrication on flexible substrates.

BST being such a good candidate for tunable RF and microwave applications, a significant amount of research has been conducted regarding the device implementation of BST materials, for example, BST-based tunable capacitors, filters, phase shifters, and so on.

The very fundamental research efforts were made towards BST capacitors, since BST material is primarily a dielectric. Both metal-insulator-metal (MIM) capacitor and inter-digital capacitor (IDC) structures have been studied for capacitance, tunability, quality factor (Q), linearity, etc. A BST capacitor with MIM structure was reported in [33]. Tunability of 71% (3.4:1) was achieved with a bias voltage of 9 V at frequencies from 45 to 500 MHz, and a Q factor of over 60 was obtained at 50 MHz for a 65 pF capacitor measured at 0V, which is comparable to that of similar semiconductor based varactor diodes. The linearity of BST MIM capacitors was improved in [34] by stacking multiple capacitors in series. The third-order intercept point at input (IIP<sub>3</sub>) was improved by 16 dB. A tunability of 50% (2:1) was measured with a bias voltage of 10 V, and a Q factor from 39 to 49 was obtained for a 1.4 pF capacitor at 1.3 GHz. The BST

varactors with MIM structure usually offer better tunability than those with IDC structure, while the fabrication complexity of BST IDC is usually lower. A BST IDC with a tunability of 21% at a 30-V maximum bias voltage was reported in [35]. Its capacitance was measured from 0.78 to 0.62 pF and a Q factor was measured from 17.1 to 25 with 0 to 30 V bias voltages at 2.5 GHz. A more recently research on a BST IDC working from low frequency to 50 GHz was presented in [36]. This capacitor exhibited a tunability of 63% with a 5 V DC bias. At 0 bias it has a capacitance of 0.2 pF and a Q factor of 50 around 30 GHz.

Other tunable RF and microwave devices based on BST capacitors have also been studied extensively. Tunable filters play a substantial role in a variety of applications in modern communication systems. For this reason, they have been investigated for different frequency bands from VHF to *Ka*-band and above [37] – [40]. A low-pass filter (LPF) and a band-pass filter (BPF) applying BST MIM capacitors and other lumped elements were studied in [37]. For the LPF, an insertion loss of 2 dB, a return loss better than 7 dB, and a tunability of 40% (120 – 170 MHz) with tuning voltages of 0 – 9 V were measured up to 500 MHz. For the BPF, an insertion loss of 3 dB, a return loss better than 7 dB, and a tunability of 57% (176 – 276 MHz) with tuning voltages of 0 – 6 V were obtained. An *S*-band BPF applying BST IDC structure was investigated in [38]. Measurements showed an insertion loss of 5.1 dB at 0 V biasing, 3.3 dB at 200 V biasing and a return loss better than 13 dB for all bias voltages. A tunability of 16% (2.44 – 2.88 GHz) with up to 200 V biasing was also obtained. A *Ku*-band miniaturized (2mm by 6mm) slow-wave tunable BPF utilizing BST IDC structure is demonstrated in [39]. This BPF exhibited an insertion loss of 5.4 dB at 0 V biasing and 3.3 dB at 30 V biasing. The return loss was measured to be

better than 10 dB, and a tunability of 20% (11.5 – 14 GHz) was also achieved. A *Ka*-band tunable BPF using BST capacitors was studied in [40]. This filter presented an insertion loss of 6.9 dB at 0 V biasing and 2.5 dB at 30 V biasing. A return loss of 24 – 13 dB and a tunability of 17% (29 – 34 GHz) were also measured.

Phase shifters are essential components in phased array antennas. Various topologies can be employed with BST capacitors as tuning elements. Two all-pass-network-based phase shifter working at 20 GHz and 30 GHz respectively using BST capacitors were proposed in [41]. The 20-GHz phase shifter reached a maximum phase shift of 330° at 21.7 GHz with a bias voltage of 60 V. The insertion loss was 6.1 dB for 0 V biasing and 4 dB for 20 and 30 V biasing. The return loss was better than 10 dB with bias voltages below 30 V and better than 4 dB with bias voltages up to 60 V. The 30-GHz phase shifter achieved a maximum phase shift of 360° at 32 GHz with a bias voltage of 60 V. The insertion loss was 7 dB for 0 V biasing and less than 5 dB for 10 to 40 V biasing. The return loss was better than 10 dB with bias voltages below 30 V and better than 4 dB with bias voltages up to 60 V. Two reflection-type phase shifters applying Lange couplers and BST IDCs were fabricated and measured in [42]. With bias voltages of 0 – 160 V, the phase shifter using a straight-type Lange coupler showed a maximum phase shift of over  $90^{\circ}$  with an insertion loss better than 2 dB measured at the frequency range of 1.9 – 2.5 GHz. The return loss was better than 14 dB. The phase shifter making use of a folded-type Lange coupler achieved over 130° phase shifter with an insertion loss better than 2.3 dB and a return loss better than 19 dB at 2.2 – 2.6 GHz. Two BST-IDC-tuned phase shifters employing lefthanded transmission line topologies were described in [43]. With bias voltages of 0 - 160 V,

maximum phase shifters of 413° for design-I and 412° for design-II were obtained; maximum insertion losses of 10.3 dB or 8 dB and return loss better than 15 dB or 10 dB were also measured at 10 GHz for design-I and design-II respectively. A phase shifter consisting of a CPW line periodically loaded with BST IDC was described in [44]. A phase shift of 360° was achieved with 40 V biasing at 30 GHz, and insertion losses of below 5 dB and around 15 dB were also measured for bias voltages of 40 V and 0 V respectively. No return loss data was reported in the study. A similar phase shifter applying the same topology was also reported in [45]. This phase shift was characterized up to 30 GHz, with a phase shift of 310° measured with a 35 V bias voltage at 30 GHz, a maximum insertion loss of 3.6 dB and a return loss better than 12 dB.

## 1.1.4 A Comparison of the Current Available Tunable Technologies

Since each tunable technology has its pros and cons, a comparison of these technologies is shown in Table 1 - 1 [1] [2] [46].

|                       | Varactor Diode | MEMS                 | Ferroelectric    |

|-----------------------|----------------|----------------------|------------------|

| Tunability            | High           | High                 | Moderate to High |

| Tuning Speed          | Fast           | Slow                 | Fast             |

| Continuous Tuning     | Continuous     | Discrete (typically) | Continuous       |

| Control Voltage       | Low            | High                 | Low to High      |

| Loss                  | Moderate       | Low                  | Moderate         |

| Power Consumption     | Poor           | Excellent            | Excellent        |

| Reliability           | Good           | Poor                 | Excellent        |

| Cost                  | Moderate       | Moderate             | Low              |

| Packaging Requirement | Need           | Need                 | No Need          |

Table 1 - 1 Comparison of current available tunable technologies

## **1.2** Flexible Electronics

Flexible electronics, as the name implies, mean electronic circuitries and devices fabricated on flexible substrates with the benefit that they can conform to a desired shape or flex before, during or after their use. The very first device was a single-crystalline silicon solar cell that was demonstrated in the 1960's. Since then, the flexible electronics industry has become a wide-open area and has been expanding rapidly [47].

A few recent applications of flexible electronics can be found in the free e-book "A Foldable World" [48]. In 2003, the world's first polymer-based transistor completely produced using continuous mass printing was presented at the Institute for Print and Media Technology at Chemnitz University of Technology. Later, the first fully printed ring oscillator on transparent and flexible substrate applying seven stages using the same printing technology was also created by the same institute [49]. Though the performance of either the transistors or the ring oscillators was not yet comparable to the semiconductor counterparts, the breakthrough of this technology still attracted a lot of attentions. In 2007, fully transparent and medically flexible nanowire transistors (NWTs) on plastic substrates were reported in [50]. These devices exhibited high-performance n-type transistor characteristics with about 82% optical transparency. In 2008, a novel way of collecting solar energy using a flexible nano-antenna electromagnetic collector (NEC) was developed in [51]. These nano-antennas can take in infrared energy that is from both sunlight and the earth's heat and convert it with higher efficiency than conventional solar cells. In later years, more advanced flexible electronics have been reported by both academic and industrial research institutes. Sony demonstrated for the first time a 4.1-inch super-thin (about 80 µm thick) organic light-emitting diode (OLED) display with a 432 × 240 resolution (121 ppi) and a 1000:1 contrast ratio. This display was so thin that it could be wrapped around a pencil while continuing to display images and videos [52]. Biocompatible LED arrays capable of bending, stretching and being implanted under the skin using traditional semiconductor GaAs (Gallium Arsenide) and conventional metals were introduced in [53]. This technology can be used to activate drugs, monitor medical conditions or perform

other biomedical tasks inside human bodies. A thin, flexible secondary Li-ion paper battery applying carbon nanotube (CNT) thin films was also reported in [54]. This battery was only 300µm-thick, yet exhibited robust mechanical flexibility (being able to bend down to less than 6 mm) and high energy density (108 mWh/g). Tests showed that this new prototype was capable of recharging up to 300 times without failure. All-printed and roll-to-roll-printable 1-bit radio frequency identification (RFID) tags on plastic foils were demonstrated in [55]. Operating at 13.56 MHz, these RFID tags could generate 102.8 Hz of clock signal as the tags approached the RFID reader.

#### **1.2.1** Materials and Fabrication Techniques for Flexible Electronics

Popular flexible substrates that serve as replacements for conventional rigid substrates include, but are not limited to, thin glass, organic polymers (plastics) and metal foil [47]. Thin glass is the standard substrate in current flat panel display technology; organic polymers such as polyethylene terephthalate (PET), polyethylene naphthalate (PEN), and polyimide (PI), are being researched to bear silicon-based devices; metal foil substrates are very attractive for emissive or reflective displays. A number of requirements need to be met in the following areas so that these materials can be used as the substrate for flexible electronics: surface roughness, mechanical properties, chemical properties, thermal and thermo-mechanical properties, optical properties, electrical and magnetic properties, etc.

Of the options discussed above, the liquid crystalline polymer (LCP), a class of aromatic polyester polymer, exhibits unique electrical, physical and chemical properties, which makes it

favorable for RF and microwave applications. Section 1.2.2 will talk about different applications of this substrate.

Two industrial approaches are being used for flexible electronics manufacturing: (1) transfer of a complete device or circuit to flexible substrates, and (2) direct fabrication of circuitry on flexible substrates. Either approach requires all components to comply with bending to a certain extent without compromising performance.

For the transfer approach, the whole device or circuit is first fabricated on a traditional rigid substrate such as a silicon or GaAs wafer, then diced and wire-bonded onto a flexible substrate. Wire-bonding has long been used in research and industry. This method provides high-performance devices comparable to those on rigid substrates. However it suffers from small surface area coverage, high cost and high-frequency operation restriction resulting from the inductive effects of the bond wires.

The direct fabrication approach is also used in many applications. It allows large-area mass production with all components fabricated directly onto the flexible substrate. Not all flexible substrates are compatible with the existing microfabrication processes, mostly because of the high-temperature related procedures. Innovative techniques are being investigated, including additive printing of each layer of the devices, the printing of masks and etching, etc.

#### 1.2.2 LCP State-of-the-art Applications

LCP material has drawn a lot of attention in the RF and microwave field because of its low relative dielectric constant, low dissipation factor and low lamination temperature. Recent

research and development have shown that LCP is probably the best polymer for multilayer packaging, because while it is flexible, lighter and much less expensive, it also exhibits device performance comparable to traditional metal and ceramic hermetic packages.

Immersion tests of patch antennas fabricated on three different flexible substrates were carried out in [56]. Results showed that the LCP substrate was superior to the other two lowmoisture-absorption-substrates tested, since it showed no measureable changes in weight or antenna resonance frequency after up to 16-days of submersion in water. It has also been found that LCP materials can be used as a low-cost substitutes for standard hermetic materials for monolithic microwave integrated circuit (MMIC) packaging applications in RF, microwave and millimeter wave (MMW) frequencies. The packaging capability of the LCP substrates was investigated as early as 1995 [57]. It was concluded that the packaged devices can be made hermetic and the weight was only half to one fourth of the ceramic-packaged devices. The cost was about one fifth of that for ceramic packaging. Recent research has showed even more capacities of this substrate. LCP substrates with laser-micromachined cavities were used as the packaging substrate for MMIC and RF MEMS devices. Results measured up to 40 GHz showed that no significant difference was found between the devices with and without LCP packaging. For millimeter wave (MMW) applications, LCP substrate was studied as the substrate/packaging material for a low-loss integrated waveguide (IWG), a microstrip line-to-IWG transition and an IWG bandpass filter (BPF) in [59]. The insertion loss was measured at 0.12 dB/mm for the IWG and 0.14 dB for the microstrip line-to-IWG transition at 60 GHz. The three-pole BPF with a center frequency of 61.1 GHz achieved a 3-dB bandwidth of 13.4%, an insertion loss of 1.8 dB

and a rejection of greater than 15 dB. For all the applications demonstrated, LCP substrate has been proven as an excellent RF and microwave substrate and a system-level packaging material.

Various antennas and power amplifiers on LCP substrates were also studied and compared with those on rigid substrates. An RFID tag antenna covering both the European (866 MHz – 868 MHz) and North American (902 MHz – 928 MHz) RFID UHF frequency bands was fabricated on 4-mil-thick LCP substrate in [60]. The measured return loss was better than 10 dB, which was in agreement with the simulation. Dual-frequency (14 GHz and 35 GHz), dualpolarization microstrip antenna arrays were demonstrated in [61]. The return losses for both frequencies were better than 15 dB, and the measured bandwidths agreed with simulation results. A CPW-fed micromachined stacked patch antenna was presented in [62]. The LCP material was used to mechanically support and form cavities to protect the radiating and parasitic patch elements. Measurement results showed a gain of 7.6 dBi and a bandwidth of 44%. A flexible ultra-wideband (UWB) elliptical slot antenna on LCP substrate was investigated for breast cancer detection in [63]. This CPW-fed antenna was capable of detecting small tumors with a size below 2 mm. The preliminary results of using a conformal 3-element array showed very promising sensitivity enhancement. A 6 – 18 GHz push-pull power amplifier (PA) module on a LCP substrate was studied in [64]. With very low even-order distortions, this PA showed a  $P_{1dB}$  power of 31 dBm and a 2<sup>nd</sup> order harmonic distortion reduction of over 20 dB compared to a single PA throughout the passband.

#### 1.3 Tunable and Flexible – The Newly-mingled Field

As both tunability and flexibility are much desired features, many research groups have invented new techniques that can realize this combination in the RF and microwave regions. The following attempts are the most cutting-edge accomplishments and thus are not commercially available yet.

One simple concept is to mount tunable components onto a flexible substrate to realize both tunability and flexibility. An example can be found in [65], in which a low-loss and compact-sized X-band analog tunable filter was fabricated and measured on a flexible LCP substrate. Tunable BST capacitor chips were surface-mounted onto the substrate using silver epoxy and ribbon bond. This design was flexible and about 50% smaller than a conventional open-loop resonator filter, and yet achieved a tuning of 12%, a return loss of better than 10 dB and an insertion loss of 1.8 – 5.5 dB. However, as mentioned in the previous section, this method has limitations, such as the extent of flexibility and the operation frequency. Specifically, the bond wires used in the circuit will add in a considerable inductive effect as the operation frequency increases.

Another remarkable approach is based on silicon-nanomembrane (SiNM), as described in detail in [66]. Silicon based devices, such as diodes (varactors) and transistors, can first be fabricated on the silicon nanomembrane, which is an elastically strain-sharing multilayer structure consisting of Si-SiGe-Si layers. This multilayer structure is originally positioned on a buried oxide (BOX) layer on a silicon wafer. By removing the BOX layer, the SiNM layer with the device is released from the silicon wafer, and can then be transferred onto a foreign substrate,

including a flexible substrate. For instance, SiNM-based PIN diodes on flexible plastic substrates were demonstrated in [67]. Measurement showed typical rectifying characteristics. An insertion loss of less than 1.7 dB and isolation better than 20 dB were achieved from DC up to 5 GHz at low bias conditions. This approach is an innovation of the monolithic fabrication of siliconbased devices. Nevertheless, the possibility of large-scale fabrication is still under investigation.

Another notable method is to take advantage of the packaging capability of flexible materials to realize reconfigurable system-on-package (SOP). In [68], two reconfigurable RF MEMS phased array antennas were integrated into a SOP on LCP substrates. LCP substrates, in this case, were used as the RF substrates as well as the packaging materials. Working at 14 GHz, both antennas (one using a single layer SOP and the other using a multilayer SOP) exhibited low loss characteristics and were able to achieve 12° of beam steering. In [69], tunable frequencyselective surfaces (FSS) and electromagnetic-bandgap (EBG) structures on rigid-flex Kapton substrates were fabricated using a newly-developed MEMS process. Kapton substrate is all dielectric and after the special treatment is semi-flexible. The FSS switching between Ku-band and Ka-band showed center frequencies of 17.8 GHz and 21.3 GHz at down-state and up-state, respectively. The measured ±90° bandwidth for the EBG was 1.91% (bias on) and 1.29% (bias off). Another example demonstrated that MEMS sensors, a flow sensor and a tactile sensor, can be fabricated directly onto the flexible LCP substrate [70]. The flow sensor tested with flow rates from 0 to 20 m/s showed an expected velocity-squared relationship. The tactile sensor displayed a hysteretic behavior originally, which disappeared after flexing the device for a few times.

BST-based tunable capacitors have also been made on copper foil with the use of controlled oxygen pressure [71] or in a nearly inert atmosphere [72] during annealing. The core of both techniques is to prevent copper from oxidazing in the high temperature annealing process. The drawback for this technique is that copper is not a typical RF and microwave substrate, therefore the applications for BST thin film on copper foil are limited.

The use of liquid crystal as the dielectric material of a tunable capacitor working in RF and microwave frequencies was also presented in [73]. With a control voltage of 5 V, a quality factor of 310 was measured at 4 GHz, and a tunability of 25.4% was obtained at 5 GHz. This approach is suitable for preparing tunable devices on flexible substrates, especially for transparent applications.

In this work, the possibility of BST thin film on LCP substrate is investigated, and a new transfer technique incorporating wafer-bonding and substrate-etching is proposed. This will be discussed in detail in Chapter 2.

#### **1.4 Dissertation Outline**

This dissertation consists of five major sections.

The first chapter is an introduction to tunable and flexible electronics. It covers the motivation of this work, and the state-of-the-art research in tunable components, flexible devices, and smart flexible electronics.

Chapter 2 is everything about BST – Barium Strontium Titanate. Material properties, deposition techniques, analytical techniques and a new transfer technique are all discussed in detail.

Chapter 3 talks about our research of a new transfer technique to realize BST-based tunable capacitors on flexible LCP (liquid crystalline polymer) substrates. Simulation, fabrication, measurement, results and detailed discussions are presented.

Chapter 4 focuses on our primary study of a BST-based reflectarray antenna. Unit cell optimization is studied and the results are verified by either simulation or measurement or both.

This dissertation is concluded in chapter 5. Future work based on this research is also proposed.

# CHAPTER TWO: BST – A SMART MATERIAL

BST, Barium Strontium Titanate, is considered a smart material mainly because of its electric-field-dependent permittivity. It also has other good qualities such as high permittivity and a high breakdown voltage. This chapter will focus on different aspects of this material, including physical and electrical properties, fabrication methods, material characterization and a new transfer technique that makes it possible to have BST thin films on flexible LCP substrates.

## 2.1 BST Material Properties

## 2.1.1 Ferroelectric Phenomenology

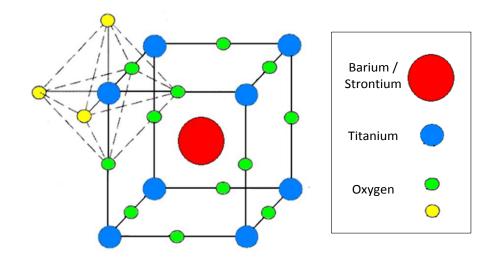

Ba<sub>1-x</sub>Sr<sub>x</sub>TiO<sub>3</sub> is a continuous solid solution between two basic substances, BaTiO<sub>3</sub> and SrTiO<sub>3</sub>. Since both of them have the perovskite crystal structure, BST naturally inherited the same structure. Figure 2 - 1 shows a BST perovskite crystalline lattice, where a large Barium (Ba) or Strontium (Sr) atom (red) occupies the center position of the cube, eight Titanium (Ti) atoms (blue) sit in the corners, and twelve Oxygen (O) atoms (green) take the midpoint of each edge. The yellow atoms are oxygen ions from adjacent molecules that share the titanium ion in that corner.

Figure 2 - 1 BST molecule structure

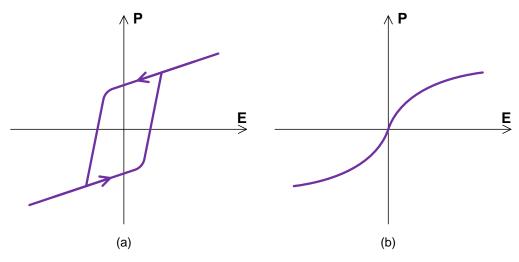

Although BST is usually considered a ferroelectric material, it undergoes two different phases, namely ferroelectric phase and paraelectric phase, separated by a transition temperature called the Curie temperature,  $T_C$  [74]. BST material is in the ferroelectric phase when the temperature is below  $T_c$ . In this phase, the BST material demonstrates a spontaneous (zero field) polarization. The direction of this spontaneous polarization can be reversed by applying an electric field (not exceeding the breakdown limit of the crystal). This polarization reorientation creates a hysteresis loop, as shown in Figure 2 - 2 (a). This phenomenon indicates that there is a memory effect in the ferroelectric phase, which can be utilized in nonvolatile memory applications. Above the Curie temperature the hysteretic effect disappears, and the BST material enters the paraelectric phase, see Figure 2 - 2 (b) [75]. The paraelectric phase is very useful for dynamic random access memories (DRAM) and tunable capacitor applications.

Figure 2 - 2 polarization of BST material (a) Ferroelectric and (b) paraelectric

Research shows that the Curie temperature  $T_c$  is a function of the stoichiometry of the BST composition, specifically, it decreases with increasing Sr content, as shown in [76]. Therefore, the Curie temperature of the BST material can be adjusted by controlling the ratio between BaTiO<sub>3</sub> and SrTiO<sub>3</sub> in the BST compound, so that the BST material will exhibit the desired phase – ferroelectric or paraelectric – in the temperature range that the device is set to work. For all the applications presented in this dissertation, the BST thin film in the paraelectric phase is used.

#### 2.1.2 Bulk vs. Thin Film BST

BST material takes two forms – bulk and thin film – and they behave quite differently. The permittivity of BST bulk ceramic is extremely high, typically in the thousands, and it increases sharply when the temperature is in the close vicinity of the Curie point  $T_c$ . This behavior shows up in both the ferroelectric and paraelectric phases. On the other hand, the permittivity of BST in the thin film form is much lower, usually in the hundreds, and there is no sharp peak observed with temperature variation. An example is shown in [77].

For the BST thin film particularly, the permittivity also varies with film thickness, as shown in [78]. A thicker film provides higher permittivity as well as higher tunability. Therefore, a certain thickness is needed in order to reach a specific value for both the permittivity and the tunability.

In this dissertation we are studying BST thin films on LCP substrates and sapphire substrates for applications in tunable capacitors, phase shifters and reflectarray antennas.

#### 2.1.3 BST Thin Film Electrical Properties

Originated from the perovskite crystal structure, the BST thin film possesses a few unique electrical properties that make it an excellent candidate for RF and microwave applications. Some of these properties are listed below.

#### 1. High permittivity.

Thin film BST permittivity is usually in the hundreds, depending on the BST composition (Ba:Sr ratio), the thickness of the film and the level of crystallization. A better crystallized BST thin film can be obtained by optimizing the deposition conditions, such as substrate temperature, annealing temperature, ambient pressure, gas mixture, etc, during both deposition and annealing processes. Thicker film and better crystallization ensures higher

permittivity, and the higher permittivity allows smaller device dimensions and therefore a compact design.

2. Tuning capability.

Tunability is the most favorable feature for tunable electronics, and is mainly determined by the BST composition (Ba:Sr ratio), doping in the material and the level of film crystallization. BST thin film has demonstrated a tunability of nearly 75% in [80], which is equivalent to a ratio of 4:1 for maximum to minimum permittivity.

Tunability is defined by:

$$Tunability = \frac{C_{\max} - C_{\min}}{C_{\max}}$$

(2-1)

3. Moderate loss.

Material loss is a regular concern for all device manufacturing. BST thin film loss tangent ranges from beyond 0.01 to 0.1[79], and is affected mainly by lattice defects and interfacial contaminations.

4. Fast tuning.

BST tuning originates from its dipole reorientation, thus its tuning speed is as fast as the rate of its electric polarization, which is normally in the picoseconds range. This is critical for applications that require fast response, like multipliers and phase shifters.

## 5. Continuous tuning

The dipole-reorientation-originated tuning is also continuous. Therefore, with a proper bias voltage, the BST permittivity can reach any value between the minimum and maximum of that particular film.

#### 6. Non-linear behavior

The non-linear relationship between the electric field (bias voltage) and the permittivity, as shown in Figure 1 - 3, makes it possible for the BST thin film to be used in frequency conversion devices, such as multipliers and mixers.

# 7. High power handling capacity

High breakdown voltage of more than  $2 \times 10^6$  V/cm has been reported in [80]. This ensures that BST thin film can handle large RF signals and thus can be used in high power devices.

8. Low power consumption or leakage current

Leakage current is the main cause for power consumption. Devices made from BST thin films exhibit low leakage current density in the order of  $10^{-8}$  A/cm<sup>2</sup> [81].

9. High frequency device feasibility

BST thin film based devices are compatible with the existing semiconductor manufacturing process. This lack of a packaging requirement enables the integration with other parts of the circuit components, thus leading to low cost applications in RF and microwave even millimeter wave (MMW) frequencies.

# 2.2 BST Deposition Techniques

The most commonly used BST deposition techniques in research and in industry are the RF magnetron sputter deposition, pulsed laser deposition (PLD), sol-gel, chemical vapor deposition (CVD) including metal-organic chemical vapor deposition (MOCVD) and combustion chemical vapor deposition (CCVD). Since RF magnetron sputtering is employed in this work, it is explained here in detail. A brief description of the other processes is also given in the following sections.

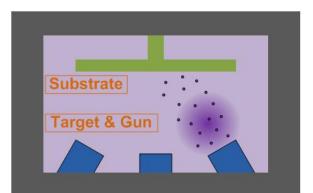

#### 2.2.1 **RF Magnetron Sputter Deposition**

Sputter deposition falls into the physical vapor deposition (PVD) category. It is a process of depositing thin films by ejecting material atoms or molecules from a source material onto a substrate using atom bombardment, which is excited by accelerating ionized neutral gas

molecules in a vacuum environment. A typical system is illustrated in Figure 2 - 3 (a) [82]. The source material is also called a 'target', also shown in Figure 2 - 3 (b), which is mounted in a 'gun' located at the bottom of the system.

(b)

(c)

Figure 2 - 3 An RF sputtering system, (a) diagram, (b) targets, and (c) the inside picture of a 3-gun sputtering system

The use of a magnetron – by placing a magnet below the target in the gun – can

considerably improve the deposition rate. Both DC power and RF power can be used in the

magnetron sputtering system. DC magnetron sputtering is only good for conducting materials while RF magnetron sputtering can be used for both conducting and non-conducting materials. The top view of an open magnetron sputtering system with 3 guns is shown in Figure 2 - 3 (c). This system is capable of loading up to 3 different materials in the same chamber. Therefore, 3 different thin films or the combination of any of them may be deposited in the same vacuum.

When the RF magnetron sputtering process starts, the magnetic field traps a good number of free electrons right above the target. This greatly increases the chance of the neutral gas molecules getting ionized by these electrons. The positively charged ions (ionized neutral gas molecules) are then attracted towards the target by the cathode connected to gun and strike the target in an accelerated fashion. The target is then eroded by these ions through momentum transfer and the source material is ejected as neutral particles – in the form of individual atoms and/or clusters of atoms or molecules – traveling in a straight line onto the substrate. Thin film deposition is achieved as a result.

An AJA ATC 1800 magnetron sputtering system is used to deposit BST thin films in this work. With three guns and two power sources, one DC and one RF, this system can deposit three different types of thin films alternatively or a combination of two materials.

#### 2.2.2 Pulsed Laser Deposition PLD

PLD is also classified as a PVD process. It utilizes a focused pulsed laser beam with high power to strike a material target in such a way that the material is vaporized and deposited onto a substrate [83]. Although a series of events occur during this whole process, the

deposited thin film keeps the exact same chemical composition as the target material. The uniqueness of this deposition is that the energy source (laser) is placed outside the chamber, thus the operating pressure can be controlled in a wide range from ultra high vacuum (UHV) to a fraction of the atmosphere pressure. Additionally, film thickness can be controlled by varying the number of laser pulses.

Detailed BST thin film deposition parameters using PLD technique can be found in [84].

#### 2.2.3 Sol-gel

The sol-gel process is a wet-chemical deposition technique that employs a 'sol' (usually a colloidal solution) as the precursor to evolve towards the formation of a solid 'gel' phase [85]. A thin film can be obtained by spin-coating or dip-coating a substrate. Other forms, such as fiber, powder, porous and dense materials, can also be produced by appropriate treatment. A drying or thermal procedure is often needed afterwards for further poly-condensation or mechanical property and stability enhancement.

A detailed description of BST thin film deposited by the sol-gel process can be found in [86].

### 2.2.4 Chemical Vapor Deposition CVD

The CVD process makes use of the reaction and/or decomposition of volatile precursors in gaseous state to produce the thin film when they pass over or come into contact with a heated substrate. CVD is extremely versatile and can be used to process a wide range of metals

and ceramics. Substrate temperature, chamber pressure and precursor concentration are the control parameters that will yield the desired thin film product [87].

The CVD process can be further classified into many different categories, among which MOCVD [88] and CCVD [89] are being used for BST thin film deposition.

### 2.3 BST Analytical Techniques

After a BST thin film is deposited onto a substrate, both its material composition and the degree of crystallization need to be characterized.

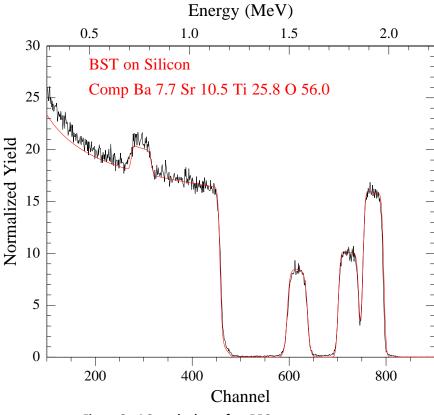

In this work, the atomic ratio of Ba:Sr:Ti:O is analyzed by a General IONIX 1.7 MU Tandetron Rutherford Backscattering Spectroscopy (RBS) system, whose primary application is to obtain a quantitative composition of a material and a depth profiling of individual elements. This is accomplished by measuring the backscattering of a beam of high energy ion – typically helium ions with energy of a few MeV – impinging on a thin film sample. The detection limits are 1-10 atomic percent for low atomic number elements and 0-100 parts per million (ppm) for high atomic number elements, which indicates a better sensitivity for heavier elements.

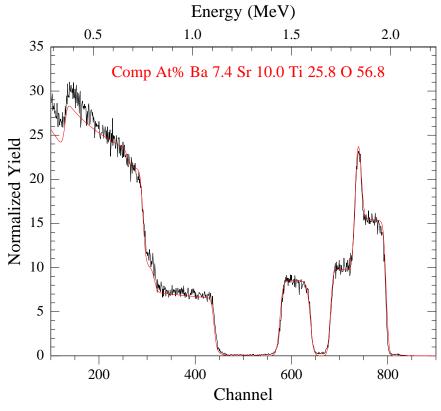

An example of the measured data of a BST thin film using RBS is shown in Figure 2 - 4. The line in black is the experimental spectrum or the raw data, and the line in red is the fit for elemental profiles generated by computer simulation. As we can see that the curve exhibits a staircase structure, which is typical for RBS measurement. Each step is associated with one of the elements in the thin film or the substrate. The X-axis of the plot is associated with the energy of the backscattered particles. The front edge position of each step defines the type of

an element, and the width of the step indicates a constant concentration of that element, which can be further used to calculate the thickness of the thin film consisting of this element. However, the substrate is an exception for obtaining thickness data, because the substrate is usually much thicker than the detection limit of the RBS system. The Y-axis of the plot is the yield or counts of the detected backscattered particles per unit energy, which is proportional to the square of the atomic number. Therefore, equal concentrations of light and heavy elements will produce different yields in the RBS spectrum. In Figure 2 - 4, the signal from the silicon substrate (located near channel 450) overlaps with that from the oxygen atoms (located near channel 300). Other signals located near channel 650, channel 750 and channel 800 are from the titanium, strontium and barium atoms respectively.

Figure 2 - 4 Sample data of an RBS measurement

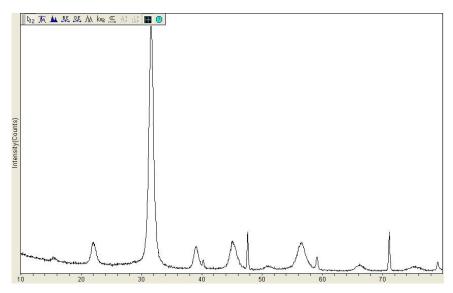

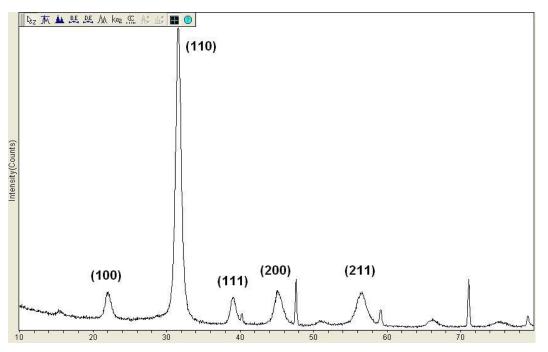

BST crystallization is examined by a Rigaku D/MAX X-Ray Diffraction (XRD) system in this study, which can determine the crystal structure and lattice parameters of a crystalline material. This is achieved by measuring the intensity of X-rays beams diffracted by the thin film under investigation. According to Bragg's Law, diffraction occurs only when the X-ray beam is incident at a certain angle that causes constructive interference. Therefore by plotting the intensity of the diffracted X-ray beams versus the incident angle, crystal orientation can be identified. Furthermore, by comparing the measured data with that in a database, an unknown crystalline phase and orientation of a sample can be labeled. An example of an XRD measurement is shown in Figure 2 - 5. The X-axis is associated with the angle of the incident X- ray, 2θ to be exact. The Y-axis is the intensity of the X-ray detected. The strongest peak near 2θ = 31 corresponds to a crystal orientation of <110> for BST thin film. The rest of the peaks associated with other crystal orientations are considerably smaller compared to the <110> peak, which indicates that this thin film is primarily consisting of crystal orientation <110>.

Figure 2 - 5 Sample data of an XRD measurement

#### 2.4 BST Transfer Technique