University of Central Florida

STARS

Electronic Theses and Dissertations, 2004-2019

2015

# The Design, Implementation, and Refinement of Wait-Free Algorithms and Containers

Steven Feldman University of Central Florida

Part of the Computer Sciences Commons, and the Engineering Commons Find similar works at: https://stars.library.ucf.edu/etd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

## **STARS Citation**

Feldman, Steven, "The Design, Implementation, and Refinement of Wait-Free Algorithms and Containers" (2015). *Electronic Theses and Dissertations, 2004-2019.* 1368. https://stars.library.ucf.edu/etd/1368

# THE DESIGN, IMPLEMENTATION, AND REFINEMENT OF WAIT-FREE ALGORITHMS AND CONTAINERS

by

STEVEN DOUGLAS FELDMAN B.S. University of Central Florida, 2012 M.S. University of Central Florida, 2013

A dissertation submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Fall Term 2015

Major Professor: Damian Dechev

© 2015 Steven Feldman

# ABSTRACT

My research has been on the development of concurrent algorithms for shared memory systems that provide guarantees of progress. Research into such algorithms is important to developers implementing applications on mission critical and time sensitive systems. These guarantees of progress provide safety properties and freedom from many hazards, such as dead-lock, live-lock, and thread starvation. In addition to the safety concerns, the fine-grained synchronization used in implementing these algorithms promises to provide scalable performance in massively parallel systems.

My research has resulted in the development of wait-free versions of the stack, hash map, ring buffer, vector, and a multi-word compare-and-swap algorithms. Through this experience, I have learned and developed new techniques and methodologies for implementing non-blocking and wait-free algorithms. I have worked with and refined existing techniques to improve their practicality and applicability. In the creation of the aforementioned algorithms, I have developed an association model for use with descriptor-based operations. This model, originally developed for the multi-word compare-and-swap algorithm, has been applied to the design of the vector and ring buffer algorithms.

To unify these algorithms and techniques, I have released *Tervel*, a wait-free library of common algorithms and containers. This library includes a framework that simplifies and improves the design of non-blocking algorithms. I have reimplemented several algorithms using this framework and the resulting implementation exhibits less code duplication and fewer perceivable states. When reimplementing algorithms, I have adapted their *Application Programming Interface* (API) specification to remove ambiguity and non-deterministic behavior found when using a sequential API in a concurrent environment.

To improve the performance of my algorithm implementations, I extended OVIS's Lightweight Distributed Metric Service (LDMS)'s data collection and transport system to support performance monitoring using perf\_event and PAPI libraries. These libraries have provided me with deeper insights into the behavior of my algorithms, and I was able to use these insights to improve the design and performance of my algorithms.

To my wife, family, and friends, none of whom are likely to read this.

# ACKNOWLEDGMENTS

I would like to begin by thanking all of my friends and family, without whom I would not have been able to make it this far. I would also like to thank the University of Central Florida for seven and a half years of education. As an undergraduate, I became involved in undergraduate research sponsored by the EXCEL and YES programs. My time in these programs provided the foundation upon which my graduate career was built.

To my advisor Damian, you inspired me to get involved in research as an undergrad. As a result of that, I have gained a considerable amount of experience and knowledge, I have contributed to the scientific community, I have worked at the National labs, and I have earned a Ph.D. For all that and more, I am very grateful.

To my friends and colleagues who have spent time proof reading many of my publications, including this very dissertation, your service is now over. I would like to specifically recognize, in alphabetical order: Matti Perez-Cubas, Damian Dechev, Joshua Katz, Pierre LaBorde, Carlos Valera-Leon, and Marianne Naniong. They have each spent numerous hours helping me with my grammar issues, improving my sentence structure, and overall being great friends. To each of you, you have my eternal gratitude and appreciation.

To my mother who has always been there for me when I needed her, who has always provided me with encouragement and support when I needed it, I love you and I could not have ask for a better mother.

Finally to my very supportive wife, whose patience knows no bounds, we are finally able to start the next big adventure of our lives.

# TABLE OF CONTENTS

| LIST C | DF FIGURES                              | i        |

|--------|-----------------------------------------|----------|

| LIST C | OF TABLES                               | 1        |

| CHAP   | TER 1: INTRODUCTION                     |          |

| 1.1    | Common Parallelization Methodologies    | <u>,</u> |

| 1.2    | Correctness and Progress                | ;        |

| 1.3    | The Problem                             | ł        |

| CHAP   | TER 2: ORGANIZATION OF DISSERTATION     | }        |

| CHAP   | TER 3: BACKGROUND                       | )        |

| 3.1    | Overview                                | )        |

| 3.2    | Other Concurrent Architectures          | )        |

| 3.3    | Correctness Conditions                  |          |

| 3.4    | Progress Conditions                     | )        |

| 3.5    | Concurrent Hazards                      | ł        |

| 3.6    | Non-Blocking Synchronization Techniques | 5        |

| CHAP | TER 4: | RESEARCH DESIGN AND METHODOLGY           |

|------|--------|------------------------------------------|

| 4.1  | Desigr | n: Wait-Free Hash Map                    |

|      | 4.1.1  | Related Work                             |

|      | 4.1.2  | Implementation Overview                  |

|      | 4.1.3  | Traversal                                |

|      | 4.1.4  | Find                                     |

|      | 4.1.5  | Insertion                                |

|      | 4.1.6  | Removal                                  |

|      | 4.1.7  | Wait-Freedom                             |

|      | 4.1.8  | Performance Evaluation                   |

|      | 4.1.9  | Tervel Implementation                    |

| 4.2  | Desigr | n: Wait-Free Multi-Word Compare-and-Swap |

|      | 4.2.1  | Related Work                             |

|      | 4.2.2  | Implementation Overview                  |

|      | 4.2.3  | Association Model                        |

|      | 4.2.4  | Performing an MCAS                       |

|      | 4.2.5  | Performance Evaluation                   |

|     | 4.2.6  | Tervel Implementation     | 35 |

|-----|--------|---------------------------|----|

| 4.3 | Design | a: Wait-Free Ring Buffer  | 36 |

|     | 4.3.1  | Related Work              | 36 |

|     | 4.3.2  | Implementation Overview   | 37 |

|     | 4.3.3  | Implementation of Enqueue | 38 |

|     | 4.3.4  | Implementation of Dequeue | 40 |

|     | 4.3.5  | Performance Evaluation    | 42 |

|     | 4.3.6  | Tervel Implementation     | 44 |

| 4.4 | Design | a: Wait-Free Vector       | 44 |

|     | 4.4.1  | Related Work              | 46 |

|     | 4.4.2  | Implementation Overview   | 47 |

|     | 4.4.3  | Tail Operations           | 47 |

|     | 4.4.4  | Optimized Tail Operations | 50 |

|     | 4.4.5  | Random Access Operations  | 51 |

|     | 4.4.6  | Multi Position Operations | 52 |

|     | 4.4.7  | Performance Evaluation    | 53 |

|     | 4.4.8  | Tervel Implementation     | 58 |

| 4.5   | Applic | ation: Dedup                    | 58 |

|-------|--------|---------------------------------|----|

|       | 4.5.1  | Overview of Dedup               | 59 |

|       | 4.5.2  | Contributions                   | 59 |

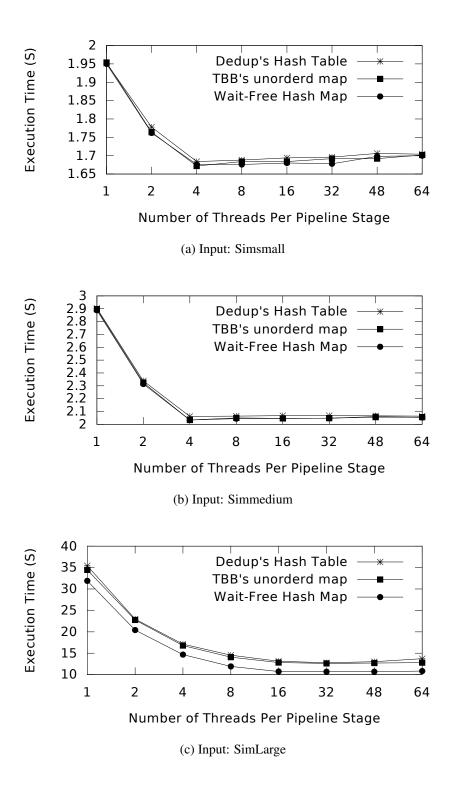

|       | 4.5.3  | Performance Evaluation          | 60 |

|       | 4.5.4  | Summary of Dedup                | 60 |

| CHAP' | TER 5: | RESULTS                         | 63 |

| 5.1   | Tervel | Overview                        | 63 |

| 5.2   | Tervel | Related Work                    | 64 |

| 5.3   | Tervel | Framework                       | 65 |

|       | 5.3.1  | Inter-Thread Helping Techniques | 65 |

|       | 5.3.2  | Recursive Helping               | 67 |

|       | 5.3.3  | Progress Assurance Scheme       | 68 |

|       | 5.3.4  | Tervel Operation Records        | 69 |

|       | 5.3.5  | Memory Protection               | 70 |

|       | 5.3.6  | Memory Reclamation              | 71 |

| 5.4   | Wait-F | Tree Algorithms and Containers  | 72 |

|       | 5.4.1  | Wait-Free Stack                 | 73 |

|        | 5.4.2   | Multi-Word Compare-And-Swap              | 79 |

|--------|---------|------------------------------------------|----|

|        | 5.4.3   | Wait-Free Hash Map                       | 82 |

| 5.5    | Tervel  | Summary                                  | 86 |

| CHAP   | ΓER 6:  | PERFORMANCE METRICS                      | 88 |

| 6.1    | Tervel  | Software Metrics                         | 89 |

| 6.2    | OVIS'   | s Lightweight Distributed Metric Service | 90 |

|        | 6.2.1   | Sampler: perf                            | 91 |

|        | 6.2.2   | Sampler: PAPI                            | 92 |

| 6.3    | Insight | s Gained                                 | 94 |

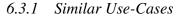

|        | 6.3.1   | Similar Use-Cases                        | 94 |

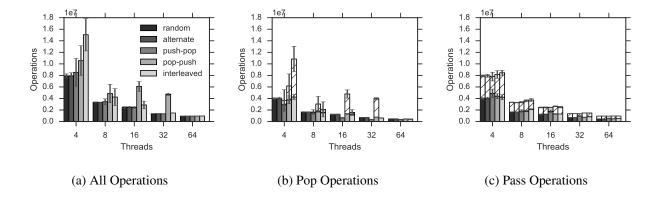

|        | 6.3.2   | Read and Write Dominated Use-Cases       | 96 |

|        | 6.3.3   | Tervel Metrics                           | 00 |

| CHAP   | ΓER 7:  | SUMMARY                                  | 03 |

| 7.1    | Future  | Work                                     | 04 |

| 7.2    | Conclu  | Iding Remarks                            | 05 |

| LIST C | F REFI  | ERENCES                                  | 06 |

# **LIST OF FIGURES**

| Figure 1.1:  | Increment Function                         | 5  |

|--------------|--------------------------------------------|----|

| Figure 4.1:  | Hash map traversal procedure               | 20 |

| Figure 4.2:  | Hash map find operation                    | 20 |

| Figure 4.3:  | Hash map insertion operation               | 22 |

| Figure 4.4:  | Hash map expand function                   | 22 |

| Figure 4.5:  | Hash map remove operation                  | 23 |

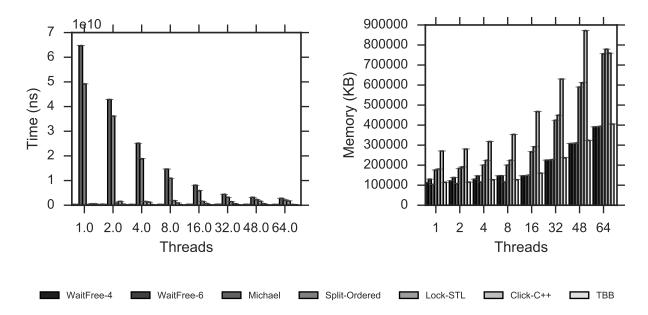

| Figure 4.6:  | 10% Get, 88% Insert, 0% Update, 2% Remove  | 26 |

| Figure 4.7:  | 34% Get, 33% Insert, 0% Update, 33% Remove | 27 |

| Figure 4.8:  | 88% Get, 10% Insert, 0% Update, 2% Remove  | 27 |

| Figure 4.9:  | Visualization of the MCAS operation        | 32 |

| Figure 4.10: | Multi-word Test Results (log scale)        | 34 |

| Figure 4.11: | Sorted Doubly-Linked List                  | 35 |

| Figure 4.12: | Ring buffer enqueue procedure              | 39 |

| Figure 4.13: | Ring buffer dequeue procedure              | 41 |

| Figure 4.14: | Performance comparison                     | 43 |

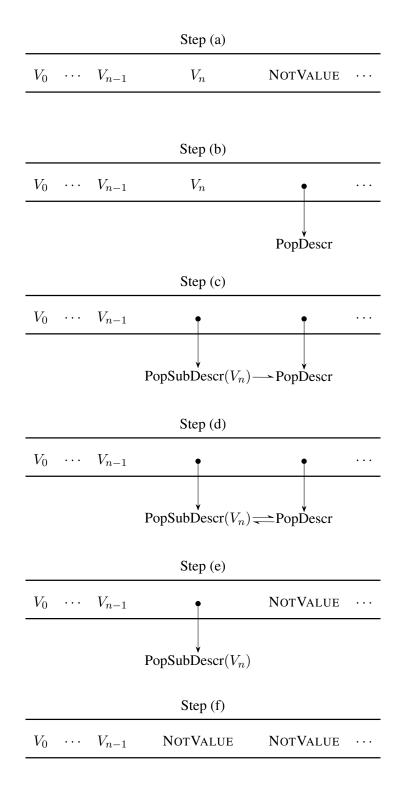

| Figure 4.15: | $pushBack(V_n)$                                                           | 48 |

|--------------|---------------------------------------------------------------------------|----|

| Figure 4.16: | popBack                                                                   | 49 |

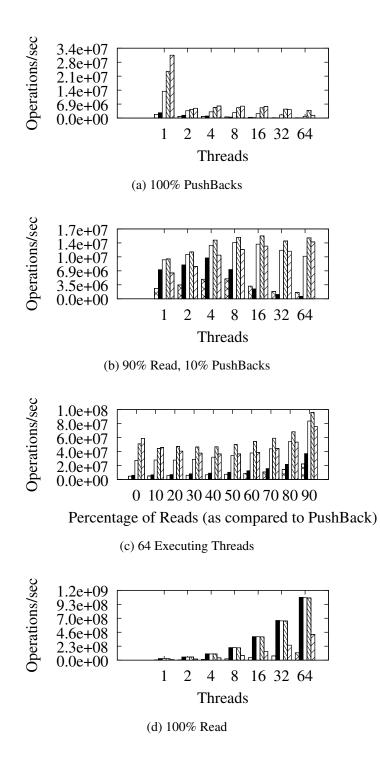

| Figure 4.17: | Random Access Reads and PushBack Operations                               | 54 |

| Figure 4.18: | Random Access Reads and Tail Operations                                   | 56 |

| Figure 4.19: | 50% insertAt, 50% eraseAt                                                 | 57 |

| Figure 4.20: | Performance of <i>Dedup</i> when using different hash map implementations | 61 |

| Figure 4.21: | Performance of <i>Dedup</i> when using different queue implementations    | 62 |

| Figure 5.1:  | Wait-Free Stack Class                                                     | 73 |

| Figure 5.2:  | Stack Node Object Class                                                   | 73 |

| Figure 5.3:  | Wait-Free Stack Pop Operation                                             | 74 |

| Figure 5.4:  | Wait-Free Stack Push Operation                                            | 75 |

| Figure 5.5:  | Stack Accessor Class                                                      | 76 |

| Figure 5.6:  | Stack Operation Record Class                                              | 76 |

| Figure 5.7:  | Stack Helper Class                                                        | 77 |

| Figure 5.8:  | Stack PopBack Operation Help Complete Function                            | 78 |

| Figure 5.9:  | MCAS operation record                                                     | 79 |

| Figure 5.10: | MCAS helper descriptor object                                             | 80 |

| Figure 5.11: | Hash map access operation        | 3 |

|--------------|----------------------------------|---|

| Figure 5.12: | Hash map remove operation        | 4 |

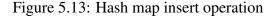

| Figure 5.13: | Hash map insert operation        | 4 |

| Figure 5.14: | Hash map insert operation record | 5 |

| Figure 5.15: | HashMapHelper descriptor object  | 6 |

| Figure 6.1:  | How to use perf_event sampler    | 2 |

| Figure 6.2:  | How to use PAPI sampler          | 3 |

| Figure 6.3:  | Similar Use Cases of a Stack     | 4 |

| Figure 6.4:  | Vector Metrics                   | 7 |

| Figure 6.5:  | Tervel Metrics                   | 8 |

# LIST OF TABLES

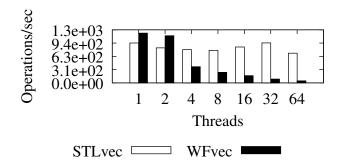

| Table 4.1: | Thread group comparison to STLvec                  | 58  |

|------------|----------------------------------------------------|-----|

| Table 5.1: | Library Features by Degree (none, low, some, high) | 65  |

| Table 6.1: | Comparison of PushBack Threads                     | 100 |

# **CHAPTER 1: INTRODUCTION**

Over the past decade, the number of systems featuring multi-core processors have exploded. Almost every new laptop, desktop, and even cellphone features a multi-core processor. Unfortunately, more often than not, the software and applications used on these devices are not designed to take advantage of this processor advancement. For decades, the majority of software architects and application developers have developed software that is executed sequentially on a single core processor. In this sequential programming paradigm, instructions are executed one after another. Certain instructions, such as loading from a disk drive, take significantly longer to execute than others. These instructions often become a performance bottleneck.

Modern processor designs incorporate features that can overcome the bottleneck caused by these long running instructions. Since 1985, processors have used pipelining to overlap the execution of instructions and improve performance [Her08]. Various techniques, such as dynamic scheduling, branch prediction, re-order buffers, and more, have been used to further reduce the effect on performance that an expensive operation may have. Multi-core technology promises to further increase the performance by enabling multiple processes to execute their instructions concurrently. Unlike previous hardware advancements, which provide performance improvement without requiring changes to application design, multi-core technology requires an application to express how it should be parallelized. In addition to the normal design considerations of sequential applications, developers of concurrent applications must also consider how to express concurrency. For example, which data is shared between units of execution (threads), how this data is synchronized between threads, and how to handle interdependencies between threads.

# 1.1 Common Parallelization Methodologies

Common ways to parallelize an application include data parallelization, task parallelization, and pipe-line processing.

Data parallelization consists of dividing up the input data between the threads and having each thread process its subset of the data independently of the other threads. This design requires the threads to synchronize and/or combine their results once they have finished. Depending on the nature of the data, some threads may take significantly longer to complete than other threads. An example of this can be seen in a naive implementation of an algorithm that identifies all prime numbers in a range. If this range is divided into subranges and each subrange is assigned to a thread, then the threads with smaller integers in their ranges will complete much faster than threads with larger integers. This is because the time taken to determine the primality of an integer increases proportionally with its value. Depending on the application and properties of the data, heuristics could be used to reduce the differences in execution time between threads. For example, instead of assigning subranges to each thread, the designer could use an offset value to divide the work amongst the threads.

Task parallelization is an alternative to data parallelization. In an ideal implementation of the scheme, an application is divided into many independent tasks, and each task is ran in isolation from one another. Most applications are unable to achieve this level of task independence and must employ synchronization methods to ensure that threads with dependencies between them behave correctly. An example of task parallelization can be found in cloud host servers, which facilitate connections from many users to clients' application. A user connected to one application can be conceptualized as a task running on a cloud host server. This task would run independently from users connected to other applications. However, users connected to the same application may have dependencies between them and require synchronization. An example of this is shared document

editing, in which users editing the same document would have dependencies and users editing different documents would not.

Pipe-line processing is a scheme inspired by the hardware pipeline model. In this scheme, data is passed from one thread to another. Each thread receives the data, performs an operation, and then passes the data onto the next thread. Unlike the hardware model, which is regulated by clock cycles, it is possible for a thread to receive a new task before completing its current task. Buffers and/or additional threads can be added to address this problem and prevent bottlenecks. This scheme is generally used in the processing of stream data, which may arrive at irregular rates.

#### 1.2 Correctness and Progress

Depending on how an application is parallelized, different synchronization methods are used to enable threads to communicate between each other. How these synchronization methods are implemented has a significant effect on the safety properties.

The safety properties of concurrent algorithms deal with both correctness and progress conditions. Correctness ensures that an algorithm behaves as described by its *Application Programming Interface* (API) in all scenarios of execution. APIs designed for sequential applications are often ambiguous in a concurrent environment, and they must be modified to remove these ambiguities. For example, sequential queues exhibit undefined behavior if a thread attempts to remove an element from an empty queue. To prevent a thread from doing so, the thread often checks the state of the queue before attempting an operation. This does not work in a concurrent environment because the state of the queue can change in between the checking of the state and the operation on the queue.

Behavior of an algorithm is also affected by the consistency model used to describe how operations

are ordered in respect to one another. For example, consider a first-in-first-out queue using a strict consistency model. If a thread pushes the value A then the value B, it should not be possible for a thread to pop B then pop A. This would break the first-in-first-out property of the queue. The consistency model may be relaxed to allow values to be reordered by a certain amount [AKY10]

In addition to correctness, meeting specified guarantees of progress is another important design constraint. The progress guarantee describes how an algorithm behaves when threads compete for resources. Concurrent algorithms can be classified by level of progress they guarantee. Some applications provide no guarantee of progress, while others guarantee that at least one thread executing in an application is always making progress. The most strict and strongest guarantee is that all threads in an application are always making progress (wait-freedom).

A thread's progress can be affected in a number of ways, and the two most common are mutually exclusive locks and loop structures. A lock may force a thread to wait an indeterminable amount of time before being able to acquire that lock. If multiple locks are used, a dead-lock scenario could occur, in which two or more threads wait on one another to release a lock. Loop structures can be used to enable a thread to re-attempt an operation in the event the operation fails. When multiple threads are attempting to modify shared resources, the actions of one thread may cause a thread's operation to fail. In the event of failure, the thread will often reattempt its operation until it is successful. It can be very challenging, and sometimes impossible, to find an upper limit on the number of times a thread can be forced to retry its operation.

#### 1.3 The Problem

Application developers designing concurrent applications depend on the availability of practical and efficient synchronization methodologies that meet their functional requirements. My research

focuses on the design, implementation, practicality, correctness, and tuning of synchronization methods that provide high guarantees of progress. Through my research, I have developed many concurrent algorithms and containers that provide wait-free progress, which is the strong guarantees of progress. The design and implementation of these algorithms have led to new methodologies and techniques [FLD11a, FLD15a, FLD13b, FBL13, FLD11b, FKD12, CCF13]. These methodologies and techniques have been used in the development of other and more complex algorithms [BFD15, FVD15].

The difficulties of implementing wait-free algorithms stem from the requirement that each executing thread must always be making meaningful progress towards completing its own operation. This must hold true even in the event of a thread being continuously unscheduled at the most inopportune times. Consider the simple function increment shown in Figure 1.1. This function loads the value of an atomic counter and then attempts to replace that value with one value higher. 1: x = counter.load();

2: while True do;

3: **if** counter.cas(x, x+1) **then**

4: break;

5: return x

#### Figure 1.1: Increment Function

The is replacement is done using an *atomic compare-and-swap* or cas operation. This operation replaces the current value of a variable with a new value only if it matches an expected value. If the value was replaced, the operation returns TRUE; otherwise, the value of the expected value variable is set equal to the current value and the operation returns FALSE. The hardware guarantees that the value of variable does not change in between the loading of its current value and the storing of a

new value.

If other threads are incrementing the value with such frequency that the cas at line 2 always returns FALSE, then the thread will never make meaningful progress. In some use cases, heuristics can be applied to allow the function to return in the event of failure, but for cases in which they can not be applied, inter-thread helping techniques must developed. These techniques enable threads to help other threads complete their operations. The challenge in designing these techniques is to ensure that the effects of the operation occur exactly once.

There have been numerous papers that present non-blocking algorithms and containers [TBK12, MS96,Mic03,ST08,HSY10,SS03,Cli,Mic02,FH07,DPS06]. These non-blocking algorithms provide concurrent implementations of sequential algorithms with varying guarantees of progress. The design of these structures is motivated by demand of real time and embedded systems that require fault tolerant applications. Additionally, the number of cores in the processing nodes of high performance computing systems are increasing. This has led to a demand for non-blocking algorithms that exploit fine grained synchronization methodologies to achieve strong scaling properties.

Strong scaling [SDM11] is the scenario in which the total problem size stays fixed while the number of processing elements is increased. The challenge is how to synchronize the work of the processing elements in a correct and efficient manner without "wasting" too many cycles on parallelism overhead. In weak scaling, the problem size assigned to each processing element remains constant while the total problem size may increase. In this case, the main challenge is how to add new processing elements to the existing system.

Wait-Free algorithms are an important type of non-blocking algorithms that provide the strongest guarantee of progress. They provide the guarantee of system wide progress, ensuring that each process or thread is making progress in its own operation. A wait-free algorithm is immune to

dead-lock, live-lock, thread starvation, and priority inversion. These properties are very important in many applications, especially in embedded systems.

An example of this importance occurred during July of 1997 when the Mars Pathfinder mission experienced a series of anomalous system resets that resulted in loss of scientific data [Low02]. It was determined that these resets were caused by a flaw in the implementation that enabled a low-priority process to block a high-priority process (priority inversion). It was also discovered that the black box testing used at the time *would not* have been able to detect this issue. This is because the flaw only reveals itself when certain events occur in a specific frequency and it was not possible to test all interleaving of events.

# **CHAPTER 2: ORGANIZATION OF DISSERTATION**

This chapter provides an overview of the organization of this dissertation.

Chapter 3 presents relevant background information on the fundamental concepts and models used in concurrent programming.

Chapter 5 presents Tervel, which is the cumulation of my research work. Tervel is both a framework for implementing wait-free algorithms and a collection of algorithms implemented using this framework. This chapter discusses the benefits, features, and philosophy of the Tervel framework, and how it has affected the design of the algorithms that have been re-implemented in this framework.

Before developing Tervel, I led the development of several wait-free algorithms and containers. I present these algorithms in Chapter 4, before Tervel, to showcase the techniques and methodologies that were created or explored in the original design of these algorithms. I also discuss how these algorithms have influenced and affected the design of Tervel.

Chapter 6 discusses how I applied and extended performance monitoring tools to identify and resolve synchronization methodologies, implementation error, and other design flaws that negatively impact the performance and/or behavior of the non-blocking algorithms implemented within Tervel.

I conclude this dissertation in Chapter 7 by summarizing the work that I have completed and presenting my plans for the future.

# **CHAPTER 3: BACKGROUND**

This chapter introduces the fundamental concepts and models used in concurrent programming. It begins by presenting a concise overview of the various concepts that are presented and defined in this section. Then the following sections expand on these overviews, providing more technical details.

## 3.1 Overview

There are several known programming models used to implement concurrent applications. An application is said to be concurrent if two or more processes work together to perform a task. These processes can be executing on different machines, processors, cores, or something else entirely. The type of concurrency a program exploits is based on the available hardware. This work focuses on programming models designed for *shared-memory multi-processor/multi-core* (*SMM*) architectures. Section 3.2 provides an overview of notable hardware architectures and how they differ from shared SMM architectures.

In shared-memory multi-procssor(*SMM*) architectures, the processors and memory models are connected by an interconnection network. This allows processes executing on different processors to read and write to the same memory. Each processor typically maintains a local memory cache that must synchronize with the shared memory cache. The *memory consistency* problem is determining when to perform the synchronization and how to reconcile concurrent reads and write. Section 3.3 provides a formal definition of this problem and describes and compares popular consistency models.

In addition to the hardware synchronization challenges, there are also software synchronization

challenges. To achieve performance improvements and better hardware utilization, developers may use threads to parallelize part or all of an application. A thread is the smallest sequence of programmed instructions that can be managed independently by a scheduler. A developer must ensure that parallelized version of the application maintains the requirements of the sequential application. Depending on how threads access and modify shared data, this task could be far from trivial. Section 3.6 provides a detailed overview of established thread-level synchronization techniques and a comparison between them.

Using these thread-level synchronization techniques, it is possible to develop a wide variety of algorithms and containers. Depending on how these techniques are used, these implementations may be susceptible to a variety of concurrency dangers. These dangers include race conditions, deadlock, live-lock, priority version, and thread starvation. Section 3.5 provides the formal definitions of these dangers and examples of how they can occur.

Non-Blocking algorithms are a class of algorithms designed without mutual exclusive critical sections and instead use atomic hardware primitives. There has been extensive research into the design of non-blocking algorithms. These algorithms are classified by the guarantee of progress that they provide. Section 3.4 provides a formal description of these progress guarantees and the common techniques used to implement them.

## 3.2 Other Concurrent Architectures

Another method by which parallelism can be achieved is by distributing the problem across many machines. In distributed computing, a problem is divided into many tasks, each of which is solved by one or more computers.

In contrast to shared memory systems, which allows processes to communicate through shared

memory, machines in a distributed system must communicate over a network. How this communication is performed often has a high impact on performance. Depending on the relative location of one machine to another, the time it takes for them to communicate varies. Machines co-located on the same network bus will have lower message latencies than those located on different network buses. Additionally, the amount of communication passing through a bus and the number of different paths through the network affect the congestion and performance of the network.

The key difference between designing distributed algorithms and shared memory algorithms is that in distributed algorithms communication is minimized and optimized, while in shared memory algorithms time spent in critical sections is minimized and access is safeguarded.

## 3.3 Correctness Conditions

Reasoning about the correctness of algorithms is a challenging task. It is often done by finding a way to equate the behavior in a concurrent environment to its behavior in a sequential environment. I used the following correctness properties when proving or reasoning about correct behavior of the algorithms that I have developed. These are formally defined and discussed in [Her08].

- Quiescent consistency: an algorithm is quiescently consistent if the effects of method calls appear to happen in a one-at-a-time sequential order and method calls separated by a period of inactivity appear to take effect in their real-time order.

- Sequential consistency: an algorithm is sequentially consistent if the effects of method calls appear to happen in a one-at-a-time sequential order and method calls appear to take effect in program order.

- Linearizability: an algorithm is linearizable if each method call appears to take effect instantaneousness some point between its invocation and response.

It is important to note that sequentially consistent algorithms are not compositional with one another, while quiescently consistent and linearizable algorithms are. Linearizability is the strongest of these three properties, and as a result it was predominately used to show the correctness of the algorithms I implemented. Showing an algorithm to be linearizable requires identifying linearization points. The linearization point is typically a single step in which the effects of a method call become visible to other threads.

Linearizability is a powerful property that allows a series of concurrent operations to be ordered by their linearization points. Given an initial state, a final state, and a set of concurrent operations, a valid sequential history can be constructed using linearization points.

# 3.4 Progress Conditions

Progress conditions are another important property of concurrent algorithms and containers. They are used to describe how concurrent method calls may affect the ability of a method call to complete. Methods can be classified either as blocking or non-blocking.

Blocking algorithms use mutual exclusion to safe guard access to critical sections. This is typically accomplished by using a lock or semaphore. The use of mutual exclusion is very common as it is easy to relate the concurrent behavior to the sequential behavior. Unfortunately, these designs have inherent dangers that are often hard to detect. Section 3.5 discusses how using mutual exclusion can introduce hazards such as dead-lock, live-lock, priority inversion, and thread starvation.

Non-blocking algorithm methods avoid the use of mutual exclusion and instead leverage hardware synchronization primitives to exploit fine grained synchronization. These primitives often operate on a single register at a time and handle coherency between the executing processes.

The most common synchronization are primitives:

- compare-and-swap: or cas is an operation that atomically compares the value at an address with the address's current value and replaces the current value with a new value if the current value matches an expected value.

- fetch-and-add: or faa is an operation that atomically increments the value at an address by a specified amount. It returns the pre-incremented value.

- store: atomically writes a value to the specified address, ensuring concurrent stores do not result in a value that is a mixture of multiple writes.

- load: atomically read a value to the specified address, ensuring that partially written values are not read.

Non-blocking algorithm methods are classified by the level of progress they guarantee. These classifications are as follows:

- Obstruction-Free: A method is obstruction-free if at any point in its execution, it executes in isolation from other methods, then it is able to finish its execution in a finite number of steps.

- Lock-Free: A method is lock-free if it guarantees that infinitely often some method call finishes its execution in a finite number of steps.

- Wait-Free: A method is wait-free if it guarantees that every method call finishes its execution in a finite number of steps.

Each classification is a superset of the previous, wait-free being the strongest and most desirable property.

# 3.5 Concurrent Hazards

In addition to logic and implementation hazards known to sequential programmers, concurrent programmers face even more hazards. Depending on how synchronization is implemented, algorithms may be prone to or contain hard to detect scenarios in which undefined behaviors may occur. These dangers are often undetectable by conventional testing methodology, as they only occur under very specific conditions.

In addition to correctness, there are other hazards that may affect the liveness of algorithms. For example, dead-lock is a situation in which two or more competing actions are each waiting for the other to finish, and thus neither ever does. Similar to a deadlock, live-lock is a situation in which the states of the processes involved constantly change with regard to one another, and thus none progresses. And finally, thread starvation is when a thread is perpetually denied a resource, preventing it from making progress in its own operation.

When designing algorithms for mission critical and embedded systems, it is important to ensure that the algorithms are free from these dangers. Otherwise, significant harm and/or damage may occur as a result of the system or part of the system becoming unresponsive. Wait-Free algorithms are free from all three of the aforementioned dangers, and as such are highly desirable for such systems.

Another danger is the ABA problem, which can be caused by the value of an address changing to a value previously held at that address. This could allow a thread to incorrectly update the value of that address. For example, let a reference to an object, A, be stored at an address and let some thread attempt to replace A with a reference to Z using a compare-and-swap operation (cas). However, before executing the cas operation, some other thread replaces A with a reference to some object B and returns A to the allocator. If A is a reallocated and a reference to A replaces B, the first thread will replace the reference to A without knowing that its state has changed.

Hazard pointer [Mic04] and reference counting [DMM01] are two common memory management techniques used to address this danger.

## 3.6 Non-Blocking Synchronization Techniques

There are many techniques used in the development of non-blocking algorithms. This section discusses two common techniques and the motivation behind them. More advanced techniques and those that I have developed are discussed in later sections.

One common technique is to use a compare-and-swap(cas) operation to conditionally change the value at an address. By examining the returned results, developers can determine if another thread modified the address. If the returned value matches the expected value, then the value was changed by the invoking thread. Otherwise, the value was changed by another thread. By including logic to handle both cases, developers have constructed complex algorithms.

If atomic stores were used instead, a developer would not be able to know what value was overwritten. For example, if incrementing a counter, a thread reads the value 0, but before the thread stores 1, another thread changes the value to 1. The first thread, not knowing the value to have already been incremented, will overwrite the value.

Another technique is the use of descriptor objects [Bar93]. These objects encapsulate logic concerning a pending operation and enable inter-thread helping. In general, a thread will attempt to place a reference to a descriptor object into a shared variable and then call the descriptor object's helping routine. If a reference to a descriptor object already exists in that variable, the thread will call that object's helping routine and try again. The helping routine is important to ensure progress of algorithms, as without it threads must wait until the object has been removed. Since it is unknown when the object will be removed, it breaks any progress guarantees. Another challenge faced, which I discuss in Section 5.3.3, is ensuring a thread will be able to place a descriptor object. Other threads may place references with such frequency that one or more other threads starve.

# **CHAPTER 4: RESEARCH DESIGN AND METHODOLGY**

My research has resulted in the development of several wait-free algorithms and containers. In the design and implementation of these algorithms, I have discovered and generalized several techniques and methodologies for implementing concurrent algorithms. The remainder of this section presents the implementation, derived techniques, and evaluation of the wait-free algorithms developed throughout my research.

#### 4.1 Design: Wait-Free Hash Map

A hash map is a container that facilitates the storage, retrieval, and updating of key-value pairs. These operations are usually performed in O(1) complexity. Hash maps are used in a wide variety of applications ranging from databases, image processing, web services, and more.

The hash map that I led the development of was the first to provide a wait-free progress guarantee for all operations on it. Other implementations are prone to live-lock and/or thread starvation in the following scenarios:

- When the capacity of the container has been reached and a resize is triggered.

- When concurrent insertion of key-value pairs may cause a thread to be continually delayed in its own operation.

- When concurrent insertion of key-value pairs may prevent a thread from ascertaining if a key is present in the container.

The main goal of the design was to provide both safety and high performance for multi-processor

applications. In experimental evaluations, this hash map design performs, on average, 7 times faster than a traditional blocking design. Additionally, it outperforms the best available alternative non-blocking designs in a large majority of cases, typically by a factor of 15 or higher.

## 4.1.1 Related Work

At the time of development, there were no existing wait-free hash maps in the literature. As a result, the design was compared to the lock-free implementations presented in [Mic02], [GGH04], and [SS03].

In [Mic02], the authors present a lock-free hash map which uses linked-lists to resolve collisions. It differs from the one I designed in that it does not guarantee constant-time for operations after a resize is performed [SS03] [Mic02].

In [GGH04], Gao et al. present an openly-addressed hash map that is *almost* wait-free; however, it degrades in performance to lock-free during a resize.

In [SS03], Shalev and Shavit present a linked-list structure that uses pointers as shortcuts to logical buckets that allow the structure to function as a hash table. In contrast to my wait-free hash map design, the work by Shalev and Shavit does not present a hash map and it is lock-free.

There was a single claim of a wait-free hash map that appeared as a presentation by Cliff Click [Cli]; the author now claims lock-freedom. Moreover, the work by Click was not published.

A popular concurrent hash map that is part of Intel's Threading Building Blocks (TBB) [Int] library is claimed to be lock-free, but is also unpublished.

#### 4.1.2 Implementation Overview

The key challenge that was faced while developing a wait-free hash map is how to increase the capacity of the hash map while facilitating concurrent operations. If a blocking synchronizations method were used, all threads would be forced to wait until the thread performing the resize has copied the key-value pairs from the old hash map to a larger hash map.

Because of this, the design of this hash map stores key-value pairs across multiple arrays, thereby removing the need for a lengthy copy-over. Each position on an array may hold a reference either to another array or to a key-value pair. The implementation uses a primary array length and secondary array length, in which the primary array length is often much larger than the secondary. Using this structure, key-value pairs are placed based on the binary representation of their keys.

Each key is conceptually divided into subsets, in which the decimal value of each subset indicates the position on an array to place the key-value pair. The number of bits in the first subset corresponds is  $log_2$ (primary array length) and the number of bits in the following subsets is  $log_2$ (secondary array length).

In the following sections, I present a high level description of each hash map operation.

# 4.1.3 Traversal

Algorithm 4.1 describes how the traversal of the hash map is performed. The decimal value of the first subset is used to determine the position on the primary array to examine. If the position holds a reference to an array, the next subset is used to determine the position on that array to examine. Once a non-array value is found, the traversal is complete.

- 1: **procedure** TRAVERSE(node, array, pos, subsets, depth)

- 2: node = array[pos].load();

- 3: while IsArray(node) do

- 4: array = array[pos];

- 5: pos = subsets[depth++];

- 6: node = array[pos].load();

- 7: **if** isMarked(node) **then**

- 8: node = expand(node, array, pos, depth);

Figure 4.1: Hash map traversal procedure

```

1: function FIND(key)

```

- 2: array = primaryArray;

- 3: subsets = getSubsets(key);

- 4: depth = 0;

- 5: pos = subsets[depth];

- 6: fcount = 0;

- 7: while True do

- 8: traverse(node, array, pos, subsets;

- 9: **if** node == null OR node.key != key **then**

- 10: **return** null;

- 11: **else**

- 12: **return** node.value;

Figure 4.2: Hash map find operation

4.1.4 Find

Algorithm 4.2 describes how the find operation is performed. Once the traversal has identified a position holding a non-array value, it acts based on that value.

• If the position holds a reference to a key-value pair whose key matches the passed key, the value member is returned.

• Otherwise null is returned.

## 4.1.5 Insertion

Algorithm 4.3 describes how the insert operation is performed. Once the traversal has identified a position holding a non-array value, it acts based on that value.

- If the position is empty, a cas operation is used to attempt to replace it with a reference to the key-value pair.

- If the position holds a reference to a key-value pair whose key matches the key being inserted, false is returned indicating that the key already exists in the hash map.

- Otherwise, the position holds a reference to a key-value pair whose key does not match the key being inserted. In this case, an expansion (Algorithm 4.4) is performed to resolve the hash collision.

If an expansion is performed or a cas operation fails, the position is re-examined.

# 4.1.6 Removal

Algorithm 4.5 describes how the remove operation is performed. Once the traversal has identified a position holding a non-array value, it acts based on that value.

- If the position holds a reference to a key-value pair whose key matches the passed key, a cas operation is used to attempt to replace it with a null reference. If successful, true is returned, otherwise the position is re-examined.

- Otherwise, false is returned, indicating the key is not present.

```

1: function INSERT(key, value)

array = primaryArray;

2:

subsets = getSubsets(key);

3:

depth = 0;

4:

pos = subsets[depth];

5:

6:

fcount = 0;

while True do

7:

traverse(node, array, pos, subsets);

8:

if node == null then

9:

if array[pos].cas(node, new pair(key,value)) then

10:

return true;

11:

12:

else if node.key == key then

return false;

13:

14:

else

15:

expand(node, array, pos, depth);

if fcount++ == MAX_FAIL then

16:

array[pos].atomicOR(0x1);

17:

expand(node, array, pos, depth);

18:

19:

fcount = 0;

```

Figure 4.3: Hash map insertion operation

- 1: **function** EXPAND(node, array, pos, depth)

- 2: newArray = new SecondaryArray;

- 3: subsets = getSubsets(node.key);

- 4: newArray[subsets[depth]] = unMark(node);

- 5: array[pos].cas(node, newArray);

- 6: **return** array[pos].load();

Figure 4.4: Hash map expand function

```

1: function REMOVE(key)

array = primaryArray;

2:

subsets = getSubsets(key);

3:

depth = 0;

4:

pos = subsets[depth];

5:

fcount = 0;

6:

7:

while True do

8:

traverse(node, array, pos, subsets;

9:

if node == null OR node.key != key then

return false;

10:

else

11:

12:

if array[pos].cas(node, null) then

return true;

13:

if fcount++ == MAX_FAIL then

14:

15:

array[pos].atomicOR(0x1);

expand(node, array, pos, depth);

16:

17:

fcount = 0;

```

Figure 4.5: Hash map remove operation

4.1.7 Wait-Freedom

As described, thread-starvation could occur in the event of keys being repeatedly inserted and removed from the same position. This use case could cause a thread's cas operation to continually fail. To prevent this, an atomic bit marking technique is used to force an expansion to occur at the contended position.

When a fail counter reaches a user defined threshold, the thread uses an atomic bitwise OR operation to place a mark on the least significant bit of the value at the position. Threads that see this bit mark must replace the reference with an array containing an unmarked version of that reference. This is shown on Line 17 Algorithm 4.3 and Line 7 Algorithm 4.1.

Given enough hash collisions and failures, the hash map will expand to a depth equal to the number

of subsets. A property of the structure of the hash map is that no hash collisions can occur at this depth. This is because the entire key has been used in the determining of this position. Because of this property, the hash map's operations use specialized logic when operating at this depth.

If an insert operation's cas failed, it implies another thread inserted that key and that it should return, indicating that the key already exists in the hash map. Likewise, if a remove operation's cas failed, it implies another thread removed that key and that it should return, indicating that the key does not exist in the hash map.

To show wait-freedom, first examine the two looping structures:

- The for loop is bounded by the number of subsets in the key, which is based on the finite size of the key data type.

- The while loop is bounded by the fail count. When it is reached, bit marking ensures that the next iteration loads a reference to an array.

Since the functions contain calls to only wait-free functions and contain only bounded loops, they are also wait-free.

### 4.1.8 Performance Evaluation

To test the performance of this design, a test was constructed to determine the time it took to execute one million operations. The distribution of operations and the number of threads executing these operations were varied. This variation showed how the hash map's performance varies across use cases.

The performance of this hash map and the following hash maps were compared:

- C++11 standard template library hash map protected by an optimized global lock (Lock-STL) [ISO11]

- Split-Ordered Lists (Split-Ordered) [SS03]

- Michael's lock-free hash map (Michael) [Mic02]

- Click's hash map [Cli]

- Intel TBB's implementation (TBB) [Int]

The operation distributions are based on the following use cases:

- The first distribution is based on a reported typical operation mix for hash maps [SS03](88% get, 10% insert, 2% remove).

- The second distribution is an inversion of the first distribution (10% get, 88% insert, 0% update 2% remove).

- The third distribution consists of an even mix of operations (update: 25% get, 25% insert, 25% update 25% remove).

Based on the Figures 4.6, 4.7, and 4.8 on average, the wait-free algorithm outperforms the traditional blocking design by a factor of 7 or more. It performs faster than the lock-free algorithms typically by a factor of 15. The lack of scalability of the blocking solution is a result of the fact that the lock is applied to all operations, not only those that conflict. Both lock-free solutions scale well; however, they perform worse when more insert operations are performed, because the insert operations trigger more global resizes. Due to the incremental approach in resizing the hash map, there is performance improvements over the other designs in the tested scenarios except for TBB. The other lock-free designs show an average of a 17.5 times performance decrease when compared to Intel's TBB implementation. In contrast, this approach is competitive with only a 14% loss in performance to provide the stronger progress guarantee of wait-freedom.

Figure 4.6: 10% Get, 88% Insert, 0% Update, 2% Remove

### 4.1.9 Tervel Implementation

This design was re-implemented in the Tervel framework. This reimplementation incorporates a new API and the application of memory reclamation. Section 5.4.3 describes these changes and the motivations behind them.

Figure 4.7: 34% Get, 33% Insert, 0% Update, 33% Remove

Figure 4.8: 88% Get, 10% Insert, 0% Update, 2% Remove

## 4.2 Design: Wait-Free Multi-Word Compare-and-Swap

A multi-word compare-and-swap (MCAS) is an algorithm used to conditionally update one or more memory addresses [HFP02]. This update occurs only if the value at each address matches an expected value. For correctness, this update must provide the appearance of atomicity, such that a thread would be unable to read a newer value and then read an older value. There are several concurrent algorithms and containers that depend on the ability to perform an MCAS operation. How these algorithms use MCAS varies. Common use cases include:

- Updating objects that are larger than a machine word. For example in [PH05], an MCAS is used to allow a non-blocking hash table to support multi-word length key and value data types. Unlike the wait-free hash map [FLD13b], this design focuses on high data locality and lower memory utilization.

- Use in an array based lock-free priority queue [LS12] to percolate higher priority elements to the front of the queue.

- A concurrent binary search tree [FH07] that uses MCAS to maintain the tree's balance. The properties of the MCAS algorithm ensure that concurrent modifications do not introduce incorrect behavior.

- A fall back path for systems that use hardware transaction memory. When operations exceed the supported size of the hardware transaction memory, MCAS can be used instead. This is because MCAS does not have a limit on the number of locations, while most HTM proposals limit the number of locations [SAH06].

## 4.2.1 Related Work

At the time of its development, I was aware of the following other MCAS algorithms that provide similar functionality.

Israeli et al. presents a lock-free and disjoint-access parallel MCAS algorithm [IR94]. This algorithm requires a thread identifier to be stored alongside the value of a memory address, limiting the number of bits available to the value. This thread identifier is used to access a set of global variables that contain information about the operations that are currently executing in the system. Israeli et al.'s design does not support the ability to perform a read through to retrieve the current value for an address. Rather they require the thread to help complete the pending operation before proceeding with its own operation. This algorithm is dependent on the LL/VL/SC primitive<sup>1</sup>, which is not provided by any contemporary system.

Anderson et al. demonstrates a wait-free MCAS algorithm that is disjoint-access parallel and supports read through parallelism [ARJ97]. In contrast to [IR94], their design requires that each memory word that contains a value to be followed by an additional memory word containing auxiliary information. This information may include the identification of a thread performing an operation at the address and the information needed to help complete the operation. Using a non-redundant helping scheme, this design chooses not to perform recursion to help complete a conflicting operation. Instead it causes the conflicting operation to be restarted. Like [IR94], this design requires the availability of the LL/VL/SC primitive. A simplified lock-free version of this algorithm was presented by Moir [Moi97]. Attiya et al. [AH11] have also presented improvements upon this design.

Harris et al. in [FH07] propose a lock-free MCAS algorithm that is disjoint-access parallel, sup-

<sup>&</sup>lt;sup>1</sup>Load-link, Validate, Store Conditional; used to ensure the value at an address has not been unknowingly modified.

ports read through parallelism, and does not depend on LL/VL/SC. Rather this design uses a CAS operation to replace the expected value at an address with a reference to a descriptor object. This design reserves the two lowermost bits of each address to distinguish between values and descriptor objects. To ensure correct behavior of the MCAS algorithm and to prevent the ABA problem, Harris et al. designed a "double compare single swap" algorithm. Compared with [IR94] and [ARJ97], their design shows a significant increase in performance and portability.

Sundell presents a wait-free MCAS algorithm based on a greedy helping scheme [Sun11]. Like Harris et al.'s design, his design is disjoint-access parallel, supports read through parallelism, and does not depend on LL/VL/SC. In the first phase of the greedy helping scheme, a thread attempts to place a reference to its MCAS operation at as many addresses in its operation as it can. In the next phase, if another MCAS operation holds some of those addresses, then one of the operations will steal addresses from the other. Unlike [FH07], Sundell makes no claim that his algorithm is ABA-free, and when examined, his algorithm can exhibit undefined behaviors in certain cases caused by the ABA-problem<sup>2</sup>. In Sundell's algorithm, thread starvation can occur in the case in which the result of a CAS operation consistently causes a thread to reattempt that CAS operation. Because of this, the algorithm is lock-free and not wait-free.

### 4.2.2 Implementation Overview

The MCAS algorithm that I led the design of was the first design to provide wait-free progress guarantees and the ABA-free safety property [FLD15a]. In synthetic tests performed with 64 threads on a 64 core workstation, the design completes on average 67.8% more MCAS operations than other comparable designs. On average, it improves performance by 8.6% over all tested scenarios.

<sup>&</sup>lt;sup>2</sup>See Sec. 3.5 for more details.

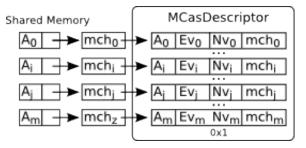

The implementation of the MCAS algorithm is based on using helper descriptor objects, MCasHelper, to hold the logical value of an address constant until the MCAS operation has completed. The MCasHelper object is composed solely of a reference to an MCAS operation record.

An MCAS operation record (MCasDescriptor) contains the following for each address:

- An expected value.

- A new value to replace the expected value.

- An atomic reference to a descriptor object that is initially null.

## 4.2.3 Association Model

The atomic reference is part of an association model that was developed to overcome correctness issues related to concurrent helping and the ABA problem. This association model enables a thread to distinguish between a descriptor object that was placed during the operation from one that was placed after the operation was completed. The latter could occur in the event that a thread is suspended from execution just before placing a descriptor. If it resumes after the operation has been completed and the value at the address matches the expected value, the thread will incorrectly place the descriptor. If not handled properly, this could allow the value of an address to be changed twice by a single operation.

#### 4.2.4 Performing an MCAS

To perform an MCAS, a thread first constructs an MCasDescriptor operation record and then calls its execute function. This function iterates through each address, and if the value currently held at the address matches the expected value, an attempt is made to replace the value with a reference to an MCasHelper descriptor. If the value currently held at the address does not match the expected value, the MCasDescriptor's state is set to a constant indicating failure, and the operation is complete.

Figure 4.9: Visualization of the MCAS operation

If it was unsuccessful with placing an MCasHelper due to concurrent modification, the current value is re-read. If the MCasHelper was successfully placed, the next step would be to attempt to associate the MCasHelper with the MCasDescriptor.

If this association failed, it implies that some other MCasHelper was used to complete the operation. It also implies that the operation has been completed. If the association was successful, the function will move onto the next address.

After replacing each expected value with a MCasHelper object, a second iteration is performed to replace each MCasHelper with its logical value.

Figure 4.9 presents a visual representation on the dependencies between the two types of objects. The left side is shared memory and the right side is the MCasDescriptor. In this figure, the value of each address has already been replaced by an MCasHelper. The association between the objects is represented by the fact that each row's atomic MCasHelper reference refers to a corresponding MCasHelper.

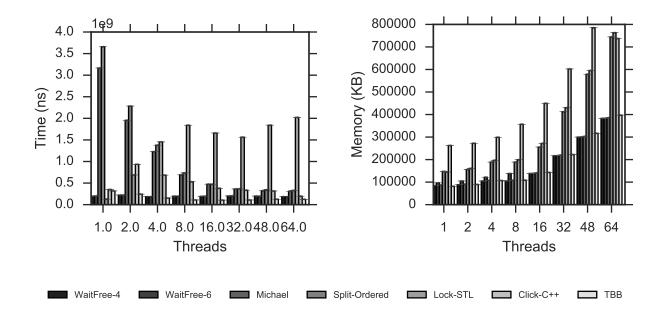

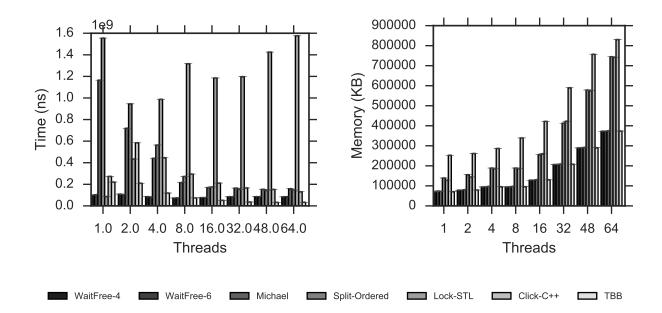

#### 4.2.5 Performance Evaluation

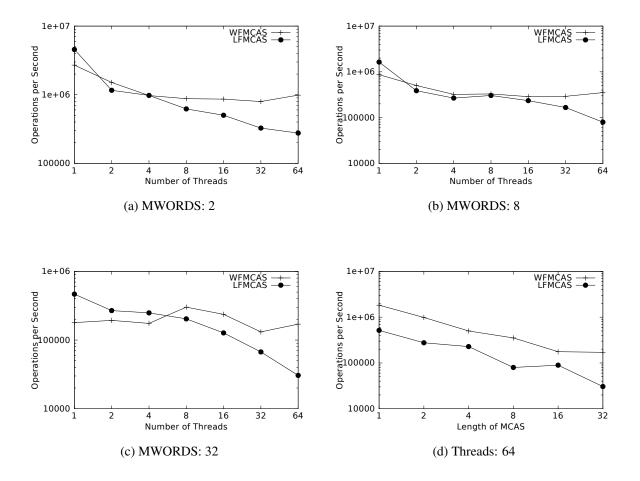

To test the performance of this design, a test was constructed to determine the number of operations that were executed over a period of time. The distribution of operations and the number of threads executing these operations were varied. This variation showed how MCAS's performance varies across use cases.

The performance of this MCAS was compared to the lock-free MCAS (LFMCAS) presented by Harris et al [FH07]. Unfortunately, when tested, Sundell's MCAS [Sun11] exhibited behavior that produced inconsistencies in the testing methodology, which invalidated the test results. All implementations were provided by their respective authors.

In a multi-word object benchmark, each thread repeatedly tries to increment the value of each word in the object by  $16^3$ .

Figure 4.10 presents a set of representative graphs based on this benchmark. Graphs 4.10a, 4.10b, and 4.10c depict the effects of increasing the number of threads updating a shared multi-word object. The WFMCAS performs on average 10% more operations per second when compared to the LFMCAS in this benchmark. When the number of threads are 16, 32 and 64, the WFMCAS performs on average 35.4%, 50.3%, and 77.1%, respectively, more operations per second.

In Graph 4.10d, the number of threads is held constant at 64, and the size of the updated object is varied. In this test, the WFMCAS performs on average 67.8% more operations than the LFMCAS.

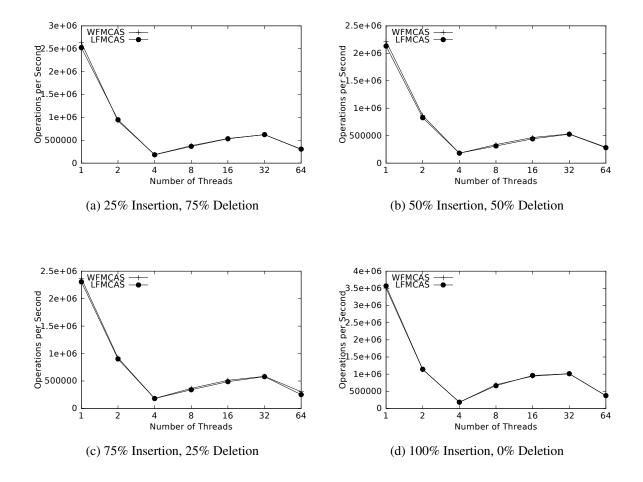

Figure 4.11 presents the performance of each MCAS algorithm when used in the construction of a *sorted doubly-linked list* container. Threads executing this test perform a higher amount of work outside of the MCAS algorithm, thereby exhibiting less thread contention. Threads performing

<sup>&</sup>lt;sup>3</sup>Incrementing by 16 ensures that the two least significant bits are always 0.

this benchmark will repeatedly try to insert and delete elements from the list. The ratio of these operations to one another were varied.

Figure 4.10: Multi-word Test Results (log scale)

In this benchmark, both implementations scaled equally well. Over all tests, the WFMCAS performs on average 2% more operations per second than the LFMCAS. This insignificant difference in performance can be attributed to the necessity of searching the list for the location to perform an operation. This search was found to consume 84% of the execution time. These benchmarks revealed that when implemented in a practical algorithm, this approach achieves wait-freedom without sacrificing performance. A more thorough examination of this performance comparison is presented in [FLD15a]

Figure 4.11: Sorted Doubly-Linked List

### 4.2.6 Tervel Implementation

In [FLD15b], a new implementation of the MCAS algorithm is described that includes memory management, a re-organization of how internal objects are represented in memory, and how the helping routines are defined. This new implementation takes advantage of the latest features of C++11 and a more refined methodology for implementing helping routines. Section 5.4.2 describes these changes and the motivations behind them.

#### 4.3 Design: Wait-Free Ring Buffer

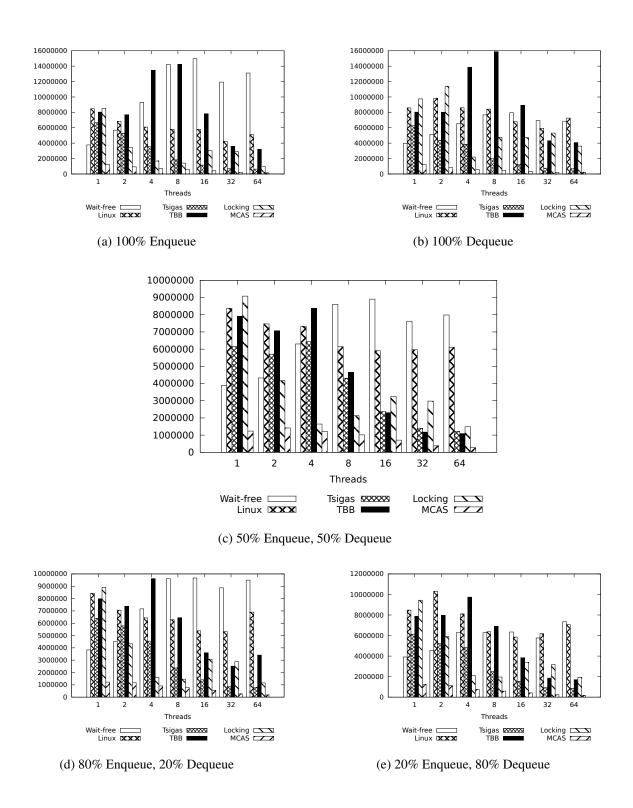

The Ring Buffer is a staple data structure in computer science. It is excellent for high demand applications such as multimedia, network routing, and trading systems. In [BFD15], I oversaw the development of a new wait-free ring buffer design. To improve performance and scalability, this design diffuses thread contention using sequence counters. On average, the design completes 15% more than TBB's concurrent bounded queue [Int], 10% more than the lock-free approach presented by Krizhanovsky [Kri13], and 140% more than the cycle queue by Tsigas [TZ01].

### 4.3.1 Related Work

At the time of the development, I was aware of the following other ring buffers that provide similar functionality:

A lock-free ring buffer by Tsigas et al. [TZ01] that uses a cas operation to apply operations. An enqueue is performed by determining the tail of the buffer and then using a cas operation to enqueue an element. A dequeue is performed by determining the head of the buffer and then using a cas operation to dequeue an element. In the event a thread is unable to successfully apply its operation, starvation could occur. Another issue with this design is that it does not diffuse thread contention. The competitive nature leads to congestion and poor scalability.

Krizhanovsky [Kri13] presents a lock-free and high performance ring buffer. This implementation relies on the atomic fetch-and-add operation to increment head and tail counters. The returned value of this operation determines the index to perform an operation. This diffuses contention and increases scalability, but also increases the complexity of the design. This increase in complexity comes form the additional logic needed to prevent incorrect behavior from occurring when positions are reused. These designs require each thread to maintain a separate tail and head value of the

last completed enqueue or dequeue. The smallest of all threads' *local* head and tail values is used to determine the head and tail value at which all threads have completed their operations. These values prevent an attempt to enqueue or dequeue at a location where a previously invoked thread has yet to complete its operation. A consequence of this design choice is that one thread's inaction could prevent all other threads from making progress. As a result, this design is not thread-death safe.

Intel Thread Building Blocks (TBB) [Int] provides a concurrent bounded queue which utilizes a fine-grained locking scheme. The algorithm uses an array of micro queues to alleviate contention on individual indexes. Upon starting an operation, threads are assigned a ticket value which is used to determine the sequence of operations in each micro queue. Threads will wait until their ticket is valid, which may take a while, in the event other threads are delayed.

In addition to the above, I also implemented a naive implementation of a ring buffer using the waitfree multi-word compare-and-swap described in Section 4.2. In this design, head and tail markers are moved along the buffer. The act of moving a marker requires the completion of six hardware compare-and-swap operations, which results in poor performance.

### 4.3.2 Implementation Overview

The design presented in [BFD15] uses sequence counters to diffuse contention and reduce forced dependencies. Before performing an operation, a thread atomically increments the relevant sequence counter and uses the result (*seqid*) to complete its operation. The monotonic nature of a counter ensures each thread has a unique value.

In general, it is unlikely that the actions of a thread may interfere with another thread. However, certain use cases may significantly increase the probability of interference. Using the sequence

numbers, I helped design logic to handle the case in which threads interfere with one another. Scenarios that could cause this include:

- An enqueue thread operating on an empty position.

- A dequeue thread operating on a non-empty position.

- A position holding a sequence ID that is less or greater than the expected sequence ID.

- A cas operation continually returns failure.

These scenarios are often the result of inopportune context switches and/or thread delay.

### 4.3.3 Implementation of Enqueue

The following describes the procedure a thread uses to perform an enqueue operation. Pseudo code from Figure 4.12 is referenced to clarify the explanation.

The enqueue function returns after a element has been enqueued (Line 24) or if it has been determined that the buffer is full (Line 28).

If the buffer is not full, the tail sequence counter is incremented and the returned result is used to determine the position at which to enqueue (Lines 5, 6). Each position on the buffer holds a *node* type that internally has a sequence ID and is either an *EmptyNode* or *DataNode*.

If the position holds a node type whose sequence number is less than expected, a back-off routine is used to allow delayed threads to complete their operation.

| 1:  | procedure ENQUEUE(val)                                 |

|-----|--------------------------------------------------------|

| 2:  | tryHelpAnother()                                       |

| 3:  | fails = 0                                              |

| 4:  | while isNotFull() do                                   |

| 5:  | <pre>seqid = nextTailSeq()</pre>                       |

| 6:  | pos = getPosition(seqid)                               |

| 7:  | newNode = ElemNode(seqid, val)                         |

| 8:  | while true do                                          |

| 9:  | if fails++ == MAXFAILS then                            |

| 10: | op = EnqueueOp(val)                                    |

| 11: | makeAnnouncement(op)                                   |

| 12: | return op.result()                                     |

| 13: | node = buffer[pos].load()                              |

| 14: | if node.op then                                        |

| 15: | <pre>node.op.associate(node, &amp;(buffer[pos]))</pre> |

| 16: | continue                                               |

| 17: | else if isSkipped(node) then                           |

| 18: | break                                                  |

| 19: | else if node.seqid < seqid then                        |

| 20: | backoff()                                              |

| 21: | if node != buffer[pos].load() then                     |

| 22: | continue                                               |

| 23: | if node.seqid <= seqid and isEmptyNode(node) then      |

| 24: | if buffer[pos].cas(node, newNode) then                 |

| 25: | return true                                            |

| 26: | else if node.seqid > seqid or isElemNode(node) then    |

| 27: | break                                                  |

| 28: | return false                                           |

Figure 4.12: Ring buffer enqueue procedure

If the position holds an *EmptyNode* whose sequence number is less than or equal to the expected sequence number, the *EmptyNode* is replaced with a new node. If the replacement is successful, the function returns. Otherwise, the value at the position is re-examined.

If the position holds a node whose sequence number is greater than expected or is a DataNode type,

then a new sequence number is needed. The dequeue function contains logic to handle skipped sequence numbers. The ability to skip sequence numbers is important to prevent one thread from blocking others.

In the event a thread is unable to complete its operation, an association model and progress assurance scheme [FLD15b] are used to allow any thread to complete another thread's operation. The associate function at Line 15 prevents the effects of the operation from occurring multiple times. Internally, this function removes an incorrectly placed object. Section 5.3.3 describes the association model and progress guarantee in detail.

### 4.3.4 Implementation of Dequeue

The following describes the procedure a thread uses to perform an enqueue operation. Pseudo code from Figure 4.13 is referenced to clarify the explanation.

If the buffer is not empty, the head sequence counter is incremented and the returned result is used to determine the position at which to dequeue (Lines 5, 6).

Like the enqueue operation, if the position holds a node type whose sequence number is less than expected, a back-off routine is used to allow delayed threads to complete their operation.

If the position holds a *DataNode* whose sequence number is equal to the expected value, that node is replaced with an *EmptyNode* containing the next sequence number for that address.

Unlike an enqueue, a dequeue can not remove a *DataNode* whose sequence number is less than expected. If this were allowed, it would break the FIFO property of the ring buffer. To maintain FIFO property and allow a dequeue to skip a sequence ID, I employ a bit marking scheme.

| 1:  | procedure DEQUEUE(&result)                                                          |

|-----|-------------------------------------------------------------------------------------|

| 2:  | tryHelpAnother()                                                                    |

| 3:  | fails = 0                                                                           |

| 4:  | while isNotEmpty() do                                                               |

| 5:  | seqid = nextHeadSeq()                                                               |

| 6:  | pos = getPosition(seqid)                                                            |

| 7:  | newNode = EmptyNode(seqid + getCapacity())                                          |

| 8:  | while true do                                                                       |

| 9:  | node = buffer[pos].load()                                                           |

| 10: | if fails++ == MAXFAILS then                                                         |

| 11: | op = DequeueOp()                                                                    |

| 12: | makeAnnouncement(op)                                                                |

| 13: | return op.result(result)                                                            |

| 14: | else if node.op then                                                                |

| 15: | node.op.associate(node, &(buffer[pos]))                                             |

| 16: | else if isSkipped(node) and isEmptyNode(node) then                                  |

| 17: | if buffer[pos].cas(node, newNode) then                                              |

| 18: | break                                                                               |

| 19: | else if seqid > node.seqid then                                                     |

| 20: | backoff()                                                                           |

| 21: | <b>if</b> node == buffer[pos].load() <b>then</b>                                    |

| 22: | if isEmptyNode(node) and buffer[pos].cas(node, newNode) then                        |

| 23: | break                                                                               |

| 24: | else                                                                                |

| 25: | setSkipped(&buffer[pos])                                                            |

| 26: | else if seqid < node.seqid then                                                     |

| 27: | break                                                                               |

| 28: | else                                                                                |

| 29: | if isElemNode(node) then                                                            |

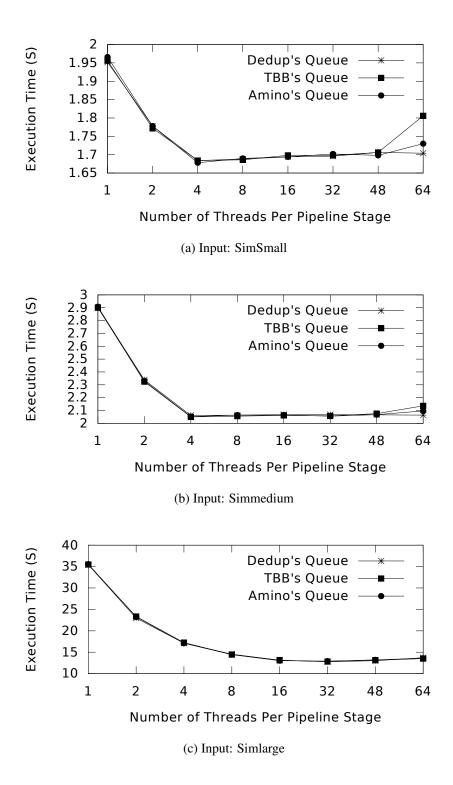

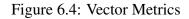

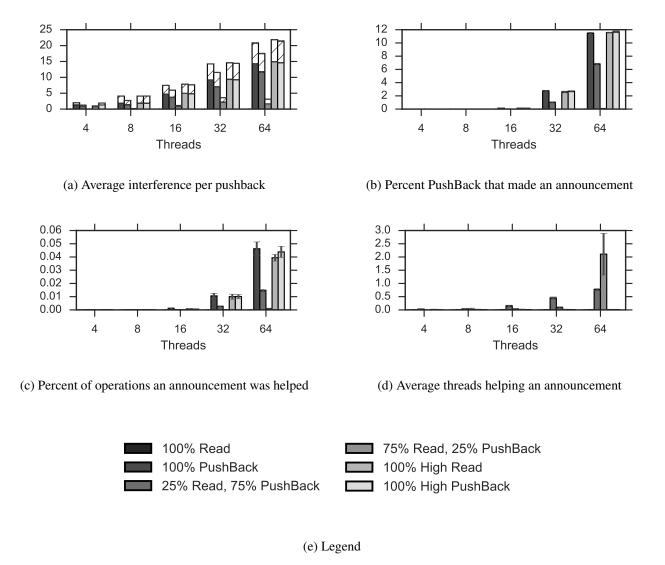

| 30: | if isSkipped(node) then                                                             |