Electronic Theses and Dissertations, 2004-2019

2006

# Chemical And Biological Treatment Of Mature Landfill Leachate

Eyad Batarseh University of Central Florida

Part of the Electrical and Electronics Commons

Find similar works at: https://stars.library.ucf.edu/etd

University of Central Florida Libraries http://library.ucf.edu

This Masters Thesis (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS Citation**

Batarseh, Eyad, "Chemical And Biological Treatment Of Mature Landfill Leachate" (2006). *Electronic Theses and Dissertations, 2004-2019.* 1129.

https://stars.library.ucf.edu/etd/1129

# A NON-ISOLATED HALF-BRIDGE BUCK-BASED CONVERTER FOR VRM APPLICATION AND SMALL SIGNAL MODELING OF A NON-CONVENTIONAL TWO PHASE BUCK

by

MAJD G. BATARSEH B.Sc. University of Jordan, 2004

A thesis submitted in partial fulfillment of the requirements for the degree of Masters of Science in the School of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida

Orlando, Florida

Fall Term 2006

Advisor: Issa Batarseh

## **ABSTRACT**

The challenges imposed on Voltage Regulator Modules (VRM) become difficult to be achieved with the conventional multiphase buck converter commonly used on PC motherboards.

For faster data transfer, a decrease in the output voltage is needed. This decrease causes small duty cycle that is accompanied by critical problems which impairs the efficiency. Therefore, these problems need to be addressed.

Transformer-based non-isolated topologies are not new approaches to extend the duty cycle and avoid the associated drawbacks. High leakage, several added components and complicated driving and control schemes are some of the trade-offs to expand the duty cycle.

The objective of this work is to present a new dc-dc buck-based topology, which extends the duty cycle with minimum drawbacks by adding two transformers that can be integrated to decrease the size and two switches with zero voltage switching (ZVS).

Another issue addressed in this thesis is deriving a small signal model for a twoinput two-phase buck converter as an introduction to a new evolving field of multi-input converters. To all beautiful minds out there...

## ACKNOWLEDGMENTS

"Thanks be to God, who always leads us in triumphal procession..."

My deepest thanks and appreciation go to my advisor Dr. Issa Batarseh for the trust he bestowed in us through his wise supervision. His enlightening discussions and encouraging words boosted my scientific curiosity and enthusiasm even more.

I would also like to sincerely thank Dr. Xiangcheng Wang for his thorough help and constant support and encouragement.

Likewise, I would like to express my appreciation to my committee members Dr. John Shen and Dr. Takis Kasparis. I am also grateful to Mr. Peter Kornetzky for his support and to Dr. Jaber A. Abu Qahouq and Ms. Hua Zhou as well.

Many thanks go to my friends and lab mates: Mr. Hussam Al Atrash for his contagious passion and continuous help and support, Mr. Ehab Al Shobaki for his valuable insight and equally to Mr. Osama Abdel Rahman for his precious suggestions and motivating encouragement. Also, I would like to thank Mr. Adje Mensah, Mr. Liangbin Yao, Mr. Khalid Rustom, Mr. Michael Pepper, Mr. Xu Cheng and all APECOR and Florida PEC members and UCF teammates. I am also indebted to Ms. Michelle Jordan for helping me in my thesis.

I have been blessed with a wonderful friend and roommate, Dr Wafaa Khattou, to whom many thanks are dedicated for her prayers encouragement and fellowship and to my cousin Dr. Eyad Batarseh for his valuable help and support.

My ultimate thanks, earnest appreciation and deep love are devoted to my family, to whom I am so indebted for their continual support, faith and love.

# TABLE OF CONTENTS

| LIST OF TABLES                                         | viii |

|--------------------------------------------------------|------|

| LIST OF FIGURES                                        | ix   |

| CHAPTER 1 INTRODUCTION                                 | 1    |

| 1.1 Overview                                           | 1    |

| 1.2 Thesis Outline                                     | 4    |

| CHAPTER 2 LITERATURE REVIEW                            | 6    |

| 2.1 Background                                         | 6    |

| 2.2 Prior Arts in High Slew Rate VRM                   | 16   |

| 2.2.1 Non Isolated Technologies                        | 17   |

| 2.2.1-I Current Compensators                           | 17   |

| 2.2.1-II Stepping Inductance VRM                       | 18   |

| 2.2.1-III Active Transient Voltage Compensators (ATVC) | 20   |

| 1) Current Injection Mode                              | 23   |

| 2) Steady-State Mode                                   | 24   |

| 3) Energy Recovery Mode                                | 25   |

| 2.2.2 Transformer Based Non-Isolated DC-DC Converters  | 26   |

| 2.2.2-I A Deeper Insight into a Small Duty Cycle       | 26   |

| 2.2.2-II Tapped Inductor (TI) Buck                     | 28   |

| 2.2.2-III TI-Buck with Lossless Clamp Circuit          | 30   |

| 2.2.2-IV The Active Clamp Couple Buck Converter        | 31   |

| 2.2.2-V A Non-Isolated Half-bridge DC-DC Converter     | 33   |

| 2.3 Chapter Recap                                      | 35   |

| CHAPTER 3 Half-bridge Buck Voltage Regulator         | 37 |

|------------------------------------------------------|----|

| 3.1 Introduction                                     | 37 |

| 3.2 Half-bridge Buck Control Schemes                 | 39 |

| 3.2.1 Symmetric Half-bridge Buck Converter:          | 39 |

| 3.2.2 Asymmetric Half-bridge Buck Converter:         | 42 |

| 3.3 HBBC Modes of Operation                          | 45 |

| 3.3.1 Symmetric Half-bridge                          | 45 |

| 3.3.2 Asymmetric Half-bridge                         | 54 |

| 3.4 Simulation Results                               | 60 |

| 3.5 Turns Ratio vs. Efficiency                       | 62 |

| 3.6 Small Signal Modeling                            | 64 |

| 3.7 Chapter Recap                                    | 67 |

| CHAPTER 4 MAGNETICS DESIGN AND EXPERMINTAL RESULTS   | 68 |

| 4.1 Introduction                                     | 68 |

| 4.2 Properties and Characteristics of Magnetic Cores | 69 |

| 4.3 Losses                                           | 74 |

| 4.3.1 Core and Hysteresis Losses                     | 74 |

| 4.3.2 Eddy Current Losses                            | 74 |

| 4.3.3 Skin Effect                                    | 75 |

| 4.4 Windings                                         | 76 |

| 4.5 Experimental Results                             | 77 |

| 4.6 Chapter Recap                                    | 83 |

| CHAPTER 5 MULTIPHASE BUCK                            | 84 |

| 5.1 Introduction                 | 84  |

|----------------------------------|-----|

| 5.2 Conventional Multiphase Buck | 88  |

| 5.3 Steady-State Analysis        | 96  |

| 5.3.1 Gain Equation              | 96  |

| 5.3.2 Ripple Calculation         | 98  |

| 5.3.3 Analysis                   | 101 |

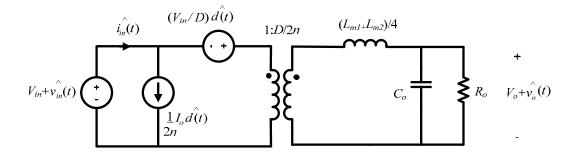

| 5.4 Small Signal Modeling        | 103 |

| 5.5 Chapter Recap                | 112 |

| CHAPTER 6 SUMMARY                | 113 |

| 6.1 Conclusion                   | 113 |

| 6.2 Future Work                  | 116 |

| REFERENCES                       | 117 |

# LIST OF TABLES

| Table 2.1.1 Intel Desktop Motherboards on LGA 775                       | 6  |

|-------------------------------------------------------------------------|----|

| Table 2.1.2 Intel Desktop Motherboards on mPGA 478                      | 7  |

| Table 2.1.3 Example Specifications for Intel Microprocessors            | 10 |

| Table 3.3.1 Voltage and Current Stress Analysis for the Symmetric HBBC  | 53 |

| Table 3.3.2 Voltage and Current Stress Analysis for the Asymmetric HBBC | 58 |

| Table 3.5.1 Turns Ratio versus Efficiency                               | 63 |

| Table 4.2.1 Core Material Comparison                                    | 73 |

# LIST OF FIGURES

| Figure 2.1.1 PGA Package and Socket                                            | 7  |

|--------------------------------------------------------------------------------|----|

| Figure 2.1.2 LGA Package and Socket                                            | 7  |

| Figure 2.1.3 LGA 775 and mPGA 478 Packages                                     | 7  |

| Figure 2.1.4 LGA Socket Assembly View                                          | 8  |

| Figure 2.1.5 Intel Desktop Motherboard                                         | 9  |

| Figure 2.1.6 A Block Diagram of a Motherboard                                  | 9  |

| Figure 2.1.7 Intel Roadmap of a 32-bit CPU showing (a) CPU Die Voltage and (b) |    |

| Current Demand and Slew Rate                                                   | 11 |

| Figure 2.1.8 A Conceptual Block of the Motherboard Main Power Source           | 11 |

| Figure 2.1.9 A Simple Basic Buck Converter.                                    | 13 |

| Figure 2.1.10 An Interleaved N phase Buck Converter                            | 14 |

| Figure 2.2.1 Linear Mode Current Compensator Topology                          | 17 |

| Figure 2.2.2 Switching Mode Current Compensator Topology                       | 18 |

| Figure 2.2.3 The Basic Configuration of the Stepping Inductance Circuit        | 19 |

| Figure 2.2.4 ATVC Circuit                                                      | 21 |

| Figure 2.2.5 Series ATVC Implementation Circuit                                | 22 |

| Figure 2.2.6 Parallel ATVC Implementation Circuit.                             | 22 |

| Figure 2.2.7 Conceptual Parallel ATVC Implementation Circuit                   | 23 |

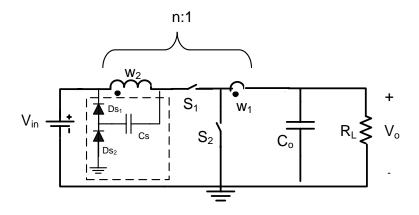

| Figure 2.2.8 The TI-Buck Circuit                                               | 28 |

| Figure 2.2.9 Rearranged TI-Buck                                                | 30 |

| Figure 2.2.10 The TI-Buck with Lossless Clamp Circuit                          | 30 |

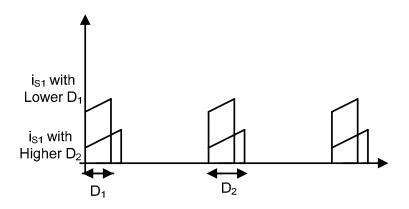

| Figure 2.2.11 Top Switch Current and Duty Cycle Relation                        | 32 |

|---------------------------------------------------------------------------------|----|

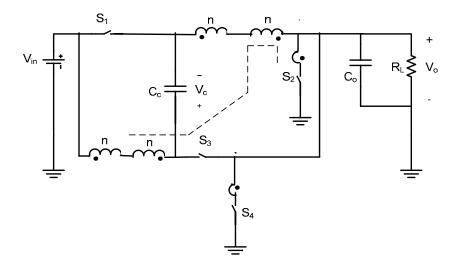

| Figure 2.2.12 The Active Clamp Couple Buck Converter                            | 33 |

| Figure 2.2.13 Non-Isolated Half-bridge Converter                                | 34 |

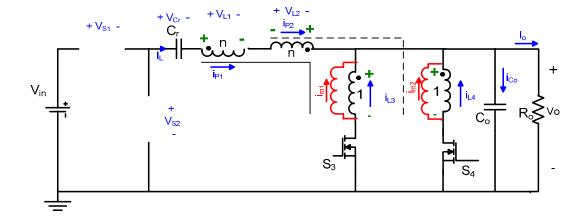

| Figure 3.1.1 Half-bridge Buck Converter Circuit Configuration                   | 37 |

| Figure 3.2.1 Switching Waveforms of the Symmetric Half-bridge Buck Converter    | 39 |

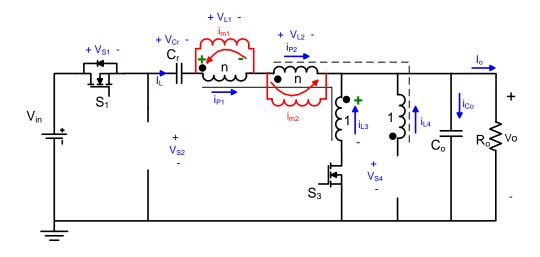

| Figure 3.2.2 Mode I of the Symmetric Half-bridge Buck Converter                 | 40 |

| Figure 3.2.3 Mode II of the Symmetric Half-bridge Buck Converter                | 41 |

| Figure 3.2.4 Mode III of the Symmetric Half-bridge Buck Converter               | 42 |

| Figure 3.2.5 Switching Waveforms of the Asymmetric Half-bridge Buck Converter   | 43 |

| Figure 3.2.6 Mode I of the Asymmetric Half-bridge Buck Converter                | 44 |

| Figure 3.2.7 Mode II of the Asymmetric Half-bridge Buck Converter               | 44 |

| Figure 3.3.1 Key Waveforms of Symmetric Half-bridge Buck Converter              | 46 |

| Figure 3.3.2 Mode I In the Analysis of Symmetric Half-bridge Buck Converter     | 47 |

| Figure 3.3.3 Mode II In the Analysis of Symmetric Half-bridge Buck Converter    | 48 |

| Figure 3.3.4 Mode III' In the Analysis of Symmetric Half-bridge Buck Converter  | 50 |

| Figure 3.3.5 Mode III In the Analysis of Symmetric Half-bridge Buck Converter   | 50 |

| Figure 3.3.6 Mode IV In the Analysis of Symmetric Half-bridge Buck Converter    | 51 |

| Figure 3.3.7 Mode V' In the Analysis of Symmetric Half-bridge Buck Converter    | 52 |

| Figure 3.3.8 Mode V In the Analysis of Symmetric Half-bridge Buck Converter     | 53 |

| Figure 3.3.9 Mode I In the Analysis of Asymmetric Half-bridge Buck Converter    | 54 |

| Figure 3.3.10 Mode II' In the Analysis of Asymmetric Half-bridge Buck Converter | 55 |

| Figure 3.3.11 Mode II In the Analysis of Asymmetric Half-bridge Buck Converter  | 56 |

| Figure 3.3.12 Mode I' In the Analysis of Asymmetric Half-bridge Buck Converter  | 58 |

| Figure 3.4.1 Simulation Circuit for a Symmetric HBBC                                | . 60 |

|-------------------------------------------------------------------------------------|------|

| Figure 3.4.2 Switching Waveforms Simulation Result for a Symmetric HBBC             | . 61 |

| Figure 3.4.3 Simulation Results for a Symmetric HBBC                                | . 61 |

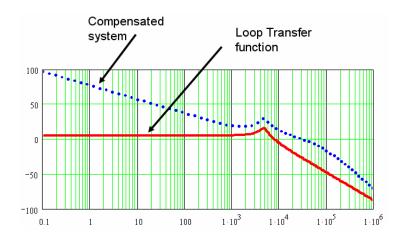

| Figure 3.6.2 Loop and Compensated System Frequency Response                         | . 66 |

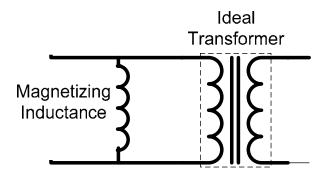

| Figure 4.2.1 Transformer Equivalent Circuit.                                        | . 70 |

| Figure 4.3.1 Effect of Skin Depth                                                   | . 75 |

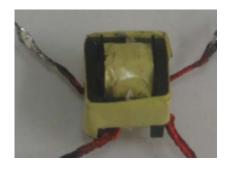

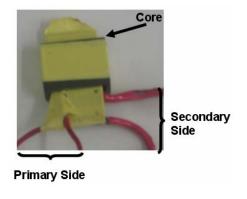

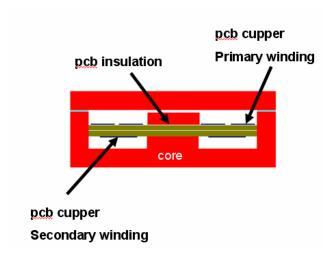

| Figure 4.5.1 PC44EE16-Z Transformer                                                 | . 78 |

| Figure 4.5.2 PC44EE16-Z Transformer Model                                           | . 78 |

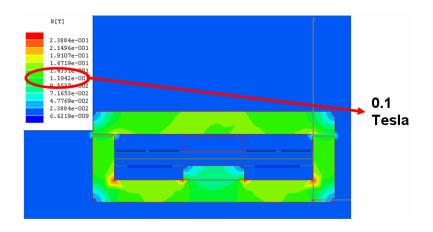

| Figure 4.5.3 PC44EE16-Z Transformer Simulation                                      | . 78 |

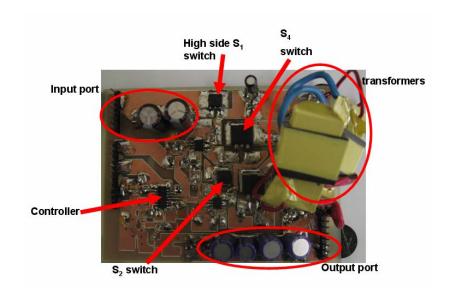

| Figure 4.5.4 Prototype #1 with PC44EE16-Z Transformer                               | . 79 |

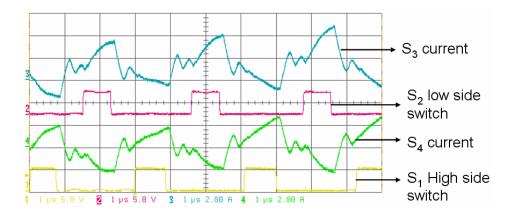

| Figure 4.5.5 Experimental Results Using PC44EE16-Z.                                 | . 80 |

| Figure 4.5.6 PC95ELT18/07.3Z Transformer                                            | . 80 |

| Figure 4.5.7 PC95ELT18/07.3Z Transformer Model.                                     | . 81 |

| Figure 4.5.8 PC95ELT18/07.3Z Transformer Simulation.                                | . 81 |

| Figure 4.5.9 Prototype #2 with PC95ELT18/07.3Z Transformer                          | . 82 |

| Figure 4.5.10 Experimental Results Using PC95ELT18/07.3Z                            | . 82 |

| Figure 5.1.1 Single Phase Buck Converter                                            | . 84 |

| Figure 5.1.2 Conventional Multiphase Buck Converter                                 | . 86 |

| Figure 5.1.3 The Top Switch Current and Duty Cycle Relation                         | . 87 |

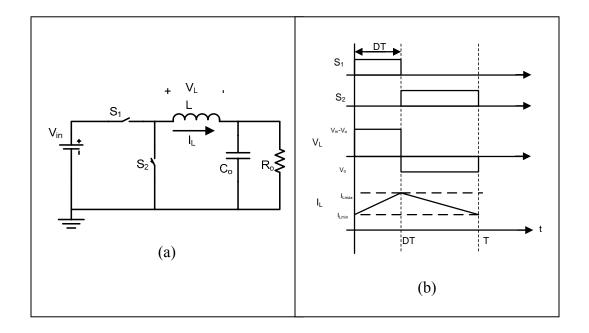

| Figure 5.2.1 Single Phase Buck (a) Circuit and (b) Switching and Inductor Waveforms | 88   |

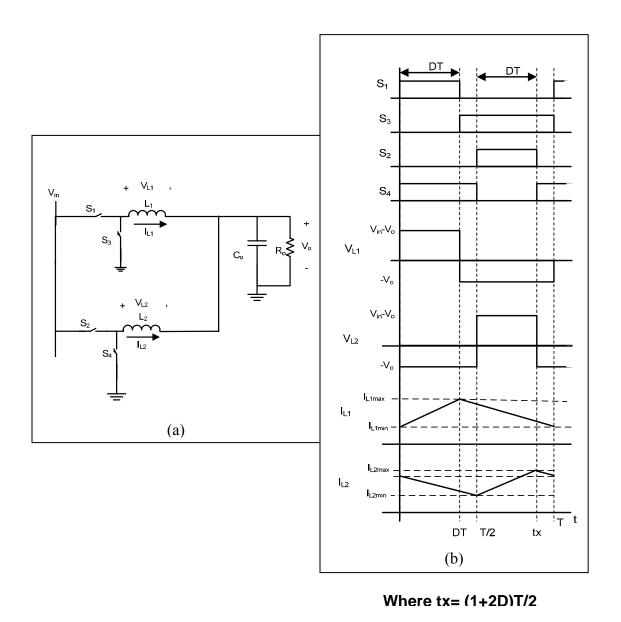

| Figure 5.2.2 Conventional Multiphase Phase Buck (a) Circuit and (b) Key Waveforms   | 90   |

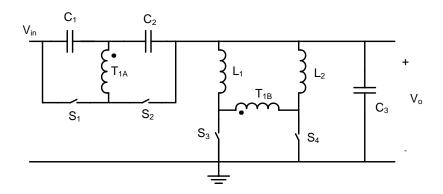

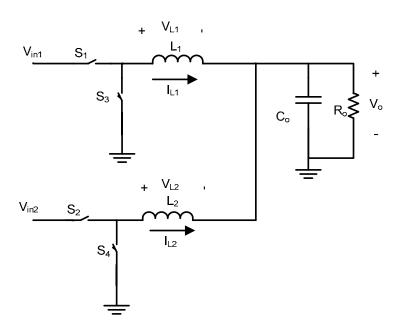

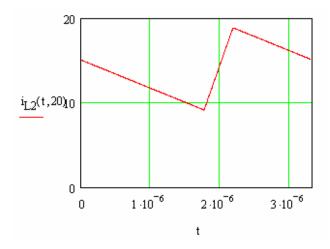

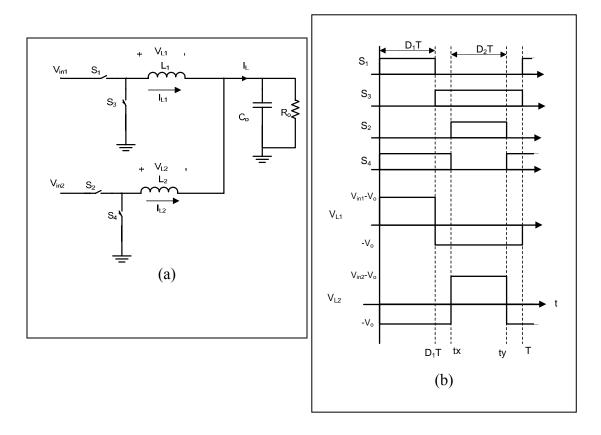

| Figure 5.2.3 Multi-Input Multiphase Phase Buck Circuit Configuration                | . 92 |

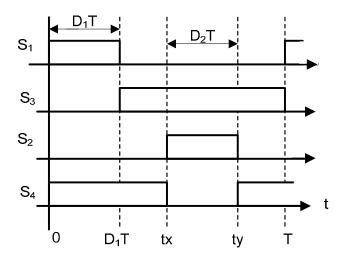

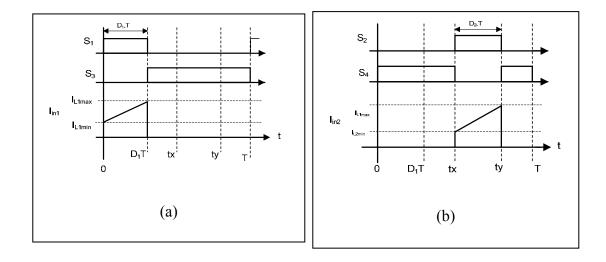

| Figure 5.2.4 Multi-Input Multiphase Phase Buck Driving Waveforms                    | . 93 |

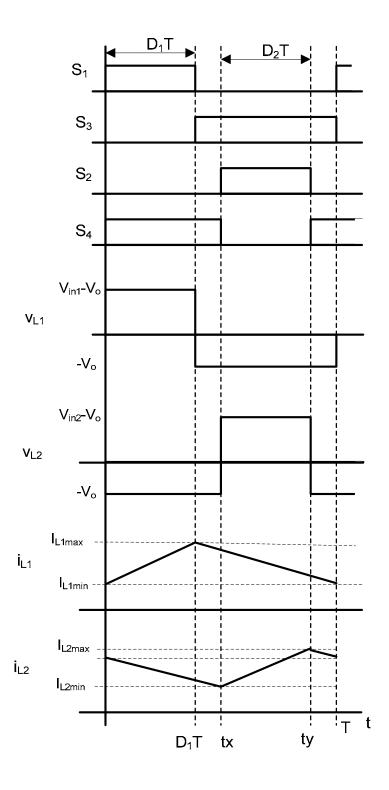

| Figure 5.2.5 Multi-Input Multiphase Phase Buck Key Waveforms                      | 94  |

|-----------------------------------------------------------------------------------|-----|

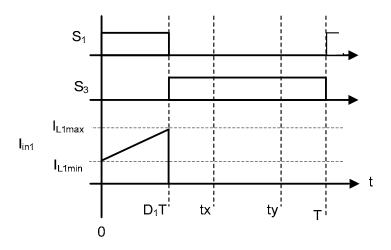

| Figure 5.3.1 Phase One Driving and Inductor Waveforms                             | 96  |

| Figure 5.3.2 Phase Two Driving and Inductor Waveforms                             | 97  |

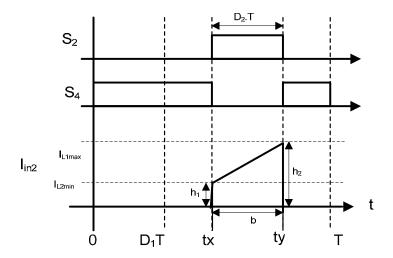

| Figure 5.3.3 Multi-Input Multiphase Converter (a) Circuit and (b) Driving Signals | 98  |

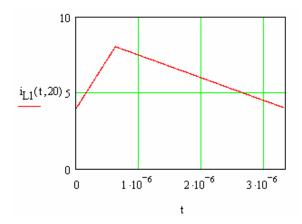

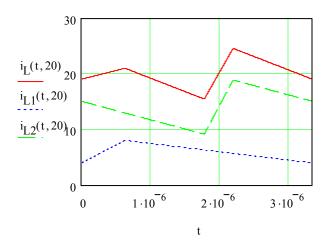

| Figure 5.3.4 Inductor Current in Phase 1 of a Two-Input Two-Phase Converter       | 102 |

| Figure 5.3.5 Inductor Current in Phase 2 of a Two-Input Two-Phase Converter       | 102 |

| Figure 5.3.6 Total Inductors Current in a Two-Input Two-Phase Converter           | 102 |

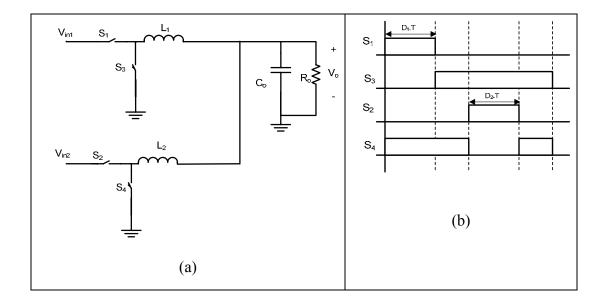

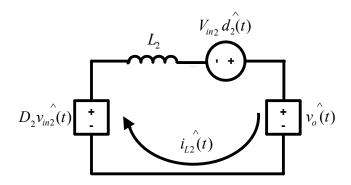

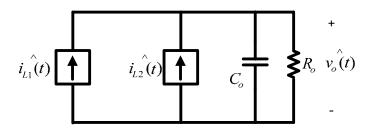

| Figure 5.4.1 Multi-Input Two-Phase Buck (a) Circuit and (b) Inductor Voltages     | 104 |

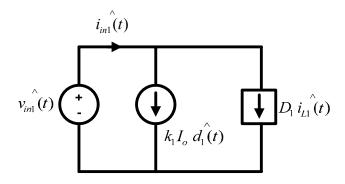

| Figure 5.4.2 Input Current in (a) Phase One (b) Phase Two                         | 106 |

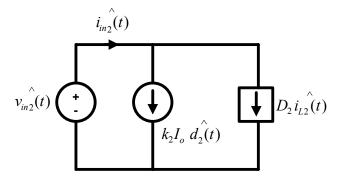

| Figure 5.4.3 Input Current of the First Phase                                     | 109 |

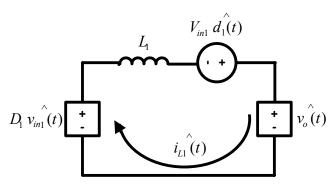

| Figure 5.4.4 Input Current of the Second Phase                                    | 109 |

| Figure 5.4.5 Energy Storage Element Number 1 (inductor in the first phase)        | 109 |

| Figure 5.4.6 Energy Storage Element Number 2 (inductor in the second phase)       | 110 |

| Figure 5.4.7 Energy Storage Element Number 3 (output filter capacitor)            | 110 |

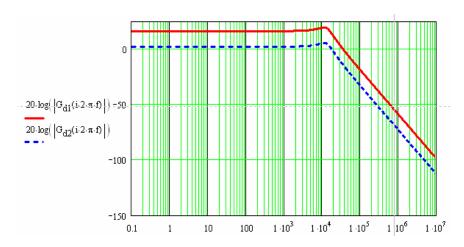

| Figure 5.4.8 Bode Plot of a Two-Input Two-Phase Buck Converter                    | 111 |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Overview

Power supplies are the core element in most of the electrical equipment needed today. Loads can be very critical in the sense that they need to be fed with a constant, highly regulated input power. Computer processors are one such example of critical loads, which is why the silver box power supply in the computer case cannot be directly connected to the microprocessor. Instead, it is connected to a dc-dc converter, the output of which feeds the processor.

Point of Load (POL) regulation has replaced the old centralized power box due to its vicinity to the microprocessor, which results in a closed dc-dc converter being dedicated to deliver the power needed by the microprocessor. This has alleviated the undesired effect of the parasitic elements that existed in the old system. These POLs are called Voltage Regulator Modules (VRM).

The trend to have low voltage VRMs as a microprocessor's power supply is increasing due to the benefit of lower power loss and faster data transfer. Hence, the initially used power delivery structure, which adopted a centralized silver box to supply the load, became unsuitable for meeting the challenge of low output voltage due to the resistive and inductive parasitics.

The equivalent inductance of the regulator is the barrier of output current slew rate; for lower ripple current and consequently lower rms current resulting in lower power loss, the output inductor should be large. On the other hand, large inductors mean

slower transient response. It is a design challenge faced by switching converter engineers to compensate both cases. Fast transient response under fast load change is a crucial issue in dc-dc converters with modern microprocessors [1-5].

Dynamic response of the converter has been a research focus to enhance the transient response of the control loop during significant step-up and step-down load conditions, which may reach 120A/us [11-17, 19, 20-24, 27-28].

The main VRM cannot handle the required fast transient effectively due to its large filter inductance, which is needed to decrease the output current ripple. The delay times of the controller, LC filter and the compensation network also add some restrictions on how fast the VRM can respond to any load change. Therefore, many efforts have been put into increasing the transient response of the VRM [11-17, 19, 20- 24, 27-28].

A conventional step-down buck converter is the building block of any VRM, but due to the high output ripple, an interleaved multiphase buck replaced the buck with the same 12 Volt input [23]. Another possible solution is to parallel several converters, each with a large inductor, which results in a small overall inductance value; however, the steady-state performance will still not be satisfactory due to higher losses.

A stepping inductor introduces a method to achieve a fast transient response during load variation, and at the same time guarantees lower current ripple during normal steady-state mode. This is done by having two different inductor values in series. The smaller value dominates during transient period and the larger during steady-state [14, 30].

The output suffers from two voltage spikes that occur during step-up and stepdown conditions [25]. The methods and suppression techniques developed so far focused mainly on decreasing the second voltage spike as there is no control over the first spike due to its very short time period and its dependency on the capacitor parasitic.

The current compensation technique to enhance the output voltage during transient is based on two injection methods: linear and switching [11-16].

Active Transient Voltage Compensator (ATVC) approaches the problem in a similar yet opposite way. It relies on injecting a voltage source instead of current [25]. ATVC simply acts as another buck converter but with smaller inductance and at a much higher frequency. The small inductor helps by increasing the slew rate of the current, and thereby minimizing the current supplied by the output capacitors and decreasing the voltage spike at the load side. The introduction of the transformer in the ATVC circuit helps in reducing the current in the switches, which will decrease the power loss. On the other hand, the lower turns ratio at the secondary side will increase the current supplied to the load.

The techniques mentioned so far focus on increasing the transient response during load change. Nevertheless, they suffer from a small duty cycle resulting from stepping the 12 Volts input down to the required one Volt at the load side. Efforts have been directed into non-isolated, transformer-based buck topologies to enlarge the duty cycle, including tapped inductor buck, active-clamp couple buck and forward and push pull converters to name a few [27-31].

#### 1.2 Thesis Outline

A concise overview of this work is presented in Chapter One, in which the problem is briefly addressed and the two major techniques to solve the problem are stated. Investigation of an Intel roadmap shows the trend of lowering the output voltage and increasing the current and power densities of future VRM. Efforts took two research directions in redesigning the current VRM to meet the new requirements of the next generation processors.

Chapter Two introduces the background of the work, discussing in detail all aspects of the VRM challenges and limitations. Two main output voltage spikes occur at the load side, and passive and active methods were deeply examined to alleviate such spikes. The passive method of adding more capacitors is limited by space and cost. Active compensation methods, which vary from current to voltage injection, are studied in Chapter Two. In Section 2.1, the complete scenario of VRM requirements is presented and the accompanied challenges are discussed. Section 2.2 reviews prior arts, which were dedicated to solving the problem by passive and active means. Transformer-based topologies are discussed in Section 2.3.

The new proposed topology, which is based on a half-bridge buck, is given in Chapter Three. The half-bridge buck offers an extended duty cycle and avoids the problems associated with small duty ratios. Detailed discussion and analysis are given in this chapter.

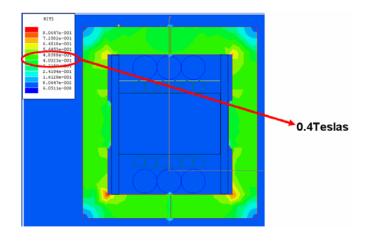

Chapter Four gives an insight on the magnetic part of the half-bridge buck presented earlier and provides a design approach and experimental results. The halfbridge buck has a flyback transformer as the core of its operation. Simulation results show the severe impact of leakage on converter efficiency and the need for a solid and tight magnetic design.

Multi-input converters are introduced in Chapter Five with a complete small-signal modeling of a two-input converter. Small-signal modeling is inevitable in control design. A two-phase buck with different inputs is analyzed in detail. Circuit averaging and Middlebrook's state space averaging are applied, and consequently, a small-signal model is derived.

The conclusion and future work are summarized in Chapter Six.

# **CHAPTER 2**

## LITERATURE REVIEW

# 2.1 Background

Roadmaps of semiconductor and microprocessor companies continue to call for the lowering of the output voltage of the VRM to values less than one Volt and are expected to even decrease more [1]. Meanwhile, VRM switching frequency is pushed higher for the purposes of decreasing the component size and enhancing the transient response.

The computer processor is connected to the motherboard through a socket, which serves as an interface between the motherboard and the processor, and it allows for electrical connectivity and easy removal to replace the processor when needed [2]. Socketing technology has moved from the micro Pin Grid Array (mPGA) to the Land Grid Array (LGA) because of some limitations that are beyond the scope of this thesis [2]. Intensive efforts at Intel have produced the LGA 775 socket [2].

Tables 2.1.1 and 2.1.2 show Intel Motherboard versions on LGA 775 and mPGA 478 sockets [3].

Table 2.1.1 Intel Desktop Motherboards on LGA 775

| Chipset                     | Intel Desktop Motherboard    |

|-----------------------------|------------------------------|

| Intel 915GV Express Chipset | Intel Desktop board D915GLVG |

| Intel 915 G Express Chipset | Intel Desktop board D915GUX  |

Table 2.1.2 Intel Desktop Motherboards on mPGA 478

| Chipset             | Intel Desktop Motherboard     |  |

|---------------------|-------------------------------|--|

| Intel 865PE Chipset | Intel Desktop board D865 PESO |  |

| Intel 865P Chipset  | Intel Desktop board D865 PCK  |  |

|                     | Intel Desktop board D865 PCD  |  |

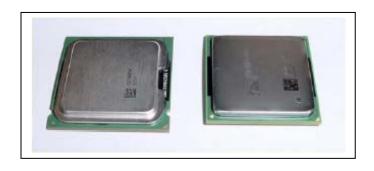

The difference between sockets PGA and LGA is that LGA has smaller fewer number of pins and a reduced cost. Figures 2.1.1 and 2.1.2 show the two different sockets [2]. Figure 2.1.3, shows both mPGA and LGA packages [2].

Figure 2.1.1 PGA Package and Socket

Figure 2.1.2 LGA Package and Socket

Figure 2.1.3 LGA 775 and mPGA 478 Packages

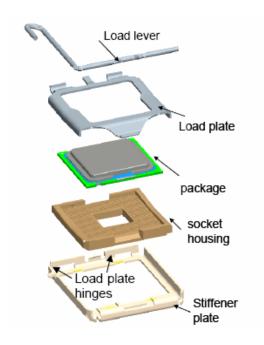

The package consists of a socket housing with stitched contacts, a stiffener plate, a load plate and a load lever as shown in Figure 2.1.4.

Figure 2.1.4 LGA Socket Assembly View

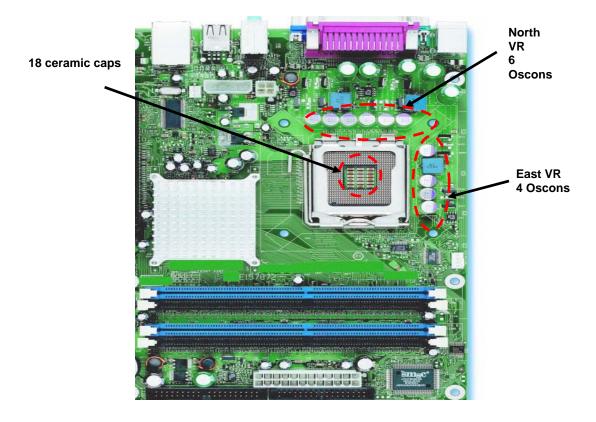

Figure 2.1.5 shows a picture of a complete assembly of an Intel motherboard D915GUX version 10.1 with VRM components and LGA package [4-5].

Figure 2.1.5 Intel Desktop Motherboard

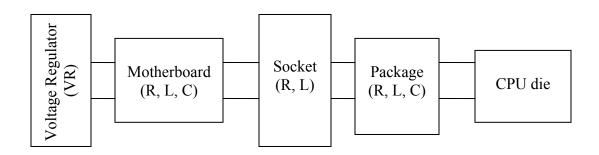

The overall circuit can be depicted in the block diagram shown in Figure 2.1.6.

Figure 2.1.6 A Block Diagram of a Motherboard

According to the International Technology Roadmap for Semiconductors (ITRS), Semiconductor Industry Association (SIA) and Intel's roadmap, the operating voltage is decreasing continuously to values less than One Volt along with increasing the processor current exceeding 100A.

Some example specifications for Intel microprocessor are shown in Table 2.1.3 [6-9].

Table 2.1.3 Example Specifications for Intel Microprocessors

| Parameter/Processor                     | Pentium® II  | Pentium® III | Pentium® 4           |

|-----------------------------------------|--------------|--------------|----------------------|

| Chal Sand (III)                         | 233M         | 600M         | 1.4G                 |

| Clock Speed (Hz)                        | 266M<br>300M | 550M<br>450M | 1.5G<br>1.7G         |

| Core Voltage (V) min. /max.             | 2.8          | 2.05         | 1.56/1.7             |

|                                         |              | 2.00         | 1.53/1.7             |

| Converter Voltage (V) min. /max.        | -            | -            | 1.627/1.7            |

|                                         | 11.8         | 17.8         | 1.61/1.7             |

| Core Current (A)                        | 12.7<br>14.2 | 17.0<br>14.5 | -                    |

| Converter Current (A)                   | -            | -            | 40.6<br>43.0<br>52.7 |

| Core Current Slew Rate ( $A/\mu s$ )    | 30           | 20           | -                    |

| Converter Current Slew Rate $(A/\mu s)$ | -            | -            | 50                   |

Inspecting the numbers in Table 2.1.3, it can be noted that there is a huge current increase from 14A in Pentium II to above 50A in Pentium 4 versus the drop in voltage from 2.8V to 1.6V in the same processors versions mentioned above.

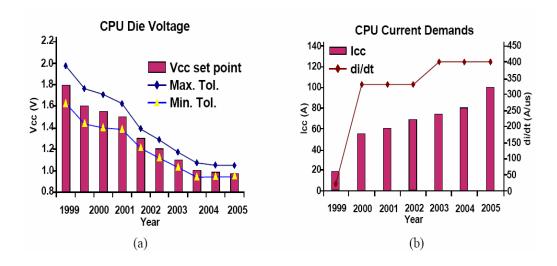

Figure 2.1.7 Intel Roadmap of a 32-bit CPU showing (a) CPU Die Voltage and (b) Current Demand and Slew Rate

Figure 2.1.7 confirms the preceding discussion; the CPU will be expected to run with a voltage below the one Volt level and currents hitting the 120A as fast as 400A/us [10].

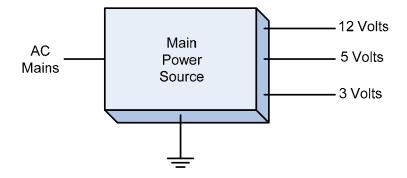

The main power source available on the motherboard provides three power levels: + 12V, +5V and +3.3 V output as depicted in Fig. 2.1.8.

Figure 2.1.8 A Conceptual Block of the Motherboard Main Power Source

As seen in the Intel roadmap shown in Fig. 2.1.7, in the late 1990s, the CPU needed 2 Volts, which were initially supplied from the 5 Volts port [9]. However, the resistive and inductive parasitic elements between the power source, known as the silver box, and the CPU dramatically affect the quantity, as well as the quality at the CPU input, -i.e. the load. With the increasing trend of lowering the output voltage, this power flow scheme could not be accepted or used any longer. Hence, the point of load (POL) converter, which was placed close enough to the load, replaced the previous power flow.

Again, the centralized silver box was no longer used due to the parasitic effect it added, which placed a restriction on further lowering of the output voltage. Consequently, dedicated dc-dc converters came to play an important role in the CPU industry. VRMs became the center of the motherboard. With the continuous decrease in the CPU voltage, and an analogous increase in the current, the input voltage shifted to the 12 Volts port [9]

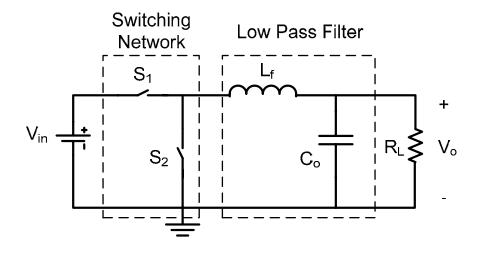

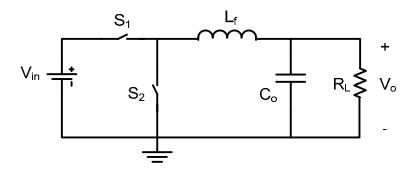

The most simple and logical method to achieve the low output voltage from the 12 Volts input is to have a voltage source stepped down to the required CPU voltage level. The buck converter is therefore the cornerstone in any VRM. A buck converter is merely a level stepping-down circuit consisting of a switching network, which is mainly N-channel MOSFET and a low pass filter, as shown in Figure 2.1.9, where the input voltage is stepped down in accordance with the switching mechanism to produce an output voltage that is less than the input by a factor equal to the duty cycle of the main switch. The switching part of the circuit is followed by a filtering network to smooth out the spikes and supply the load with a clean output voltage of the desired value. The

control variable in this case is the duty cycle; in other words, the output voltage is ideally proportional to the duty cycle.

Figure 2.1.9 A Simple Basic Buck Converter

Central Processing Units (CPUs) in computers are treated as critical loads in VRM literature. The challenges VRM designers face are compacted in two aspects:

- 1) The clean, constant and low-output voltage the CPU needs, together with high current and power densities, add thermal issues to the design complexity.

- 2) The fast transient response is equally important as in the CPU realm. With the above design considerations in mind, it is obvious that a single-phase buck converter will not meet the CPU requirements due to the large inductor ripples that the single buck presents. The shift to interleaved multiphase buck was inevitable [23].

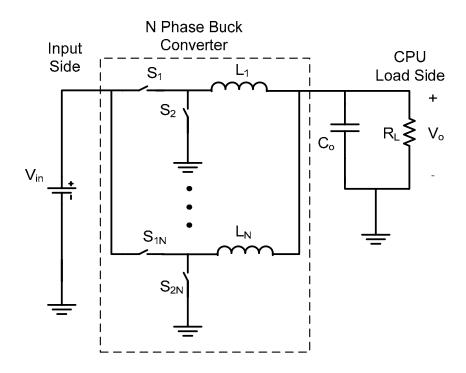

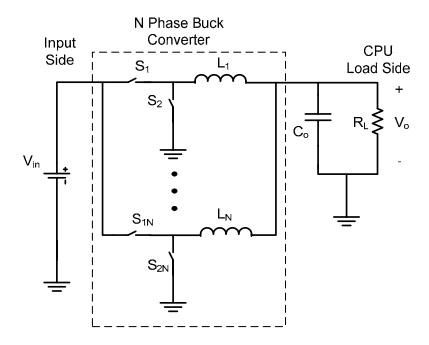

An interleaved multiphase buck converter efficiently replaced its single phase counterpart improving the transient response and increasing the efficiency. Figure 2.1.10, shows an N phase buck consisting of identical N phases shifted by 360° / N. This control scheme obviously decreases the output current ripples. The lower the current ripple, the

lower the rms current, which means the lower the losses. This can also mean better efficiency and better thermal management.

Figure 2.1.10 An Interleaved N phase Buck Converter

As discussed earlier, the input to the VRM has been switched from the 5 Volt to the 12 Volt port. Thus, there is a 12 DC Voltage source at the input of a multiphase buck converter that supplies the processor of the motherboard with the low voltage it needs. The lower the output voltage, the less the power consumption and the faster the data transfer becomes. Therefore, the future trend is to further decrease the voltage and consequently increase the current. The amount of data handled by the processor varies with the number of programs being run that comprise the processor load. The load may not only change from no load to full load, but it can do so with a very high slew rate up to 120A/us [10].

When the load change occurs, whether step-up or down, the difference of the current should be handled. In the case of step-up load, the extreme scenario is when the load changes from no load to full load. When this happens, the output voltage tends to decrease, but in order to maintain a constant output voltage, current injection will be needed from the source which leads to increase the duty cycle to be able to supply the load with the current it needs. Before the VRM supplies the output load completely, the output capacitor will help in supplying the current needed, and thus a voltage spike will occur at the output voltage. In an analogous way, when step-down load happens, energy stored in the filter inductor needs be recovered and thus the off time — no source period — increases until all the energy that was stored in the filter inductor is consumed.

In the above cases, the controller, the LC filter, and the compensation network delay times will deteriorate the voltage spike at the output. In short, there are two voltage spikes that appear at the output, and their presence is a problem and their remedy depends on the understanding of their original source. The first voltage spike is determined by the capacitor parasitic ESR and ESL and also by the output current slew rate SR<sub>o</sub>. The second spike is determined by the energy stored in the inductor.

Only passive methods can reduce the first voltage spike by adding more output capacitors to reduce their equivalent series resistance and inductance, which is cost and space limited. As seen in Figure 2.1.5, many OSCON and ceramic capacitors are dwelled close to the CPU and occupy a lot of space on the motherboard [4, 5].

The first voltage spike is almost constant for a certain output filter inductance value, and it is hardly dependant on the inductor value and mainly relies on the parasitic values of the capacitor. The only way of eliminating the spike is to add more output

capacitors in parallel, thus decreasing the ESR and ESL. This passive method is limited by the available free space on the motherboard and by the cost.

The second spike is controllable, and is highly dependent on the filter inductance. The smaller the inductor the faster the transient response, and thus, the less the charge and the smaller the voltage spike becomes. In other words, the first voltage spike dominates when a small filter inductor is used at which the second spike is eliminated due to the high transient response. Similarly, the larger the inductor value, the slower the transient response and the larger the voltage spike. Thus, the second spike dominates with a large filter inductance.

Consequently, there are two design methods: the first method is an ESR- and ESL-based transient design with a small filter inductance [19]. The second design method is an energy-based design procedure with a large output filter inductance. As mentioned earlier, those spikes are deteriorated with non-ideal controllers. All practical controllers suffer from delay times, which when added to the delays resulting from IC propagation time and LC network will have even more impact on increasing the spikes.

# 2.2 Prior Arts in High Slew Rate VRM

This section presents previous approaches to designing VRMs to meet the stringent requirements of the VRM design. There are two main fields in VRM: non-isolated topologies which focus on enhancing the transient response [11-19, 20-24, 27-28], and isolated topologies in which a transformer is applied to extend the duty cycle [25-29]. These two VRM topologies are discussed in this section.

# 2.2.1 Non Isolated Technologies

# 2.2.1-I Current Compensators

As stated before, the problem of the inability of the main voltage regulator in supplying the load with the needed current under-load changes is of great concern. Therefore, current compensators are based on the idea of injecting the current needed during transients instead of relying on the output capacitors to provide the load current. Current compensation injects current in two modes: linear mode current compensators, [11-13] and switching mode current compensators, [15-16] as shown in Figures 2.2.1 and 2.2.2, respectively.

In both topologies, the unbalanced current is supplied by the extra converter and results in high-current stresses.

Figure 2.2.1 Linear Mode Current Compensator Topology

Figure 2.2.2 Switching Mode Current Compensator Topology

The auxiliary circuit provides the unbalanced current in either a linear or a switching mode. The main disadvantage in the linear compensator is the conduction losses, and in the switching compensator, the disadvantage is the switching losses that result in a major decrease in efficiency of the overall converter, making current compensators very difficult in low-voltage and high-current applications.

# 2.2.1-II Stepping Inductance VRM

Figure 2.2.3 shows the basic configuration of the stepping inductance where, inductor  $L_r$  is smaller than  $L_o$  [14].

Figure 2.2.3 The Basic Configuration of the Stepping Inductance Circuit

$S_1$  is programmed to turn on during increased-load transients and  $S_2$  turns on during decreased-load transients to short circuit the larger inductor  $L_0$  in both cases [14]. When  $S_1$  turns on, the net inductance decreases, leaving the smaller one to be used, and this will increase the output inductor slew rate during that period, resulting in a reduced voltage deviation [14].

At step-up load, the output voltage decreases, and as a result,  $S_1$  turns on, which also decreases the output inductance. This will increase its slew rate until the current in the leakage inductance reaches the output current, and then  $V_o$  stops decreasing and starts to increase. When it reaches a certain value,  $S_1$  turns off, and once again,  $L_o$  takes over the output inductance and its current  $i_{Lo}$  dominates. However, since it is still less than the output-load current, the output voltage will decrease again, and consequently,  $S_1$  will turn on once the output voltage reaches a value less than a certain threshold. This oscillatory on and off switching of  $S_1$  stops once the  $i_{Lo}$  equals the output load current  $I_o$  [14].

Having a voltage source,  $V_1$  serves in keeping the large inductor current increasing during the time period when  $M_1$  and  $S_1$  are on. This further decreases the transient period and results in a faster transient response to maintain a constant output voltage to the load. The same operation takes place in a reverse order at load step-down switching S2 on and off [14].

# 2.2.1-III Active Transient Voltage Compensators (ATVC)

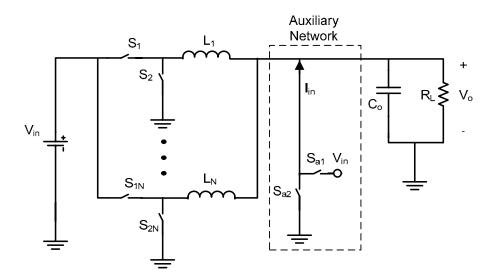

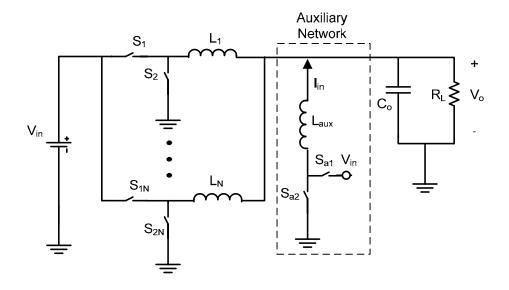

Active transient voltage compensator (ATVC) approaches the problem in a similar yet opposite way. It relies on injecting voltage source instead of current. Figure 2.2.4 shows the ATVC circuit [25].

ATVC simply acts as another buck converter, with smaller inductance and at much higher frequency. The small inductor helps to increase the slew rate of the current and thus minimizing the difference between the output current and the current from the main VRM. Once this difference decreases, the output capacitor charge decreases and leads to lower voltage spike at the output.

As shown in Figure 2.2.4, ATVC consists of a transformer with N turn ratio, two auxiliary switches  $S_{a1}$  and  $S_{a2}$  and a voltage source  $V_1$  that can be of any value.

Figure 2.2.4 ATVC Circuit

The introduction of the transformer helps in decreasing the current in the switches. This will decrease the power loss, from which the current compensation methods suffer. On the other hand, the lower turn ratio at the secondary will increase the current supplied to the load. The main VRM operates at relatively low frequencies maintaining good efficiency values.

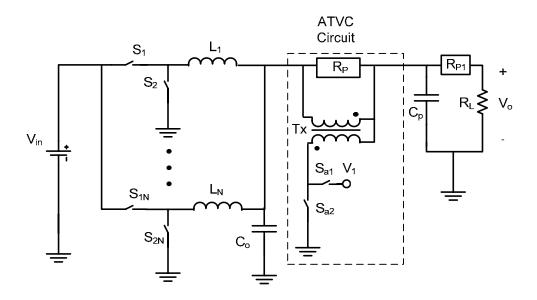

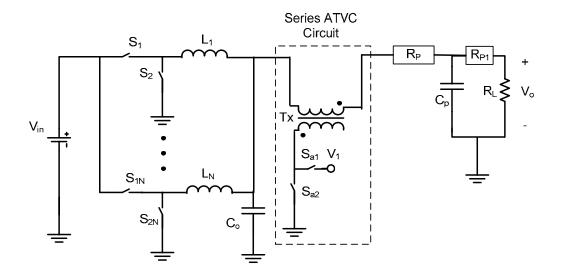

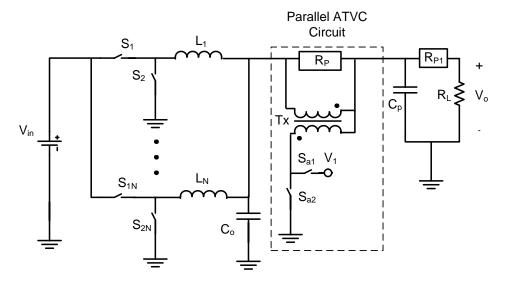

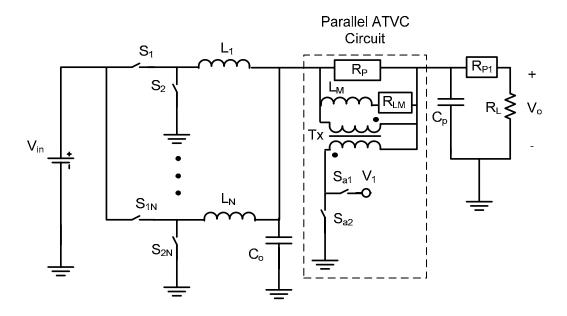

ATVC comes in two configurations: series and parallel, which are shown in Figures 2.2.5 and 2.2.6, respectively.

Figure 2.2.5 Series ATVC Implementation Circuit

Figure 2.2.6 Parallel ATVC Implementation Circuit

The only difference between series and parallel ATVC is that series ATVC handles all the unbalanced current between the main VRM and the load, whereas parallel ATVC carries only a portion of that current according to the voltage divider (K) of  $R_p$  and  $R_{LM}$ , following the equation;

$$K = \frac{R_P}{\left(R_P + R_{LM}\right)}$$

Where:

$R_p$  is the equivalent resistance of the traces and the parasitic, and,

$R_{LM}$  is the magnetizing inductance resistance as shown in Figure 2.2.7.

Figure 2.2.7 Conceptual Parallel ATVC Implementation Circuit

Hence, parallel ATVC current stress is less than that in series ATVC. Also, series ATVC increases the static load line, and yet, the transient load line improvements of both ATVC types are the same.

The complete cycle of ATVC can be divided into three modes of operation: current injection mode, steady-state and energy recovery mode.

# 1) Current Injection Mode

This is the period of time during which the load current increases abruptly.

Consequently, the output voltage decreases according to the power conservation during

this mode when ATVC kicks in to help the main VRM in supplying the current needed at the load side.

The small leakage inductance is what is needed to increase the slew rate of the current injected by the ATVC, so that the current is quickly supplied to the load without the help of the output capacitors, decreasing the charge difference and consequently decreasing the voltage spikes at the output. When the load current increases, the output voltage will consequently decrease to a certain limit when S<sub>a1</sub> turns on. At this instance, ATVC is activated, and the current supplying the load is the addition of the current from the main VRM plus the current from ATVC. Due to the small leakage inductance, the current rises very quickly with a high slew rate.

The transition between the on and off states of  $S_{a1}$  and off and on states of  $S_{a2}$  will continue until the magnetizing current (main VRM) reaches the output needed current and the output voltage reaches  $V_o$ . This period of time is what is known as current injection period.

#### 2) Steady-State Mode

Once the current supplied to the load from the main VRM, along with the added current from the ATVC side, reaches the current needed at the output, then the ATVC can go into standby mode.

It should be noted here that with the introduction of the transformer with N turns ratio, ATVC handles a current (1+N) times less than that handled by the current compensators thus reducing the conduction and the switching losses. In addition, it provides a current (1+N) higher than that of the previous arts with same filter inductance.

During the steady-state mode of operation both auxiliary switches  $S_{a1}$  and  $S_{a2}$  turn off. The body diode of  $S_{a2}$  should not turn on during this mode and this can be guaranteed by satisfying the following condition:  $N \cdot V_S < Vo + V_D$

Where: Vs is the secondary voltage of the transformer and  $V_D$  is the on-state voltage drop of the body diode of  $S_{a2}$ . Since the voltage drop across  $R_p$  is small, the above condition can be met easily.

### 3) Energy Recovery Mode

The last mode of operation is the energy recovery mode. During this period, the load current steps down with a very large negative slope, thus the output voltage increases. The excess energy should be recovered, and this is done by making the ATVC act as a boost converter by controlling  $S_{a2}$ .

This mode is the mirror opposite of the current injection mode in that the same logic is applied, but instead of increasing the current, the direction is taken into recovering the energy (discharging the current in the inductors feeding it back to the supply voltages).

This mode will continue until the output voltage decreases to the required value.

In summary, ATVC injects high slew rate current in step-up load and recycles extra energy stored in the VRM filter inductor into its input voltage  $V_I$  during step-down load.

#### 2.2.2 Transformer Based Non-Isolated DC-DC Converters

As mentioned earlier, a conventional step-down Buck converter is the building block of any VRM, but due to the high output ripple, interleaved-multiphase buck replaced the simple single-phase buck with the same 12 Volts input.

The stepping down from the 12 Volts input to the required one Volt at the load side entails a very small duty cycle, and added to that is the high switching frequency that results in some associated problems and low efficiency.

Efforts have been directed into non-isolated transformer-based buck topologies to solve the above mentioned problems, including tapped inductor buck, active-clamp couple buck and forward and push pull converters to name a few [26-29].

## 2.2.2-I A Deeper Insight into a Small Duty Cycle

The major problem associated with low output voltage and high switching frequency is having a small duty cycle as mentioned above. This is considered the source of all other accompanied limitations as listed below [29-32]:

- 1- A fast comparator is needed to create the small driving signal, which will increase the cost.

- 2- The top switch conduction period decreases with the increasing of the switching frequency, which may cause a malfunction of the converter, known as gate drive problems, and that cause an increase in the switching losses of the top switch and consequently increase the conduction loss of the lower switch.

- 3- Asymmetric transient response causes a clear difference in the step-up and stepdown speeds.

- 4- Efficiency will drop due to the high peak current that is associated with the small duty cycle and the long conduction period of the bottom body diode switch.

The problems associated with a small duty cycle are of great importance especially with the accompanied increase of switching frequencies to improve the transient response and to decrease the size. To address the small duty cycle issue, designers used coupled magnetic configuration including tapped inductor, coupled buck converters [26, 27] and the non-isolated Push Pull Converter [28, 32].

The straight forward solution to the above problem is to add another control parameter besides the duty cycle, which allows us to decrease the output voltage and maintain an optimum duty cycle and consequently avoids the problems related to small-duty ratios.

Transformer-based non isolated-dc-dc converters were foreseeable and an expected solution. It helps achieve the desired low-output voltage and, at the same time, sustain a relatively high duty cycle with better ripple cancellation and lower switching currents [32].

It is essential here to stress the fact that for many 12 V microprocessor power supplies, which are the subject of this study, there is no isolation required [32]. This explains why VRM designers are inclined towards transformer-based yet non-isolated dc-dc converters.

Two of the VRM requirements come back to back. The output voltage is in continuous decrease and the need for smaller passive components and faster transient response dictate the shift to higher switching frequencies. But, this doesn't come easily or empty handed, as the lower the output voltage, the lower the duty cycle. With the necessity of higher switching frequency, the efficiency will go down as well. Hence, there is justification to add a transformer to create a new VRM family designated for the

transformer-based non-isolated dc-dc converter, which includes: the tapped inductor buck converter [26] (with its twin circuit with lossless clamp circuit [29]) the active clamp couple buck converter [27], push pull buck [28] and the non-isolated half-bridge [29].

Each of these converters adds an advantage and a contribution for solving the above mentioned problems. But a well-known trade off issue is that it also fails in one aspect. The following is a brief listing of the pros and cons of the above converters.

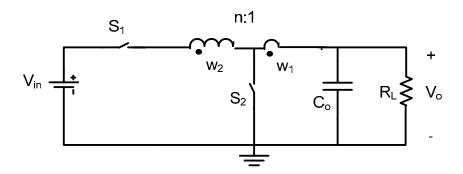

#### 2.2.2-II Tapped Inductor (TI) Buck

As with the case of the stepping inductance, the idea is to have a smaller inductance value to enhance the transient response. The two windings  $w_1$  and  $w_2$  shown in Figure 2.2.8 constitute the overall inductance in the charging period, whereas the small winding,  $w_2$ , takes over during the discharging period [26, 29].

Figure 2.2.8 The TI-Buck Circuit

The advantages of the tapped inductance are summarized as follows:

1- The availability of another parameter to control the output voltage besides the duty cycle allows for a better (wider) duty cycle according to the equation below [26, 29]:

$$D = \frac{nV_o}{V_{in} + (n-1)V_o}$$

This allows for solving the problem by extending the duty cycle.

- 2- The mismatch between the transient response speeds can be solved by precisely designing for  $w_1$  and  $w_2$  [26, 29].

- 3- Efficiency is also claimed to be better due to the n factor that decreases the current that passes through the top switch, and the enlarged duty cycle achieved will decrease the conduction period of the bottom switch body diode. These two consequences will increase the efficiency.

On the other hand, the TI-Buck suffers from limitations that counteract its above list of advantages.

The top switch driving scheme becomes a challenge, since it will not be as easy as the conventional buck. The second severe limitation is due to leakage energy. The leakage energy of winding  $w_2$  will be lost in the resonant circuit of  $w_2$ , and the top switch capacitor creates a high voltage spike across the switch, which decreases the efficiency and generates the possibility of destroying the top switch. Thus, the twin circuit of the TI-buck with the added clamp circuit offered a solution for the leakage energy.

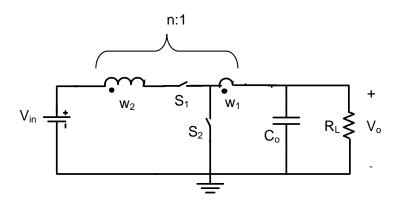

## 2.2.2-III TI-Buck with Lossless Clamp Circuit

The TI-buck shown in Figure 2.2.8 was rearranged to form the converter shown in Figure 2.2.9. This new arrangement will solve the gate driving problem simply by using the boot strap circuit for the top switch  $S_1$  [29].

Figure 2.2.9 Rearranged TI-Buck

Adding a lossless circuit to trap the leakage energy resulted in the circuit shown in Figure 2.2.10.

Figure 2.2.10 The TI-Buck with Lossless Clamp Circuit

The modified TI-Buck solves the problem of the basic TI-Buck but with the added complexity of the magnetic design plus the losses of the two added diodes in the clamp circuit.

Therefore, the solution offered by the modified TI-Buck with the lossless clamp circuit was equally leveled by the disadvantages of the magnetic design difficulty and the clamp diodes losses.

### 2.2.2-IV The Active Clamp Couple Buck Converter

As discussed before, the synchronous multiphase buck became the building block of the VRM for the benefits of transient response improvement and output current ripple cancellation, which help to decrease the output capacitance.

Nevertheless, the small duty cycle limits the ripple cancellation gained unless more phases are added with increased complexity.

The other problem addressed is the asymmetric transient response. Reducing the inductance value and decreasing the bandwidth are two approaches adapted to achieve symmetric transient response on one side. But on the other pane of the balance, these approaches decrease the efficiency and increase the output capacitance [27].

The TI-Buck offers a new parameter that helps in getting the transient responses closer to being symmetric. This parameter is the turn ratio of the two windings of the inductance.

The parameter n controls the slopes of the charging and discharging periods.

Therefore, the design challenge is to get the precise value of the turn ratio n of the two

windings  $w_1$  and  $w_2$ , which makes the slopes during the two intervals of the switching period equal, resulting in symmetric transients [26- 27, 29].

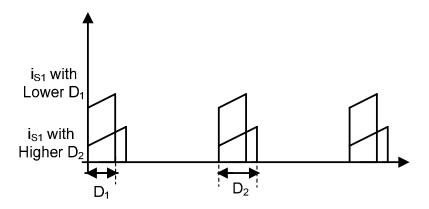

Increasing the duty cycle will go side-by-side with decreasing the current in the top switch  $i_{s1}$ . Figure 2.2.11 shows a comparison between the top switch current  $i_{s1}$  with small duty cycle  $D_1$  and higher duty cycle  $D_2$ . This can be translated also into lower losses and higher efficiency.

Figure 2.2.11 Top Switch Current and Duty Cycle Relation

Again, the other shortcoming suffered by the TI-buck is the leakage energy, which is dissipated into the top switch capacitor and creates a voltage spike across the switch and could possibly impair the switch. To overcome this problem, the 30V MOSFET is no longer suitable for use and should be replaced with a higher voltage switch, which can be stated as higher  $R_{dson}$  which results in higher conduction losses [27].

Many designers faced the challenge of coming up with a lossless snubber circuit to alleviate the spike without negatively affecting either the cost of adding more components or the efficiency.

Figure 2.2.12 The Active Clamp Couple Buck Converter

One of the proposed snubbers is the active clamp couple buck shown in Figure 2.2.12. The complexity of the control and the magnetic design is expected including the added cost and decreased efficiency.

## 2.2.2-V A Non-Isolated Half-bridge DC-DC Converter

The non-isolated half-bridge converter offers the following advantages: lower losses accompanied with the lower peak current and higher duty cycle through the integration of the transformer with its turn ratio and the faster turn off of  $S_2$  [30]. The circuit configuration is shown in Figure 2.2.13.

Figure 2.2.13 Non-Isolated Half-bridge Converter

As with the case in the previously discussed topologies, the non-isolated half-bridge doesn't offer the above listed advantages for free. The lower current in the primary branch dictates a higher current in the secondary and is translated into higher conduction losses. A transformer and an inductor are added, which increase the cost as well as the associated losses in the core and cupper besides adding to the design complexity [30].

#### 2.3 Chapter Recap

Future VRMs are heading into lower voltage, higher current and power densities in addition to shifting the switching frequency to ranges as high as mega Hertz in the aim of decreasing the size and enhancing the transient response. Today's converters suffer from two spikes at the output. The first voltage spike is almost uncontrollable but can be suppressed by paralleling different kinds of capacitors. However, this passive method is limited by cost and space.

The second voltage spike is determined by the energy stored in the inductor and there are different approaches to lowering it. But along with lowering it, there is a big tradeoff and design challenge. The smaller the inductor, the faster the response, but the ripple becomes an issue. The higher bandwidth and the smaller spike shift the switching frequency to higher band values, which lead to higher switching losses and therefore lower efficiencies.

Efforts have been made to alleviate the second voltage spike. The conventional current compensation was an attractive method of injecting high slew rate current in step-up load and absorbing the voltage overshoot in step-down load whether by linear or switching modes. The drawback is the large current stress that results in high conduction loss in linear mode and high switching loss in the switching mode.

Active Transient Voltage Compensator (ATVC) is a voltage injection method. The power loss is reduced due to the transformer that is being introduced as a vital element in the circuit of the ATVC. It relies on injecting high slew rate current during step-up load and energy recovery in step-down load.

ATVC activates only during transients with several MHz operating frequencies, whereas the main VRM remains at relatively lower frequency range to maintain better efficiency.

Large delay times inherited in the controller, compensation network and the LC filter deteriorate the voltage spikes even more. Now, all attention has been directed to enhance the controller design.

Finally, ATVC has improved AC load line mainly for the suppression of the second voltage spike with small power loss. It is a very attractive way in high slew rate applications.

The lower the output voltage, the smaller the duty cycle and the lower the efficiency will be. Many design approaches were taken into consideration including adding another output voltage control parameter. The most logical solution was to add a transformer while maintaining the non-isolation requirement of the VRM.

Tapped Inductor Buck was the original solution on which many other topologies were based, and clamp circuits were designed to solve the leakage energy problem. Other topologies were derived from the half-bridge or push pull converters.

Advantages were addressed together with its tail-to-tail limitations.

#### **CHAPTER 3**

#### HALF-BRIDGE BUCK VOLTAGE REGULATOR

#### 3.1 Introduction

Intel roadmap predicts that future VRM will operate at low output voltage hitting the one Volt limit with an increase in current and power densities. Smaller output voltage translates into smaller duty cycle, and this impairs the efficiency of the converter due to the problems discussed in Chapter Two. In non-isolated topologies, D is used to decrease the output voltage. However, for very small output voltage requirements, D becomes very small, and this will result in high current and voltage stresses and therefore high switching losses. A transformer is embedded in non-isolated topologies to add another output voltage level control with an optimized D and therefore provide lower switching losses and higher efficiencies.

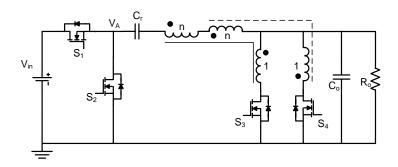

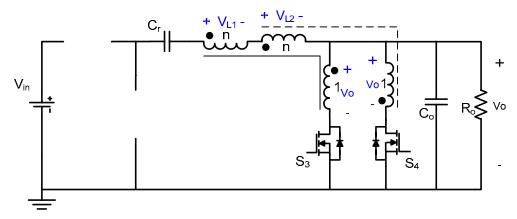

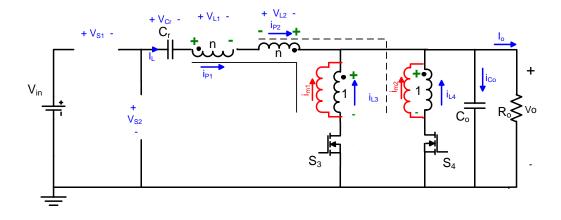

The Half-bridge Buck Converter (HBBC) presented in this chapter offers an added control parameter allowing an extended duty cycle for optimum operation and better efficiency. Figure 3.1.1 shows the circuit configuration for the HBBC.

Figure 3.1.1 Half-bridge Buck Converter Circuit Configuration

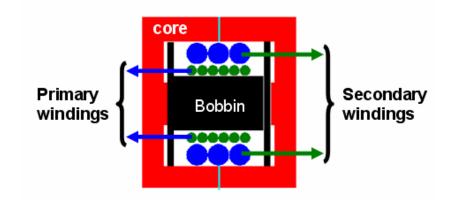

The HBBC incorporates two coupled inductors, and the turn ratio not only helps to reduce the output voltage by a factor equal to the reciprocal of the turn ratio, but it also increases the current supplied to the load by the secondary side of the transformer enhancing the transient response.

If compared to a conventional two-phase buck converter, the voltage across the lower switches  $S_3$  and  $S_4$ , shown in Figure 3.1.1, is lower by a factor of 1/n. This allows for the use of lower voltage MOSFETs with the advantage of lower  $R_{dson}$ , which decreases the conduction losses compared to a two-phase buck converter

The current at the primary side is decreased by 1/n, which also decreases the conduction losses of the upper switches  $S_1$  and  $S_2$ .

The blocking capacitor,  $C_{\rm r}$ , holds the average voltage,  $V_{\rm Cr}$ , according to the equation:  $V_{\rm Cr}=V_{\rm A}-V_{\rm o}$

Where:  $V_A$  is the average voltage of  $v_A$  at the phase node as shown in Figure 3.1.1, and it depends on the control type adopted, symmetric or asymmetric, which are analyzed in the following section.

## 3.2 Half-bridge Buck Control Schemes

# 3.2.1 Symmetric Half-bridge Buck Converter:

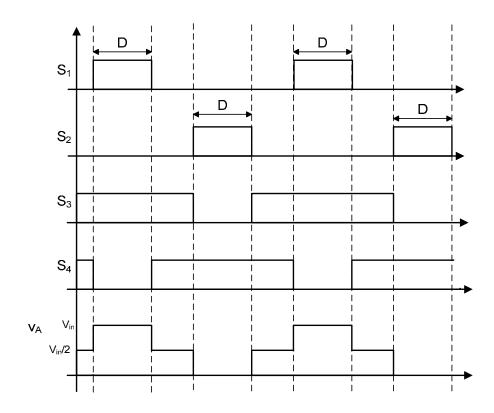

The switching waveforms of the symmetric HBBC are shown in Figure 3.2.1.

Figure 3.2.1 Switching Waveforms of the Symmetric Half-bridge Buck Converter

It can be shown that the average value of  $v_A$  is given by:

$$V_A = V_{in} \cdot D + \frac{V_{in}}{2} (1 - 2 \cdot D)$$

$$= V_{in} D + \frac{V_{in}}{2} - V_{in} D$$

$$= \frac{V_{in}}{2}$$

Therefore,

$$V_{Cr} = \frac{V_{in}}{2} - V_o$$

And this can be considered a voltage source of a value equal to  $\frac{V_{in}}{2} - V_o$ .

To derive the gain equation, we apply the voltage second balance across the inductors, and from the above waveforms, we can see that there are three different modes of operation: The first mode is when  $S_1$  is ON and  $S_2$  is OFF for the duration of DT. The second mode is when  $S_2$  is ON and  $S_1$  is OFF, and this mode lasts for the same duration of time as the first mode (DT), since the driving signals of the switches are symmetric. And the last mode is when both  $S_1$  and  $S_2$  are OFF. Also, the third mode repeats twice within one switching period, and therefore, the duration of the third mode is (1-2D) T.

#### Mode I (DT):

During this mode, S<sub>1</sub> and S<sub>3</sub> are ON as shown in Figure 3.2.2

Figure 3.2.2 Mode I of the Symmetric Half-bridge Buck Converter

The inductor voltages are given by the following relations

$$\begin{split} v_{L1} &= nV_o \\ v_{L2} &= V_{in} - V_{Cr} - nV_o - V_o \end{split}$$

Where  $V_{Cr}$  can be substituted by  $V_{Cr} = \frac{V_{in}}{2} - V_o$  to yield,

$$v_{L2} = \frac{V_{in}}{2} - nV_o$$

## Mode II (DT):

During this mode,  $S_2$  and  $S_4$  are ON as shown in Figure 3.2.3

Figure 3.2.3 Mode II of the Symmetric Half-bridge Buck Converter

In this mode, the inductor voltages can be written as;

$$\begin{split} v_{L2} &= -nV_o \\ v_{L1} &= -V_{Cr} + nV_o - V_o \end{split}$$

Where:

$$V_{Cr} = \frac{V_{in}}{2} - V_o$$

Therefore,

$$v_{L2} = \frac{-V_{in}}{2} + nV_o$$

## Mode III (1-2D)T:

Figure 3.2.4 Mode III of the Symmetric Half-bridge Buck Converter

In this mode,  $S_3$  and  $S_4$  are ON as shown in Figure 3.2.4 and the inductor voltages are expressed as;

$$v_{L1} = nV_o$$

$$v_{L2} = -nV_o$$

Applying the volt second balance on L1 or L2, we obtain:

$$nV_o D + (nV_o - \frac{V_{in}}{2})D + nV_o (1 - 2D) = 0$$

Hence, the voltage gain becomes;

$$\frac{V_o}{V_{in}} = \frac{D}{2n}$$

#### 3.2.2 Asymmetric Half-bridge Buck Converter:

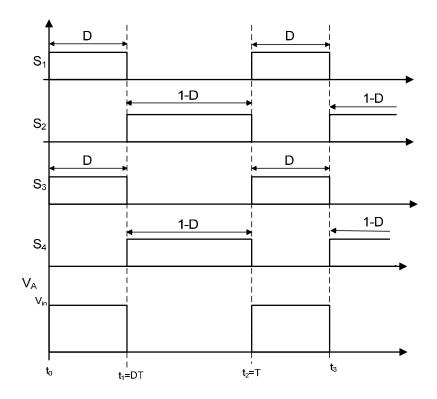

As opposed to the symmetric HBBC, the switching waveforms of the asymmetric HBBC are shown in Figure 3.2.5.

Figure 3.2.5 Switching Waveforms of the Asymmetric Half-bridge Buck Converter

Where the average voltage at the phase node in the Asymmetric HBBC is guven by:  $V_{A~asym} = V_{in} D$

Therefore, for the asymmetric case:  $V_{\rm Cr} = V_{\rm in} D - V_{\rm o}$

As noted in the asymmetric case, the blocking capacitor voltage depends on the duty cycle D, whereas on the symmetric case it is a constant value equal to  $\frac{V_{in}}{2} - V_o$ .

To derive the gain equation, we apply the volt second balance across the inductors. Also, we have two modes of operation as shown in Figure 2.3.5.

The first mode is when  $S_1$  is ON, and this mode continues for a period of time equal to DT. The second mode is when  $S_1$  is OFF and  $S_2$  is ON for duration of time equal to (1-D) T.

Applying the volt second balance for the inductors, we get the gain of the converter as shown below.

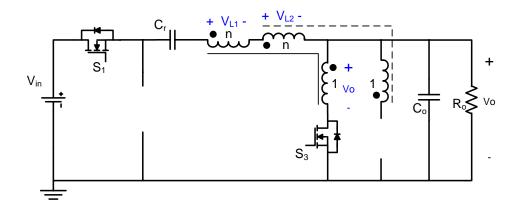

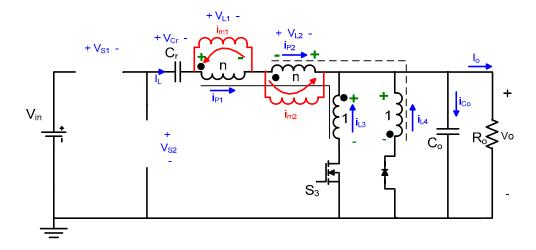

## Mode I: (DT)

In this mode,  $S_1$  and  $S_3$  are ON while  $S_2$  and  $S_4$  both are OFF. The equivalent circuit is shown in Figure 3.2.6:

Figure 3.2.6 Mode I of the Asymmetric Half-bridge Buck Converter

The inductor voltages are given by:

$$\begin{aligned} v_{L1} &= n \cdot V_o \\ v_{L2} &= V_{in} - V_{Cr} - nV_o - V_o \end{aligned}$$

## Mode II (1-D)T:

Figure 3.2.7 Mode II of the Asymmetric Half-bridge Buck Converter

$$\begin{aligned} v_{L2} &= -nV_o \\ v_{L1} &= -V_{Cr} + nV_o - V_o \end{aligned}$$

Where:

$$V_{Cr} = V_{in}D - V_o$$

Substituting  $V_{Cr}$  we get,  $v_{L1} = -V_{in}D + nV_o$

Applying the volt second balance on  $V_{L1}$  or  $V_{L2}$ , we get:

$$nV_{o}D + (nV_{o} - V_{in}D) \cdot (1 - D) = 0$$

The voltage gain in the Asymmetric HBBC can be written as:

$$\frac{V_o}{V_{in}} = \frac{D(1-D)}{n}$$

## 3.3 HBBC Modes of Operation

## 3.3.1 Symmetric Half-bridge

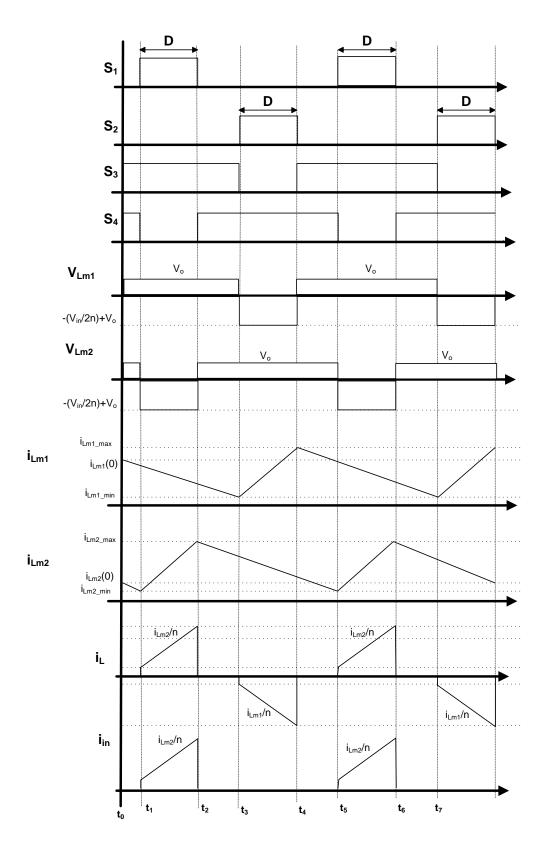

The Half-bridge Buck Converter will be analyzed in more depth in this section, and the symmetric HBBC will be examined prior to the asymmetric. Modes of operation and stress analysis are inspected for both control methods. Figure 3.3.1 shows key waveforms of the converter.

Figure 3.3.1 Key Waveforms of Symmetric Half-bridge Buck Converter

The modes of operation of the converter are as follows;

# **Mode I:** $(t_0 - t_1)$

| $S_1$ | $S_2$ | $S_3$ | $S_4$ |

|-------|-------|-------|-------|

| OFF   | OFF   | ON    | ON    |

Figure 3.3.2 Mode I In the Analysis of Symmetric Half-bridge Buck Converter

In this mode, the main switches are off and the energy in the magnetizing inductance will be trapped in the transformer. Whereas, the secondary currents  $i_{L3}$  and  $i_{L4}$ will supply the load current as shown in the following equations:

$$i_L = 0$$

$$v_{L3} = v_{Lm1} = V_o$$

$$v_{L4} = v_{Lm2} = V_o$$

The equations take into consideration the dot notation as shown in Figure 3.3.2.

Therefore:

$$v_{L1} = nV_o$$

$$v_{L2} = -nV_o$$

$$V_{L2} = -nV_o$$

Where the primary winding of the first transformer can be written as;

$$v_{p1} = v_{L1} = nV_{Lm1}$$

Similarly,

$$v_{p2} = v_{L2} = -nV_{Lm2}$$

The currents through the magnetizing inductance can be expressed as;

$$\begin{split} i_{m1} &= -\frac{V_o}{L_{m1}} \cdot t + I_{m1} \\ i_{m2} &= \frac{-V_o}{L_{m2}} \cdot t + I_{m2} \end{split}$$

Where:  $I_{m1}$  and  $I_{m2}$  are the initial conditions for the first and second magnetizing currents respectively.

The output capacitor current and the voltage across  $S_1$  and  $S_2$  are given by;

$$i_{Co} = i_{Lm1} + i_{Lm2} - I_o$$

and

$$v_{s1} = v_{s2} = \frac{V_{in}}{2}$$

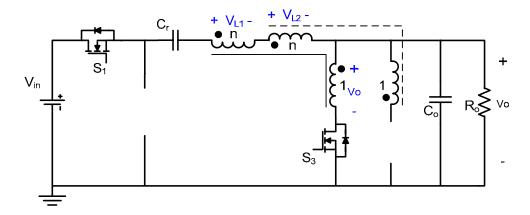

**Mode II:**  $(t_1 - t_2)$

| $S_1$ | $S_2$ | $S_3$ | $S_4$ |

|-------|-------|-------|-------|

| ON    | OFF   | ON    | OFF   |

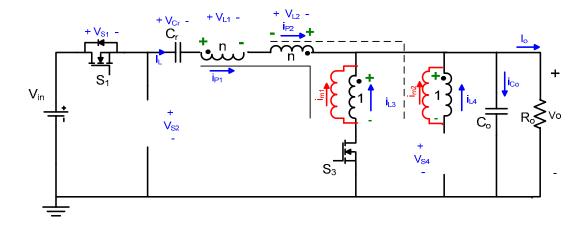

Figure 3.3.3 Mode II In the Analysis of Symmetric Half-bridge Buck Converter

The second inductor acts as an inductance making  $i_{p2} = 0$  and with  $S_4$  open,  $i_{L4} = 0$ .

$$i_{p2} = i_{L4} = 0$$

Examining Figure 3.3.3, the voltages across the inductors can be written as;

$$\begin{split} v_{L3} &= V_o \\ v_{L1} &= nV_o \\ v_{L2} &= V_{in} - V_{Cr} - v_{L1} - V_o \\ &= V_{in} - (\frac{V_{in}}{2} - V_o) - nV_o - V_o \\ &= \frac{V_{in}}{2} - nV_o \end{split}$$

The currents through the magnetizing inductances are given by;

$$i_{m1} = -\frac{V_o}{L_{m1}} \cdot (t - t_1) + i_{m1}(t_1)$$

$$i_{m2} = \frac{V_{in} - 2n \cdot V_o}{2nL_{m2}} \cdot (t - t_1) + i_{m2}(t_1)$$

The current  $i_L$  through the blocking capacitor  $C_r$ , and the output capacitor current  $i_{Co}$  are given as;

$$\begin{split} i_{L} &= \frac{i_{m2}}{n} \\ i_{Co} &= i_{m1} + i_{m2} + i_{L} - I_{o} \end{split}$$

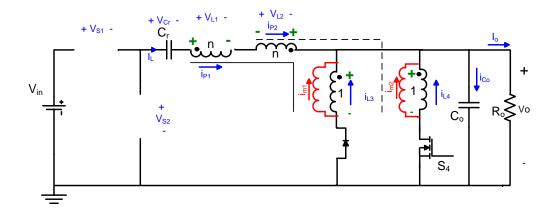

# **Mode III':** (t<sub>2</sub>- t<sub>2</sub>·)

| $S_1$ | $S_2$ | $S_3$ | $S_4$             |

|-------|-------|-------|-------------------|

| OFF   | OFF   | ON    | $OFF - D_{S4} ON$ |

Figure 3.3.4 Mode III' In the Analysis of Symmetric Half-bridge Buck Converter

In this mode,  $S_1$  is turned off and, before turning on  $S_4$ , the body diode of  $S_4$  starts conducting for a short period. It is not even shown in waveforms, which allows it to achieve ZVS for  $S_4$ . Then, when  $S_4$  is turned on with ZVS, we enter mode IV.

**Mode III:**  $(t_{2}, -t_{3})$ :

| $S_1$ | $S_2$ | $S_3$ | $S_4$ |

|-------|-------|-------|-------|

| OFF   | OFF   | ON    | ON    |

Figure 3.3.5 Mode III In the Analysis of Symmetric Half-bridge Buck Converter

Again, we enter a freewheeling mode in which the load current is supplied by the secondary sides, and the primary side traps the magnetizing currents. The first magnetizing current is negative, and the second one is positive. This mode is no more than the exact duplicate of Mode I, with the appropriate time shift of  $(t - t_2)$ .

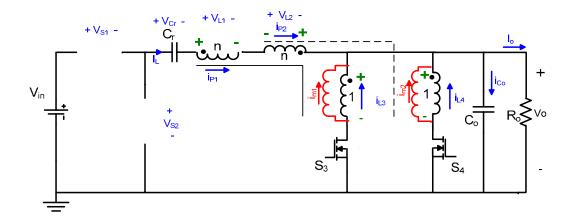

Figure 3.3.6 Mode IV In the Analysis of Symmetric Half-bridge Buck Converter

The first inductor acts as an inductance making  $i_{p1} = 0$  and with S<sub>3</sub> open,  $i_{L3} = 0$ .

$$i_{L3} = i_{P1} = 0$$

Examining Figure 3.3.6, the voltages across the inductors can be written as;

$$\begin{split} v_{L4} &= V_o = V_{Lm2} \\ v_{L2} &= -nV_o \\ v_{L1} &= -V_{Cr} - v_{L2} - V_o \\ &= -(\frac{V_{in}}{2} - V_o) + nV_o - V_o \\ &= -(\frac{V_{in}}{2}) + nV_o \end{split}$$

The currents through the magnetizing inductances are given by;

$$i_{Lm2} = -\frac{V_o}{L_{m2}} \cdot (t - t_3) + i_{m2}(t_3)$$

$$i_{m1} = \frac{+V_{in} - 2n \cdot V_o}{L_{m1}} \cdot (t - t_3) + i_{m1}(t_3)$$

We can notice that both magnetizing currents reverse their slope direction, where  $i_{m1}$  was negative, and now it is ramping up with a positive slope. The same applies on  $i_{m2}$  but in the opposite direction.

The current  $i_L$  through the blocking capacitor  $C_r$ , and the output capacitor current  $i_{Co}$  are given as;

$$i_{L} = \frac{i_{m2}}{n}$$

$$i_{Co} = i_{m1} + i_{m2} + i_{L} - I_{o}$$

## Mode V': $(t_4 - t_4')$ :

| $S_1$ | $S_2$ | $S_3$                   | $S_4$ |

|-------|-------|-------------------------|-------|

| OFF   | OFF   | OFF- D <sub>S3</sub> ON | ON    |

Figure 3.3.7 Mode V' In the Analysis of Symmetric Half-bridge Buck Converter

In this mode,  $S_2$  is turned off, and before turning on  $S_3$ , the body diode of  $S_3$  conducts in this mode which is a short period of time and is not shown in the waveforms.

This allows achieving ZVS for S3 and minimizing the body diode conduction losses, Then, when  $S_3$  is turned on with ZVS, we enter mode V and repeat the cycle.

Mode V:  $(t_4' - t_5)$

| $S_1$ | $S_2$ | $S_3$ | $S_4$ |

|-------|-------|-------|-------|

| OFF   | OFF   | ON    | ON    |

Figure 3.3.8 Mode V In the Analysis of Symmetric Half-bridge Buck Converter

Again, this mode is an exact duplicate of mode I, with the exception of the appropriate time shift that is now  $(t - t_4)$ .

As a summary of the voltage and current stresses across and through the switches, the Table 3.3.1 shows the voltages across the switches during turn off and the current through the switches while conducting.

Table 3.3.1 Voltage and Current Stress Analysis for the Symmetric HBBC

|       | Mode II         |                 | Mode I, III, V     |          | Mode IV         |                  |

|-------|-----------------|-----------------|--------------------|----------|-----------------|------------------|

|       | V.S.            | I.S.            | V.S.               | I.S.     | V.S.            | I.S.             |

| $S_1$ | 0               | i <sub>m2</sub> | V <sub>in</sub> /2 | 0        | V <sub>in</sub> | 0                |

| $S_2$ | V <sub>in</sub> | 0               | V <sub>in</sub> /2 | 0        | 0               | -i <sub>m1</sub> |

| $S_3$ | 0               | $i_{L3}$        | 0                  | $i_{L3}$ | $V_{in}/(2n)$   | 0                |

| $S_4$ | $V_{in}/(2n)$   | 0               | 0                  | $i_{L4}$ | 0               | $i_{L4}$         |

# 3.3.2 Asymmetric Half-bridge

## **Modes of Operation:**

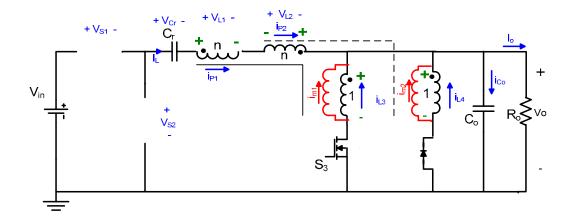

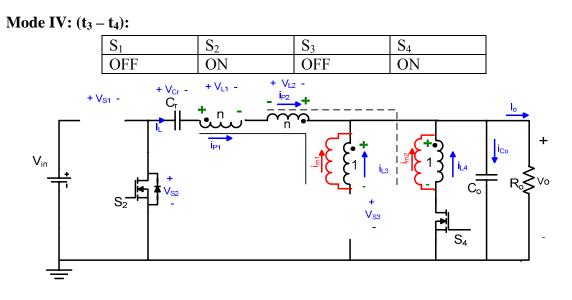

**Mode I:**  $(t_0 - t_1)$ :  $(t_0 - DT)$

| $S_1$ | $S_2$ | $S_3$ | $S_4$ |

|-------|-------|-------|-------|

| ON    | OFF   | ON    | OFF   |

Figure 3.3.9 Mode I In the Analysis of Asymmetric Half-bridge Buck Converter

The second inductor acts as an inductance making  $i_{p2} = 0$  and with S<sub>4</sub> open,  $i_{L4} = 0$ .

$$i_{p2} = i_{L4} = 0$$

Examining Figure 3.3.9, the voltages across the inductors can be written as;

$$\begin{split} v_{L3} &= V_o \\ v_{L1} &= nV_o \\ v_{L2} &= V_{in} - V_{Cr} - v_{L1} - V_o \\ &= V_{in} - (V_{in}D - V_o) - n \cdot V_o - V_o \\ &= V_{in} (1 - D) - n \cdot V_o \end{split}$$

The currents through the magnetizing inductances are given by;

$$\begin{split} i_{m1} &= -\frac{n \cdot V_o}{L_{m1}} \cdot t + I_{m1} \\ i_{m2} &= \frac{(V_{in}(1-D) - n \cdot V_o)}{L_{m2}} \cdot t + I_{m2} \\ i_{P1} &= i_{m1} + i_{m2} \end{split}$$

Where:  $I_{m1}$  and  $I_{m2}$  are the initial conditions of the first and second magnetizing inductances respectively.

The current through  $S_3$  is  $i_{L3} = n \cdot i_{P1}$

The current  $i_L$  through the blocking capacitor  $C_r$ , and the output capacitor current  $i_{Co}$  are given as;

$$\begin{split} i_L &= i_{m2} \\ i_{Co} &= i_{m2} + i_{L3} - I_o \end{split}$$

## **Mode II':** $(t_1 - t_{1'})$

| $S_1$ | $S_2$ | $S_3$ | $S_4$             |

|-------|-------|-------|-------------------|

| OFF   | OFF   | ON    | $OFF - D_{S4} ON$ |

Figure 3.3.10 Mode II' In the Analysis of Asymmetric Half-bridge Buck Converter

In this mode,  $S_1$  and  $S_3$  are turned off and before turning on  $S_4$ ; the body diode of  $S_4$  conducts in this mode for a short period of time and is not shown in waveforms, allowing it to achieve ZVS for  $S_4$ . Then, when  $S_2$  and  $S_4$  are turned on with ZVS for  $S_4$ , we enter mode II.

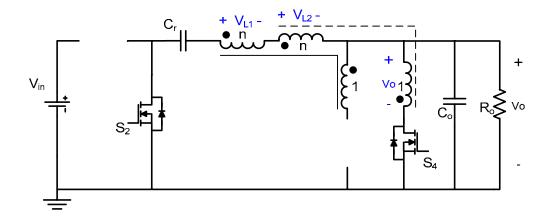

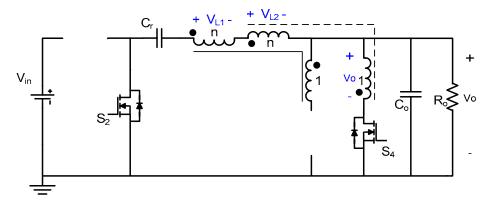

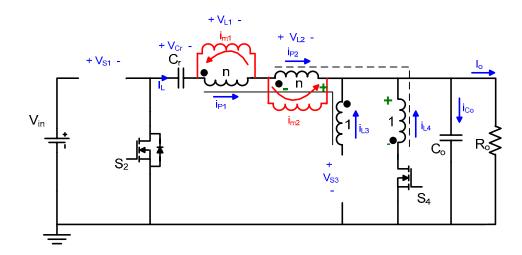

**Mode II:**  $(t_1' - t_2)$ :  $(t_1' - (1-D) T)$ :

| $S_1$ | $S_2$ | $S_3$ | $S_4$ |

|-------|-------|-------|-------|

| OFF   | ON    | OFF   | ON    |

Figure 3.3.11 Mode II In the Analysis of Asymmetric Half-bridge Buck Converter

The first inductor acts as an inductance making  $i_{pl} = 0$  and with S<sub>3</sub> open,  $i_{L3} = 0$ .

$$i_{L3} = i_{P1} = 0$$

Examining Figure 3.3.11, the voltages across the inductors can be written as;

$$\begin{split} v_{L4} &= V_o \\ v_{L2} &= -n \cdot V_o \\ v_{L1} &= -V_{Cr} - v_{L2} - V_o \\ &= -(V_{in}D - V_o) + nV_o - V_o \\ &= -V_{in}D + nV_o \end{split}$$

The currents through the magnetizing inductances are given by;

$$i_{m2} = -\frac{n \cdot V_o}{L_{m2}} \cdot t + i_{m2}(t_2)$$

$$i_{m1} = \frac{-V_{in}D + n \cdot V_o}{L_{m1}} \cdot t + i_{m1}(t_2)$$

$$i_{P2} = -(i_{m1} + i_{m2})$$

We can note that both magnetizing currents reversed their slope direction, where  $i_{m1}$  was negative and now it is ramped up with a positive slope. The same applies on  $i_{m2}$  but in the opposite direction.

$$i_{L4} = -n \cdot i_{P2}$$

The current  $i_L$  through the blocking capacitor  $C_r$ , and the output capacitor current  $i_{Co}$  are given as;

$$\begin{split} i_{L} &= -i_{m1} \\ i_{Co} &= -i_{m1} + i_{L4} - I_{o} \end{split}$$

The cycle repeats, and to illustrate the ZVS for  $S_3$  switch, another half cycle is discussed below.

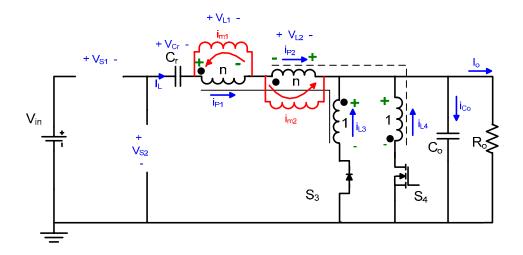

Mode I':  $(t_2 - t_{3'})$ :

| $S_1$ | $S_2$ | $S_3$             | $S_4$ |

|-------|-------|-------------------|-------|

| OFF   | OFF   | $OFF - D_{S3} ON$ | ON    |

Figure 3.3.12 Mode I' In the Analysis of Asymmetric Half-bridge Buck Converter

In this mode,  $S_2$  is turned off, and before turning on  $S_3$ , the body diode of  $S_3$  conducts. This mode should be short and is not shown in the waveforms, as the body diode conduction losses are high allowing it to achieve ZVS for  $S_3$ . Then when  $S_1$  and  $S_3$  are turned on with ZVS for  $S_3$ , the cycle is repeated, and we enter mode I again.

As a summary of the voltage and current stresses across and through the switches, Table 3.3.2 shows the voltages across the switches during turn off and the current through the switches while conducting.

Table 3.3.2 Voltage and Current Stress Analysis for the Asymmetric HBBC

|       | Mode I          |                 | Mode II             |                  |

|-------|-----------------|-----------------|---------------------|------------------|

|       | V.S.            | I.S.            | V.S.                | I.S.             |

| $S_1$ | 0               | i <sub>m2</sub> | $V_{in}$            | 0                |

| $S_2$ | V <sub>in</sub> | 0               | 0                   | -i <sub>m1</sub> |

| $S_3$ | 0               | $i_{L3}$        | V <sub>in</sub> D/n | 0                |

| $S_4$ | $V_{in}(1-D)/n$ | 0               | 0                   | $i_{L4}$         |

The focus of this work in centered on symmetric control for the benefit it offers of identical transformer design, which facilitates the magnetic design.

It is clear from the above discussion that the asymmetric half-bridge will need different magnetizing inductances to compensate for the difference in the period during which they store energy. This will complicate the analysis and is subject to future investigation.

Duty Cycle Shift (DCS) is another attractive control scheme in which Zero Voltage Switching can be achieved on  $S_1$  and  $S_2$ , which further reduces the switching losses and increases efficiency. Again, this control scheme is not covered in this work and falls in the scope of future analysis.

# 3.4 Simulation Results

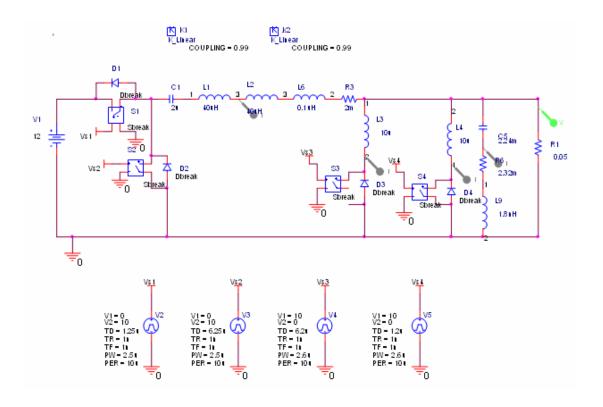

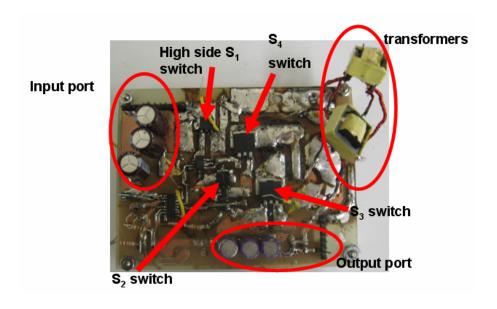

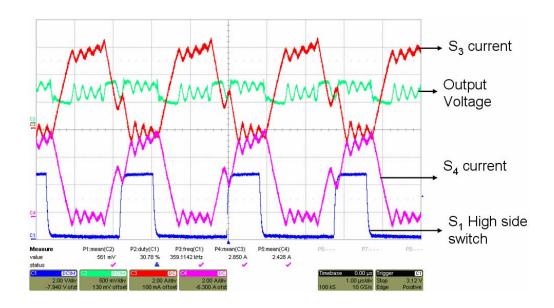

The HBBC circuit is simulated and some waveforms are shown in Figures 3.4.1 and 3.4.2:

Figure 3.4.1 Simulation Circuit for a Symmetric HBBC

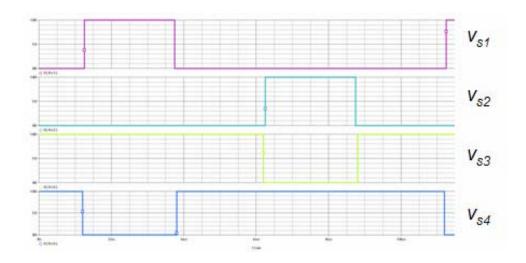

The switching signals  $v_{S1}$ ,  $v_{S2}$ ,  $v_{S3}$  and  $v_{S4}$  are shown in Figure 3.4.2 with a small dead time to allow ZVS for  $S_3$  and  $S_4$  as explained in the modes of operation.

Figure 3.4.2 Switching Waveforms Simulation Result for a Symmetric HBBC

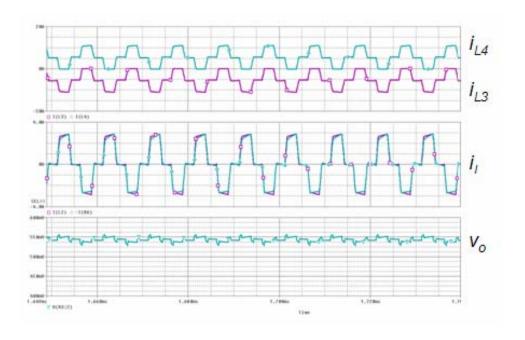

Some other waveforms of interest are as shown in Figure 3.4.3.

Figure 3.4.3 Simulation Results for a Symmetric HBBC

## 3.5 Turns Ratio vs. Efficiency

The microprocessor industry is moving towards lowering the output voltage for faster data transfer and lower power consumption together with increasing the current and the power density. The target of the industry now is to feed the processor with as little as one Volt.