University of Central Florida

STARS

Electronic Theses and Dissertations, 2004-2019

2007

# Integrated Topologies And Digital Control For Satellite Power Management And Distribution Systems

Hussam Al-Atrash University of Central Florida

Part of the Electrical and Electronics Commons Find similar works at: https://stars.library.ucf.edu/etd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

### **STARS Citation**

Al-Atrash, Hussam, "Integrated Topologies And Digital Control For Satellite Power Management And Distribution Systems" (2007). *Electronic Theses and Dissertations, 2004-2019.* 3055. https://stars.library.ucf.edu/etd/3055

## INTEGRATED TOPOLOGIES AND DIGITAL CONTROL FOR SATELLITE POWER MANAGEMENT AND DISTRIBUTION SYSTEMS

by

### HUSSAM J. AL-ATRASH B.S. University of Jordan, 2003 M.S.E.E. University of Central Florida, 2005

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the School of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Summer Term 2007

Major Professor: Issa Batarseh

© 2007 Hussam J. Al-Atrash

### ABSTRACT

This work is focused on exploring advanced solutions for space power management and distribution (PMAD) systems. As spacecraft power requirements continue to increase, paralleled by the pressures for reducing cost and overall system weight, power electronics engineers will continue to face major redesigns of the space power systems in order to meet such challenges. Front-end PMAD systems, used to interface the solar sources and battery backup to the distribution bus, need to be designed with increased efficiency, reliability, and power density.

A new family of integrated single-stage power converter structures is introduced here. This family allows the interface and control of multiple power sources and storage devices in order to optimize utilization of available resources. Employing single-stage power topologies, these converters control power flow efficiently and cost-effectively. This is achieved by modifying the operation and control strategies of isolated soft-switched half-bridge and fullbridge converters—two of the most popular two-port converter topologies. These topologies are reconfigured and utilized to realize three power processing paths. These paths simultaneously utilize the power devices, allowing increased functionality while promising reduced losses and enhanced power densities.

Each of the proposed topologies is capable of performing simultaneous control of two of its three ports. Control objectives include battery or ultra-capacitor charge regulation, solar array maximum power point tracking (MPPT), and/or bus voltage regulation. Another advantage of the proposed power structure is that current engineering design concepts can be used to optimize the new topologies in a fashion similar to the mother topologies. This includes component selection and magnetic design procedures, as well as achieving soft-switching for increased efficiency at higher switching frequencies. Galvanic isolation of the load port through high-frequency transformers provides design flexibility for high step-up/step-down conversion ratios. It further allows the converters to be used as power electronics building blocks (PEBB) with outputs connected in different series/parallel combinations to meet different load requirements. Utilizing such converters promises significant savings in size, weight, and costs of the power management system as well as the devices it manages.

Chapter 1 of this dissertation provides an introduction to the requirements, challenges, and trends of space PMAD. A review of existing multi-port converter technologies and digital control techniques is given in Chapter 2. Chapter 3 discusses different PMAD system architectures. It outlines the basic concepts used for PMAD integration and discusses the potential for improvement. Chapters 4 and 5 present and discuss the operation and characteristics of three different integrated multi-port converters. Chapter 6 presents improved methods for practical digital control of switching converters, which are especially useful in complex multi-objective controllers used for PMAD. This is followed by conclusions and suggested future work.

To those who fear but dare to stand, and those who grieve but dare to smile.

To the land of sad oranges...

### ACKNOWLEDGEMENTS

I wish to express deep gratitude to all people and firms that contributed to the work presented in this dissertation. I am particularly indebted to my advisor, Dr. Issa Batarseh, for his numerous discussions and unwavering support and guidance. I thank Drs. John Shen, Jiann-shiun Yuan, and Christopher Iannello for serving on my committee and providing helpful comments.

The work presented here is a result of a collaborative effort between the Florida Power Electronics Center (FloridaPEC) at the University of Central Florida (UCF) and the Advanced Power Electronics Corporation (APECOR). This effort was partially funded by the National Aeronautics and Space Administration - Glenn Research Center (NASA-GRC) under Small Business Innovation Research (SBIR) Phase I contract #NNC07QA26P. Team members from UCF and APECOR have made critical contributions to the success of this effort. The diligent work of Feng Tian, Rene Kersten, Michael Pepper, Justin Reese, Khalid Rustom, Osama Abdel-Rahman, and Adje Mensah is highly appreciated.

Hussam Al-Atrash

July 2007

## TABLE OF CONTENTS

| LIST OF FIGU | RES                                                                  | xii     |

|--------------|----------------------------------------------------------------------|---------|

| LIST OF TABL | JES                                                                  | xvii    |

| LIST OF ACRO | DNYMS                                                                | xviii   |

| CHAPTER 1:   | INTRODUCTION                                                         | 1       |

| 1.1.         | Trends and Challenges of Satellite Power Management and Distribution | on 1    |

| 1.1.1.       | Photovoltaics and Maximum Power Point Tracking                       | 2       |

| 1.1.2.       | Batteries and Battery Management                                     | 4       |

| 1.1.3.       | Power Management and Distribution                                    | 6       |

| CHAPTER 2:   | REVIEW OF MULTI-PORT CONVERTERS AND                                  | DIGITAL |

| CONTROL TE   | CHNIQUES                                                             |         |

| 2.1.         | Multi-Port Converter Technologies                                    |         |

| 2.1.1.       | Integrated Multi-Input Converters                                    | 13      |

| 2.1.2.       | Isolated Bidirectional Multi-Port Converters                         | 17      |

| 2.1.3.       | Integrated Power Factor Correction Converters                        | 19      |

| 2.2.         | Digital Control of Switching Power Converters                        |         |

| CHAPTER 3:   | THREE-PORT CONVERTER SYSTEM INTEGRATION                              |         |

| 3.1.         | Integration Objectives                                               |         |

| 3.1.1.       | Objectives for the Power Stage                                       |         |

| 3.1.2.       | Control Objectives                                                   |         |

| 3.1.3.     | Modularity Objectives                                         | 26 |

|------------|---------------------------------------------------------------|----|

| 3.2.       | Topology Integration Approach                                 | 27 |

| 3.2.1.     | Unity of Power Topologies                                     | 27 |

| 3.2.2.     | Savings Potential                                             | 30 |

| 3.2.3.     | Attractive Conventional Topologies                            | 32 |

| 3.2.3.1    | The Duty-Cycle Shifted Half-Bridge Converter                  | 32 |

| 3.2.3.2    | The Phase-Shift Full-Bridge Converter                         | 33 |

| 3.3.       | Three-Port Topology Options                                   | 34 |

| 3.3.1.     | The Tri-Modal Half-Bridge Converter                           | 34 |

| 3.3.2.     | Boost-Integrated Phase-Shift Full-Bridge Converters           | 35 |

| 3.4.       | Control Aspects of Multi-Port Systems                         | 37 |

| 3.4.1.     | Control Objectives, and Degrees of Freedom                    | 37 |

| 3.4.2.     | Operating Modes of a Battery-Backed Photovoltaic Power System | 38 |

| 3.4.2.1    | Sample Control Structure                                      | 39 |

| CHAPTER 4: | TRI-MODAL HALF-BRIDGE CONVERTER                               | 41 |

| 4.1.       | Modes of Operation and Steady-State Analysis                  | 42 |

| 4.1.1.     | Regular Operating Modes                                       | 43 |

| 4.1.2.     | Irregular Operating Modes                                     | 44 |

| 4.2.       | Component Stress and Design Considerations                    | 44 |

| 4.2.1.     | Magnetizing Current                                           | 44 |

| 4.2.2.     | Semiconductor Stress                                          | 45 |

| 4.2.3.     | Selecting the Transformer Turns' Ratio                        | 46 |

| 4.2.4.     | Driving Considerations                                        | 48 |

| 4.3.       | Control Strategy                     |                  |             |

|------------|--------------------------------------|------------------|-------------|

| 4.4.       | Experimental Verification            |                  |             |

| CHAPTER 5: | BOOST-INTEGRATED                     | PHASE-SHIFT      | FULL-BRIDGE |

| CONVERTERS |                                      |                  |             |

| 5.1.       | Symmetric Boost-Integrated Phase-Shi | ft Full-Bridge   |             |

| 5.1.1.     | Operation and Steady-State Analysi   | s                |             |

| 5.1.2.     | Semiconductor Stress Analysis        |                  | 61          |

| 5.1.3.     | Zero-Voltage Switching               |                  |             |

| 5.1.3.1    | Switches (a) and (b): Leading Le     | eg Switches      |             |

| 5.1.3.2    | Switch (c) and (d): Lagging Leg      | Switches         |             |

| 5.1.4.     | Power Loss Estimation                |                  |             |

| 5.1.4.1    | Conduction loss                      |                  |             |

| 5.1.4.2    | Switching Loss                       |                  |             |

| 5.2.       | Asymmetric Boost-Integrated Phase-Sl | nift Full-Bridge |             |

| 5.2.1.     | Operation and Steady-State Analysi   | S                |             |

| 5.2.2.     | Semiconductor Stress Analysis        |                  |             |

| 5.2.3.     | Zero-Voltage Switching               |                  |             |

| 5.2.3.1    | Switches (a) and (b): Leading Le     | eg Switches      |             |

| 5.2.3.2    | Switch (c) and (d): Lagging Leg      | Switches         |             |

| 5.2.4.     | Power Loss Estimation                |                  |             |

| 5.2.4.1    | Conduction Loss                      |                  |             |

| 5.2.4.2    | Switching Loss                       |                  |             |

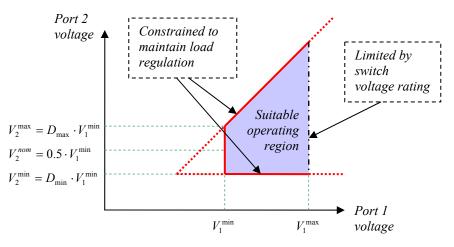

| 5.3.       | Port Voltage Considerations          |                  |             |

| 5.3.1.     | The Symmetric Case                                                | 72  |

|------------|-------------------------------------------------------------------|-----|

| 5.3.2.     | The Asymmetric Case                                               | 73  |

| 5.3.3.     | Recommended Port Voltages                                         | 74  |

| 5.4.       | Topology Comparison and Selection Guidelines                      | 75  |

| 5.4.1.     | Chopper Switch Conduction Loss                                    | 76  |

| 5.4.1.1    | Typical Design Scenario                                           | 78  |

| 5.4.2.     | Rectifier Diode Voltage Stress                                    | 80  |

| 5.4.3.     | ZVS Operation of Chopper FETs                                     | 82  |

| 5.4.4.     | Comparison Summary                                                | 85  |

| 5.5.       | Control Strategy and Controller Design                            | 85  |

| 5.5.1.     | Sample Control Structure                                          | 85  |

| 5.5.2.     | Controller Design                                                 | 87  |

| 5.6.       | Experimental Verification                                         | 88  |

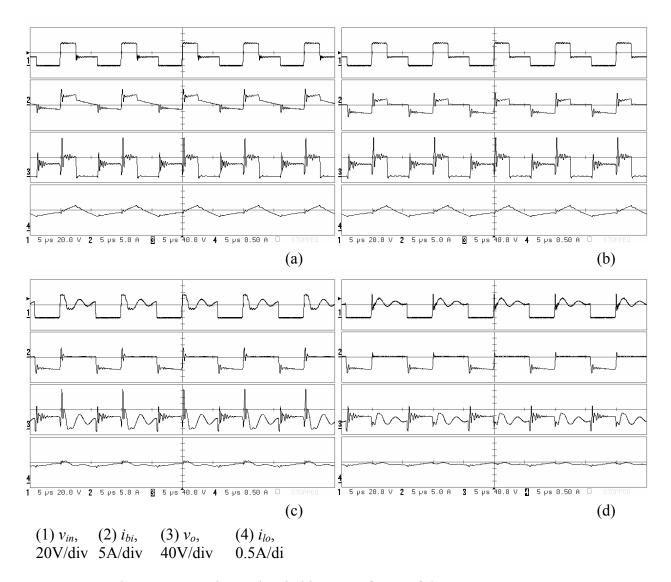

| 5.6.1.     | Switching and ZVS Waveforms                                       | 90  |

| 5.6.1.1    | The Symmetric Case                                                | 90  |

| 5.6.1.2    | The Asymmetric Case                                               | 92  |

| 5.6.2.     | Experimental Efficiency Comparison                                | 94  |

| 5.6.3.     | Controller Response                                               | 98  |

| CHAPTER 6: | IMPROVED DIGITAL CONTROLLER DESIGN                                | 100 |

| 6.1.       | Direct-Digital Controller Design in the Analog Frequency Domain   | 100 |

| 6.1.1.     | Digital Zero/Pole Families                                        | 102 |

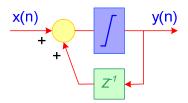

| 6.1.2.     | Integrators                                                       | 106 |

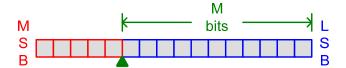

| 6.2.       | Number Representation and Arithmetic in a Fixed-Point Environment | 106 |

| 6.2.1.     | Referenced Interpretation of Binary Values                  | 107 |

|------------|-------------------------------------------------------------|-----|

| 6.2.2.     | Referencing Rules and Guidelines                            |     |

| 6.3.       | Modeling and Implementation of Digital Controller Functions | 110 |

| 6.3.1.     | Analog-to-Digital Converter Model                           |     |

| 6.3.2.     | Pulse-Width Modulator Model                                 |     |

| 6.3.3.     | Digital-to-Analog Converter Models                          |     |

| 6.3.3.1    | Dedicated DAC                                               |     |

| 6.3.3.2    | PWM DAC                                                     |     |

| 6.3.4.     | Delay and Zero-Order Hold Models                            |     |

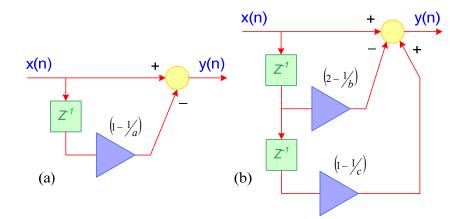

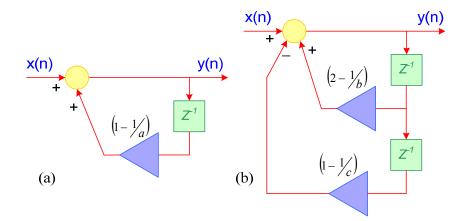

| 6.3.5.     | Implementation of Compensator Zeros, Poles, and Integrators |     |

| 6.4.       | Design Example: Synchronous Buck Voltage Regulator          | 116 |

| 6.4.1.     | Loop Modeling and Compensator Design                        | 117 |

| 6.4.2.     | Controller Coding                                           |     |

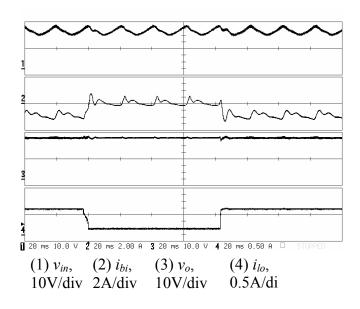

| 6.5.       | Experimental Results                                        |     |

| CHAPTER 7: | SUMMARY AND FUTURE WORK                                     |     |

| 7.1.       | Summary                                                     |     |

| 7.2.       | Future Work                                                 |     |

| REFERENCES |                                                             |     |

## LIST OF FIGURES

| Figure 1 Typical -normalized- terminal characteristics of solar arrays                       |

|----------------------------------------------------------------------------------------------|

| Figure 2 Unregulated bus topology                                                            |

| Figure 3 Regulated bus topology                                                              |

| Figure 4 Battery-dominated MPPT bus topology                                                 |

| Figure 5 Two-stage fully-regulated PMAD topology                                             |

| Figure 6 Fully-regulated PMAD topologies with bidirectional battery chargers 10              |

| Figure 7 Fully-regulated PMAD with independent battery charging/discharging 11               |

| Figure 8 Bidirectional multi-input converter system for HEVs [16]                            |

| Figure 9 Topology of the two-input tri-state dc-dc converter [18]14                          |

| Figure 10 A multi-input flyback converter [19] 14                                            |

| Figure 11 A multi-input buck-boost converter [20] 15                                         |

| Figure 12 A multi-input multi-output flyback converter [21] 15                               |

| Figure 13 A two-input isolated boost converter [22]                                          |

| Figure 14 Triple-voltage bus dc-dc converter [23]17                                          |

| Figure 15 Bidirectional magnetically coupled multi-port converter [24] 18                    |

| Figure 16 The construction of isolated bidirectional multi-port converters using full-bridge |

| structures [25]                                                                              |

| Figure 17 PFC converters integrating a boost and a PS-FB stage [26-29]                       |

| Figure 18 Constraining the voltage of the bulk capacitor using combined duty-cycle and phase-     |

|---------------------------------------------------------------------------------------------------|

| shift control                                                                                     |

| Figure 19 The frequency response of an analog zero and several digital approximations             |

| Figure 20 Typical loop frequency response with an analog controller and its digital redesigns 22  |

| Figure 21 NASA's SCBR configuration [41]                                                          |

| Figure 22 PEBB approach applied to three-port converters                                          |

| Figure 23 Typical functions of a phase-leg                                                        |

| Figure 24 Unity of (a) buck, (b) active clamp forward, and (c) half-bridge converter topologies29 |

| Figure 25 Savings potential of the proposed topology integration approach                         |

| Figure 26 Soft-switched DCS-HB converter with auxiliary branch                                    |

| Figure 27 The PS-FB converter                                                                     |

| Figure 28 The TM-HB converter                                                                     |

| Figure 29 The A-BI-PS-FB converter                                                                |

| Figure 30 The S-BI-PS-FB converter                                                                |

| Figure 31 Sample controller structure for a battery-backed solar power system                     |

| Figure 32 The TM-HB converter                                                                     |

| Figure 33 Basic switching waveforms of the TM-HB converter                                        |

| Figure 34 Turns' ratio design curves                                                              |

| Figure 35 Suggested control structure for battery-balanced operation of a solar power system. 50  |

| Figure 36 Small signal dynamic model structure of the closed-loop system                          |

| Figure 37 Experimental TM-HB prototype                                                            |

| Figure 38 Experimental switching waveforms of the TM-HB converter                                 |

| Figure 39 Load transient under closed-loop operation                                              |

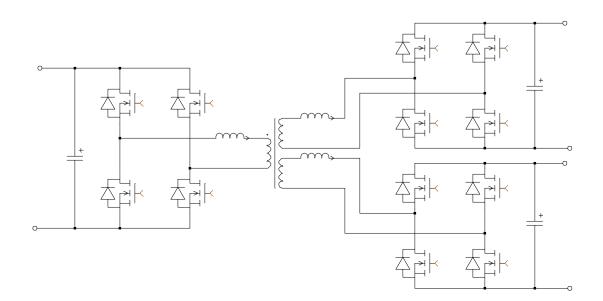

| Figure 40 The S-BI-PS-FB converter                                                    | 58   |

|---------------------------------------------------------------------------------------|------|

| Figure 41 Steady-state switching waveforms of the S-BI-PS-FB topology                 | 59   |

| Figure 42 The A-BI-PS-FB converter                                                    | 65   |

| Figure 43 Steady-state switching waveforms of the A-BI-PS-FB topology                 | 66   |

| Figure 44 Relation of suitable operating voltages                                     | 75   |

| Figure 45 Equivalent conventional cascaded system                                     | 76   |

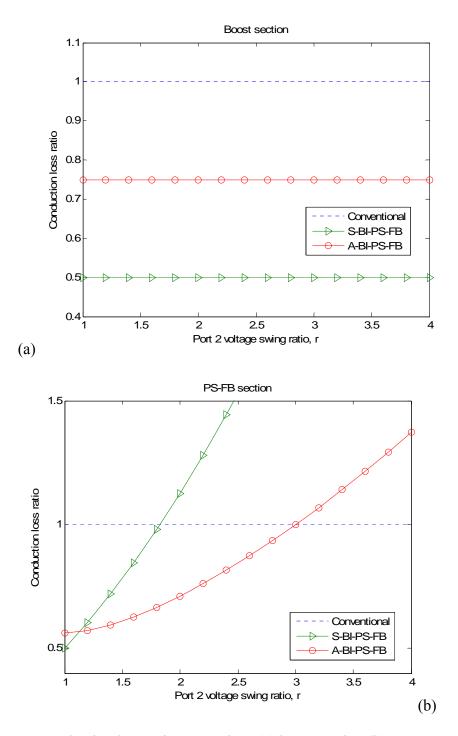

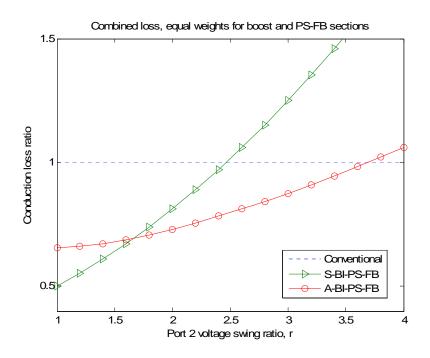

| Figure 46 Conduction loss ratio comparison (a) boost section (b) PS-FB section        | 79   |

| Figure 47 Conduction loss ratio comparison assuming equal utilization of boost and Pa | S-FB |

| sections                                                                              | 80   |

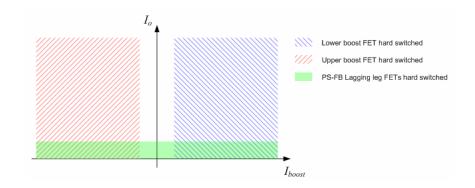

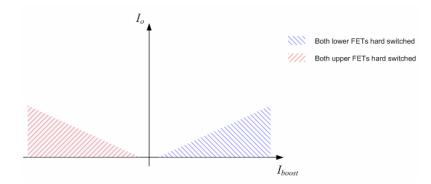

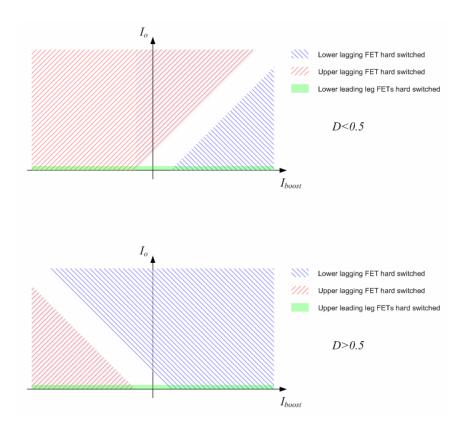

| Figure 48 ZVS profile of the conventional cascaded system                             | 83   |

| Figure 49 ZVS profile of the S-BI-PS-FB converter                                     | 83   |

| Figure 50 ZVS profile of the A-BI-PS-FB converter with (a) D<0.5 (b) D>0.5            | 84   |

| Figure 51 Sample controller structure for a battery-backed solar power system         | 86   |

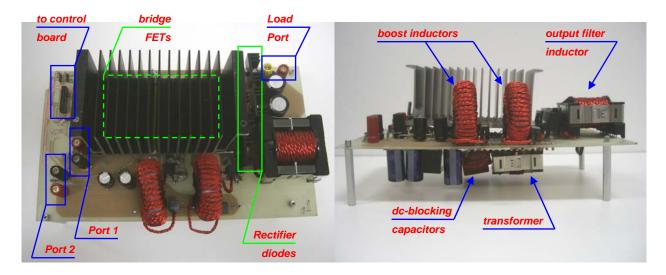

| Figure 52 Experimental test-bed                                                       | 89   |

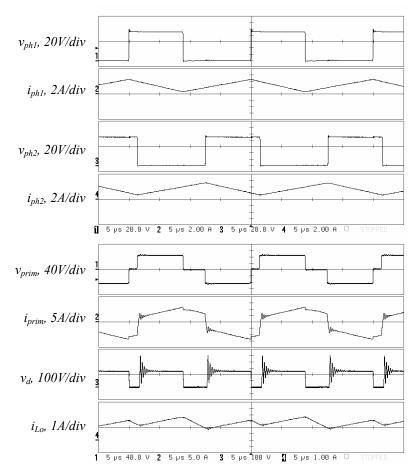

| Figure 53 Switching waveforms of the S-BI-PS-FB converter                             | 91   |

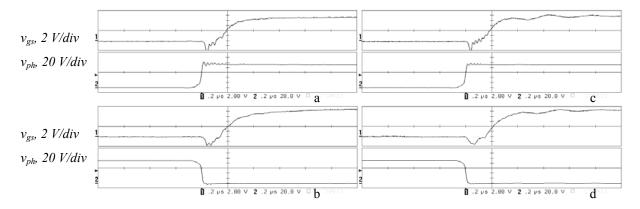

| Figure 54 ZVS waveforms of the S-BI-PS-FB converter                                   | 92   |

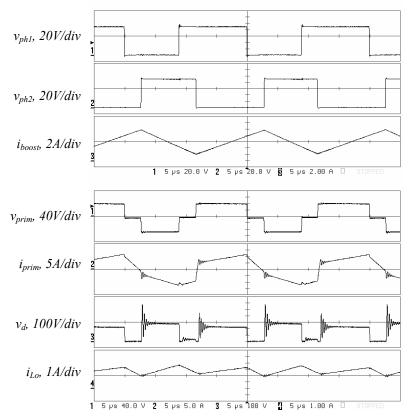

| Figure 55 Switching waveforms of the A-BI-PS-FB converter                             | 93   |

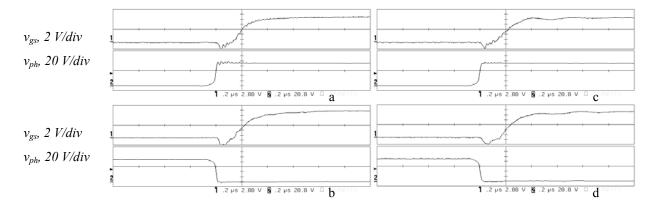

| Figure 56 ZVS waveforms of the A-BI-PS-FB converter                                   | 94   |

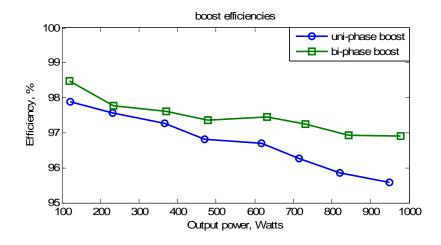

| Figure 57 Efficiency comparison of uni- and bi-phase boost converters                 | 95   |

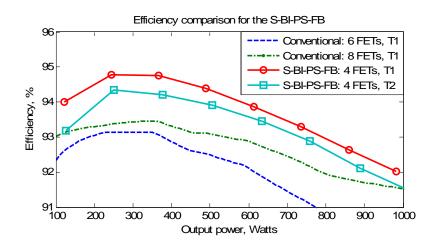

| Figure 58 Efficiency comparison of PS-FB converters using transformers T1 and T2      | 96   |

| Figure 59 Efficiency comparison of the S-BI-PS-FB converter to the conventional case  | aded |

| system                                                                                | 97   |

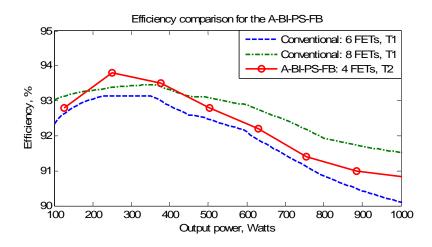

| Figure 60 Efficiency comparison of the A-BI-PS-FB converter to the conventional  | cascaded |

|----------------------------------------------------------------------------------|----------|

| system                                                                           |          |

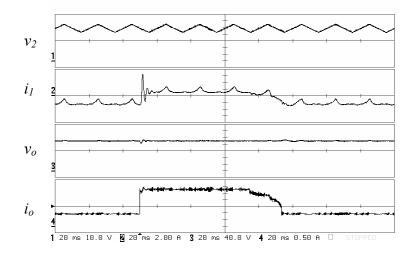

| Figure 61 Experimental response of the close-loop system to a load transient     |          |

| Figure 62 Frequency response of common feedback loop components                  | 101      |

| Figure 63 Frequency response of first order digital zeros                        | 103      |

| Figure 64 Frequency response of "hard" complex conjugate zero pairs              | 104      |

| Figure 65 Frequency response of a family of "soft" complex conjugate zero pairs  | 105      |

| Figure 66 Number representation in rM format                                     | 107      |

| Figure 67 Implementation of digital zeros (a) first order (b) soft complex pairs |          |

| Figure 68 Implementation of digital poles (a) first order (b) soft complex pairs | 115      |

| Figure 69 Implementation of a limited Euler integrator                           | 116      |

| Figure 70 Layout of the closed-loop system                                       | 117      |

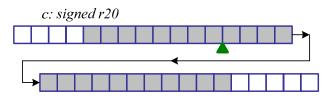

| Figure 71 Theoretical closed-loop frequency response for a $2.5\Omega$ load      | 120      |

| Figure 72 Simulated closed-loop response to a 2-6A load transient                | 120      |

| Figure 73 Controller implementation layout                                       | 121      |

| Figure 74 Controller software "blueprint"                                        | 122      |

| Figure 75 Difference signal in signed r15 format within a 16-bit register        | 123      |

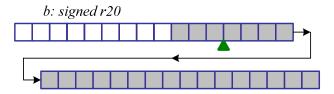

| Figure 76 A controller state in signed r20 format within a 16-bit register       | 123      |

| Figure 77 A compensator state in signed r20 format within a 32-bit register      | 124      |

| Figure 78 Compensator output in signed r20 format within a 32-bit register       | 124      |

| Figure 79 Integrator input in signed r20 format within a 32-bit register         | 125      |

| Figure 80 The digital controller blueprint translated into C-language code       | 127      |

| Figure 81 Experimental closed-loop frequency response for a 2.5Ω load            | 128      |

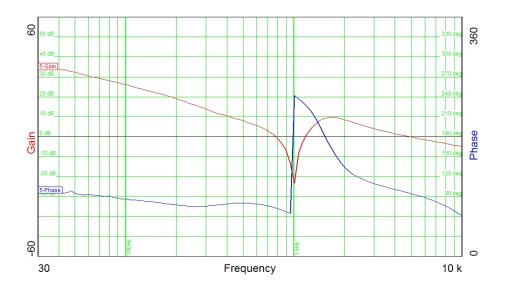

| Figure 82 Experimental closed-loop response to a 2-6A load transier | t 128 |

|---------------------------------------------------------------------|-------|

|---------------------------------------------------------------------|-------|

## LIST OF TABLES

| Table 1 Components used in the converters tested    89 |

|--------------------------------------------------------|

|--------------------------------------------------------|

## LIST OF ACRONYMS

| A-BI-PS-FB | Asymmetric boost-integrated phase-shift full-bridge |

|------------|-----------------------------------------------------|

| Ac         | Alternating current                                 |

| ADC        | Analog-to-digital converter                         |

| APECOR     | Advanced Power Electronics Corporation              |

| ASIC       | Application-specific integrated circuit             |

| ССМ        | Continuous conduction mode                          |

| DAC        | Digital-to-analog converter                         |

| Dc         | Direct current                                      |

| DCM        | Discontinuous conduction mode                       |

| DCS-HB     | Duty-cycle shifted half-bridge                      |

| DSP        | Digital signal processor                            |

| EMI        | Electromagnetic interference                        |

| FET        | Field effect transistor                             |

| FloridaPEC | Florida Power Electronics Center                    |

| FPGA       | Field-programmable gate array                       |

| HEV        | Hybrid-electric vehicle                             |

| IC         | Integrated circuit                                  |

| IGBT       | Insulated gate bipolar transistor                   |

| IncCond    | Incremental conductance                             |

| IVR        | Input voltage regulation                                              |

|------------|-----------------------------------------------------------------------|

| LHS        | Left-hand side                                                        |

| LPF        | Low-pass filter                                                       |

| LSB        | Least significant bit                                                 |

| MPP        | Maximum power point                                                   |

| MPPT       | Maximum power point tracking                                          |

| MSB        | Most significant bit                                                  |

| NASA-GRC   | National Aeronautics and Space Administration - Glenn Research Center |

| OVR        | Output voltage regulation                                             |

| PEBB       | Power electronics building block                                      |

| PFC        | Power factor correction                                               |

| PMAD       | Power management and distribution                                     |

| PnO        | Perturb and observe                                                   |

| POL        | Point-of-load                                                         |

| PS-FB      | Phase-shift full-bridge                                               |

| PWM        | Pulse-width modulation                                                |

| RHS        | Right-hand side                                                       |

| Rms        | Root-mean square                                                      |

| S-BI-PS-FB | Symmetric boost-integrated phase-shift full-bridge                    |

| SBIR       | Small Business Innovation Research                                    |

| SCBR       | Series-Connected Boost Regulator                                      |

| TM-HB      | Tri-modal half-bridge                                                 |

| UCF        | University of Central Florida                                         |

- ZOH Zero-order hold

- ZVS Zero voltage switching

### CHAPTER 1: INTRODUCTION

The Sun provides the energy necessary to support life on Earth. Thousands of miles above, it remains the primary source of energy. Solar radiation is the most abundant, convenient, and reliable source of energy for satellite systems. Battery energy storage is utilized in order to accommodate the mismatch between solar power availability and loading profiles.

The ever-increasing cost of launching a spacecraft into space, approximately \$100,000/kg, is a major driving force behind the efforts to minimize the volume and weight of the different systems it comprises [1]. It is generally accepted that the platform power system constitutes around 25% of the total dry spacecraft mass, while the battery and the solar arrays account for 90% of the power system mass [2]. In this light, highly optimized utilization of the solar source and batteries is an important design concern. This calls for the use of flexible PMAD systems with advanced control.

### 1.1. Trends and Challenges of Satellite Power Management and Distribution

The state-of-the-art, trends, and challenges relating to the different components of satellite PMAD systems are discussed in this section.

#### 1.1.1. Photovoltaics and Maximum Power Point Tracking

Photovoltaic (solar) cells are semiconductor devices capable of producing voltage and associated current when exposed to light. Solar cell technology has made significant progress over the last few decades. Crystalline silicon, both mono- and multi-crystalline, dominates the solar cell industry. This material is a poor absorber of light and requires a large thickness, but yields stable solar cells with good efficiencies (11-16%) and uses process technology developed from the vast knowledge base of the microelectronics industry [3]. Thin film technologies were developed to reduce cost by utilizing materials with better light absorption. Thin film materials include amorphous silicon and the polycrystalline materials: cadmium telluride and copper indium (gallium) diselenide. This technology still faces challenges in manufacturability, durability, and efficiency (5-8%). The potential for lower cost remains the main drive for thin film solar cells.

For space solar cells, constraints on size, weight, and reliability are far more critical than manufacturing cost. This has escalated the interest in complex high-efficiency cells for space applications. Multi-junction solar cell technologies target a wider portion of the incident spectrum and promise efficiencies in excess of 30% [4, 5]. The development of nano-materials also holds potential for the future.

The voltage-current relationship of a typical solar array is given by Equation (1.1): [6]

$$I = I_{photo} - I_o \cdot \left( \exp\left[\frac{q}{AKT} \cdot \left(V + I \cdot R_{series}\right)\right] - 1 \right) - \frac{V}{R_{shunt}}$$

(1.1)

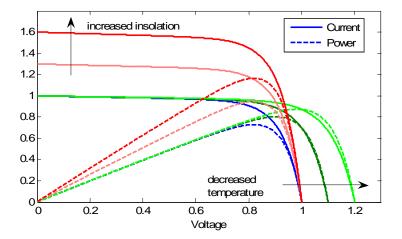

where  $I_{photo}$  is the photo current generated due to insolation,  $I_o$  is the reverse saturation current of semiconductor material,  $R_{series}$  represents series ohmic resistance of the cell,  $R_{shunt}$ accounts for leakage current, K is Boltzman's constant, T is the absolute operating temperature, q is the charge of a single electron, and *A* is an ideality factor of the p-n junction. Typical terminal characteristics of a solar array at different operating conditions are shown in Figure 1. The incremental resistance of the array is negative; that is, the current output of the array strictly decreases with increased terminal voltage. Each curve has a point at which it delivers maximum power, dubbed the maximum power point (MPP). This point is the optimal operating point, since it maximizes the utilization efficiency of the solar arrays. It separates the left (LHS) of the curve from its right (RHS). On the LHS, the array resembles a current source, supplying increased power with increased voltage. On the RHS, the array resembles a voltage source, supplying decreased power with increased voltage. The terminal characteristics continuously change following variations in irradiance, temperature, and other operating conditions. The location of the MPP moves accordingly.

Figure 1 Typical -normalized- terminal characteristics of solar arrays

MPPT is a control scheme under which the MPP of the solar source is located in realtime. Active control—often by dc-dc converters—forces the system to operate at that point. Such an approach significantly increases the average power yield of a given array [2] and allows the system to avoid large-signal instability conditions [7-9].

Different approaches to MPPT have been developed over the years. One class of algorithms requires prior examination of the source characteristics and uses a model of these characteristics to relate the location of the MPP to ambient condition measurements [10]. Another class, called hill-climbing algorithms, locates the MPP by relating changes in power to changes in the control variable used to control the array. This class includes the perturb and observe algorithm (PnO) [11-13], the incremental conductance algorithm (IncCond) [11-12, 14], as well as other more elaborate algorithms derived from them. This group of algorithms is particularly popular because it does not require prior study or modeling of the source characteristics and can account for characteristics drift resulting from ageing, shadowing, or other operating irregularities.

#### 1.1.2. Batteries and Battery Management

Solar cells are limited power sources. An attempt to draw more power from a solar array than what is available results in large-signal instability and the collapse of the power system [9]. It is impractical and often impossible to size the solar source to suffice the load under all operating conditions and load levels. The utilization of a properly-sized battery bank allows the solar arrays to be sized slightly larger than the average load. During light loading, excess energy is stored in the battery bank. The load is supported by the battery bank when its demand exceeds the power available from the solar source.

High energy density, low or no maintenance, together with a long lifetime are all critical requirements for batteries used in space. One of the first space batteries was the Silver-Zinc

battery, which dominated the industry in the 1960s. This is a premium system with very high specific power and energy, but it is quite expensive due to the use of Silver. These batteries have a relatively short life cycle. Nickel-Cadmium has been the most common space battery since the 1970s. They were used in all commercial communications satellites, in most earth orbiters, and in some space probes. They are compact, can last ten to twenty years in space, and are tolerant to severe radiation environments. The Nickel-Hydrogen battery is currently the most popular space battery. It is significantly lighter than Nickel-Cadmium, but it is more difficult to package. It is the longest-lasting space battery yet built, commonly with ten to twenty-year lifetimes. The latest technology for space is the Lithium-Ion battery. High voltage Lithium-Ion cells are moving into space for short to moderate length missions. They are easy to package and very light [15].

It is very convenient to think of a battery as an ideal voltage source/sink or as a huge capacitor, and to use it accordingly. Such an approach, however, degrades battery performance, lifetime, and reliability. Most batteries require a specific charging scheme for optimized performance. A high-end battery charger is able to apply controlled charging currents, and/or controlled charging voltages. Some schemes also require pulse-charging at some stage of the charging process. Lithium-based batteries, a space industry trend, are especially sensitive to the charging method and require a three-stage charging process that includes both constant-voltage and constant-current stages. In order to allow the application of customized charging schemes to a particular battery, the power system is required to provide a control degree of freedom to be used for charge regulation. This is often the duty-cycle of some converter stage interfaced to that battery bank.

#### 1.1.3. Power Management and Distribution

The design of a spacecraft PMAD system is heavily dominated by the compromise between system architectures. A limited number of conversion stages yields a simple nonflexible system, often with over-sized sources and storage components. Adding more conversion stages allows enhanced power management with tighter bus regulation at the cost of increased conversion loss and control complexity.

Batteries are conventionally interfaced to a solar power system in several fashions as discussed next:

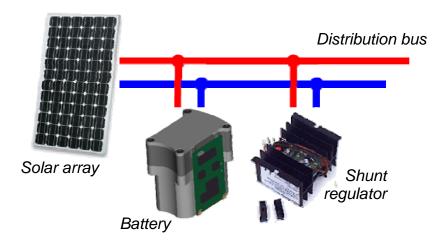

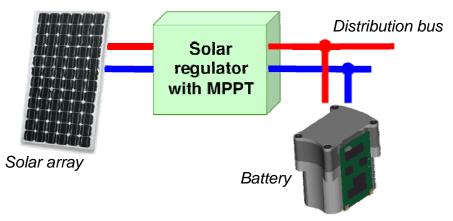

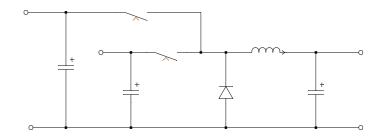

Unregulated bus topology: connecting the solar array directly to the battery, as shown in Figure 2, offers a very simple, reliable, and cost-saving solution. A shunt regulator is connected for battery protection from over-charge. Unfortunately, this topology does not allow control over the solar array voltage, nor bus voltage regulation.

Figure 2 Unregulated bus topology

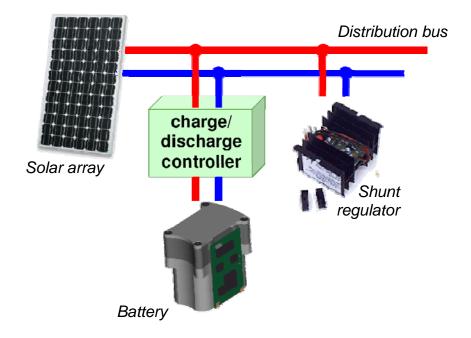

2. Regulated bus topology: interfacing the battery to the system through a charge/discharge regulator, as shown in Figure 3, allows voltage regulation of the system bus. The solar array voltage is clamped to that bus voltage and cannot be independently controlled.

Figure 3 Regulated bus topology

3. MPPT battery bus topology: a dc-dc converter interfacing the array to the battery, as shown in Figure 4, allows control over the operating voltage of the array, and opens the door for the advantageous MPPT operation. The bus voltage, however, is not regulated and is a function of the battery state of charge.

Figure 4 Battery-dominated MPPT bus topology

Many missions require voltage regulation of the distribution bus. It is desirable to achieve this while maintaining either MPPT or battery charge regulation. The risk of large signal instability due to source-load mismatch is eliminated by charging the battery during periods of high insolation, and covering the load power deficit from the battery during periods of low insolation. The solar arrays can then be sized to suffice the average load, allowing significant reduction of their size. These goals require the addition of one more power control variable, or power conversion path.

The interfaced system components are a power source, a power sink, and a bidirectional power storage device: the array, the distribution bus, and battery respectively. The power path configurations that can achieve this are:

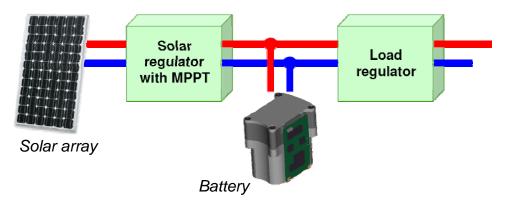

Two stage interface: the solar array is interfaced through an MPPT converter to an intermediate battery-dominated dc-link. Another converter stage then interfaces that link to the distribution bus, as shown in Figure 5. The main disadvantage of this scheme is that solar power goes through two lossy conversion stages before reaching the output.

Figure 5 Two-stage fully-regulated PMAD topology

2. Bidirectional chargers: the solar array is interfaced to the distribution bus through a single-stage converter, thus allowing higher input to output efficiency. A bidirectional converter interfaces the battery either to the input or to the output, as shown in Figure 6. If interfaced to the input, the battery charge needs to go through two conversion stages to reach the bus. If interfaced directly to the bus, the battery is charged from the solar array through two conversion stages. This scheme is efficient if the loading pattern closely matches the source, and very low energy is stored and later drawn from the battery.

Figure 6 Fully-regulated PMAD topologies with bidirectional battery chargers

3. Independent charge and discharge: the bidirectional battery converter can be split into two unidirectional converters: a charger interfaced to the input, and a discharge converter interfaced to the distribution bus. This configuration, shown in Figure 7, assures that power goes through one conversion stage when traveling between any two ports, allowing for higher efficiency. The price paid is an additional converter, increased size, weight, cost, and increased component count of the system.

Figure 7 Fully-regulated PMAD with independent battery charging/discharging

The added complexity, together with increased losses, size, weight, and cost, as well as decreased reliability, has impeded wide-spread adoption of such architectures for space. The potentially profitable MPPT technology has often been difficult to justify given the cost and control complexity overhead.

Proposed here is the use of a single converter stage to efficiently achieve the functionality of the three-converter configuration. This greatly simplifies the power architecture and control schemes needed for realizing MPPT and battery charge control. The multi-function utilization of power processing components and integration of control tasks reduces the size, cost, and complexity, making these control objectives more relevant and the design alternatives more feasible.

### CHAPTER 2: REVIEW OF MULTI-PORT CONVERTERS AND DIGITAL CONTROL TECHNIQUES

An increased demand for versatile energy harvesting and management systems has been witnessed in recent years. Systems capable of collecting energy from solar cells, fuel cells, regenerative braking, and mechanical oscillations are particularly useful for powering remote communication repeaters, traffic lights, sensor networks, small satellites, hybrid electric vehicles (HEVs), laptops, and other electronic products. This chapter reviews the existing and emerging technologies for multi-port systems. It also reviews the recent trends for digital control of power electronics—an enabler technology for effective multi-variable multi-objective control of complex systems.

#### 2.1. Multi-Port Converter Technologies

The simplest approach to building multi-port converters is the interface of several converter stages to a common dc bus with centralized control. A multi-input bidirectional converter system, shown in Figure 8, was designed for use in HEVs and interfaces a fuel cell, a battery, and a super-capacitor bank [16].

Figure 8 Bidirectional multi-input converter system for HEVs [16]

The investigation of new converter topologies designed to handle multiple power ports has recently become a recurring theme. Many believe that topologies specifically tailored for multi-port applications can reduce cost and losses while retaining the functionality of more traditional multi-converter designs.

#### 2.1.1. Integrated Multi-Input Converters

A two-input tri-state dc-dc converter, shown in Figure 9, based on the buck topology was an early attempt to integrate spacecraft front-end PMAD systems [17]. Dynamic modeling and control of this converter were further discussed in [18]. This converter provides two degrees of freedom, and thus can be used to achieve two control objectives. When sourced by a solar array and the system battery, it is possible to simultaneously perform MPPT and output voltage regulation. Unfortunately, the input ports are unidirectional and the converter cannot be used to charge the battery from the solar array. This converter also requires bidirectional-blocking devices to properly operate, uncommon in the industry for the voltage and power levels intended.

Figure 9 Topology of the two-input tri-state dc-dc converter [18]

Another multi-input converter was proposed in [19] based on the flyback topology. This converter, shown in Figure 10, can achieve galvanic isolation between all ports by coupling them to a common flyback transformer.

Figure 10 A multi-input flyback converter [19]

A simplified version of this circuit was later proposed as shown in Figure 11 [20]. This multi-input circuit, based on the buck-boost (non-isolated flyback) topology, was later modified

to isolate the loading port only and generalized to supply multiple loads as shown in Figure 12 [21]. The power budgeting capabilities of these configurations were also discussed in [21]. Each of these topologies possesses a number of control variables equal to the number of sources. They can perform independent regulation over a maximum of one output given that regulation over one of the inputs is dropped. It was again shown that a two-input converter can regulate its load voltage while governing the operating point of a solar array connected as one of its inputs.

Figure 11 A multi-input buck-boost converter [20].

Figure 12 A multi-input multi-output flyback converter [21]

The main limitations of these configurations are the lack of a bidirectional port for energy storage, the utilization of bidirectional-blocking switches, the limitation of individual duty-cycles

when a large number of sources is used, and/or operation based on the flyback principle with magnified inductor currents.

Figure 13 shows a two-input boost-derived isolated converter proposed in [22]. This converter is able to simultaneously achieve MPPT of a solar input, power factor correction (PFC) of a sinusoidal source, and load regulation. This converter, being boost-derived, draws low ripple input currents from its sources. Due to instantaneous energy balance constraints, the speed by which the load is regulated is limited. The main disadvantage, however, is its requirement of a large number of bidirectional-blocking switches, and the absence of a bidirectional port.

Figure 13 A two-input isolated boost converter [22]

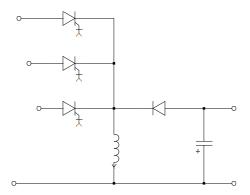

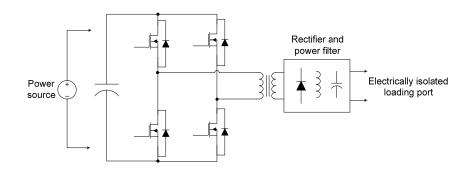

#### 2.1.2. Isolated Bidirectional Multi-Port Converters

Recent publications focused on load-side control through the utilization of a half-bridge structure magnetically coupled to the source chopper [23, 24]. The converter shown in Figure 14 is suitable for HEVs or fuel cell powered electric vehicles [23]. Energy exchange between the 14V and 42V busses is governed by the duty-cycle of the primary-side phase-leg, while energy exchange with the high voltage bus on the secondary side is governed by the relative phase-shift between the switching waveforms on either side of the transformer.

Figure 14 Triple-voltage bus dc-dc converter [23]

This concept can be further extended to a larger number of isolated and non-isolated ports [24]. A number of half-bridge circuits can be coupled as shown in Figure 15. These are essentially independent converters that share a common ac distribution transformer. Control over the power flow can be achieved by changing the relative phase-shift between the switching sequences of those bridges. It is also possible to interface additional non-isolated ports to the system by adding buck/boost stages.

Figure 15 Bidirectional magnetically coupled multi-port converter [24]

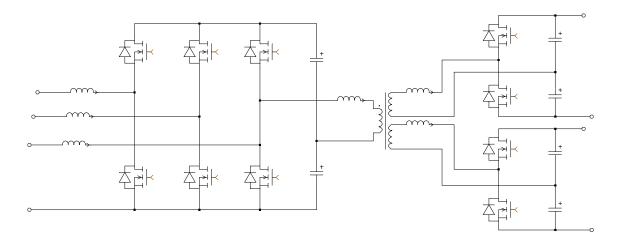

Following the same principle, isolated bidirectional multi-port converters can be constructed out of full-bridge structures as shown in Figure 16 [25]. Full-bridge structures are more popular for lower voltage higher current applications since they apply the full bias voltage to the transformer and thus circulate lower currents.

Figure 16 The construction of isolated bidirectional multi-port converters using full-bridge structures [25]

The main advantage of these systems is that all ports are bidirectional and can be chosen to be isolated. They utilize the very popular phase-leg structure with popular unidirectionalblocking switches that make them especially attractive and expandable. They utilize, however, a large number of active switches, and require fairly complex modulators and controllers.

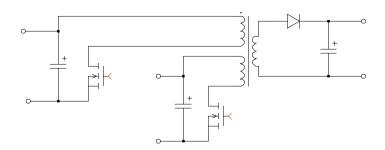

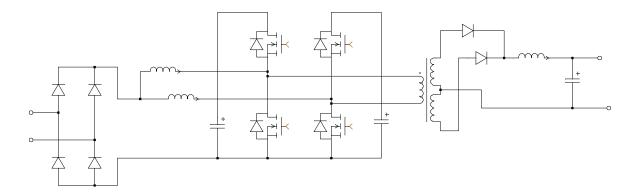

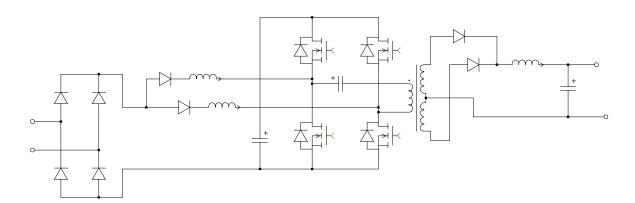

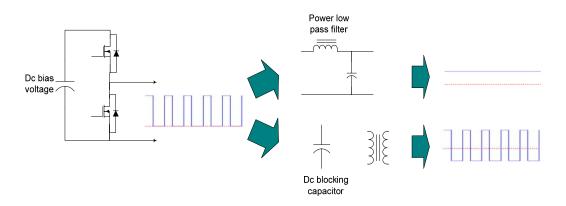

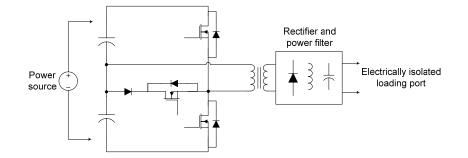

## 2.1.3. Integrated Power Factor Correction Converters

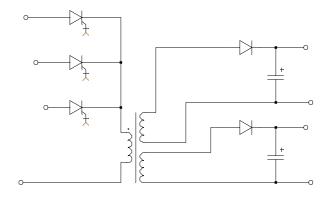

Power factor correction (PFC) converters are two-port converters. They, however, require the storage of energy in an intermediate capacitor that would absorb the instantaneous difference between the pulsating power from the source and the power delivered to the load. This bulk capacitor represents a long-term energy storage element, and its capacity can be better utilized if it is not directly interfaced to the source or the load. In this case, a PFC converter essentially becomes a three-port converter with a bidirectional port interfacing that bulk capacitor. Several publications have proposed the integration of a bi-phase boost into a phase-shift full-bridge (PS-FB) converter in order to achieve single-stage PFC, see Figure 17 [26-29].

Figure 17 PFC converters integrating a boost and a PS-FB stage [26-29]

Interestingly, simultaneous variation of duty-cycle and phase-shift was proposed in [29] to allow output voltage regulation, while constraining the amount of energy storage in the bulk capacitor. In this converter, shown in Figure 18, the boost inductors are designed to operate in discontinuous conduction mode (DCM) in order to enhance the power factor. The phase-shift between the switching of the two legs is used to control power flow to the load. The duty-cycle of each leg is used to achieve some control over the voltage of the bulk capacitor, reducing the voltage stress over the switching bridge and rectifier diodes. The application of this scheme to PFC introduced a number of challenges that overshadowed a lot of it merits.

Figure 18 Constraining the voltage of the bulk capacitor using combined duty-cycle and phaseshift control

### 2.2. Digital Control of Switching Power Converters

A strong trend toward digital control of power converters, or "digital power," has recently surfaced. Digital power is gaining momentum due to: the need for supervisory digital controllers in many systems, rapid increase in digital integrated circuit (IC) resources paralleled by a rapid decrease in their cost, reduced board space and system cost due to integration of multiple control functions into a single digital chip, increased flexibility with feed-forward and non-linear control techniques, and improved protection and health monitoring [30-36]. Still missing, however, is a simple step-by-step design method approachable by a practicing engineer. Bridging the gap between digital control and practicing engineers requires improvements in two key challenging areas: compensator design, and controller mapping into software code.

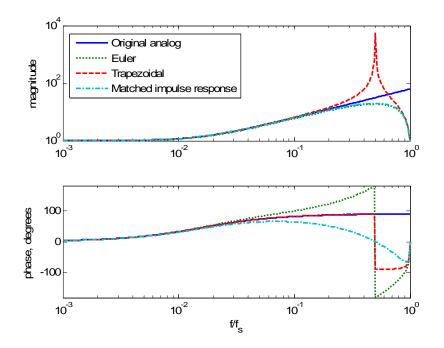

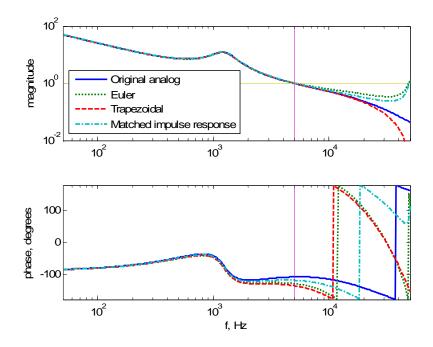

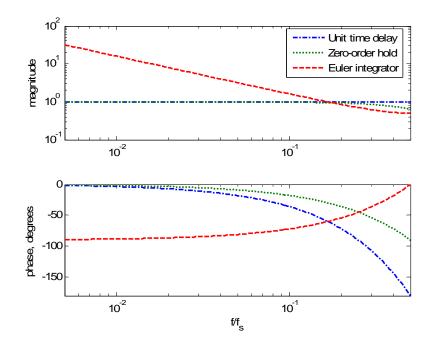

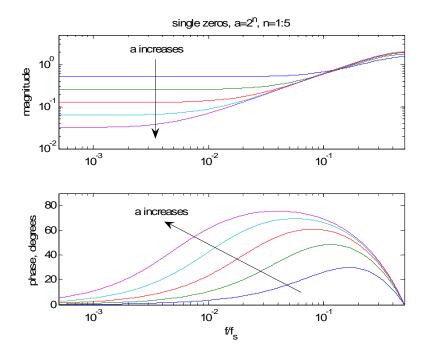

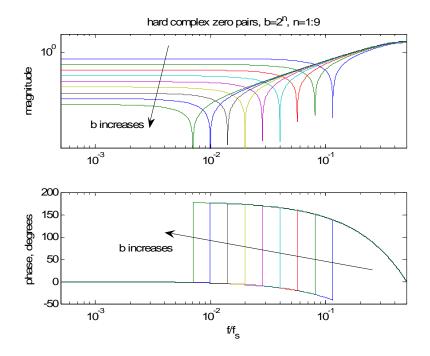

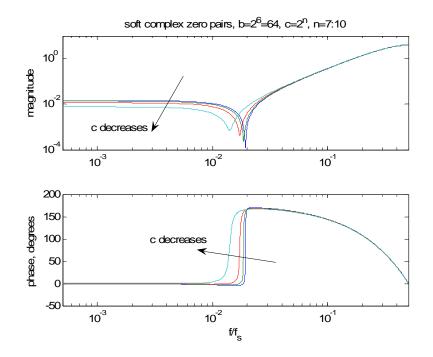

In recent years, digital controller design for power converters has been an active area of research. Two main approaches were proposed: analog redesign, and direct-digital design. Analog redesign proceeds by using a chosen transformation to approximate the continuous-time s-domain controller transfer function by one in the discrete-time z-domain [32-35]. This approach is popular because it relies on traditional design techniques in the analog frequency domain. However, it suffers an inherent behavioral mismatch between the original analog, and the resultant digital designs. Figure 19 shows several digital approximations of an analog zero, while Figure 20 shows the response of the resultant digital closed loops compared to an analog-controlled original. The trapezoidal rule has the closest correspondence to the original analog function, but yields the most complicated expression in the z-domain. Moreover, the analog redesign method fails to account for a zero-order holds (ZOH) and computational time delays inherent in a digitally closed loop.

Figure 19 The frequency response of an analog zero and several digital approximations

Figure 20 Typical loop frequency response with an analog controller and its digital redesigns

A number of powerful direct-digital controller design techniques have been introduced and demonstrated in literature [36-40]. Controller design is performed in the z-domain using an approximated discrete-time model of the controlled plant. Nonetheless, these were not widely used by practicing engineers because they are mathematically involved and lack a strong link to traditional analog controller design methods.

Mapping the digital controller function into software code requires full understanding and accurate modeling of the components of the digital controller. Several publications presented good models of the analog-to-digital converter (ADC) and pulse-width modulator (PWM) modules, and discussed their quantization effects [30, 40]. Quantization effects within the internal registers of a fixed-point controller IC—dominating the digital power market—have not been fully addressed. A simple system for efficient number storage and manipulation is still needed.

# CHAPTER 3: THREE-PORT CONVERTER SYSTEM INTEGRATION

This chapter explores the basic principles of converter integration into multi-port systems.

### 3.1. Integration Objectives

The main objective of converter integration is the construction of flexible, efficient, reliable, and light-weight PMAD systems. These objectives translate to a more specific set governing the power converters, their controllers, and the general architecture.

## 3.1.1. Objectives for the Power Stage

This work targets the integration of the power train into a single converter stage that interfaces three power ports: an input, an output, and a bidirectional port. This promises reduced losses thus allowing enhanced utilization of available power, reduced thermal stress, and enhanced power density.

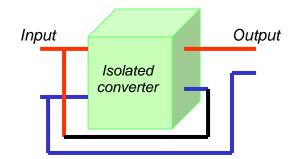

Galvanic isolation of the output port through a transformer is required. This ensures:

- Design flexibility for choosing the output voltage level: high bus voltages reduce distribution losses in large systems, while lower voltages simplify the design of point-ofload (POL) converters.

- 2. Ability to achieve high voltage step-up/down ratios.

- 3. Fault isolation and enhanced operator safety.

- 4. Flexible series/parallel converter connection in modular designs, and compatibility with NASA's Series Connected Boost Regulator (SCBR) concept, shown in Figure 21 [41].

Figure 21 NASA's SCBR configuration [41]

It is preferable to base integrated converter topologies on popular existing two-port converters. Engineering concepts and experiences available with practicing engineers can then be used to optimize the new topologies in a fashion similar to their mother topologies. This includes component selection and magnetic design procedures, as well as achieving soft-switching for increased efficiency at higher switching frequencies.

### 3.1.2. Control Objectives

Following energy conservation principle, a maximum of two ports can be independently controlled in a three-port power converter. The third port operating point is governed by the need for it to accept or supply the power balance and compensate for conversion power losses.

Control decisions and transients on one power port in a multi-port system are expected to affect the remainder. Controller coordination and feed-forward architectures can simplify controller design and enhance performance. An integrated controller performing simultaneous control over two power ports is targeted in this work. The goal controller also should be able to switch between different control objectives in real time. Choices in a battery-backed solar power system are: MPPT, battery charge control, and bus voltage regulation.

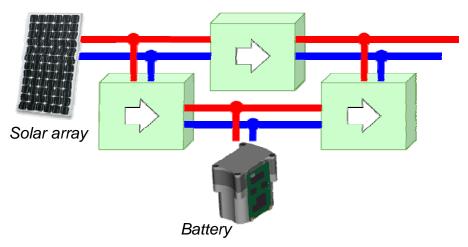

## 3.1.3. Modularity Objectives

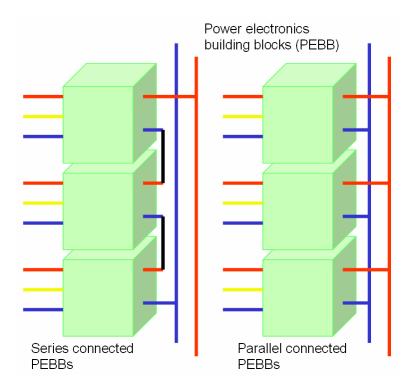

The utilization of PEBBs is becoming increasingly popular in space PMAD systems [42]. The standardization of power modules allows repetitive utilization of optimized designs, thus reducing the design time and cost, and simplifying testing and qualification cycles. Paralleled converter structures provide hot-swap capabilities and enhanced fault-tolerance, thus improving system reliability and availability.

The standardized converters must be able to be independently sourced or parallel connected at their input, as well as at their storage ports. With electrically isolated output ports, these can be the building blocks for a wide choice of voltage and current ratings at the bus. Converter outputs can be connected in series or parallel, as shown in Figure 22, independent from the input connection topology. Techniques for uniform voltage, current, and power stress distribution must be implemented.

Figure 22 PEBB approach applied to three-port converters

## 3.2. <u>Topology Integration Approach</u>

The fundamental scientific concepts upon which this work is based are described in this section. This is followed by a description of some members of a novel topological family.

## 3.2.1. Unity of Power Topologies

The operation of a large majority of power electronic circuits relies on different variations of one basic structure. This structure, often dubbed a phase-leg, consists of two series connected switching devices biased by a dc voltage bus, as shown in Figure 23. The switching action causes the middle point (phase-node) to be connected alternatively to either rail of the biasing dc voltage. This is then utilized in one of two ways:

- As an ideally lossless "time-division voltage divider": a power filter is used to smooth the voltage at the phase-leg into a controlled voltage value. In this case, one of the switches can be replaced by a diode to create the basic topologies: buck, boost, and buck-boost. It is, however, common practice to keep it an active switch, allowing the topology to achieve bidirectional power flow, as well as decreased conduction losses in low voltage applications.

- 2. As a driver for a high-frequency transformer: the ac component of the phase-leg voltage waveform is applied to the primary winding of a transformer. A rectifier circuit, together with a filter, is used to reconstruct a dc voltage level at the secondary. This is the operating principle of the half-bridge, forward/active-clamp forward, and the full-bridge topologies.

Figure 23 Typical functions of a phase-leg

There is a striking similarity between the half-bridge converter and the active-clamp forward converter. The half-bridge circuit places the source at the dc bias voltage of the phaseleg, while a dc voltage is accumulated on a filter capacitor that removes the dc component from the transformer voltage waveforms. The active-clamp forward circuit connects the source in place of this dc-blocking capacitor, and results in creating a higher dc-bias voltage across the phase-leg. With both sources connected, the relationship between the dc-bias and the dc-blocking voltages are governed by the characteristics of the "parasitic" synchronous buck converter interfacing them.

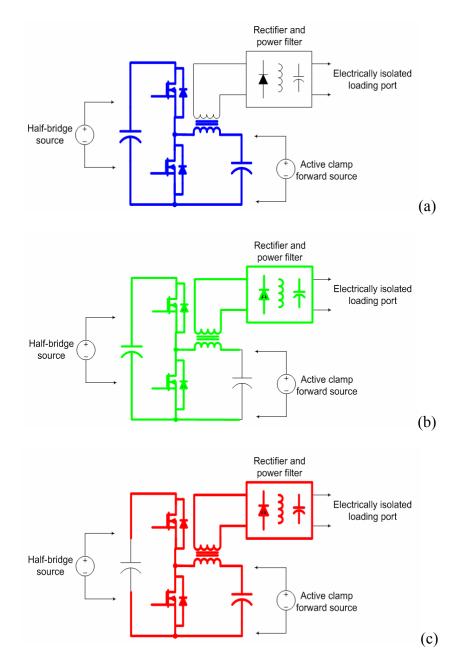

Figure 24 Unity of (a) buck, (b) active clamp forward, and (c) half-bridge converter topologies

The dual utilization of a phase-leg as a time-division voltage divider and a transformer driver is a powerful tool for three-port interface. The ac and dc components of the phase node waveform can be independently controlled to realize tight regulation of two power ports.

### 3.2.2. Savings Potential

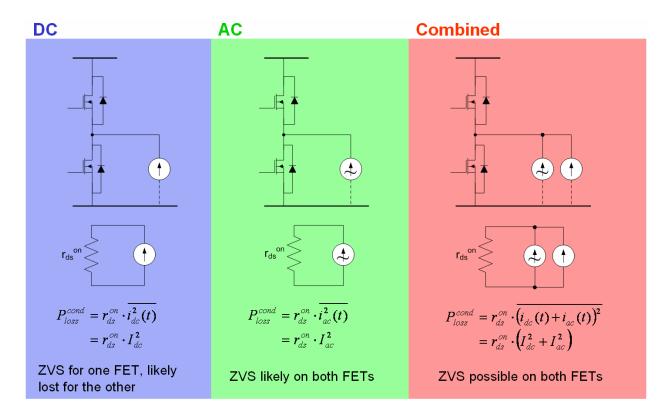

This integration concept has great potential to deliver savings in both conduction and switching losses—see Figure 25. In a non-isolated topology, the phase-leg would drive low-ripple dc current. Using two FETs with equal on-state resistance, the conduction loss incurred by these FETs can be estimated as:

$$P_{loss}^{cond} = r_{ds}^{on} \cdot \overline{i_{dc}^{2}} = r_{ds}^{on} \cdot I_{dc}^{2}$$

$$(3.1)$$

where  $r_{ds}^{on}$  is the on-state resistance of the FETs used, and  $I_{dc}$  is the value of dc current driven by that phase-leg.

When driving ac current through the transformer of an isolated topology, the conduction loss would be estimated as:

$$P_{loss}^{cond} = r_{ds}^{on} \cdot \overline{i_{ac}^{2}} = r_{ds}^{on} \cdot I_{ac}^{2}$$

$$(3.2)$$

When the same phase-leg is used to drive both currents, conduction loss is estimated as:

$$P_{loss}^{cond} = r_{ds}^{on} \cdot \overline{(i_{dc} + i_{ac})^2} = r_{ds}^{on} \cdot \left(I_{dc}^2 + I_{ac}^2\right)$$

(3.3)

where  $I_{ac}$  is the rms value of ac current driven by that phase-leg.

Note that the result is simply the sum of the individual loss to be incurred by the dc and ac components separately. This means, ideally, that a single phase-leg can be used to do the job of two without increasing the conduction power loss. The designer can also choose to invest the same silicon area—perhaps by paralleling the devices of the two phase-legs. In such a case, the

on-resistance would significantly drop, allowing the integrated structure to incur lower conduction loss using the same investment in silicon.

The integrated structure is also capable of reducing FET turn-on losses through zerovoltage switching (ZVS). When a phase-leg drives a dc current in a non-isolated topology, ZVS is naturally achieved for one FET only while the other remains hard-switched. The upper FET is hard-switched in a buck converter, while a boost converter hard-switches its lower FET. In many isolated topologies, the transformer current direction is suitable to force ZVS turn-on of all primary FETs. An integrated topology is likely to have a wide range of operating conditions where all FETs are switched with ZVS. In other words, the ac current of the isolated section aids in avoiding the hard-switched transition of the non-isolated section.

Figure 25 Savings potential of the proposed topology integration approach

### 3.2.3. Attractive Conventional Topologies

A number of popular conventional isolated topologies exist that can be modified to interface three ports. Rather than searching for completely new configurations, this evolutionary approach recaptures the technical merits of popular existing two-port topologies. It allows circuit designers to use their design experience and knowledge base to better optimize the new topologies.

#### 3.2.3.1 <u>The Duty-Cycle Shifted Half-Bridge Converter</u>

The half-bridge topology uses a single phase-leg to create the driving waveforms for the transformer. A dc-blocking capacitor is used to remove the dc component from the driving waveforms. This is particularly attractive because of its reduced switch count and simplified control.

Symmetric control of the half bridge circuit balances voltage stresses across the circuit components and achieves regulation of the load. Unfortunately, this driving scheme does not allow ZVS of the switches, creating voltage stress and electromagnetic interference (EMI) problems in the converter. Asymmetric control of this topology has been introduced as a technique for achieving ZVS operation, but at the expense of unbalanced stresses across converter components [43].

The Florida Power Electronics Center has introduced the concept of the duty-cycle shifted half-bridge (DCS-HB) converter [44]. This converter, shown in Figure 26, is able to achieve ZVS on one of the switches while retaining the symmetry of component stresses. Moreover, the addition of an auxiliary switch path allows soft-switching on all switches of the

circuit. This lowers component stresses and switching losses, and solves EMI problems in the circuit. This approach has thus been adopted in commercial production.

Figure 26 Soft-switched DCS-HB converter with auxiliary branch

# 3.2.3.2 The Phase-Shift Full-Bridge Converter

Full-bridge isolated converters, as that shown in Figure 27, utilize two phase-legs to drive the transformer. The increased switch count is justified by the configuration ability to instantaneously apply the full input voltage to the transformer winding. ZVS for all four switches can be achieved by driving the topology in a phase-shift controlled manner. This has made this topology specifically popular at moderate-to-high power conversion applications.

Figure 27 The PS-FB converter

The development of different three-port converter topologies based on such practical optimized conventional techniques provides feasible alternatives for a wide variety of applications at different power levels.

### 3.3. Three-Port Topology Options

Introduced here are some possible members of the novel three-port family that were based upon the topologies described above.

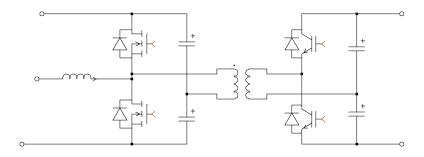

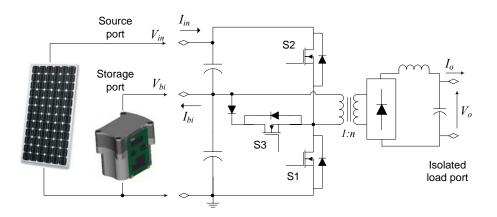

# 3.3.1. The Tri-Modal Half-Bridge Converter

The DCS-HB with the auxiliary switch branch is topologically suitable for use as a threeport converter, as shown in Figure 28. A bidirectional port is readily available at the lower dcblocking capacitor on the primary side. This capacitor voltage is conventionally set to half of the input voltage by equating the duty-cycles of the two phase-leg switches. Dynamic control of this duty-cycle ratio allows independent control of this bidirectional port. The resultant converter has three modes of operation within a constant-frequency switching cycle, and was thus dubbed the tri-modal half-bridge (TM-HB) [45, 46].

Figure 28 The TM-HB converter

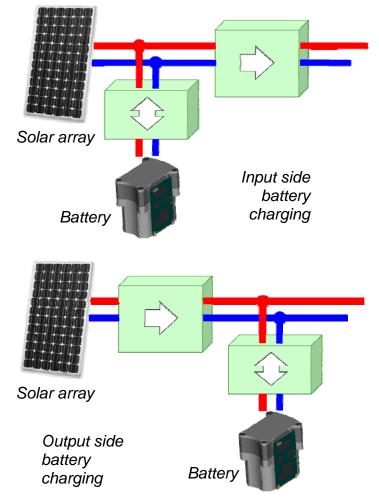

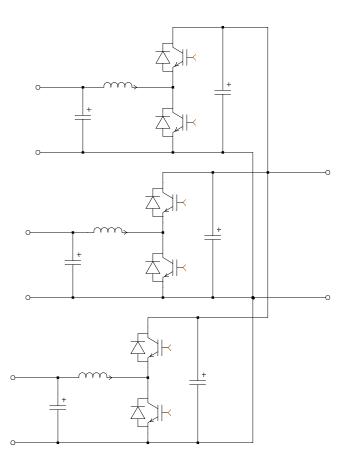

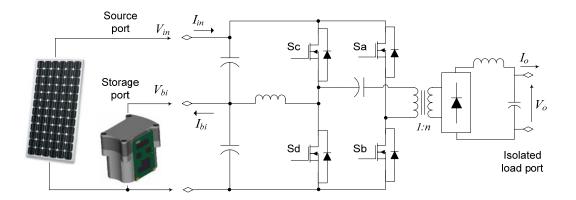

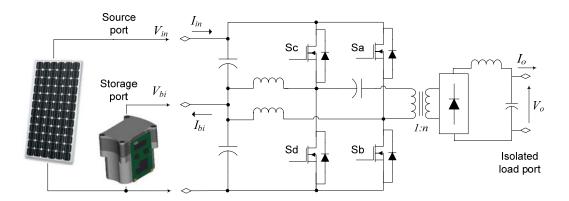

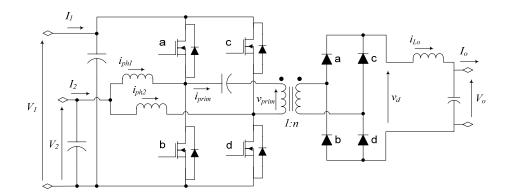

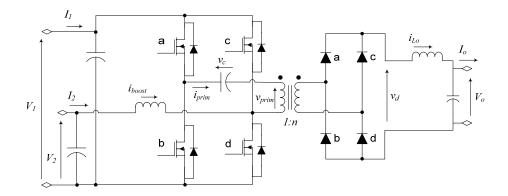

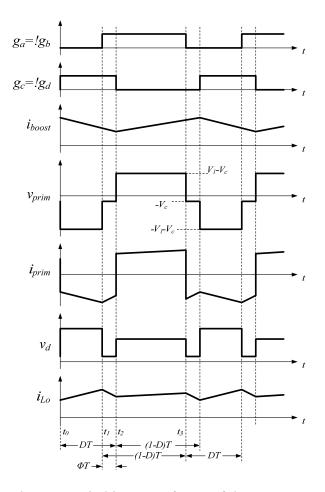

### 3.3.2. Boost-Integrated Phase-Shift Full-Bridge Converters

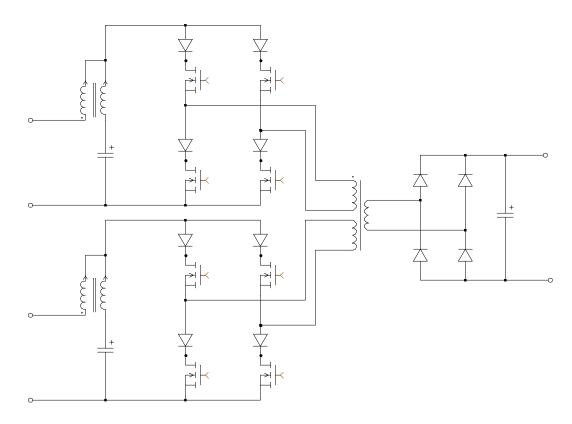

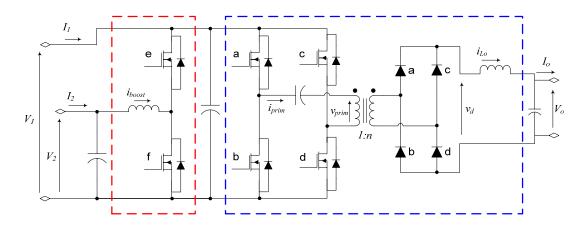

Phase-Shift Full-Bridge (PS-FB) converters are more suitable for higher power applications, [47], typically above 1kW. Applying the same concept of dual use of the phase-legs, two three-port topologies can be derived from the full-bridge circuit. The asymmetric boost-integrated phase-shift full-bridge (A-BI-PS-FB) converter results from adding an inductor to the structure as shown in Figure 29. This creates a "parasitic" synchronous boost stage that interfaces a new bidirectional port. The voltage of this bidirectional port is controlled by duty-cycle of the phase-leg used. Power flow to the output is controlled by modulating the phase-shift between the two phase-legs in a similar fashion to the conventional PS-FB converter [48-50].

Figure 29 The A-BI-PS-FB converter

It is also possible to interface this added bidirectional port using two boost inductors each connected to a different phase-leg as shown in Figure 30. This allows better distribution of the current stress among the bridge FETs. The resultant topology, the symmetric boost-integrated phase-shift full-bridge (S-BI-PS-FB), is more suitable when a large amount of current flows in the boost section. Power flow is controlled in a similar fashion as in the A-BI-PS-FB.

Figure 30 The S-BI-PS-FB converter

### 3.4. Control Aspects of Multi-Port Systems

## 3.4.1. Control Objectives, and Degrees of Freedom

In the general sense, the switching waveforms of a power converter can provide any number of degrees of freedom, translating to control variables. The number required, however, depends on the control functionality it is expected to perform. Bus converters do not require a control variable and often implement a fixed voltage transfer ratio. Conventional two-port converter topologies generally provide a single control variable, which is utilized to perform a single control function. Output voltage regulation is a classic example of such a control objective.

In some cases, a single control variable is utilized to achieve multiple mutuallydependent control objectives. The most common example is input current shaping and average output voltage regulation in a PFC ac-dc stage. It is notable here, however, that the shape of the input current is tightly regulated, while its amplitude is variable and is adjusted to regulate the average output voltage.

According to the principle of conservation of energy, a generalized *n*-port converter operating in steady-state, and containing no independently controlled loss mechanisms (dissipative regulators), can perform independent regulation of the operating parameters of up to (n-1) ports. This follows from the need for at least a single flexible unregulated port that maintains the power balance in the circuit.

While the number of independently regulated ports is limited in such a system, the number of degrees of freedom provided in the converter is not. The existence of degrees of freedom that exceed the number of independently controlled ports is generally associated with the existence of intermediate converter states not directly coupled to any of the outputs.

Intermediate bus capacitor voltages are a common example of such states. In such cases, it is preferable that the control structure used for the conversion system monitors such intermediate states and ensures their convergence to a suitable steady-state value.

Each of the topologies proposed above exhibits two degrees of freedom, or control variables. For the TM-HB, these are the duty-cycles of the two main switches. For the BI-PS-FB topologies, these are the duty-cycle of the phase-legs, and the relative phase-shift between their switching waveforms.

The two control variables of each topology are sufficient to perform tight independent regulation of two of the converter's ports. The choice of regulated ports is dependent on the application. This choice strongly affects the control structure adopted. It is further possible to dynamically alter the choice of regulated ports and control objectives, as well as the associated control structure, depending on the operating conditions of the devices and systems interfaced through the converter.

## 3.4.2. Operating Modes of a Battery-Backed Photovoltaic Power System

Consider a sample photovoltaic power system where a solar array and a battery bank are connected to the two ports on the input side of a three-port converter, while the output bus is interfaced through the isolated port on the secondary side. Such a system is likely to operate in one of three modes:

1. <u>Battery-balanced operation:</u> the output voltage is tightly regulated, and the solar array is run under MPPT control. In this case, the battery preserves the power balance in the system by storing unconsumed solar power, or providing the deficit during peak load intervals.

- Excess insolation operation: the output voltage is regulated and sinks less power than is available, while the battery charge rate is limited. In this case, the battery current or voltage is regulated, while the solar array is left to operate in its voltage-source region where it provides less power than it has available.

- 3. <u>Flexible load operation:</u> the battery charge is regulated, and MPPT controls the solar arrays. This mode is active when the load is able to sink a variable amount of power, while the battery charge rate is limited. This is useful for a grid-tie inverter system.

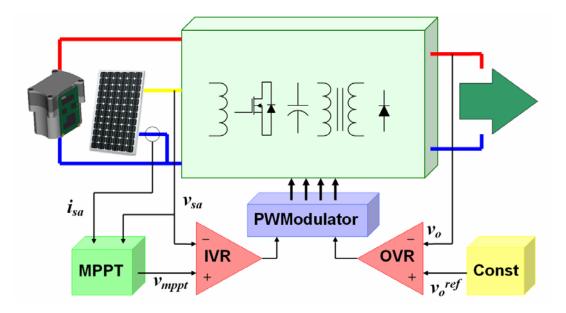

## 3.4.2.1 Sample Control Structure

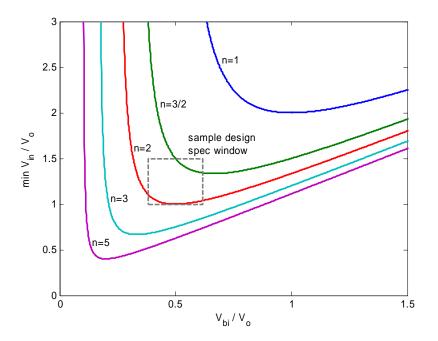

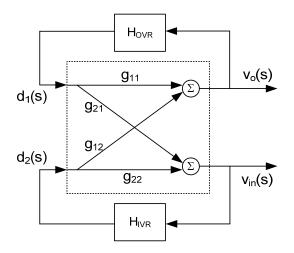

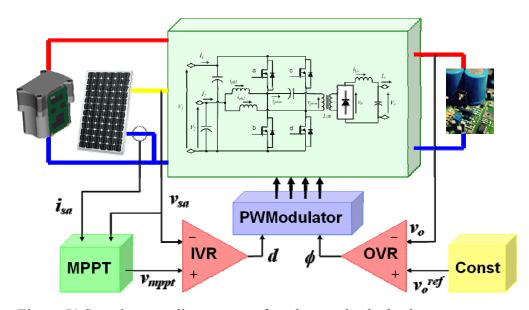

For the purpose of demonstration, a possible control structure is presented for the mode of battery-balanced operation. The control objectives can be achieved by closing two feedback loops: input voltage regulation (IVR), and output voltage regulation (OVR), as shown in Figure 31.

Figure 31 Sample controller structure for a battery-backed solar power system

The IVR loop is used to regulate the solar array voltage to its reference value. This reference is to be provided by an MPPT controller, and represents an estimate of the optimal operating voltage. This intermediate IVR loop allows improved performance and enhanced stability of the MPPT controller whose design is beyond the scope of this work. The OVR loop uses the remaining control variable to tightly regulate the voltage at the output port. Operation of each of the proposed converters under this scheme is discussed in later chapters.

# CHAPTER 4: TRI-MODAL HALF-BRIDGE CONVERTER

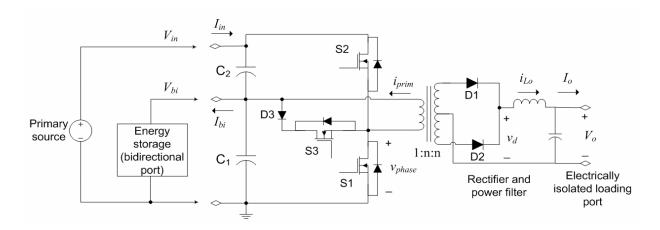

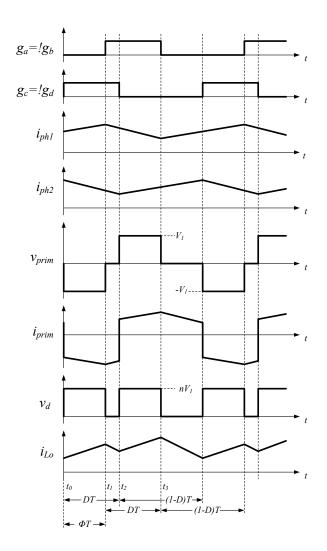

In this chapter, the operation and characteristics of the TM-HB converter are discussed. This three-port converter, shown in Figure 32, is a modified version of the DCS-HB converter reported in [44]. The fundamental difference is that the DCS-HB topology is a two-port topology with its two main switches, S1 and S2, operated at equal duty-cycles. The proposed tri-modal topology independently controls the duty-cycles of these switches in order to introduce an additional control variable necessary for interfacing the added bidirectional port. This modification results in asymmetric operation of the topology, and changes the design constraints on the converter components, while preserving the topological ability for ZVS. Figure 33 shows the expected steady-state operating waveforms of the proposed topology.

Figure 32 The TM-HB converter

Figure 33 Basic switching waveforms of the TM-HB converter

# 4.1. Modes of Operation and Steady-State Analysis

In a constant frequency PWM control scheme, the tri-modal topology has three basic modes of operation within a switching cycle. In Mode I, S1 is gated on, applying a positive voltage to the transformer primary winding, until S2 is turned on and S1 turned off to start Mode II. In Mode II, a negative voltage is applied to the transformer primary winding until S3 is gated on to start Mode III, during which zero voltage is applied to the transformer primary. This allows both the magnetizing and load-filter inductor currents to free-wheel.

#### 4.1.1. Regular Operating Modes

Assuming an ideal lossless converter, the steady-state relations between different port voltages can be determined by equating the voltage-second product across the converter's two main inductors to zero. First, using volt-second balance across the primary transformer magnetizing inductance when operating in continuous conduction mode (CCM), there is:

$$-D_1 \cdot T \cdot V_{C1} + D_2 \cdot T \cdot V_{C2} = 0$$

With  $V_{in} = V_{CI} + V_{C2}$ , and  $V_{bi} = V_{CI}$ , the voltage at the bidirectional port,  $V_{bi}$ , may be given by:

$$V_{bi} = \frac{D_2}{D_1 + D_2} \cdot V_{in}$$

(4.1)

where  $V_{in}$  is the voltage of the input port,  $D_1$  and  $D_2$  are the duty-cycles of S1 and S2, respectively, and *T* is the duration of the switching cycle. Assuming CCM operation, the voltsecond balance across the load filter inductor yields:

$$D_{1} \cdot T \cdot (n \cdot V_{c1} - V_{o}) + D_{2} \cdot T \cdot (n \cdot V_{c2} - V_{o}) - (1 - D_{1} - D_{2}) \cdot T \cdot V_{o} = 0$$

$$V_{o} = D_{1} \cdot n \cdot V_{c1} + D_{2} \cdot n \cdot V_{c2} = 2 \cdot \frac{D_{1} \cdot D_{2}}{D_{1} + D_{2}} \cdot n \cdot V_{in}$$

(4.2)

where *n* is the turns' ratio of the transformer, and  $V_o$  is the load-port voltage. Using Equation (4.1), this can also be re-written as:

$$V_o = 2 \cdot D_1 \cdot n \cdot V_{bi} \tag{4.3}$$

Assuming a lossless converter, steady-state port currents can be related by applying the power conservation principle as follows:

$$V_{in} \cdot I_{in} = V_{bi} \cdot I_{bi} + V_o \cdot I_o \tag{4.4}$$

where  $I_{in}$ ,  $I_{bi}$ ,  $I_o$  are the average input, bidirectional, and load currents, respectively.

### 4.1.2. Irregular Operating Modes

While S3 is gated on, if the load filter inductor current is not sufficient to free-wheel the magnetizing inductor current, and if this magnetizing current is negative, the current of D1 drops to zero and turns it off. D2 still conducts the load current, the D3-S3 branch is turned off, and the magnetizing current is either locked to the reflected load current, or exceeds it and forces the body diode of S2 on.

Under such modes, the converter voltages do not follow the relations in Equations (4.1) to (4.3). It is important to note that while these modes are irregular, they are not dangerous. In fact, these modes of operation allow the converter to continue supplying the load from the bidirectional port if the main source is absent. Experimental waveforms of the converter operating under these modes are shown in Section 4.4.

### 4.2. <u>Component Stress and Design Considerations</u>

#### 4.2.1. Magnetizing Current

The magnetizing inductance of the transformer is used to store energy to interface the input and bidirectional ports. The transformer design needs to allow for this dc current flow and becomes similar to an inductor or a flyback transformer design. The average magnetizing current,  $I_M$ , reflected to the primary side satisfies:

$$I_{bi} = D_1 \cdot (I_M - n \cdot I_o) + D_2 \cdot (I_M + n \cdot I_o)$$

Rearranging:

$$I_{M} = \frac{I_{bi} + (D_{1} - D_{2}) \cdot n \cdot I_{o}}{D_{1} + D_{2}}$$

(4.5)

Another expression for  $I_M$  can be obtained by using the average input current relation given by:

$$I_{in} = D_2 \cdot (I_M + n \cdot I_o)$$

Rearranging, we have:

$$I_M = \frac{I_{in}}{D_2} - n \cdot I_o \tag{4.6}$$

Notice that  $I_M$  can be reduced during design by increasing the nominal value of  $D_1$  and  $D_2$ .

# 4.2.2. Semiconductor Stress

The ideal reverse voltages seen by the switches on the primary side are:

$$V_{S1} = V_{S2} = V_{in} \tag{4.7.a}$$

$$V_{S3} = V_{bi}$$

(4.7.b)

While that seen by the diode, D3, is:

$$V_{D3} = V_{in} - V_{bi} \tag{4.8}$$

Assuming CCM operation, and neglecting inductor ripple currents, the rms current in the primary switches are given by:

$$I_{S1}^{rms} = \sqrt{D_1} \cdot \left| \boldsymbol{n} \cdot \boldsymbol{I}_o - \boldsymbol{I}_M \right| \tag{4.9.a}$$

$$I_{S2}^{rms} = \sqrt{D_2} \cdot \left| n \cdot I_o + I_M \right| \tag{4.9.b}$$

$$I_{S3}^{rms} = \sqrt{1 - D_1 - D_2} \cdot \left| n \cdot I_o + I_M \right|$$

(4.9.c)

The average current of carried by D3 is:

$$I_{D3}^{avg} = (1 - D_1 - D_2) \cdot (n \cdot I_o + I_M)$$

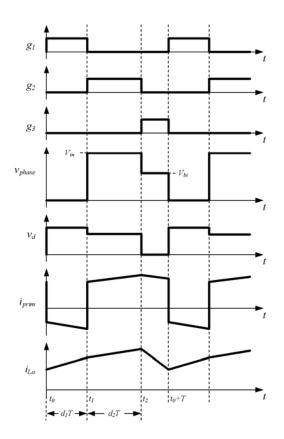

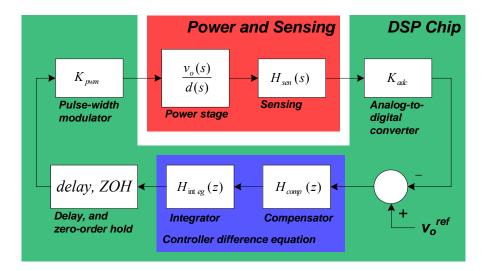

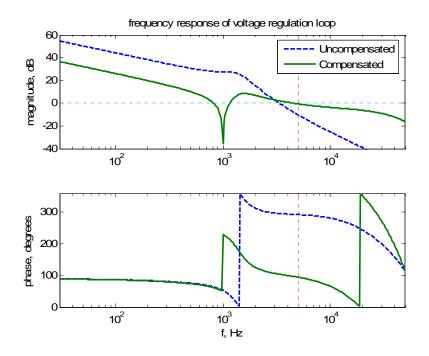

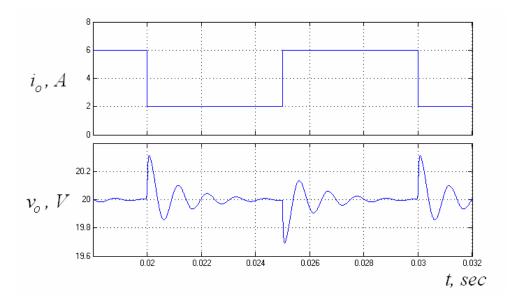

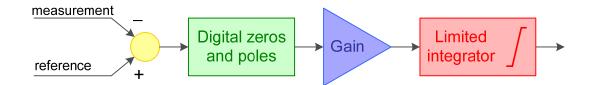

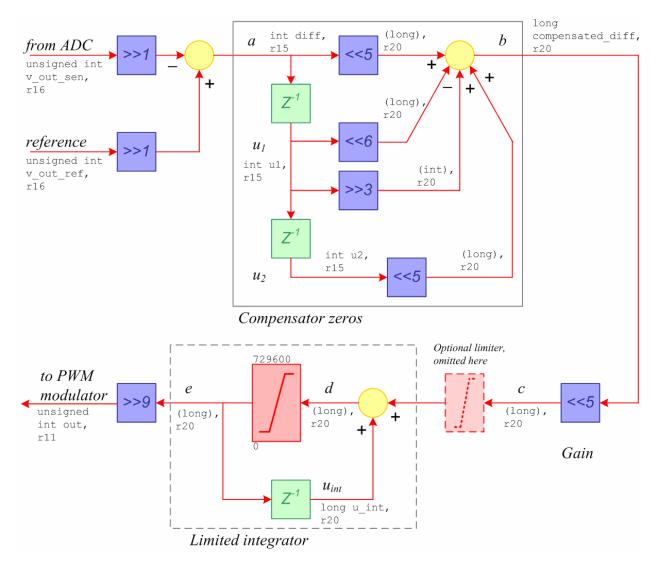

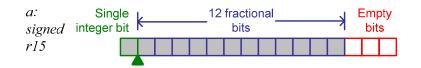

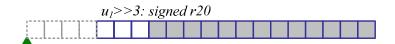

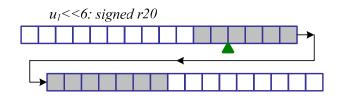

(4.10)