University of Central Florida

Electronic Theses and Dissertations, 2004-2019

2008

# A Competitive Reconfiguration Approach To Autonomous Fault Handling Using Genetic Algorithms

Kening Zhang University of Central Florida

Part of the Computer Engineering Commons Find similar works at: https://stars.library.ucf.edu/etd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS Citation**

Zhang, Kening, "A Competitive Reconfiguration Approach To Autonomous Fault Handling Using Genetic Algorithms" (2008). *Electronic Theses and Dissertations, 2004-2019.* 3499. https://stars.library.ucf.edu/etd/3499

# A COMPETITIVE RECONFIGURATION APPROACH TO AUTONOMOUS FAULT HANDLING USING GENETIC ALGORITHMS

by

KENING ZHANG B.S. Xidian University, 1998 M.S. University of Central Florida, 2004

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the School of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Summer Term 2008

Major Professor: Ronald F. DeMara

© 2008 Kening Zhang

## ABSTRACT

In this dissertation, a novel self-repair approach based on Consensus Based Evaluation (CBE) for autonomous repair of SRAM-based Field Programmable Gate Arrays (FPGAs) is developed, evaluated, and refined. An initial population of functionally identical (same input-output behavior), yet physically distinct (alternative design or place-and-route realization) FPGA configurations is produced at design time. During run-time, the CBE approach ranks these alternative configurations after evaluating their discrepancy relative to the consensus formed by the population. Through runtime competition, faults in the logical resources become occluded from the visibility of subsequent FPGA operations. Meanwhile, offspring formed through crossover and mutation of faulty and viable configurations are selected at a controlled re-introduction rate for evaluation and refurbishment. Refurbishments are evolved in-situ, with online real-time input-based performance evaluation, enhancing system availability and sustainability, creating an Organic Embedded System (OES).

A fault tolerance model called N Modular Redundancy with Standby (NMRSB) is developed which combines the two popular fault tolerance techniques of NMR and Standby fault tolerance in order to facilitate the CBE approach. This dissertation develops two of instances of the NMRSB system – Triple Modular Redundancy with Standby (TMRSB) and Duplex with Standby (DSB). A hypothetical Xilinx Virtex-II Pro FPGA model demonstrates their viability for various applications including a 3-bit x 3-bit multiplier, and the MCNC91 benchmark circuits. Experiments conducted on the model evaluate the performance of three new genetic operators and demonstrate progress towards a completely self-contained single-chip implementation so that the FPGA can refurbish itself without requiring a PC host to execute the Genetic Algorithm.

This dissertation presents results from the simulations of multiple applications with a CBE model implemented in the C++ programming language. Starting with an initial population of 20 and 30 viable configurations for TMRSB and DSB respectively, a single stuck-at fault is introduced in the logic resources. Fault refurbishment experiments are conducted under supervision of CBE using a fitness state evaluation function based on competing outputs, fitness adjustment, and different level threshold. The device remains online throughout the process by which a complete repair is realized with Hamming Distance and Bitweight voting schemes. The results indicate a Hamming Distance TMRSB approach can prevent the most pervasive fault impacts and realize complete refurbishment. Experimental results also show that the Autonomic Laver demonstrates 100% faulty component isolation for both Functional Elements (FEs) and Autonomous Elements (AEs) with randomly injected single and multiple faults. Using logic circuits from the MCNC-91 benchmark set, availability during repair phases averaged 75.05%, 82.21%, and 65.21% for the z4ml, cm85a, and cm138a circuits respectively under stated conditions. In addition to simulation, the proposed OES architecture synthesized from HDL was prototyped on a Xilinx Virtex II Pro FPGA device supporting partial reconfiguration to demonstrate the feasibility for intrinsic regeneration of the selected circuit.

# TABLE OF CONTENTS

| LIST OF | FIG   | URES                                                                 | viii |

|---------|-------|----------------------------------------------------------------------|------|

| LIST OF | F TAE | BLES                                                                 | X    |

| CHAPTI  | ER 1: | INTRODUCTION                                                         | 1    |

| 1.1.    | Intro | oduction to Genetic Algorithms                                       | 1    |

| 1.2.    | Usii  | ng Evolvable Hardware to Increase Reliability                        | 3    |

| 1.3.    | FPC   | GA Architecture                                                      | 7    |

| 1.3.    | 1.    | Xilinx FPGA Architecture                                             | 7    |

| 1.3.    | 2.    | Hypothetical FPGA Architecture                                       | 9    |

| 1.4.    | Org   | anic Computing Concept                                               | . 11 |

| 1.5.    | Con   | tribution of Dissertation                                            | . 13 |

| 1.5.    | 1.    | Integrate Fault Detection, Isolation, Diagnosis, and Recovery phases | . 15 |

| 1.5.    | 2.    | Realize Adaptable Quality of Service (QoS) Levels for Reliability    | . 15 |

| 1.5.    | 3.    | Realize Online Device Refurbishment                                  | . 15 |

| 1.5.    | 4.    | Proposed Self-Recovery Architecture                                  | . 16 |

| CHAPTI  | ER 2: | PREVIOUS WORK                                                        | . 18 |

| 2.1.    | Ove   | rview                                                                | . 18 |

| 2.2.    | EHV   | W Approaches to Increases Reliability                                | . 18 |

| 2.3.    | Self  | -X properties on Organic Architecture                                | . 22 |

| 2.4.    | TM    | R and Standby System Application on Improving Reliability            | . 26 |

| CHAPTI  | ER 3: | TMR, STANDBY AND TMRSB SYSTEM                                        | . 29 |

| 3.1.    | Ove   | rview of Traditional Fault Tolerance Strategy                        | . 30 |

| 3.1.    | 1.    | Embedded Device Properties Influencing Redundancy Strategies         | . 33 |

| 3.2.    | Syst  | tem Reliability Analysis                                             | . 38 |

| 3.2.1. Standby System                                                       | . 38 |

|-----------------------------------------------------------------------------|------|

| 3.2.1.1. Imperfect Switching                                                | . 40 |

| 3.2.1.2. Unknown Configurations Status                                      | . 43 |

| 3.2.2. NMR System                                                           | . 45 |

| 3.2.3. Hybrid System                                                        | . 47 |

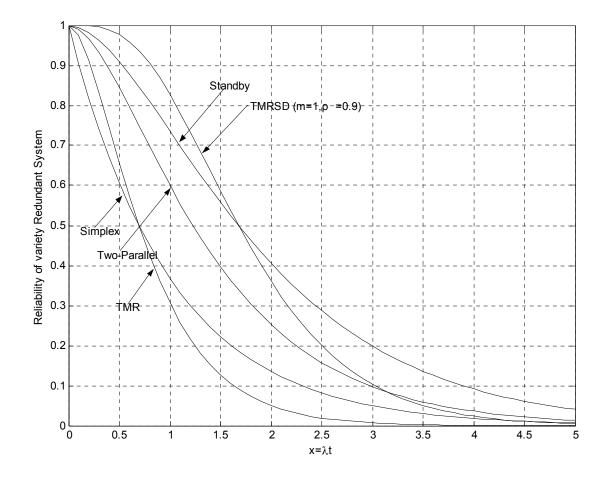

| 3.3. Simulation Result                                                      | . 50 |

| CHAPTER 4: AUTONOMOUS REPAIR USING COMPETITIVE RUNTIME RECONFIGURATION      | . 54 |

| 4.1. Detecting Faults using a Population of Alternatives                    | . 54 |

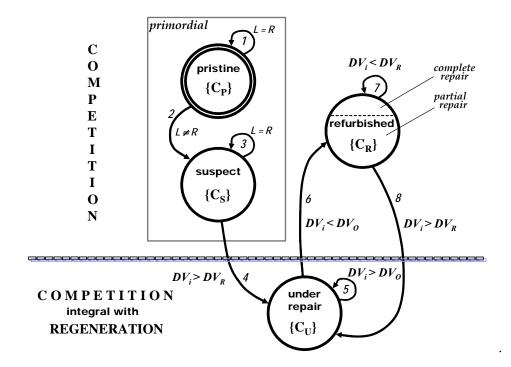

| 4.2. CBE Approach                                                           | . 56 |

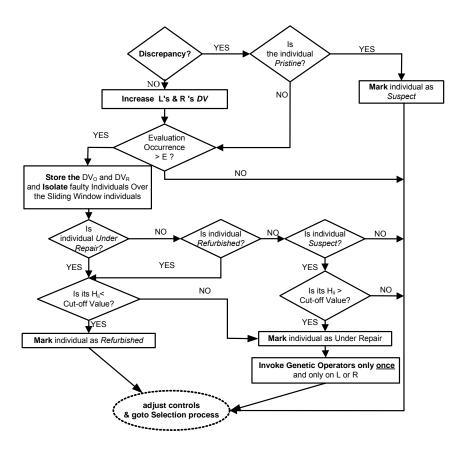

| 4.3. Self-Adaptive Fitness Assessment using Outlier Identification          | . 58 |

| 4.4. Achieving Device Refurbishment                                         | . 61 |

| CHAPTER 5: PERFORMANCE EVALUATION OF CBE APPROACH                           | . 63 |

| 5.1. Circuit Representation and Benchmark Characteristics                   | . 63 |

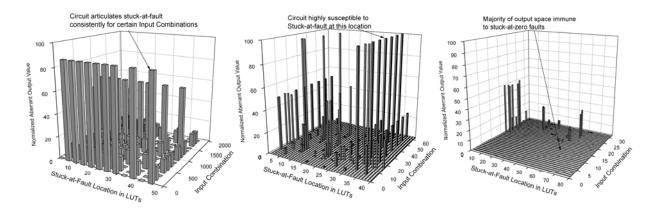

| 5.2. Quantifying Search Space Complexity under Fault                        | . 66 |

| 5.3. Source of Redundancy in Digital Circuits                               | . 68 |

| 5.4. Initial Circuit Population Design                                      | . 69 |

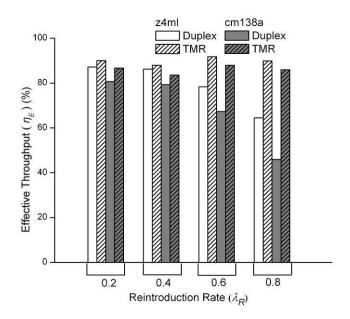

| 5.5. Effect of Reintroduction Rate on Refurbishment Performance             | . 73 |

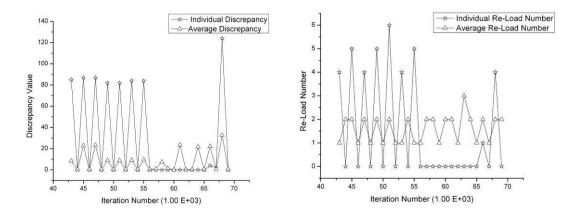

| 5.6. Comparing Discrepancy Scoring Schemes                                  | . 75 |

| 5.7. Recovery from Pervasive Faults                                         | . 78 |

| CHAPTER 6: FAULT MONITORING AND RECOVERING USING ORGANIC COMPUTING APPROACH | . 80 |

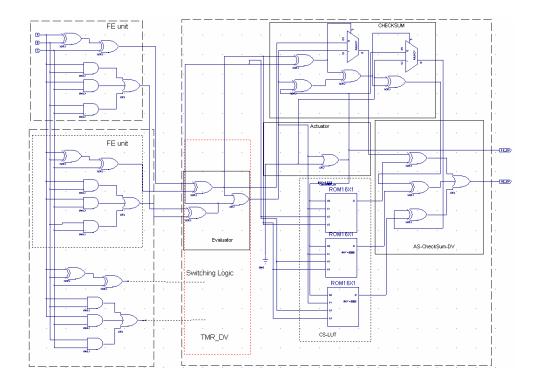

| 6.1. Embedded Organic Computing Architecture                                | . 80 |

| 6.1.1. Requirements and Architectural Overview                              | . 80 |

| 6.1.2. System Operation                                                     | . 83 |

| 6.1.2.1.        | System Initialization Phase                              | 84  |

|-----------------|----------------------------------------------------------|-----|

| 6.1.2.2.        | FE Fault Detection/Recovery and AE monitoring Phase      | 85  |

| 6.1.2.3.        | AE Fault Detection Phase                                 | 86  |

| 6.1.3. CBE      | evaluation process and AE fault recovery Phase on the AS | 87  |

| 6.2. Evolution  | ary Process FE and AE                                    | 88  |

| 6.2.1. Geno     | otype Definition                                         | 88  |

| 6.2.2. Gene     | etic Operations                                          | 90  |

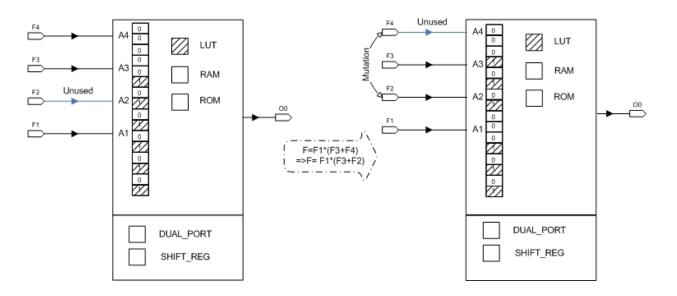

| 6.2.2.1.        | Mutation Operation                                       | 90  |

| 6.2.2.2.        | Cell-Swap Operation                                      | 91  |

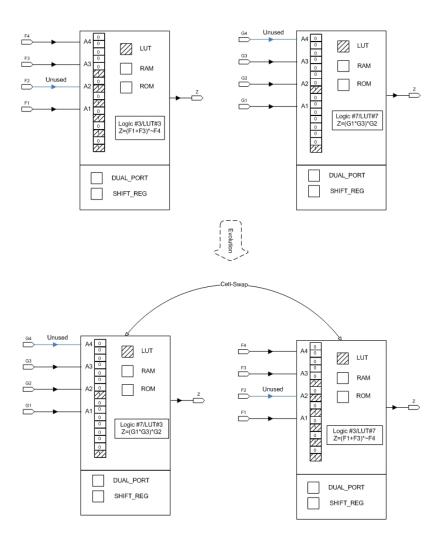

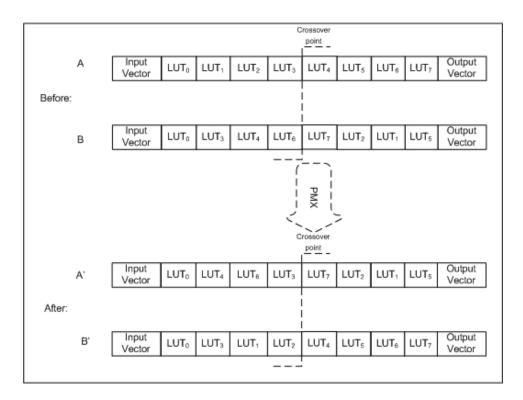

| 6.2.2.3.        | Partial Match Crossover Operation                        | 93  |

| 6.2.3. Cons     | ensus Based Evaluation (CBE)                             | 95  |

| 6.3. Experiment | nt Configuration                                         | 96  |

| 6.3.1. FE an    | nd AE Failure Coverage                                   | 96  |

| 6.3.2. Singl    | le vs. Multiple Fault Coverage                           | 96  |

| 6.3.3. Hard     | ware Prototype                                           | 99  |

| 6.4. Result and | d Analysis                                               | 101 |

| CHAPTER 7: CO   | DNCLUSION                                                | 110 |

| 7.1. OVERVII    | EW                                                       | 110 |

| 7.2. Evolvable  | Hardware and CBE                                         | 111 |

| 7.3. Organic C  | Computing Architecture                                   | 113 |

| 7.4. Future Wo  | ork                                                      | 115 |

| LIST OF REFEREN | VCES                                                     | 117 |

# LIST OF FIGURES

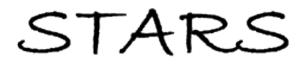

| Figure 1: Genetic Algorithm Process                                                   | 2  |

|---------------------------------------------------------------------------------------|----|

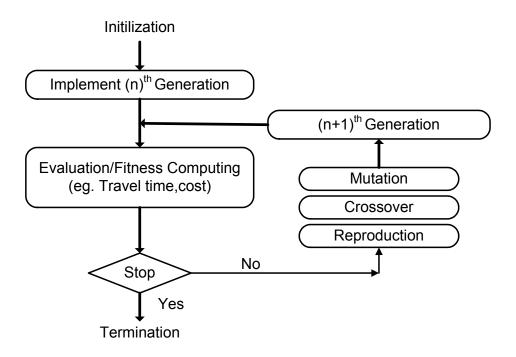

| Figure 2: Xilinx Virtex-II Pro device Generic Architecture Overview                   |    |

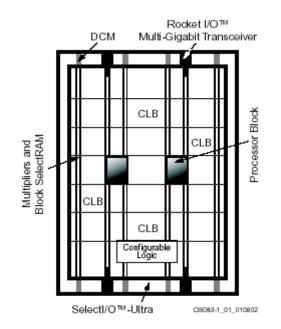

| Figure 3: Genotype in a rectangular array cells                                       | 10 |

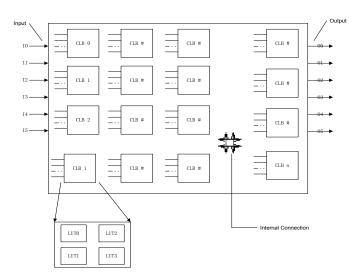

| Figure 4: Genotype array representations                                              | 11 |

| Figure 5: Dual-Layer ASoC platform from Lipsa et al [29]                              | 12 |

| Figure 6: TMR System                                                                  |    |

| Figure 7: Standby System                                                              |    |

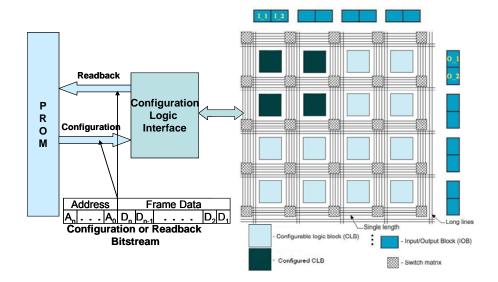

| Figure 8: FPGA Configuration and Readback Mechanism                                   |    |

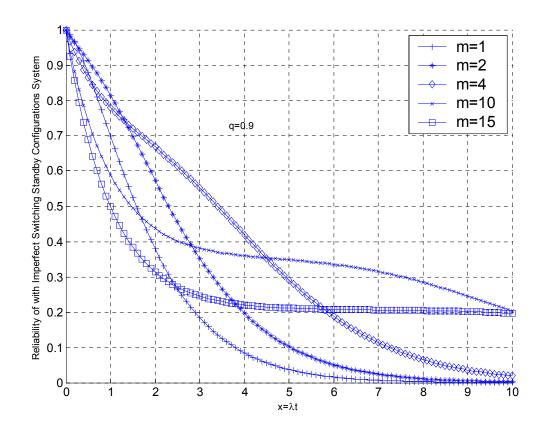

| Figure 9: Reliability of Imperfect Switching Standby System                           |    |

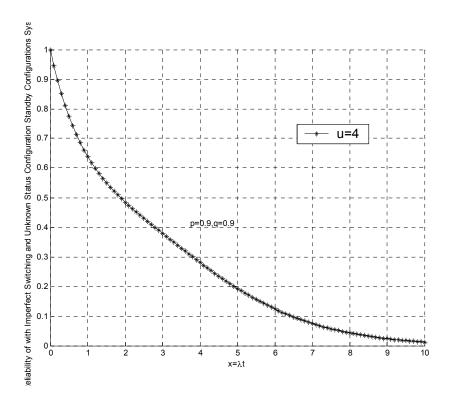

| Figure 10: The Standby System with Imperfect switching and Unknown Co<br>Status       |    |

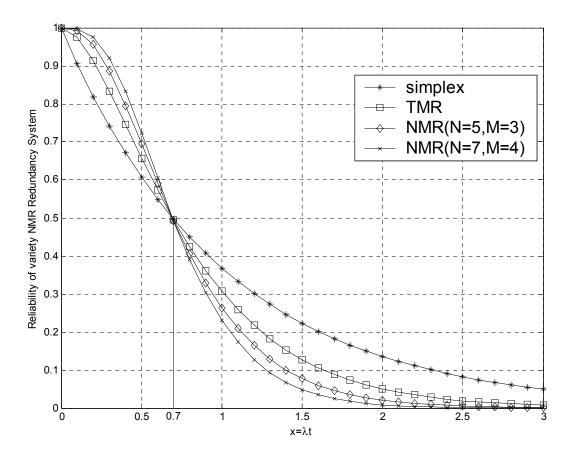

| Figure 11: NMR System                                                                 |    |

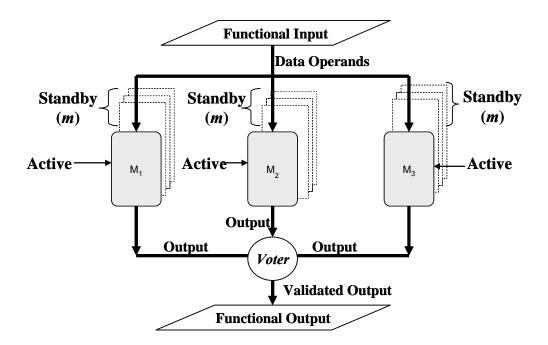

| Figure 12: TMRSB System                                                               |    |

| Figure 13: Comparison of Simplex, TRM, Two-Parallel-Redundancy, Standle Reliabilities | -  |

| Figure 14: States in the Lifetime of the <i>i</i> <sup>th</sup> Half-Configuration    | 57 |

| Figure 15: Fitness State Adjustment Process in the CBE Technique                      |    |

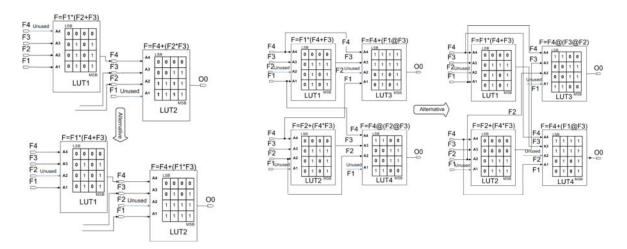

| Figure 16: Generation of Alternate Configurations by –                                | 64 |

| Figure 17: MCNC91 Benchmark Circuit Sensitivity to Stuck-at Faults                    | 67 |

| Figure 18: Prioritizing Individuals for Refurbishment                                 | 69 |

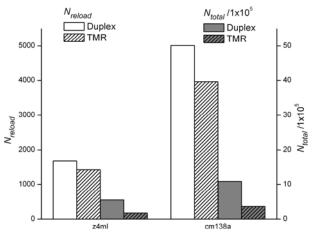

| Figure 19: Effective Throughput $\eta_E$ during Regeneration Under Duplex and TMR M of Operation |       |

|--------------------------------------------------------------------------------------------------|-------|

| Figure 20: Comparison of Performance Characteristics under Duplex and TMR Mode                   | es 70 |

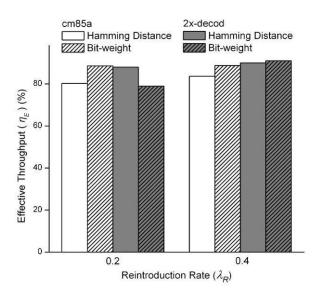

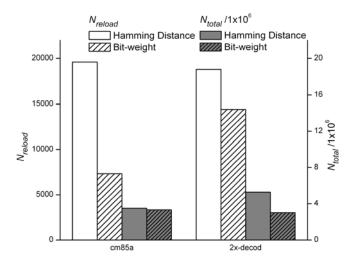

| Figure 21: Effective Throughput with Hamming Distance and Bit-weight Schemes                     | 76    |

| Figure 22: CBE Performance Characteristics with Hamming Distance and Bit-w<br>Schemes            | -     |

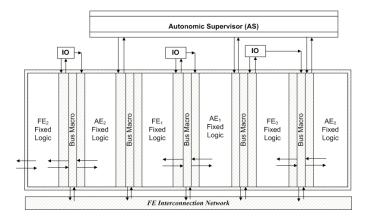

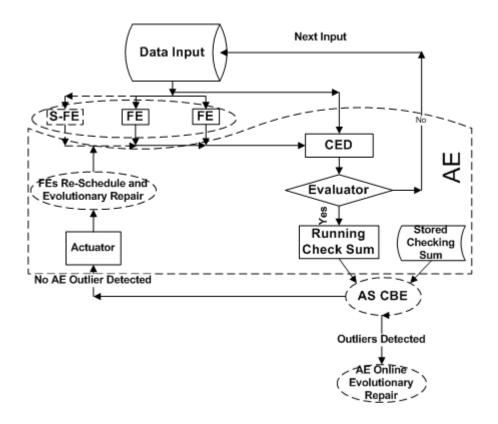

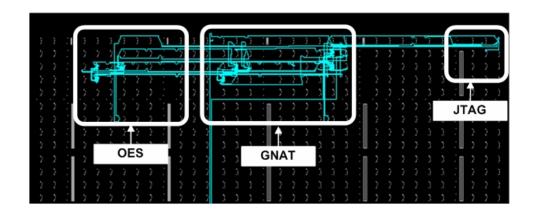

| Figure 23: Column-oriented OES on Xilinx Virtex II Pro FPGA platform                             | 81    |

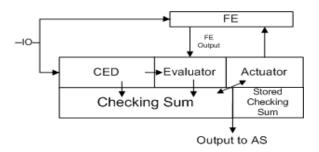

| Figure 24: AE architecture in OES                                                                | 82    |

| Figure 25: OES Integrated FE and AE Failure Detection Procedure                                  | 84    |

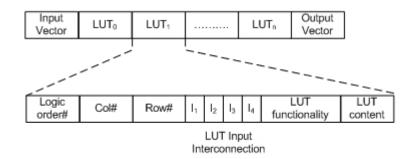

| Figure 26: Genotype Chromosomes of GA Operation                                                  | 89    |

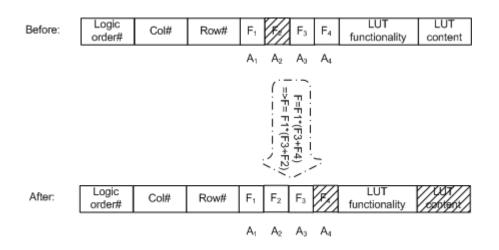

| Figure 27: Mutation on the Genotype Chromosomes                                                  | 91    |

| Figure 28: Mutation on the Phenotype                                                             | 91    |

| Figure 29: Cell-Swap operation on Genotype chromosomes                                           | 92    |

| Figure 30: Cell-Swap operation on Phenotype chromosomes                                          | 93    |

| Figure 31: PMX operation on Genotype chromosomes                                                 | 94    |

| Figure 32: Gate Level Design of OES (Case study)                                                 | . 100 |

| Figure 33: Physical Layout of OES system on FPGA with GNAT/JTAG shown                            | . 101 |

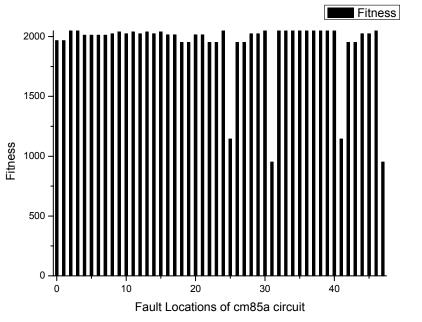

| Figure 34: Fitness as a function of 12 LUTs with 48 fault locations tested                       | . 103 |

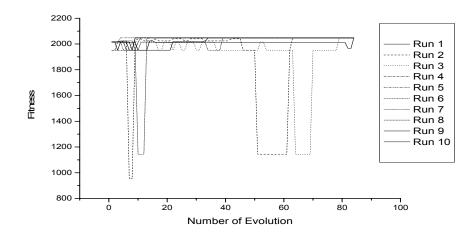

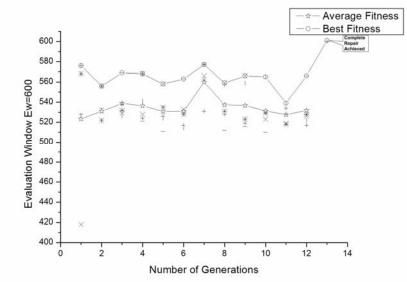

| Figure 35: cm85a FE Evolutionary Recovery without CBE                                            | . 107 |

| Figure 36: AE Evolutionary Repair for cm85a Circuit using CBE                                    | . 108 |

# LIST OF TABLES

| Table 1: Attributes of proposed technique                                                                           |

|---------------------------------------------------------------------------------------------------------------------|

| Table 2: Fault Recovery Characteristics of Selected Approaches    22                                                |

| Table 3 Performance Characteristics of FPGA-based Fault Tolerance technique                                         |

| Table 4 Stadnby System Simulation Result                                                                            |

| Table 5 TMRSB Simulation Result    52                                                                               |

| Table 6: Characteristics of Benchmark Circuits    66                                                                |

| Table 7: CBE Performance under Duplex and TMR Modes for Two Different Circuits. 72                                  |

| Table 8: Number of Fully Refurbished Individuals vs. Effect of Reintroduction Rate ( $\lambda_R$ )for Four Circuits |

| Table 9: CBE Performance under Hamming Distance and Bit-weight Performance      Evaluation Schemes                  |

| Table 10: MCNC-91 Benchmark Circuits Evaluated on OES Architecture                                                  |

| Table 11: z4ml Circuit Experiment Results                                                                           |

| Table 12: cm85a Circuit Experiment Results    105                                                                   |

| Table 13: cm138a Circuit Experiment Result                                                                          |

# CHAPTER 1: INTRODUCTION

#### 1.1. Introduction to Genetic Algorithms

In computer science, Evolutionary Computation (EC) [1] is a subfield of Artificial Intelligence (AI) [2] that involves combinatorial optimization problems which uses iterative progress, such as growth or development in a population using guided random search to achieve the desired end. Two developed techniques involved in EC which are based on identical principles, but different biology behaviors are Evolutionary Algorithms (EAs) [3] and Swarm Intelligence (SI) [4]. They have been heavily researched and implemented in different problem solutions which start from limited available information about uncertain environment and eventually develop an approximated informative solution based on interaction of the population solutions themselves. EA emphasizes population-based metaheuristic optimization approach which is composed of Genetic Algorithms (GA) [5], Evolutionary Programming (EP) [6], Evolutionary Strategy (ES) [7], Genetic Programming (GP) [8-10] and Learning Classifier System (LCS) [11], while SI is more based around the study of collective behavior in decentralized system which composed of Ant Colony Optimization (ACO) [12] and Particle Swarm Optimization (PSO) [8]. This dissertation concentrates on developing EA-based approach for fault-handling methods.

Genetic Algorithms (GAs) [1] are the most popular EA technique inspired by biological mechanisms of evolution used in finding exact or approximated solutions to either search problems or optimization problems originated by John H. Holland and his colleagues at the University of Michigan in the 1970s. A computer simulation, a population of individuals,

each of which represents a potential solution to the problem, explores and exploits the search space in response to the environment of the individuals undergoing adaptation. An individual is encoded by various computer manipulatable structures, and the typical structure is a binary string although the best representations are determined by the problem being solved. Problem representation is one of the key decisions to be made when applying a GA because it may affect the adaptation process in terms of shape of the solution space that a GA searches through as well as solution complexity and precision. Furthermore, a measurement of the performance of the population named the *Fitness Function* is implemented to select the candidate for the next generation for further operation. Figure 1 below shows a conventional GA flow.

Figure 1: Genetic Algorithm Process

The GA repeats the above steps in Figure 1 iteratively in order to create better designs. The procedure begins with the initialization of the *individuals* in the population. An evaluation mechanism for the assessing the suitability of each individual design in the population is utilized called a *fitness function*. A fitness function computes how well a particular design performs in terms of some specific metrics. Different operators like *mutation* and *crossover* will be used for new offspring generations until the stop condition can be achieved for termination the process. The application field of GA is focused on the optimization and search problems which appear in biogenetics, computer science, engineering, economics, chemistry, manufacturing, mathematics, and physics [3, 8, 10, 13-17]. Evolvable Hardware is one of emerging application fields which emphasizes digital circuit design and fault tolerance based on reprogrammable devices.

#### 1.2. Using Evolvable Hardware to Increase Reliability

Reliable embedded computing systems are vital to every sector of our economy and daily personal lives. Embedded systems using *Field Programmable Gate Arrays (*FPGAs) are frequently relied upon in mission-critical applications like deep space explore missions where the safety of human life and material assets are at risk. The recent availability of large multi-million gate-equivalent FPGAs provides the necessary resources facilitates the feasibility of using *Genetic Algorithms* (GAs) on these devices. GAs are used to evolve diverse and competitive solutions for a variety of problems, ranging from the general to the specific, by occluding the faults in the device at runtime. The reason GAs can be an appropriate adaptive mechanism for embedded systems are that they can adjust the solution quality without external control or

supervision. GAs can also adapt and respond to many unforeseen fluctuations in the operating environment.

*Evolvable Hardware* (EHW) [10, 14, 18] combines the benefits of reconfigurable hardware with GAs to offer efficient solutions to fault-related problems. Conventionally, EHW can be classified into two categories depending on the method of simulation. In the *Extrinsic Evolutionary* method, the physical condition of real circuits is simulated and a user defined genotype is used to evolve each individual outside of the real chip. Finally, the best-fit individual is selected and programmed into the real chip. On the other hand, in the *Intrinsic Evolutionary* method, the fitness is evaluated at run-time by using the phenotypes of the individuals directly in the real chip.

Depending on the application, EHW can be classified into two categories. One perspective is an alternative to traditional, specification-based manual circuit design techniques. In the other perspective, EHW is online device capability for autonomous reconfiguration. This dissertation will view EHW along the lines of the second approach. A fundamental difference of these two views is the former places the emphasis on the design phase and the latter emphasizes the execution, or run-time phase. The evolutionary design approach has several advantages as compared to the manual approach. For example, no a-priori knowledge is required on the specific domain, and the availability of a wider search space may help exploration of novel solutions.

With benefits of the EHW introduced in the previous section, still, there exist some substantial obstacles to overcome before there is wide utilization of this approach. First of all, the limited

number of optimal/suboptimal potential solutions within a large the gigantic search space always lead to excessive evolution time even under parallel search with multiple individuals in a population. This may not satisfy the cost-effective and efficiency of most problem solving criteria. For example, suppose there is a 2-bit adder composed of 10 gates and each gate can be implemented using 4 different functionalities (AND, OR, XOR, NOT). Without considering interconnection, there are 4<sup>10</sup> possible ways and whenever one more gate is added to current design, that will increase 4-fold the possible designs over the previous designs. Instead of starting from scratch, some heuristic approaches have to be used as auxiliary tools to assistance exploring and exploiting the search space. To address this problem, a diverse population is used to supply candidate solutions initially as described below. Previous work did not investigate the benefit of diversity.

Secondly, each candidate problem is going to use specific application dependent fitness function to evaluate the new generated individuals for further evolution. Until now, no one has been proposed any universal fitness functions which can fit even similar classes of applications. However, without a versatile fitness function, it is difficult to assess how adaptive it will be for a GAs concept. Since a special fitness function must be dedicated for certain application in order to get accurate evaluation, knowing all of the circuit functionalities becomes a prerequisite system constraint which definitely decreases the feasibility of the GA utilization. To address this problem, this dissertation develops a standardized fitness assessment scheme based on discrepancy behavior suitable for any combinational logic circuit.

Lastly, most current EHW research is focused on digital circuit design which use randomly generated configurations as seeds which are evolved further with new offspring individuals in

subsequent generations. Starting from scratch is one possible way for small design, but not appropriate for design scalability since current FPGA device have multi-million gate capacities. Unlike conventional fault tolerance technology such as Triple Module Redundancy (TMR) [19] which uses majority information to maintain the current output for the system, there is no previously proposed idea to utilize the majority of the operational information contained in the population to maintain the system performance.

Consensus Based Evaluation (CBE) for autonomous repair of SRAM-based Field Programmable Gate Arrays (FPGAs) proposed in the dissertation is first implemented as a system using a general population consensus information to replace the specific fitness function based on a predesigned population of functionally identical (same input-output behavior), yet physically distinct (alternative design or place-and-route realization) FPGA configurations. Instead of exploring the entire search space for the solution, any surviving individuals under a fault condition will be used as starting point for evolution. Furthermore, even if there are no individuals that survive unaffected, the population still can maintain acceptable system availability using partial working configuration which may not generate all possible correct outputs, yet maintain a useful amount of correct outputs.

For the CBE approach, the target applications are those mission-critical embedded systems which can utilize hundreds of field programmable devices with very limited capacity for spares. Another feature is that human intervention is infeasible for such applications in deep space or deep sea missions which required autonomy self-recovery as primary functionality. Also even they are mission-critical, using background evolution cycles, the system still provides attractive alternatives to device redundancy under graceful degradation except for catastrophic failures.

However, the system is not required to anticipate any specific environment it will experience and instead can dynamically adjust its configuration according to correspondent external conditions.

Two experimental applications are presented in this dissertation. One is using standard benchmark circuits implemented on an FPGA software model for system reliability analysis and the other on a prototype of an Organic Computing model. Both applications are using Xilinx Virtex-II Pro architecture model as hardware platform which introduced in next two sections and detailed in Chapter 4 and 5. The last section of this chapter presented the research objectives of this dissertation in more detail.

## 1.3. FPGA Architecture

#### 1.3.1. Xilinx FPGA Architecture

The FPGA hypothetical model is inspired by Xilinx-style architecture [20-22].

Figure 2: Xilinx Virtex-II Pro device Generic Architecture Overview

- Virtex-II Pro devices, as shown in Figure 2, are built on the Virtex-II FPGA architecture and are user-programmable gate arrays with various configurable elements and embedded cores optimized for high-density and high-performance system designs. The Virtex-II Pro family has the following features crucial to the design.

- Up to 22,592 Configurable Logic Blocks (CLBs) provide abundant reconfigurable recourses [21] with strong functional elements for combinatorial and synchronous logic, including basic storage elements (distributed RAM), MUX, fast carry chains, arithmetic logic, and BUFTs (3-state buffers).

- Up to four Incorporated embedded PPC405 cores in a single Virtex-II Pro device operate up to 400+ MHz with specially designed interface logic integrates the core with the surrounding CLBs, block RAMs, and general routing resources, which not only makes the implementation of autonomous system possible but also brings more flexibility and possibility to carry out complex reconfiguration application, such as GAs, in an even faster way by reducing off-chip I/O.

- A large amount of memory are available on-chip and on board, including the onchip block RAM, on-board SDRAM SODIMM, Mobile SDRAM, Asynchronous SRAM and Flash, which provides huge extension for large calculation and reconfigurations.

The additional functionalities, such as Embedded 18-bit x 18-bit multipliers, Digital Clock Manager (DCM) blocks and multi-gigabit transceiver blocks, etc, [20], may greatly enhance programmable logic design and provide possible application extensions in the future as well.

## 1.3.2. Hypothetical FPGA Architecture

The hypothetical structure used in this dissertation is shown in Figure 3, which is similar to the architecture introduced in section 1.3.1. The feed-forward combinational logic digital circuit uses a rectangular array of nodes with two inputs and one output. Each node represents a Look-up Table (LUT) in the FGPA device, and a Configurable Logic Block (CLB) is composed of four LUTs. In the array, each CLB will be a row of the array and two LUTs are represented as four columns of the array. There are five dyadic functions -- OR, AND, XOR, NOR, NAND --

and one unary-function NOT, each of which can be assigned to an LUT. The LUTs in the CLB array will be indexed from 1 to *n*. This linear labeling enforces a feed-forward property in the combinational digital circuit for the array interconnection and routing.

Array routing is defined by the internal connectivity and the inputs/outputs of the array. Internal connectivity is specified by the connections between the array cells. The inputs of the cells can only be the outputs of cells with lower row numbers. Alternatively, the outputs of each cell are only allowed to be inputs of cells with higher row numbers.

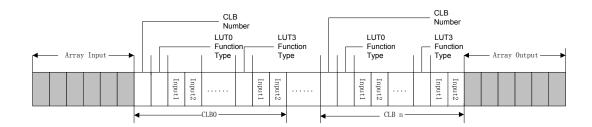

Figure 3: Genotype in a rectangular array cells

A phenotype is any observable characteristic of an organism, such as its morphology, development, biochemical or physiological properties, or behavior. They can also be represented as a linear string of integers as shown in Figure 4. This scheme is comprised of multiple CLB fields as well as array input and output fields. Array input-output fields are at the beginning and at the end of the entire configuration. Each CLB field is composed of a number of component

LUTs whose functionality and interconnection is specified. The first bit of the CLB field is the CLB number that indicates the relative order of the CLB in the entire configuration. Each LUT field within the CLBs is composed of a bit which reflects the functionality and bits which reflect the two inputs of the LUT. The array input and output sections both have six input bits and six output bits at the beginning and the end of the configuration.

Figure 4: Genotype array representations

#### 1.4. Organic Computing Concept

The realizations of systems that are capable of exhibiting such adaptive behaviors constitute the vision sought by *Organic Computing (OC)* [23]. OC *self-x* properties include self-configuration, self-reorganization, and self-healing which comprise the focus of this dissertation [23-26]. Ideally, these objectives are maintained in an autonomous fashion, yet sufficiently constrained to avoid undesirable emergent behaviors. In particular, OC systems rely on self-organization to respond to internal imbalances and changing environmental conditions using *an Observer/Controller* architecture [23, 27, 28].

To provide OC architectures with sufficient capability for exhibiting self-adaptive behavior, reconfigurable logic devices offer an attractive hardware platform. SRAM-based Field

Programmable Gate Arrays (FPGAs) logic devices can realize self-adaptation within their reconfigurable logic fabric using Evolvable Hardware techniques. Since evolution is employed, the *Observer/Controller* has the task of detecting internal/external errors and well as initiating reconfiguration when necessary.

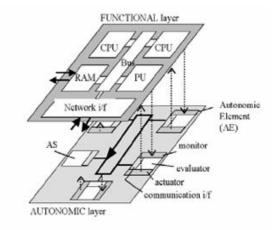

A widely known generic OC platform called the Autonomous System-on-a-Chip (ASoC) architecture proposed in [29] is depicted in Figure 5. The ASoC platform consists of two layers: the *Functional* Layer and the *Autonomic Layer*. The Autonomic layer contains *Autonomic Elements (AEs)* that are responsible for correct operation of the corresponding *Functional Elements (FEs)* present on the Functional Layer. Every FE such as CPU, RAM, and Network Interface has a counterpart Monitor, Evaluator, and Actuator component within the Autonomic Layer. The Autonomic Layer (AS) that has no counterpart on the Functional Layer. The AS is responsible for the correct functionality of all AEs on the Autonomic Layer.

Figure 5: Dual-Layer ASoC platform from Lipsa et al [29]

The Dual-Layer ASoC design approach in Figure 5 is extended herein to provide fault coverage at both the Functional Layer and Autonomic Layer. This is achieved by assessing consensus among elements in a two-fold approach. Consensus is used first to realize failure detection. Once identified, consensus provides an organic method for fitness evaluation of competing alternatives during evolution providing a self-regulating approach to fault resolution. The measured performance is analyzed as an integrated OC system for self-configuration and self-healing. This demonstrates a generic OC architecture that can detect faults and refurbish itself while still providing a degraded level of valid throughput even during the online repair period.

#### 1.5. Contribution of Dissertation

One point which comes through clearly from the previous discussion is that the fitness function is indispensable central composition of the GA process. It measurs the performance of different individual's structure and makes a trajectory through the possible solution search space under the successive GA operations. Conventionally, most GA applications such as function optimization and scheduling problems perceived their ultimate objectives prior to the design time. However, for the real time electronic device, the operation environment is full of unknown factors which may not be apparent to the designers. Even worse, the devices may be affected by a fluctuating operational environment during long execution times. Apparently, the static Fitness function cannot provide sufficient support for such applications. With FPGA devices in most missioncritical applications confront severe natural conditions, a new approach should be proposed and evaluated. In response to the questions presented above, a consensus based Fitness evaluation approach is presented in this dissertation using population information and a new fault tolerance model which embedded both traditional TMR and Standby system and FPGA device reconfiguablity property in order to facilitate real-time competitive computing for autonomous regeneration of embedded reprogrammable model. An analytical software model is constructed to simulate the large-scale reconfigurable on-chip resources. Failures will be occluded by iteratively developed adaptive reconfiguration techniques in Extrinsic Evolvable Hardware. The most significant attributes and advantages are listed in Table 1.

| Technique<br>Terminology                                         | Problem Domain                     | Attributes of Proposed<br>Approach                                                   | Significant Contribution                                                                                                                    |  |

|------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

| Consensus<br>Based<br>Evaluation<br>(CBE)                        | Genetic algorithm fitness function | Population-based<br>evaluation which is driven<br>by execution environment           | First use of fitness function<br>that depends on explicitly<br>global population<br>information and implicitly<br>environmental information |  |

| Triple<br>Modular<br>Redundancy<br>+ Standby<br>Model<br>(TMRSB) | Reliability model                  | TMR with standby<br>individuals in component-<br>level                               | First proposed reliability<br>model which takes<br>advantage of the<br>reconfiguration capacity in<br>FPGA device                           |  |

| Evolutionary<br>Organic<br>Computing<br>Architecture<br>(OC)     | Self-organization<br>architecture  | Autonomous fault-<br>detection and self-recovery                                     | New OC architecture with utilization of EHW idea                                                                                            |  |

| Specific<br>Genetic<br>Operators                                 | Genetic operators                  | Genetic operators which<br>can manipulate the<br>configuration of<br>SRAM-based FPGA | New operators which are<br>specifically designed to<br>facilitate SRAM-based<br>FPGA genetic operation                                      |  |

Table 1: Attributes of proposed technique

This novel self-regeneration approach for embedded systems is based on CBE. Instead of using redundant spares to handle failures, it synthesizes fault-specific reconfigurations to regain lost functionality. Mechanisms of competitive computation are developed to achieve each Research Objective identified below.

#### 1.5.1. Integrate Fault Detection, Isolation, Diagnosis, and Recovery phases

Real-time competitive computing approaches for autonomous regeneration of embedded reprogrammable model are developed and evaluated in this dissertation. An analytical software model is constructed to simulate the large-scale reconfigurable on-chip resources. Failures are occluded by adaptive reconfiguration techniques for Extrinsic Evolvable Hardware.

#### 1.5.2. Realize Adaptable Quality of Service (QoS) Levels for Reliability

A novel self-adaptive population-based mechanism for all fault-handling stages in embedded reconfigurable devices is developed. This approach will *detect* faults by comparing outputs of competing configuration alternatives. By comparing discrepancies from alternative configurations, it is possible to *isolate* the failed physical resource. Remapping operators are then used to realize a failure-specific *refurbishment* during normal operations to make detailed physical failure mode *diagnosis* unnecessary. The refurbishment procedure will be realized using established mechanisms of *crossover*, *mutation*, and *deterministic guided search*. This objective will be realized with an experimental hardware-in-the loop research strategy.

#### 1.5.3. Realize Online Device Refurbishment

By varying only an FEW parameters of the competition process, a wide range of reliability vs. overhead tradeoffs are obtained. Under the CBE technique, the costs of FPGA resource space

overhead, additional power consumption, and throughput delay incurred to support regeneration are *continuously variable*. Analytical modeling of these costs provides us not only a composite measure of system performance, but also feedback for adaptively reconfiguring FPGAs. Specifically, the *Evaluation Window Interval* and *Re-introduction Rate* can be updated according to recent discrepancy counts in order to maintain a suitable *Mean-Time-To-Repair* (MTTR) vs. *Mean-Time-Between-Failures* (MTBF) condition under adaptive and possibly hybrid control algorithms. To ensure system availability, parts need to be regenerated at a faster rate than they are failing such that a MTTR < MTBF condition is maintained. This objective of quantifying and optimizing the performance characteristics of the proposed CBE method will realize adaptive *Quality of Service (*QoS) levels for reliability via analytical modeling and advanced controls.

#### 1.5.4. Proposed Self-Recovery Architecture

It is demonstrated, with the exception of catastrophic failures, how a device can be refurbished online without additional *function* or *resource* test vectors. This will be achieved by integrating competition and refurbishment wholly within the *FPGA's* normal data throughput processing flow. Because a fitness adjustment function is used that favors fault-free behavior, the *FPGA's* normal input data throughput stream can be used to evaluate fitness states while the device is under normal operation. The benefits of fitness adjustment functions based on *Binary Discrepancy* and *Hamming Distance* will be determined. This research will be conducted by developing a unified framework that involves techniques from three separate areas:

combinatorial analysis of the problem space and statistical analysis of fault occurrence versus population size.

## CHAPTER 2: PREVIOUS WORK

#### 2.1. Overview

This chapter will present a broad overview and survey of the techniques utilized in this dissertation including EHW applications under GAs, OC architectures, and fault tolerance strategies. The most advantage of above techniques is presented as well as the drawback in terms of their efficiency, overhead, and adaptive capacity. The successful EHW [14, 15, 18, 30] [16] applications are shown in Section 2.2 and the OC architecture [23] introduction follows and finally the TMR and Standby fault tolerance system are analyzed in terms of their own properties.

#### 2.2. EHW Approaches to Increases Reliability

Several previous works describe other Regenerative Fault-Handling Techniques in EHW and how they attempt to actively restore mission-critical functionality in FPGA devices. They provide attractive alternatives to device redundancy for permanent degradation due to thermal fatigue, oxide breakdown, electromigration, and radiation-induced stuck-at-faults. Benefits of regeneration include fault recovery without the increased weight and size normally associated with spares. Also, failures need not be precisely diagnosed through external means, due to the intrinsic assessment of the remaining functionality on the device itself. Furthermore, a competitive regeneration approach enables failure-time synthesis of new FPGA configurations to handle failure scenarios that are unforeseen at design time. Lohn, Larchev, and DeMara [14, 15, 31] develop an FPGA bit-string representation along with mutation and two-point crossover operators for actively refurbishing interconnection as well as logic resources. This related work demonstrated the complete regeneration of a Quadrature Decoder on a Xilinx SRAM-based Virtex XCV1000 FPGA. It shows that a stuck-at-fault on the input to a FPGA's Configurable Logic Block (CLB) can be occluded through reconfiguration. The Genetic Algorithm (GA) developed synthesizes a new alternative configuration using evolution in a population of 40 competing configurations after a few hundred generations. The GA is shown to recycle the damaged part as well. It was observed that partially-damaged CLBs were reassigned to new functions based on the residual functionality that could be utilized in the refurbished configuration. While achieving complete regeneration for modestly-sized circuits, refurbishment was performed offline and required exhaustive fitness test vectors.

Lach's deterministic approach segments the FPGA into static tiles at design time with a known functionality, some redundant resources, and a pre-designed alternate configuration. Spare tiles can be selected when needed, but their functionality is predetermined and thus limited. On the other hand, Roving STARS [18] is a resource-oriented dynamic online test approach that performs Built-in Self-Tests (BISTs) on roving sub-sections of the FPGA. Each portion is continually taken offline in succession and tested while its functionality moved to a new location. STARS' detection latency can be excessive since the tests must sweep through all resources. Also, STARS' power consumption and unavailability due to unnecessary reconfigurations when no faults have yet occurred can be prohibitive.

An alternative approach is taken by Keymeulen, Stoica, and Zebulem [30] using a design-time emphasis. They develop evolutionary techniques so that field programmable circuits are initially

designed to remain functional even in presence of various faults. Their population-based fault tolerant design method evolves circuits and then selects the most fault-insensitive individual. This method provides good resource coverage and passive runtime operation. The technique may be applicable for constructing a diverse initial population under our proposed CBE approach.

Table 2 addresses active *Fault Recovery* characteristics. Ideally, recovery would be performed with the residual functionality in faulty device remaining online whenever possible, but only STARS and CBE attempt this. Vigander's and Lohn's methods exhibit likelihood of recovery related to the FPGA's *design complexity*. In other words, they try to design an original repair where only a single failed configuration is available from which to learn from. Instead, CBE draws upon a diverse population to bias search towards regions of alternative configurations that are still operational. While the quality of recovery under evolutionary approaches cannot be guaranteed, static redundancy approaches like Lach's are either completely recovered or completely beyond recovery. STARS' quality of recovery is restricted by a fixed routing scheme that cannot adapt.

As listed in Table 2, several active recovery approaches support resource recycling, including the CBE. Under the CBE, the frequency of reconfiguration can be varied to tradeoff configuration overhead vs. recovery capability. With regards to pre-determined system recovery limits, only dynamic competitive approaches are truly restriction-free. While competitive and evolutionary recovery approaches have been demonstrated on small applications, the focus of this dissertation will be to extend the methods to larger, more useful circuits using improved techniques of the CBE with statistical, adaptive, and hybrid design methods of control.

In this dissertation, CBE utilizes an innovative *temporal voting* approach whereby the outputs of just two competing instances are compared. The presence or absence of a discrepancy is used to adjust the fitness statues of both individuals without rendering any judgment at that instant on which individual is actually faulty. The faulty, or later exonerated, configuration is determined over time when each individual is paired with other competing configurations under certain times. The competitive process is applied repeatedly to form a strong consensus across a diverse pool of alternatives. Under CBE, the FPGA's outputs are compared before they leave the chip so fault detection occurs on the first erroneous output and detection latency is negligible. A unique advantage of this competition-based approach is that it also permits coverage for active elements of the fault comparator itself by embedding an instance of the fault checker in each configuration. Fault isolation in the TMR, Vigander, and Lach approaches are restricted to coarse predefined granularities. Meanwhile, STARS attempts to isolate resource faults at only the very finest granularity. Alternatively, as in Vigander's and Lohn/Larchev/DeMara's approach, CBE does not require fault isolation of a particular granularity in order to achieve refurbishment. Under CBE, transients reduce instantaneous fitness values, but their effects are automatically attenuated over time so that unnecessary refurbishment is not triggered given a properly-selected Threshold.

| Approach                      | Online<br>Recovery | Basis for<br>Likelihood of<br>Recovery          | Quality of<br>Recovery                                       | Availability                  | Externally-supplied<br>Elements                                                                                              | Potential for<br>Faulty<br>Resource<br>Recycling | Pre-<br>determined<br>Recovery<br>Limits                    |

|-------------------------------|--------------------|-------------------------------------------------|--------------------------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------|

| TMR                           | No                 | Not addressed                                   |                                                              |                               |                                                                                                                              |                                                  |                                                             |

| Vigander                      | No                 | Design<br>complexity                            | Non-<br>deterministic                                        | Non-<br>deterministic         | GA Controller, function test vectors                                                                                         | Yes                                              | None                                                        |

| Keymeulen,<br>Stoica, Zebulum | No                 | Depends on<br>characteristics<br>at design time | Non-<br>deterministic                                        | Not<br>addressed              | None at runtime                                                                                                              | No                                               | Depends on<br>characteristics<br>at design time             |

| Lohn,<br>Larchev, DeMara      | No                 | Design<br>complexity                            | Non-<br>deterministic                                        | Non-<br>deterministic         | GA Controller, function test vectors                                                                                         | Yes                                              | None                                                        |

| Lach                          | No                 | Available spares                                | Either complete<br>or none                                   | Either<br>complete or<br>none | Device test vectors                                                                                                          | No                                               | Only one faulty<br>CLB per tile                             |

| STARS                         | Yes                | Available spares                                | Restricted by<br>non-<br>optimizable re-<br>routing strategy |                               | Test Reconfiguration<br>Controller + device test<br>vectors                                                                  | Yes                                              | Free STARS<br>available and<br>fixed routing<br>chokepoints |

| CBE                           | Yes                | Recovery<br>complexity                          | Optimized by<br>second-order<br>fitness metric<br>scheme     | Adaptable                     | Optional external RAM.<br>Fault coverage for this<br>RAM is intrinsic when<br>configuration loaded.<br>No test vectors used. | Yes                                              | None                                                        |

# Table 2: Fault Recovery Characteristics of Selected Approaches

## 2.3. Self-X properties on Organic Architecture

Related works in the literature have explored techniques useful for development of an OC system from various theoretical and practical perspectives. A frequent focus among these has been the design of OC architectures and OC development methodologies for systems with potential for exhibiting increased reliability and sustainability. For example, in [32] a runtime reliability evaluation of ASoC architectures was addressed. The objective was to design SoCs that can tolerate faults by introducing dynamic reliability, power management, and security tradeoffs, as well as adaptation to environmental changes and unpredictable failure scenarios. Under these conditions, a theoretical model for calculating error probability during run-time is presented. A related fault model in [26, 33] concentrated on transient and timing faults caused by ionizing radiation or variations at the technology or device level. The C-program simulations executed on Leon-2 processor code resulted in a penalty of two cycles for the detection and correction of an error in the processor's pipeline. Work has also been conducted on prototyping platforms capable of support OC architectures. For instance, the *Egret* system provides a platform for reconfigurable SoC's supporting applications such as OC [34]. The Design objectives of the Egret is to provide a platform that students can use to rapidly prototype new reconfigurable, embedded computing application and the second objective is to provide a straightforward path to commercialization of prototyped designs. The platform consists of modular functional elements that can be interconnected to design an embedded application for reconfigurable logic.

From the design methodology perspective, various previously-proven agent concepts were combined into a system-level design approach for OC development. This is presented in [27] which developed an adequate, model-driven software engineering methodology based on the Unified Modeling Language (UML) and Model Driven Architecture (MDA). The model was applied and tested on a manufacturing control system which exhibited various self-x properties. In [28], Observer/Controller architecture was developed to provide a generic template to develop OC systems. The template was used to implement the control of an urban traffic network.

While maintaining area/performance and power requirements, Avizienis [35] suggests integrating biology inspired concepts into the integrated circuit design process with the main objective being achievement of higher reliability. The immune system which was proposed continuously identifies and handles problems either internally or with the aid of external agents. In more a general study, identification of SoC system requirements for detecting faults and handling the faulty components is addressed in [26]. Fault tolerant error detection techniques are classified into three groups: hardware redundancy, information redundancy, and time redundancy. The three techniques and their combination are surveyed on Autonomous SoC design consisting of the two layers: the Functional Layer and Autonomic Layer. In this theoretical research framework, it is suggested that the Autonomic SoC would need a well-tailored AE layer which would cope with malfunctioning subcomponents. The simulation consists of a paradigm with priori knowledge about the system's behavior when an error occurs and examines setting a threshold for errors that can occur before the system goes into self-organizing mode [26].

In order for an autonomous system to invoke its self-healing mode, it must be able on its own to detect errors during run-time [36, 37]. Reconfiguration and detection techniques explored include *scrubbing* which is the continuous reconfiguration of the bitstream to refresh the stored configuration [38], Built-In-Self-Test (BIST) techniques [39], on-chip hardware test benches [40] and Triple Modular Redundancy (TMR) [41]. Decentralized approaches to Observer/Controller units can be preferable in the design of fault-detection and self-healing systems due to the fact that the observer/controller system itself might be faulty [36, 37], and this is one focus of the OES Architecture described in Chapter four.

For realization of the recovery phase, Genetic Algorithms (GAs) have been applied to FPGA devices in various approaches. In the cases of intrinsic hardware evolution, the GA is invoked to apply crossover and mutation on the FPGA bitstream to evolve a fault-specific repair in-situ on the device. A software-simulation study of this approach was presented in [42]. It also explored the use of voting systems that operate in parallel despite imperfect GA solutions to refurbishment of local permanent damage in the FPGA fabric. Results showed improvement in aggregate repair performance from several different incomplete repairs obtained by the GAs. In [28], an autonomous self-repair approach for SRAM-based FPGAs is developed based on Competitive Runtime Reconfigurability. This approach was applied to a FPGA-based multiplier design which demonstrated evolution of a complete repair for 3x3 multiplier from several stuck-at-faults within a few thousand iterations. Using conventional offline population based approaches, GAs were also explored in [31] and [14, 15] for evolutionary fault recovery in Virtex FPGAs using an external controller and an offline repair process.

Other examples of OC architectural approaches include an OC system developed for face recognition [24]. The system utilizes some characteristics of an OC system such as self-organization and robustness. Methods for recognition of an input face from variation of images based on learning from biological systems are discussed. Others have argued that neutrality is a necessity for optimal self-adaptation [43]. They emphasize the need to provide a unifying formalism to embed approaches to self-adaptation in evolutionary computation.

## 2.4. TMR and Standby System Application on Improving Reliability

The TMR approach, first proposed by Von Neumann [19], is shown in Figure 1. It was widely used in software fault tolerance [3] and reliable hardware [30] applications. The primary drawback of the TMR approach is resource overhead. The TMR design triples the area and power consumption of physical resources over a simplex design. Duplex systems with a hot standby component based on a process pair [14] paradigm for fault tolerance are widely implemented in Network Access Devices (NAD) [15] and other uninterruptible operational systems.

However, much of the superiority of TMR and Standby type systems hinges upon some critical components. The reliability (or lack or reliability) of the majority voter in TMR systems and the Standby system switch mechanism may be detrimental to the overall system reliability. There are other issues to consider including: the reliability of memory which stores the standby configurations, the capability of sensing improper operation to trigger a switch, or how the majority voter and the switch operation must maintain data consistency between the primary and backup components.

Several previous works on TMR systems for FPGAs are introduced in [10] [30] and [13]. In [10], the TMR system with voting technique is combined with bitstream scrubbing implemented in a Virtex FPGA device in order to mitigate Single Event Upset (SEU) effects [44]. The voting mechanism identifies the faulty configuration based on single failure assumption and reconfigures (scrubs) the device with an alternative bitstream. However, the reconfiguration has

to take place off-line and can only deal with a transient faults which can be restrictive for use during deep space missions.

Fault detection characteristics relevant to embedded FPGAs are presented in multiple approaches. A traditional approach to fault-handling such as *Triple Modular Redundancy* (TMR) utilizes a fixed pool of three identical device resources. Under TMR, only the majority vote of three outputs is propagated, realizing online fault handling with negligible detection latency. Vigander's [16] approach extends TMR-style voting to utilize faulty FPGAs that have been partially regenerated using evolutionary algorithms. He demonstrates that FPGA-based implementations of 4-bit x 4-bit multipliers can be automatically reconfigured to realize partial refurbishment. Yet since each partially refurbished multiplier is deficient with respect to only certain input pairs, a voting arrangement of partially refurbished parts exhibits complete regeneration of the lost functionality. TMR, Vigander's, and other n-plex spatial voting approaches can deliver real-time fault detection, but also increase power consumption n-fold during fault-free operation and insert a critical voting element into the reliability path.

A TMR application for the Virtex series of Xilinx FPGA is described in [45]. The Majority voter is implemented with tri-State buffers based on the Virtex bus structures. Different types of data structures such as Throughput Logic, State-Machine Logic and I/O Logic are illustrated in terms of a TMR technique. Some special features provided by the Virtex architecture are also mentioned.

Another analysis of the TMR with mitigation of SEU effects in the Xilinx FPGA device is [46]. A selective TMR architecture is implemented for sensitive portions of the circuit in order to harden against the SEU effects. However, as the authors mentioned in the conclusion section, the result of STMR is based on the input signal probabilities and nature of the circuit and may only be beneficial to the circuit with input environments where the size of the SEU sensitive portion is smaller than the original one. Such an approach narrows down the application range and can not be viewed as useful for general utilization in different kinds of circuit design.

Furthermore, an analysis of the SEU effects in the TMR architecture in [47] shows that TMR may not be sufficient to harden a circuit. The results presented show most of the faults escape the TMR architecture. They proposed a smart floorplan for the placement and routing which may improve mitigation of SEU effects using TMR.

A VHDL design methodology for redundancy in combinatorial and sequential logic research is developed in [48]. A VHDL approach has been developed for automatic TMR insertion and demonstration in order to mitigate the SEU effects. Both module level mitigation and gate level mitigation are discussed.

All the above enumerated techniques or architectures based on electronic embedded system have their own advantage and restriction in terms of different applications and different system performance requirement. Based on current techniques and architectures, we proposed a new technique CBE approach in order to cover some of disadvantage of previous approaches such as constant fitness evaluation, online repair, and specific architecture-oriented GA operations through evaluation multiple benchmark circuits. Also a new proposed OC architecture is shown in this dissertation to utilize either the Lispa's layered OC concept [29] in conjunction with the CBE technique.

# CHAPTER 3: TMR, STANDBY AND TMRSB SYSTEM

Despite continued improvements in reliability at the component level, fault tolerance strategies still retain an essential role for applications that require high reliability in environments with unpredictable adverse effects. Fault tolerance strategy utilizing redundant components have a variety of architectures that can be used to obtain higher system reliability. Many previous fault tolerance approaches such as Triple Modular Redundancy (TMR), Simplex/TMR and Standby systems were extensively covered in literature [19] [35] [49] [50] starting in the 1950s. In recent decades new types of electronic devices have become available, such as reconfigurable hardware that has allowed some inefficient strategies, which were never considered or implemented before, to become viable due to the unique characteristics of such devices.

Consider the variety of embedded computing environments which frequently occupy harsh and difficult-to-regulate surroundings with thermal, mechanical or acoustical stress. In addition, space or avionic applications may also face very high levels of radiation exposure. Higher reliability systems required for long duration missions have, in most cases, limited capabilities for interactive diagnosis, repair and onboard spares. These systems must count on system level fault tolerance strategies even though implemented with high reliability components.

Furthermore, along with the finer granularity of the electronic device, the measurement of the system/component reliability may not satisfy the evaluation of the current implementation scenario and restrict ad-hoc repair strategy as well. The concepts of residual functionality after fault and autonomous repair are receiving increasing affection beyond traditional fault tolerance

techniques. Addressing these new considerations may improve not only the system reliability, but can be achieved in parallel with the system throughput without human intervention.

### 3.1. Overview of Traditional Fault Tolerance Strategy

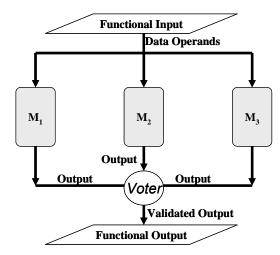

The TMR approach, first proposed by Von Neumann [19] is shown in Figure 6. It was widely used in software fault tolerance [49] and reliable computer architecture [35] and Evolvable Hardware design[50]. The utmost drawback of the TMR approach is resource overhead which will increase by 200% the area and power consumption of physical resources over a simplex design and introduce the extra voting components which introduce new the vulnerability of the system. This may be infeasible to a system with limited payload capacity such as space application.

Figure 6: TMR System

The approach combines time and spatial redundancy by applying time redundancy to TMR systems. For the permanent fault, a reconfiguration will be implemented on either all of three

instances or just the failed module. For the transient fault, a data roll-back will be implemented by re-computing the task without replacement. However, in order to obtain accurate detection, the TMR system needs an extra vote which induces higher overhead. The Markov Chain model was utilized in this dissertation to analyze the system reliability and availability.

The conventional *N* modular Redundancy (NMR) [51] system provides a powerful approach of improving reliability and fault tolerance capacity of digital systems. *N* functional modules, N=2m-1 and m>1, implemented identically, are given concurrent computation tasks and utilize a majority voter on the output to obtain the final result whenever at least *m* modules are functioning correctly. Each module is identical in functionality, but fault independent and may have a different physical implementation or design in order to minimize fault impacts such as Common Mode Failure (CMF) [52]. The arbitrary fault can be masked by the majority voter without sudden performance degradation except in the case of catastrophic failure. Among NMR approaches, TMR [19] [41] has been one of the most popular fault-tolerance schemes using spatial redundancy in a practical system. In Figure 6, the three functionally identical modules M1, M2, M3 are deployed in parallel and the outputs converge at the majority voter to obtain the validated output for the system.

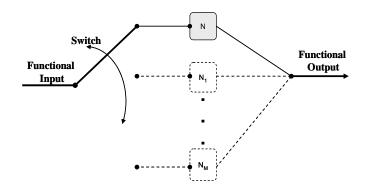

Another fault tolerance strategy is a Standby System (SB) arrangement. A Standby Model refers to the case in which a primary component (or system) has one or more identical backup components in an "off" or "off-line" state. When the original active component fails, a switch mechanism selects one of the "Standby" backup components and makes it the new active component. The system continues to operate with execution effected only by switching overhead. Duplex systems with a hot standby component based on process pair [53] paradigm for fault tolerance are widely implemented in Network Access Devices (NAD) [54], Web Server Systems (WSS) [55] and other uninterruptible operational systems. However, the "Hot" standby component will be active and have same fault probability as the current operating component even though the switch may have less impact on the system performance.

According to the backup component states, three varied types of standby system are defined. The "Hot" standby is keeping the primary and secondary (backup) components running simultaneously with the backup tracking the primary system in real time. This will allow a seamless switch when a fault in the primary component is detected. The "Cold" standby system is a method in which the secondary component is only called upon when the primary component fails. Between the "Hot" and "Warm" standby system, the "Warm" standby system will periodically mirror the primary component which means that there are times when both components do not contain the exact same data. As shown in Figure 7, the standby configuration can be in Hot, Cold, and Warm states depends on the specific system design.

However, much of the superiority of TMR and Standby type systems depends on some key components. The reliability (or lack or reliability) of the majority voter in TMR systems and the Standby system switch mechanism may be detrimental to the overall system reliability. There are other issues to consider like the reliability of memory which stores the standby configurations, the system power supply, the capability of sensing improper operation to trigger a switch, or how the majority voter and the switch operation must keep data integration between the primary and backup components.

Redundancy techniques are widely used in different applications. One example would be improving transmission rates of a communication system by expecting packet loss, duplicating, and reordering the corrupted data. Power plant stations and the power supply grid use redundant generators or power supply networks to continue to provide power in case of an emergency. It is also well known the reliability of digital system can be improved through the appropriate arrangement of additional components. High reliability and availability are particularly sought after in mission critical system.

Figure 7: Standby System

## 3.1.1. Embedded Device Properties Influencing Redundancy Strategies

As the application scope of digital system have extended into science and engineering fields, a strong desire for operational fault tolerance has developed especially in mission-critical equipment. The particular requirement of fault tolerance and fault repair has to be compatible with the specific characteristics of a digital device in order to obtain the practical benefit. On the other hand, new up-to-date devices which have unique characteristics can also be catalysts to develop new fault tolerance structures as is the case in this chapter.

Figure 8: FPGA Configuration and Readback Mechanism

SRAM-based reprogrammable devices known as a Field Programmable Gate Arrays (FPGAs) are large multi-million gate-equivalent devices that employ these technologies extensively. Over 100 FPGA devices can be embedded in a mission-critical system. The FPGA configuration is stored in bitstream format in the PROM and loaded into or read back from the FPGA chip through Configuration Logic Interface shown in Figure 8. The different connections on the FPGA chip integrate the Configuration Logic Blocks (CLBs) or Look Up Tables (LUTs) to implement computation logic tasks.

Environmental challenges to reliability in space applications can be modeled as having a uniform failure rate exposure despite status and locations of device activity in the system. Therefore, the impact of device wear-out (active components vs. cold spares) is small relative to radiation exposures, which makes ambiguous the active vs. standby role in terms of reliability in the various standby models. In other words the radiation effects far outweigh device aging effects and because both active and standby components are exposed to radiation equally their lifespan is primarily and equally determined by the effects of the radiation environment.

The pertinent reliability exposures for embedded FPGA's include hot carrier aging, ultra-thin gate oxide breakdown, and electromigration effects. FPGA's now utilize deep submicrometer (0.13  $\mu$ m) CMOS technology. As geometries and supply voltages shrink and electric current densities raise, increasing interconnect failure rates caused by high current electromigration can be observed over long product deployments.

Several previous works on TMR system in the FPGA are introduced in [56]. In [56] [45],[46],[47] and [48], the TMR system with voting technique combine with bitstream scrubbing implemented in a Virtex FPGA device in order to mitigate *Single Event Upset* (SEU) effects. The voting mechanism identifies the faulty configuration based on single configuration failure assumption and reconfigures (scrubs) the device with an alternative bitstream. However, the reconfiguration has to take place off-line and can only deal with a transient fault which maybe inappropriate for a practical system.

A TMR logic generation control log for the Virtex series of Xilinx FPGA is described in [45]. The Majority voter is implemented with tri-State buffers based on the Virtex bus structures. Different types of data structures such as *Throughput Logic*, *State-Machine Logic* and *I/O Logic* are illustrated in terms of TMR technique. Some special features provided by the Virtex architecture are also mentioned. The attached example uses the XVRWARE synthesis library

which provides macros and synthesis for constructing TMR circuits in VHDL for the Virtex architecture.

Another analysis of the TMR with mitigation of SEU effects in the Xilinx FPGA device is [46]. A selective TMR architecture is implemented for sensitive portions of the circuit in order to harden against the SEU effects. However, as the authors mentioned in the conclusion, the result of *Selective TMR* (STMR) is based on the input signal probabilities and nature of the circuit and may only be beneficial to the circuit with input environments where the size of the SEU sensitive portion is smaller than the original one. Such an approach narrows down the application range and can not be viewed as a general approach in different kinds of circuit design.

Radiation-induced Single Event Upsets (SEUs) can produce soft failures in both the configuration memory itself and in the mapped circuit on the throughput data-path. In addition, changes induced to the configuration memory not only change the circuit memory but can change the functionality of the mapped circuit as well. Given the architecture of FPGAs, the two different types of failures can have equivalent effects. The result of a SEU that makes the device totally or partially lose functionality is generally defined as Single Event Functional Interrupt (SEFI) [44]. In order to accurately evaluate the SEU effect, a stuck-at fault model is used in this dissertation for simulating single and multiple failure scenarios.

FPGAs are the ideal platform for reliability models like NMR and SB. Their unlimited reprogrammable property makes the standby components switches feasible with low delay and overhead. Furthermore, the reprogrammability enables designers to consider the appropriate recovery mechanisms which can extend mission lifetime compared to the non-repair system.

After all, the millions gates capacity makes more physical resources reusable and provides more alternative space for rearranging the routing.

Autonomous repair of FPGAs is of particular interest in aerospace applications for both in-flight and Ground Support Equipment devices. Several advantages drive the FPGA as an appropriate platform for the spacecraft electronics. First of all, high flexibility in achieving multiple requirements such as high performance, low Non-Recurring Engineering (NRE) costs and fast turnaround allow systems to be made in a more efficient manner. Second, FPGA devices can be utilized in remote hard to maintain systems such as satellites and space probes and can allow for remote reconfiguration and repair without too much overhead while maintaining performance.

The emerging field of autonomous repair has essentially impacted deployable systems for deeper space exploration mission and other high availability, sustainability and serviceability application that need to survive and perform at optimal functionality during long duration in unknown, harsh and/or changing environment. Many techniques have been developed to generate the pre-complied alternative fault tolerance configurations and stored in memory or generate new fault tolerance configurations after a permanent fault is detected in order to reconfigure when a fault occurs.

Frequently, such systems have limited capacity for spares yet still have requirements for reliable operation over long lifetimes [50]. This dissertation approach in this chapter is to design and implement a hybrid system redundant architecture to handle a wide range of transient faults through automatic FPGA reconfiguration and also permanent failures though automatic selection

from a diverse set of standby components, which implement identical functionality, but may use different physical resources, and dynamic update of these alternative configurations.

### 3.2. System Reliability Analysis

## 3.2.1. Standby System

Consider the SB system configuration depicted in Figure 7. It contains m+1 identical component of which exactly one is active at any time and the remaining m components act as switchable spares. Up to m of these spares may provide feasible alternative standby configurations in order to extend the mission time.