# STARS

University of Central Florida

STARS

Electronic Theses and Dissertations, 2004-2019

2006

# Synthesis Of Self-resetting Stage Logic Pipelines

Rashad Oreifej University of Central Florida

Part of the Computer Engineering Commons Find similar works at: https://stars.library.ucf.edu/etd University of Central Florida Libraries http://library.ucf.edu

This Masters Thesis (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

### **STARS Citation**

Oreifej, Rashad, "Synthesis Of Self-resetting Stage Logic Pipelines" (2006). *Electronic Theses and Dissertations, 2004-2019.* 1108. https://stars.library.ucf.edu/etd/1108

# SYNTHESIS OF SELF-RESETTING STAGE LOGIC PIPELINES

by

# RASHAD OREIFEJ B.S. University of Jordan, 2000

A thesis submitted in partial fulfillment of the requirements for the degree of Masters of Science in the School of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Summer Term 2006

© 2006 Rashad Oreifej

# ABSTRACT

As designers began to pack multi-million transistors onto a single chip, their reliance on a global clocking signal to orchestrate the operations of the chip has started to face almost insurmountable difficulties. As a result, designers started to explore clockless circuits to avoid the global clocking problem. Recently, self-resetting circuits implemented in dynamic logic families have been proposed as viable clockless alternatives. While these circuits can produce excellent performances, they display serious limitations in terms of area cost and power consumption. A middle-of-the-road alternative, which can provide a good performance and avoid the limitations seen in dynamic self-resetting circuits, would be to implement self-resetting behavior in static circuits. This alternative has been introduced recently as *Self-Resetting Stage Logic* and used to propose three types of clockless pipelines. Experimental studies show that these pipelines have the potential to produce high throughputs with a minimum area overhead if a suitable synthesis methodology is available.

This thesis proposes a novel synthesis methodology to design and verify clockless pipelines implemented in SRSL by taking advantage of the maturity of current CAD tools. This methodology formulates the synthesis problem as a combinatorial analytical problem for which a run-time efficient exact solution is difficult to derive. Consequently, a two-phase algorithm is proposed to synthesize these pipelines from gate netlists subject to user-specified constraints. The first phase is a heuristic based on the *as-soon-as-possible* scheduling strategy in which each gate of the netlist is assigned to a single pipeline stage without violating the period constraint of each pipeline stage. On the other hand, the second phase consists of a heuristic, based on the

Kernighan-Lin partitioning strategy, to minimize the number of nets crossing each pair of adjacent pipeline stages. The objective of this optimization is to reduce the number of latches separating pipeline stages since these latches tend to occupy large areas.

Experiments conducted on a prototype of the synthesis algorithm reveal that these self-resetting stage logic pipelines can easily reach throughputs higher than 1 GHz. Furthermore, these experiments reveal that the area overhead needed to implement the self-resetting circuitry of these pipelines can be easily amortized over the area of the logic embedded in the pipeline stages. In the overall, the synthesis methods developed for SRSL produce low area overhead pipelines for wide and deep gate netlists while it tends to produce high throughput pipelines for wide and shallow gate netlists. This shows that these pipelines are mostly suitable for coarse-grain datapaths.

## ACKNOWLEDGMENTS

I would like to thank all who made this possible either directly by their contribution in this project, or indirectly by their support and love.

I wish to express my sincere gratitude to Dr. Abdel Ejnioui for his great support, continuous supervision, and valuable contribution in this thesis.

I also would like to thank my friend Abdelhalim Alsharqawi for the great team-spirit and professional atmosphere we experienced in working together through the many challenges in this project.

I'd like to thank my family in Jordan and my family in Orlando for their copious support, love, and care for which I am so grateful, and without which, it would have not been possible.

Finally, I'd like to thank all my friends here in Orlando who by their earnest friendship encouraged me to carry out this achievement.

# **TABLE OF CONTENTS**

| LIST OF FIGURES                                              | ix  |

|--------------------------------------------------------------|-----|

| LIST OF TABLES                                               | xii |

| CHAPTER ONE: INTRODUCTION                                    | 1   |

| 1.1 Limitations of Clocked Circuits                          | 1   |

| 1.2 Self-Resetting Circuits                                  |     |

| 1.3 Self-Resetting Stage Logic and Its Synthesis Methodology |     |

| 1.4 Thesis Contributions                                     | 7   |

| 1.5 Thesis Overview                                          |     |

| CHAPTER TWO: RELATED WORK                                    |     |

| 2.1 Delayed Reset Logic                                      |     |

| 2.2 Global/Local Self-Resetting CMOS                         |     |

| 2.3 Local Self-Resetting CMOS                                |     |

| 2.4 Dual-Rail Self-Reset Logic with Input Disable            |     |

| 2.5 Summary of Self-Resetting Techniques                     |     |

| CHAPTER THREE: SELF-RESETTING STAGE LOGIC                    |     |

| 3.1 Self-Resetting Stage Logic                               |     |

| 3.2 Stage-to-Stage Self-Resetting Stage Logic                |     |

| 3.3 Pipeline-Controlled Self-Resetting Stage Logic           |     |

| 3.4 Delay-Tolerant Self-Resetting Stage Logic                |     |

| 3.4.1 Pipeline Structure                                     |     |

| 3.4.2 Phase Control Block                                    |     |

| 3.4.3 Latch Control Block                            |    |

|------------------------------------------------------|----|

| 3.5 Summary                                          |    |

| CHAPTER FOUR: SYNTHESIS OF SRSL PIPELINES            |    |

| 4.1 SRSL Pipeline Design Methodology                 |    |

| 4.2 Synthesis of SRSL Pipelines                      |    |

| 4.3 Preliminaries                                    |    |

| 4.4 Analytical Formulation of the Pipelining Problem |    |

| 4.5 Heuristic SRSL Pipelining                        |    |

| 4.5.1 Stage Assignment Phase                         |    |

| 4.5.1.1 Phase I Approach                             |    |

| 4.5.1.2 Phase I Algorithm                            | 60 |

| 4.5.2 Vertex Shuffling Phase                         | 61 |

| 4.5.2.1 Phase II Approach                            | 61 |

| 4.5.2.2 Phase II Algorithm                           |    |

| CHAPTER FIVE: EXPERIMENTAL RESULTS                   | 71 |

| 5.1. Experimental Setup                              | 71 |

| 5.2. P-SRSL Experiments                              |    |

| 5.2.1. P-SRSL Area Cost                              |    |

| 5.2.2. P-SRSL Throughput                             |    |

| 5.3. D-SRSL Experiments                              |    |

| 5.3.1. D-SRSL Area Cost                              |    |

| 5.3.2. D-SRSL Throughput                             |    |

| 5.4. Summary                                         |    |

| CHAPTER SIX: SUMMARY AND CONCLUSION | 84 |

|-------------------------------------|----|

|                                     |    |

| LIST OF REFERENCES                  | 87 |

# LIST OF FIGURES

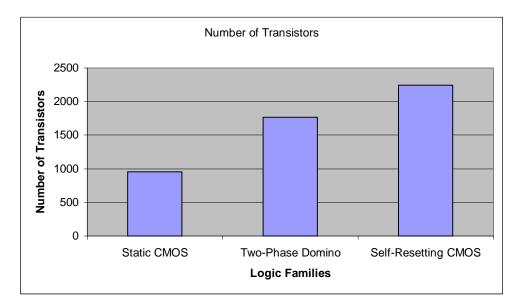

| Figure 1.1: Area cost of an add-compare-select unit implemented in three logic families       | 4  |

|-----------------------------------------------------------------------------------------------|----|

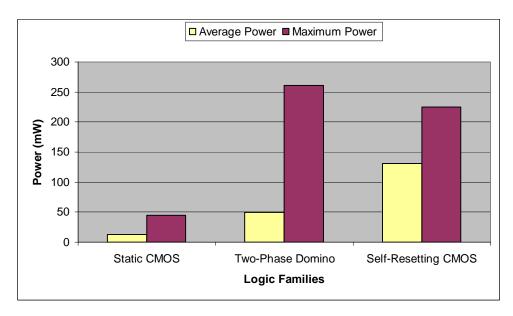

| Figure 1.2: Power consumption of an add-compare-select unit implemented in three logi         | ic |

| families                                                                                      | 4  |

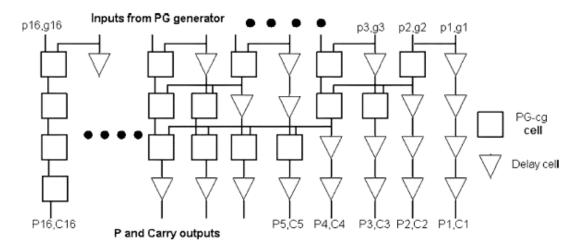

| Figure 1.3: Rough padding in a carry generator block of a self-resetting carry lookahead adde | er |

| [7]                                                                                           | 5  |

| Figure 2.1: DSRL pipeline and its self-resetting circuitry                                    | 1  |

| Figure 2.2: Timing chart of DSRL control signals of a pipeline stage                          | 1  |

| Figure 2.3: Basic SRCMOS gate                                                                 | 3  |

| Figure 2.4: SRCMOS macro                                                                      | 4  |

| Figure 2.5: Local self-resetting CMOS                                                         | 6  |

| Figure 2.6: Latch-free pipeline based in LSRCMOS                                              | 7  |

| Figure 2.7: Pulse stretcher                                                                   | 7  |

| Figure 2.8: Basic DRSRL-ID gate                                                               | 9  |

| Figure 3.1: Reset network of an SRSL stage                                                    | 3  |

| Figure 3.2: STG of the SRSL reset network                                                     | 4  |

| Figure 3.3: Four-stage S-SRSL pipeline                                                        | 6  |

| Figure 3.4: STG of the S-SRSL pipeline shown in Figure 3.3                                    | 7  |

| Figure 3.5: Assertion of the stage reset signals                                              | 8  |

| Figure 3.6: Reset phase of all stages                                                         | 8  |

| Figure 3.7: Evaluate phase of stage 4                                                         | 9  |

| Figure 3.8: Evaluate phase of stage 3                                                         | 9  |

| Figure 3.9: Evaluate phase of stage 2 and 4                             | 30 |

|-------------------------------------------------------------------------|----|

| Figure 3.10: Evaluate phase of stage 1 and 3                            | 30 |

| Figure 3.11: Evaluate phase of stage 2 and 4                            | 31 |

| Figure 3.12: Evaluate phase of stage 1 and 3                            | 31 |

| Figure 3.13: Four-stage P-SRSL pipeline.                                | 32 |

| Figure 3.14: STG of the four-stage P-SRSL pipeline shown in Figure 3.13 | 34 |

| Figure 3.15: Assertion of the stage reset signals                       | 35 |

| Figure 3.16: Reset phase of all stages                                  | 35 |

| Figure 3.17: Evaluate phase of all stages                               | 36 |

| Figure 3.18: Evaluate phase of stage 3 and 1                            | 36 |

| Figure 3.19: Evaluate phase of stage 4 and 2                            | 37 |

| Figure 3.20: Evaluate phase of Stage 1 and 3                            | 37 |

| Figure 3.21: Four-stage D-SRSL pipeline.                                | 38 |

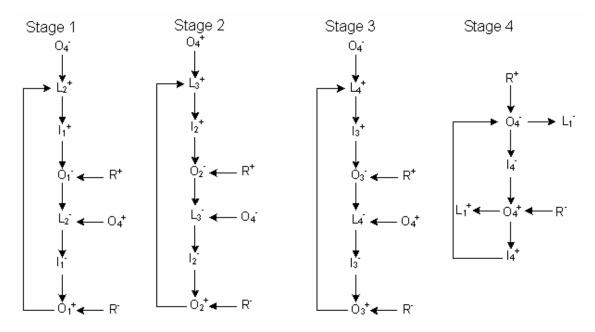

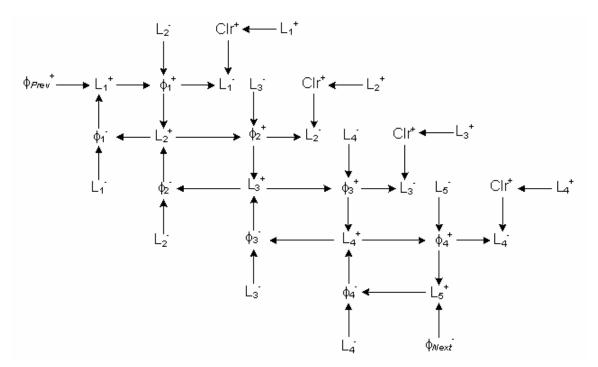

| Figure 3.22: STG of the D-SRSL pipeline.                                | 39 |

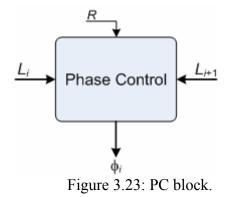

| Figure 3.23: PC block.                                                  | 40 |

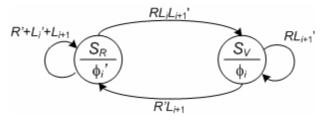

| Figure 3.24: State graph of the PC block                                | 41 |

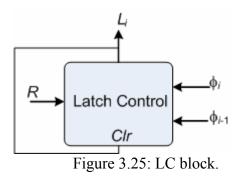

| Figure 3.25: LC block.                                                  | 42 |

| Figure 3.26: State graph of the LC block                                | 42 |

| Figure 4.1: SRSL design flow                                            | 45 |

| Figure 4.2: Example of a Boolean network.                               | 48 |

| Figure 4.3: Boolean graph of the Boolean network shown in Figure 4.2.   | 51 |

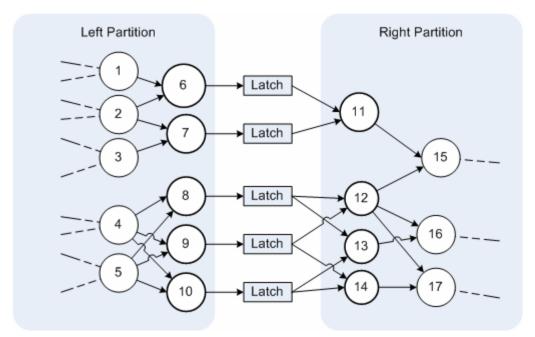

| Figure 4.4: Latch placement two Boolean graph partitions                | 62 |

| Figure 5.1: SRSL pipelining procedure of the benchmark circuits.        | 73 |

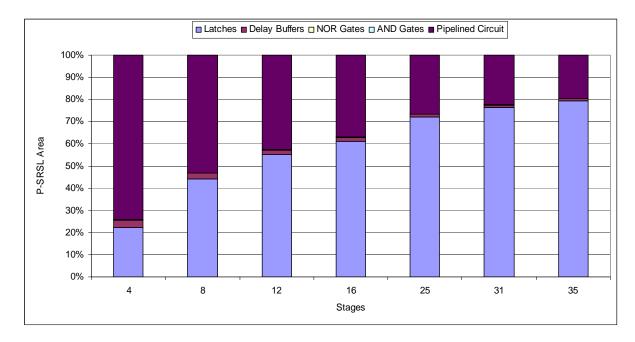

| Figure 5.2: P-SRSL area as a percentage of the pipeline area across different pipelines of th |

|-----------------------------------------------------------------------------------------------|

| C6822 benchmark circuit                                                                       |

| Figure 5.3: P-SRSL area as a percentage of the pipeline area across various depth pipelines7  |

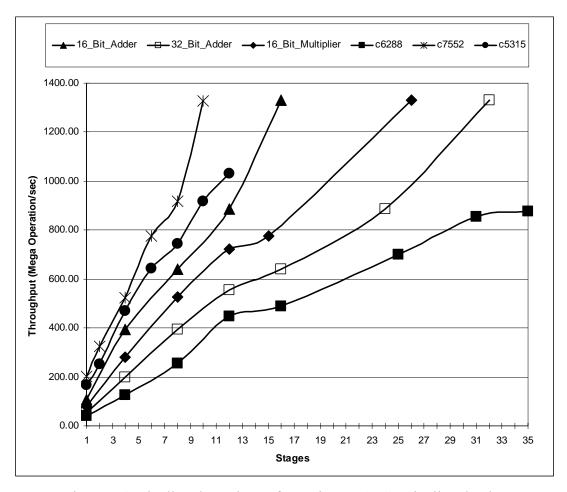

| Figure 5.4: Pipeline throughputs for various P-SRSL pipeline depths                           |

| Figure 5.5: D-SRSL area as a percentage of the pipeline area across different pipelines of th |

| C5135 benchmark circuit                                                                       |

| Figure 5.6: Pipeline throughputs for various D-SRSL pipeline depths                           |

# LIST OF TABLES

| Table 2.1: Summary of self-resetting techniques.                         | 21 |

|--------------------------------------------------------------------------|----|

| Table 5.1: Experimental circuits.                                        | 72 |

| Table 5.2: Area cost and throughput summary of the experimental circuits | 83 |

# **CHAPTER ONE: INTRODUCTION**

This chapter describes the problems caused by the reliance on global clocking to synchronize the operations of digital circuits. Faced with these problems, designers are exploring other classes of circuits which do not rely on clocking. In this context, the chapter discusses a class of clockless circuits known as self-resetting circuits. Because these circuits suffer from serious limitations in spite of their high performances, the chapter introduces briefly self-resetting stage logic and its pipelining schemes. Based on this new self-resetting technique, it argues for a synthesis methodology that is suitable to support clockless pipelines.

#### **1.1 Limitations of Clocked Circuits**

Clocked circuits have been dominating digital design for some time. Because they are synchronized by a global signal, these circuits are easy to build and verify. By abstracting away the complex interactions between circuit signals in the time domain, the timing analysis of these circuits is greatly simplified [1]. This simplification is narrowed to the analysis of delays on the critical path of the underlying gate netlist of the circuit. In essence, the design process of digital circuits is reduced to embedding combinational logic between clocked registers. This approach simplifies further the timing analysis by ignoring completely the impact of unwanted signal transitions between clock events. As time went by, interest grew in designing larger clocked circuit to meet new emerging applications. At the same time, market forces began to compel designers to reduce the

time-to-market of newly introduced technology products in order to maximize potential profits in the market. The combination of these factors contributed significantly to the development of automatic tools to design and verify these clocked circuits. This development effort culminated in the wide acceptance of a unified design methodology supported by widely available CAD tools. While these change were taking place, the quick pace of innovation in CMOS technology made the integration of multi-million transistors onto the same die possible. As designers kept packing more devices into chips to take advantage of these large scales of integration, significant challenges have emerged of which the reliance on a clock signal to orchestrate logic operations across an entire chip seems to be the most important [2]. This problem is considered the primary cause of three consequential obstacles in current VLSI design [3]:

- (i) Design cycle time: Design time can be extended significantly by unexpected clocking problems. These extensions can disturb product schedules and shrink potential market profits.

- (ii) Power budget: The power budget allocated for a design initially may be completely underestimated if clocking problems are not addressed early in the design cycle. Even if they are, there is no guarantee that the power budget will remain within initial estimates. Getting the power budget right is critical since excessive power consumption may disrupt the correct operations of the circuit.

- (iii) *Chip area*: To overcome the technical difficulties imposed by the distribution of the clock to different parts of a chip, substantial silicon area has to be

sacrificed to support this distribution. This additional area can increase significantly the final cost of the circuit.

#### **1.2 Self-Resetting Circuits**

As global clocking is causing these problems, designers are exploring the alternative of asynchronous circuits [4]. Recently, a special family of dynamic circuit, known as selfresetting logic, has been exploited successfully in memory design [5, 6]. Only a few attempts have been made to study the effectiveness of this logic family in implementing asynchronous datapath circuits [7, 8]. Self-resetting behavior can be described as the ability of a logic block to reset its output pulse a short time after it has been asserted. The reset signal is often generated within the block based on the output pulse. Depending on the implementation of the self-resetting behavior, the granularity of the block can range from a single gate to a large macro. Most self-resetting dynamic circuits are fine-grain implementations targeted to high performance arithmetic circuits. Since the majority of these circuits are pulse-mode circuits, they are usually organized into pulsed latch-free pipelines. These pipelines can produce high throughputs that are made possible by the fast cycle time of self-resetting dynamic circuits. Although dynamic circuits exhibit smaller area overhead than static circuits, the implementation of self-resetting dynamic circuits tend to occupy larger areas as shown in Figure 1.1 [9]. This area overhead is primarily caused by the self-resetting circuitry and additional buffering to equalize signal delay on various logic paths.

Figure 1.1: Area cost of an add-compare-select unit of a Viterbi Decoder implemented in three logic families.

While it is known that dynamic circuits can be power hungrier than static circuits, self-resetting dynamic circuits tend to consume substantially more power than even their clocked dynamic counterparts as shown in Figure 1.2 [10].

Figure 1.2: Power consumption of an add-compare-select unit of a Viterbi Decoder implemented in three logic families.

As for timing requirements, with the exception of a few self-resetting approaches [9, 11], most self-resetting circuits rely heavily on equalization of path delays [8, 12]. In fact, because some self-resetting circuits are intended for wave pipelining [7], rough padding is extensively applied on all paths in order to minimize the difference between fast and slow paths [13] as shown in Figure 1.3.

Figure 1.3: Rough padding in a carry generator block of a self-resetting carry lookahead adder [7].

Buffers can occupy up to 40% of the circuit area in some cases [10]. As a result, additional effort must be invested in meeting timing constraints that are specific to these circuits. This significant demand on maintaining signal integrity is exacerbated further by the pulse-driven nature of self-resetting circuits.

Since self-resetting behavior can be realized using any circuit family, one can opt to use static CMOS instead. Doing so presents several advantages. In static circuits, signals do not have to be pulses. Instead, voltage levels are sufficient to support self-resetting

behavior. If voltage levels are used, the stringent timing constraints encountered in pulse mode circuits can be relaxed without affecting circuit robustness. In addition, significant power savings can be realized by using static circuits. While static circuits are not as fast as dynamic circuits, one can overcome more or less effectively this difficulty by adopting performance-enhancing techniques such as aggressive pipelining and the exclusion of the reset circuitry from the critical path of the datapath. Moreover, the use of static selfresetting latch-based pipelines is particularly beneficial since their timing verification is reduced to the verification process encountered in synchronous logic. Furthermore, these self-resetting circuits can be synthesized and verified using current synthesis and verification tools. It is worth noting that there are no mature synthesis and verification tools available for dynamic circuits [14]. In fact, the design community ought to exploit the maturity of current CAD tools to build large asynchronous architectures which go beyond proof-of-concepts designs. To do so, this community can pursue a design methodology which adopts as much as possible the existing CAD design flow and deviates from it as little as possible [15].

#### 1.3 Self-Resetting Stage Logic and Its Synthesis Methodology

Following the objective of maximum adoption of the current design methodology, a novel coarse-grain self-resetting technique, called *self-resetting stage logic* implemented in static CMOS, has been recently proposed [16]. Based on this self-resetting stage logic (SRSL) technique, three pipelining schemes have been proposed where the first and second pipelines require that stages have equal delays while the third pipeline can tolerate

any arbitrary stage delay [17-21]. This thesis proposes a synthesis methodology to build these SRSL pipelines [22-24]. This methodology operates on flat gate netlists synthesized by current CAD tools and implemented in standard library cells used in ASIC design. The synthesis methodology is assessed through experimentation on benchmark circuits with various depths and breadths. As an experimental requirement, these SRSL pipelines have been synthesized and verified using current CAD tools, then implemented using a standard static CMOS cell library [25, 26].

#### **1.4 Thesis Contributions**

This thesis presents a new synthesis methodology specifically designed for pipelining SRSL logic. As mentioned before, this methodology is highly suitable for existing CAD tools. Specifically, the contributions of this thesis are as follows:

- (i) A novel design methodology based on synthesizing SRSL pipelines using current CAD tools and standard cell libraries. Designing clockless circuits using this methodology is highly similar to designing digital synchronous circuits.

- (ii) Graph-theoretic and analytical formulations of a combinatorial problem encountered in the synthesis of SRSL pipelines. Specifically, this problem consists of synthesizing an SRSL pipeline from a gate netlist with a minimum area overhead based on a specified data rate. The analytical formulation consists primarily of an integer programming problem.

- (iii) Since the size of the integer programming problem formulation is significantly large, a new heuristic algorithm is proposed to solve it. Because latches tend to occupy a large silicon area, the main goal of the algorithm is to minimize the area occupied by inter-stage latches without violating any timing constraints. This is accomplished by executing two successive phases where phase I assigns each gate in the gate netlist to a specific pipeline stage whereas phase II minimizes the number of inter-stage latches between every pair of neighboring pipeline stages.

- (iv) Pipelining experiments conducted on the SRSL pipeline show that they can reach throughputs above the GHz range without incurring an excessive area overhead.

- (v) The same pipelining experiments reveal that the area overhead remain beneficial as long as it represents a small fraction of the logic area embedded in a pipeline stage. This requirement makes SRSL pipelines highly suitable for pipelining coarse-grain datapaths.

#### **1.5 Thesis Overview**

This thesis consists of six chapters in which the current chapter presents the motivation behind the synthesis methodology of SRSL pipelines by drawing attention to the global clocking problem. Chapter 2 reviews the self-resetting circuit techniques previously described. These techniques are all implemented in dynamic CMOS. Chapter 3 introduces SRSL and describes the operations of the three pipelines based on SRSL. Chapter 4 describes the synthesis methodology that is proposed to support the design and verification of SRSL pipelines, presents the formulation of the combinatorial problem stemming from the synthesis of SRSL pipelines, and describes the synthesis algorithm implemented for this purpose. Chapter 5 presents the experiments conducted on benchmark circuits in order to evaluate the performance profiles of each SRSL pipeline. Finally, Chapter 6 concludes the thesis and suggests avenues for future work.

#### **CHAPTER TWO: RELATED WORK**

In this chapter, a review of the different design techniques based on self-resetting logic is presented. Section 2.1 presents delayed reset logic while section 2.2 describes a self-resetting technique controlled by local and global reset signals. Section 2.3 describes a self-resetting technique driven by local reset signals while section 2.4 describes a dual rail self-resetting technique with input disable. Section 2.5 concludes the chapter by presenting a summary of the reviewed techniques and contrasting them to SRSL.

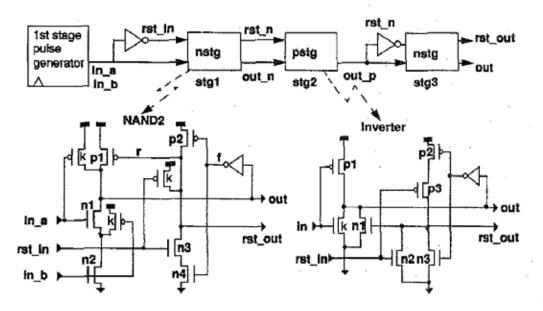

#### 2.1 Delayed Reset Logic

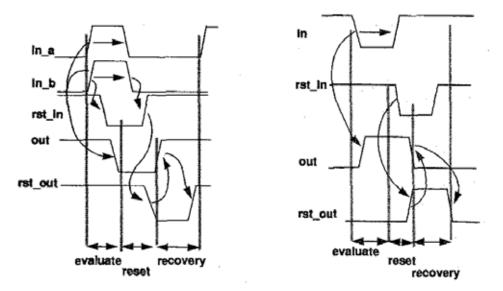

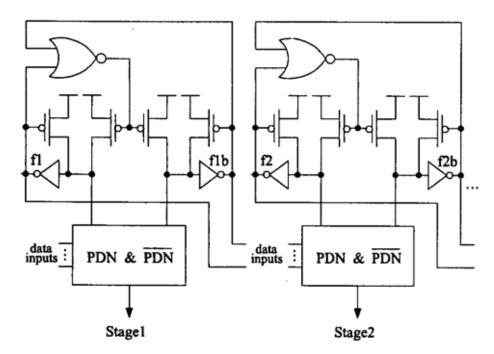

In [11], the authors propose a pipelined technique based on delayed self-reset logic (DSRL). The refinement of this technique is inspired from the self-reset technique proposed in [27]. DSRL is a single rail logic optimized for pipelining memory access in multimedia processors. This reset technique is driven by pulses and can be modified to accommodate voltage levels. Figure 2.1 shows the structure of a DSRL pipeline while Figure 2.2 shows timing charts of control signals within the pipeline. In DSRL, a stage can transition through three states: evaluate, reset, and recover. Before computation begins, a stage is in a quiescent state. When the inputs (in\_a and in\_b) are absorbed, the stage enters the evaluate state as shown in Figure 2.2. The evaluation time depends on the delay within the NMOS and PMOS networks. At the end of this state, the output (out\_n or out\_p) becomes stable at which point the stage enters the reset state. The stage remains in this state as long as the reset signal (rst\_in) has not arrived from the previous stage. Note that this signal is also labeled rst\_out on the output side of the same stage.

Figure 2.1: DSRL pipeline and its self-resetting circuitry.

Figure 2.2: Timing chart of DSRL control signals of a pipeline stage.

As Figure 2.1 shows, the reset signal (rst\_in) travels between every two adjacent stages. When the latter signal arrives, the stage enters the recovery state. This state is locally timed in each stage by

insuring that transistor n3 is turned off before transistor n4 is turned on in the beginning of the evaluate state. This signal control allows the stages to have arbitrary different delays.

Implemented in domino logic, DSRL pipelines consist of alternating NMOS and PMOS stages without any latches between the stages. Although these pipelines are suitable for memory cell design, it is doubtful whether they are also suitable for datapaths or not given their fine-grain nature. In addition, their design requires that careful calibration be applied to the pulse generator located in the first pipeline stage as shown in Figure 2.1. This calibration is needed to compensate for environmental variations. Furthermore, since these pipelines are mainly custom circuits, their design and verification can be time-consuming and error-prone.

#### 2.2 Global/Local Self-Resetting CMOS

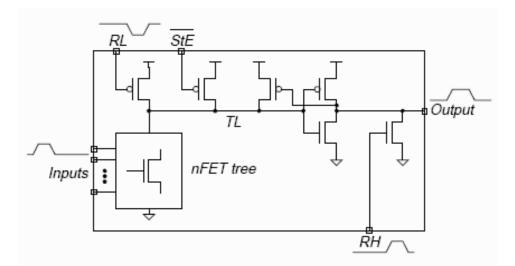

In [8, 12], the authors propose a single-rail self-resetting technique in which the gates are reset locally (LSRCMOS). However, the gates within a large macro are reset through a global reset signal (GLSRCMOS). Figure 2.3 shows a basic GLSRCMOS gate. This gate has active-high pulsed inputs and outputs. Its non-inverting logic evaluation depends on the logic function of the NMOS tree. If the right input combination occurs at the right time, a conducting path from the TL node emerges, which leads to discharging the capacitance at the output side of the gate. This brings TL to logic 0 while the output goes up to logic 1, thus creating the leading edge of the output pulse. When the input pulse ends, the RL signal arrives by falling to logic 0, thus resetting the TL node to logic 1. After TL becomes asserted, the RH signal arrives, by rising to logic 1, to terminate the output pulse.

Figure 2.3: Basic SRCMOS gate.

These basic GLSRCMOS gates are incorporated within macros. An SRCMOS macro consists of a number of gates whose reset signals drive a reset generator circuit located inside the macro. Figure 2.4 shows a GLSRCMOS macro. The triggering of this generator can be realized through ORing of reset signals, majority circuits, or interlocking signals from multiple paths. As a rule, the reset generator must be triggered when the macro is active. A delay chain generates the required signals within the reset generator. Initially, a macro is in standby mode. Once it receives its triggering pulses, it enters the evaluate mode, then resets its outputs before returning to the standby mode.

In [8], the designs of a number of macros are assembled to implement a 64-bit carry lookahead adder in a 0.25  $\mu$ m CMOS process. This adder can reach a throughput of 400 MHz. Since this adder uses a pipelined pulsed approach to increase its throughput, a number of buffers have been added to the adder in order to control delay on logic evaluation paths.

Figure 2.4: SRCMOS macro.

While the authors refer to pulse pipelining, they do not clearly describe how macros are pipelined within the adder. This omission does not clarify how two adjacent macros synchronize their state transition in order to exchange data safely. Whereas the insertion of buffers can help in overcoming timing issues, it can become quite unwieldy when dealing with large datapaths with large numbers of logic paths. At best, buffer insertion bloats the datapaths leading to a large area overhead. In addition, if macro size increases to accommodate deep logic, it may require increasing the length of the reset chains within a macro. This can be achieved by inserting inverters in this chain, which in turn complicates the timing verification of the macro. These ensuing timing difficulties explain the motivation of the authors in [12] to propose a special tool for performing accurate timing verification of GLSRCMOS circuits.

#### 2.3 Local Self-Resetting CMOS

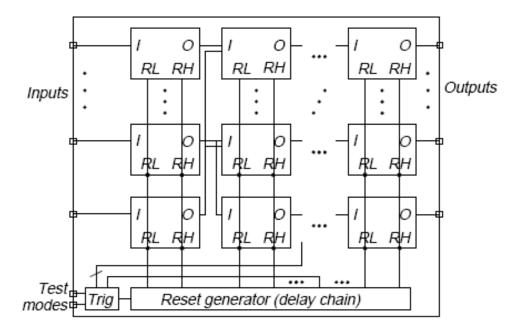

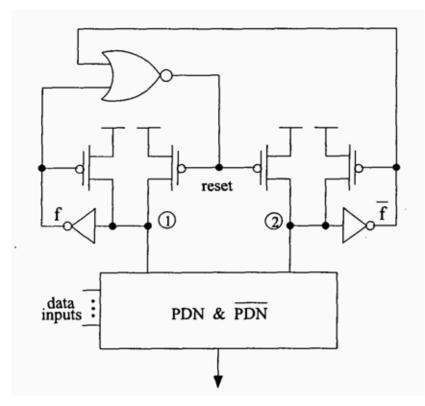

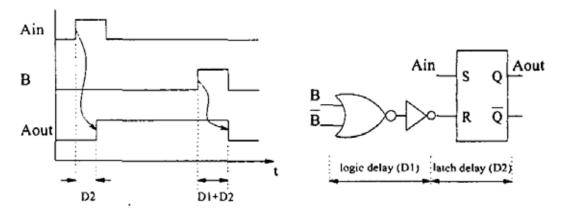

In [9], the authors propose a single-rail input dual-rail output self-resetting technique in dynamic CMOS. In this technique, the reset signal is generated within the stage by NORing the stage output and its complement. As a result, two NMOS networks are required to generate the output and its complement. Figure 2.5 shows the local self-resetting CMOS (LSRCMOS). In this circuit, node 1 will switch to low or high depending on the input. At the same time, node 2 will switch to the complement logic level of node 1 given the same input. At this time, both NMOS networks are in the evaluate state. Subsequently, signal f and f' go through the NOR gate whose output switches to low. The low output of the NOR gate turns on both precharge transistors connected to the reset node thus charging the capacitance at the outputs of both NMOS networks. As a result, nodes 1 and 2 switch to high to propel both NMOS networks in the reset state. At this moment, both NMOS networks are ready to accept new input pulses. Following this, signal f and f' switch both to low thus forcing the output of the NOR gate to switch to high. This in turn turns off both precharge transistors to allow both NMOS networks to evaluate the newly arrived input pulses.

Contrary to GLSRCMOS presented in the previous section, the reset signal in LSRCMOS does not go through any timing chain. As shown in Figure 2.5, the reset time remains constant regardless of the evaluation time of both NMOS networks. However, the delay through the loop consisting of an output node, the NOR gate, and the reset node should be longer than the duration of the input pulses to avoid in-fighting between the precharge transistors. This technique can be used to build latch-free pipelines in dynamic CMOS as shown in Figure 2.6.

Figure 2.5: Local self-resetting CMOS.

In [10], the authors apply LSRCMOS to design an add-compare-select (ACS) unit of a Viterbi decoder. While the ACS unit is 1.71 faster than its counterpart in clocked static CMOS, it is 110 times power hungrier than its static counterpart. In addition, it occupies 2.35 times more area than its static counterpart in spite of the effort of the authors in using pulse stretchers to control path delay. While the authors claim that these stretchers reduce area overhead in contrast to buffers, they do not specify how many pulse stretchers they used within the ACS unit and how much area they occupy. In fact, a pulse stretcher consists of an SR latch whose R input is connected to a NOR gate as shown in Figure 2.7.

Figure 2.6: Latch-free pipeline based in LSRCMOS.

Based on popular latch layouts, an SR latch in static CMOS can easily occupy three to seven times more area than a two-input NAND gate. To scale to dynamic CMOS implementations, a rough estimate can be obtained by halving the area estimates in static CMOS. Based on this estimate, even pulse stretchers may add a substantial area overhead although it is doubtful it would be on the order of the area overhead caused by buffer insertion.

Figure 2.7: Pulse stretcher.

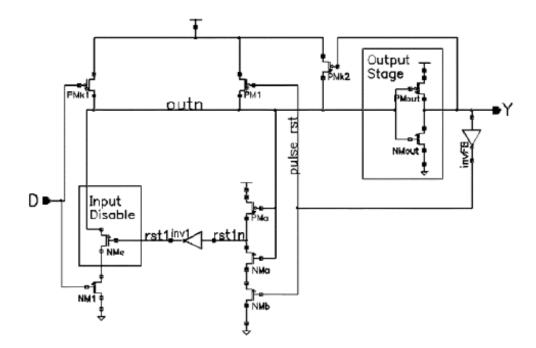

#### 2.4 Dual-Rail Self-Reset Logic with Input Disable

In [7], the authors propose a dual-rail self-resetting technique, called DRSRL-ID, in which the reset signal is generated locally. Figure 2.8 shows a basic DRSRL-ID gate. The ID initials represent the input disable block shown in Figure 2.8. This block consists of an extra NMOS transistor NMe in series with the NMOS transistor NM1. When the gate is in standby mode, capacitance is pulled down to ground switching the node outn to high. In return, this makes the node rst1n switch to high to turn on the NMe transistor. At this point, the gate is ready to absorb the D input. If D becomes high, node outn switches to low, which turns on and off the PMa and NMa transistors respectively. After a short time, node rst1 switches to low to turn off the NMe transistor. When the latter device is off, the input is disabled. The discharging of the node outn causes output Y to rise, thus generating the leading edge of the output. Y is fed through inverter invFB to turn on the PM1 transistor in charge of pulling up node outn. This brings back the gate to its standby mode. As node outn starts going high, its voltage switches the transistors of the output stage forcing the Y output to go low. When Y becomes low, it deactivates the reset signal to enable input readout. As such, the gate reenables the inputs only when the output pulse is completely formed. The layout of the basic DRSRL-ID gate forces the width of the output pulse to remain constant regardless of fanout. The width of the output pulse depends only on the output stage and the feedback loop that controls the reset signal. It is completely independent of the implementation of the NMOS network in charge of evaluating logic.

Figure 2.8: Basic DRSRL-ID gate.

The authors use this design technique to build a 16-bit wave-pipelined carry propagate adder in a  $0.18 \ \mu m$  CMOS process which can reach 2.5 GHz throughput. Because wave pipelining aims at reducing the delay differences between long and short paths, the authors resort to extensive rough padding to reach this objective.

While timing calibration seems to be straightforward at gate level, it is not clear how it can be achieved at datapath level. In fact, if buffer insertion is used for path delay equalization, this indicates that substantial effort must be invested in timing calibration at datapath level. In addition, buffer insertion contributes to bloating datapath size. By considering the number of transistors needed to support input disabling and resetting behavior on a cell basis, it is clear that area overhead can be incurred also at cell level. In fact, some basic two-input gates can incur a penalty of 12 to 16 transistors to support their input-disabling and reset behavior.

#### 2.5 Summary of Self-Resetting Techniques

Table 2.1 shows a summary of the self-resetting techniques reviewed in this chapter. The table shows that all the reviewed techniques are implemented in custom dynamic CMOS using pulsedriven circuits. Pulse driven circuits require precise sequencing of the input pulses. In contrast, voltage level circuits do not require such sequencing. In addition, custom circuits using dynamic CMOS require a substantial effort in verification. This effort is further hampered by a total lack of mature CAD tools destined for synthesis and verification of circuits implemented in dynamic CMOS. In the reviewed circuits, the reset signal is always tied to the output pulse making the reset signal tightly coupled to the path of evaluated logic. If glitches affect the output signals, these glitches will propagate to the reset signals resulting in a temporary or permanent disruption of the state transitions in these circuits. None of the reviewed papers speculate on the consequences of such glitches. To build datapaths, these circuits are assembled into fine-grain latch-free pipelines. While these pipelines tend to be small in area, their verification is not a trivial task. This situation is further exacerbated in the reviewed techniques that require equal stage delay across the pipeline.

In contrast to the reviewed self-resetting techniques, this thesis proposes a design technique to support SRSL which has been previously reported in [16]. Implemented in static CMOS, SRSL has adequate coarse granularity to make it suitable for implementing large datapaths.

Static circuits consume less power than dynamic circuits. Furthermore, since SRSL exploits self-resetting at datapath level, its area overhead is significantly smaller than the area overhead seen in the reviewed self-resetting techniques. The latter techniques implement self-resetting behavior at gate level instead. While dynamic circuits can display a superior performance, static circuits can

provide similar performance levels if aggressive pipelining is applied in a disciplined manner. SRSL uses voltage levels instead of pulsed inputs and outputs. For circuit robustness, SRSL separates the path of self-resetting circuitry from that of logic circuitry. Since SRSL is implemented in static circuits, its pipelines use latches to separate logic stages. The insertion of latches facilitates the control of the cycle time and subsequently the timing validation of these pipelines.

|                                       | DSRL                                                                                                            | LGSRCMOS                                                                               | LSRCMOS             | DRSRL-ID      | SRSL                                                                                            |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------|---------------|-------------------------------------------------------------------------------------------------|

| Pulse vs.<br>voltage level            | Pulse                                                                                                           | Pulse                                                                                  | Pulse               | Pulse         | Voltage levels                                                                                  |

| Source of<br>reset signal             | <ul> <li>Incoming<br/>reset from<br/>previous stage</li> <li>Outgoing<br/>reset in current<br/>stage</li> </ul> | <ul> <li>Local reset<br/>in current gate</li> <li>Global reset<br/>in macro</li> </ul> | Current stage       | Current stage | <ul> <li>Current<br/>stage (S/P-<br/>SRSL)</li> <li>Previous<br/>stage (D-<br/>SRSL)</li> </ul> |

| Destination of reset signal           | Next stage                                                                                                      | In macro                                                                               | Current stage       | Current stage | Previous stage                                                                                  |

| Tying of reset<br>signal to<br>output | Yes                                                                                                             | Yes                                                                                    | Yes                 | Yes           | No                                                                                              |

| Signal delay<br>handling              | None                                                                                                            | Buffering                                                                              | Pulse<br>stretching | Buffering     | Buffering                                                                                       |

| Path of reset signal                  | Logic path                                                                                                      | Logic path                                                                             | Logic path          | Logic path    | Control path                                                                                    |

| Stage delay                           | Arbitrary                                                                                                       | Equal                                                                                  | Arbitrary           | Equal         | <ul> <li>Equal (S/P-SRSL)</li> <li>Arbitrary (D-SRSL)</li> </ul>                                |

| Pipelining                            | No Latches                                                                                                      | No Latches                                                                             | No Latches          | No Latches    | Latches                                                                                         |

| CMOS                                  | Dynamic                                                                                                         | Dynamic                                                                                | Dynamic             | Dynamic       | Static                                                                                          |

| Granularity                           | Fine                                                                                                            | Fine                                                                                   | Fine                | Fine          | Coarse                                                                                          |

| Tools                                 | None                                                                                                            | Proprietary                                                                            | None                | None          | Current CAD                                                                                     |

Table 2.1: Summary of self-resetting techniques.

This thesis proposes a design methodology which leverages the maturity of current CAD tools to synthesize and verify SRSL pipelines. The methodology does not deviate from the established design methodology used in synchronous logic. At the core of this methodology is a synthesis flow which transforms a synchronous gate netlist into an SRSL netlist before the latter is placed and routed.

## **CHAPTER THREE: SELF-RESETTING STAGE LOGIC**

This chapter presents *self-resetting stage logic*, which is a digital design technique that is characterized by periodic oscillations. This technique can be used to establish handshaking exchanges between two computational stages in a dataflow pipeline. Its underlying concept is introduced in section 3.1. Section 3.2 describes the *stage-to-stage self-resetting stage logic* pipeline followed by the description of the *pipeline-controlled self-resetting stage logic* pipeline in section 3.3. Section 3.4 describes *delay-tolerant self-resetting stage logic* pipeline before section 3.5 concludes the chapter.

#### 3.1 Self-Resetting Stage Logic

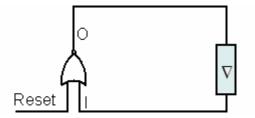

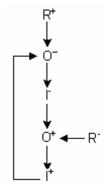

Self-resetting stage logic (SRSL) is a design approach which can be used to synchronize data flow between neighboring computing blocks without relying on a global clock signal. In the SRSL pipeline, each stage consists of two distinctive networks: a *combinational network* and a *reset network*. The combinational network represents the combinational logic embedded in a given stage while the reset network represents an oscillating loop used to control data transfer from one combinational network to another. The reset network consists of a two-input NOR gate whose output O feeds back one of its inputs I, while its other input is tied to the Reset global signal as shown in Figure 3.

Figure 3.1: Reset network of an SRSL stage.

As long as the Reset signal is asserted, O remains 0. When the Reset signal is de-asserted, O oscillates between 0 and 1. The oscillation frequency is controlled by the delay block  $\Delta$  embedded in the feedback loop between the NOR output and its input. When O is 0, the reset network is in the *reset* phase. Later, when O switches to 1, the reset network is in the *evaluate* phase. As such, a reset network oscillates between two distinct phases in an autonomous fashion. The duration of these two phases constitutes a single oscillation cycle or *period*. This autonomous oscillation is illustrated with the *state transition graph* (STG) shown in Figure 3.2.

Figure 3.2: STG of the SRSL reset network.

In the above STG, O, I, and R are the three signals shown in Figure 3.1.  $O^+$ ,  $I^+$ , and  $R^+$  represent the rising transitions on those signals respectively while  $O^-$ ,  $I^-$ , and  $R^-$  represent the falling transition on the same signals respectively. In addition, a directed edge connecting two transitions means that the transition at the tail of the edge precedes in time the transition at the head of the edge. The oscillations of a reset network can be used to synchronize data transfer between neighboring stages in a pipeline. To allow the combinational network of a stage sufficient time to absorb and process its inputs, SRSL

prepares a stage to (i) receive inputs from the preceding stage when it is in the reset phase, and (ii) send its outputs to the following stage when it is in the evaluate phase.

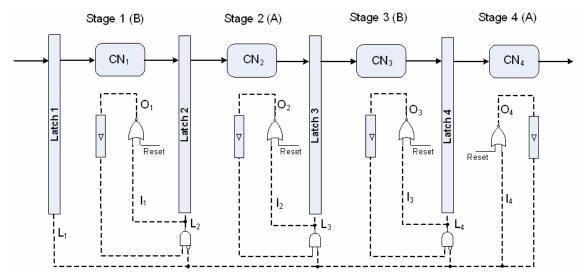

# 3.2 Stage-to-Stage Self-Resetting Stage Logic

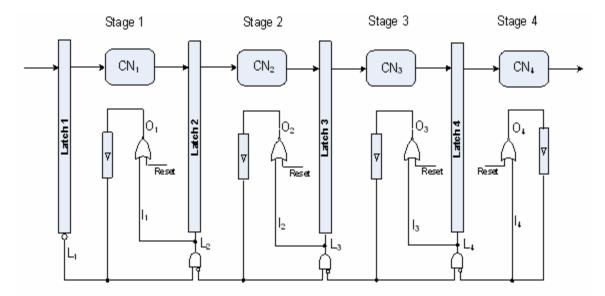

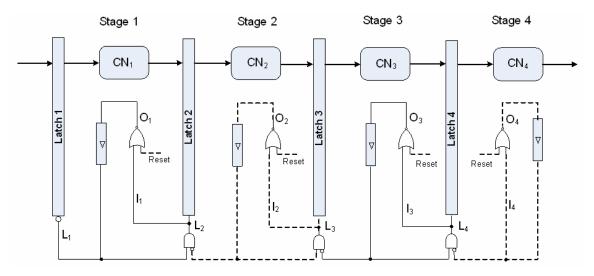

In stage-to-stage self-resetting stage logic (S-SRSL), the synchronization is realized between each pair of stages in the pipeline. In this pipeline, each stage is ready to absorb inputs when it enters the reset phase and produce an output when it enters its evaluate phase. As a result, data transfer occurs between two neighboring stages when the left stage is in the evaluate phase while the right stage is in the reset phase.

Figure 3.3 shows the interconnection structure of a four-stage S-SRSL pipeline where each stage consists of a combinational and a reset network. In addition to the reset network, SRSL relies on inter-stage latches to capture data moving from one stage to another. These latches are enabled when the left stage is ready to push data to the right stage in a pipeline. This occurs when the left and right stages are in the evaluate and reset phases respectively. As shown in Figure 3.3, the enable ( $L_i$ ) of each inter-stage latch is tied to the output of an AND gate whose inputs are connected to the phase lines of the left and right stages. These phase lines represent the outputs of the NOR gates embedded in the reset networks of both stages. Note that the right input of the AND gate is inverted. Because the control of these inter-stage latches is exercised between each pair of pipeline stages, this synchronization technique is qualified as a stage-to-stage SRSL. It is worth emphasizing the fact that all the stages in the pipeline should have equal cycles in order to insure correct data flow throughout the pipeline.

Figure 3.3: Four-stage S-SRSL pipeline.

At any oscillation cycle, the latch on the left side of a stage in the reset phase will be enabled while the latch on its right side will be disabled. The latter will be enabled only when the stage enters its *evaluate* phase. This periodic oscillation forces every other stage to enter the evaluate phase while the remaining stages enter their reset phase. A cycle later, the stages that were in the reset phase start their evaluate phases while the stages that were in the evaluate phase start their reset phase.

The STG for the four-stage S-SRSL pipeline shown in Figure 3.3 is shown in Figure 3.4. In Figure 3.4, the STG shows that the rising transition of  $L_3$  occurs after  $O_2$  and  $O_3$  experience a rising and falling transition respectively. This means that latch 3 is enabled only when stage 2 is in the evaluate phase while stage 3 is in the reset phase. If  $O_3$  experiences a falling transition, this forces another falling transition on  $L_4$ . This shows that while latch 3 is enabled, latch 4 is disabled.

Figure 3.4: STG of the S-SRSL pipeline shown in Figure 3.3.

Figure 3.5 through Figure 3.12 show how the stages alternate between phases as data flows across the pipeline by depicting two execution cycles of a four-stage S-SRSL pipeline. The asserted and de-asserted signals are represented as solid and dashed lines respectively in these figures.

Figure 3.5: Assertion of the stage reset signals.

Figure 3.6: Reset phase of all stages.

Figure 3.7: Evaluate phase of stage 4.

Figure 3.8: Evaluate phase of stage 3.

Figure 3.9: Evaluate phase of stage 2 and 4.

Figure 3.10: Evaluate phase of stage 1 and 3.

Figure 3.11: Evaluate phase of stage 2 and 4.

Figure 3.12: Evaluate phase of stage 1 and 3.

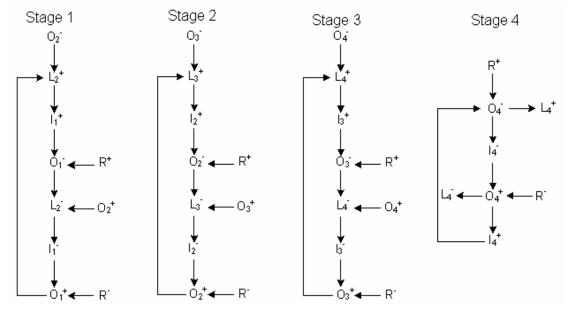

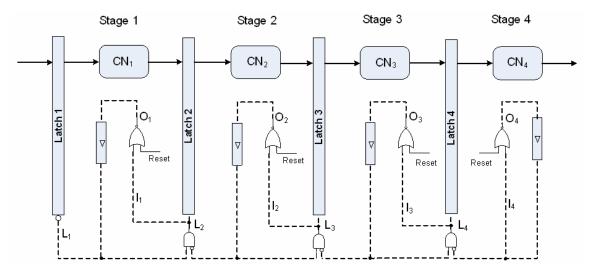

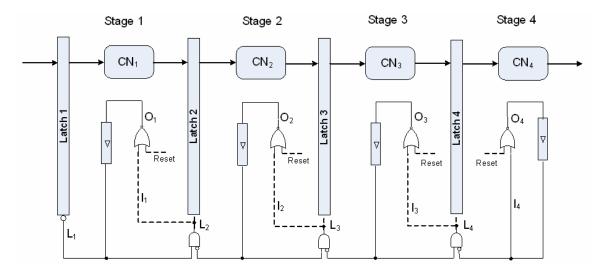

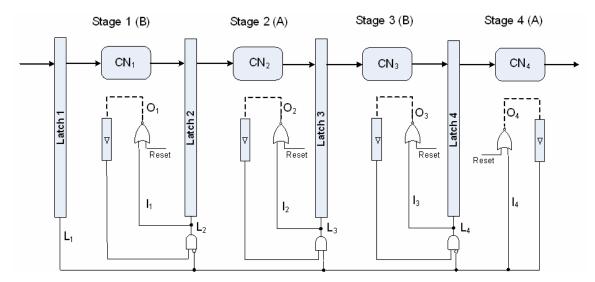

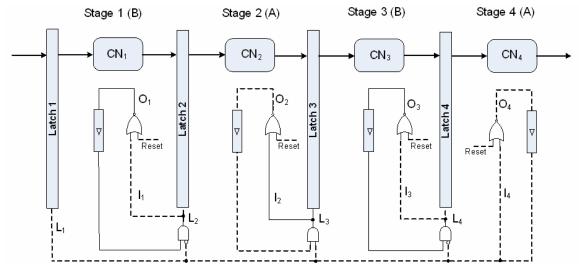

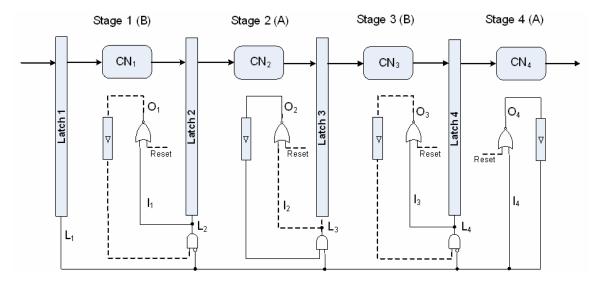

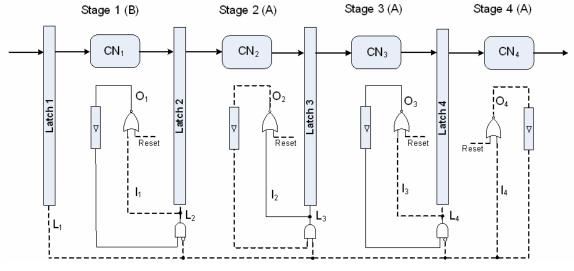

#### 3.3 Pipeline-Controlled Self-Resetting Stage Logic

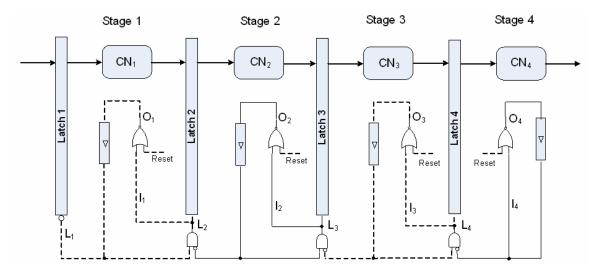

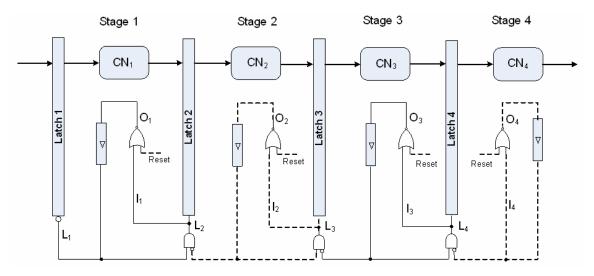

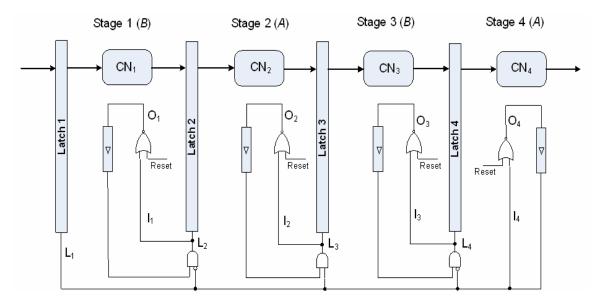

In pipeline-controlled self-resetting stage logic (P-SRSL), synchronization occurs between the last stage and any other stage in the pipeline. Similarly to S-SRSL, each stage is ready to absorb inputs when it enters the reset phase and produce an output when it enters its evaluate phase. As a result, data transfer occurs between two neighboring stages when the left stage is in the evaluate phase while the right stage is in the reset phase. Figure 3.13 shows the interconnection structure of a four-stage S-SRSL pipeline where each stage contains a combinational and a reset network. In addition to the two networks, each pair of stages is separated by a latch whose enable port is tied to the output of an AND gate. This AND gates has two inputs where the first is tied to the phase line of the last stage while the second is tied to the phase line of the last stage while the right input of the AND gate is inverted in some while it is not in others.

Figure 3.13: Four-stage P-SRSL pipeline.

*Definition 3.1:* A pipeline stage is said to be of *type A* if the phase signal of the last stage is inverted when it reaches the AND gate controlling the latch of the stage.

*Definition 3.2:* A pipeline stage is said to be of *type B* if the phase signal of the last stage is not inverted when it reaches the AND gate controlling the latch of the stage.

Based on these two definitions, stage 1 and 3 are of type B while stage 2 and 4 are of type A in Figure 3.13. Stages of the same type oscillate in the same phase while stages of opposite types oscillate in opposite phases. When the last stage enters its reset phase, every stage of type B starts its own evaluate phase while every stage of type A starts its own reset phase. As soon as the last stage transitions to its evaluate phase, all the stages switch phase. During the reset phase of a stage of type A, the stage's left latch is enabled while the stage's right latch is disabled. Both latches are driven by the reset phase of the last stage in the pipeline. The latter latch will be enabled only when the stage switches phase, which occurs when the last stage enters its evaluate phase. At any cycle, every other stage will be in the reset phase while the remaining stages will be in the evaluate phase. A cycle later, the stages that were in the reset phase start their evaluate phases while the stages that were in the evaluate phase start their reset phases. Similarly to the S-SRSL pipeline, the P-SRSL pipeline requires that all stages in the pipeline have equal cycles to guarantee correct data flow. The STG for the four-stage P-SRSL pipeline shown in Figure 3.13 is shown in Figure 3.14. This STG shows that the rising transition of  $L_3$  occurs after  $O_2$  and  $O_4$  experience both rising transitions. This means that latch 3 is enabled when both stages 2 and 4 are in the evaluate phase. However when O<sub>4</sub>

experiences a rising transition,  $L_2$  and  $L_4$  experience falling transitions. This shows that when latch 3 is enabled, latch 2 and 4 are disabled. Figure 4.3 shows how the stages alternate between phases as data flows across the pipeline by representing asserted and de-asserted signals as solid and dashed lines respectively.

Figure 3.14: STG of the four-stage P-SRSL pipeline shown in Figure 3.13.

Figure 3.15 through Figure 3.20 show how the stages alternate between phases as data flows across the pipeline by depicting two execution cycles of a four-stage P-SRSL pipeline. The asserted and de-asserted signals are represented as solid and dashed lines respectively.

Figure 3.15: Assertion of the stage reset signals.

Figure 3.16: Reset phase of all stages.

Figure 3.17: Evaluate phase of all stages.

Figure 3.18: Evaluate phase of stage 3 and 1.

Figure 3.19: Evaluate phase of stage 4 and 2.

Figure 3.20: Evaluate phase of Stage 1 and 3.

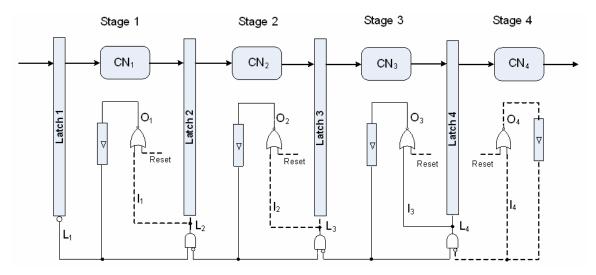

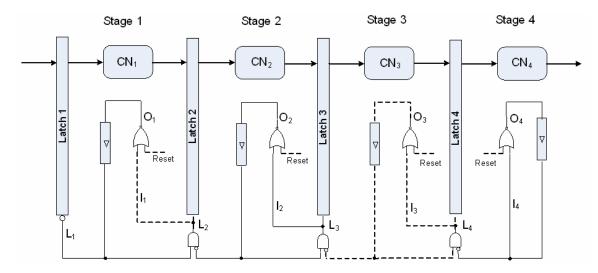

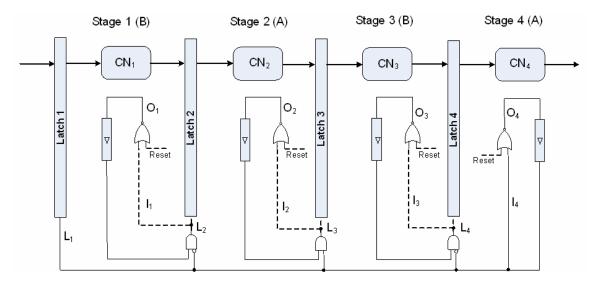

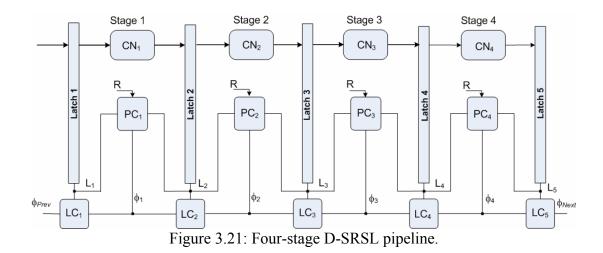

# 3.4 Delay-Tolerant Self-Resetting Stage Logic

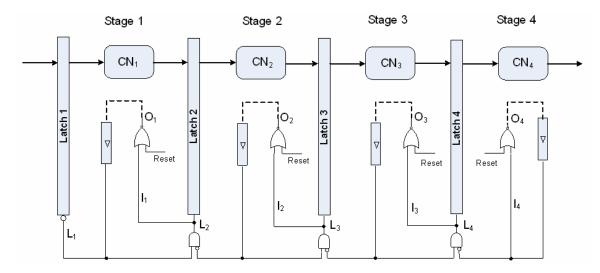

Whereas correct operation rests on stage having equal cycles in the S-SRSL and P-SRSL pipelines, this requirement is completely unnecessary in delay-tolerant self-resetting stage

logic (D-SRSL) pipelines. In fact, stages can have arbitrary delays without affecting the correct data flow across the pipeline. Hence, the delay-tolerant property of these pipelines as implied by their name. In this approach, stages communicate with each other through their respective phases. Figure 3.21 shows a four-stage D-SRSL pipeline.

# 3.4.1 Pipeline Structure

In D-SRSL pipelines, the latches are controlled by a *latch control* (LC) block. The phase oscillation of each stage is indicated by the signal  $\phi$  as shown in Figure 3.21. A stage is ready to take in new inputs when it is in the reset phase while it produces outputs when it is the evaluate phase. The evaluation of the incoming inputs is performed by a combinational network (CN) embedded within the stage. The control of this phase oscillation is performed by a *phase control* (PC) block, which can be reset at any moment by the reset signal *R*. In each stage, the CN is completely decoupled from the PC block,

and can have an arbitrary delay. Similarly to S-SRSL and P-SRSL pipelines, data flows from one stage to another when the first stage is in the evaluate phase while the second stage is in the reset phase.

Figure 3.22 shows the STG of the D-SRSL linear pipeline shown in Figure 3.21. Although the (*Clr*) signal in Figure 3.22 is not shown in Figure 3.21, its function within the LC block is described in the coming few paragraphs. The STG shows that the rising transition of  $L_3$  occurs after both  $\phi_2$  and  $\phi_3$  experience a rising and falling transition respectively. This means that latch 3 is enabled only when stage 2 is in the evaluate phase while stage 3 is in the reset phase. Since  $L_3$  is asserted while stage 3 is in the reset phase, this guarantees that latch 4 will not be enabled until  $\phi_3$  experiences a rising transition.

Figure 3.22: STG of the D-SRSL pipeline.

#### **3.4.2 Phase Control Block**

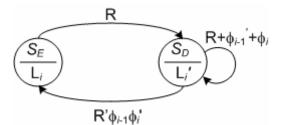

Figure 3.23 shows that the PC block receives three inputs: (i) the reset signal, *R*, which resets the PC block output to 0, (ii)  $L_i$  which is the latch enable of the left latch of stage *i*, and (iii)  $L_{i+1}$ , which is the latch enable of the right stage *i*+1. In turn, it produces an output,  $\phi_i$ , which is the phase signal of stage *i*.

To illustrate the behavior of the PC block, Figure 3.24 shows its state graph which consists of two states: (i) the reset state,  $S_R$ , in which the phase signal becomes 0, and (ii) the evaluate state,  $S_V$ , in which the phase signal becomes 1. As shown in Figure 3.24, the PC block enters the reset state after the reset signal is de-asserted. In this state,  $\phi_i$  is de-asserted, which indicates that the stage is in the reset phase. The PC block remains in this state as long as *R* and  $L_i$  are de-asserted while  $L_{i+1}$  is asserted. Once  $L_{i+1}$  is de-asserted while  $L_i$  becomes asserted, the PC block transitions to the evaluate state in which  $\phi_i$  is asserted. This means that the stage is in the evaluate phase. As long as  $L_{i+1}$  remains de-asserted, the PC block remains in the evaluate state until  $L_{i+1}$  become both asserted, in which case the PC block returns to the reset state. As  $\phi_i$  switches back and forth, a stage

can oscillate between a reset and evaluate phase in a single execution cycle. Given this oscillation, a stage is ready to absorb inputs when it is in the reset phase.

Figure 3.24: State graph of the PC block.

While the inputs are traveling along the critical path of the CN,  $\phi_i$  is similarly traveling along a path that is extended by a delay equal to the critical path delay in the CN. This extended delay is implemented by a buffer which delays the reset phase long enough to allow CN outputs to stabilize. Based on this oscillation, a PC block can be embedded in a pipeline stage forcing the stage to oscillate between two phases. This oscillation can be used to synchronize data transfer between neighboring stages in a D-SRSL pipeline.

#### **3.4.3 Latch Control Block**

Figure 3.25 shows the block diagram of the LC block. This block has three inputs,  $\phi_i$  and  $\phi_{i-1}$ , which are the phases of the current and previous stages respectively, and the reset (*R*) signal. In addition, it has one output  $L_i$ , as defined above, which feeds back into the clear port (Clr) of the LC block.  $L_i$  is the enable signal of the latch between stage *i* and its predecessor stage *i*-1.

To show the behavior of the LC block, Figure 3.26 shows its state graph which consist of two states, namely the enabled state  $S_E$ , and the disabled state  $S_D$ . When the reset signal is asserted, the LC block enters the disabled state in which  $L_i$  gets de-asserted. As long as  $\phi_{i-1}$  is de-asserted while  $\phi_i$  is asserted, the block remains in the disabled state. The LC block waits until  $\phi_{i-1}$  gets asserted while  $\phi_i$  becomes de-asserted to transition to the enabled state. In this state,  $L_i$  gets asserted in order to allow the latch of stage *i* to capture the incoming data from stage *i*-1. After a delay, sufficiently long to allow the data to go through the latch, has elapsed, the LC block returns automatically to the disabled state, thus disabling the latch.

Figure 3.26: State graph of the LC block.

#### 3.5 Summary

This chapter introduces SRSL and shows how this technique can be used to establish handshake signaling between two specific stages in a clockless pipeline. SRSL is used as a foundation to propose three different pipelining techniques: (i) S-SRSL pipelines in which synchronization takes place between two neighboring stages using a fine grain approach, (ii) P-SRSL pipelines in which the oscillation of the pipeline stages are driven by the oscillation of the last stage in the pipeline, and (iii) D-SRSL pipelines where synchronization occurs between each pair of neighboring stages using a coarse-grain approach. While S-SRSL and P-SRSL pipelines require that the stages display equal cycles in the pipeline, D-SRSL can handle individual pipeline stages with arbitrary delays. Although this chapter presents only the linear variants of these three pipelines, the examination of their non-linear variants and the presentation of a detailed timing analysis for each pipeline is presented in [16].

# **CHAPTER FOUR: SYNTHESIS OF SRSL PIPELINES**

This chapter presents a specific SRSL design methodology in section 4.1 while section 4.2 presents the synthesis of SRSL pipelines. This design methodology has been formulated in [16]. Section 4.3 reviews the preliminary concepts used to formulate the synthesis of the SRSL pipeline synthesis problem. The modeling and the formulation of this problem is presented in section 4.4 while section 4.5 explains the proposed heuristic solution.

#### 4.1 SRSL Pipeline Design Methodology

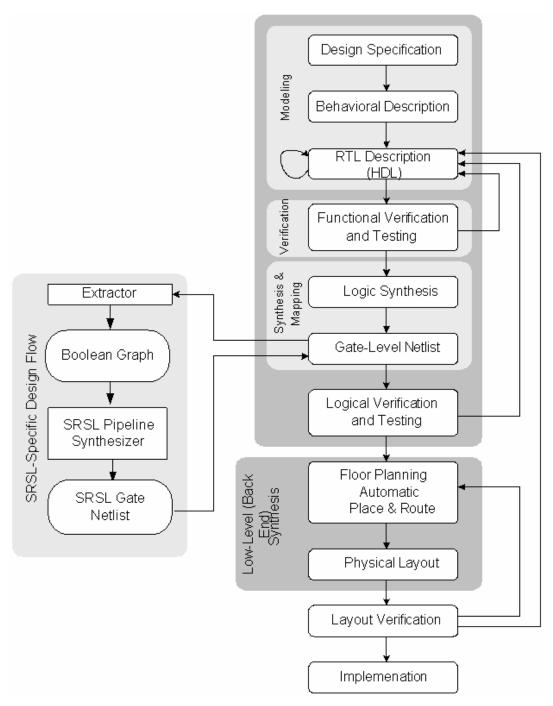

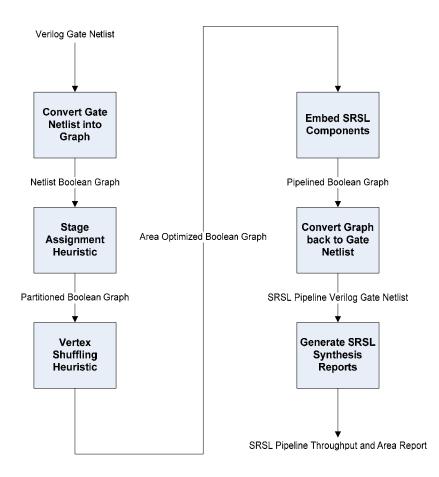

In order to leverage the investment spent on current commercial design tools used in clocked logic, it would make sense to adopt the same design methodology and flow supported by these tools to synthesize SRSL pipelines as argued in [16]. Figure 4.1 proposes the adopted design flow for SRSL logic. In the figure, a parser extracts the clocked gate netlist in order to build a Boolean graph. Next, an SRSL pipeline synthesizer partitions the graph into stages and inserts the latches and the reset network of each stage in appropriate places inside the graph without violating performance constraints. At the end, the synthesizer produces an SRSL pipeline represented as a gate netlist. The SRSL gate netlist can be simulated with any commercial simulator. It can also be mapped onto a standard cell library using any commercial technology mapper in order to produce a cell netlist. The latter can be placed and routed using conventional physical synthesis tools by propagating the same performance constraints used in high level synthesis to the physical synthesis tools.

Figure 4.1: SRSL design flow.

#### **4.2 Synthesis of SRSL Pipelines**

The synthesis of SRSL pipelines consist of transforming a clocked gate netlist into an SRSL pipeline characterized by a data rate and an area cost. Note that by area cost, it is meant the gate area needed to support an SRSL pipeline structure. This gate area consists primarily of (i) latches located between pipeline stages, and (ii) delay elements needed for the reset network of each stage. As such, this synthesis requires (i) the availability of specific gate resources, and (ii) the specification of performance constraints. The gate resources consist of primitive combinational gates, latches, and delay elements. Each resource is characterized by a function, area, and delay attributes. On the other hand, performance constraints can be area or timing constraints. The former refers to a specified upper limit on gate area needed to convert a gate netlist into an SRSL pipeline while the latter refers to a specified lower limit on data rates that can be achieved by converting a gate netlist into an SRSL pipeline.

To transform a gate netlist into an SRSL pipeline, three problems emerge:

**Problem 1 (P1):** Given a gate netlist and a data rate, transform the gate netlist into an SRSL pipeline by incurring the smallest area cost. P1 can be called *the data rate constrained minimum area SRSL pipelining problem*.

**Problem 2 (P2):** Given a gate netlist and an area cost, transform the gate netlist into an SRSL pipeline by achieving the highest data rate. P2 can be called *the area constrained maximum data rate SRSL pipelining problem*.

**Problem 3 (P3):** Given a gate netlist, transform the netlist into an SRSL pipeline with the smallest area cost and the highest data rate. P3 can be called *the unconstrained maximum data rate minimum area SRSL pipelining problem*.

Based on their formulations, both P1 and P2 are dual problems. From a practical perspective, P1 is more relevant to designers than P2 and P3.

# **4.3 Preliminaries**

In order to transform a gate netlist into an SRSL pipeline, a gate netlist is abstracted into an algebraic representation suitable for computation.

*Definition 4.1:* An *incidence structure* consists of a set of modules, a set of nets, and an incidence relation among modules and nets [28].

For instance, an incidence structure can be specified by representing each module with its terminals, also called pins or ports, and to describe the incidence among nets and pins. The incidence relationship can be represented by a matrix.

Definition 4.2: A Boolean network is an incidence structure where:

- Each module performs a Boolean function.

- Each module has multiple inputs and a single output.

- Pins are partitioned into input and output pins.

- Pins that do not belong to modules are primary inputs and primary outputs.

- Each net has a terminal, called source and an orientation from the source to the other terminals, called sinks.

- The source of a net can be either a primary input or the output of a module.

- The sink of a net can be either a module input or a primary output.

- The relation induced by the nets on the module is a partial order [28].

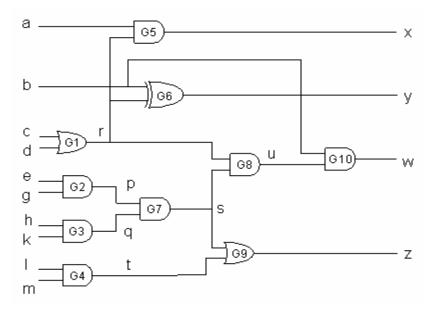

Figure 4.2 shows a Boolean network with 10 primary inputs, 10 modules, and four primary outputs [28].

Figure 4.2: Example of a Boolean network.

Boolean networks can be represented in abstract algebraic structures such as graphs.

Definition 4.3: A graph G(V, E) is a pair (V, E) where V is a set and E is a binary relation on V.

Two vertices in *V* are *neighbors* or *adjacent* if they are connected by an edge in *E*. In this thesis, only finite graphs are considered, meaning graphs with finite sets *V*. The elements of *V* are *vertices* while the elements of *E* are *edges*.

*Definition 4.4:* A *directed graph* is graph G(V, E) where *E* is a set of ordered pairs of vertices.

In a directed graph, if two vertices,  $v_i$  and  $v_j$ , are adjacent, meaning  $(v_i, v_j) \in E$ , the *predecessor* is the vertex located at the tail of the edge, namely  $v_i$ , while the successor is the vertex located at the head of the same edge, namely  $v_j$ . In contrast, the edges are unordered pairs in an *undirected graph*.

*Definition 4.5:* A *path* from vertex *v* to *w* in a graph G(V, E) is a sequence of edges  $v_0v_1$ ,  $v_1v_2, ..., v_{k-1}v_k$ , such that  $v = v_0$  and  $v_k = w$ . The length of the path is *k*.

Such a path can also be represented as an ordered (*k*+1)-tuple:  $\pi = (v_0, v_1, v_2, ..., v_k)$ . In directed graphs, paths follow the direction of the edges.

*Definition 4.6:* A *cycle* in a directed graph is a nonempty path such that the first vertex and the last vertex are identical.

Definition 4.7: A graph is acyclic if it has no cycles.

*Definition 4.8:* A *Boolean graph* G(V, E) is a directed graph where:

- The vertex set *V* is a one-to-one correspondence with the primary inputs, modules, and primary outputs of a Boolean network.

- The directed edge set *E* represents the decomposition of the multi-terminal nets of the Boolean network into two-terminal nets.

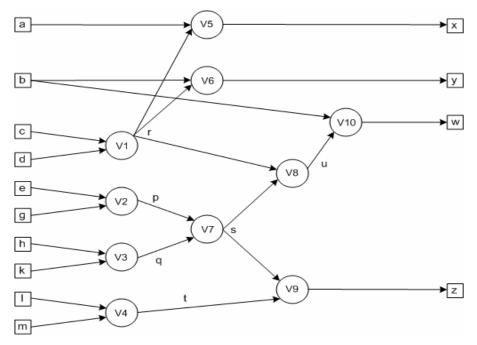

Figure 4.3 shows a Boolean graph based on the Boolean network of Figure 4.2. Note that the Boolean graph is acyclic since the nets induce a partial order on the modules.

Figure 4.3: Boolean graph of the Boolean network shown in Figure 4.2.

The modules of a Boolean network can be mapped to Boolean gates. In this case, its resulting Boolean graph is *a mapped or bound* Boolean graph. The gate netlist produced by the compiler is a mapped Boolean network. Before it is transformed into an SRSL pipeline, it is translated into a Boolean graph.

# **4.4 Analytical Formulation of the Pipelining Problem**

It is assumed that a clocked gate netlist is specified by a mapped Boolean graph which is subject to a set of constraints. In addition, it is assumed that the function, area, and delay of each gate representing each vertex in the Boolean graph G(V, E) are known. The constraints can be either data rates or area costs. Transforming a gate netlist into an SRSL pipeline is equivalent to partitioning the Boolean graph of the gate netlist into partitions and assigning each partition to a distinct pipeline stage. Let  $S = \{s_1, s_2, ..., s_{|S|}\}$  be the set of pipeline stages where the size of this set, |S|, is some positive integer. Let  $V = \{v_i ; i = 1, 2, ..., |V|\}$  and  $E = \{(v_i, v_j) ; i, j = 1, 2, ..., |E|\}$ .

Definition 4.9: A pipelining of a Boolean graph is a function  $\varphi: V \to Z^+$  where  $\varphi(v_i) = s_k$  denotes the gate assignment to a stage  $s_k \in S$  such that  $\varphi(v_i) \le \varphi(v_j), \forall (v_i, v_j) \in E$ .

Since each vertex in V has a delay,  $D = \{d_i; i = 1, 2, ..., |V|\}$ . It is assumed that there are no delays on edges in E beside the delays on the vertices in V. Adding delays to the edges will not disturb the modeling of the synthesis problem; in fact, it will improve the quality of its solution. Obviously, such a graph, in which a delay is attributed to each vertex, will have a critical path.

Definition 4.10: The delay of a path p in a graph G, denoted by  $d_p$ , is the sum of the delays of the vertices in p, i.e.,  $d_p = \sum_{i:y_i \in p} d_i$ .

Definition 4.11: Let  $\Pi$  be the set of all paths in a Boolean graph G(V, E). A critical path in G is a path  $\pi$  whose delay is the largest path delay in  $\Pi$ , i.e.,  $d_{\pi} = \max \{ d_p : p \in \Pi \}$ . In P1, a data rate *f* is given and the objective is to minimize the area cost incurred by partitioning the Boolean graph into stage partitions. The period *P* of a single stage can be obtained from *f* as  $P = \frac{1}{f}$ . Surely, there is a critical path  $\pi$  in the Boolean graph *G* whose delay is  $d_{\pi}$ . An upper bound on the number of stages in the pipeline, called *maximum pipeline depth*, can be obtained from *P* and  $d_{\pi}$ . If |S| is the cardinality of *S*, the maximum pipeline depth is  $|S| = \left\lceil \frac{d_{\pi}}{P} \right\rceil = \left\lceil d_{\pi} f \right\rceil$ . Moreover, |S| can be refined further by using an alternative upper bound if the synthesized pipeline is an S-SRSL pipeline as discussed in [16]. In this case,  $|S| = \min\left\{ \left\lceil \frac{d_{\pi}}{P} \right\rceil, \left\lfloor 1 + \frac{1}{\delta} \left( \frac{P}{2} - d \left( L_{1}^{+} \right) \right) \right\} \right\}$  based on [16].

*Definition 4.12:* A binary variable  $x_{i,s}$  is associated with each vertex  $v_i$  in V of G(V, E) where:

- (i)  $x_{i,s} = 1$  iff the gate *i*, represented by  $v_i$ , is assigned to stage *s*

- (ii)  $x_{i,s} = 0$  otherwise.

In order to realize a correct partitioning, it is imperative that each vertex in the Boolean graph be assigned to a single stage. This requirement is the foundation for a set of constraints called *assignment constraints*:

$$\sum_{s=1}^{|s|} x_{i,s} = 1, \quad i = 1, 2, ..., |V|$$

(4.1)

There are |V| such constraints in the problem. It also imperative to observe the condition stated in Definition 4.9, namely that the successor of a vertex should be assigned to (i) the same stage as its predecessor, or (ii) a stage located after the stage of its predecessor. This requirement is the foundation for a set of constraints called *precedence constraints*:

$$\sum_{s=1}^{|s|} sx_{i,s} \le \sum_{s=1}^{|s|} sx_{j,s}, \quad \forall (v_i, v_j) \in E$$

$$(4.2)$$

These constraints can be rewritten as:

$$\sum_{s=1}^{|s|} sx_{j,s} - \sum_{s=1}^{|s|} sx_{i,s} \ge 0, \quad \forall (v_i, v_j) \in E$$

(4.3)

There are |E| such constraints in the problem. Since *P* can be obtained from the given data rate, it is important that the delay through each stage does not exceed *P*:

$$\sum_{i:v_i \in \pi} d_i x_{i,s} \le p, \ s = 1, 2, ..., |S|$$

(4.4)

There are |S| such constraints in the problem. By partitioning the Boolean graph into stages, segments of the critical path, or subpaths, are assigned to different stages. The delay on these subpaths determines primarily the period of the stage in which they are included. Constraint (4.4) can be rewritten as an equality if a *balanced pipeline* is desired. A balanced pipelined is a pipeline in which all the stages have the same period, i.e.,  $P = P_i$ , i = 1, 2, ..., |S|. Balancing a pipeline is relevant only when synthesizing S-SRSL and P-SRSL pipelines. The partitioning of the gate netlist into stages requires the insertion of (i) latches to separate neighboring stages, and (ii) delay elements to realize the reset network of each pipeline stage. In general, the number of latches inserted between two adjacent vertices,  $(v_i, v_j) \in E$ , depend on the stages,  $s_k$  and  $s_l \in S$ , to which both vertices are assigned respectively. Two cases are possible based on the precedence constraints (4.2):

- (i) k = l: This means that both stages represent the same stage. In this case,  $v_i$  and  $v_j$  are assigned to the same stage.

- (ii)  $k \neq l$ : This means that both stages are different. In this case,  $v_i$  and  $v_j$  are assigned to distinct stages. However, there is no indication that both stages,  $s_k$  and  $s_l$  are neighbors.

In fact, it is possible that two adjacent vertices may be assigned to two non-neighboring stages. For example, if  $v_i$  is assigned to stage 3 and  $v_j$  is assigned to stage 7, the edge between the two vertices has to cross the latches of stage 3, 4, 6, and 7, which may require the insertion of four latches to accommodate this case.

*Definition 4.13:* If two adjacent vertices,  $(v_i, v_j) \in E$ , are assigned to stages  $s_k$  and  $s_l \in S$  respectively, the *pipeline distance* between  $v_i$  and  $v_j$ , denoted by  $\delta_{i,j}$ , is  $\delta_{i,j} = l - k$ .

Depending on the bit width of the combinational network in a given stage, latches of different bit widths can be used to separate a stage from its neighbor. It would make sense to quantify the area of the inter-stage latches by multiplying the area of a single-bit latch by the number of output bit lines crossing from stage to stage. These lines correspond to edges in the Boolean graph. Assume that  $a_l$  is the area of a single-bit latch. If *n* bit lines are crossing from a stage to another, *n* latches are needed adding up to an

area of  $na_l$ . Using the definition of pipeline distance, the number of 1-bit latches between two adjacent vertices can be determined as:

$$\delta_{i,j} = \sum_{s=1}^{|s|} s x_{j,s} - \sum_{s=1}^{|s|} s x_{i,s}, \quad (v_i, v_j) \in E$$

(4.5)

If applied to a single edge, (4.5) is similar to the left-hand side of (4.3). The latch area needed to support the stages between  $v_i$  and  $v_j$  is  $\delta_{i,j}a_i$ . By considering all the edges in the Boolean graph, the total latch area needed in an entire pipeline can be determined as follows:

$$\sum_{\forall (v_i, v_j) \in E} a_l \left( \sum_{s=1}^{|S|} s x_{j,s} - \sum_{s=1}^{|S|} s x_{i,s} \right)$$

(4.6)

Beside the insertion of latches, the insertion of delay elements is also needed to realize the reset network of a stage. These delay elements can be inverters, buffers, or gates. Since the role of the matching delay of a reset network in SRSL is to provide a delay equal to the delay of the critical path of the combinational network, it would make sense to use gates as delay elements to realize the matching delay of the reset network. In fact, the critical path of the combinational network can be merely duplicated and the obtained copy can be used as a matching delay in the reset network. In this case, the area of the matching delay to be inserted in the reset network of a stage can be determined by obtaining the area of the critical path of the combinational network in the stage. Since each vertex in *V* has an area,  $A = \{a_i; i = 1, 2, ..., |V|\}$ . If the area of the matching delay of a stage *s* is  $a_s$ , then:

$$a_{s} = \sum_{i:v_{i}\in\pi} a_{i}x_{i,s}, \quad s = 1, 2, ..., |S|$$

(4.7)

By considering all the stages in the pipeline, the total area of matching delays can be determined as:

$$\sum_{s=1}^{|s|} \left( \sum_{i:v_i \in \pi} a_i x_{i,s} \right)$$

(4.8)

By summing the total area needed for latches shown in (4.6), and matching delays shown in (4.8), the minimization of the area cost can be expressed as the following objective function:

$$\min a_{l} \sum_{\forall (v_{i}, v_{j}) \in E} \left( \sum_{s=1}^{|S|} sx_{j,s} - \sum_{s=1}^{|S|} sx_{i,s} \right) + \sum_{s=1}^{|S|} \left( \sum_{i: v_{i} \in \pi} a_{i} x_{i,s} \right)$$

(4.9)

In summary, P1 can be formulated as the following *integer programming* (IP) problem [29]:

$$\min a_{i} \sum_{\forall (v_{i}, v_{j}) \in E} \left( \sum_{s=1}^{|s|} sx_{j,s} - \sum_{s=1}^{|s|} sx_{i,s} \right) + \sum_{s=1}^{|s|} \left( \sum_{i:v_{i} \in \pi} a_{i}x_{i,s} \right)$$

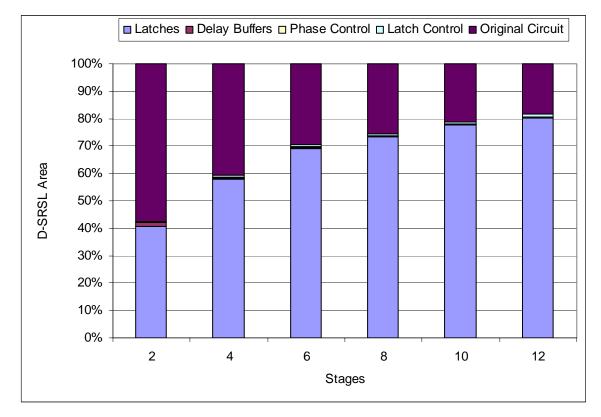

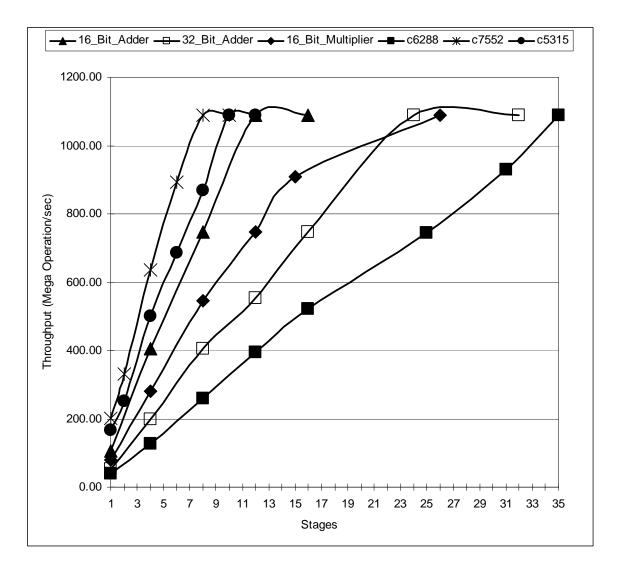

(4.9)