University of Central Florida

Electronic Theses and Dissertations, 2004-2019

2016

# Advanced Metrology and Diagnostic Loss Analytics for Crystalline Silicon Photovoltaics.

Eric Schneller University of Central Florida

Part of the Engineering Science and Materials Commons Find similar works at: https://stars.library.ucf.edu/etd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

## **STARS Citation**

Schneller, Eric, "Advanced Metrology and Diagnostic Loss Analytics for Crystalline Silicon Photovoltaics." (2016). *Electronic Theses and Dissertations, 2004-2019.* 5266. https://stars.library.ucf.edu/etd/5266

# ADVANCED METROLOGY AND DIAGNOSTIC LOSS ANALYTICS FOR CRYSTALLINE SILCION PHOTOVOLTAICS

by

**ERIC SCHNELLER**

B.S. in Physics, Point Loma Nazarene University, 2010 M.S. in Material Science and Engineering, University of Central Florida, 2012

> A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Material Science and Engineering in the College of Computer Science and Engineering at the University of Central Florida Orlando, Florida

> > Fall Term 2016

Major Professor: Winston Schoenfeld

© 2016 Eric Schneller

#### ABSTRACT

Characterization plays a key role in developing a comprehensive understanding of the structure and performance of photovoltaic devices. High quality characterization methods enable researchers to assess material choices and processing steps, ultimately giving way to improved device performance and reduced manufacturing costs. In this work, several aspects of advanced metrology for crystalline silicon photovoltaic are investigated including in-line applications for manufacturing, off-line applications for research and development, and module/system level applications to evaluate long-term reliability.

A frame work was developed to assess the cost and potential value of metrology within a manufacturing line. This framework has been published to an on-line calculator in an effort to provide the solar industry with an intuitive and transparent method of evaluating the economics of in-line metrology. One important use of metrology is in evaluating spatial non-uniformities, as localized defects in large area solar cells often reduce overall device performance. Techniques that probe spatial uniformity were explored and analysis algorithms were developed that provide insights regarding process non-uniformity and its impact on device performance. Finally, a comprehensive suite of module level characterization was developed to accurately evaluate performance and identify degradation mechanisms in field deployed photovoltaic modules. For each of these applications, case-studies were used to demonstrate the value of these techniques and to highlight potential use cases.

iii

## ACKNOWLEDGMENTS

This dissertation represents the culmination of a long, wonderful journey that has both humbled and inspired me along the way. I would not be where I am today were it not for all of the guidance, support and encouragement I have received from many people.

First, I would like to express my gratitude to my advisor Winton Schoenfeld for his technical and professional guidance and for the open and productive work environment he has provided for my PhD research. I am grateful to my committee members James Fenton, Jayan Thomas, Kalpathy Sundaram, and Kevin Coffey for their time and feedback. I am especially grateful to Kristopher Davis for the many hours of discussion that have undoubtable improved the quality of this work.

This research would not be possible without the technical input from many researchers at the Florida Solar Energy Center including Narendra Shiradkar, Hubert Seignuer, Joseph Walters, Neelkanth Dhere, Paul Brooker, Siyu Guo, A.J. Dunevent, Jason Lincoln and Kortan Ogutman. The insight provided by Greg Horner (Tau Science) and Keith McIntosh (PV Lighthouse) have been instrumental in developing the content for this dissertation. There are many others, of which there are too many to name, with whom I have crossed paths, all contributing in their small way and to them I am grateful.

Finally, I would like to thank my family for providing me with the foundation on which all of this was possible, and most importantly to AnnMarie who has been there to support me every step of the way.

"Anyone who has never made a mistake has never tried anything new." - Albert Einstein

# TABLE OF CONTENTS

| LIST OF FIGURES                                          | vii  |

|----------------------------------------------------------|------|

| LIST OF TABLES                                           | xi   |

| LIST OF SYMBOLS                                          | xii  |

| LIST OF ABBREVIATIONS                                    | xiii |

| CHAPTER 1: INTRODUCTION                                  | 1    |

| 1.1 Trends within the Energy Industry                    | 1    |

| 1.2 Photovoltaic Energy                                  |      |

| 1.2.1 Brief History                                      | 3    |

| 1.2.2 Conversion Technologies                            | 6    |

| 1.2.3 Economic Driving Forces                            | 8    |

| 1.3 Motivation                                           | 12   |

| CHAPTER 2: OVERVIEW OF CRYSTALLINE SILICON PHOTOVOLTAICS | 13   |

| 2.1 Photovoltaic Cells                                   | 13   |

| 2.1.1 Device Operation                                   | 13   |

| 2.1.2 Diode Equations                                    |      |

| 2.1.3 I-V Characteristics                                |      |

| 2.2 Cell Design                                          | 20   |

| 2.2.1 Conventional Cell Designs                          | 20   |

| 2.2.2 Advanced Cell Designs                              | 23   |

| 2.3 Module Design                                        | 24   |

| 2.3.1 Manufacturing Process                              | 24   |

| 2.3.2 Reliability Concerns                               | 26   |

| CHAPTER 3: EVALUATING THE VALUE OF METROLOGY             | 30   |

| 3.1 Introduction                                         | 30   |

| 3.2 The Value of Metrology                               |      |

| 3.2.1 Defining Value                                     |      |

| 3.2.2 Quality Control                                    |      |

| 3.2.3 Opportunity Cost                                   |      |

| 3.3 Calculator Methodology                               |      |

| 3.3.1 Terminology                                        |      |

| 3.3.2 Overview                                           |      |

| 3.3.3 Inputs                                             |      |

| 3.3.4 Outputs                                            | 51   |

| 3.3.5 Discussion                                         |      |

| 3.4     | Case Studies                                                    | 54  |

|---------|-----------------------------------------------------------------|-----|

| 3.4.1   | Wafer Rejection Based on iVoc Prior to Metallization            | 54  |

| 3.4.2   | Advanced Optical Inspection for Screen Printing Process Control | 59  |

| 3.5     | Conclusions                                                     | 65  |

|         |                                                                 |     |

| CHAPTER | R 4: SPATIALLY RESOLVED CELL CHARACTERIZATION                   | 67  |

| 4.1     | Introduction                                                    | 67  |

| 4.1.1   | Quantum Efficiency Measurements                                 | 67  |

| 4.2     | Luminescence Imaging                                            | 69  |

| 4.2.1   | Luminescence Imaging for Defect Detection.                      | 71  |

| 4.3     | Quantum Efficiency Mapping                                      | 74  |

| 4.3.1   | Measurement System                                              | 74  |

| 4.3.2   | Quantification of Loss Mechanisms                               | 78  |

| 4.3.3   | Spatially Resolved Current Loss Analysis                        | 88  |

| 4.3.4   |                                                                 |     |

| 4.3.5   |                                                                 |     |

| 4.3.6   | Assessment of Measurement Uncertainty                           | 96  |

| 4.4     | Case Studies                                                    | 101 |

| 4.4.1   | Impact of Diamond Wire Sawing                                   | 101 |

| 4.4.2   | - F · · · · · · · · · · · · · · · · · ·                         |     |

| 4.4.3   | Cell Fracture Analysis                                          | 113 |

| 4.5     | Conclusions                                                     | 117 |

| СНАРТЕ  | S 5: MODULE LOSS ANALYSIS                                       | 118 |

| 5.1     | Module Performance Characterization                             |     |

| 5.1.1   |                                                                 |     |

| 5.1.2   | -                                                               |     |

| 5.2     | Case Studies                                                    |     |

| 5.2.1   |                                                                 |     |

| 5.2.1   | -                                                               |     |

| 5.3     | Conclusions                                                     |     |

| 5.5     |                                                                 | 138 |

| CHAPTER | 8 6: CONCLUSION                                                 | 139 |

| REFEREN | CES                                                             |     |

|         |                                                                 |     |

| LIST | OF | FIG | JRES |

|------|----|-----|------|

|------|----|-----|------|

| Figure 1. Historic and projected electricity generation capacity installations (in Gigawatts) in the U.S. by fuel type [2].                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2. Cumulative electricity generation capacity (in billion kilowatthours) within the U.S. by fuel type [2]2                                                                                                                                                                    |

| Figure 3. Utility-Scale solar PV capacity projections (in gigawatts) from the Annual Energy Outlook 2011 to 2015 [4].                                                                                                                                                                |

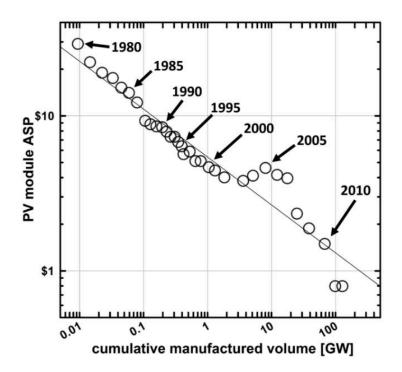

| Figure 4. PV module manufacturing cost learning curve5                                                                                                                                                                                                                               |

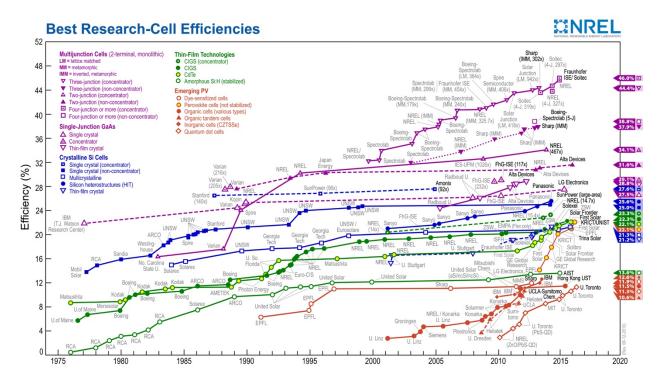

| Figure 5. Record efficiencies for various PV technologies over time5                                                                                                                                                                                                                 |

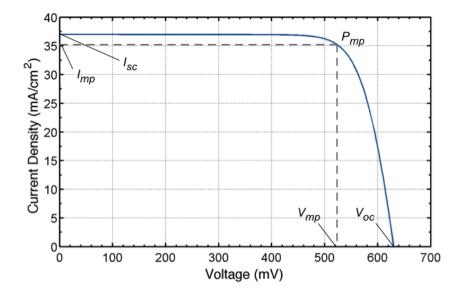

| Figure 6. Example J-V characteristics representative of conventional c-Si device performance                                                                                                                                                                                         |

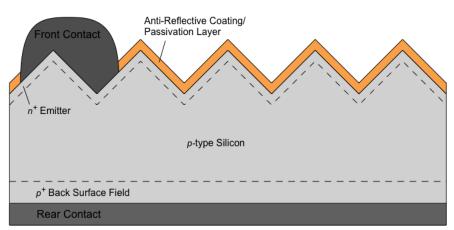

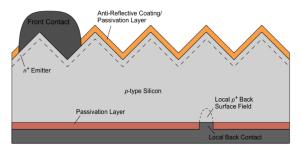

| Figure 7. Figure of Al-BSF cell architecture                                                                                                                                                                                                                                         |

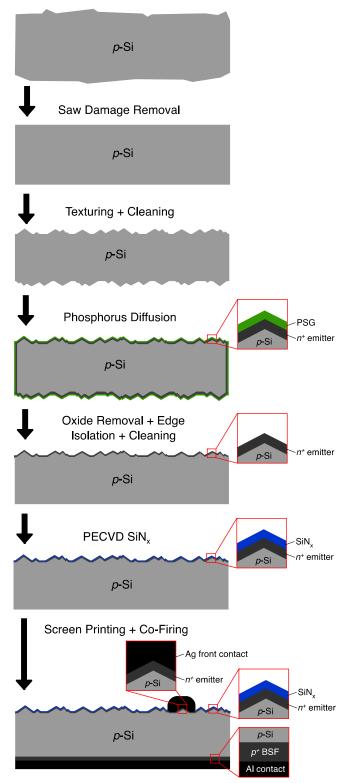

| Figure 8. Process Flow for a standard AI-BSF solar cell22                                                                                                                                                                                                                            |

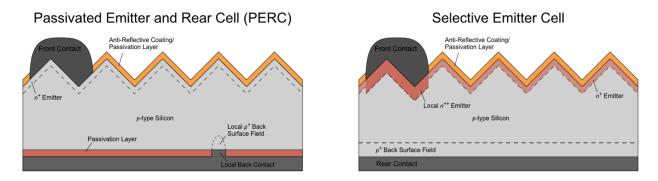

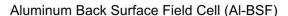

| Figure 9. Design for a PERC cell (left) and a selective emitter cell (right)                                                                                                                                                                                                         |

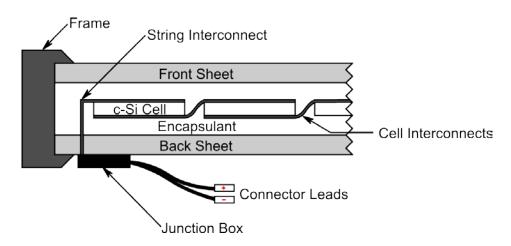

| Figure 10. Typical structure of a PV module25                                                                                                                                                                                                                                        |

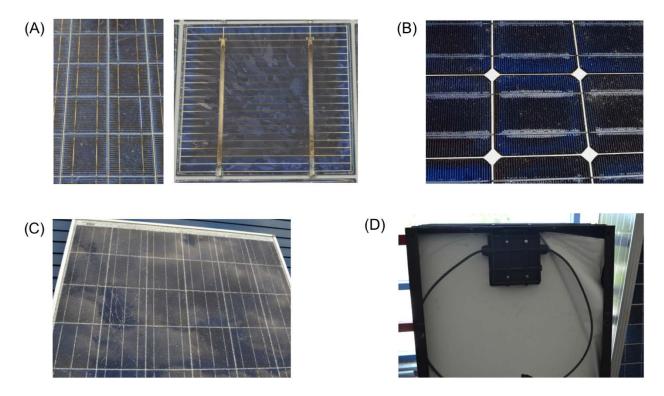

| Figure 11. Example of module packaging degradation and failures. (a) browning or discoloration of the encapsulant, (b) delamination of the encapsulant near the busbars, (c) glass breakage and (d) back sheet delamination28                                                        |

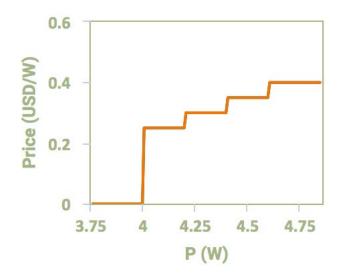

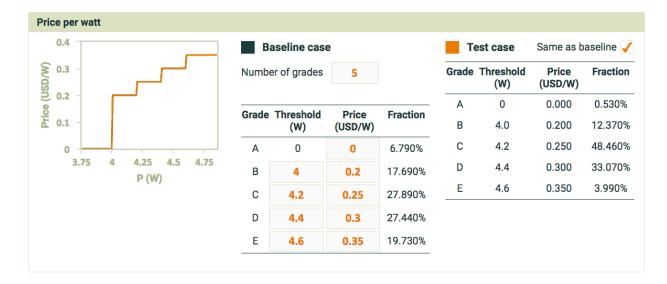

| Figure 12. Example of a price per watt function for c-Si PV cells                                                                                                                                                                                                                    |

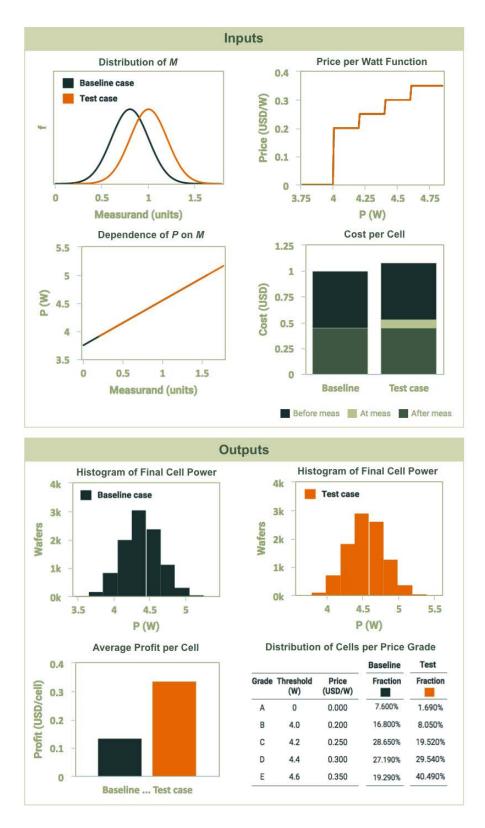

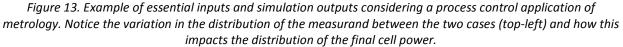

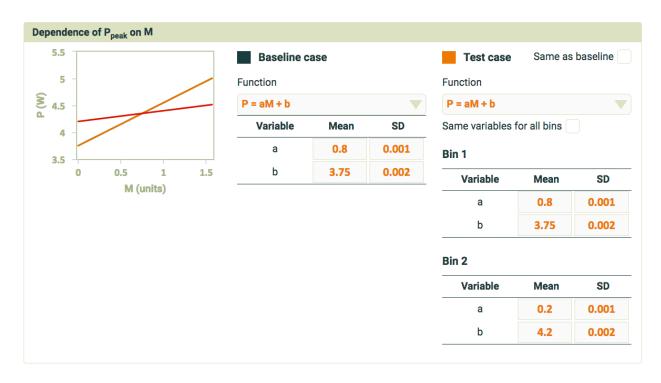

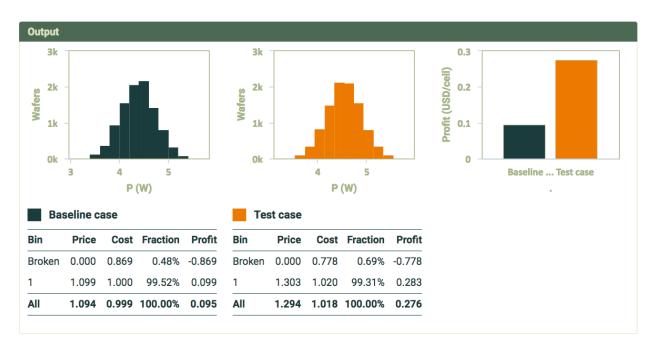

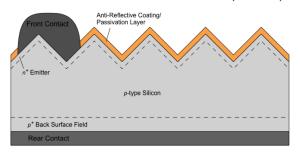

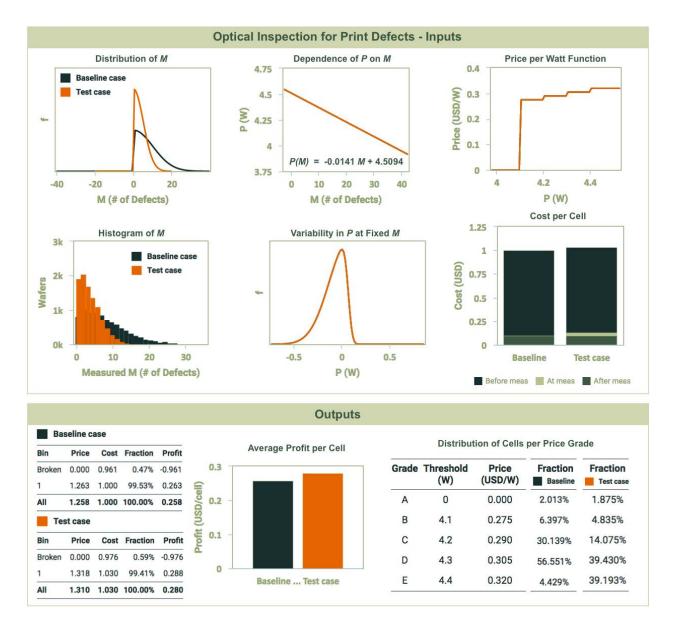

| Figure 13. Example of essential inputs and simulation outputs considering a process control application of metrology.<br>Notice the variation in the distribution of the measurand between the two cases (top-left) and how this impacts<br>the distribution of the final cell power |

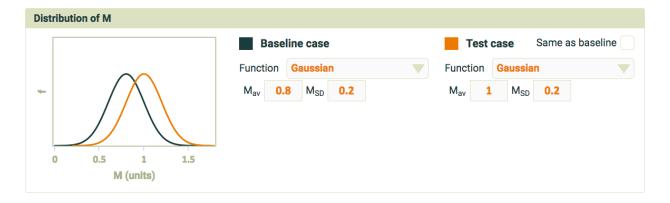

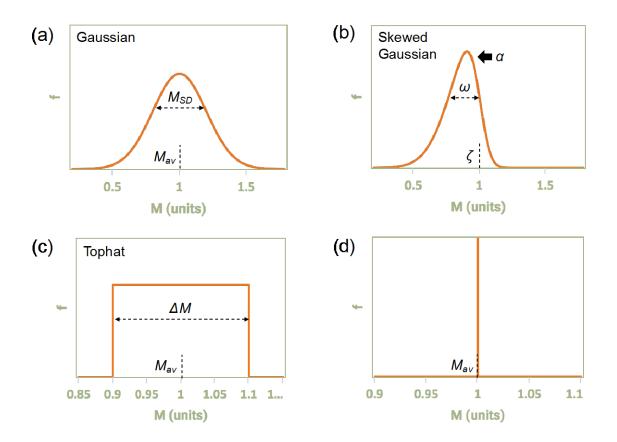

| Figure 14. Input dialog for the distribution of the M40                                                                                                                                                                                                                              |

| Figure 15. Possible distribution functions including the parameters used to describe each function                                                                                                                                                                                   |

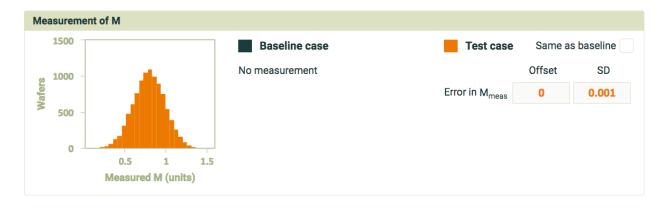

| Figure 16. Input dialog for measurement of M43                                                                                                                                                                                                                                       |

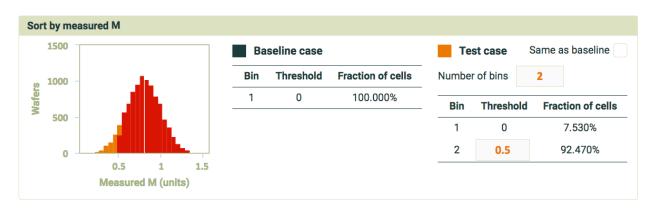

| Figure 17. Input dialog for sort by measured M44                                                                                                                                                                                                                                     |

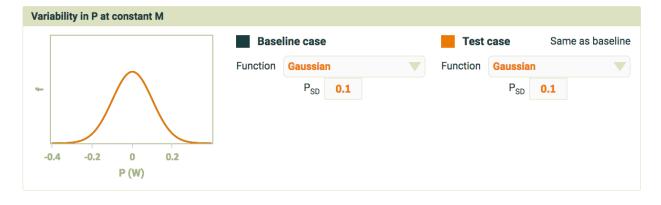

| Figure 18. Input dialog for variability in P at a constant M45                                                                                                                                                                                                                       |

| Figure 19. Input dialog for dependence of P on M46                                                                                                                                                                                                                                   |

| Figure 20. Input dialog for production costs per cell                                                                                                                                                                                                                                |

| Figure 21. Input dialog for defining the sale price of cells                                                                                                                                                                                                                         |

| Figure 22. Input dialog for mechanical yield50                                                                                                                                                                                                                                       |

| Figure 23. Cost-Benefit Calculator Outputs                                                                                                                                                                                                                                           |

| Figure 24. Cell architecture for PERC and Al-BSF cells. The front surface is highlighted in orange and the rear surface passivated of the PERC cell is highlighted in red                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 25. Critical inputs for simulating wafer rejection from iV $_{oc}$ measurements for                                                                                                                                                                                                                  |

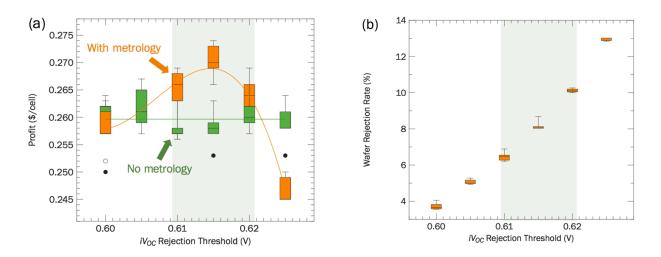

| Figure 26. Influence of the rejection threshold on the (a) profit per cell and (b) wafer rejection rate                                                                                                                                                                                                     |

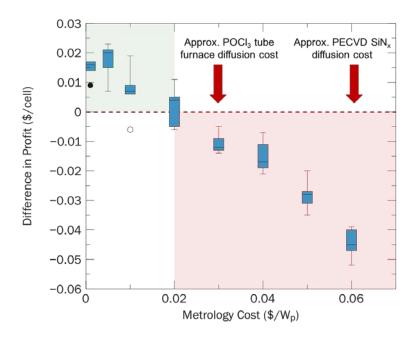

| Figure 27. Impact of metrology cost on profit for wafer rejection                                                                                                                                                                                                                                           |

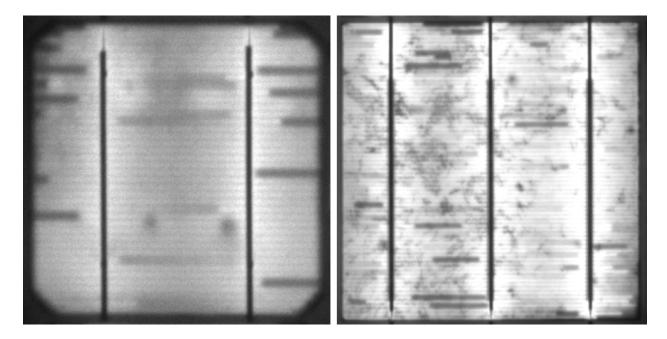

| Figure 28. Electroluminescence image of a monocrystalline cell (left) and a multicrystalline cell (right) with a high number of metallization defects                                                                                                                                                       |

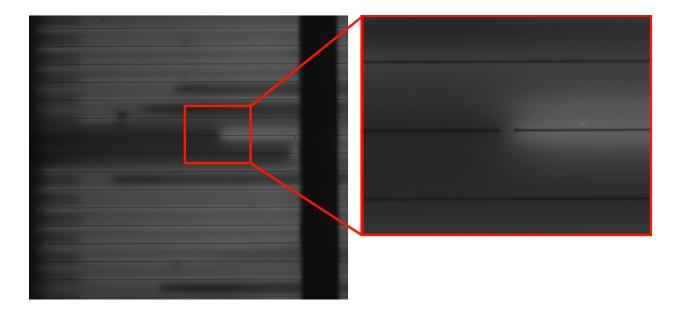

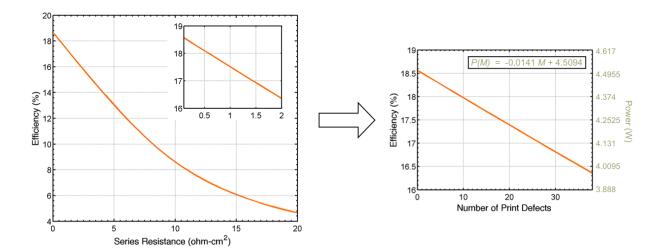

| Figure 29. Zoomed in electroluminescence image of a metallization defect clearly showing the discontinuity60                                                                                                                                                                                                |

| Figure 30. Relevant Input and outputs from the cost-benefit analysis for the use of optical inspection after the screen printing step                                                                                                                                                                       |

| Figure 31. Relationship between cell efficiency and series resistance (left) with the range of interest highlighted in the inset. Assuming that each defect increases the series resistance by 0.05 ohm cm <sup>2</sup> , the relationship between cell power and number of defects is determined (right)62 |

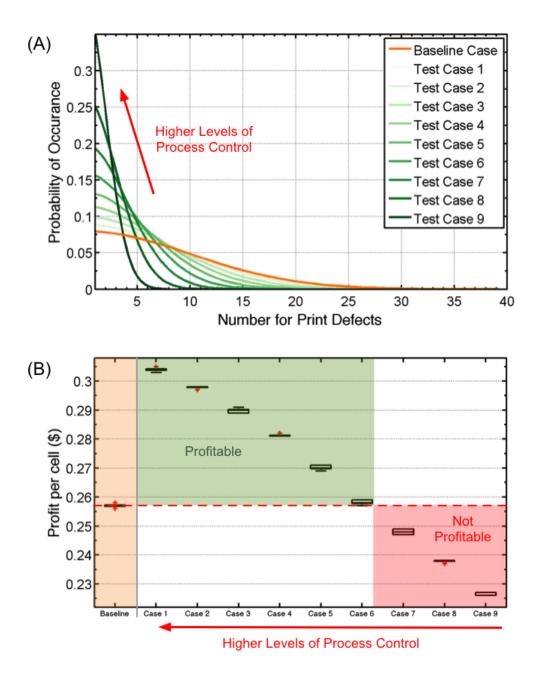

| Figure 32. Cost analysis considering several variations in the distribution of M                                                                                                                                                                                                                            |

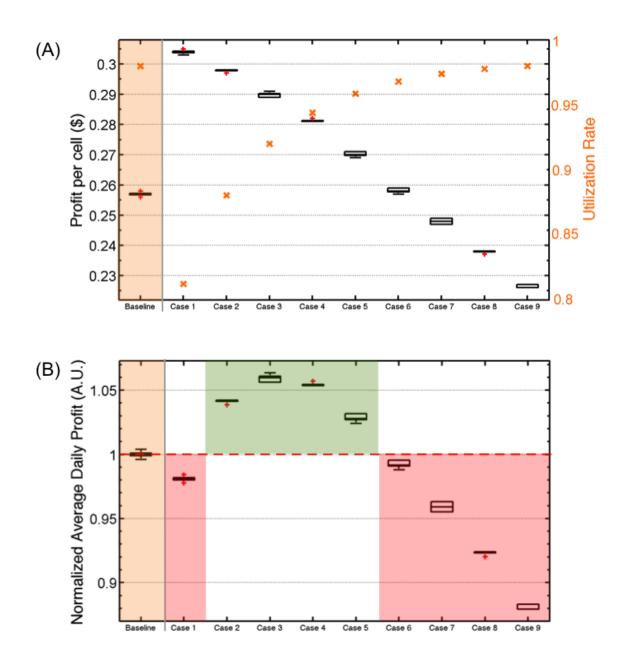

| Figure 33. Cost analysis considering the influence of utilization rate (A) on the profitability of each process control case (B)                                                                                                                                                                            |

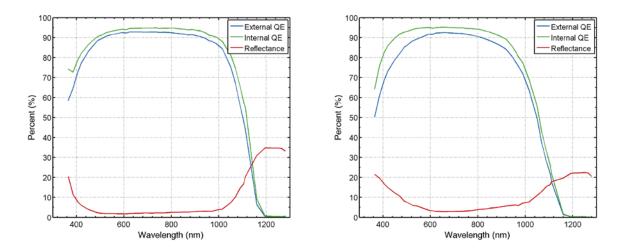

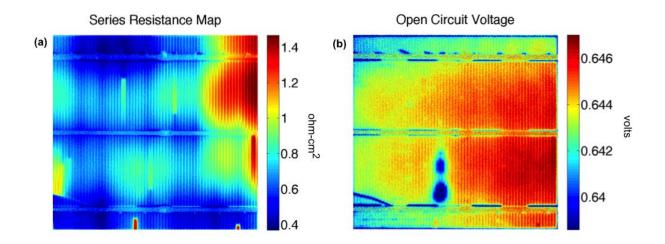

| Figure 34. Example EQE, IQE and reflectance spectra for two cells monocrystalline PERC (left) and multicrystalline Al-<br>BSF (right)                                                                                                                                                                       |

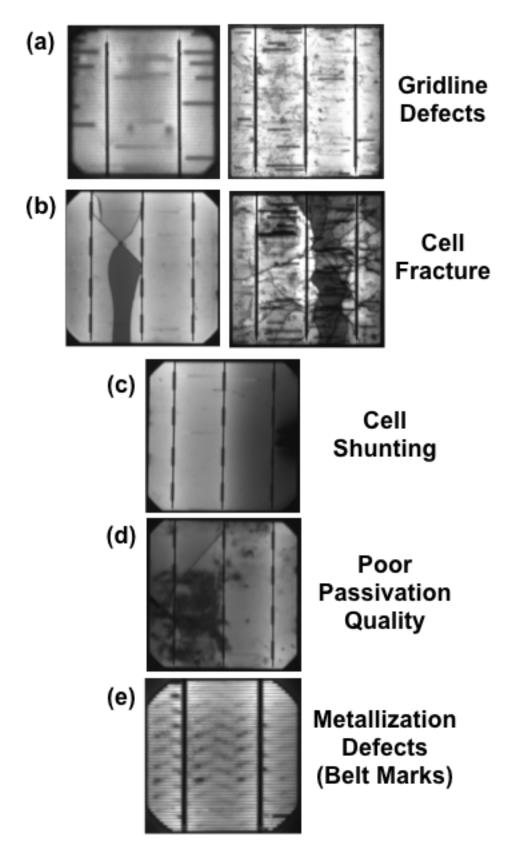

| Figure 35. EL images exhibiting various spatially resolved defects impacting performance                                                                                                                                                                                                                    |

| Figure 36. Parameter maps derived from PL imaging73                                                                                                                                                                                                                                                         |

| Figure 37. FlashQE Measurement System76                                                                                                                                                                                                                                                                     |

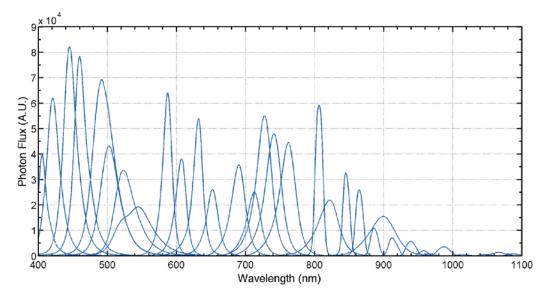

| Figure 38. Spectra of LED's in the FlashQE system76                                                                                                                                                                                                                                                         |

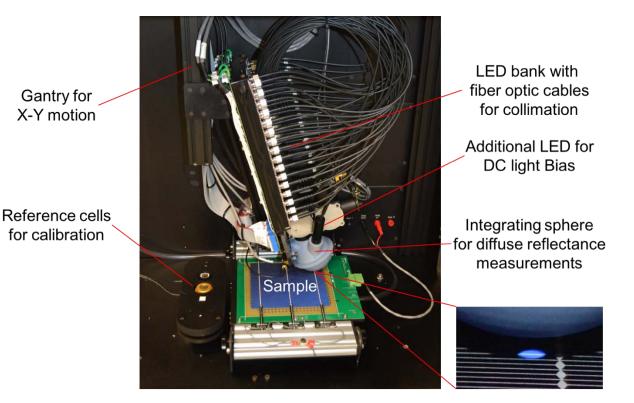

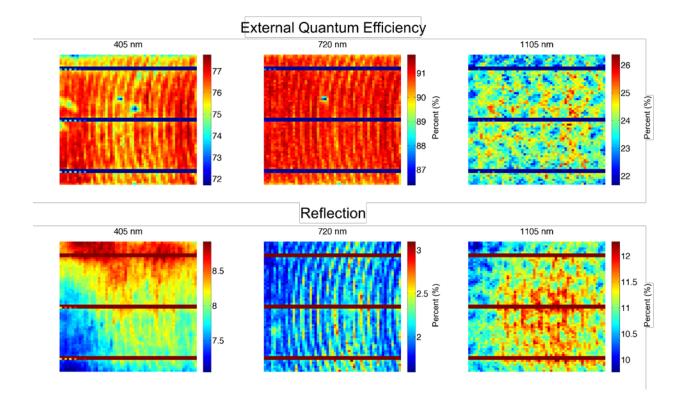

| Figure 39. EQE and reflectance maps of one cell at several wavelengths78                                                                                                                                                                                                                                    |

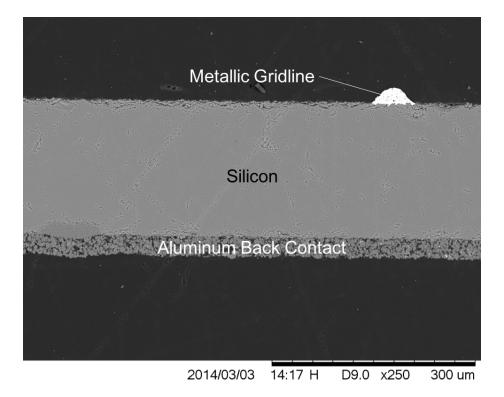

| Figure 40. Cross Sectional SEM of monocrystalline PERC device81                                                                                                                                                                                                                                             |

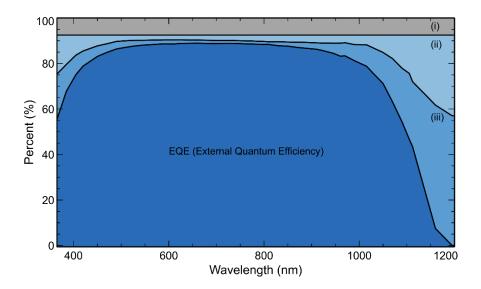

| Figure 41. EQE of a high quality monocrystalline pPERC83                                                                                                                                                                                                                                                    |

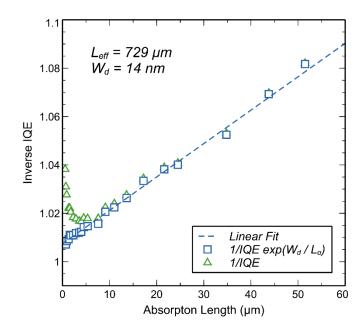

| Figure 42. Inverse IQE as a function of absorption length in a mono-crystalline pPERC cell                                                                                                                                                                                                                  |

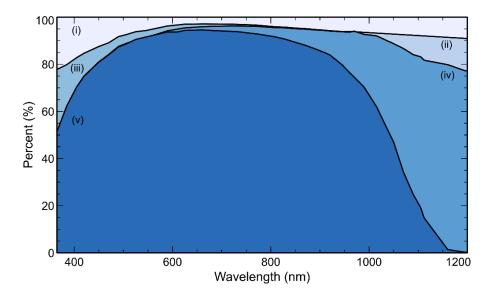

| Figure 43. EQE of a multicrystalline AI-BSF cell with several loss mechanisms identified                                                                                                                                                                                                                    |

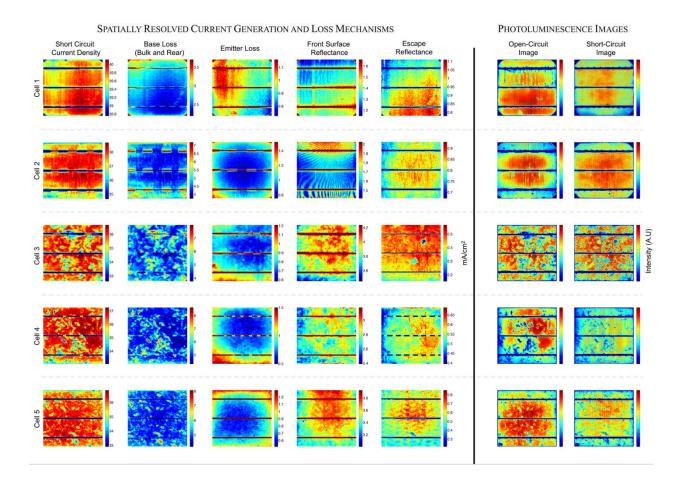

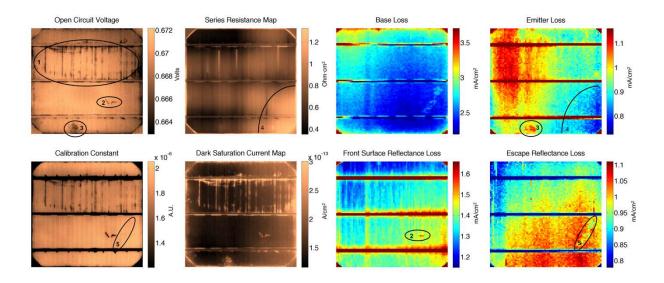

| Figure 44. Spatially resolved $J_{sc}$ along with each of the current loss mechanisms measurements for five cells                                                                                                                                                                                           |

| Figure 45. Comparison of defects using both photoluminescence imaging techniques and spatially resolved current<br>loss analysis                                                                                                                                                                            |

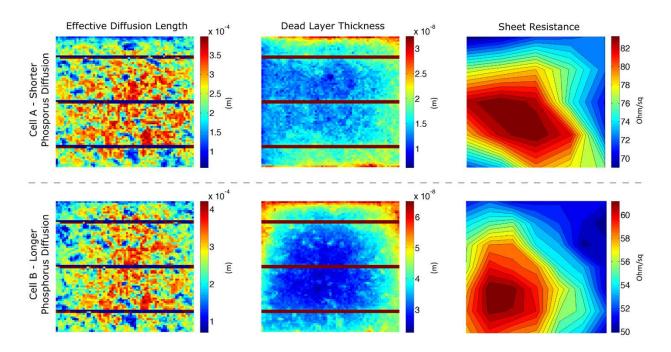

| Figure 46: Maps for base diffusion length, dead layer thickness and sheet resistance                                                                                                                                                                                                                        |

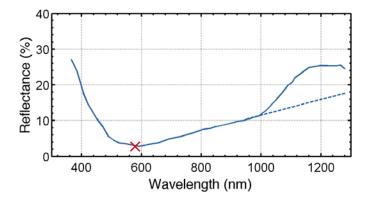

| Figure 47. Reflectance spectra for a multicrystalline Al-BSF cell. The characteristic minimum is marked in red and the extrapolated ARC reflectance is shown with the dotted line                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

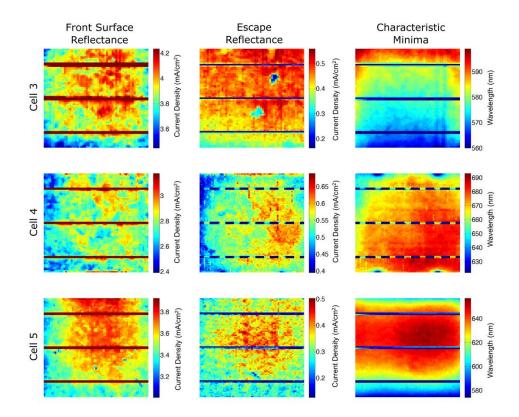

| Figure 48: Maps of front surface reflectance, escape reflectance and characteristic minima for three cells                                                                                                                       |

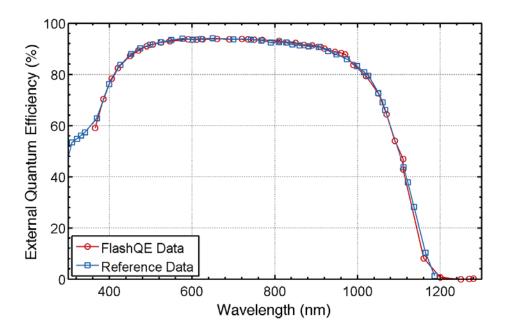

| Figure 49. Comparison of Flash QE data with results from a calibration laboratory                                                                                                                                                |

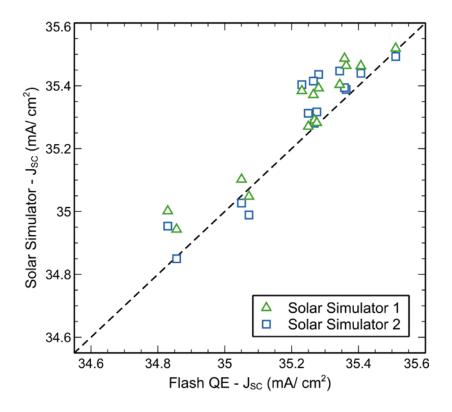

| Figure 50. Comparison of FlashQE J <sub>sc</sub> measurements with Solar Simulator results100                                                                                                                                    |

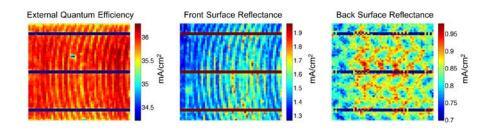

| Figure 51: Short-circuit current density (left), front surface reflectance loss (center), escape reflectance loss (right)<br>maps for a cell exhibiting pilgrim wave features as a result of the diamond wire sawing process103  |

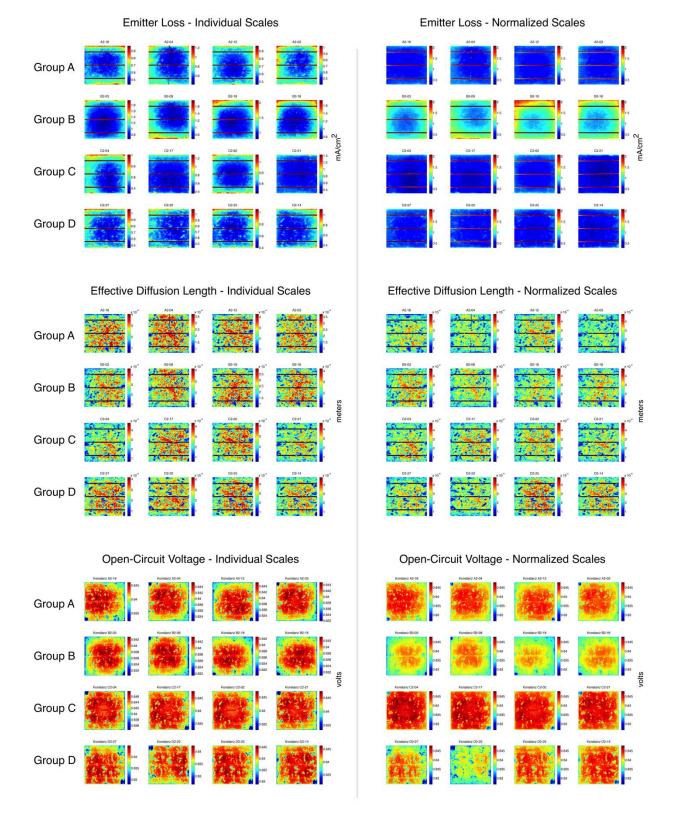

| Figure 52: Parameters maps derived from photoluminescence imaging                                                                                                                                                                |

| Figure 53. Structure of a selective emitter cell architecture with the two distinct emitter regions highlighted in red.<br>                                                                                                      |

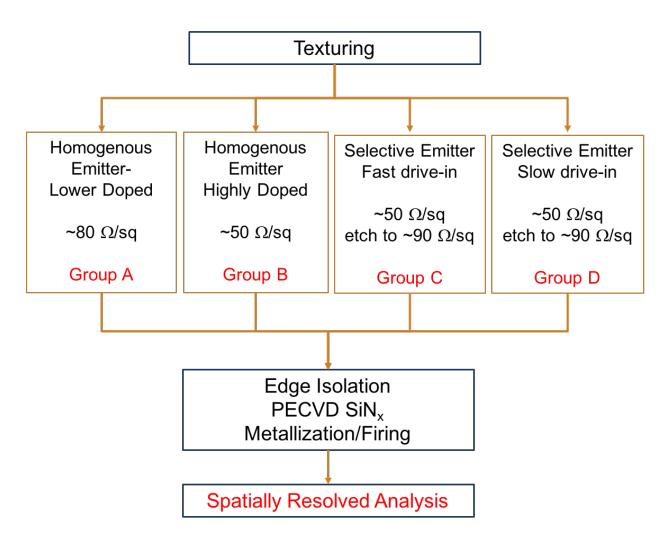

| Figure 54. Process flow and process variation for selective emitter study                                                                                                                                                        |

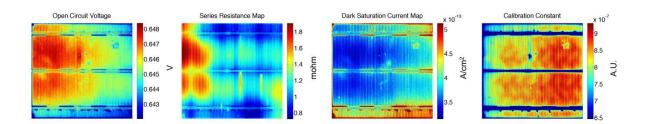

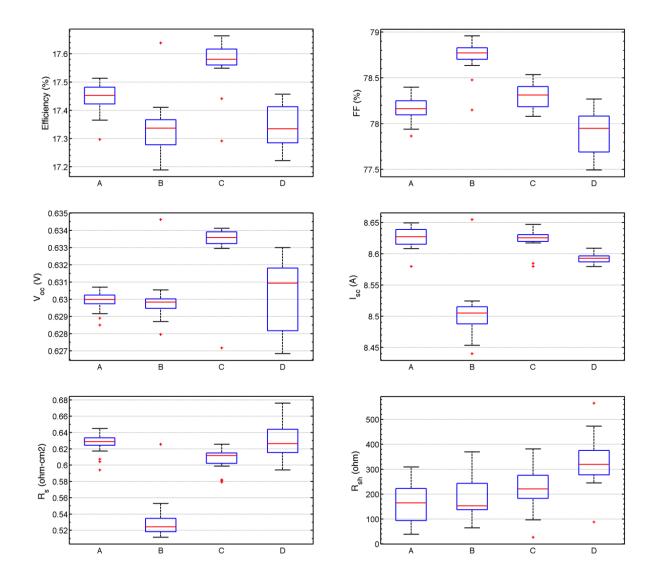

| Figure 55. Summary of I-V analysis for selective emitter study. Box-plots were constructed using the 25 cells in each the four groups                                                                                            |

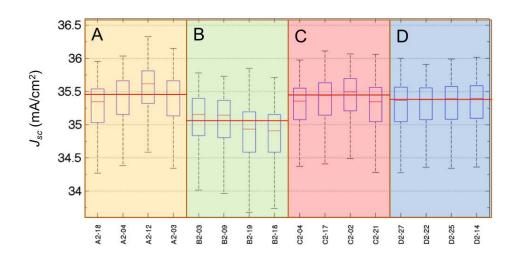

| Figure 56. Spatially resolved J <sub>sc</sub> as calculated from Eq. (16) for 16 cells109                                                                                                                                        |

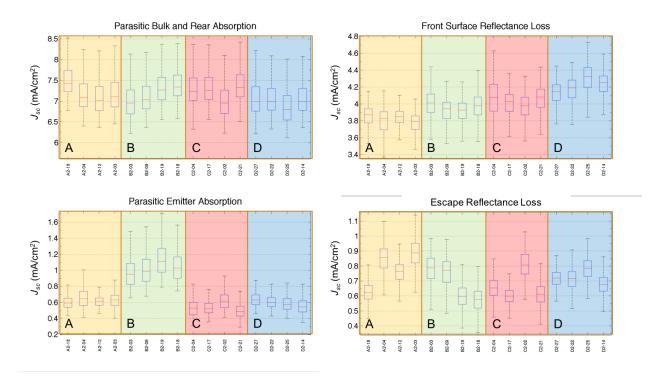

| Figure 57. Box-plots for each of the current loss mechanisms as determined from FlashQE measurements, with the distribution for each cell generated from the spatially resolved analysis                                         |

| Figure 58. Parameter maps derived from Flash QE and PL imaging112                                                                                                                                                                |

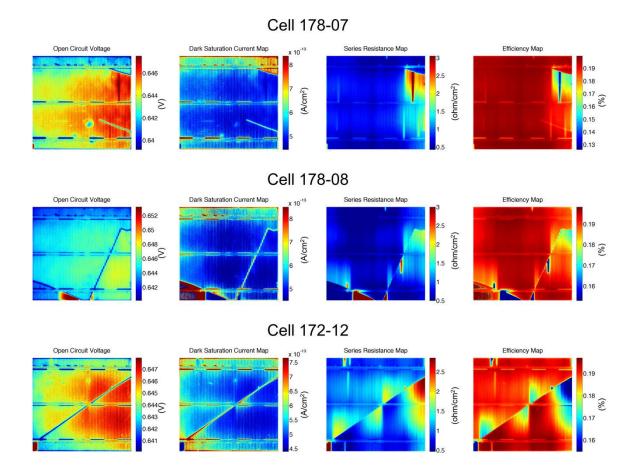

| Figure 59. Parameter maps derived from PL imaging for three cells that exhibit cell fracture                                                                                                                                     |

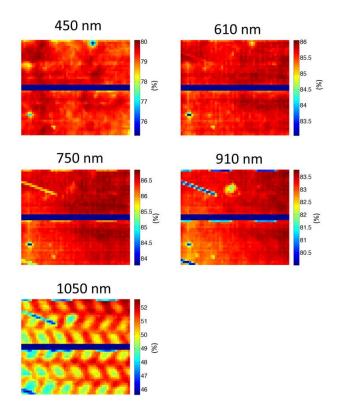

| Figure 60. EQE maps at five distinct wavelengths for a partially fractured cell                                                                                                                                                  |

| Figure 61. Sinton FMT-350 solar simulator; (left) view from the light source toward the module and (right) module during illumination                                                                                            |

| Figure 62. Spire 4600 solar simulator. Modules are placed face down on the glass                                                                                                                                                 |

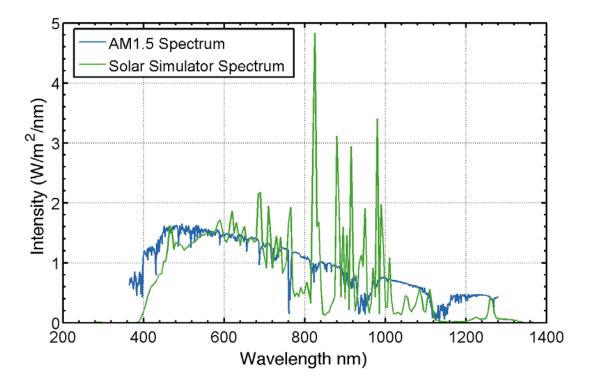

| Figure 63. Comparison of the standard solar spectrum with a spectrum from a SPIRE 4600 solar simulator120                                                                                                                        |

| Figure 64. Uniformity profiles for two large area solar simulators used in this work. Each square represents a 6" by 6" area, with the units in percentages of the nominal 1000W/m <sup>2</sup> value                            |

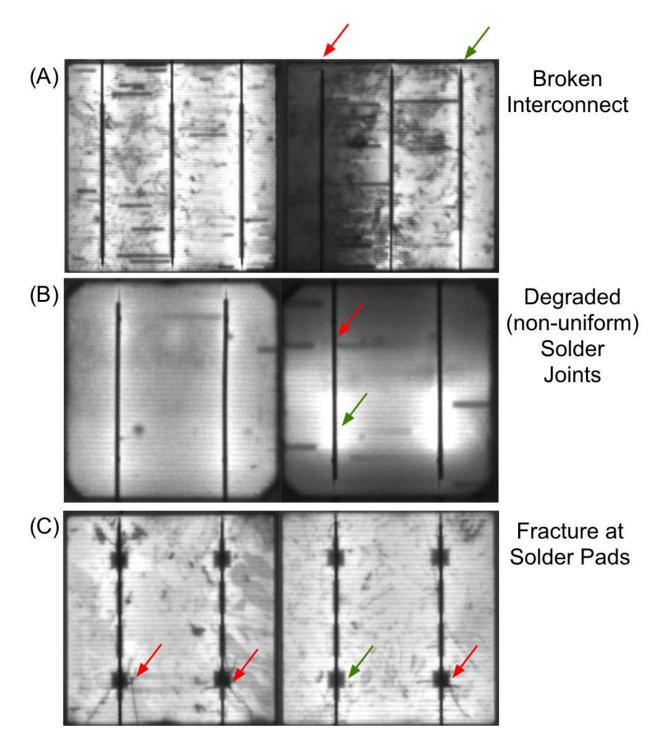

| Figure 65. Example of module related defects; (A) broken interconnect highlighted in red, (B) degraded solder joint between the interconnect ribbon and the cell busbar, (C) cell fracture induced from the soldering process125 |

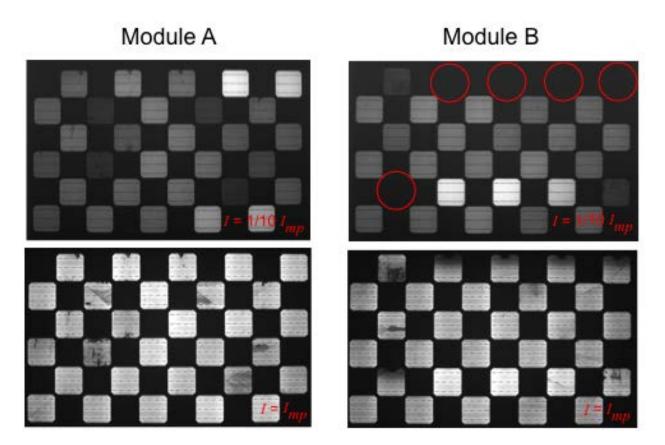

| Figure 66. EL images at 1/10 Imp and Imp for both modules used in this study. The red circles highlight the 5 cells that have severe shunts                                                                                      |

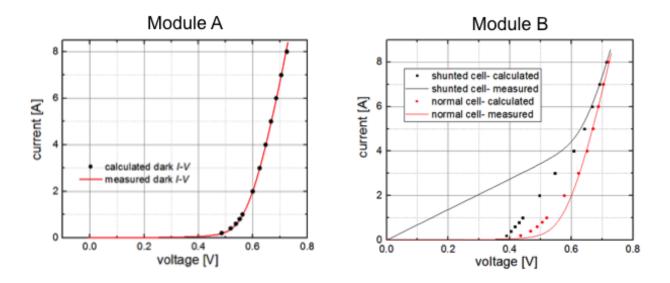

| Figure 67. Comparison of electrical measurements with EL derived (calculated) data for select cells128                                                                                                                           |

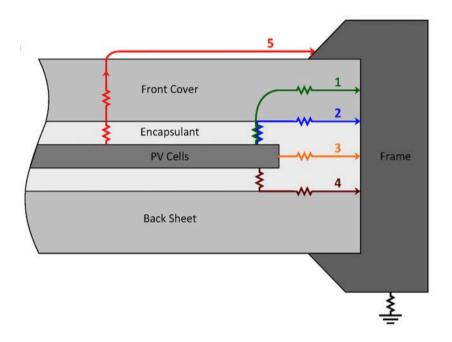

| Figure 68. Cross section diagram of a PV showing the conduction pathways through the module packaging when a large potential exists                                                                                              |

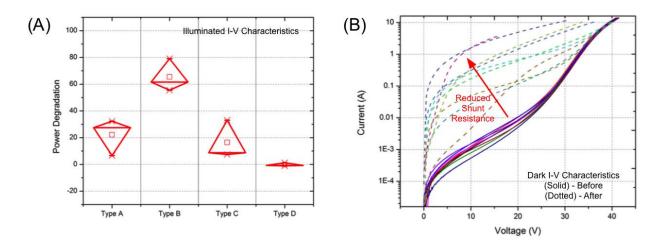

| Figure 69. Performance of modules used in the PID study; (A) Power degradation for each module type, (B) Dark I-V characteristics showing a clear reduction in shunt resistance on all degraded modules                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

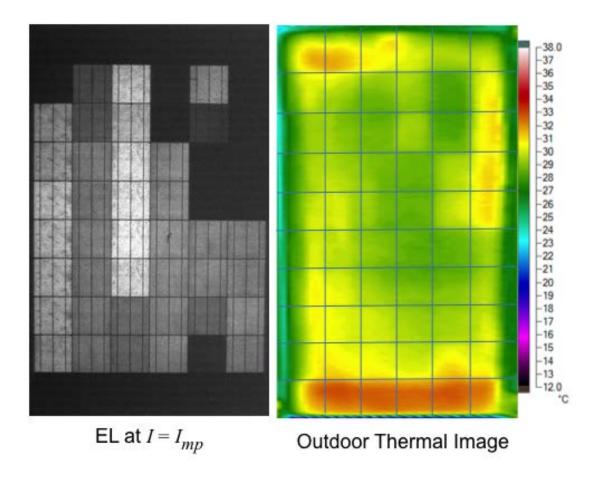

| Figure 70. Electroluminescence image and thermal image of module showing PID degradation                                                                                                                                                           |

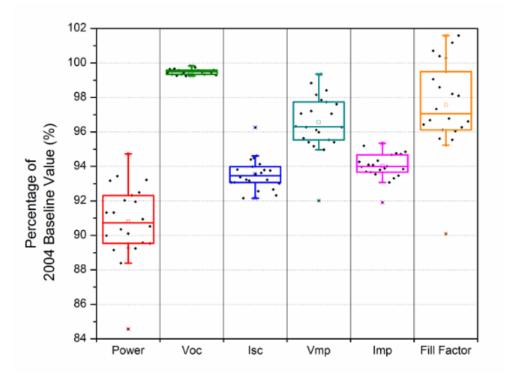

| Figure 71. PV Performance parameters as a percentage of their original baseline values after 10 years of outdoor exposure                                                                                                                          |

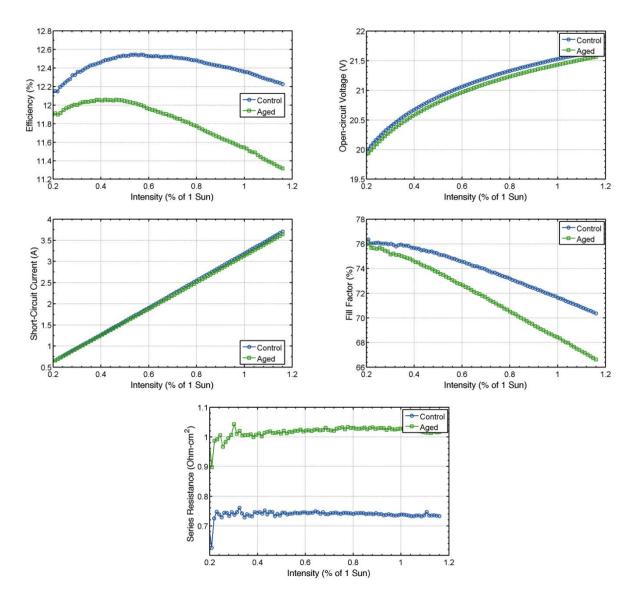

| Figure 72. Analysis of two modules (control and aged) over a range of intensities for several performance parameters.<br>                                                                                                                          |

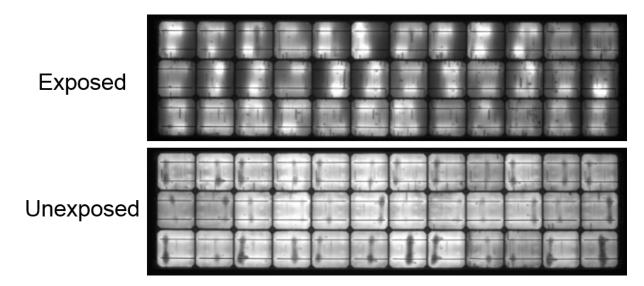

| Figure 73. EL images taken with a forward current equal to Isc for the control (unexposed) and aged (exposed) modules                                                                                                                              |

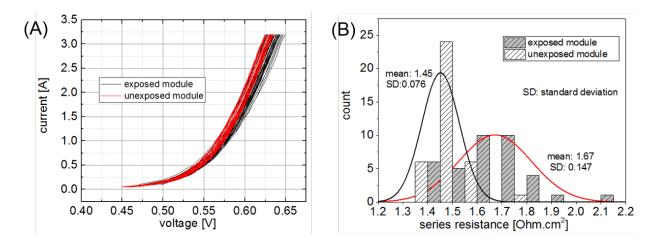

| Figure 74. (A) I-V characteristics determined from the EL imaging technique for each cell in both modules and (B) the histogram of the series resistance for each cell as determined from fitting of the ideal diode equation to the curves in (A) |

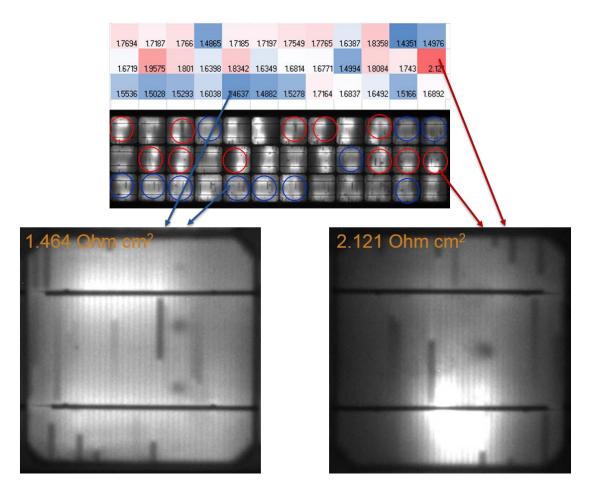

| Figure 75. EL                                                                                                                                                                                                                                      |

## LIST OF TABLES

| Table 1. List of parameters relevant to c-Si PV manufacturing along with the appropriate inse | ertion points in the |

|-----------------------------------------------------------------------------------------------|----------------------|

| manufacturing process flow                                                                    |                      |

|                                                                                               |                      |

| Table 2. Cost point allocation for a typical Al-BSF process sequence [26]                     | 48                   |

| Symbol                 | Description (Common Units)                                            |

|------------------------|-----------------------------------------------------------------------|

| 4                      | Absorption within Anti Doflactive Costing                             |

| AARC                   | Absorption within Anti-Reflective Coating                             |

| α                      | Absorption Coefficient (cm <sup>-1</sup> )                            |

| C                      | Speed of Light (m/s)                                                  |

| fmetal<br>f            | Metal Fraction of Cell Area                                           |

| feff                   | Effective Shading Fraction                                            |

| h                      | Plank's Constant                                                      |

| Imp                    | Maximum Power Current (A)                                             |

| l <sub>sc</sub>        | Short-Circuit Current (A)                                             |

| <i>І</i> ам1.5         | Intensity of Standard Air Mass 1.5 Solar Spectrum (W/m <sup>2</sup> ) |

| iV <sub>oc</sub>       | Implied Open Circuit Voltage (mV)                                     |

| Jo                     | Dark Saturation Current Density (mA/cm <sup>2</sup> )                 |

| J <sub>sc</sub>        | Short Circuit Current Density (mA/cm <sup>2</sup> )                   |

| k                      | Boltzmann's Constant                                                  |

| Ld,base                | Diffusion Length in the Base ( $\mu m$ )                              |

| L <sub>d,emitter</sub> | Diffusion Length in the Emitter ( $\mu$ m)                            |

| L <sub>d,eff</sub>     | Effective Diffusion Length (μm)                                       |

| Lα                     | Absorption Length in Silicon (cm)                                     |

| P <sub>mp</sub>        | Maximum Power Point (W)                                               |

| М                      | Measurand                                                             |

| $\eta$                 | Efficiency (%)                                                        |

| п                      | Refractive Index                                                      |

| q                      | Charge of Electron (eV)                                               |

| Ractive                | Reflectance of the Active Area of the Cell                            |

| RARC                   | Reflectance of the Anti-Reflective Coating                            |

| R <sub>meas</sub>      | Measured Reflectance                                                  |

| Rescape                | Escape Reflectance                                                    |

| R <sub>metal</sub>     | Reflectance of Metallic Front Contact                                 |

| Rseries                | Series Resistance (Ohm cm <sup>2</sup> )                              |

| Rshunt                 | Shunt Resistance (Ohm)                                                |

| Sfront                 | Front Surface Recombination Velocity                                  |

| Srear                  | Rear Surface Recombination Velocity                                   |

| t                      | Film Thickness (nm)                                                   |

| τ                      | Carrier Lifetime(µsec)                                                |

| Voc                    | Open-Circuit Voltage (mV)                                             |

| V <sub>mp</sub>        | Maximum Power Voltage (mV)                                            |

| Vτ                     | Thermal Voltage                                                       |

| W <sub>d</sub>         | Dead-Layer Thickness (cm)                                             |

| λ                      | Wavelength (nm)                                                       |

| $\Phi_{ph}$            | Incident Photon Flux (cm <sup>-2</sup> ·s <sup>-1</sup> )             |

## LIST OF ABBREVIATIONS

| Abbreviation | Description                             |

|--------------|-----------------------------------------|

| Al-BSF       | Aluminum Back Surface Field             |

| ARC          | Anti-Reflective Coating                 |

| BSF          | Back Surface Field                      |

| c-Si         | Crystalline Silicon                     |

| EL           | Electroluminescence                     |

| EQE          | External Quantum Efficiency             |

| FTIR         | Fourier Transform Infrared Spectroscopy |

| IQE          | Internal Quantum Efficiency             |

| I-V          | Current-Voltage                         |

| LCOE         | Leveled Cost of Energy                  |

| LED          | Light Emitting Diode                    |

| LID          | Light Induced Degradation               |

| NIR          | Near-Infrared                           |

| 0&M          | Operation and Maintenance               |

| PERC         | Passivated Emitter and Rear Cell        |

| PID          | Potential Induced Degradation           |

| PL           | Photoluminescence                       |

| PV           | Photovoltaic                            |

| SEM          | Scanning Electron Microscopy            |

| SNR          | Signal to Noise Ratio                   |

| STC          | Standard Test Conditions                |

## **CHAPTER 1: INTRODUCTION**

#### 1.1 <u>Trends within the Energy Industry</u>

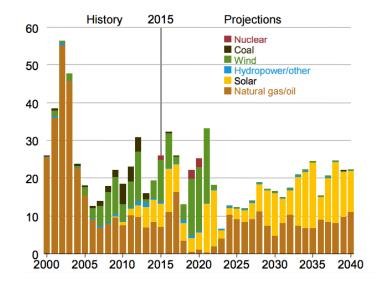

Worldwide energy demand is expected to increase over the next several decades [1]. Even with significant advances in energy efficiency, the electrification of countries such as India and China will require the deployment of new energy generation capacity around the world. Because of the potential risks due to increased carbon dioxide in the atmosphere, the world is looking to carbon free alternatives for supplying this energy demand. With recent cost reductions in both wind and solar energy technologies, renewables are now considered a viable, cost competitive alternative to fossil fuels in many markets. In fact, in the United States more than half of all new electricity generation comes from renewable sources. Projections from the U.S. Energy Information Administration have solar and natural gas as the two dominant technologies that will be deployed for the coming decades [2].

Figure 1. Historic and projected electricity generation capacity installations (in Gigawatts) in the U.S. by fuel type [2].

Figure 2. Cumulative electricity generation capacity (in billion kilowatthours) within the U.S. by fuel type [2].

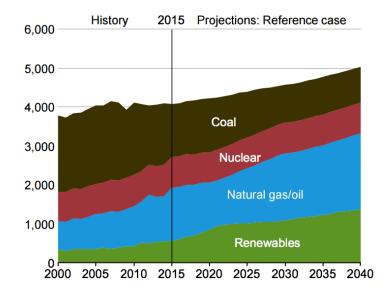

This deployment of renewables is promising, but it is important to realize that existing generation capacity consists largely of coal, nuclear, and natural gas. In terms of cumulative generation capacity, renewables remain only a fraction of the total energy mix. Even though government policy, such as the enactment of the U.S. Clean Power Plan, may affect the rate of deployment, significant changes to these projections require further cost reductions for these technologies.

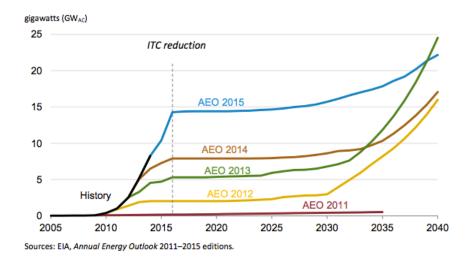

The price of renewable energy technologies, particularly photovoltaic (PV) technologies, have declined rapidly in the past decade. This has caught many international agencies off guard. For example, in 2004 the International Energy Agency predicted that renewables (excluding hydro) would account for only 4% of global electricity generation by 2030 [3]. Less than ten years later this 4% mark has been exceeded. Another example would be the U.S. Energy Information Administration projections provided each year in their Annual Energy Outlook report [4]. As seen in Figure 3, estimates have greatly underestimated the rate of PV deployment in the U.S. for several consecutive years. The takeaway here is that large shifts in the economics of specific technologies can change the global outlook in extraordinary ways.

Figure 3. Utility-Scale solar PV capacity projections (in gigawatts) from the Annual Energy Outlook 2011 to 2015 [4].

#### 1.2 Photovoltaic Energy

#### 1.2.1 Brief History

Photovoltaic solar cells were first explored in the mid-20<sup>th</sup> century, with the world's first crystalline Silicon (c-Si) based solar cell developed in 1954 at Bell Laboratories [5]. Space applications quickly became a major market for these devices. In 1958, the Vanguard I became the first satellite to utilize PV cells to power its radio communications. To this day, PV cells continues to be the go-to energy source for space applications. This early market allowed for developments to continue, however the high costs remained prohibitive for many terrestrial

applications. Slowly, efficiency of these devices continued to increase while prices continued to decline.

During the 1970's and 80's deployment of flat-plate PV systems became a reality. c-Si became the dominant technology for terrestrial applications, however higher efficiency alternatives including Gallium Arsenide (GaAs) and multijunction cells took over the space industry. As costs continued to decline for PV, new applications emerged. For remote locations where it was expensive or impossible to connect to the grid, PV became a viable alternative. In terms of solar resource, the amount of energy incident on our planet in one year is ~7000 times more than the current global energy demand [6]. Because of the tremendous potential, harnessing the power of the sun to meet the electricity demands of the world remained a dream for many. Until recently, this was only a dream. Today, after 50 years of innovation, PV is now a cost competitive alternative to traditional fossil fuel sources.

The cost of PV has been declining continuously for many years. When the module sale price is plotted against the cumulative module production on a log-log scale, as shown in Figure 4, a linear trend is observed. Here you can see early modules prices above 20 \$/W and where prices stand today at about 0.55 \$/W. It is important to note that this represents only the module cost, and does not represent the true cost of energy, or the levelized cost of electricity (LCOE). The LCOE depends on many factors including the system configuration and geographic location. This variability is what ultimately determines the local economics of PV deployment [7]. Either way, module costs continue to decline as manufacturing improves and capacity expands. More importantly, there is no reason to believe this trend will not continue well into the future.

*Figure 4. PV module manufacturing cost learning curve.*

Figure 5. Record efficiencies for various PV technologies over time.

#### 1.2.2 <u>Conversion Technologies</u>

In an effort to reduce cost and improve efficiency, a wide range of PV technologies have been explored over the years. Figure 5 shows the record efficiencies for all technologies that have been pursued. Interestingly one of the first materials investigated, c-Si, continues to be the dominant PV technology today [8]. Silicon was viewed as less than ideal choice for many decades because it was an indirect band-gap material and required expensive purification and crystal growth methods.

Standard single junction PV devices rely on a semiconductor material that has a band-gap in the range of 1.0-1.75 eV. Direct band-gap semiconductors have the advantage of strong optical absorption, and can therefore be much thinner than c-Si cells. As an alternative to c-Si, thin-film technologies were developed in an attempt to reduce manufacturing costs. Here the cells would be directly deposited on to glass substrates, eliminating the costly crystal growth process inherent to c-Si. Successful candidates included hydrogenated amorphous-Silicon (a-Si:H), Cadmium Telluride (CdTe), and Copper Indium Gallium DiSelenide (CIGS) and required only a few microns of material. Because these devices are fabricated using chemical vapor deposition (CVD) or physical vapor deposition (PVD) techniques the resulting thin-film was either polycrystalline or amorphous. The presence of crystal defects (e.g. grain boundaries) often lead to lower efficiencies than monocrystalline Silicon devices. The greatly reduced manufacturing cost were expected to outweigh these efficiency penalties. Unfortunately, only a few companies have successfully scaled up production using these thin-film technologies, accounting for only a small percentage of PV installations overall. It should be noted that at the cell level, CdTe and CIGS have achieved efficiencies at or above those achieved with multicrystalline Silicon devices as

shown in Figure 5. Many of these technologies have also been fabricated on flexible substrates, opening up unique applications in niche markets.

The highest single-junction device efficiency has been achieved using GaAs. The current record sits at 27.6% under 1-sun illumination. To push the limits even further, multijunction devices have been developed that consist of multiple PV cells stacked on top of each other (i.e. in tandem). The spectral response of each cell is tuned to capture a unique region of the spectrum maximizing the amount of light that can be collected. These devices are also designed with III-V semiconductors. Here, the record efficiencies have been push up to 38.8% for 1-sun conditions and up to 46.0% under concentration. An amazing feat of science and engineering, however the cost remains extremely high. This is due to the expensive substrates and low throughput epitaxial growth techniques. The use of concentrated light has been the most attractive approach to reduce LCOE cost for these devices. An optical concentrator, typically a Fresnel lens, is used to focus a large area of sunlight onto a small area device. This reduces the amount of active area (i.e. PV cell area) that is required. Only direct sunlight can be concentrated, so tracking is required to follow the sun throughout the day. These systems are considerably more complex than standard flat-plate fixed-tilt solar arrays and have yet to compete on a large scale. In space applications, where cost is of less concern, these III-V devices are the standard.

Finally, organic PV devices have been explored as an extremely lost cost alternative. Efficiencies have remained low for these type of devices that employ organic polymers as the active absorber layers. In recent years, perovskite based cells, a type of organic/inorganic blend have reached efficiencies up to 22.1%. When examining the efficiencies in Figure 5, the rise in efficiencies of these perovskite devices is unprecedented. In just a few years these devices have

made significant improvements in performance. Concerns related to the stability of these materials remain the largest challenge for these technologies if they are going to be commercialized.

#### 1.2.3 <u>Economic Driving Forces</u>

Evaluating the cost of solar energy requires an understanding of several key metrics. These can be broken down into to two areas; (1) cost considerations and (2) performance.

Performance of PV is generally defined in terms of conversion efficiency ( $\eta$ ) under what is known as standard test conditions (STC). These conditions refer to an irradiance of 1000 W/m2 using the standard air-mass 1.5 solar spectrum ( $I_{AM1.5}$ ) with the cell at 25 degrees Celsius. These conditions are what determined the efficiencies presented in Figure 5 (excluding concentration results). The 1000W/m<sup>2</sup> value is referred to as 1-Sun conditions throughout this work. This standard provides the industry with a clear method to define the performance of a particular solar cell or module. Efficiency is calculated from Eq. (1) using the peak output power ( $P_{mp}$ ), the input irradiance, and the cell area (A).

$$\eta = \frac{P_{mp}}{I_{AM1,5}*A} \tag{1}$$

A simple cost metric can be determined from the measured power at STC and the manufacturing costs according to Eq. (2). This cost per watt peak  $(\$/W_p)$ , allows for simple cost comparison of various PV technologies. Notice how power, as opposed to conversion efficiency, is the critical factor. Here, even a low efficiency technology can be competitive if manufactured at sufficiently low costs.

Cost per Watt Peak =  $\frac{Cost \text{ of Manufacturing}}{Performance at STC}$

This simple cost metric, although useful, does not necessarily provide information on the cost of energy in terms of dollars per kilowatthours ( $\frac{k}{kWh}$ ). This more complete metric, defined as the levelized cost of electricity (LCOE), is needed to compare costs against traditional energy source like fossil fuels. There are many factors that influence this metric, making it harder to accurately determine. The LCOE is defined in Eq. (3).

$$Levelized \ Cost \ of \ Electricity = \frac{Total \ Lifecycle \ Cost}{Total \ Lifetime \ Energy \ Production}$$

(3)

To determine the total lifetime energy production, much more than performance at STC is required [9]. This requires the quantification of several factor that are both technology specific and system/site specific. At a given site the amount of energy produced is dependent on the array orientation, the tilt angle, potential shading, and the regional climate conditions such as the temperature and irradiance profile. A simple observation of field deployed systems will show that STC conditions (1000 W/m<sup>2</sup>, 25°C) rarely exist. In fact, when the intensity of the sun is at its maximum, module temperatures can exceed 50°C. Alternatively, most of the useful daylight hours have intensities well below 1000 W/m<sup>2</sup>, with the angle of incidence varying over a wide range. These factor depend significantly on the geographic location. These consideration underscore how limited efficiency measurements at STC are at describing the full story.

Measurements of efficiency over a wide range of temperatures and irradiance conditions are needed to provide a more comprehensive evaluation of performance.

The total lifetime cost of the system is also influenced by a wide variety of factors. Here, the cost can be broken down into two aspects; (1) upfront costs and (2) operation and maintenance (O&M). Upfront costs include standard items like the cost of components (*e.g.* modules, racking, inverters) and the cost of labor for installation. There are other factors, particularly for large scale systems, like the cost of capital and interconnection fees that also must be accounted for. Once the system is operational, the ongoing cost are referred to as O&M costs. This refers to regular trimming of vegetation, repair work, and in some cases module cleaning.

Finally, after considering all of these factors, there is still one more critical aspect impacting LCOE. This factor is the lifetime of the system. For PV modules, manufacturers regularly provide warranties up to 25 years. This is often assumed to be the system lifetime, however, this is not necessarily determined from empirical data. This is of great importance. Consider if the lifetime of the system was doubled from 25 to 50 years. This could cut the overall LCOE in half. This has sparked tremendous interest from investors, as the reliability of the system is potentially the most important factor influencing LCOE. Electronic components such as transformers and inverters can be replaced, but a field of several thousand failed modules presents a much larger risk.

Reliability of PV modules has been an active area of study since the first systems were deployed in the 1970's [10, 11]. The only true way to test reliability is to deploy the system and monitor the results. Unfortunately, to verify a 25-year lifetime, one would have to wait 25 years. Although some systems do exist that have been deployed for a considerable amount of time [12],

a method to evaluate new materials and technologies is required. To evaluate module reliability, modules are exposed to environmental stresses at an accelerated rate within a laboratory [13]. A qualification standard has been developed to replicate several real-world stressors within a time frame of only a few months. These accelerated aging tests provide some level of confidence that modules will not fail prematurely in the field, however, these test do not provide quantitative details on the module lifetime. Since these qualification test do not characterize long-term wear out mechanisms, they are unable to quantify the rate of module degradation. Module degradation rates are a critical factor in evaluating how the system will perform over time. Lastly, even if a particular module design is effective in ensuring a long operational lifetime, poor quality management within the manufacturing environment could result in unexpected field failures, undermining the success of the initial module design.

When you go back and consider the dollar per watt assessment, it is evident that this metric is often inadequate in accurately capturing the cost of energy from PV. As manufacturers continue on the downward trend of reducing manufacturing costs, it is essential that the integrity of the module is not compromised. Although new technologies may present themselves as cheaper alternatives based of STC measurements, it may in fact be the long-term performance that determines LCOE. This may, in part, provide an explanation as to why c-Si is the dominant PV technology today. Large scale investment requires confidence on the part of the investor and with the long, successful track record of c-Si modules, it has been difficult for other technologies to compete.

#### 1.3 Motivation

Although photovoltaic solar energy systems have become a viable energy source in many markets, more work is required. Further reductions in cost will accelerate the rate of deployment which would have tremendous implications on the use of energy around the world. Although research work continues in an effort to identify new materials and to develop new cell architectures, c-Si based solar cells are having an impact in today's world. From this perspective, research focused on incremental improvements on existing c-Si technologies would be the most effective route to impact the economics of solar energy in the near term.

This work intends to identify how advanced metrology can be used to improve the economics of PV, focusing on several unique aspects of the cost structure. Within manufacturing, in-line metrology strategies are investigated to establish methods that could improve manufacturing yield and production line efficiencies. To assist research and development teams, spatially resolved cell analysis methods are developed to identify process non-uniformities and quantify their impact on cell performance. Finally, at the module level, a systematic loss analysis is presented that can be used to quantify various aspects of module reliability. In the never ending quest to reduce manufacturing cost and improve device performance, this work aims to provide the PV industry with innovative metrology solutions that can assist in achieving this goal.

#### CHAPTER 2: OVERVIEW OF CRYSTALLINE SILICON PHOTOVOLTAICS

#### 2.1 Photovoltaic Cells

#### 2.1.1 Device Operation

The fundamental operation of a photovoltaic (PV) cell it to convert incident light into usable power. In a semiconductor, photons with an energy greater than or equal to the band gap energy ( $E_g$ ) can be absorbed by an electron, pushing it from valence band to the conduction band. The rate, and depth, at which this absorption occurs is a described by the absorption coefficient ( $\alpha$ ), or alternatively the absorption length ( $L_\alpha$ ), which varies as a function of wavelength. Fundamentally, as the photon energy increases beyond  $E_g$ , electrons deeper within the valence band can be excited, increasing the probability of absorption. This means that shorter wavelengths will be absorbed closer to the surface as compared to longer wavelengths.

Once carriers are generated, these carriers need to be extracted from the device to generate electricity. To achieve this, a *p*-*n* junction is used. This junction generates an internal electric field, sweeping carriers across the junction. Once across the junction, metal contacts are required to extract carriers from the device. On the front side, a metal grid is required to allow for both illumination and conduction.

To increase the amount of carriers generated within the device, it is important to minimize reflection. This is achieved through the use of surface texture and anti-reflective coatings (ARC). Surface texture refers to geometrical structures that increase the probability of reflected light hitting the surface more than once. An ARC is a thin dielectric layer intended to cause destructive interference of the incoming optical wave maximizing light transmission into the device. For standard silicon devices, Silicon Nitride (SiN<sub>x</sub>) is used with a thickness of about

75nm. These two methods reduce reflection considerably when compared to a planar silicon surface.

Because of the indirect band gap of silicon, absorption of photons is weak near the band edge. This requires the use of a relatively thick (~200µm) device in order to ensure maximum absorption. Surface texture has the added advantage of directing light at an angle through the device allowing it to cover more distance before reaching the rear surface. The distance at which light travels through the device is described as the optical path length. The optical path length can be further enhanced by designing a highly reflective back surface to allow light to pass through the cell a second time. An optimal rear reflector would be a Lambertian rear surface where reflected light is randomized, increasing the occurrence of total internal reflection.

Once carriers are generated within the device, they need to make their way to the junction in order to be extracted. Transport to the junction relies on carrier diffusion. One important metric for solar cells is the minority carrier diffusion length ( $L_d$ ). This refers to the average distance a carrier travels before a recombination event occurs. Alternatively, this could be describe in terms of the carrier lifetime ( $\tau$ ), as in the average time it takes for a generated carrier to recombine. The lifetime is defined by Eq. (4) using the excess carrier density ( $\Delta n$ ), also referred to as the injection level, and the total recombination rate (U). The longer the carrier lifetime, or diffusion length, the more likely a carrier will find its way to the junction.

$$\tau = \frac{\Delta n}{U} \tag{4}$$

Minimizing recombination is essential for high quality c-Si devices. Recombination can occur both in the volume of the semiconductor and at the surfaces. There are three main mechanisms for recombination which include radiative recombination, Auger recombination and Shockley Read Hall (SRH) recombination. Because of the indirect band gap in silicon, radiative recombination rates are relatively low. This recombination is critical, however, and will be discussed in subsequent chapters in the context of luminescence imaging.

SRH recombination refers to any defect that creates an energy level within the band gap of the material. Carriers encounter these defects and become "trapped" in this lower energy state. The carrier will stay there until it is thermally excited back into the conduction band or an oppositely charge carrier causes recombination. Here the closer the energy level is to the middle of the band gap, the more detrimental this defect is. A defect with an energy level closer to the band edge will allow the carrier back into the conduction band more easily, reducing the rate of recombination at that site. SRH recombination occurs at any point in which the crystal lattice is disturbed. This can be point defects, dislocations, grain boundaries and surfaces. A large part of c-Si cell device research revolves around eliminating or passivating these defects.

Auger recombination is an inherent mechanism within any semiconductor. Auger recombination relies on the interaction of a third charge carrier. In this case the energy released from the recombination process is transferred to the third carrier. That energy is eventually released back to the lattice through thermal relaxation. This process cannot be avoided and therefore represents the absolute upper limit for carrier lifetimes. This process, which relies on the presence of a third carrier, increases with increasing excess carrier density.

The effective carrier lifetime ( $\tau_{eff}$ ) is a combination of all of these factors and is the focus of many studies in this field. The carrier lifetime can be determined through a number of techniques including photoluminescence, microwave photoconductance and quantum efficiency measurements. The most widely used technique is quasi-steady-state photoconductance measurements [14, 15]. For this technique a wafer, generally with surface passivation, is exposed to illumination and the wafer conductivity, which relates directly to the excess carrier density, is measured. Under steady state conditions the generation of carriers must balance with the recombination of carriers, allowing the use of Eq. (4) to calculate the effective lifetime.

Another way to refer to recombination is to think in terms of dark-saturation currents. This approach relates directly to the current-voltage characteristics of the cell and is described in the following section.

#### 2.1.2 Diode Equations

The basic structure of a solar cell involves the presence of a semiconductor diode created from the interaction between a *p*-type and *n*-type material. This junction creates an in-built electric field and the Current-Voltage (*I-V*) behavior is described using the Shockley's ideal diode equation [16].

$$I = I_0 \left[ exp\left(\frac{v}{v_T}\right) - 1 \right] \tag{5}$$

$$V_T = \frac{kT}{q} \tag{6}$$

Here,  $I_0$  is known as the dark-saturation current and  $V_T$  represents the thermal voltage define in Eq. (6) using the Boltzmann's constant k, the temperature T, and the electron charge q. The magnitude of  $I_0$  under thermal equilibrium is equivalent to the recombination current. This parameter, often represented in terms of current density ( $J_0$ ), is commonly referred to as the recombination parameter [17]. Recombination current in this equation generally refers to SRH recombination. Under illumination, carriers are generated within the device and contribute to the diffusion current of the device. A light generated current component ( $I_L$ ) can then be added to Eq. (5).

$$I = I_L - I_0 \left[ exp\left(\frac{V}{V_T}\right) - 1 \right] \tag{7}$$

This equation represents the ideal equation for a single *p*-*n* junction under illumination. Deviations from this ideal equation are due to the presence of finite series resistance ( $R_s$ ), shunt resistance ( $R_{sh}$ ) and recombination mechanisms other than SRH. Series resistance is introduced as charge carriers are extracted from the device from metal contacts on both the front and rear surface. Shunt resistance represents current flow, or leakage, through alternative paths within the device. These resistive effects are accounted for in Eq. (8).

$$I = I_L - I_0 \exp\left(\frac{V + IR_s}{V_T}\right) + \frac{V + IR_s}{R_{sh}}$$

(8)

To account for non-ideal behavior, it is common to incorporate addition parameters. To account for recombination due to mechanisms other than bulk SRH, a second diode is often incorporated into this device. In this case  $I_{01}$  and  $I_{02}$  represent the saturation current for specific recombination mechanisms. An ideality factor is often incorporated as a method to describe which mechanisms is being accounted for. Standard bulk SRH recombination would have an ideality factor of 1. Other mechanism, such as edge or surface recombination, have been associated with ideality factors up to 2. A two diode model including ideality factors ( $m_1$  and  $m_2$ ) and resistive effects is expressed in Eq. (9).

$$I = I_{L} - I_{01} \left[ exp\left(\frac{V + IR_{s}}{m_{1}V_{T}}\right) - 1 \right] - I_{02} \left[ exp\left(\frac{V + IR_{s}}{m_{2}V_{T}}\right) - 1 \right] + \frac{V + IR_{s}}{R_{sh}}$$

(9)

The ideal diode equation described in this work are useful in understanding how basic device mechanisms, such as resistance and recombination impact device performance. Often these models are fit to experimental data in order to extract relevant device parameters.

#### 2.1.3 I-V Characteristics

Figure 6. Example J-V characteristics representative of conventional c-Si device performance.

Current-Voltage measurements are performed to characterize the performance of the solar cell. As mentioned in the first chapter, the *official* efficiency of a solar cell is determined from illuminated *I-V* measurements using standard test conditions (1000 W/m<sup>2</sup>, 25°C). A typical *I-V* curve is shown in Figure 6. There are several key parameters determined from these *I-V* characteristics including the short circuit current ( $I_{sc}$ ), the open circuit voltage( $V_{oc}$ ), the maximum power point ( $P_{mp}$ ), the current at maximum power ( $I_{mp}$ ) and the voltage at maximum power ( $V_{mp}$ ). Each of these parameters are shown in Figure 6. Current is often normalized for area, defined in term of current density (J), in order to compare devices of different area.

The fill factor (*FF*) is another common metric that describes the "squareness" of the *I-V* curve. The fill factor is influenced largely by non-ideal resistive and recombination affects. Record efficiency c-Si devices have achieved fill factors above 80%. The fill factor is calculated from Eq. (10)

$$FF = \frac{I_{mp}V_{mp}}{I_{sc}V_{oc}} \tag{10}$$

These parameters all relate to the fundamental mechanisms governing device performance. When performance is near ideal, experimentally measured I-V characteristic can be described quite well using the ideal diode equations in the previous section. Deviations are a result of various loss mechanisms. These loss mechanisms are often defined as either optical, resistive, or recombination related. Understanding these various loss mechanism, and being able to quantify them, is critical for improving device performance.

### 2.2 <u>Cell Design</u>

#### 2.2.1 <u>Conventional Cell Designs</u>

# Aluminum Back Surface Field Cell (AI-BSF)

Figure 7. Figure of AI-BSF cell architecture

The most common cell architecture is the Aluminum back surface field (Al-BSF) design.

This design has been the industry standard for several decades. This device, as shown in Figure

7, utilizes *p*-type Silicon, either monocrystalline or multicrystalline, as the base and a thin phosphorus doped *n*-type region as the emitter. SiN<sub>x</sub> behaves both as an ARC and a passivating film for the emitter and is has a thickness of typically 75nm. During metallization, Aluminum is incorporated within the Silicon to form a highly doped  $p^+$  region at the rear surface. This doped region shields majority carriers, in this case holes, from the surface helping to reduce surface recombination in this area and is referred to as the back surface field (BSF). This device typically achieves efficiencies between 16-19% in production. The lower end refers to multicrystalline wafers, with higher efficiencies possible for devices fabricated from monocrystalline wafers.

The conversion of incoming p-type c-Si wafers into AI-BSF cells can be divided into four primary process areas: (1) wet chemical processes; (2) emitter formation (*e.g.* P diffusion); (3) ARC/passivation deposition; and (4) metallization. The process flow for cell manufacturing is depicted in Figure 7. Several wet chemical processes are carried out after wafer production including post-wafering cleaning (*i.e.* saw damage removal) and texturing, and after emitter formation including edge isolation and phosphosilicate glass (PSG) removal. The emitter is typically formed through a high temperature diffusion of phosphorus into the crystal lattice. The SiN<sub>x</sub> ARC/passivation layer is then deposited by plasma-enhanced chemical vapor deposition (PECVD). Finally, contacts are formed through the screen-printing and co-firing process. Typically, Ag is used for the front contact and AI is used as the rear contact. To ensure efficient extraction of photogenerated carriers, metallization must provide good electrical contact with low interfacial recombination velocity between the silicon wafer and metal contacts. Because the Ag paste is printed on top of the SiN<sub>x</sub>, additives are included within the paste to allow the paste to eat through the ARC during firing and make good contact with emitter.

#### As-Cut Wafer

Figure 8. Process Flow for a standard Al-BSF solar cell.

#### 2.2.2 Advanced Cell Designs

To increase the efficiency of c-Si devices a number of techniques have been established. The first and most important consideration is the starting wafer quality. Controlling the number of crystallographic defects, limiting the concentration of metal impurities, and optimizing the background doping densities (*i.e.* wafer resistivity) are critical for establishing high quality devices. Czochralzki (CZ) crystal growth methods have generally been the most cost effective route to produce *p*-type silicon ingots. As an alternative to CZ, multicrystalline ingot growth has been explored as a method to reduce cost while maintaining sufficient quality. Recent efforts have shown that efficiencies of 20.8% can be achieved through improved defect engineering of the starting multicrystalline ingot [18]. Alternatively, there are high cost crystal growth methods, such as float-zone processes that enable extremely pure and very low resistivity wafers. Often, n-type wafers are fabricated from these processes.

After optimizing the wafer quality, the next logical path to efficiency improvements is through reducing the surface, or interface, recombination. The rear surface BSF in conventional cells limits recombination by shielding majority carriers. Because both an electron and hole is required for recombination to take place, limiting the concentration of one carrier reduces the overall recombination rate. Another, more direct, route to reduce surface recombination is through chemical passivation which can actually reduce the concentration of defects at an interface. Many cell designs involve the use of a rear passivating film to reduce recombination at this interface, in turn increasing the *V*<sub>oc</sub> of the cell. The most prominent example is the passivated emitter and rear cell (PERC). Here a dielectric film, typically Aluminum Oxide (Al<sub>2</sub>O<sub>3</sub>), is deposited on the rear surface and local openings are made to allow the conduction to the Al back contact. This device design is shown in Figure 9.

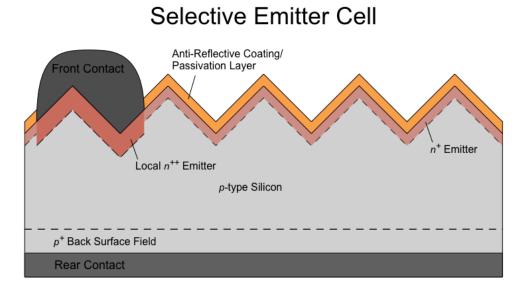

Figure 9. Design for a PERC cell (left) and a selective emitter cell (right).

Another method to reduce recombination is to modify the emitter of the device. Typical emitter design requires a trade off in terms of contact resistivity and SRH recombination, both of which increase with higher doping concentrations. Lower contact resistivity is achieved for metals in contact with a highly doped semiconductor (*i.e.* high conductivity) This higher doping concentration is only required directly under the metal contacts, whereas lower doping densities elsewhere would be beneficial in reducing the recombination. Traditional diffusion processes do not allow for this selectivity, however a wide range of patterning methods have been developed to address this issue. The selective emitter design is shown in Figure 9.

# 2.3 <u>Module Design</u>

## 2.3.1 Manufacturing Process

Photovoltaic (PV) module manufacturing is the process of converting completed solar cells into a single, functional unit that is ready for field deployment. For PV modules based on

standard c-Si solar cells this process can be divided into three primary categories: (1) stringing and tabbing, (2) lamination, and (3) integration of the junction box and bypass diode(s). This module fabrication process has been in use for over three decades and is effective in producing standardized solar panels with sufficient power and durability for use in a variety of applications.

Because the power produced from a single solar cell is relatively small, several cells must be electrically connected together to form a practical PV module. Typical configurations involve the serial connection of cells, with the front contact of one cell connected to the back contact of the adjacent cell. This interconnection process is known as stringing and tabbing. Once the cells are electrically configured, they are encapsulated within a protective package to ensure reliable operation in the outdoor environment. This packaging scheme includes a frontsheet, backsheet, and encapsulant secured together during a lamination step. Finally, a junction box is secured to the backside of the module. The junction box is typically where string interconnections are made, module connector leads are attached, and bypass diodes are incorporated. A cross section of a typical module is shown in Figure 10.

Figure 10. Typical structure of a PV module.

#### 2.3.2 Reliability Concerns

Once a module is deployed, reliability refers to how that module will perform overtime. Although the module fabrication process is simple, there are a number of potential failure modes and degradation mechanisms that could impact the long term performance of the module. These issues are discussed in this section.

Several different failure modes can develop during or as a result of the cell interconnection processes. The failure modes include microcrack formation and cell fracture, solder bond failure, ribbon or interconnect failure, and corrosion. Microcracks, which may lead to cell fracture and increased module series resistance, can develop due to stresses caused by differences in coefficient of thermal expansion or applied pressure from soldering. Methods to avoid cell damage during soldering include using a low yield strength ribbon to allow for expansion during cooling and simultaneous stringing and tabbing reducing the thermal stress induced from the two soldering processes. Increased resistance also results from solder bond failure, which can be a result of poor solderability of the cell metallization, incompatible solder metal alloys, inappropriately sized solder joints, or metal diffusion from the solder. Ribbons can fail as a result of thermally-driven stresses, resulting in increased resistance and current crowding. Corrosion, although driven generally by moisture and other contaminants within the laminate, has also been linked to the laminate conductivity and both negative and positive biases during operation.

A number of metrology techniques including methods for individual component as well entire modules have been used to characterize and predict durability issues during the stringing and tabbing process step. Interconnect degradation can be determined through measurements

of module series resistance, which can be measured using illuminated or dark I-V curves or qualitatively through electroluminescence imaging. Electroluminescence imaging has also been used to identify grid-finger failures, cell fracture, and interconnect failure. Infrared thermography, both steady sate and lock-in, can be used to evaluate hot spots that form due to weak or failed solder bonds resulting in Joule heating of the solder ribbon. Additionally, thermal cycling can be used as a method to stress solder bonds and interconnects, to screen modules for issues related to thermal expansion.

There are also several component level tests that can be used to quantify properties of materials used and determine the quality of solder bonds or interconnects. The peel test can be used to determine the adhesion between the cell interconnect and the silicon substrate. The pull test can be used to determine the maximum stress level before failure. Dynamic mechanical analysis is useful in determining ribbon cycle lifetime. Information about solder bond quality can be obtained through electron microscopy techniques.

Lamination is the process of encapsulating interconnected cells to provide mechanical support, offer protection from environmental stresses, and ensure safe and reliable operation. A typical packaging scheme, or laminate, utilizes a glass front cover, multilayer polymer backsheet, and internal encapsulant such as EVA. Failure of the fundamental functions of the module packaging can lead to safety hazards, degradation of internal components or complete failure of the module. The failure modes for the module packaging itself are discoloration, delamination, mechanical failure, and backsheet degradation. Examples of these failures are shown in Figure 11. The laminate also has a significant influence on degradation mechanisms of the active internal

components including potential induced degradation within the cell and corrosion of the cell interconnects, metallic front or rear contacts, and cell antireflection coatings.

Figure 11. Example of module packaging degradation and failures. (a) browning or discoloration of the encapsulant, (b) delamination of the encapsulant near the busbars, (c) glass breakage and (d) back sheet delamination.