Electronic Theses and Dissertations, 2004-2019

2015

## Post Conversion Correction of Non-Linear Mismatches for Time Interleaved Analog-to-Digital Converters

Charna Parkey University of Central Florida

Part of the Electrical and Electronics Commons

Find similar works at: https://stars.library.ucf.edu/etd

University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### STARS Citation

Parkey, Charna, "Post Conversion Correction of Non-Linear Mismatches for Time Interleaved Analog-to-Digital Converters" (2015). *Electronic Theses and Dissertations, 2004-2019.* 1164. https://stars.library.ucf.edu/etd/1164

### POST CONVERSION CORRECTION OF NON-LINEAR MISMATCHES FOR TIME INTERLEAVED ANALOG-TO-DIGITAL CONVERTERS

by

# CHARNA RAE PARKEY B.S. DeVry University Orlando, 2007 B.S. DeVry University Orlando, 2007 M.S. University of Central Florida, 2010

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida

Orlando, Florida

Spring Term 2015

Major Professor: Wasfy B. Mikhael

© 2015 Charna R. Parkey

#### **ABSTRACT**

Time Interleaved Analog-to-Digital Converters (TI-ADCs) utilize an architecture which enables conversion rates well beyond the capabilities of a single converter while preserving most or all of the other performance characteristics of the converters on which said architecture is based. Most of the approaches discussed here are independent of architecture; some solutions take advantage of specific architectures. Chapter 1 provides the problem formulation and reviews the errors found in ADCs as well as a brief literature review of available TI-ADC error correction solutions. Chapter 2 presents the methods and materials used in implementation as well as extend the state of the art for post conversion correction. Chapter 3 presents the simulation results of this work and Chapter 4 concludes the work. The contribution of this research is three fold: A new behavioral model was developed in Simulink<sup>TM</sup> and MATLAB<sup>TM</sup> to model and test linear and nonlinear mismatch errors emulating the performance data of actual converters. The details of this model are presented as well as the results of cumulant statistical calculations of the mismatch errors which is followed by the detailed explanation and performance evaluation of the extension developed in this research effort. Leading post conversion correction methods are presented and an extension with derivations is presented. It is shown that the data converter subsystem architecture developed is capable of realizing better performance of those currently reported in the literature while having a more efficient implementation.

This dissertation is dedicated to my friends and family, you made sure I had the moral and emotional support I needed. When I shut myself away for days at a time researching, simulating or writing you took turns pulling me back out into the world to have fun. When I let myself get caught up in doing too many things at once you nudged me back into focus. And in particular, to my brother Michael Parkey, you moved me and my stuff around Florida so many times in the last 7 years and only requested one thing, never move to the third floor again. I think I can handle that.

#### **ACKNOWLEDGMENTS**

To Dr. David Chester and Dr. Wasfy B Michael your encouragement, support, wisdom and expertise guiding me through this process as my Co-Advisors was invaluable. Without your help I would have several concussions from beating my head against the proverbial wall.

#### **TABLE OF CONTENTS**

| LIST OF FIGURES                                             | X    |

|-------------------------------------------------------------|------|

| LIST OF TABLES                                              | xii  |

| LIST OF MEDIA/ABBREVIATIONS/NOMENCLATURE/ACRONYMS           | xiii |

| CHAPTER 1: GENERAL INTRODUCTION                             | 1    |

| Problem Formulation                                         | 3    |

| Errors                                                      | 6    |

| Offset                                                      | 7    |

| Gain                                                        | 9    |

| INL                                                         | 9    |

| Aperture Delay and Jitter                                   | 10   |

| Analog Front End and S/H errors                             | 12   |

| Combined Time Interleaved Mismatches                        | 15   |

| Mismatch Correction                                         | 17   |

| CHAPTER 2: METHODS AND MATERIALS                            | 22   |

| Design of the Behavioral Model                              | 23   |

| Error Implementations: Offset, Gain, Quantization, DNL, INL | 25   |

| Aperture Jitter                                             | 31   |

| Cumulant Statistics                                         | 33   |

| Cumulant Equations                       | 34 |

|------------------------------------------|----|

| Cumulants of Error Sources               | 36 |

| Cumulant Adaptation                      | 38 |

| Polynomial Model Implementation          | 40 |

| Post Conversion Correction               | 41 |

| Related work                             | 42 |

| Original Contribution                    | 44 |

| Adaptive Theory                          | 48 |

| Interpolation Implementation             | 50 |

| CHAPTER 3: RESULTS                       | 53 |

| Behavioral Model Characteristics         | 53 |

| Cumulant Statistic Simulations           | 58 |

| Post Conversion Correction Algorithms    | 65 |

| Polynomial Model, Channelized Correction | 66 |

| Behavioral Model, Channelized Correction | 69 |

| CHAPTER 4: CONCLUSIONS                   | 77 |

| APPENDIX A: IEEE COPYRIGHT PERMISSION    | 79 |

| APPENDIX B: MATLAB CODE                  | 82 |

| Simulink <sup>TM</sup> Models            | 83 |

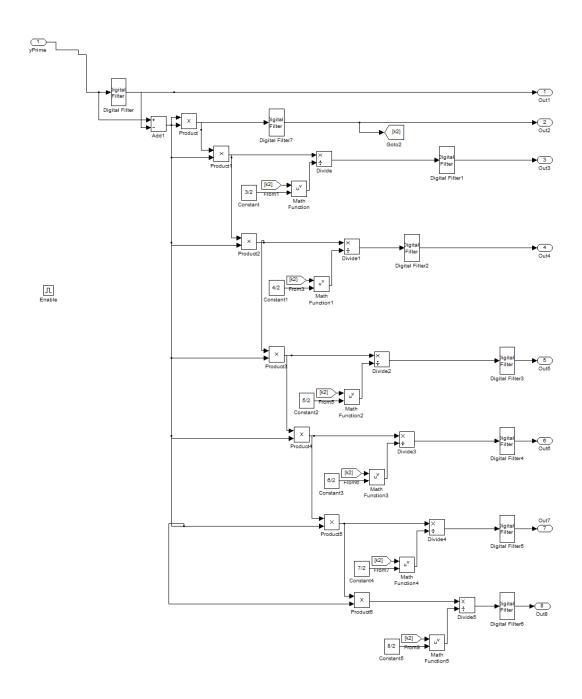

|    | Polynomial Model                        | . 83 |

|----|-----------------------------------------|------|

|    | Behavioral Model single ADC             | . 84 |

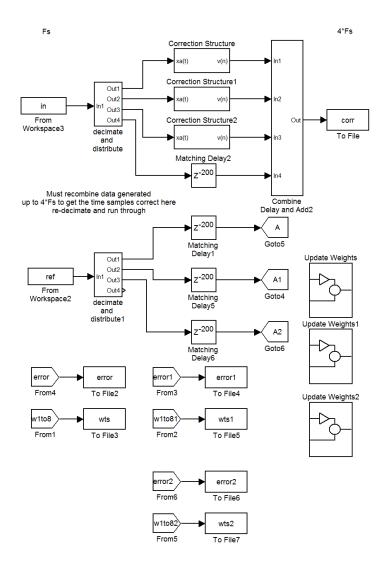

|    | 2 TI-ADC Model with Correction and Test | . 85 |

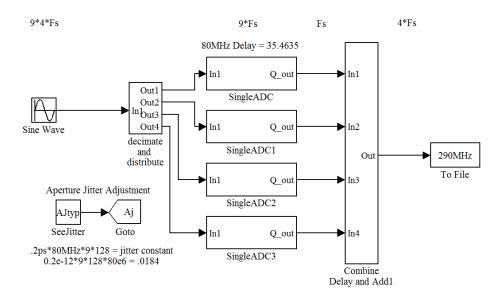

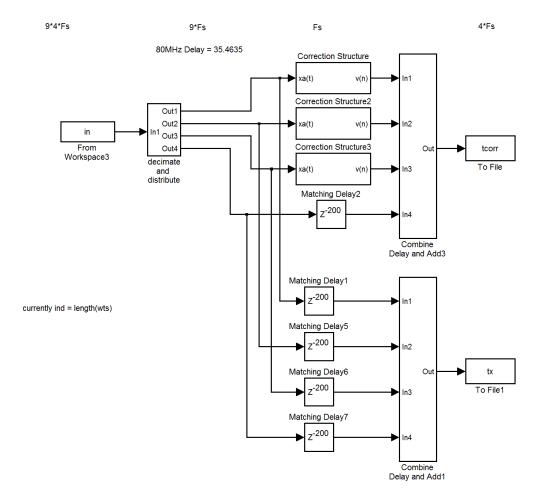

|    | 4 TI-ADC Model with Correction and Test | . 87 |

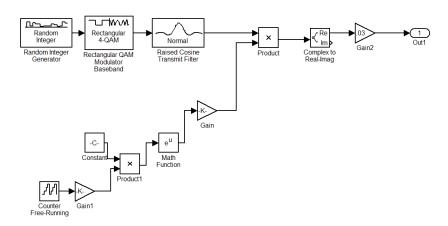

|    | Generate QPSK Input                     | . 90 |

|    | Cumulant Calculation                    | . 91 |

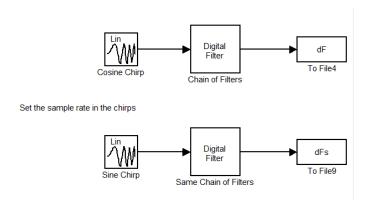

|    | Chirp Response                          | . 92 |

| C  | Sustom Functions                        | . 92 |

|    | CreateINLErrorFirpm                     | . 92 |

|    | gainErr_equi_D_p011                     | . 98 |

|    | LoadHalfBandInterps                     | . 99 |

| IS | T OF REFERENCES                         | 102  |

#### LIST OF FIGURES

| Figure 1: Academic publication trends in TI-ADCs                                                                                                  |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2: General TI-ADC Structure © 2013 IEEE                                                                                                    | 4   |

| Figure 3: Ideal Uniform Quantization © 2013 IEEE                                                                                                  | 6   |

| Figure 4: Stair Case Illustrations of Mismatch Errors © 2013 IEEE                                                                                 | 8   |

| Figure 5: Aperture Delay and Jitter Mismatch © 2013 IEEE                                                                                          |     |

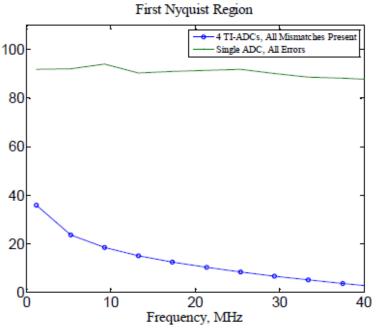

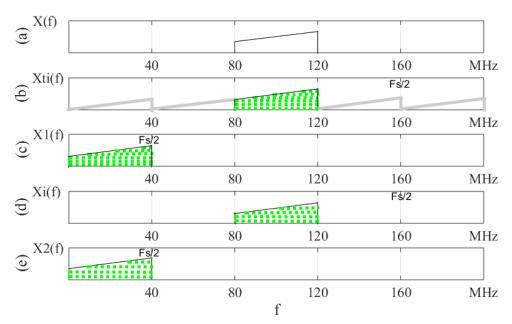

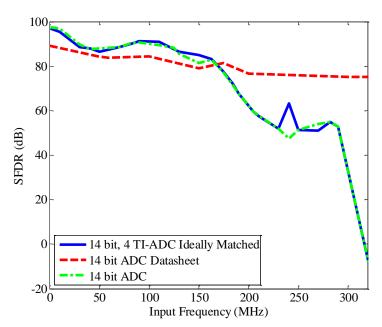

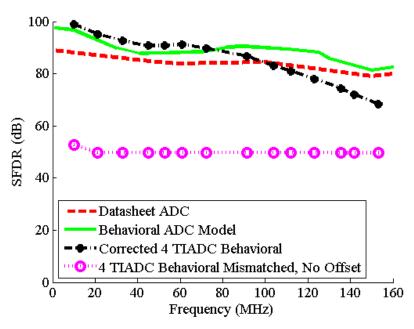

| Figure 6: TI-ADC SFDR vs. Frequency © 2011 IEEE                                                                                                   | 16  |

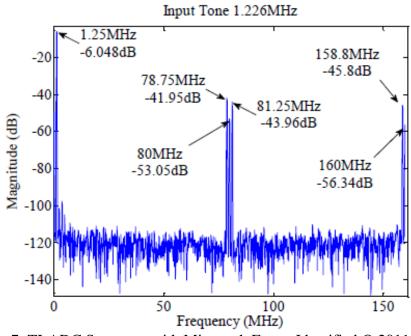

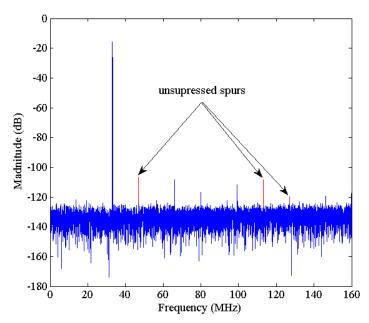

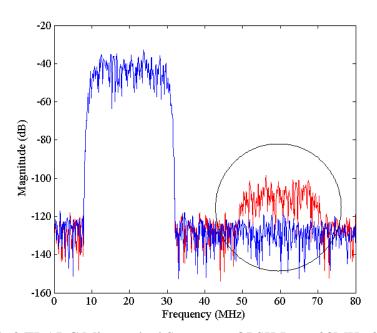

| Figure 7: TI-ADC Spectrum with Mismatch Errors Identified © 2011 IEEE                                                                             |     |

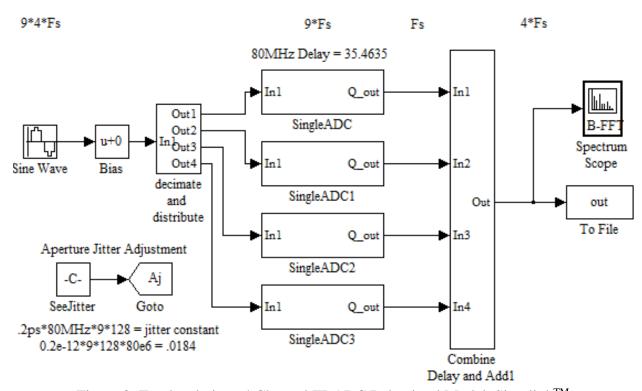

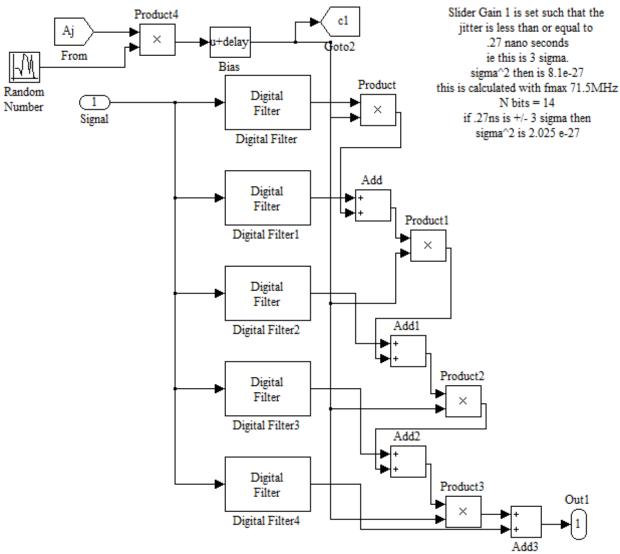

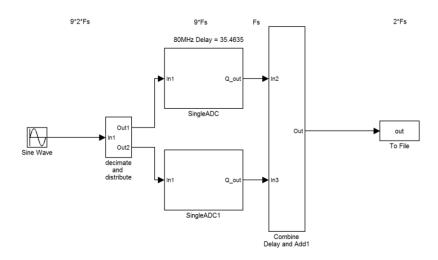

| Figure 8: Top level view, 4 Channel TI-ADC Behavioral Model, Simulink <sup>TM</sup>                                                               | 24  |

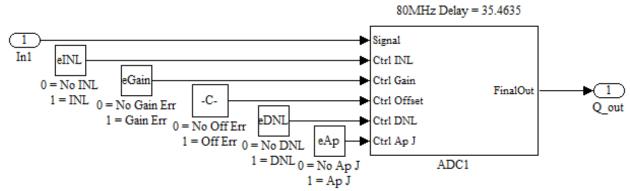

| Figure 9: Single ADC block view, illustration of enabling errors, Simulink <sup>TM</sup>                                                          |     |

| Figure 10: Offset Error Implementation, Simulink <sup>TM</sup>                                                                                    |     |

| Figure 11: Nonlinear Gain Error Implementation, Simulink <sup>TM</sup>                                                                            | 26  |

| Figure 12: Quantization and DNL error implementation, Simulink <sup>TM</sup>                                                                      | 28  |

| Figure 13: INL Error Modeling in Simulink <sup>TM</sup>                                                                                           |     |

| Figure 14: Aperture jitter implementation, Simulink <sup>TM</sup>                                                                                 | 33  |

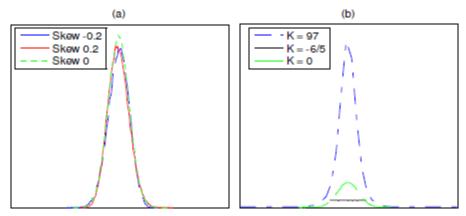

| Figure 15: (a) Skewness and (b) Kurtosis Illustrations © 2012 IEEE                                                                                | 36  |

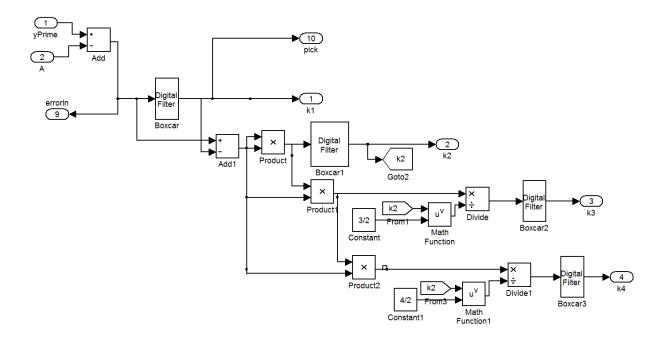

| Figure 16: Boxcar cumulant approximation, Simulink <sup>TM</sup>                                                                                  | 39  |

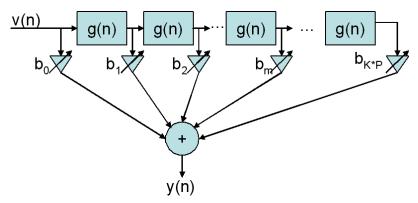

| Figure 17: Polynomial model implementation, Simulink <sup>TM</sup>                                                                                |     |

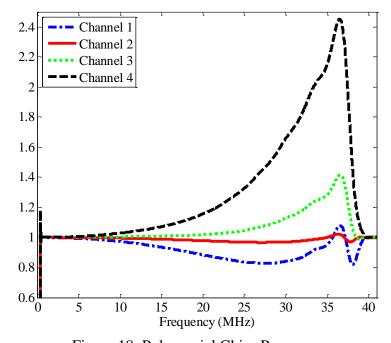

| Figure 18: Polynomial Chirp Responses                                                                                                             |     |

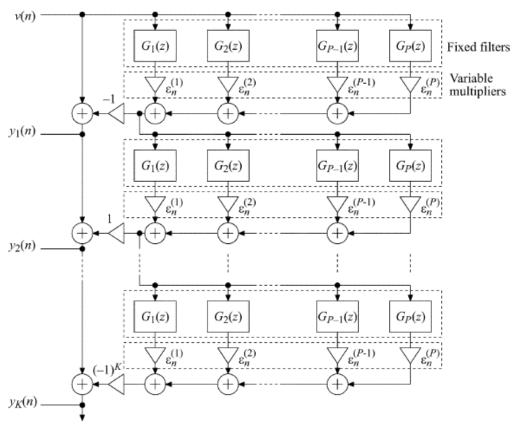

| Figure 19: Nested Compensation Structure, © 2009 IEEE                                                                                             |     |

| Figure 20: Adaptive compensation structure, fixed, filters, adaptive weights                                                                      |     |

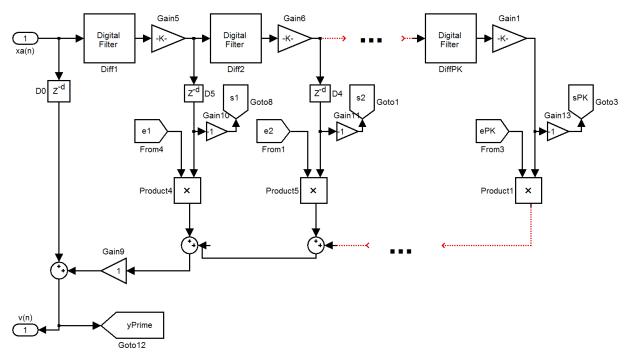

| Figure 21: Compensation Implementation, Simulink <sup>TM</sup>                                                                                    |     |

| Figure 22: 4 TI-ADC Corrected Spectrum, Two Step Sizes, Indicated Spurs from Larger                                                               |     |

| Size                                                                                                                                              | _   |

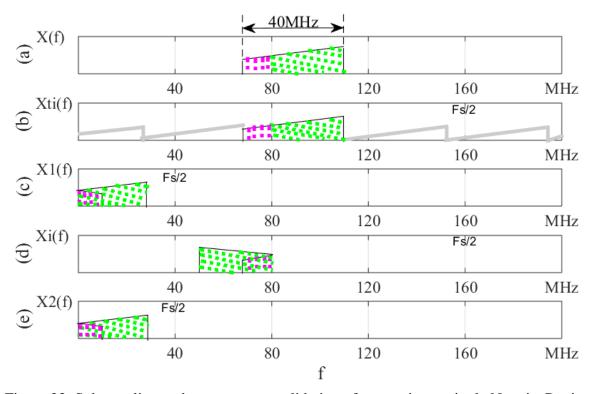

| Figure 23: Subsampling and recovery, consolidation of energy into a single Nyquist Region                                                         |     |

| analog signal spectrum (b) mismatched 4 TI-ADC spectrum (c) channel 1 ADC spectrum                                                                |     |

| interpolated shifted spectrum (e) channel 2 ADC spectrum                                                                                          |     |

| Figure 24: Subsampling and recovery (a) analog signal spectrum (b) mismatched 4 TI-A                                                              | ADC |

| spectrum (c) channel 1 ADC spectrum (d) interpolated shifted spectrum (e) channel 2 A                                                             |     |

| Spectrum                                                                                                                                          |     |

| Figure 25: TI-ADC SFDR vs. Frequency © 2011 IEEE                                                                                                  |     |

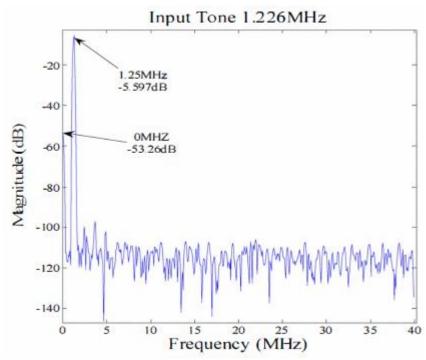

| Figure 26: Single ADC with All Errors Enabled                                                                                                     |     |

| Figure 27: TI-ADC Spectrum with Mismatch Errors Identified © 2011 IEEE                                                                            |     |

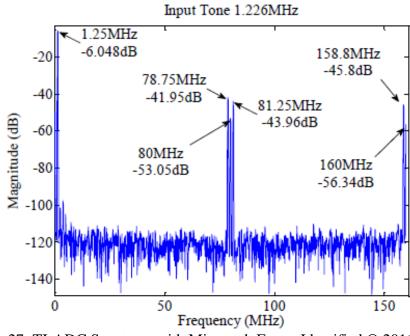

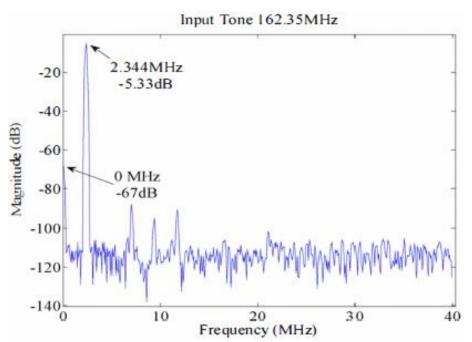

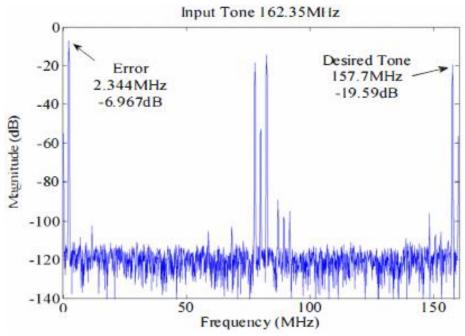

| Figure 28: Single ADC, Fifth Nyquist Tone with All Errors                                                                                         |     |

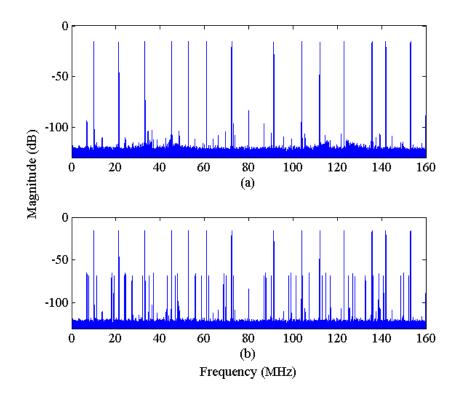

| Figure 29: Second Nyquist Tone, 4 TI-ADC with Uncorrected Mismatch Errors                                                                         |     |

| Figure 30: SFDR of ideally matched 4 TI-ADC system                                                                                                |     |

| Figure 31: 2 TI-ADC Mismatched Spectrum, QPSK Input 20MHz Symbol Rate                                                                             |     |

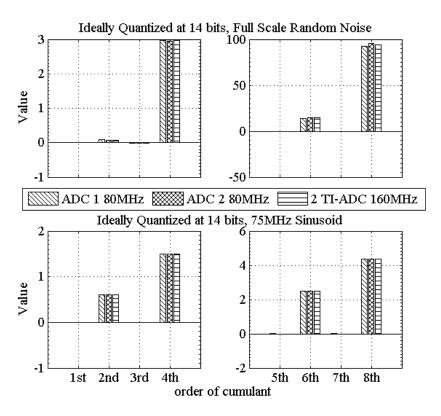

| Figure 32: Input Cumulants                                                                                                                        |     |

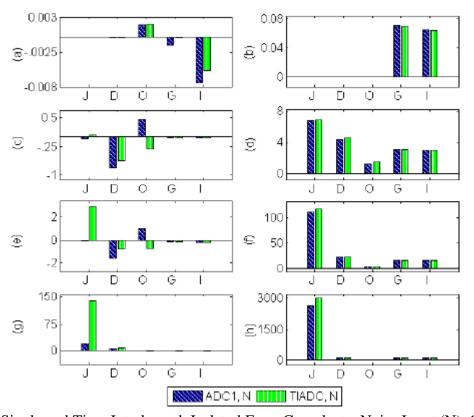

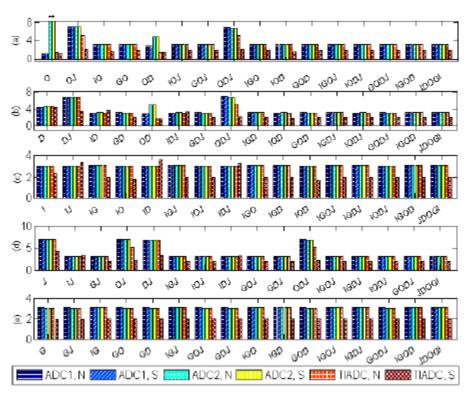

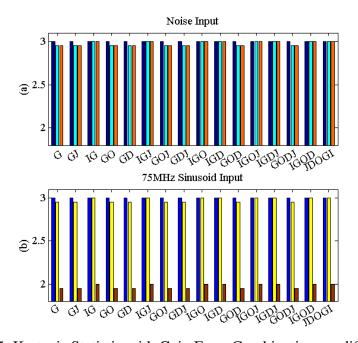

| Figure 33: Single and Time Interleaved, Isolated Error Cumulants, Noise Input (N), Cumu                                                           |     |

| (a) Mean, (b) Variance, (c) Skew, (d) Kurtosis, (e) 5 <sup>th</sup> , (f) 6 <sup>th</sup> , (g) 7 <sup>th</sup> , (h) 8 <sup>th</sup> © 2012 IEEE |     |

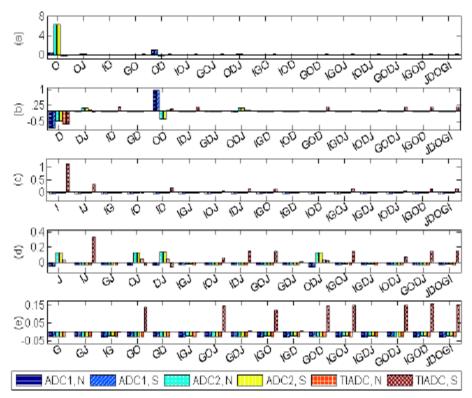

| Figure 34: Fourth Order Cumulants, Error Combinations for Noise (N) and Sinusoidal (S      | ) inputs: |

|--------------------------------------------------------------------------------------------|-----------|

| (a) Offset, (b) DNL, (c) INL, (d) Aperture Jitter, (e) Gain, *bar extends axis, zoomed for |           |

| 2012 IEEE                                                                                  |           |

| Figure 35: Kurtosis Statistic with Gain Error Combinations, a different view               |           |

| Figure 36: Third Order Cumulants, Error Combinations (a) Offset, (b) DNL, (c) INL, (c)     |           |

| (e) Gain © 2012 IEEE                                                                       |           |

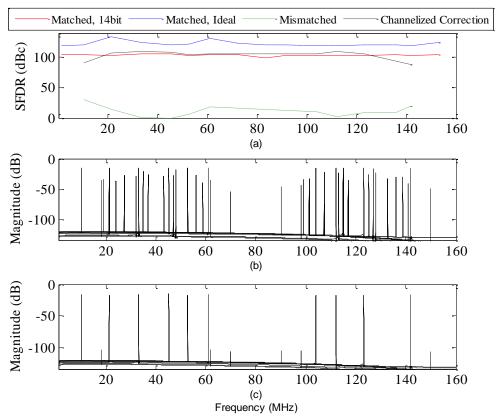

| Figure 37: Polynomial Model a) SFDR for 4 TI-ADC matched, mismatched, char                 |           |

| correction, and interleaved correction. b) 4 TI-ADC multitone input uncorrected c) 4 '     |           |

| multitone input with channelized correction                                                | 67        |

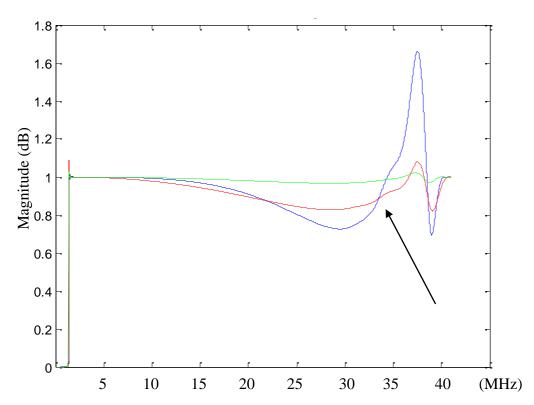

| Figure 38: Chirp response 2 TI-ADC, red ADC 1, green ADC2, blue ADC1 after correct         | ion only  |

| at 33.1MHz                                                                                 | -         |

| Figure 39: SFDR, Ideally Matched Error 4 TI-ADC                                            | 70        |

| Figure 40: Behavioral Model Ideally Matched Error a) 4 TI-ADC multitone inp                | out with  |

| channelized correction b) 4 TI-ADC multitone input uncorrected                             | 71        |

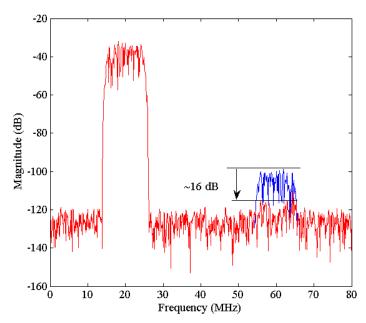

| Figure 41: 2 TI-ADC Input (blue) overlapped with Corrected (red) 4 QPSK spectrum           | 72        |

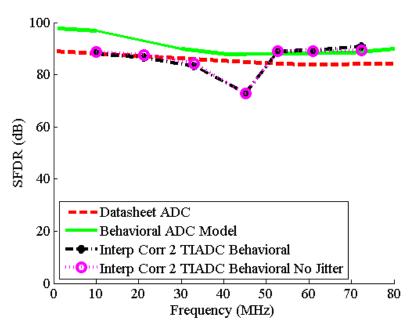

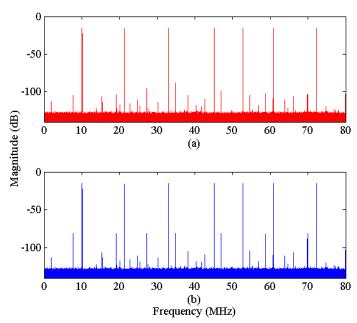

| Figure 42: SFDR, Interpolated Reference 2 TI-ADC                                           | 73        |

| Figure 43: Behavioral Model Interpolated Error a) 2 TI-ADC multitone input with char       | nnelized  |

| correction b) 2 TI-ADC multi-tone input uncorrected                                        | 74        |

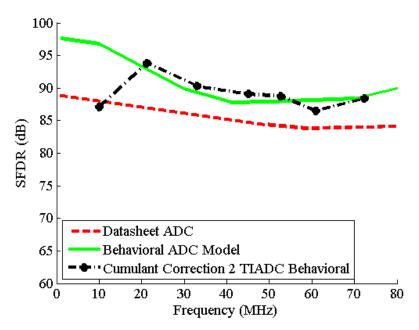

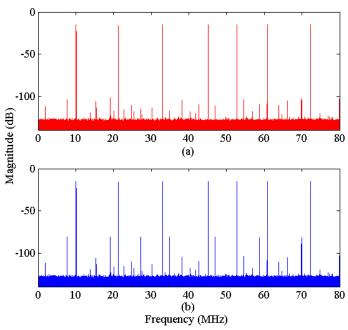

| Figure 44: SFDR, Cumulant Correction 2 TI-ADC                                              | 75        |

| Figure 45: Behavioral Model Cumulant Based Correction 2 TI-ADC multitone input             | (a) with  |

| channelized correction b) uncorrected                                                      |           |

| Figure 46: Partially suppressed QPSK correction based on cumulant statistics               | 76        |

| Figure 47: Polynomial 4 TI-ADC Model                                                       |           |

| Figure 48: Individual Polynomial Channel Model                                             | 84        |

| Figure 49: Single ADC Behavioral Model                                                     | 84        |

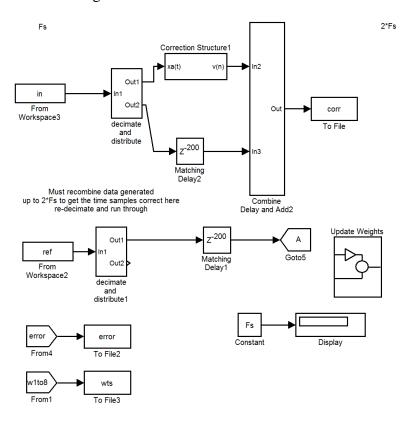

| Figure 50: Behavioral 2 TI-ADC Model                                                       |           |

| Figure 51: Behavioral 2 TI-ADC Correction Model                                            |           |

| Figure 52: Behavioral 2 TI-ADC Weights Test Model                                          |           |

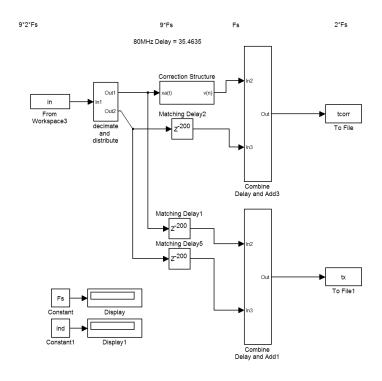

| Figure 53: Behavioral 4 TI-ADC Model                                                       |           |

| Figure 54: Behavioral 4 TI-ADC Correction Model                                            |           |

| Figure 55: Behavioral 4 TI-ADC Weights Test Model                                          | 89        |

| Figure 56: Wideband QPSK Passband Input Model                                              | 90        |

| Figure 57: Cumulant Calculation Model                                                      |           |

| Figure 58: Generic Single Rate Chirp Response Model                                        | 92        |

#### LIST OF TABLES

| Table 1: Categories of Mismatch Correction Methods                             | . 19 |

|--------------------------------------------------------------------------------|------|

| Table 2: Select Fabricated TI-ADCs                                             |      |

| Table 3: MAX 12554 Datasheet Characteristics and Parameters                    | 24   |

| Table 4: 3 <sup>rd</sup> and 4 <sup>th</sup> Cumulants of Common Distributions |      |

| Table 5: Input Cumulant Estimation Lengths                                     |      |

#### LIST OF MEDIA/ABBREVIATIONS/NOMENCLATURE/ACRONYMS

**Acronym** Description

ADC Analog-to-Digital Converter

bkgd background

BLMS block least mean squared

BW bandwidth

cal calibration

CIC cascade integrator-comb

CMOS complementary metal-oxide-semiconductor

COTS commercial off the shelf

DAC Digital to Analog Converter

dB decibels

DNL differential non-linearity

ENOB effective number of bits

FIR finite impulse response

Freq frequency

FS full scale

Fs sampling rate

Gsps giga samples per second

HOCS higher order cyclostationary statistics

HOS higher order statistics

Hz Hertz

I/O Inputs/Outputs

IEEE Institute of Electrical and Electronics Engineers

IF intermediate frequency

INL integral non-linearity

LMS least mean squared

LSB least significant bit

MHz mega hertz

mW milli Watt

NLMS normalized least mean squared

NRE non-recurring engineering

OBALMS optimum bock adaptive least mean squared

PM phase modulation

ps pico second

RMS root mean square

S/H sample and hold

SAR successive approximation

SFDR spurious free dynamic range

SNDR signal to noise and distortion ratio

sps samples per second

SWaP size, weight, and power

T/H track and hold

TI-ADC Time Interleaved Analog to Digital Converter

Typ typical

UWB ultra wide band

V Volt

VDF variable digital filter

#### **CHAPTER 1: GENERAL INTRODUCTION**

Time interleaved analog-to-digital converters (TI-ADCs) are made up of multiple ADCs, also known as sub-ADCs, which sample the input signal in a round robin fashion to increase the sample rate of the system [1]. An ideal TI-ADC increases the overall sample rate by *M* times while preserving the critical performance characteristics, where *M* is the number of converters interleaved. In practice periodic time varying mismatches are introduced through device differences that exacerbate the single device's linear, nonlinear and timing errors and distortion. In addition to the errors introduced strictly due to interleaving the sub-ADCs, the analog front end including the sample and hold(s) that may be required to support the sampling operation add additional nonlinear errors. The first step in matching the ADCs is during device selection, by picking closely matched devices from a large inventory. However since the devices cannot be fully matched to near required accuracies largely due to semiconductor process variations the use of post conversion correction is needed.

The first paper written on TI-ADCs was by Black and Hodges [1], published in 1980. Though the technology is not a new concept, the evolution of semiconductor technology to enable the concepts to be practically implemented has resulted in a recent expansion of interest in TI-ADCs that has produced over 30 US Patents awarded in the last 5 years. Current and emerging applications benefiting from TI-ADCs include instrumentation, ultra wide band (UWB) communications [2], high-bandwidth I/Os requiring sampling rates of 10 to 25GHz, 70GHz radar systems [2], etc. Direct conversion techniques for Radar and communications [3-7], measurement systems [8,9], and photonic sampling systems [10] have been addressed in the past

year with TI-ADCs using a variety of device architectures such as pipeline, Flash, successive approximation (SAR), optical and photonic ADCs.

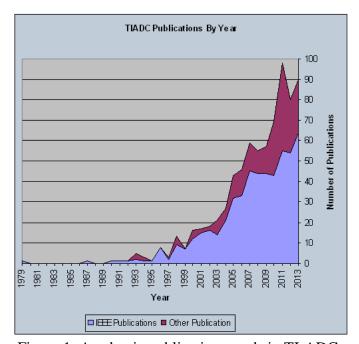

In 2014 there were 37 of 62 articles reporting TI-ADC hardware level simulations and fabrication developments in the Institute of Electrical and Electronics Engineers (IEEE) proceedings and journals, Figure 1 shows the increasing trend of reported developments for all academic pursuits of TI-ADCs including theory, mismatch correction research, tutorials, supportive circuitry, applications, and hardware.

Figure 1: Academic publication trends in TI-ADCs

Taking advantage of TI-ADCs requires a basic understanding of the hardware, errors, layout, application, and correction algorithms used to maximize the performance of the system. A basic knowledge of the uniform sampling analog-to-digital conversion process is assumed; this

understanding is extended with the basic concepts of TI-ADC technology and its recent developments.

The following subsections discuss the general structure of a TI-ADC and the use cases that the application of TI-ADCs were intended to address. The errors sources present in the analog front end, individual and time interleaved converters are then discussed before introducing current mismatch correction methods.

#### **Problem Formulation**

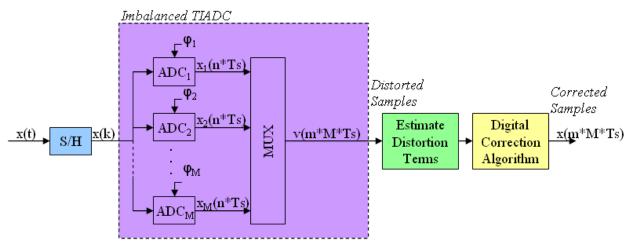

The bottleneck in most cutting edge signal processing based technologies is the barrier between the analog and discrete time amplitude domains: the data converter and specifically the more performance limited is the ADC on the receive side. The limiting factor in most use cases is the performance characteristics as a function of either the input frequency or sampling rate. The motivation of TI-ADCs is to cost effectively increase the sample rate of a converter by M times while maintaining the level of performance at or near that of a single constituent. The top level architecture of an M ADC, TI-ADC is illustrated in the signal block diagram in Figure 2. In the figure, x(t) is the analog input signal; the sample and hold (S/H) block may contain a single S/H [11], an individual S/H for each sub-ADC [2], or a number of S/Hs for groups of sub-ADCs [12] with an output of x(k), followed by sub-ADCs for digitization. In the instantiation case where a single S/H feeds all M sub ADCs the bandwidth of the S/H must support an input bandwidth which is greater than or equal to M \* Fs/2 where Fs is the sample rate of the sub ADCs. In the instantiation case where each of M/K S/Hs feed K sub ADCs the bandwidth of the S/Hs must support an input bandwidth which is greater than or equal to K \* Fs/2 fed by a single S/H with

an M\*Fs/2 bandwidth or each of the M/K S/Hs must have a M\*Fs/2 bandwidth. Each of the sub-ADCs is clocked with an appropriately phase shifted clock divided to trigger the round robin sampling of each ADC. The samples are then multiplexed and the output v(m) is the composite sampled signal at the M\*Fs rate affected by the cyclic mismatches and nonlinearities in the ADCs and the analog front end. The estimation and compensation blocks correct the samples v(m) at the M\*Fs rate and will be discussed later.

Figure 2: General TI-ADC Structure © 2013 IEEE

Power, area, performance, and cost are the variables that are balanced in any given sampling application. Computational complexity of the estimation and mismatch correction is a concern for TI-ADCs in both single device semiconductor and multiple device application specific implementations independent of the difference in non-recurring engineering (NRE) versus recurring engineering cost trade models. In the latter product space upfront matching of the converters increases the initial test time but reduces the computational power needed for correction. However even in single die instantiations of the converters the devices cannot be exactly matched and the use of analog circuitry and/or post conversion correction can only

compensate for the mismatch errors to a certain, usually inadequate, level. Additionally, analog domain calibration circuits are area consuming and digital correction algorithms are preferred in most cases for this reason and additionally for the level of compensation that they can provide. Digital correction also better lends itself to off the shelf implementations due to their adaptability and stability over time and temperature.

As previously mentioned, the differences in devices translate into what is called *M*-periodic error mismatch or simply *M*-periodic mismatches. Periodic mismatches deteriorate the performance of the composite converter structure reducing the effective performance. This problem can be addressed to some level, either online or offline in hardware or software. The purpose of this compensation is not to correct the errors of the individual ADCs, only to compensate for differences between them. Thus the ideal case is not an ideal converter but a multi-channel converter wherein all of the channels have identical transfer functions and have sample intervals which are as uniform as a single device sampling interval. In other words the goal of the compensation circuit is to make the time interleaved multiple channel data converter perform as closely to ideal sampling as illustrated in Figure 3 for a uniform staircase as one of its channels sampling at 1/M the rate and ignoring clock jitter considerations (described below).

Figure 3: Ideal Uniform Quantization © 2013 IEEE

#### **Errors**

Ideally the TI-ADC system is uniformly sampled to within the required accuracy with non-periodic errors. Note two key concepts that can cause confusion: 1) quantization error is not caused by non-ideal behavior as a result of the hardware instantiation but is inherent in the quantization process, and 2) compensation in a TI-ADC is not attempting to change the transfer function of any single converter to be closer to the ideal but is meant to match the transfer functions of the multiple devices.

While non-uniform sampling is not considered in this dissertation, it is worth pointing out the generalized Nyquist sampling theory allows for non-uniform sampling and reconstruction. For a recent reference on the application of non-uniform sampling in TI-ADCs see [13]. However, non-uniform sampled signal processing is very computationally intensive. A compromise is to

generate uniform samples from the non-uniform samples. This is computationally within the realm of feasibility given *a priori* knowledge of the temporal offset of each sample. In most practical applications acquisition of said offset information is more limiting than the correction itself. In consideration of these facts the reader is once again reminded that the goal of post conversion correction algorithms is not to make the individual ADC performance better but to correct mismatches to make the TI-ADC performance approximate the single ADC performance characteristics while increasing the sample rate by correcting the periodic errors.

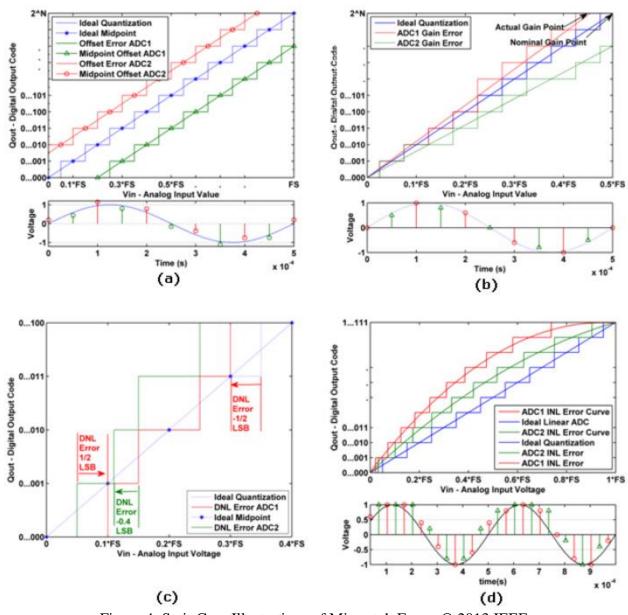

The following reviews the non-quantization errors of a typical ADC that is relevant to TI-ADCs and their impact on interleaved performance; the figures in each subsection visually exaggerate the magnitude of the errors so that the reader can see the impact. When realistic error levels are used they are difficult if not impossible to see in the time domain waveform with the naked eye. Actual performance is the aggregated effects of all of the errors and the aggregated effects differ device to device. By convention, first the error sources of a single ADC are described. Then how the effects are exacerbated in a 2 channel TI-ADC, Figure 4 shows the blue lines as the ideal reference ADC and the red and green lines as the two non-ideal ADCs to be interleaved. Subsequent subsections refer back to this figure in detail.

#### Offset

The offset error in a single converter with a bipolar input capability is the midstep value when the digital output is zero. For a TI-ADC this error is M periodic if left uncorrected as seen in Figure 4a where the sample points are the TI-ADC samples of the sinusoid. In a single converter the error affects all codes by the same amount so this is a static periodic error. In the frequency

domain, the periodic error shows up as spurs at multiples of the sub ADC sample rate *Fs*. Offset mismatch is a well understood problem with available simple solutions in the public domain, for example the use of a sinusoid to determine the value to subtract in the time domain samples of sub-ADC outputs compared to a reference channel.

Figure 4: Stair Case Illustrations of Mismatch Errors © 2013 IEEE

#### Gain

Gain error for a single ADC is the difference between the nominal and actual gain points on the transfer function after the offset error has been corrected to zero. The error results in a difference in slope of the actual and ideal transfer function as seen in Figure 4b. This error, if large enough can cause missing codes as can be seen in the actual ADC staircase approximation. The mismatch effect in an interleaved system is again periodic for this static gain error, and the frequency domain spurs for a single sinusoid are located at the input frequency plus and minus multiples of the sampling rate,  $\pm f_i + k * Fs$  where  $k = \{0,1,...M-1\}$ . This static mismatch is also well known and has been addressed with a single gain correction parameter multiplying the output of the non-reference channel ADCs. It is the case in implementation however that this gain error is not uniform across frequency and may not be completely matched across the entire frequency range with a single correction parameter. This nonlinear mismatch as well as the nonlinearities to be discussed later are highly dependent on manufacturing process and thus relevant information is often held as proprietary and is not well documented in the open literature. This results in its correction being a current challenge in TI-ADC research.

#### INL

The difference between the ideal and measured code transition levels after correcting for static offset and gain is called integral nonlinearity (INL). This is a nonlinear error that originates from various sources but typically results from semiconductor process  $f_T^1$  limits which is also process

<sup>&</sup>lt;sup>1</sup> f<sub>T</sub> is the convention for describing the bandwidth of a semiconductor process and is formally defined as the frequency at which the maximum gain of a transistor implemented in that processes is unity.

bandwidth limitations. INL is shown graphically in Figure 4d and it has an unpredictable impact on the interleaved output. Manufacturers specify the effects of INL in a few different ways; the most descriptive plots related to INL show the spurious free dynamic range (SFDR) of the converter as a function of frequency. This particular parameterization is useful in sub sampling applications that tend to exploit the full input bandwidth of the ADCs analog front end but not its logic circuitry. Again, this periodic nonlinear mismatch is unpredictable in its combination across frequency but can be characterized via measurement.

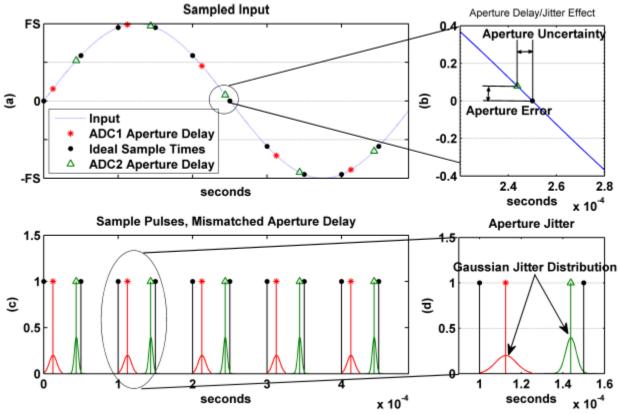

#### Aperture Delay and Jitter

A limiting factor in high speed applications, especially in subsampling, is the uncertainty of the sampling aperture. Aperture jitter is the source of error in the temporal dimension of the error "fuzz ball" around each converted sample. (The other dimension being the dimension of the quantity being measured, e.g. voltage.) The aperture is the time window of deviation from the ideal sampling instant. This causes a deviation from ideal equal samples of the measurement of the input to the ADC and therefore affects the output. Any deviation from ideal uniform spacing manifests itself as a frequency dependent amplitude error. Individual ADCs have an overall aperture delay which is static and results from a fixed sampling clock propagation delay. As this is a fixed delay it is a measurable fixed delay in the output. However when interleaving this delay is no longer constant but periodic as seen in Figure 5 and is one aspect of the timing mismatch when interleaved. At any given tonal frequency it is a periodic phase modulation with phase increasing linearly with frequency. In the figure the black sample points and times indicate

the ideal sample location and the green triangles and red circles indicate the extremes of where the sample might be taken in time for each sample.

Error compensation for aperture delay mismatch has been well researched and the four methods often used to correct this Skew are interpolation, blind compensation, fractional delay filters and the perfect reconstruction method, more discussion of these methods can be found in [14] and its references. As inferred above, constant time offset looks like a phase dependent amplitude error a.k.a. a fixed phase offset.

Aperture jitter or aperture uncertainty is generally specified as the standard deviation of the sampling time, also called timing jitter and timing phase noise. This standard deviation defines a Gaussian distributed random process which defines one limitation of the maximum frequency of the input. Figure 5 illustrates both periodic delay and jitter. Though the sample times are shown in Figure 5a as periodic delays, Figure 5c shows the distribution of the sample time that could actually occur. This jitter impacts estimation and correction of the mismatch.

Figure 5: Aperture Delay and Jitter Mismatch © 2013 IEEE

#### Analog Front End and S/H errors

Some architectures require the use of a S/H for each sub-ADC which can introduce bandwidth mismatches and nonlinear mismatch errors when interleaving due to the nonlinear behavior inherent in S/H circuits. Today most S/Hs are integrated into the ADC however it is important to understand the operation of the S/H as it contributes to the dynamic performance of the ADC and the mismatch errors encountered in TI-ADCs. S/Hs may also need to be used as additional discrete components in the time interleaving circuit to allow for the desired higher BW of interleaved sampling rate.

ADCs use comparators or capacitors to convert an analog input to a discrete value, continuous variations in the input cause errors in the conversion. The S/H is used to eliminate these variations by maintaining the input to the ADC at a constant value during conversion. A simplistic S/H can be realized as a switch and a capacitor. When the switch closes current flows, charging the capacitor this is the sample stage. The charging time constant is proportional to the input impedance and the capacitance. When the switch opens the capacitor discharges over a period proportionate to the output impedance and the capacitance this is the hold stage. When the input impedance is zero and the output is infinity the S/H performs ideally with the input being sampled very quickly and held for infinity. This is impossible however, and implementation requires tradeoffs.

If the capacitor is large, switching errors are minimized with a stable hold period but the performance of the circuit is not ideal and a smaller capacitor is needed for fast sampling. This is because the capacitor charging time depends on the time constant set by the size of the capacitance and on the resistance of the switch. Any resistive load on the output will cause an error in the voltage held by discharging the capacitor when the switch is opened, when this error is greater than ½ LSB before the conversion is complete, the problem needs to be addressed. Operational amplifiers are used to mitigate this problem.

The simplest implementation structure is made up of an input buffer amplifier, the switch and capacitor and an output buffer. Others structure exist with various benefits and drawbacks, but the specifications that describe S/H operation in its four states, sample mode, sample to hold transition, hold mode and hold to sample transition are the same. During sampling the static

specifications of concern are offset, gain error and nonlinearity and the dynamic specifications are settling time, bandwidth, slew rate, distortion and noise. The transition from sample to hold specifies the pedestal, and pedestal nonlinearity static behavior and aperture delay time, aperture jitter, switching transient, and settling time dynamic behavior. During the hold period static behavior of concern includes droop, and dielectric absorption; feedthrough, distortion, and noise as the dynamic. Finally the hold to sample transition specifies the dynamic performance of acquisition time, and switching transient.

The dielectric absorption is of particular concern because of the memory effect introduced that allows the previous sample to contaminate a new one, introducing random errors. This memory effect and other nonlinear effects introduced by the S/H forces compensation in the form a Volterra series filter. The Volterra series inverts the nonlinearity with a nonlinear series with memory. Satarzadeh, Levy and Hurst show in their 2009 paper that modeling of this nonlinearity can be achieved with a Volterra series expansion and compensation can be achieved at the cost of oversampling and linear filters cascaded with digital mixers [15].

It is possible to implement a time-interleaved system with individual S/Hs per interleaved ADC; however an additional level of mismatch is introduced through the unique parameters inherent in each S/H mentioned above, particularly offset, gain, nonlinearity, bandwidth, aperture delay and jitter. While the aperture delay of a single S/H is not an error, differences in delay introduce a periodic mismatch delay. However the use of two stages of S/H where the first stage is a single S/H that sets the sampling instant and the second stage of interleaved S/Hs does not contribute to time Skew interleaving errors is possible [11].

#### Combined Time Interleaved Mismatches

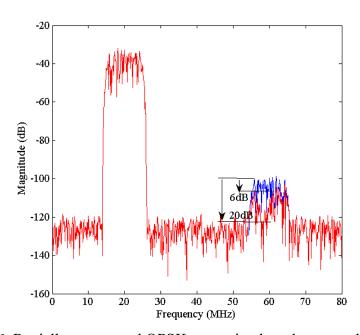

Taking the example of four time interleaved ADCs in this subsection, the components are independent parts driven by the same clock source with their own specific internal and external characteristics such as clock delay due to layout and manufacturing variances. When individually analyzing each error and their mismatch, the frequency domain characteristics measured and the contributing mismatches can be at least partially identified. However this is more difficult in the interleaved case. The time variant spectral characteristics resulting from mismatch errors with unknown aggregation features can combine to create greater or lesser harmonics due to the relative differences between individual ADC transfer functions. Examples of the combined mismatch errors are shown in Figure 6 and Figure 7. The behavioral model that is detailed in chapter 2 was developed as a part of this research and previously published in [16, 17] was used to simulate the interleaved system with errors specified in the extreme to extreme range of a high performance ADC data sheet [18].

The linear distortions might be approached with the use of M FIR polyphase filters in each of M lower rate channels or an M periodic FIR filter at the higher interleaved rate whose filter coefficient are periodic. However these schemes do not address the nonlinear errors from the gain, DNL, INL and S/H(s) in the system. There is very little published work in this area, and the few that have addressed the topic suggest varying methods of compensation, one such method is the Volterra series based nonlinear polyphase filter [19, 20].

Figure 6: TI-ADC SFDR vs. Frequency © 2011 IEEE

Figure 7: TI-ADC Spectrum with Mismatch Errors Identified © 2011 IEEE

#### Mismatch Correction

As stated above, the goal of post conversion correction algorithms is not to make the individual ADC performance better but to correct mismatches to make the TI-ADC performance approximate the single ADC performance characteristics by eliminating the periodic errors resulting from device and physical implementation mismatch. One method is to utilize one channel as a reference while all other channels are compensated to match the reference by producing the inverse of the differences of the responses. This is a realizable compromise to the theoretical ideal of taking the inverse of each channel with respect to the ideal sampling response. If the ideal of perfect compensation were physically realizably then there would be no need to interleave ADCs let alone use post conversion correction to match their performance.

There are two main categories of correction methods: online and offline, which can be done in the foreground or background, with active or passive correction. Here we use the term online to mean that the TI-ADC is in use while the correction is being made i.e. a post conversion correction in real time. Offline is either hardware based, where characterized converters are matched to each other, or static correction methods that do not take into account time-varying characteristics of the transfer function and their impact on ADC performance. Online methods allow for periodic or continuous updating of the mismatch compensation.

Foreground methods require the periodic or event triggered interruption of the normal operation of the subsystem so that a known input sequence can be applied and compared to the expected output, that is the application of a data driven adaptive correction methodology. This methodology is most viable when the host system has an *a priori* need for known sequences as is

found for example in communications systems requiring a known header, frame sync, etc. appended to an incoming message. Background techniques allow for the continued normal operation of subsystems, including a TI-ADC.

The described methodologies can be used in various combinations. For example, in either foreground or background techniques, active or passive methods may be used. Active implies the use of a known injected signal, while passive assumes the method is blind or semi blind (where nothing or very little about the incoming signal is known *a priori*) utilizing the unknown signal for correction. Background methods are limited in the measurement and correction of errors to a typically out of band frequency range that is excited by the unknown signal or by having an extremely low level in band signal. Additionally, background methods typically require fast adaptation or correlation based error detection to make them beneficial Table 1 summarizes the section by listing advantages and disadvantages to the mismatch correction methods; this table is not exhaustive but rather gives examples of each type of method discussed.

Table 1: Categories of Mismatch Correction Methods

|            | Online | Offline |                       | Correction Methods      | Disadvantages          |

|------------|--------|---------|-----------------------|-------------------------|------------------------|

|            | Online | Offfine | Example               | Advantages              | Disadvantages          |

| Active,    | X      |         | Providing a           | Could allow for more    | Requires interruption  |

| Foreground |        |         | calibration mode that | accurate correction of  | of the system and      |

|            |        |         | is activated through  | mismatches with the     | does not               |

|            |        |         | software in the field | use of a clean test     | automatically correct  |

|            |        |         | such as with          | signal over the desired | for long term varying  |

|            |        |         | instrumentation.      | frequency range         | errors such as         |

|            |        |         |                       | 1 1 1 3                 | temperature            |

| Active,    | X      |         | Injecting a tone in a | Allows for short term   | Limited to correcting  |

| Background |        |         | known vacant area of  | and long term           | the errors present or  |

|            |        |         | the spectrum.         | adaptation to errors.   | measurable at the      |

|            |        |         |                       | Can take advantage of   | tone frequency of      |

|            |        |         |                       | existing architectures  | interest               |

| Active,    |        | X       | In the production and | One time correction,    | Requires hands on      |

| Foreground |        |         | or system testing     | allows for reduction in | individual testing of  |

|            |        |         | phase a chirp is used | computational           | each system. Does      |

|            |        |         | to determine TI-      | complexity due to       | not adapt over time to |

|            |        |         | ADC system            | relative simplicity of  | error changes          |

|            |        |         | response.             | static correction       |                        |

| Passive,   | X      |         | A Software Defined    | A known signal is       | Overhead to the        |

| Foreground |        |         | Radio will be         | available, which could  | message is required,   |

|            |        |         | receiving frame       | allow for faster or     | if adaptation is not   |

|            |        |         | syncs in front of     | better error reduction. | able to finish with    |

|            |        |         | each message. These   |                         | one message            |

|            |        |         | are used to adapt the |                         | performance can be     |

|            |        |         | correction.           |                         | temporarily reduced.   |

| Passive,   | X      |         | An adaptive blind     | No additional signal    | Computational          |

| Background |        |         | method is used to     | required, allows for    | complexity may be      |

|            |        |         | adapt a polyphase     | short and long term     | high, an additional    |

|            |        |         | filter bank to reduce | adaptation to errors.   | FPGA will be needed    |

|            |        |         | frequency response    |                         | to perform the         |

|            |        |         | mismatch.             |                         | correction.            |

| Passive,   |        | X       | Utilizing in house    | Requires no additional  | Does not take          |

| Foreground |        |         | testing of the ADCs   | computational           | advantage of           |

|            |        |         | closely match the     | complexity              | correction structures  |

|            |        |         | responses of the      |                         | and performance will   |

|            |        |         | hardware.             |                         | suffer. Does not       |

|            |        |         |                       |                         | adapt to changes over  |

|            |        |         |                       |                         | time.                  |

© 2013 IEEE

The performance improvement limitation of any method used to correct mismatch errors in TI-ADCs is the performance of the individual ADCs, S/H(s), the clock characteristics, and the uniformity of the layout used in the implementation of the subsystem. We seek to improve the performance of the interleaved data converter subsystem, dominated herein by its SFDR, to that

of a single constituent ADC while increasing the sample rate. Other limitations may include channel limitations due to size, weight, and power (SWaP) requirements, noise, clock stability etc. Clock stability is the ultimate limiter of sampling accuracy in any data conversion operation due to limitations imposed by aperture jitter.

To better illustrate some of the research ongoing in TI-ADCs, Table 2 details a subset of the latest publications on implemented TI-ADCs spanning 2 to 128 channels and up to 6 sub-ADC architectures. Exclusively simulation results are not included in this table.

Table 2: Select Fabricated TI-ADCs

| Table 2: Select Fabricated TI-ADCs           Reference         [38]         [34]         [33]         [37]         [39]         [35] |                                                                                                  |                                                                                                             |                                                                                          | [35]                                                | [36]                                                   |                                                                                                   |                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Reference [56] [54]                                                                                                                  |                                                                                                  | [33]                                                                                                        | [37]                                                                                     | [37]                                                | [33]                                                   | [50]                                                                                              |                                                                                                      |

| Channels                                                                                                                             | 2                                                                                                | 4                                                                                                           | 8                                                                                        | 16                                                  | 24                                                     | 64                                                                                                | 128                                                                                                  |

| Resolution (bits) 14 7                                                                                                               |                                                                                                  | 6                                                                                                           | 11                                                                                       | 11                                                  | 10                                                     | 7/8/9                                                                                             |                                                                                                      |

| ENOB *11.2525                                                                                                                        |                                                                                                  | 6                                                                                                           | 4.9                                                                                      | *6.6844                                             | 8.1                                                    | *7.7641                                                                                           | *6.186/7.0166/<br>8.0133                                                                             |

| Sample Rate (Gsps) 0.2 2.2                                                                                                           |                                                                                                  | 2.2                                                                                                         | 16                                                                                       | 3.6                                                 | 2.8                                                    | 2.6                                                                                               | 1/0.5/0.25                                                                                           |

| Architecture                                                                                                                         | Pipeline &<br>Flash (7 &<br>1 per<br>channel)                                                    | Subranging                                                                                                  | Flash                                                                                    | SAR                                                 | SAR                                                    | SAR                                                                                               | Channel counter ADC aka single slope converters                                                      |

| Compensation<br>Method                                                                                                               | LMS-FIR<br>and interp<br>filter.<br>Corrects<br>offset, gain,<br>BW and<br>sample<br>time error. | Distributed resistor array for gain, digitally corrective current sources for offset, nested T/H for timing | Digital<br>offset and<br>timing<br>skew,<br>using an<br>on chip<br>cal signal            | Startup<br>and<br>bkgd cal                          | Two extra SAR for calibratio n using LMS weight update | Startup on<br>chip cal<br>for offset<br>and gain<br>mismatch<br>es as well<br>as DAC<br>linearity | Cal of the devices at statup and at regular intervals using foreground cal and continuous correction |

| Complexity                                                                                                                           | Un-<br>specified<br>filter<br>lengths                                                            | Analog<br>Circuitry, a<br>resistor network<br>and additional<br>T/H of high<br>BW                           | One<br>Random<br>chopping<br>latch, Two<br>Choppers,<br>& a zero<br>crossing<br>detector | 2, 12b<br>current<br>steering<br>startup<br>caldacs | Extra<br>hardware<br>& simple<br>LMS                   | Un-<br>specified                                                                                  | Buffer shifting<br>and<br>subtraction                                                                |

| <b>Power (mW)</b> 460 40                                                                                                             |                                                                                                  | 435                                                                                                         | 795                                                                                      | 44.6                                                | 480                                                    | 26.5/26/25.3                                                                                      |                                                                                                      |

| Supply(V)                                                                                                                            | 1.8                                                                                              | 1.15                                                                                                        | 1.5                                                                                      | 1.2/2.5                                             | 1.2                                                    | 1.2/1.3/1.6                                                                                       | 1.2                                                                                                  |

| SNDR (dB)                                                                                                                            | 69.5@<br>15.3MHz                                                                                 | 38@ 1080MHz                                                                                                 | 30.8@<br>170MHz                                                                          | 42@<br>Nyq                                          | 48.2@<br>Nyq                                           | 48.5@<br>Nyq                                                                                      | 39/44/50@<br>Nyq                                                                                     |

| Active Area (mm²) 15.2 0.2                                                                                                           |                                                                                                  | 0.2                                                                                                         | 0.93x1.58                                                                                | 7.44                                                | 1.03x1.6<br>6                                          | 5.1                                                                                               | 0.55                                                                                                 |

| *calculated based on SNDR_not reported                                                                                               |                                                                                                  |                                                                                                             |                                                                                          |                                                     |                                                        | )D ====================================                                                           |                                                                                                      |

\*calculated based on SNDR, not reported

### **CHAPTER 2: METHODS AND MATERIALS**

A key stumbling block to cost effective research and development for improving TI-ADC performance is the availability of high fidelity, high level models for simulations incorporating realistic error performance of data converters. Without realistic high level models researchers are forced to use simplified approximations that are inadequate from the point of view of both error sources and fidelity, spice models that are too costly to develop and time consuming to run, or hardware based emulation which forces the use of expensive hardware based simulations and does not allow researchers to selectively apply error sources to facilitate effective evaluation of the correction algorithms under development. The Simulink<sup>TM</sup> model presented herein simulates high performance ADCs tuned to emulate the performance of known commercial off the shelf (COTS) devices. This model can be generalized to *M* analog-to-digital converters and serves as a basis for the research described herein.

In this dissertation four ADCs are used in an interleaved configuration to serve as the base example. The following subsections discuss the behavioral model and presents statistical properties of the mismatch errors. In some simulations a polynomial model is used to compare performance to other methods of post conversion correction; the implementation is also described here. For completeness a survey of recent correction methods is presented and their models and methods noted at the end of this chapter and it is used for comparison in a later chapter.

### Design of the Behavioral Model

As a research and development tool the goal of the behavioral model is to closely approximate the behavior of the dominate error sources in an ADC such that when combined, the overall ADC simulation represents the behavior of that ADC to a required fidelity without the use of expensive time consuming Spice models or the inflexibility of hardware in the loop. To this end each error source is modeled independently so that they can be individually enabled as desired to aid the performance evaluation process.

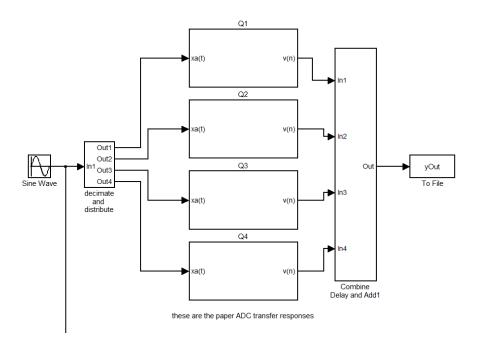

Table 1 shows the parameters used from the Maxim 12554 14 bit, 80Msps, 3.3V ADC to configure the model. Since the converter has a wide input bandwidth and supports subsampling, the error model must likewise support these capabilities. Figure 8 shows the top level diagram of the implementation of the behavioral model of a 4 channel TI-ADC in Simulink<sup>TM</sup>. The input sine wave sampling rate is 9 times the interleaved rate of 4\*Fs where Fs is the sub-ADC (per channel) sampling rate. It is important to note here that the 9 times oversampling is required in the model to relax the filter requirements on the implementation of the Farrow filter structure introducing jitter as well as supporting subsampling behavior for the INL and gain errors and is not based on an actual hardware instantiation requirement. This oversampling requirement shall be discussed in the description of the aperture jitter section detailing the Farrow resampling filter below.

Table 3: MAX 12554 Datasheet Characteristics and Parameters

| Parameter       | Data Sheet Values                           | Model Values          |

|-----------------|---------------------------------------------|-----------------------|

| FS Range        | +/- 0.35V to +/- 1.10V                      | +/- 1.10V             |

| INL             | +/-2.4 Typ, +/-4.9 Max (LSB): at 3MHz       | Used Plot across Freq |

| DNL             | -1 Min, +/-0.5 Typ, +1.3 Max (LSB): at 3MHz | Used Plot across Freq |

| Offset Error    | +/- 0.1 Typ, +/- 0.72 Max (%FS)             | +/- 0.1 %FS           |

| Gain Error      | +/- 0.5 Typ, +/- 4.9 Max (%FS)              | +/- 0.5 %FS           |

| Aperture Jitter | <0.2 ps RMS                                 | 0.2 ps RMS            |

Figure 8: Top level view, 4 Channel TI-ADC Behavioral Model, Simulink<sup>TM</sup>

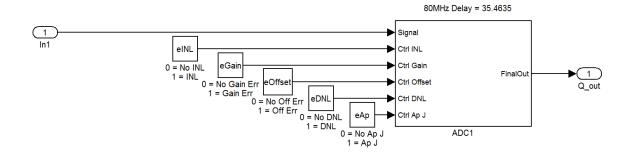

Figure 9 shows a top level block diagram of the single ADC Simulink behavioral model and its error source control mechanism. As seen in the figure each error source has an individual control bit that is set to enable the corresponding error source model. This enables the analysis of the

effect of the correction algorithm under evaluation on the error sources individually and in all possible combinations.

Figure 9: Single ADC block view, illustration of enabling errors, Simulink<sup>TM</sup>

Error Implementations: Offset, Gain, Quantization, DNL, INL

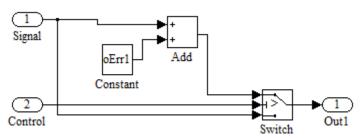

The device targeted for description in this dissertation has a constant DC offset of 0.1% full scale (FS) [40]. This error is seen in the spectrum of the output as a non-zero value at DC. In the model, offset error is modeled by adding a constant to the signal prior to digitization as shown in Figure 10. If left uncorrected, when interleaved, the distortion due to mismatch manifests itself as harmonics of k \* Fs/M, where Fs is the interleaved sampling rate, M is the number of converters interleaved, and k is an integer; 1,2, 3,4 . . . [41].

Figure 10: Offset Error Implementation, Simulink<sup>TM</sup>

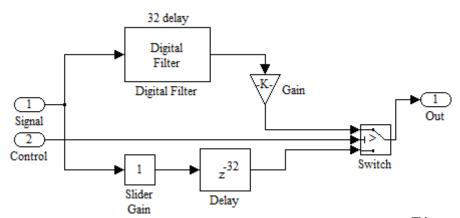

Gain error is modeled by an equiripple gain deviation from the ideal as shown in Figure 11. Though this is a simplistic implementation it provides a worst case scenario. The proposed correction algorithm does not take unique advantage of the equidistant peaks and these peaks allow multiple gain errors at the maximum. This is accomplished with a polynomial approximation in the passband region of interest. The ripple as a function of frequency is described in linear terms, consistent with the published data for the device being modeled, is calculated within the band of interest as  $D_{pass} = FS * E_{gain}$  where FS is the full scale value and  $E_{gain}$  is the percent of full scale gain error as specified in the characterization of the device. This error manifests itself in the frequency domain as amplitude ripple. It should be noted that the gain errors can usually be trimmed by the user; however with multiple interleaved ADCs, if left uncorrected, the mismatch distortion will be present in the spectrum at  $\pm f_i + k * Fs/M$  [42].

Figure 11: Nonlinear Gain Error Implementation, Simulink<sup>TM</sup>

The quantizer component of an ADC converts a discrete time, continuous voltage sample into a discrete time, discrete voltage sample where the voltage is represented as a numerical value. DNL error is due exclusively to the encoding process [43] and can be combined with quantization error as non-uniform quantization levels. That is, ideally the transition voltage

between consecutive codes should be uniform and DNL characterizes the deviations from the ideal spacing.

A statistical distribution of the DNL error is used in this model. In this model it is assumed that the error mechanism is a stationary random process related to the manufacturing process, uncorrelated with the input, and a white-noise process. Ideal quantization is a uniform probability distribution over the range of quantization that is commonly described with the following statistical representation.

For small quantization levels  $\Delta$ , it is assumed that the error due to quantization,  $e_Q[n]$  is a uniformly distributed random variable from  $-\frac{\Delta}{2}$  to  $\frac{\Delta}{2}$ . Assume also that successive noise samples are uncorrelated with each other. The mean value is zero and the variance is  $\sigma_e^2 = \int_{-\Delta/2}^{\Delta/2} e^2 \frac{1}{\Delta} de = \frac{\Delta^2}{12}$ . DNL error can be combined with the above formulation of quantization error by no longer assuming that  $\Delta$  is a constant width.

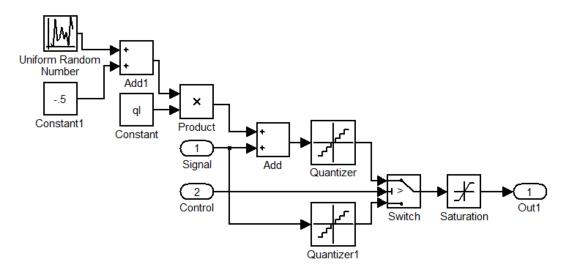

Figure 12 shows the implementation of quantization and DNL in Simulink<sup>TM</sup>. When modeling quantization the provided quantizer block is ideal and thus passes its input through a stair-step function so that a certain interval is mapped to one level at the output. The output is computed using the round-to-nearest method which produces an output that is symmetric about zero. The spectrum effect is that of an additive uniform noise process. The DNL plot in the characterization of the target device shows that error appears to have an approximate uniform distribution across digital output codes with a mean around -.15 LSB (least significant bit) and a range of 0.7 LSB. NOTE: the actual error mechanism is likely more precisely a truncated Gaussian process but the

uniform distribution used in the model provides the required accuracy without the added complexity of truncating a Gaussian distributed noise source. This is reproduced in Simulink<sup>TM</sup> using a uniform random number generator with a minimum set to 0 and max set to 0.7, 0.5 is subtracted from the number to adjust the mean. This number is then multiplied by the quantization interval to convert to the scale relative to the size of the LSB and added to the incoming signal to model DNL. Distortion products depend on the amplitude and positioning of the DNL along the quantizer transfer function. As can be deduce from the description of DNL, for lower level signals the harmonic content becomes dominated by the DNL and does not generally decrease proportionally with decreases in signal amplitude. INL in contrast determines the distortion of nearly full-scale signals [43].

Figure 12: Quantization and DNL error implementation, Simulink<sup>TM</sup>

The sample and hold component of an ADC ideally samples a continuous time signal at equally spaced time intervals and holds the sampled voltage fixed while the quantizer measures the voltage to the accuracy of its minimum quantization level. In simplistic terms, the sample and

hold is an ideal analog switch and an ideal holding amplifier. In practice these requirements present a conundrum. Capacitance is required to track and hold the input voltage. To track a signal varying with high frequency content requires a low capacitance. However, to hold the voltage constant during the quantization process requires a high capacitance. (To be completely accurate it is the resistance-capacitance (RC) products that must be low and high.) These conflicting requirements force design tradeoffs to be made and the conflicting requirements are magnified in sub-sampling application spaces of which TI-ADC are inherently members.

Conflicting requirements like those just described coupled with the bandwidth limitations of any semiconductor process introduce INL. INL is due primarily to the nonlinearities, slew rates due to device bandwidth limits, etc. in the analog front end of the ADC. This includes the sample and hold amplifier as well as to a lesser extent the overall nonlinearity of the ADC and is ultimately influenced by the process  $f_T$ , the frequency at which the transistor current gain drops to unity, an indicator of process bandwidth.

Distortions produced by INL have amplitudes that vary as a function of the input signal amplitude and frequency. The location of the spurious harmonics can be calculated based upon the input signal's span of frequency components, amplitude and on other factors affecting the specific ADC transfer function. For an interleaved configuration with INL mismatch errors, spurs from multiple ADCs can interact to create worse or lesser harmonics depending on the periodically varying combined spectrums of the ADCs.

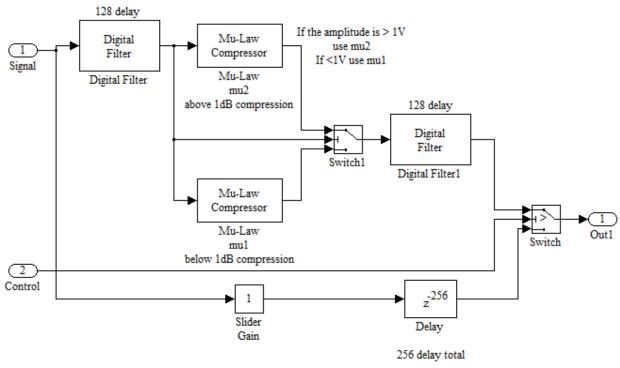

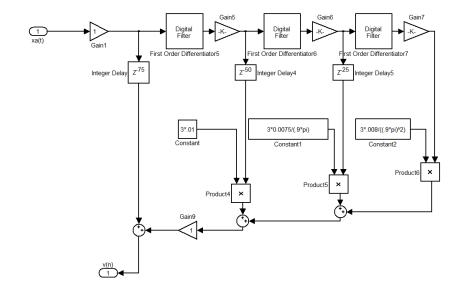

To model this type of error practically one must use the representative measured INL characteristics of the ADC being modeled as a performance template. The SFDR plots relate the

input frequency and amplitude of the signal from which INLs can be derived. By analyzing the characteristic data for this parameter family, a sufficient approximation to the lumped nonlinearities can be produced. For the model described herein the lumped integral nonlinearities were modeled as frequency dependent amplitude nonlinearity. This can be seen in Figure 13 where the first digital filter channelizes the input into frequency dependent segments in which nonlinearities are introduced as a function of frequency and amplitude, the mu law compressors generate nonlinearities as a function of amplitude and the second digital filter recombines the frequency dependent nonlinear channels back into a single contiguous composite channel.

Figure 13: INL Error Modeling in Simulink<sup>TM</sup>

# Aperture Jitter

Quantization of an analog signal into a discrete time digital signal is a two dimensional process. To this point error sources in the amplitude dimension have been discussed. The other dimension is temporal and although non-uniform sampling is valid from a theoretical perspective, it is complex to practically implement, especially for random sample times. (In practice the two dimensional quantization error sources are vernacularly referred to as the error "fuzz ball.")

In high performance data converter implementations, especially subsampling implementations, aperture jitter is usually the dominant temporal error source and the overall performance limiter of the conversion process. Aperture jitter is driven by the highest input frequency. In real input Nyquist sampling implementations, the highest input frequency is approximately equal to the converter's Nyquist frequency. In subsampling implementations aperture jitter requirements are driven by the highest intermediate frequency (IF) signal frequency input to the subsampling ADC.

Any aperture jitter manifests itself as breaking the assumption of equally spaced samples input to any subsequent digital signal processes and can be viewed as phase modulation (PM). When using multiple sampling phase offset ADCs, a constant sampling clock offset is introduced between the ADCs creating an additional and deterministic PM. The mismatch distortion is located at intervals of  $\pm f_i + k * Fs/M$  [42].

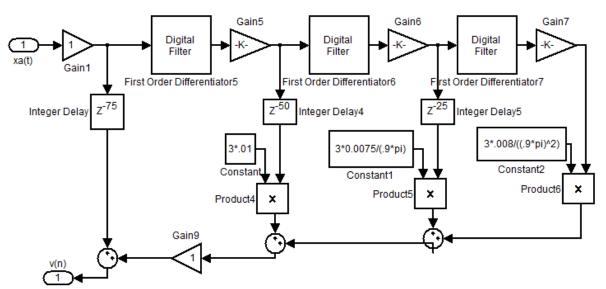

In modeling aperture jitter, a Farrow filter with the timing offset signal driven by a Gaussian random number generator is used to emulate continuously deviating sample times of the input signal in the Simulink<sup>TM</sup> model. In order to relax the interpolation filter requirements the

sampling rate of the input data is set at 9 times the required rate for the rest of the simulation and then additionally interpolated 128 times to meet the desired delay times to be introduced. This structure is shown in Figure 14. The Farrow structure is accurate for only small frequencies compared to the overall bandwidth. The data sheet of the converter which is the example for this dissertation specifies the aperture jitter typical in the ADC as <0.2ps. For the 14-bit ADC 0.2ps corresponds to 97.14MHz before the aperture jitter causes more than ½ LSB of sampling error as described by reorganizing the maximum jitter Equation in 1 to find f<sub>max</sub>.

$$t_{j,max} = \frac{1}{2\pi f_{max} 2^{N-1}} \tag{1}$$

Figure 14: Aperture jitter implementation, Simulink<sup>TM</sup>

# **Cumulant Statistics**

Identifying, classifying the source, and quantifying the presence of errors in ADCs and TI-ADCs is fundamental in the pursuit of correcting these errors. This problem, characterization of error effects as a function of error source and mechanism is investigated through calculation of higher

order statistics on the error signals of each type of error source individually and combined in a single ADC and time interleaved configuration.

The concept of the calculation of high order statistics and their interpretation in the context of this dissertation is presented and applied to time varying error environments and input signals. The behavioral model allows for isolation of the errors sources in the device as well as any varying combination. Second order statistics are sufficient whenever the signals can be completely characterized by the first two moments. If the desire is to characterize Gaussian signals, this would be sufficient but the errors that are being characterized in this study benefit from higher order statistics. Cumulants of a Gaussian random process greater than the second order are zero (if excess Kurtosis is considered the fourth order statistic). All distributions except the Gaussian do not have a finite number of non-zero cumulants (statistics), shown by Marcinkiewicz [44]. Using higher order statistics, a departure from Gaussianity can be exploited, such as in nonlinear system identification.

Background on the first eight order statistics is described further in the following subsection. The method of computation and results of the higher order analysis is also presented and discussed.

#### **Cumulant Equations**

Cumulants are the coefficients in the Taylor series expansion of the cumulant generating function about the origin. The first two cumulants are equal to the first two moments, the mean and the variance. However, higher order cumulants are not the same as moments about the mean, though they can be related to the moments. There are two common important properties of cumulants mentioned in the literature: Cumulants suppress additive Gaussian noise of unknown

covariance, and the cumulant generating function of the sum of independent processes is the sum of the cumulants instead of the product. These properties and more can be found in [45] and [46].

The *kth order cumulant* in general can be calculated as described in Equation 2, the ratio of the expected value of the variable x to the *k*th power of the standard deviation for integers of k>2. For k=1 the cumulant is simply the mean of the signal, and for k=2 the cumulant is the variance.