Electronic Theses and Dissertations, 2004-2019

2005

# Design And Synthesis Of Clockless Pipelines Based On Selfresetting Stage Logic

Abdelhalim Alsharqawi University of Central Florida

Part of the Computer Engineering Commons

Find similar works at: https://stars.library.ucf.edu/etd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS Citation**

Alsharqawi, Abdelhalim, "Design And Synthesis Of Clockless Pipelines Based On Self-resetting Stage Logic" (2005). *Electronic Theses and Dissertations, 2004-2019.* 524. https://stars.library.ucf.edu/etd/524

# DESIGN AND SYNTHESIS OF CLOCKLESS PIPELINES BASED ON SELF-RESETTING STAGE LOGIC

by

ABDELHALIM M. ALSHARQAWI B.S. Princess Sumaya University, 2000 M.S. University of Central Florida, 2002

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering in the College of Engineering and Computer Science at the University of Central Florida

Orlando, Florida

Fall Term 2005

Major Professor: Abdel Ejnioui

© 2005 Abdelhalim Alsharqawi

#### **ABSTRACT**

For decades, digital design has been primarily dominated by clocked circuits. With larger scales of integration made possible by improved semiconductor manufacturing techniques, relying on a clock signal to orchestrate logic operations across an entire chip became increasingly difficult. Motivated by this problem, designers are currently considering circuits which can operate without a clock. However, the wide acceptance of these circuits by the digital design community requires two ingredients: (i) a unified design methodology supported by widely available CAD tools, and (ii) a granularity of design techniques suitable for synthesizing large designs. Currently, there is no unified established design methodology to support the design and verification of these circuits. Moreover, the majority of clockless design techniques is conceived at circuit level, and is subsequently so fine-grain, that their application to large designs can have unacceptable area costs.

Given these considerations, this dissertation presents a new clockless technique, called *self-resetting stage logic* (SRSL), in which the computation of a block is reset periodically from within the block itself. SRSL is used as a building block for three coarse-grain pipelining techniques:

(i) Stage-controlled self-resetting stage logic (S-SRSL) Pipelines: In these pipelines, the control of the communication between stages is performed locally between each pair of stages. This communication is performed in a uni-directional manner in order to simplify its implementation.

- (ii) Pipeline-controlled self-resetting stage logic (P-SRSL) Pipelines: In these pipelines, the communication between each pair of stages in the pipeline is driven by the oscillation of the last pipeline stage. Their communication scheme is identical to the one used in S-SRSL pipelines.

- (iii) Delay-tolerant self-resetting stage logic (D-SRSL) Pipelines: While communication in these pipelines is local in nature in a manner similar to the one used in S-SRL pipelines, this communication is nevertheless extended in both directions. The result of this bi-directional approach is an increase in the capability of the pipeline to handle stages with random delay.

Based on these pipelining techniques, a new design methodology is proposed to synthesize clockless designs. The synthesis problem consists of synthesizing an SRSL pipeline from a gate netlist with a minimum area overhead given a specified data rate. A two-phase heuristic algorithm is proposed to solve this problem. The goal of the algorithm is to pipeline a given datapath by minimizing the area occupied by inter-stage latches without violating any timing constraints. Experiments with this synthesis algorithm show that while P-SRSL pipelines can reach high throughputs in shallow pipelines, D-SRSL pipelines can achieve comparable throughputs in deeper pipelines.

#### ACKNOWLEDGMENTS

I would like to express my gratitude to my advisor, Dr. Abdel Ejnioui, who invested time and patience toward the completion of this dissertation. Without his encouragement, support, and guidance, this dissertation would not have been possible. I would like to thank my committee members, Drs. Issa Batarseh, Ronald F. Demara, Hassan Foroosh, and Alain Kassab, for their support and willingness to serve on my defense examination. In particular, I would like to show my special gratitude to Dr. Issa Batarseh for supporting my research work in times when support resources were scarce. Beside Dr. Batarseh, I would like to show the same gratitude to Dr. Harold Klee for providing me with department support whenever possible. Also, I would like to thank Donald Harper for his patience and generosity in supporting the EDA design tools in the VLSI Lab. Furthermore, I am grateful to my friend and lab mate, Rashad Oreifej, for his insightful comments and helpful feedback on my work.

I would like to express my sincere thanks to my parents for their unconditional support, guidance, and sacrifice. They have always believed in me and gratified me with their unending love. Finally, I would like to thank my loving wife Amani for her generosity, support, and understanding throughout my graduate studies. Her presence has been a pillar of steadfastness on which to lean after long hours of toiling in the VLSI Lab.

# **TABLE OF CONTENTS**

| LIST OF FIGURES                                 | xii  |

|-------------------------------------------------|------|

| LIST OF TABLES                                  | xvii |

| CHAPTER ONE: INTRODUCTION                       | 1    |

| 1.1 Motivation                                  | 1    |

| 1.1.1 The Clocking Problem                      | 1    |

| 1.1.2 Growing Importance of Clockless Circuits. | 2    |

| 1.1.3 Coarse-Grain Clockless Pipelining         | 4    |

| 1.2 Design Methodology in Clocked Circuits      | 5    |

| 1.2.1 Specification and Modeling                | 5    |

| 1.2.2 Verification                              | 6    |

| 1.2.3 Synthesis                                 | 6    |

| 1.2.4 Mapping                                   | 8    |

| 1.3 Limitations of Clocked Circuits             | 8    |

| 1.3.1 Clock Frequency                           | 8    |

| 1.3.2 Timing Closure                            | 9    |

| 1.3.3 Power Implications                        | 9    |

| 1.3.4 Area Implications                         | 9    |

| 1.3.5 Noise Margins                             | 10   |

| 1.3.6 Multiple Clock Domains                    | 10   |

| 1.4 Clockless Circuits                          | 11   |

| 1.4.1 Self-Clocked Circuits                     | 11   |

| 1.4.2 Speed-Independent Circuits                           | 13  |

|------------------------------------------------------------|-----|

| 1.4.3 Delay-Insensitive Circuits                           | 13  |

| 1.4.4 Self-Timed Circuits                                  | 14  |

| 1.4.5 Self-Resetting Circuits                              | 15  |

| 1.5 Design Methodology in Clockless Circuits               | 15  |

| 1.6 Contributions of the Dissertation                      | 17  |

| 1.7 Overview of the Dissertation                           | 19  |

| CHAPTER TWO: RELATED CLOCKLESS DESIGN METHODOLOGIES        | 21  |

| 2.1 Petri Nets                                             | 21  |

| 2.2 Signal Transition Graphs                               | 25  |

| 2.3 Micropipelines                                         | 27  |

| 2.4 Null Convention Logic                                  | 30  |

| 2.5 Burst Mode Machine                                     | 34  |

| 2.6 Handshake Circuits                                     | 36  |

| 2.7 Extended Delay Insensitive Model                       | 39  |

| 2.8 Summary                                                | 39  |

| CHAPTER THREE: STAGE-CONTROLLED SELF-RESETTING STAGE LOGIC |     |

| PIPELINES                                                  | 42  |

| 3.1 SRSL                                                   | 42  |

| 3.2 S-SRSL Linear Pipelines                                | 44  |

| 3.3 S-SRSL Non-linear Pipelines                            | 50  |

| 3.3.1 S-SRSL Join Operation                                | 50  |

| 3 3 2 S-SRSL Fork Operation                                | 52. |

| 3.4 Performance of the Pipeline                               | 54      |

|---------------------------------------------------------------|---------|

| 3.4.1 Parameter Definitions                                   | 54      |

| 3.4.2 Analysis of the Reset and Evaluate Phase                | 55      |

| 3.4.3 Effect of $\delta$ on the Pipeline Stages               | 58      |

| 3.4.4 δ and Pipeline Depth                                    | 59      |

| 3.4.5 Area Cost                                               | 61      |

| 3.4.6 Fault Handling                                          | 61      |

| 3.5 Prototype Implementation of the S-SRSL Pipelines          | 65      |

| 3.5.1 The S-SRSL Linear Pipeline                              | 66      |

| 3.5.2 The S-SRSL Non-Linear Pipeline                          | 70      |

| 3.5.2.1 The S-SRSL Join Pipeline                              | 70      |

| 3.5.2.2 The S-SRSL Fork Pipeline                              | 72      |

| 3.6 Summary                                                   | 74      |

| CHAPTER FOUR: PIPLINE-CONTROLLED SELF-RESETTING STAGE LOGIC P | IPLINES |

|                                                               | 75      |

| 4. 1 P-SRSL Linear Pipeline                                   | 75      |

| 4.2 P-SRSL Non-Linear Pipelines                               | 82      |

| 4.2.1 P-SRSL Join Pipeline                                    | 82      |

| 4.2.2 P-SRSL Fork Pipeline                                    | 85      |

| 4.3 Performance of the Pipeline                               | 87      |

| 4.3.1 Analysis of the Reset and Evaluate Phase                | 87      |

| 4.3.2 Effect of $\delta$ on the Pipeline Stages               | 90      |

| 4.3.3 Effect of the Period on the Latch Enable                | 91      |

| 4.3.4 Area Cost                                                   | . 92 |

|-------------------------------------------------------------------|------|

| 4.3.5 Fault Handling                                              | . 92 |

| 4.4 Prototype Implementation of the P-SRSL Pipeline               | . 94 |

| 4.4.1 Implementation of the Linear Pipeline                       | . 94 |

| 4.4.2 Implementation of the Non-Linear Pipelines                  | . 97 |

| 4.4.2.1 The P-SRSL Join Pipeline                                  | . 97 |

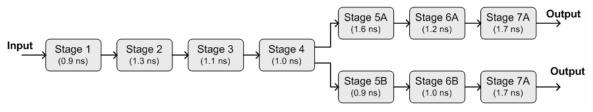

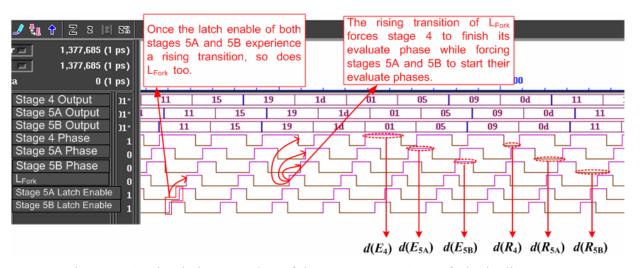

| 4.4.2.2 The P-SRSL Fork Pipeline.                                 | 100  |

| 4.5 Comparison of P-PRSL to S-SRSL Pipelines                      | 102  |

| 4.6 Summary                                                       | 103  |

| CHAPTER FIVE: DELAY TOLERANT SELF-RESETTING STAGE LOGIC PIPELINES | 104  |

| 5.1. D-SRSL Linear Pipeline                                       | 104  |

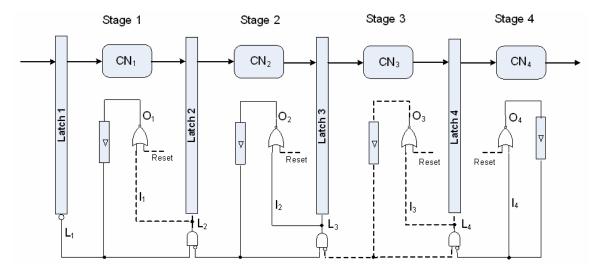

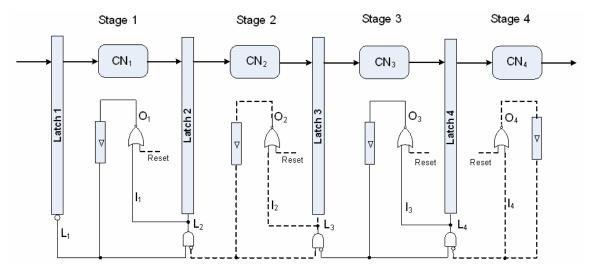

| 5.1.1 Pipeline Structure.                                         | 104  |

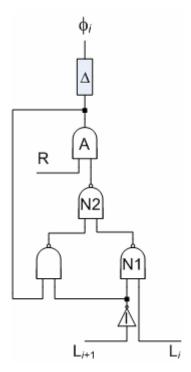

| 5.1.2 Phase Control Block                                         | 106  |

| 5.1.3 Latch Control Block                                         | 108  |

| 5.2. D-SRSL Non-Linear Pipelines                                  | 109  |

| 5.2.1 D-SRSL Join Pipeline                                        | 109  |

| 5.2.2 D-SRSL Fork Pipeline                                        | 114  |

| 5.3. Performance of the Pipeline                                  | 118  |

| 5.3.1 The Reset and Evaluate Phase                                | 118  |

| 5.3.2 Duration of Latch Enable                                    | 122  |

| 5.3.3 Stage Delay and Period                                      | 123  |

| 5.3.4 Area Cost                                                   | 128  |

| 5 3 5 Fault Handling                                              | 128  |

| 5.4 Prototype Implementation of the D-SRSL Pipeline  | 131 |

|------------------------------------------------------|-----|

| 5.4.1 Implementation of the PC Block                 | 131 |

| 5.4.2 Implementation of the LC Block                 | 132 |

| 5.4.3 Implementation of the Join Block               | 134 |

| 5.4.4 Implementation of the Fork Block               | 136 |

| 5.4.5 Implementation of D-SRSL Pipeline              | 137 |

| 5.5. Conclusion                                      | 141 |

| CHAPTER SIX: SYNTHESIS OF SRSL PIPELINES             | 143 |

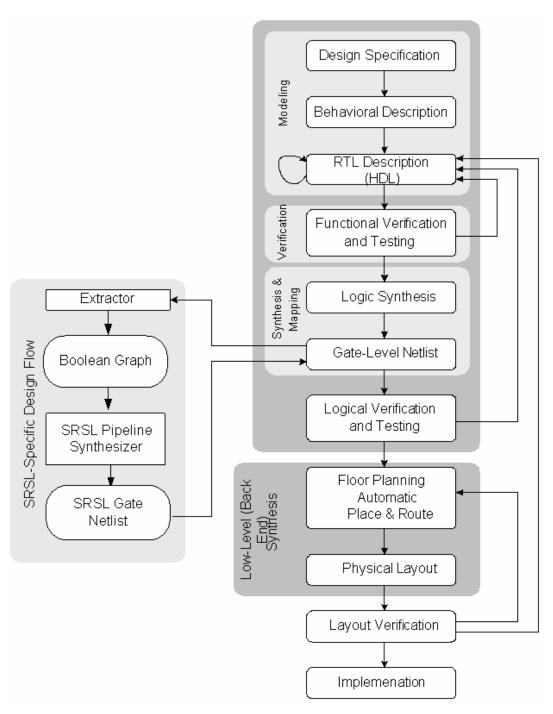

| 6.1 SRSL Pipeline Design Methodology                 | 143 |

| 6.2 Synthesis of SRSL Pipelines                      | 145 |

| 6.3 Preliminaries                                    | 146 |

| 6.4 Modeling of the Synthesis Problem                | 150 |

| 6.5 Proposed Solution of the SRSL Pipeline Synthesis | 156 |

| 6.5.1 Phase I: Stage Assignment                      | 157 |

| 6.5.1.1 Phase I Approach                             | 158 |

| 6.5.1.2 Phase I Algorithm                            | 159 |

| 6.5.2 Phase II: Vertex Shuffling                     | 161 |

| 6.5.2.1 Phase II Approach                            | 161 |

| 6.5.2.2 Phase II Algorithm                           | 168 |

| 6.6 Experimental Results                             | 170 |

| 6.6.1 P-SRSL Pipelining Experiments                  | 170 |

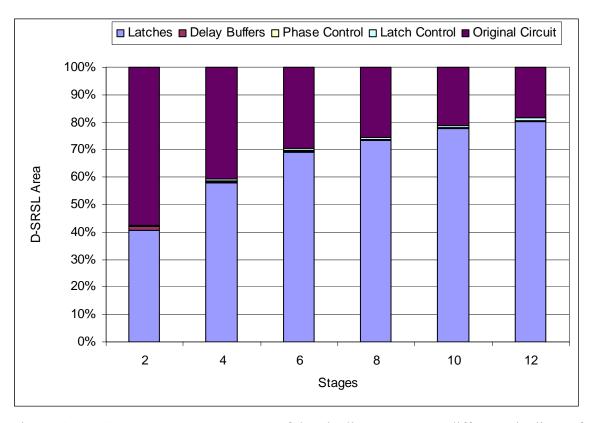

| 6.6.2 D-SRSL Pipelining Experiments                  | 177 |

| 6.6.3 Summary of the Experiment Results              | 182 |

| 6.7 Summary                   | 184 |

|-------------------------------|-----|

| CHAPTER SEVEN: CONCLUSION     | 186 |

| 7.1 Summary of Completed Work | 186 |

| 7.2 Future Work               | 190 |

| LIST OF REFERENCES            | 193 |

# LIST OF FIGURES

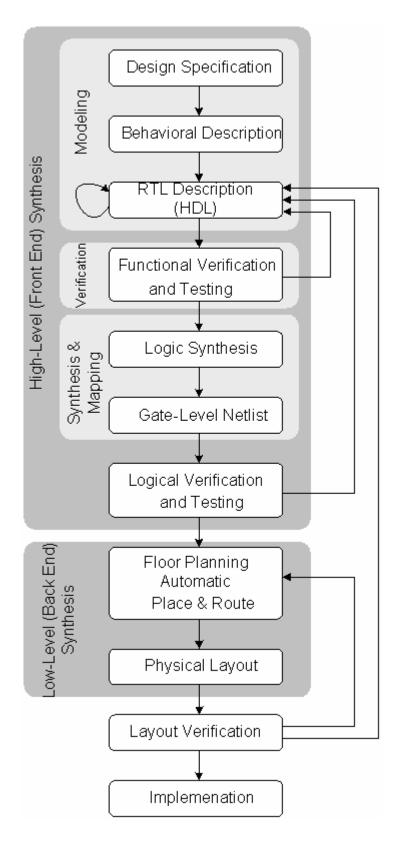

| Figure 1.1: Design flow of clocked circuits [14].                         | 7  |

|---------------------------------------------------------------------------|----|

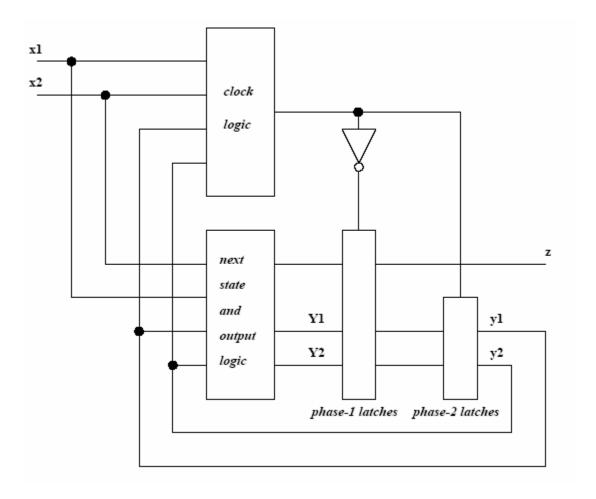

| Figure 1.2: General architecture of SC circuits [25]                      | 12 |

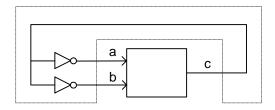

| Figure 2.1: C-element and its surrounding dummy environment [27].         | 22 |

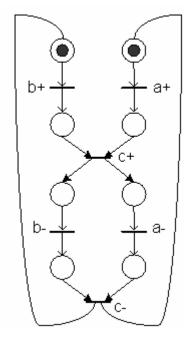

| Figure 2.2: The PN of the C-element shown in Figure 2.1 [27].             | 22 |

| Figure 2.3: Petrify framework                                             | 24 |

| Figure 2.4 :Timing diagram of the C-element shown in Figure 2.1.          | 26 |

| Figure 2.5: STG of the C-element shown in Figure 2.1.                     | 26 |

| Figure 2.6: Synthesis flow of clockless circuits from STG specifications. | 27 |

| Figure 2.7: Micropipeline handshake protocols                             | 28 |

| Figure 2.8: Basic structure of a micropipeline.                           | 28 |

| Figure 2.9: Pipefitter framework                                          | 29 |

| Figure 2.10: NCL 2-of-3 threshold gate.                                   | 31 |

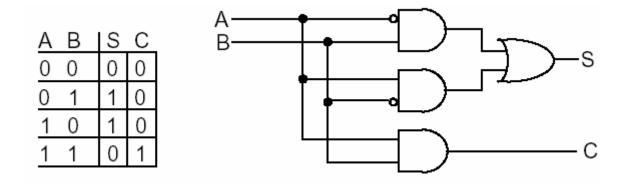

| Figure 2.11: A half adder circuit in conventional Boolean logic           | 31 |

| Figure 2.12: NCL half adder circuit.                                      | 32 |

| Figure 2.13: RTL flow for NCL design [51].                                | 33 |

| Figure 2.14: Burst mode specification of a C-element.                     | 35 |

| Figure 2.15: Handshake channel                                            | 36 |

| Figure 2.16: The Tangram Toolset.                                         | 38 |

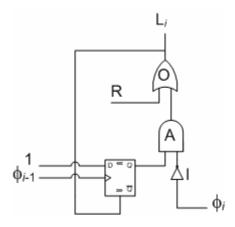

| Figure 3.1: Reset and evaluate network of an SRSL stage.                  | 43 |

| Figure 3.2: STG of the reset network shown in Figure 3.1.                 | 43 |

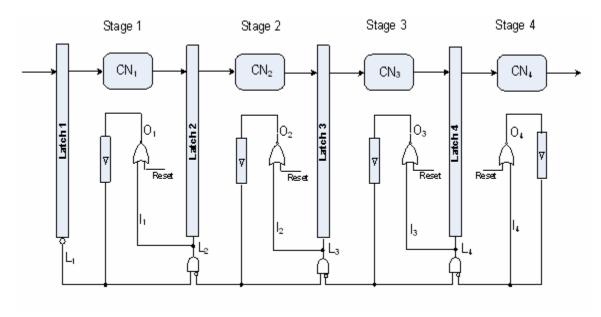

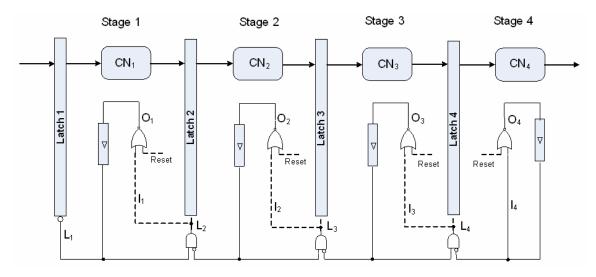

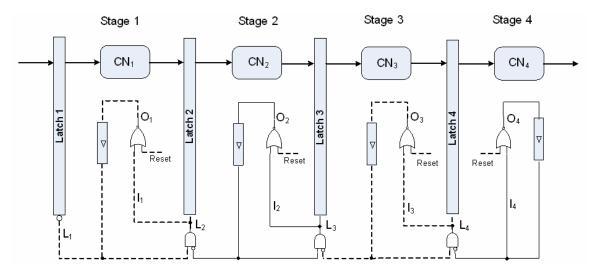

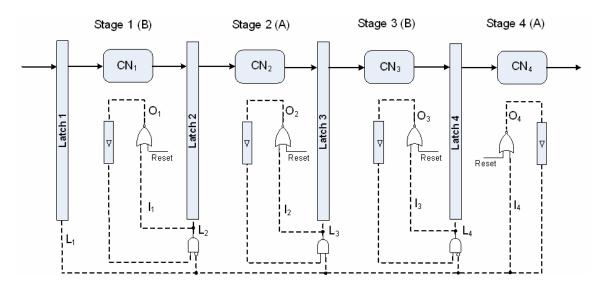

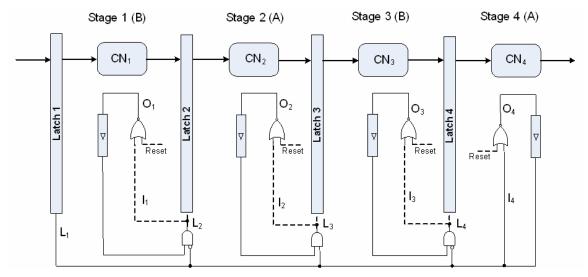

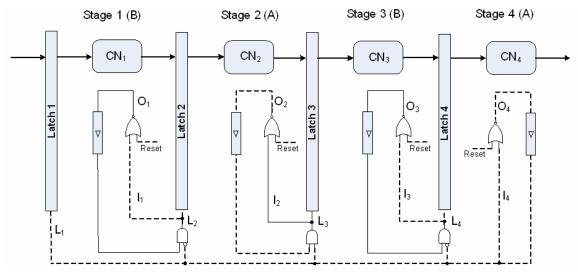

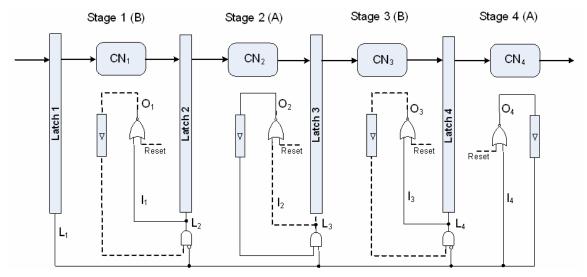

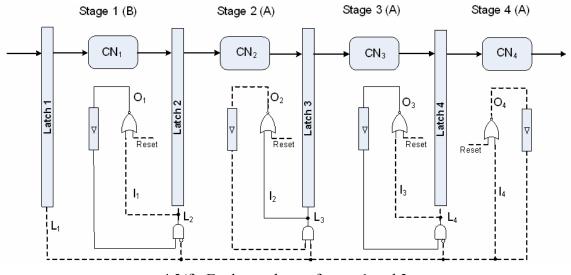

| Figure 3.3: A four-stage S-SRSL pipeline.                                 | 44 |

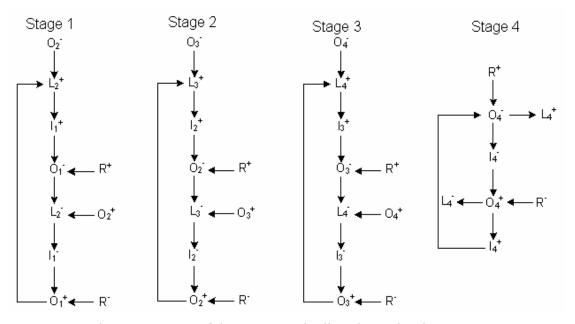

| Figure 3.4: STG of the S-SRSL pipeline shown in Figure 3.3.                                                      | 45   |

|------------------------------------------------------------------------------------------------------------------|------|

| Figure 3.5: Two execution cycles of a four-stage S-SRSL Pipeline                                                 | 49   |

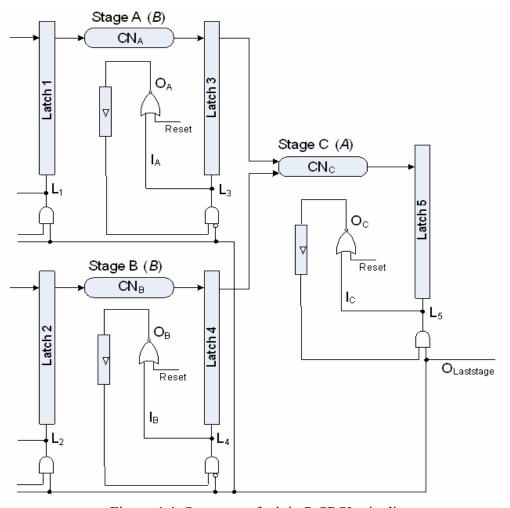

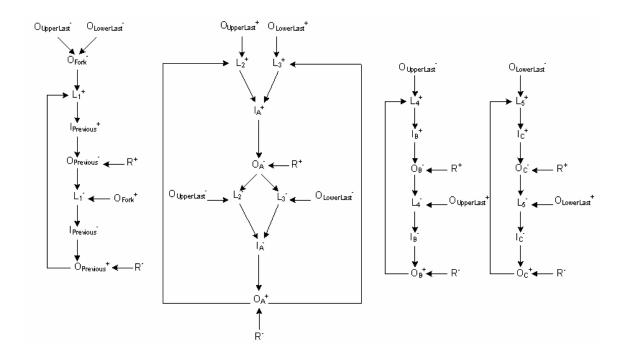

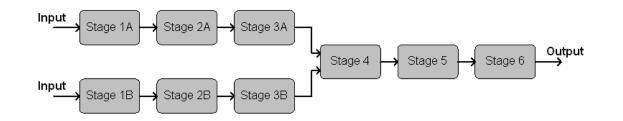

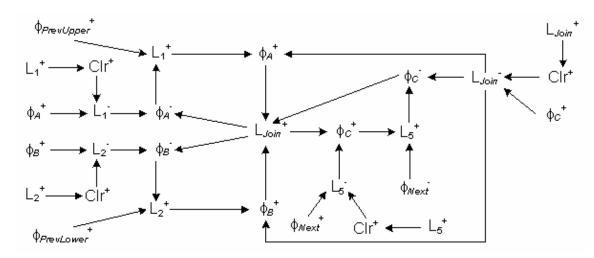

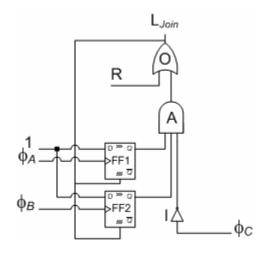

| Figure 3.6: Structure of the join S-SRSL pipeline.                                                               | 51   |

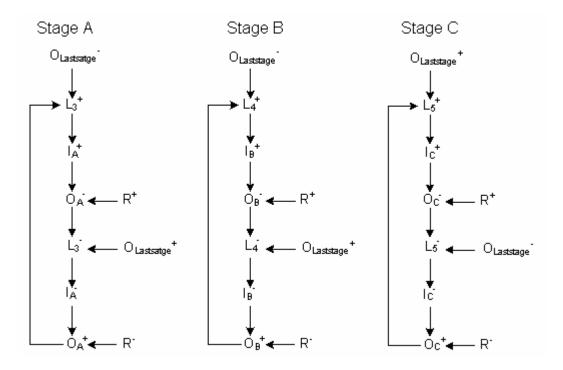

| Figure 3.7: STG of the S-SRSL join pipeline shown in Figure 3.6.                                                 | 52   |

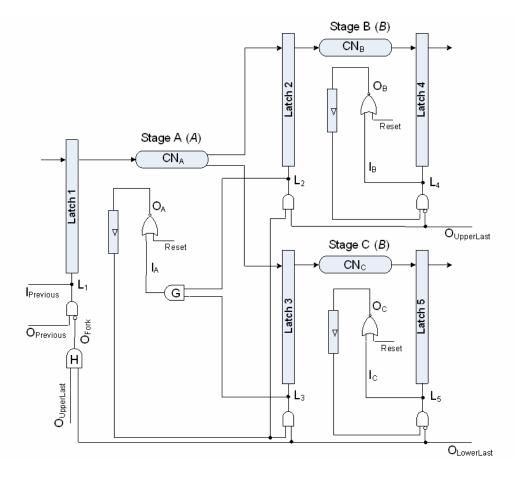

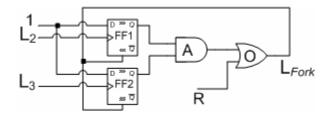

| Figure 3.8: Structure of the fork S-SRSL pipeline.                                                               | 53   |

| Figure 3.9: STG of the S-SRSL fork pipeline shown in Figure 3.8.                                                 | 54   |

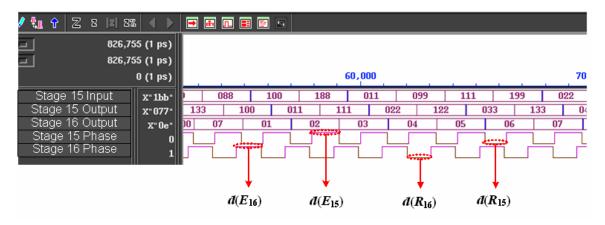

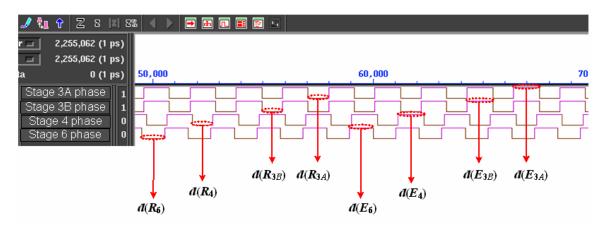

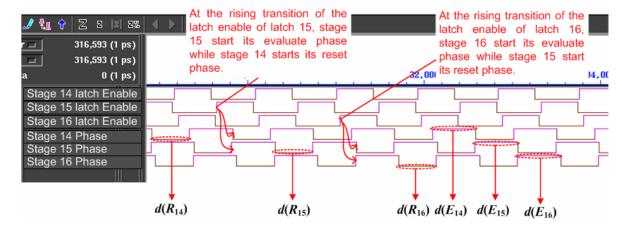

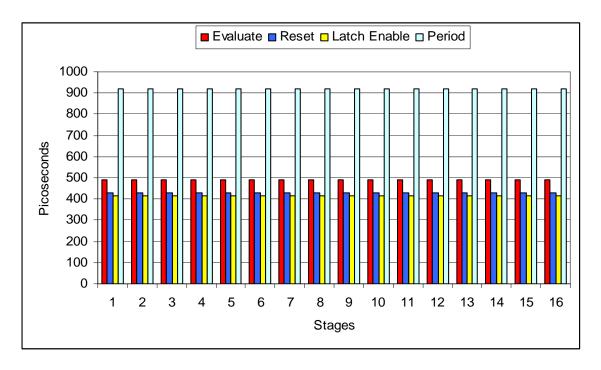

| Figure 3.10: Simulation snapshot of stage 15 and 16 in a 16-stage prototype S-SRSL pipeline                      | . 56 |

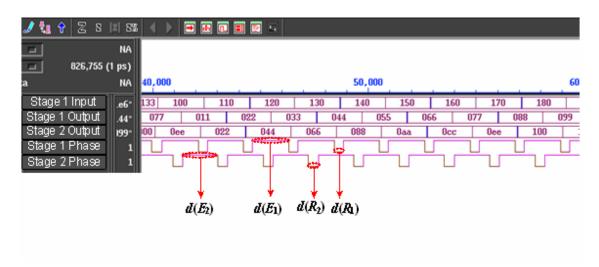

| Figure 3.11: Simulation snapshot of stage 1 and 2 in a 16-stage prototype S-SRSL pipeline                        | 56   |

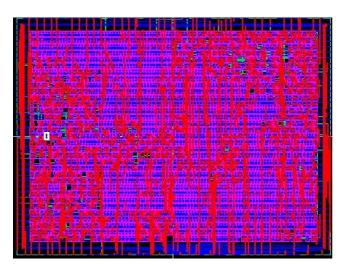

| Figure 3.12: Chip layout of the four-bit 16-stage S-SRSL pipeline.                                               | 66   |

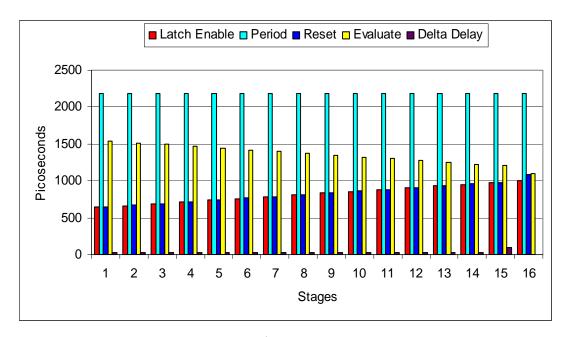

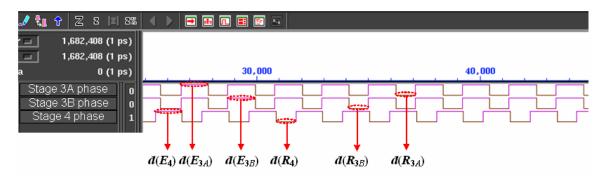

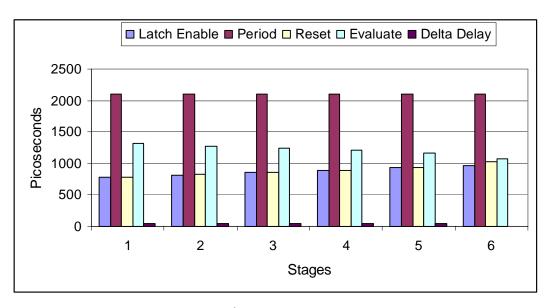

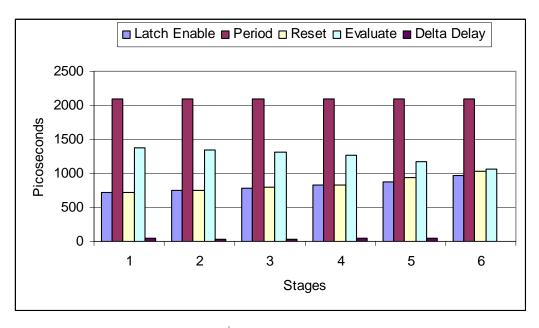

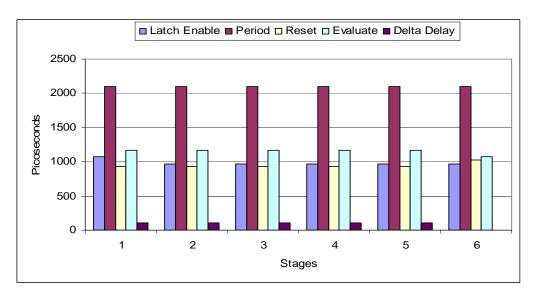

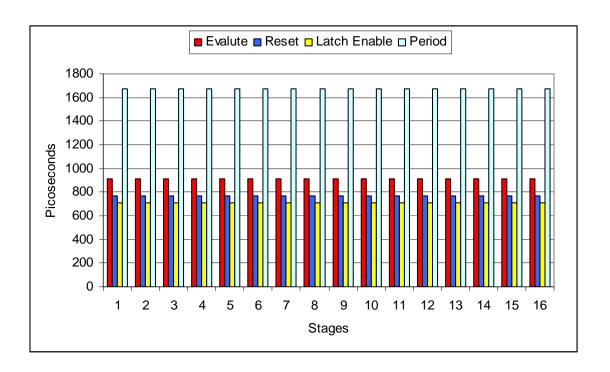

| Figure 3.13: Simulation results of $d(L^+)$ , $d(R)$ , $d(E)$ , $\delta$ , and $P$ in a 16-stage S-SRSL pipeline | 68   |

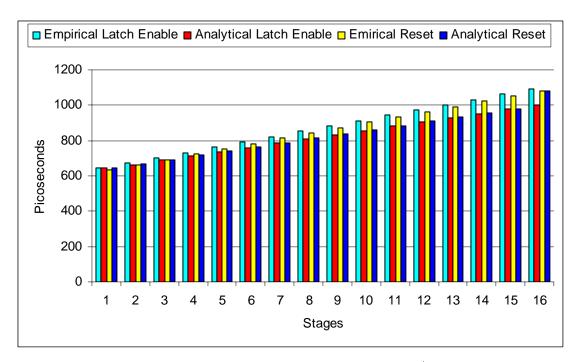

| Figure 3.14: The empirical and analytical values of $d(R)$ and $d(L^+)$ in a 16-stage S-SRSL                     |      |

| pipeline                                                                                                         | 69   |

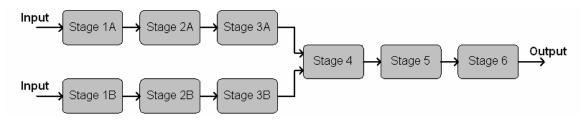

| Figure 3.15: Four-bit six-stage S-SRSL join pipeline.                                                            | 70   |

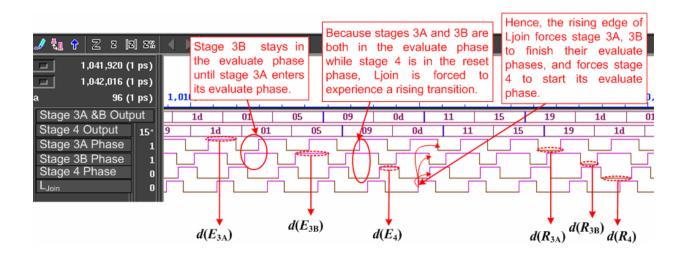

| Figure 3.16: Simulation snapshot of the prototype S-SRSL join pipeline.                                          | 71   |

| Figure 3.17: Simulation results of $d(L^+)$ , $d(R)$ , $d(E)$ , $\delta$ , and $P$ in the S-SRSL join pipeline   | 72   |

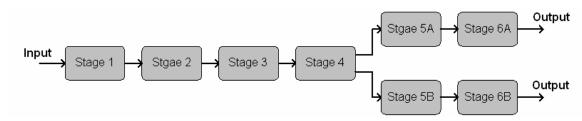

| Figure 3.18: Four-bit six-stage S-SRSL fork pipeline.                                                            | 72   |

| Figure 3.19: Simulation snapshot of the prototype S-SRSL fork pipeline                                           | 73   |

| Figure 3.20: Simulation results of $d(L^+)$ , $d(R)$ , $d(E)$ , $\delta$ , and $P$ in the S-SRSL fork pipeline   | 74   |

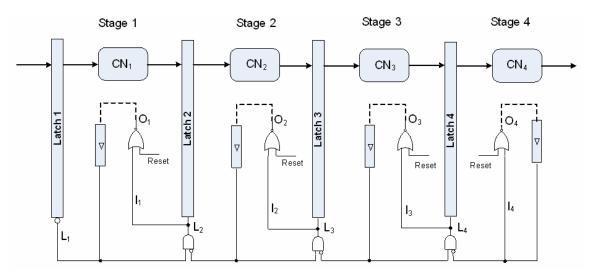

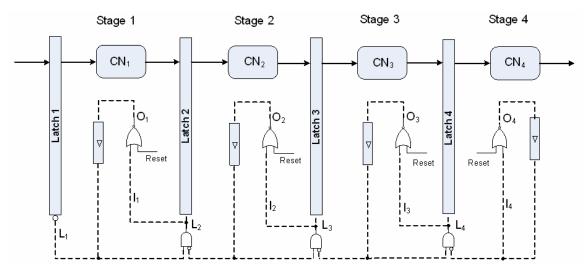

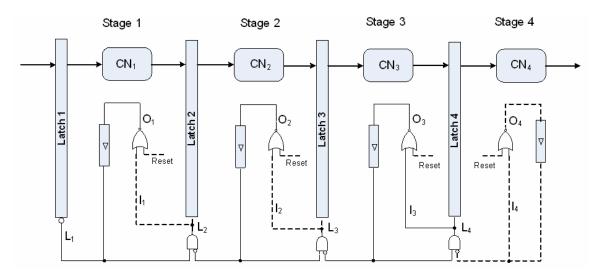

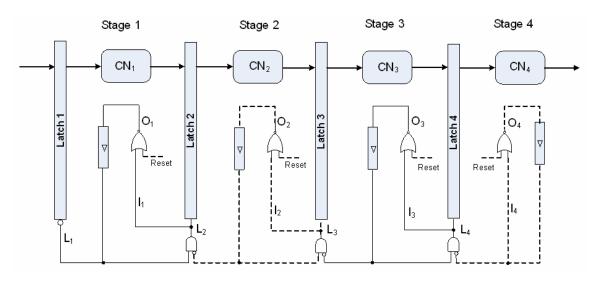

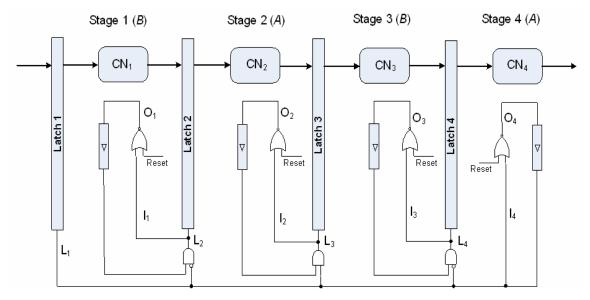

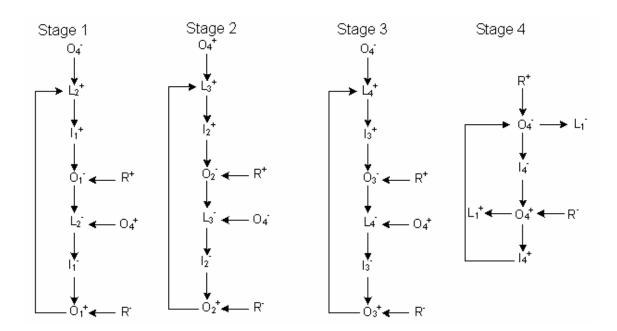

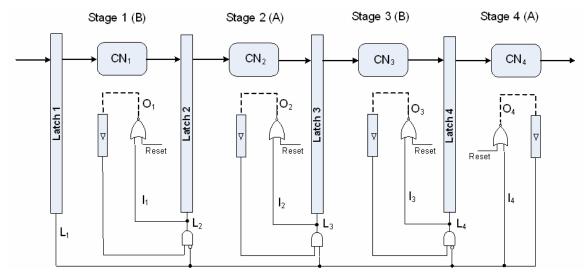

| Figure 4.1: A four-stage P-SRSL pipeline.                                                                        | 76   |

| Figure 4.2: STG of the P-SRSL pipeline shown in Figure 4.1.                                                      | 78   |

| Figure 4.3: Two execution cycles of a four-stage P-SRSL Pipeline                                                 | 81   |

| Figure 4.4: Structure of a join P-SRSL pipeline.                                                                 | 83   |

| Figure 4.5: STG of the P-SRSL join pipeline shown in Figure 4.3.                                                 | 84   |

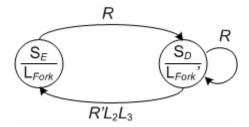

| Figure 4.6: Structure of a fork P-SRSL pipeline                                                                 | 85  |

|-----------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.7: STG of the P-SRSL fork pipeline shown in Figure 4.6                                                 | 86  |

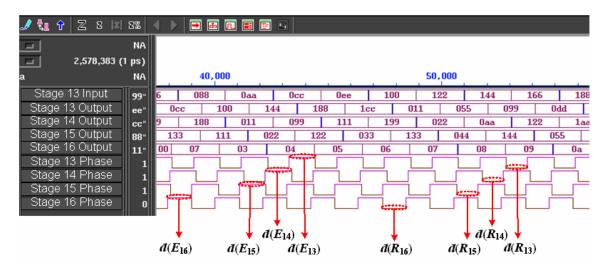

| Figure 4.8: Simulation snapshot of stages 13, 14, 15 and 16 in a 16-stage prototype P-SRSL                      |     |

| pipeline                                                                                                        | 89  |

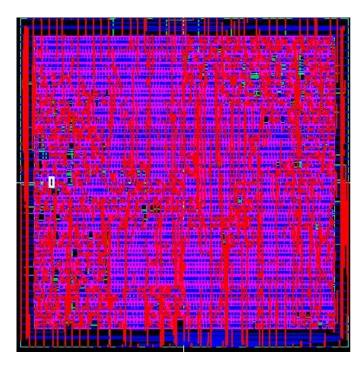

| Figure 4.9: Chip layout of the four-bit 16-stage P-SRSL pipeline.                                               | 95  |

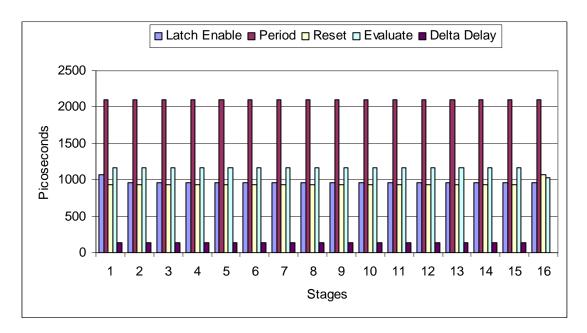

| Figure 4.10: Simulation results of $d(L^+)$ , $d(R)$ , $d(E)$ , $\delta$ , and $P$ in a P-SRSL pipeline         | 96  |

| Figure 4.11: Four-bit six-stage P-SRSL join pipeline.                                                           | 98  |

| Figure 4.12: Simulation snapshot of the prototype P-SRSL join pipeline.                                         | 98  |

| Figure 4.13: Simulation results of $d(L^+)$ , $d(R)$ , $d(E)$ , $\delta$ , and $P$ in the P-SRSL prototype join |     |

| pipeline                                                                                                        | 99  |

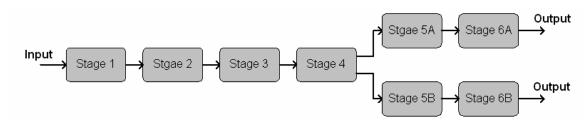

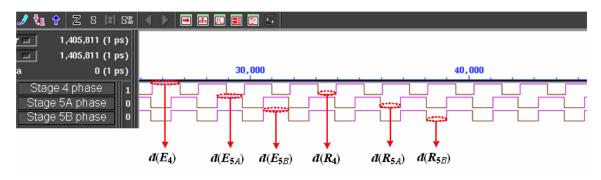

| Figure 4.14: Four-bit six-stage P-SRSL fork pipeline.                                                           | 100 |

| Figure 4.15: Simulation snapshot of the prototype P-SRSL fork pipeline.                                         | 100 |

| Figure 4.16: Simulation results of $d(L^+)$ , $d(R)$ , $d(E)$ , $\delta$ , and $P$ in the P-SRSL prototype fork |     |

| pipeline                                                                                                        | 102 |

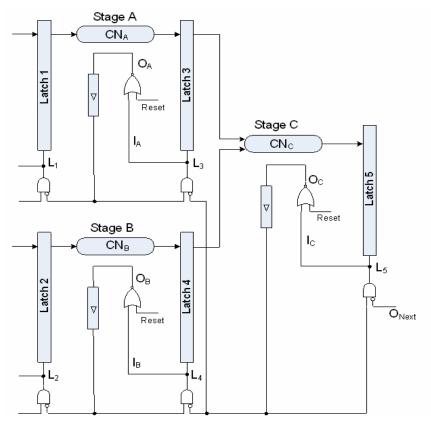

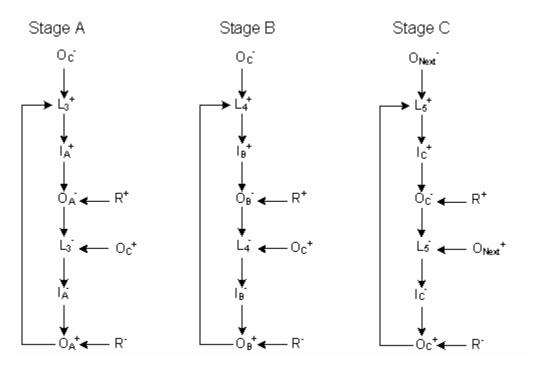

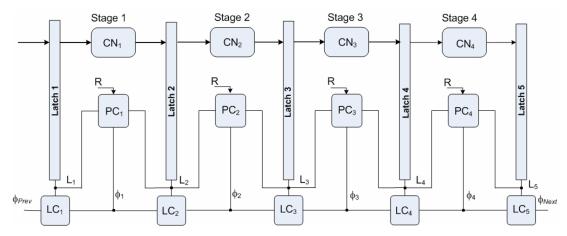

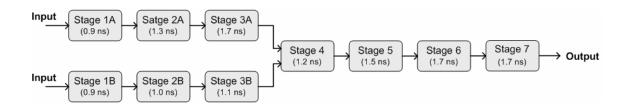

| Figure 5.1: A four-stage D-SRSL pipeline.                                                                       | 105 |

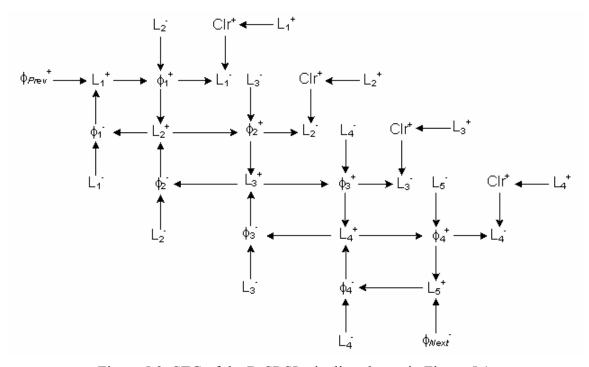

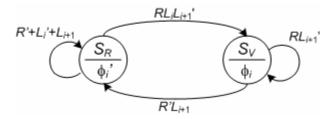

| Figure 5.2: STG of the D-SRSL pipeline shown in Figure 5.1.                                                     | 106 |

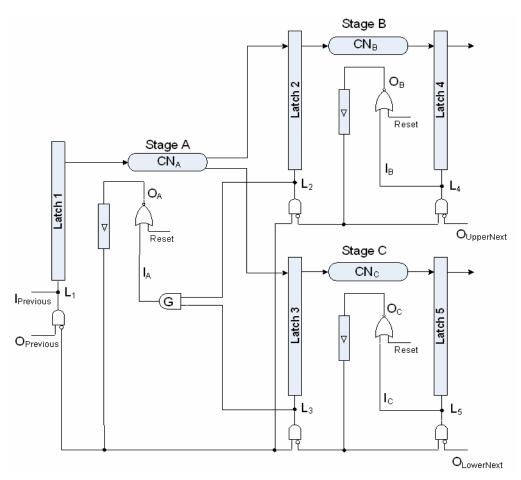

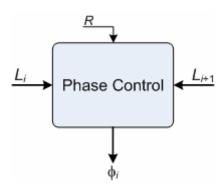

| Figure 5.3.:Phase control block.                                                                                | 107 |

| Figure 5.4: State graph of the PC block.                                                                        | 107 |

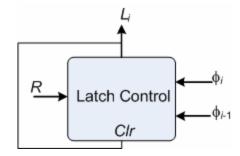

| Figure 5.5: Latch control block                                                                                 | 109 |

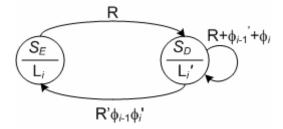

| Figure 5.6: State graph of the latch control block.                                                             | 109 |

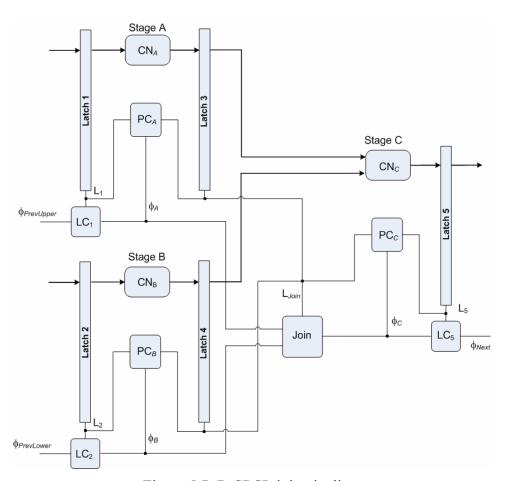

| Figure 5.7: D-SRSL join pipeline.                                                                               | 110 |

| Figure 5.8: STG of the D-SRSL join pipeline shown in Figure 5.7.                                                | 111 |

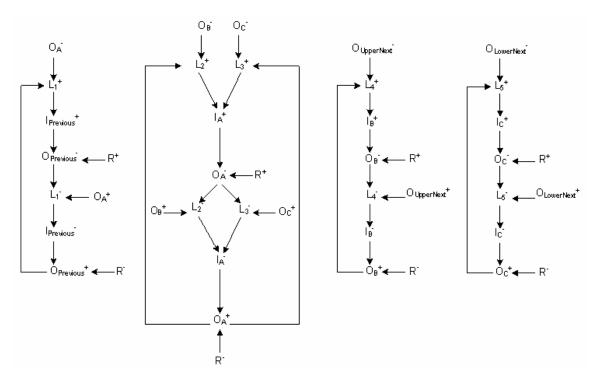

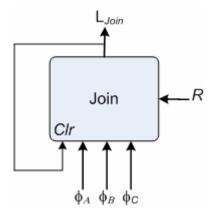

| Figure 5.9: The Join block                                                                                      | 111 |

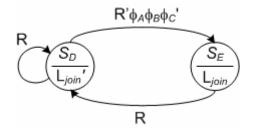

| Figure 5.10: State graph of the Join block.                                                              | 112   |

|----------------------------------------------------------------------------------------------------------|-------|

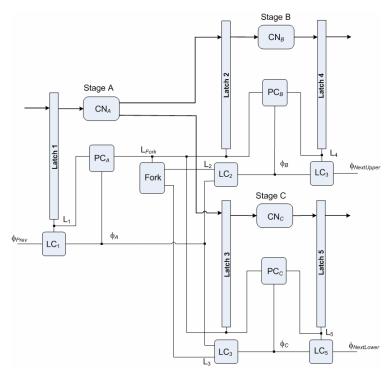

| Figure 5.11: Prototype D-SRSL join pipeline.                                                             | 112   |

| Figure 5.12: Simulation snapshot of the prototype D-SRSL join pipeline.                                  | 113   |

| Figure 5.13: D-SRSL fork pipeline.                                                                       | 115   |

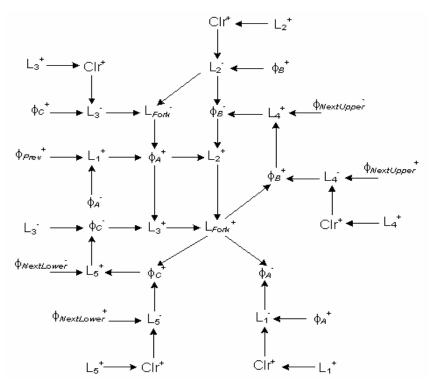

| Figure 5.14: STG of the D-SRSL fork pipeline shown in Figure 5.13.                                       | 115   |

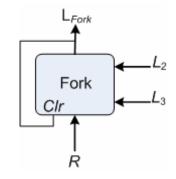

| Figure 5.15: Fork block.                                                                                 | 116   |

| Figure 5.16: State graph of the Fork block.                                                              | 116   |

| Figure 5.17: Prototype D-SRSL fork pipeline.                                                             | 116   |

| Figure 5.18: Simulation snapshot of the prototype D-SRSL fork pipeline                                   | 117   |

| Figure 5.19: Simulation snapshot of stage 14, 15 and 16 in a 16-stage prototype D-SRSL                   |       |

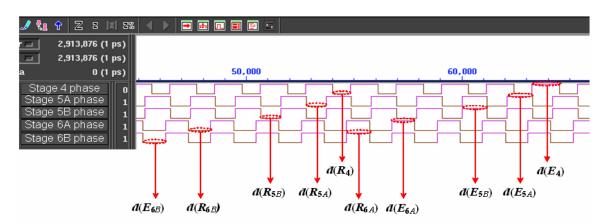

| pipeline                                                                                                 | 119   |

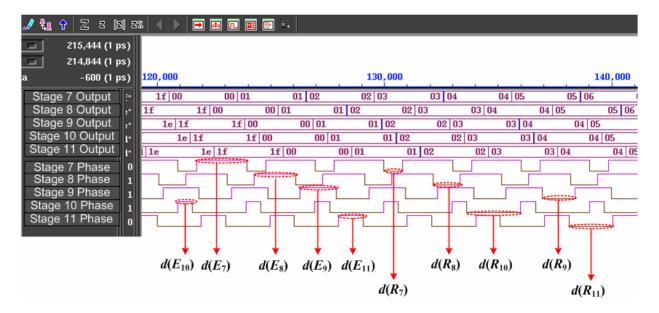

| Figure 5.20: Simulation snapshot of stages 7 through 11 in a 17-stage prototype D-SRSL                   |       |

| pipeline                                                                                                 | 124   |

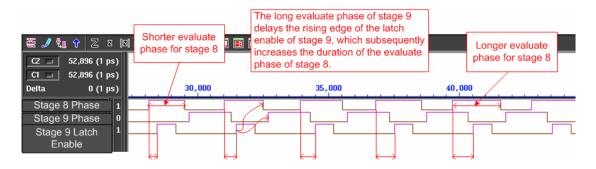

| Figure 5.21: Simulation snapshot of stages 8 and 9 in the 17-stage D-SRSL prototype pipeli               | ine.  |

|                                                                                                          | 125   |

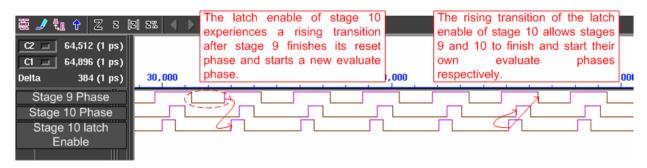

| Figure 5.22: Simulation snapshot of stages 9 and 10 in the 17-stage D-SRSL prototype pipe                | line. |

|                                                                                                          | 126   |

| Figure 5.23: Synthesized netlist of the PC block.                                                        | 132   |

| Figure 5.24: Synthesized netlist of the LC block.                                                        | 133   |

| Figure 5.25: Synthesized netlist of the Join block.                                                      | 134   |

| Figure 5.26: Synthesized netlist of the Fork block.                                                      | 136   |

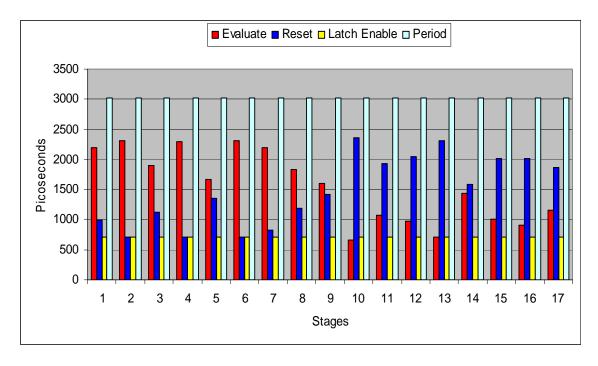

| Figure 5.27: Simulation results of $P$ , $d(E)$ , $d(R)$ , and $d(L^{+})$ in D-SRSL prototype pipeline 1 | 139   |

| Figure 5.28: Simulation results of P, $d(E)$ , $d(R)$ , and $d(L^{+})$ in D-SRSL prototype pipeline 2    | 140   |

| Figure 5.29: Simulation results of $P$ , $d(E)$ , $d(R)$ , and $d(L^+)$ in D-SRSL prototype pipeline3 | 141   |

|-------------------------------------------------------------------------------------------------------|-------|

| Figure 6.1: SRSL design flow.                                                                         | 144   |

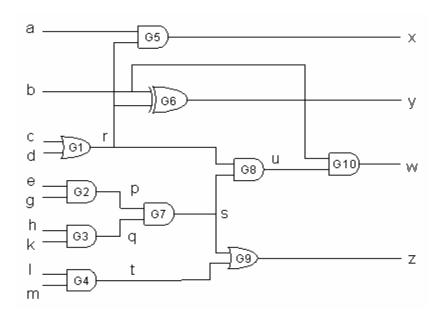

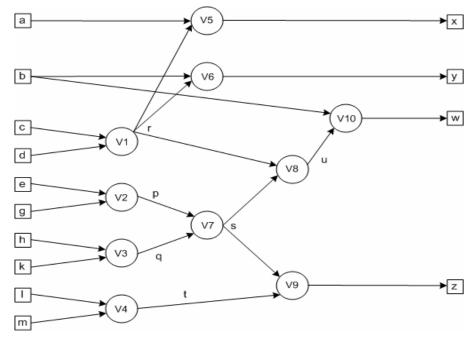

| Figure 6.2: Example of a Boolean network.                                                             | 147   |

| Figure 6.3: Boolean graph of the Boolean network shown in Figure 6.2.                                 | 149   |

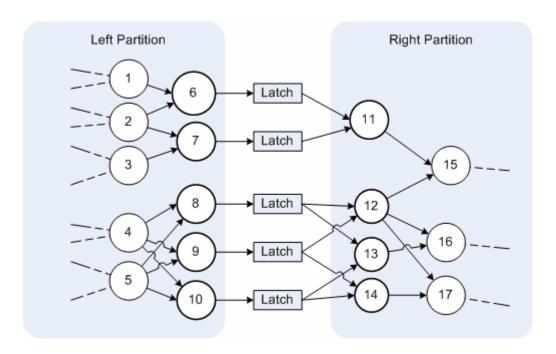

| Figure 6.4: Latch insertion between two neighboring pipeline stages                                   | 162   |

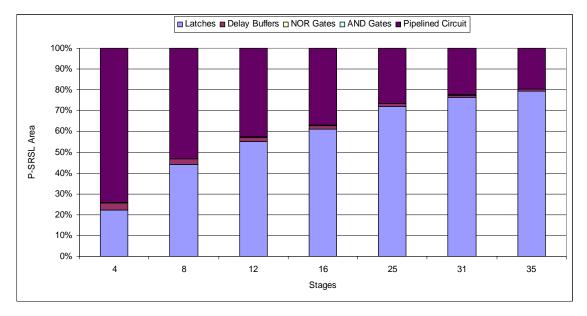

| Figure 6.5: P-SRSL area as a percentage of the pipeline area across different pipelines of the        |       |

| C6822 benchmark circuit.                                                                              | 171   |

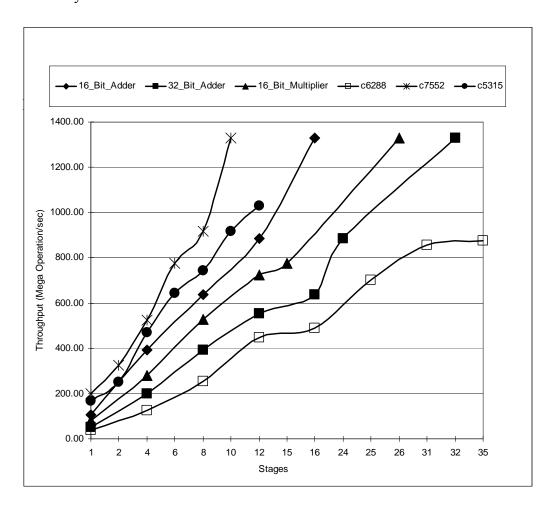

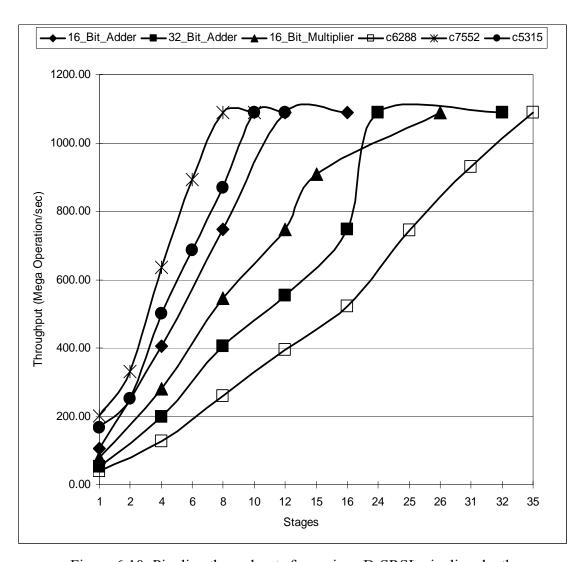

| Figure 6.6: Pipeline throughputs for various P-SRSL pipeline depths.                                  | 172   |

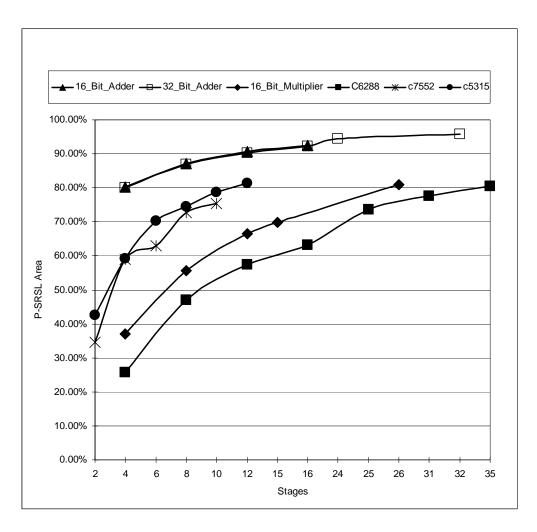

| Figure 6.7: P-SRSL area as a percentage of the pipeline area across various depth pipelines           | 174   |

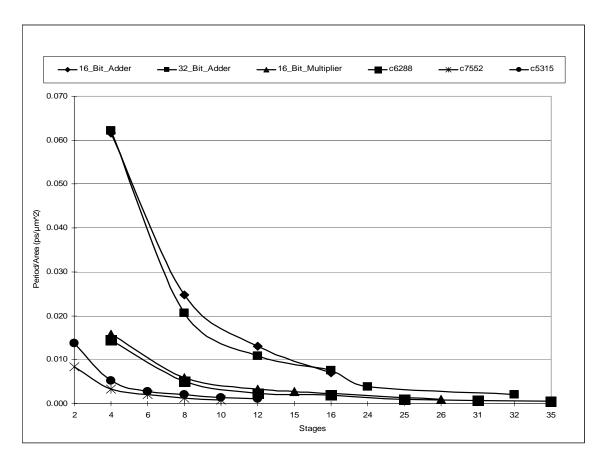

| Figure 6.8: Period over area ratios for different depths P-SRSL pipelines.                            | 176   |

| Figure 6.9: D-SRSL area as a percentage of the pipeline area across different pipelines of the        |       |

| C5135 benchmark circuit.                                                                              | 178   |

| Figure 6.10: Pipeline throughputs for various D-SRSL pipeline depths.                                 | 179   |

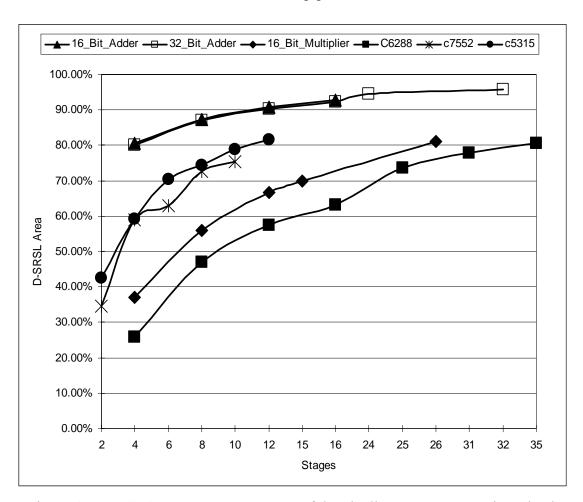

| Figure 6.11: D-SRSL area as a percentage of the pipeline area across various depth pipelines.         | . 181 |

# LIST OF TABLES

| Table 2.1: Summary of clockless design methodologies.           | 41  |

|-----------------------------------------------------------------|-----|

| Table 3.1: S-SRSL linear pipeline implementation                | 67  |

| Table 4.1: P-SRSL pipeline implementation.                      | 95  |

| Table 4.2: Comparison summary of the P-SRSL to S-SRSL pipeline. | 103 |

| Table 5.1: D-SRSL pipeline implementation.                      | 138 |

| Table 5.2: Gate area of a single D-SRSL stage.                  | 138 |

| Table 6.1: Experimental circuits.                               | 170 |

| Table 7.1: SRSL pipelining parameters.                          | 188 |

| Table 7.2: Fault handling in the three pipelines                | 189 |

#### **CHAPTER ONE: INTRODUCTION**

#### 1.1 Motivation

In this section, the rationale and the motivation behind the work undertaken in this dissertation is presented.

#### 1.1.1 The Clocking Problem

For three decades, digital design has been primarily dominated by clocked circuits since these circuits can be extremely robust and fairly easy to build. The use of a clock signal in clocked circuits introduces a level of abstraction in the time domain that hides many details about the temporal relations among circuit signals. This greatly simplifies the timing analysis of such circuits by reducing it to a mere analysis of the critical paths contained within the circuit. In a clocked circuit, a designer can simply define the combinational logic necessary to compute the given functions and surround it with latches. By setting the clock rate to a sufficiently long period, concerns about undesired signal transitions and the dynamic state of the circuit are eliminated [1]. The ease of design in clocked circuits has made them inevitably highly attractive to members of the commercial and research communities. In return, this interest has lead to a significant investment in the automation of designing these circuits thus culminating in the wide acceptance of a unified design methodology supported by widely available CAD tools. Along this evolution, the semiconductor industry has kept improving fabrication processes by shrinking silicon features to attain larger scale of integration. New

manufacturing techniques have made the integration of multi-million transistors onto the same die possible. As designers kept packing more devices into chips to take advantage of these large scales of integration, significant challenges have emerged the most important of which is the reliance on a clock signal to orchestrate logic operations across an entire chip. This challenge is known as the *clocking problem*. Today, this problem is considered at the root of three consequential fundamental obstacles in current VLSI design:

- (i) Design cycle time: Design time can be extended significantly by unexpected clocking problems. These extensions can disturb product schedules and shrink potential market profits.

- (ii) *Power budget*: The power budget allocated for a design initially may be completely underestimated if clocking problems are not addressed early in the design cycle. Even if they are, there is still no guarantee that the power budget will remain within initial estimates.

- (iii) Chip area: To overcome the technical difficulties imposed by the distribution of the clock to different parts of a chip, substantial silicon area has to be sacrificed to support this distribution. As known in the economics of the semiconductor industry, area cost can add up to the fixed cost of producing each chip unit.

#### 1.1.2 Growing Importance of Clockless Circuits

Motivated by the gravity of the clocking problem and its severe consequences, designers are currently considering other circuits which can operate without a clock.

These circuits are known as *clockless circuits* [1]. Although considered esoteric by most digital designers, these circuits have been subject to intensive investigation for some time. While clockless circuits have some disadvantages, there is wide agreement among researchers that their well known advantages make them suitable to overcome the clocking problem. Unfortunately, at this time, there is no unified established design methodology to support the design and verification of clockless circuits although a plethora of ad-hoc design methodologies have been proposed in the past for various classes of clockless circuits [2-10]. In fact, this variety of design methodologies triggered strong reluctance from digital designers to consider clockless circuits as viable alternatives. As a result, since existing CAD tools have been intended for clocked designs, it would be reasonable to adapt them for clockless designs considering the massive investments that have been spent on the developments of these tools. An ideal solution to leverage these investments would be a design methodology that would exploit existing CAD tools as much as possible and deviate from them as little as possible. Even by adopting such a methodology, one quickly realizes that only a handful of clockless circuits can be designed and verified using this adopted methodology. For instance, most of the pipeline-based clockless techniques, such as micropipelines, are not adequate to synthesize large data paths. These clockless pipelines, often implemented at circuit level, are so fine-grain that their application to pipeline data paths can have an unacceptable area overhead.

#### 1.1.3 Coarse-Grain Clockless Pipelining

Faced with this difficulty, it would make sense to (i) either select a few coarse-grain pipelining techniques among previously proposed clockless techniques, or (ii) propose new coarse-grain clockless pipelining techniques that seem supportable by existing CAD tools. A few attempts have been already undertaken in pursuing the former alternative [2, 11-12]. However, if the latter alternative is pursued, the best place to transform a clocked design into a clockless one is at the gate level where minimum disruption of the design flow supported by existing CAD tools is achievable. By doing so, the synthesis step of the clocked gate netlist from the initial register transfer level (RTL) model in the design flow is completely preserved. The obtained clockless gate netlist can be mapped using technology mappers packaged in existing CAD tools, and standard cell libraries which do not contain any specially designed handshaking components. In addition, the same gate netlist can be simulated using any existing simulators. Furthermore, the proposed clockless design technique is of sufficient granularity as to not impose a high area overhead.

Based on the rationale of the second alternative, this dissertation presents a novel clockless design technique highly adaptable for existing CAD tools. This technique can be incorporated within existing CAD tools without altering their design flow. This design technique is used to develop three coarse-grain pipelining techniques with distinct control mechanisms, which can be used to transform a clocked gate netlist into a highly pipelined clockless gate netlist based on data rate and area cost specifications. The remainder of this chapter reviews the design methodology of clocked circuits in section 1.2. In section

1.3, a review of the limitations of clocked circuits is presented while section 1.4 introduces several classes of clockless circuits. Section 1.5 gives an overview of the design methodologies used in synthesizing clockless circuits while section 1.6 presents the contributions of this dissertation. Finally, section 1.7 shows an overview of the dissertation.

#### **1.2 Design Methodology in Clocked Circuits**

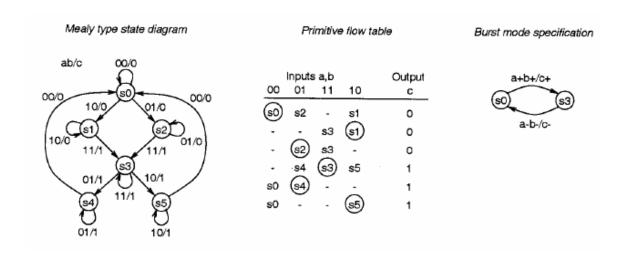

Today, the design methodology of clocked circuits is widely accepted and supported by existing CAD tools. As shown in Figure 1.1, this methodology consists of (i) specification and modeling, (ii) verification, (iii) synthesis, (iv) technology mapping, and (v) physical layout.

#### 1.2.1 Specification and Modeling

A clocked circuit is specified in both general and specific terms that provide design targets such as functionality, speed, and size. These specifications are used to create an abstract, high level model using a high level hardware description language (HDL). The abstract model contains information on behavior of each block and the interaction among the blocks in the circuit [13]. VHDL and Verilog HDL are the most widely used HDLs in the digital design community to model these circuits.

#### 1.2.2 Verification

The HDL model is subjected to extensive verification wherein the design is checked to ensure correct functionality. Simulation is the most widely used form of verification. During simulation, test benches are created and applied on the design to validate its functionality against initial requirements.

#### 1.2.3 Synthesis

The synthesis step consists of creating a gate implementation of the specified model. This step can be performed as follows:

- (i) Translate the abstract Register Transfer Level (RTL) design description to register elements and combinational logic.

- (ii) Optimize the combinational logic by minimizing, flattening and factoring the resulting Boolean equations.

- (iii) Translate the optimized logic level description to a generic gate netlist using cells from a generic library.

Figure 1.1: Design flow of clocked circuits [14].

#### 1.2.4 Mapping

In this step, the optimized generic gate netlist is mapped to a specific standard cell library in a given technology. The mapping must satisfy area and timing constraints specified earlier in the design flow. After mapping, simulation can be performed on the mapped gate netlist in order to compare its results with the results obtained from the simulation of the model specified in the modeling step of the design flow.

#### **1.3 Limitations of Clocked Circuits**

In nanometer technology processes, circuit designers can build super fast transistors capable of processing data in several steps during the time it takes a wire to carry a signal from one side of a chip to the other [15]. Keeping operation frequency identical across the chip area requires substantial effort in distributing the clock to the various areas of the chip. To do so, the clock distribution at chip level can generate numerous costly difficulties that exacerbate the three fundamental obstacles encountered in current VLSI design.

#### 1.3.1 Clock Frequency

To insure correct synchronization of the latches across the chip, designers assume a clock frequency based on the worst case propagation delay through the slowest path in the design [16-18]. This pessimistic estimation usually accounts for maximum clock skew, and process variations due to process, voltage, and temperature. The margin allotted for these variations tend to increase as nanometer processes are adopted.

#### **1.3.2 Timing Closure**

For high performance designs, timing closure can become a major bottleneck before tape out time. In principle, the delay through the slowest paths, augmented with the safety margins accounting for process variation and skew, should be less than the target clock period. Often, design teams realize that the target is not met after layout in spite of the extensive simulations at different levels of the design flow. Designers are forced then to iterate numerous times through the design flow cycle in order to meet the target. These iterations can cause costly delays in production schedules.

#### 1.3.3 Power Implications

It has been established that the clock network can consume a sizable portion of the chip power budget. This phenomenon is highly acute in high-capacity Field Programmable Gate Arrays (FPGA) chips [19]. In fact, the clock is continually switching unless clock gating techniques are used. This means that latches are dissipating heat whether they are processing data or not [17]. Clock gating techniques can alleviate the problem to some degree at the expense of added design complexity and a drop in performance [20, 21].

#### **1.3.4 Area Implications**

Several researchers have proposed advanced approaches to alleviate clock distribution and de-skewing problems. However these approaches can, in some cases, impose a substantial cost in added area. There were reported instances in which a

complex clock-driver network on a commercial microprocessor was designed to keep the clock skew within 300 picoseconds. However, this resulted in a circuit that occupied 10% of the chip area and consumed more than 40% of the total power budget [22]. In semi-custom designs, the clock network can occupy an area that is even larger reaching 30 to 40% of the total chip area.

#### 1.3.5 Noise Margins

Beside increases in area and power cost, clock networks are highly noisy. By keeping all signal transitions in lock step, the clock network creates the worst environment to suppress noise. Similar to data signals, current transitions on clock lines become synchronized to some degree thus maximizing the AC component of any generated noise in relation to the harmonics of the clock frequency.

#### 1.3.6 Multiple Clock Domains

With increasing numbers of clock domains in current chips, concerns are growing about synchronization of cross-domain signal paths. A complex communication system-on-chip can contain up to 300 such domains [23]. The synchronization of these domains requires proper placement of synchronizers at precise points in the design. Even with proper placement, there is no guarantee that all the bits of a domain-crossing bit vector in a cross-domain path signal will cross domain boundaries at the same time through these synchronizers. This is further complicated by the fact that clock frequencies across domains differ widely, which necessitates the insertion of FIFO buffers at various points in the design. Insertion of FIFO buffers raises sizing and correct

implementation issues. While synchronizer placement and buffer insertion can be performed manually, it is not advised in most cases since it is labor-intensive and highly prone to errors. Designers can overcome these difficulties if automatic tools for placement and verification were available. Unfortunately, there are no specialized tools to support these tasks on the market at this time.

#### **1.4 Clockless Circuits**

Clockless circuits are circuits that operate without the synchronization of a clock signal. Although numerous clockless circuits have been proposed before, they can nevertheless be classified based on a limited number of characteristics. The most important characteristic in distinguishing the underlying principle behind the operation of a clockless circuit is how signal delay is handled in order to insure the proper synchronization of the different components of the circuit. This assumption is known as the *delay model*. Based on this delay model, clockless circuits can be divided in five distinct classes of circuits.

#### 1.4.1 Self-Clocked Circuits

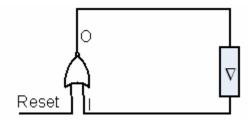

In general, *self-clocked (SC) circuits* consist of three components as shown in Figure 1.2 [24] [25]:

Figure 1.2: General architecture of SC circuits [25].

- (i) Clock logic: This component generates a clock pulse only whenever the state or output signals change. It is used to eliminate hazards and control state changes of the machine.

- (ii) Storage elements: These elements capture data by responding to the clock signal.

- (iii) Combinational logic: This component does not require special care to protect it from hazards. The clock component is chosen to be slow enough to allow outputs to settle before it is fed back to the combinational logic.

SC circuits are simple and attractive since they reduce the potential overhead due to the clock. In addition, they allow the realization of hazard-free logic based on the specification of finite state machines.

#### 1.4.2 Speed-Independent Circuits

Speed-independent (SI) circuits were introduced by David Muller in the 1950s [26]. These circuits operate correctly regardless of gate delays. In these circuits, wires are assumed to have zero or negligible delay. As a result, every fork in the circuit is assumed to be an isochronic fork causing only a negligible skew. An isochronic fork is a wire fork in which the delays on the branches of the fork are equal. If this delay model is assumed, an SI circuit works properly for all possible ordering of events associated with all possible and varying relative delays of the components of the circuit. SI circuits can be synthesized from Petri nets and signal transition graphs used in synthesizing clockless circuits.

#### **1.4.3 Delay-Insensitive Circuits**

Delay-Insensitive (DI) circuits are circuits which operate correctly with positive and unbounded delay in wires and gates [27]. In a bounded-delay model, it is assumed that a circuit will settle in a stable state as a response to an input if given enough time. Immediately after, a new input can be safely fed to the circuit. Micropipelines and burst mode circuits are examples of circuits whose operations are based on the bounded-delay model. However, in an unbounded delay model, no matter how long a circuit waits, there is no guarantee that the input will be properly absorbed. This required some kind of

handshaking protocol between sender and receiver components of the circuit. The sender sends data and waits on an acknowledge signal from the receiver. The latter receives the data and sends the acknowledge signal back to the sender. By managing these signal exchanges, handshaking protocols can make circuits highly immune to hazards. Unfortunately, the number of DI circuits, built out of simple gates and operators, is quite small. In fact, it has been proven that almost no useful DI circuits can be built if one is restricted to a class of simple gates and operators [28]. However, many practical DI circuits can be built if one allows more complex components [29].

Because the unbounded delay model is too restrictive, it can be slightly relaxed by allowing bounded delays on wire forks or using isochronic forks. In adopting this modified unbounded delay model, DI circuits can be refined further into a subclass of *quasi-delay-insensitive (QDI) circuits* [27]. In contrast to QDI circuits, delays on the different fork branches of DI circuits are completely independent and may vary considerably. DI circuits can be built from Null Convention Logic, handshake-based circuits, and extended delay insensitive clockless models.

#### 1.4.4 Self-Timed Circuits

In [30], *self-timed (ST) circuits* are described as interconnections of parts called "elements". Each element is contained in an "equipotential region" in which wires have negligible or well-bounded delay. An element itself may be an SI circuit, or a circuit whose correct operation relies on the use of local timing assumptions. However, no timing assumptions are made on the communication between regions; that is,

communication between regions is delay-insensitive. Null Convention Logic (NCL) is considered as ST circuits.

#### 1.4.5 Self-Resetting Circuits

Earlier implementations of self-resetting circuits rely on circuit techniques to realize self-resetting behavior. For instance, self-resetting CMOS (SRCMOS) operates on signals represented as short-duration pulses rather than as voltage levels [31]. After a logic gate processes a set of input pulses, a reset signal is activated to restore the logic gate to a state in which it is ready to receive another set of input pulses. The input pulses must arrive at the same time and must overlap with one another for a minimum duration. Several reset schemes have been proposed before. Jung has proposed two techniques to increase the robustness and efficiency of SRCMOS circuits [32]. The first technique uses a logical structure to properly sequence the reset and evaluates modes of an SRCMOS logic stage without having to rely on a timing chain. The second technique uses a pulse stretcher so that input pulses of widely different arrival times can be properly combined at a given stage logic. Beside Jung schemes, Dooply has proposed locally self resetting CMOS where the reset signal for each stage is generated locally [33]. This technique is based on single-rail domino logic stages in which the reset signal is obtained by sending the stage own output through a short delay chain.

#### 1.5 Design Methodology in Clockless Circuits

Various design methodologies have been proposed in the past to synthesize clockless circuits. In general, there is a close relationship between the theoretical model

used to represent the behavior of clockless circuits and the tools used to model this behavior. Given this relationship, design methodologies for clockless circuits can be classified as follows:

- (i) Graph-based methodologies: These methodologies require the modeling of the circuit as Petri nets (PNs) or signal transition graphs (STGs). Circuits are synthesized from these graphs and mapped onto general C-elements and complex gates [3-8].

- (ii) *HDL-based methodologies*: These methodologies require the modeling of a circuit using an existing HDL [2, 9-10], [34-37]. The model is translated to a netlist that can be mapped onto a standard cell library.

- (iii) *Script-based methodologies*: In these methodologies, circuit behavior is described using algebraic expressions and saved as scripts [38-41]. The scripts are expanded into graphs from which circuits are synthesized and mapped.

- (iv) Compilation-based methodologies: These methodologies require the use of high level programming languages, some of which are proprietary, designed to express concurrency, handshaking, and sequencing [42-45]. The source code of the program describing the circuit behavior is parsed and compiled into a circuit containing pre-designed components which support the programming language constructs for concurrency, handshaking, and sequencing.

Given this diversity of design methodologies, it is understandable why most designers are reluctant to delve in clockless logic. This reluctance can be justified by the

fact that adopting any methodology requires some amount of retraining and retooling on the part of the designers. This reluctance is reinforced further by a visible lack of simulation and verification tools at all levels of the design flow that is suggested by these methodologies. In addition, proprietary cell libraries are necessary to map circuits using some of these methodologies. What most designers are seeking instead is a single uniform design methodology that is (i) familiar, (ii) widely accepted, (iii) tested and proven by a long usage experience, (iv) and may use proprietary resources as little as possible. Such a methodology has been already in use for some time to produce clocked circuits in the form of successful commercial CAD or EDA tools. In this case, the design methodology of these CAD tools can be used to support clockless design techniques that can be specified and modeled using current HDLs. The obtained HDL models can be verified through simulation. Next, the HDL models can be synthesized into clockless gate netlist which can be mapped using standard cell libraries found in the realization of clocked circuits. Note that, in general, these libraries do not contain any special cells designed to handle events specific to clockless logic such as concurrency, rendez-vous, and handshaking. By implementing these clockless techniques using existing CAD tools with a minimum modification to the design flow of these tools, the need for relearning and retooling can be eliminated.

#### **1.6 Contributions of the Dissertation**

This dissertation presents a new clockless design technique suitable for existing CAD tools. Specifically, its contributions are as follows:

- (i) A new self-resetting logic technique, called *self-resetting stage logic* (SRSL), in which the computation of a block is reset periodically from inside the block. This automatic self-resetting behavior manifests itself in the form of a periodic oscillation of the block driven by a reset loop similar to an internal clock. This simplifies the synchronization scheme by using a uni-directional communication channel between senders and receivers.

- (ii) A pipelining technique based on SRSL controlled at stage level, called *stage-controlled self-resetting stage logic* (S-SRSL). In S-SRSL, the control of the communication between stages is performed between each pair of stages.

- (iii) A pipelining technique based on SRSL controlled at pipeline level, called *pipeline-controlled self-resetting stage logic* (P-SRSL). In P-SRSL, the control of the communication between stages is performed by the last stage in the pipeline whereby the oscillation of the last stage drives the oscillatory behavior of the other stages in the pipeline.

- (iv) A coarse-grain pipelining technique called *delay-tolerant self-resetting stage* logic (D-SRSL) that is similar to S-SRSL pipelining where data flow across stages is orchestrated by each pair of neighboring stages. Whereas S-SRSL and P-SRSL pipelines require that intra-stage delay and communication scheme be identical and uni-directional respectively, D-SRSL can tolerate stages with arbitrarily different delays by using a bi-directional communication scheme.

- (v) Graph-theoretic and analytical formulations of a combinatorial problem encountered in the synthesis of SRSL pipelines. Specifically, this problem

consists of synthesizing an SRSL pipeline from a gate netlist with a minimum area overhead based on a specified data rate. The analytical formulation consists primarily of an integer programming problem.

(vi) Since the size of the integer programming problem formulation is significantly large, and subsequently solving it using analytical approaches is impractical, a new heuristic algorithm is proposed to solve it. Because latches tend to occupy a large silicon area, the main goal of the algorithm is to minimize the area occupied by inter-stage latches without violating any timing constraints. This algorithm accomplishes this by executing two successive phases where phase I assigns each gate in the gate netlist to a specific pipeline stage whereas phase II minimizes the number of inter-stage latches between every pair of neighboring pipeline stages.

#### 1.7 Overview of the Dissertation

This dissertation consists of six chapters beside the current chapter. Chapter 2 reviews the main clockless design methodologies and evaluates their suitability for existing CAD tools. Chapter 3 explains the underlying concepts behind SRSL and introduces S-SRSL pipelines followed by an analysis of the experimental results conducted on these pipelines. Chapter 4 presents P-SRSL pipelines and the experiments conducted on these pipelines followed by a comparison of S-SRSL and P-SRSL pipelines. Chapter 5 presents D-SRSL pipelines and analyzes the results obtained from the prototyping experiments conducted on these pipelines. Chapter 6 introduces the synthesis problem of SRSL pipelines, presents the formulation of the combinatorial

problem stemming from the synthesis of SRSL pipelines, and describes the synthesis algorithm implemented for this purpose. Finally, Chapter 7 concludes the dissertation and suggests avenues for future work.

# CHAPTER TWO: RELATED CLOCKLESS DESIGN METHODOLOGIES

This chapter reviews the main clockless design methodologies and the available tools that support each design methodology as reported in the literature. Section 2.1 presents methodologies based on Petri nets while section 2.2 presents methodologies based on signal transition graphs. Section 2.3 presents micropipelines while section 2.4 presents Null Convention Logic. Burst mode machines are described in section 2.5. Section 2.6 describes handshake circuits while section 2.7 describes the extended delay insensitive model. Finally, section 2.8 gives a summary of the chapter and compares the listed design methodologies with the proposed SRSL technique.

# 2.1 Petri Nets

Petri Nets (PNs) is a formal syntax and semantic representation suitable to specify causality, concurrency and choice between events. PNs can be a powerful tool to model clockless circuits [3, 46, 47]. Formally, a PN is a triple N = (P, T, F) where:

- (i) P is a finite set of places.

- (ii) T is a finite set of transitions:  $T \cap P = \emptyset$ .

- (iii)  $F: F \subseteq (P \times T) \cup (T \times P)$  is the flow function.

Transitions in PNs represent events in the system such as a request to access a memory bank in a multi processor system. On the other hand, places in PNs represent placeholders for needed resources and conditions necessary for events to occur. Figure 2.1 shows a C-element and its surrounding environment while figure 2.2 shows its PN specification.

Figure 2.1: C-element and its surrounding dummy environment [27].

Figure 2.2: The PN of the C-element shown in Figure 2.1 [27].

The PN is marked with tokens on the input places to the a+ and b+ transition. The a+ and b+ transitions may fire in any order. The c+ transition becomes enabled to fire when both a+ and b+ transitions fire [27]. Previously developed methods for PN-based synthesis of clockless circuits can fall in one of the following two approaches [48]:

- (i) A direct, syntax oriented, translation of the PN into logic.

- (ii) A translation of the PN into a *signal transition graph* (STG) followed by the synthesis of a circuit from the obtained STG.

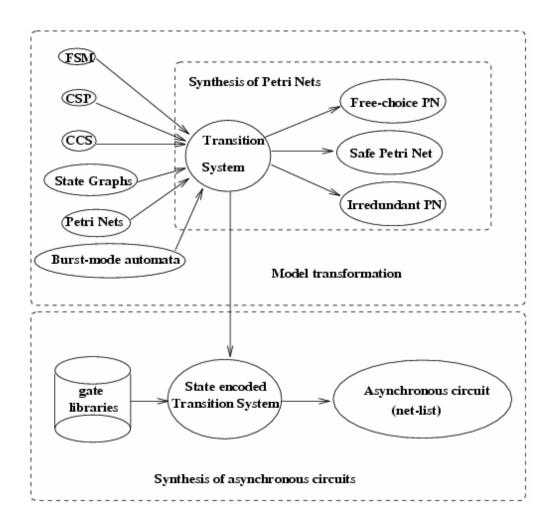

The approach in (i) can be used to obtain implemented circuit in three steps. In the first step, a net model is extracted from the circuit model described in the PN while in the second step the net model is transformed into an equivalent net where each signal event is associated with a unique transition. Finally, the net is translated into the circuit that can be constructed from a standard set of event-based modules. So far, most previous research focused on the synthesis of the clockless circuits from STGs. Petrify belongs to category (i) of synthesis tools. It is mainly a research tool used in the synthesis of clockless controllers from PN specifications [4]. Petrify reads a specification PN and generates a reduced version of the initial PN where the latter is used to produce an optimized netlist of a clockless controller based on a target gate library. Recent improvements to Petrify consist of generating circuits from STGs instead of solely PN specifications. These improvements help Petrify fall in category (ii) of synthesis tools. As shown in Figure 2.3, Petrify can be used as a standalone synthesis tool. The design flow shown in the figure starts from a specification of the system behavior described by a PN, state graph, or finite state machine (FSM) in a textual format. Petrify performs logic synthesis on the construction state graph in which each reachable state is assigned a binary code representing the value of each signal. This allows the generation of a circuit using logic minimization techniques. The circuit can be constructed from C-elements and generic complex gates. If these generic complex gates are not available in the gate library, Petrify performs combinational and sequential decomposition of the logic into primitive gates that are available in the target gate library. The PNs accepted by Petrify can also be interpreted as behavior-specifying STGs of clockless controllers.

Figure 2.3: Petrify framework.

Since Petrify uses symbolic techniques to represent the state space, it can synthesize large controllers whose specifications consist of more than 20 signals if well-structured behavior is specified. However, previous experiments showed that Petrify is not appropriate for data-path synthesis since it cannot always guarantee a correct synthesized netlist [5]. Although Petrify starts its synthesis process from a PN or STG specification, the latter two representations are not widely used among digital designers. Specifying system behavior in these representations can be challenging if the designer does not have proper knowledge on how to use them. In addition, it is difficult to integrate Petrify with existing simulation and synthesis tools since it is intended to

operate as a stand-alone tool. Furthermore, Petrify does not offer any capability to support verification or simulation of the PNs or STGs before they are synthesized into circuits. Petrify support mapping the synthesized netlist to C-element and complex gates assuming that the target cell library contains such elements and gates.

#### **2.2 Signal Transition Graphs**

Signal transition graphs (STGs) are a subset of PNs. When PNs are used to model clockless circuits, it is sometimes necessary to relate transitions to events on signal wires [6-8]. Several PN variants have been proposed to relate these transition events including M-nets, I-nets, change diagrams, and STGs. An STG is a labeled safe PN which is modeled as a 7-tuple  $(P, T, F, M_0, N, s_0, \lambda_T)$ , where:

- (i) P, T, F are defined in the PN section.

- (ii)  $M_0$  is the initial marking representing the function that maps the places to natural numbers.

- (iii)  $N = I \cup O$  is the set of signals where I is the set of the input signals and O is the set of the output signals

- (iv)  $s_0$  is the initial value for each signal in the initial state.

- (v)  $\lambda_T : T \to N \times \{+, -\}$  is the transition labeling function.

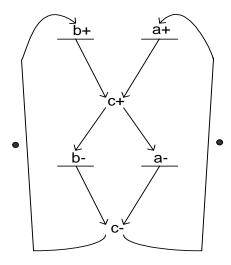

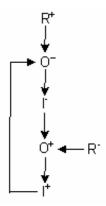

In an STG, each transition is labeled with a rising transition, s+, or a falling transition, s-. An s+ label indicates that the transition corresponds to a  $0 \rightarrow 1$  transition on the signal wire s. On the other hand, an s- label indicates that the transition corresponds to a  $1 \rightarrow 0$  transition on s. Figure 2.5 shows the STG specification for the C-

element shown in Figure 2.1. This specification can be directly derived by following the causality arrows defined in the timing diagram shown in Figure 2.4 [27].

Figure 2.4: Timing diagram of the C-element shown in Figure 2.1.

Figure 2.5: STG of the C-element shown in Figure 2.1.

The first step in STG-based synthesis is the generation of a *stage graph* (SG). After obtaining an SG, there are two approaches to implement a circuit. In the first approach, if the SG is free of *complete state coding* (CSC) violations, a Boolean equation is derived and directly implemented with an SI circuit using generalized C-elements. A CSC violation represents the situation in which different states of a state machine are encoded with the same binary code although they imply contradictory next values for at least one of the output signals. However, in the second approach, specific state encoding

methods are applied to get a realizable STG. The Boolean equation of the newly obtained realizable STG can be used to realize a circuit directly using generalized C-elements. In general, the derived Boolean equation may not be implementable as a single complex gate. In that case, logic decomposition is applied to transform the equation into smaller equations, which can be implemented using simple gates. Figure 2.6 shows the design flow to synthesize clockless circuit from STGs [47]. Petrify can be used to synthesize circuits from STG specifications and support mapping the synthesized netlist to C-elements and complex gates.

Figure 2.6: Synthesis flow of clockless circuits from STG specifications.

#### 2.3 Micropipelines

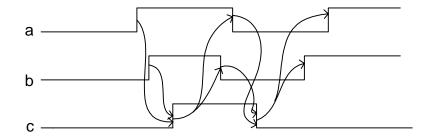

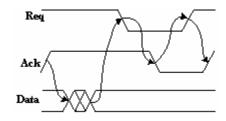

Microppipelines consist of event-driven elastic pipelines [49]. These pipelines can realize fast and efficient implementations of arithmetic circuits by using a two-phase handshake protocol instead of a four-phase handshake protocol. Both protocols are shown in Figure 2.7. The implementation structure for a micropipeline is the controlled first-in first-out (FIFO) queue, shown in Figure 2.8, in which the gates labeled C are Muller C-elements. In addition, the registers in the Figure 2.8 are level-sensitive latches that respond to transitions on two inputs instead of responding to a single clock wire as is done in clocked latches.

(a) Two-phase handshake protocol.

(b) Four-phase handshake protocol.

Figure 2.7: Micropipeline handshake protocols.

Figure 2.8: Basic structure of a micropipeline.

These latches are initially active by passing data directly from data inputs to data outputs. When a transition occurs on the *capture* wire of the latch, labeled C, data is no longer allowed to pass, and the current value of the outputs is statically maintained. Once a transition occurs on the *pass* input, labeled P, data is again allowed to pass from input to output, and the cycle repeats. The Cd and Pd ports on the latch simply keep copies of the control signals that are delayed so that the register completes its response to the control signal transitions before they are sent back out.

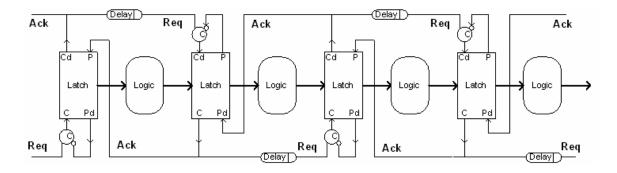

*Pipefitter* has been proposed as a tool for automated synthesis of micropipelined clockless circuits consisting of a 4-phase control unit and a clockless data path with matched delays [9, 10]. The synthesized control unit supports concurrency, sequencing

and choice. As shown in Figure 2.9, Pipefitter's framework uses Verilog HDL as the output format for intermediate representations of both control unit and data path.

Figure 2.9: Pipefitter framework.

Based on this representation, designers can use existing EDA tools for most design phases, including synthesis, simulation and layout. The Verilog source code is optimized and split into two separated databases: one for the control unit and the other for the data path. After the Verilog netlist is generated, a standard logic synthesis tool can be used for technology mapping. Pipefitter can automatically generate a netlist of matched delays for each block in the data path. In addition, it can generate the netlist of the control unit by calling Petrify. By merging the netlist of both control unit and data path, a complete netlist is constructed. At this point, the netlist can be placed and routed in order to produce a final layout. While Pipefitter can be integrated with existing EDA tools better than Petrify can, its shortcomings stems from the fact that it supports only a

restricted subset of Verilog statements. Pipefitter uses existing EDA commercial tools for simulation, and the final standard netlist can be mapped to a standard cell library.

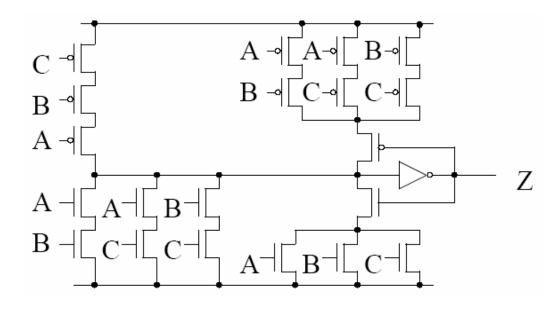

# 2.4 Null Convention Logic

The NULL Convention Logic (NCL) synthesis flow is a framework that integrates data transformation and control into a single expression thus yielding delay-insensitive circuits [50]. NCL uses threshold gates with hysteresis to provide the basic building block of NCL designs. Threshold gate inputs and outputs can be in one of two states, DATA or NULL. DATA corresponds to a logic-1 voltage level while NULL corresponds to a logic-0 voltage level in the normal logic mapping [34, 36]. The operation of NCL gates is based on two primary properties of M-of-N gate, namely threshold behavior and hysteresis behavior. Threshold behavior requires that the output becomes DATA if at least M of the N inputs are DATA. On the other hand, hysteresis behavior requires that the output changes only after a sufficiently complete set of input values have been established. In the case of a transition to DATA, the output remains at NULL until at least M of the N inputs become DATA. On the other hand, in the case of a transition to NULL, the output remains at DATA until all N inputs become NULL. Since these gates use two-value logic, as traditional Boolean logic does, they can be constructed with traditional CMOS, Bipolar, or even more exotic processes [36]. Figure 2.10 shows a 2-of-3 threshold gate that fires when two of it is inputs are active and return to null when all of the inputs are null.

Figure 2.11 shows a half adder circuit in Boolean logic with its clock while Figure 2.12 shows its NCL counterpart [37].

Figure 2.10: NCL 2-of-3 threshold gate.

Figure 2.11: A half adder circuit in conventional Boolean logic.

Although NCL can use any delay insensitive encoding, it uses mostly a dual rail one-hot encoding in which the presence of DATA on one of two wires indicates a TRUE state while the presence of DATA on both wires indicates a FALSE state. Unlike previously described clockless approaches, the algebraic theory behind NCL makes it extremely applicable to high-level design methodologies such as RTL simulation, RTL

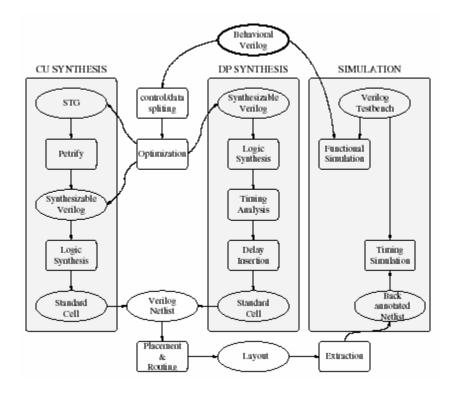

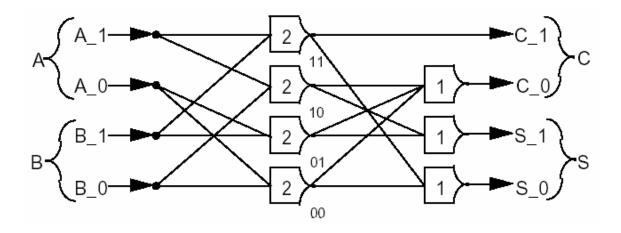

synthesis, and gate optimization. Motivated by these advantages, Theseus Logic has developed a synthesis and simulation flow based on existing, off-the-shelf, EDA tools from industry leaders such as Synopsys and Mentor Graphics. Based on this flow, NCL designers can specify their designs in VHDL or Verilog and simulate them using existing EDA tools. As shown in Figure 2.13, the NCL flow is centered around two primary synthesis steps [51, 52]:

Figure 2.12: NCL half adder circuit.

- (i) Translate the HDL code into a 3NCL netlist: This stage starts with an HDL source code written with 3NCL, a single-rail multi-valued representation of the initial NCL. The synthesis tool performs HDL optimizations and outputs an unmapped VHDL dataflow description expressed by AND and INV assignments. This dataflow description is referred to as a 3NCL netlist.

- (ii) Optimize the 3NCL netlist into a 2NCL netlist: the second stage expands the intermediate 3NCL netlist into a fully dual-rail 2NCL netlist by overloading all AND and INV assignment as Delay-Insensitive Minterm Synthesis (DIMS) dual rail type assignments. This expansion is described in a VHDL

package. At this point, multilevel minimization of Boolean networks, available in existing CAD tools, can be performed if an NCL target library is available.

Figure 2.13: RTL flow for NCL design [51].

While threshold and hysterisis properties provide NCL with advantages that are not available in other clockless methodologies, they remain responsible for some of its disadvantages [5]:

(i) By using existing synthesis tools, the area of some NCL designs can be sometimes two to three times larger than the area of the same designs synthesized in clocked logic.

- (ii) The throughput of NCL designs may suffer unless heavy pipelining is used which may result in an area increase.

- (iii) Experimentation shows that straightforward translations of clocked logic to NCL designs results in a substantial increase in power consumption.

- (iv) Although existing synthesis tools can be used to implement NCL designs, proprietary libraries owned by Theseus are necessary to map the synthesized designs onto library cells if a high quality implementation is desired.

To remedy the problem described in (i), synthesis tools tailored to NCL logic may be necessary. However, this would defeat the advantage of leveraging the investment spent on existing synthesis tools.

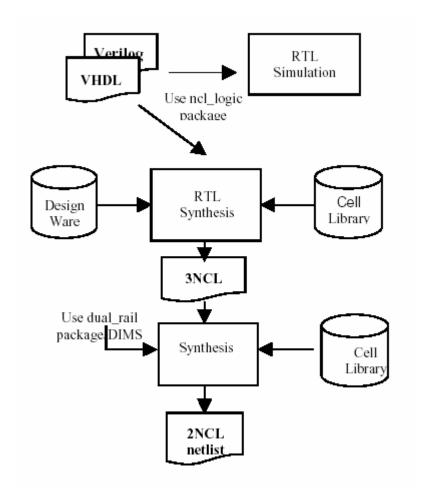

### 2.5 Burst Mode Machine

When in a stable state, a burst-mode circuit waits for a set of input signals to change in arbitrary order. After this input burst has completed, the machine computes a burst of output signals and new values of internal variables. The surrounding environment is not allowed to change a new input burst until the circuit has completely reacted to the previous burst [44, 45, 53]. Figure 2.14 shows an example of burst mode circuit [27].

Burst-mode circuits are specified using state graphs similar to those used in the design of clocked circuits. Several tools for synthesizing burst-mode controllers have been previously developed primarily in academia. *MINIMALIST*, developed at Columbia University, is a CAD package for synthesis, optimization and verification of burst-mode

controllers [54]. The focus of the package is on technology-independent synthesis. *MINIMALIST* includes a number of highly-optimized algorithms for state minimization, optimal state assignment, two-level hazard-free logic minimization, synthesis of generalized C-element implementations, and verification. The latter is achieved by using a simulation environment to verify the modeled burst mode machines. The synthesized implementations are hazard-free gate-level circuits consisting of two-level AND-OR networks and generalized-C elements. These circuits can then be technology-mapped using existing technology mapping tools. To support this functionality, MINIMALIST provides a graphical display to show specifications and implementations, an interactive shell, design scripts, help menus, and a tutorial.

Figure 2.14: Burst mode specification of a C-element.

Beside *MINIMALIST*, 3D, developed at University of California, is a synthesis package which uses the *extended burst-mode* (XBM) model [55]. The XBM design style covers a wide spectrum of sequential circuits ranging from DI to clocked circuits. 3D can synthesize multiple-input change clockless finite state machines in addition to numerous

circuits that fall in the area between clocked and clockless logic. These circuits are difficult and sometimes impossible to synthesize automatically using existing methods. 3D synthesizes XBM controllers in two-level AND-OR networks, and maps these networks to a generic CMOS standard cell library or generalized C-elements. Both tools do not offer any HDL front-end interface. As a result, a designer can interact with these tools only in two modes: using prepared design scripts or typing individual commands.

# **2.6 Handshake Circuits**

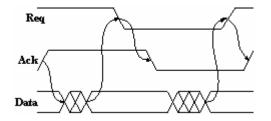

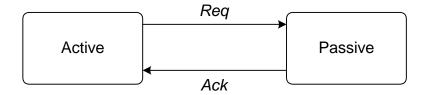

An alternative to clockless finite-state machines that communicate using fundamental mode or burst-mode has been proposed as handshaking circuits. Figure 2.15 shows a handshake channel, which is a point-to-point connection between an active and a passive block.

Figure 2.15: Handshake channel.

This approach requires that both blocks be connected by two wires: a request (Req) and an acknowledge (Ack) wire. A handshake is initiated by the active block, which starts by sending a signal via Req, and waits until a signal arrives via Ack. After a request arrives to the passive block, this block sends an acknowledge [27, 42, 56-58]. Most clockless circuits use a four-phase handshake protocol. This protocol consists of a channel which starts in a state where both Req and Ack are low. The active block starts a

handshake by making *Req* high. When the passive block receives *Req*, it sets *Ack* to high. A return-to-zero cycle follows, during which *Req* and *Ack* go low thus returning to the initial state.

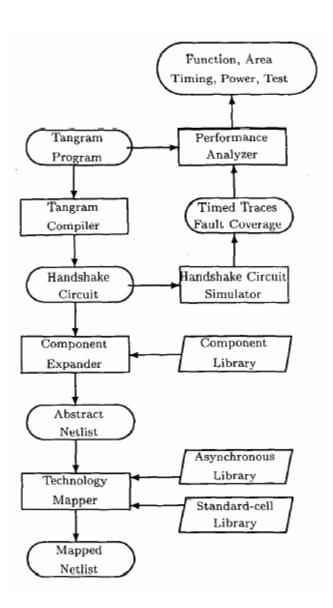

To support this handshake methodology, the *Tangram* toolset has been proposed [43]. As shown in Figure 2.16, a design can be specified in Tangram, which is a programming language, similar to the C language, extended to include constructs that support concurrency and communication.

In fact, Tangram has language constructs which support blocks sharing and waiting for clock-like edges. A compiler translates Tangram programs into handshake circuits, which are netlists composed from a library of some 40 handshake components. Each handshake component implements a language construct, such sequencing, communication, and sharing. Packaged with the compiler, the handshake circuit simulator and performance analyzer give the designer feedback about the design function, area, timing, and power of the synthesized circuit. The process of mapping the handshake circuit using a conventional standard cell library can be done in two steps. In the first step, the component expander uses the component library to generate an abstract netlist of combinational logic, registers, and clockless cells, such as Muller C-elements. This step also determines the encoding of data and handshake protocol. In the second step, a commercial synthesis tool and technology mapper can be used to generate the cell netlist. Today, Tangram is considered one of the most complete toolset used to design medium size clockless integrated circuits. Besides being a proprietary toolset, designers will have

to endure the learning curve of a new programming language if they are interested in using the Tangram toolset.

Figure 2.16: The Tangram Toolset.

#### 2.7 Extended Delay Insensitive Model

The eXtended model for Delay-Insensitive systems (XDI) is a theoretical framework used to define the external structure and observable behavior of DI systems. Besides being state-based, the framework includes refinement or satisfaction relations and composition operators. The XDI model specifies the conditions and the rules to implement a DI circuit from initial specifications by taking in consideration the expression of progress requirements for the circuit and its environment. XDI transforms these specification to DI-algebra first, and then to a state graph that is expressed in AND/IF-notation [38-40]. A handful of tools such *Digg* and *Ludwig* have been proposed to automate the refinement process [40]. Digg transforms a DI-algebra specification into XDI automata. DI-algebra specification can be expressed as recursive DI-algebraic expression while XDI automata can be represented as AND/IF graphs. After Digg's transformation, Ludwig can analyze and synthesize the obtained state graph into a circuit. A major shortcoming of this design methodology is the absence of simulation and mapping tools based on existing cell libraries.

# 2.8 Summary

This chapter presents a review of previously proposed clockless design methodologies. Although there are different design methodologies, none can be easily integrated in a complete design flow using existing CAD tools without significant modifications to the design flow. While designs in some design methodologies cannot be modeled using existing HDLs, others cannot be simulated using existing simulators. In addition, some design methodologies requires special synthesizers and mappers which

technique is sufficiently flexible to be supported by existing CAD tools. SRSL can be modeled using existing HDLs, simulated using existing simulators, synthesized using existing synthesis compilers, and mapped using existing technology mappers. At the end, a pipelined SRSL netlist is produced with can be placed and routed using existing physical layout tools granted that design constraints are propagated from synthesis to layout tools. Table 2.1 shows a summary of the design methodologies.

Table 2.1: Summary of clockless design methodologies.

| Design<br>Methodology  | Modeling                                   | Verification                | Synthesis                                                                   | Mapping                                                                                                                                       | Features                                                                                                                                 |