University of Central Florida

Electronic Theses and Dissertations, 2004-2019

2007

# High Current Density Low Voltage Isolated Dc-dc Converterswith Fast Transient Response

Liangbin Yao University of Central Florida

Part of the Electrical and Electronics Commons Find similar works at: https://stars.library.ucf.edu/etd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS Citation**

Yao, Liangbin, "High Current Density Low Voltage Isolated Dc-dc Converterswith Fast Transient Response" (2007). *Electronic Theses and Dissertations, 2004-2019.* 3421. https://stars.library.ucf.edu/etd/3421

# HIGH CURRENT DENSITY LOW VOLTAGE ISOLATED DC-DC CONVERTERS WITH FAST TRANSIENT RESPONSE

by

LIANGBIN YAO B.S. Zhejiang University, 2003 M.S. University of Central Florida, 2005

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the School of Electrical Engineering and Computer Science in the College of Engineering & Computer Science at the University of Central Florida Orlando, Florida

Summer Term 2007

Major Professor: Issa Batarseh

© 2007 Liangbin Yao

#### ABSTRACT

With the rapid development of microprocessor and semiconductor technology, industry continues to update the requirements for power supplies. For telecommunication and computing system applications, power supplies require increasing current level while the supply voltage keeps decreasing. For example, the Intel's CPU core voltage decreased from 2 volt in 1999 to 1 volt in 2005 while the supply current increased from 20A in 1999 to up to 100A in 2005. As a result, low-voltage high-current high efficiency dc-dc converters with high power-density are demanded for state-of-the-art applications and also the future applications.

Half-bridge dc-dc converter with current-doubler rectification is regarded as a good topology that is suitable for high-current low-voltage applications. There are three control schemes for half-bridge dc-dc converters and in order to provide a valid unified analog model for optimal compensator design, the analog state-space modeling and small signal modeling are studied in the dissertation and unified state-space and analog small signal model are derived. In addition, the digital control gains a lot of attentions due to its flexibility and re-programmability. In this dissertation, a unified digital small signal model for half-bridge dc-dc converter with current doubler rectifier is also developed and the digital compensator based on the derived model is implemented and verified by the experiments with the TI DSP chip.

In addition, although current doubler rectifier is widely used in industry, the key issue is the current sharing between two inductors. The current imbalance is well studied and solved in non-isolated multi-phase buck converters, yet few discusse this issue in the current doubler rectification topology within academia and industry. This dissertation analyze the current sharing issue in comparison with multi-phase buck and one modified current doubler rectifier topology is proposed to achieve passive current sharing. The performance is evaluated with half bridge dc-dc converter; good current sharing is achieved without additional circuitry.

Due to increasing demands for high-efficiency high-power-density low-voltage high current topologies for future applications, the thermal management is challenging. Since the secondary-side conduction loss dominates the overall power loss in low-voltage high-current isolated dc-dc converters, a novel current tripler rectification topology is proposed. Theoretical analysis, comparison and experimental results verify that the proposed rectification technique has good thermal management and well-distributed power dissipation, simplified magnetic design and low copper loss for inductors and transformer. That is due to the fact that the load current is better distributed in three inductors and the rms current in transformer windings is reduced.

Another challenge in telecommunication and computing applications is fast transient response of the converter to the increasing slew-rate of load current change. For instance, from Intel's roadmap, it can be observed that the current slew rate of the age regulator has dramatically increased from 25A/uS in 1999 to 400A/us in 2005. One of the solutions to achieve fast transient response is secondary-side control technique to eliminate the delay of optocoupler to increase the system bandwidth. Active-clamp half bridge dc-dc converter with secondary-side control is presented and one industry standard 16<sup>th</sup> prototype is built and tested; good efficiency and transient response are shown in the experimental section. However, one key issue for implementation of secondary-side control is start-up. A new zero-voltage-switching buck-flyback isolated dc-dc converter with synchronous rectification is

proposed, and it is only suitable for start-up circuit for secondary-side controlled converter, but also for house-keeping power supplies and standalone power supplies requiring multi-outputs.

To my parents: Wengang Yao Hongfu Li

#### ACKNOWLEDGMENTS

With my sincere appreciation from heart, I would like to thank my advisor, Dr. Issa Batarseh, for his guidance, encouragement and support throughout this work and my studies at University of Central Florida. Dr. Batarseh's extensive vision and creative thinking have been the source of inspiration for me throughout my PhD student life. In the past years, I have learned from him not only power electronics but also his personality and management techniques. This knowledge is going to benefit me for the rest of my life.

I would also like to thank the other four members of my advisory committee: Dr. Wasfy Mikael, Dr. Louis Chow, Dr. Jiann-shiun Yuan and Dr. Christopher Iannello for their support, suggestions and encouragement in my dissertation and study.

Part of this work is supported and funded by ASTEC Power/Emerson. I would like to thank Mr. Geof Potter and Brad Higgins from ASTEC for their valuable insight, technical guidance, support and encouragement throughout this work. Without their valuable suggestions and useful inputs, this work could not have been finished successfully.

It has been a great pleasure to study in the Florida Power Electronics Center at University of Central Florida. I will cherish the friendships that I have made during my studies here. I would like to thank my colleagues: Dr. Hong Mao, Dr. Songquan Deng, Dr. Jun Liu, Dr. Xiangcheng Wang, Dr. Jaber A. Abu Qahouq, Dr. Osama Abdel Rahama, Mr. Hussam Al-Atrush, Ms. Majd Batarseh, Mr. Feng Tian, Ms. Yangyang Wen, Mr. Charles Scholl and Mr. Khalid Rustom for their dedicated teamwork, useful discussion and support. I would also like to thank other faculty and colleagues: Dr. Thomas Wu, Dr. John Shen, Ms. Hua Zhou and Mr. Shangyang Xiao for their support and useful discussions.

I would also like to express my appreciation to Ms. Michelle Jordan for her invaluable editing work on my dissertation.

Finally, my deepest and heartfelt appreciation goes to my parents in China for their unconditional love, encouragement and support throughout my Ph.D. study.

Liangbin Yao July 2007

# TABLE OF CONTENTS

| LIST OF FIGURES                                                               | xii     |

|-------------------------------------------------------------------------------|---------|

| LIST OF TABLES                                                                | xvi     |

| CHAPTER ONE: INTRODUCTION                                                     | 1       |

| 1.1 DC-DC Switching Power Converter                                           | 1       |

| 1.2 Low Voltage High Current DC-DC Converter                                  | 7       |

| 1.3 Compensation for DC-DC Converter                                          |         |

| 1.3.1 Analog Controller for DC-DC Converter                                   | 11      |

| 1.3.2 Digital Controller for DC-DC Converter                                  |         |

| 1.4 Dissertation Outline                                                      |         |

| CHAPTER TWO: HALF BRIDGE DC-DC CONVERTER WITH CURRENT                         | DOUBLER |

| RECTIFIER                                                                     |         |

| 2.1 Topology and Operation                                                    |         |

| 2.2 Unified State Space Model for HB Converter with Current Doubler Rectifier |         |

| 2.3 Unified Analog Small Signal Model for HB Current Doubler Converter        |         |

| 2.4 Unified Digital Small Signal Model for HB Current Doubler Converter       |         |

| 2.5. Digital Control of HB DC-DC Converter with Current Doubler Rectifier     |         |

|                                                                               |         |

| CHAPTER THREE: CURRENT SHARING ANALYSIS OF CURRENT                            | DOUBLER |

| CHAPTER THREE: CURRENT SHARING ANALYSIS OF CURRENT RECTIFIER                  |         |

|                                                                               |         |

| 3.3 Comparison of Two-phase Buck Converters with a Current Doubler Rectifier in Half-bridge |

|---------------------------------------------------------------------------------------------|

| DC-DC Converters                                                                            |

| 3.4 Proposed Half-bridge Current-doubler-rectifier DC-DC Topology with Passive Current      |

| Sharing                                                                                     |

| 3.5 Experimental Results                                                                    |

| CHAPTER FOUR: THE CURRENT TRIPLER RECTIFICATION TOPOLOGY                                    |

| 4.1 Proposed Rectification Topology                                                         |

| 4.1.1. Current Tripler Rectification Topology                                               |

| 4.1.2. Principle of Operation                                                               |

| 4.1.3. DC Analysis of the Proposed Topology                                                 |

| 4.2 Features and Design Considerations                                                      |

| 4.2.1. Major Features and Comparison with Conventional Rectification Topologies77           |

| 4.2.2. Design Considerations                                                                |

| 4.3 Derivative Topologies                                                                   |

| 4.4 Experimental Results                                                                    |

| 4.5 Conclusions                                                                             |

| CHAPTER FIVE: HIGH-EFFICIENCY ISOLATED DC-DC CONVERTERS WITH FAST                           |

| TRANSIENT RESPONSE                                                                          |

| 5.1 Demo Y Topology and Operation                                                           |

| 5.2 Experimental Results                                                                    |

| CHAPTER SIX: ZERO-VOLTAGE-SWITCHING BUCK- FLYBACK ISOLATED DC-DC                            |

| CONVERTER WITH SYNCHORNOUS RECTIFICATION                                                    |

| 6.1 Steady-state and DC Analysis                       | 112 |

|--------------------------------------------------------|-----|

| 6.1.1. DC Analysis                                     | 113 |

| 6.1.2. Steady-state Operation Mode Analysis            |     |

| 6.2 Average State-space Model of the Proposed Topology |     |

| 6.3 Features and Design Considerations                 |     |

| 6.3.1. Main Features                                   |     |

| 6.3.2. Design Considerations                           |     |

| 6.4 Experimental Results                               |     |

| 6.5 Conclusions                                        |     |

| CHAPTER SEVEN: CONCLUSION                              |     |

| 7.1 Summary                                            |     |

| 7.2 Future Work                                        |     |

| LIST OF REFERENCES                                     | 144 |

# LIST OF FIGURES

| Figure 1.1 Typical block diagram of a linear regulator power supply                      | 1     |

|------------------------------------------------------------------------------------------|-------|

| Figure 1.2 Block diagram of a switch mode power supply with multiple outputs             | 3     |

| Figure 1.3 Block diagram of conventional PWM isolated dc-dc converters                   | 4     |

| Figure 1.4 Various types of rectifier topologies                                         | 5     |

| Figure 1.5 Examples of isolated dc-dc topologies                                         | 6     |

| Figure 1.6 Basic architecture of a distributed power system                              | 8     |

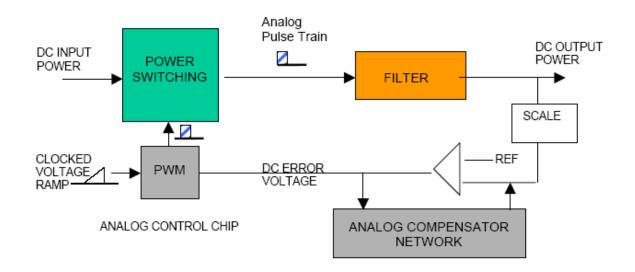

| Figure 1.7 Typical switching power converter architecture with analog controller         | 11    |

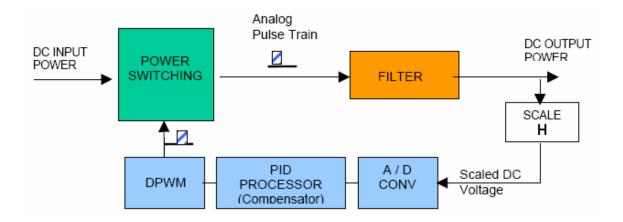

| Figure 1.8 Typical switching power converter architecture with digital controller        | 14    |

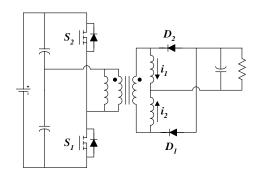

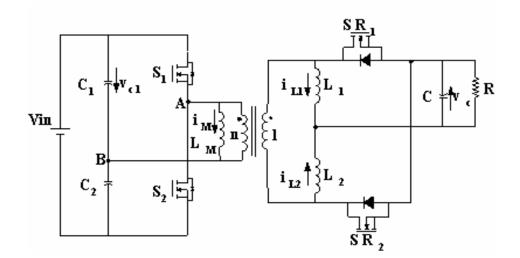

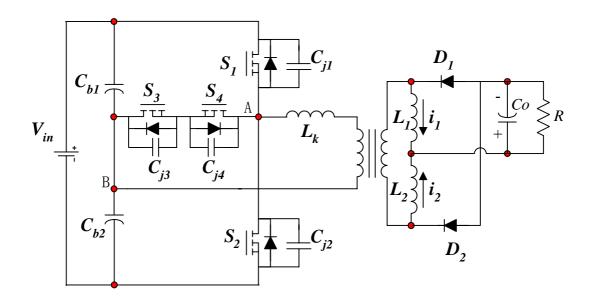

| Figure 2.1 Half bridge dc-dc converters with current doubler rectifier                   | 21    |

| Figure 2.2 Operation modes                                                               | 23    |

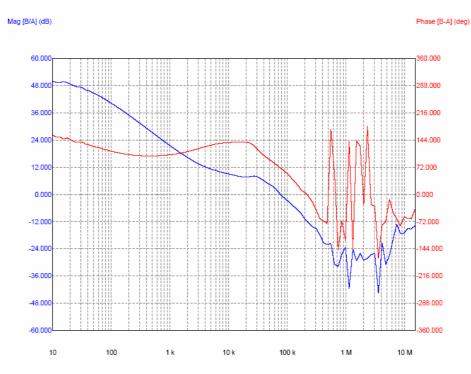

| Figure 2.3 Bode diagrams of three converter models                                       | 32    |

| Figure 2.4 Close loop gain of theoretical desig                                          | 33    |

| Figure 2.5 Close loop gain of experimental result                                        | 33    |

| Figure 2.6 The primary-side and secondary-side gate driving signals with 100ns dead-time | me in |

| symmetrical control case                                                                 | 35    |

| Figure 2.7 The gate signals with 100ns dead-time in asymmetrical control case            | 35    |

| Figure 2.8 The primary signals with 100ns dead time in a DCS case                        | 36    |

| Figure 2.9 The output voltage with significant noise                                     | 37    |

| Figure 2.10 Close loop diagram with power stage and DSP controller                       | 37    |

| Figure 2.11 The output voltage 1.5 volt and gate signal with 0.26 duty cycle at steady state |

|----------------------------------------------------------------------------------------------|

| with a DSP controller (digital PI compensator) in symmetrical control case                   |

| Figure 2.12 The transformer primary current waveform for symmetrical control case 39         |

| Figure 2.13 The transformer primary-side current and switch-node voltage                     |

| Figure 3.1 Two-phase buck converter                                                          |

| Figure 3.2 Modes of operation                                                                |

| Figure 3.3 Half-bridge dc-dc converter with current doubler rectifier                        |

| Figure 3.4 Duty cycle offset under asymmetric inductor DCR values                            |

| Figure 3.5 Half-bridge dc-dc converter with the modified current doubler rectifier           |

| Figure 3.6. Modes of operation for the proposed half-bridge dc-dc converter with passive     |

| current sharing                                                                              |

| Figure.3.7 Conventional HB dc-dc converter                                                   |

| Figure 3.8 Symmetric HB dc-dc converter with asymmetric inductor DCR values without          |

| passive current sharing                                                                      |

| Figure 3.9 Proposed HB CDR dc-dc converter                                                   |

| Figure 3.10 Proposed HB CDR dc-dc converter under asymmetric duty cycles                     |

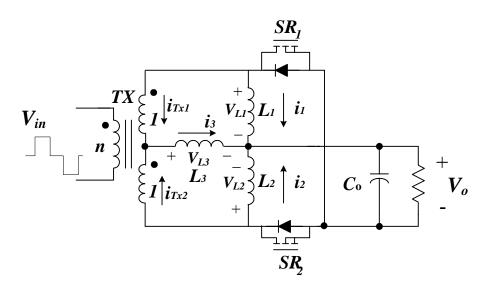

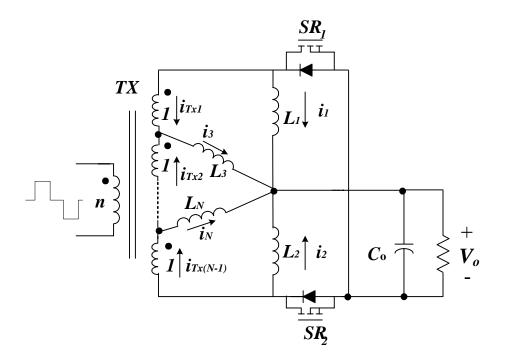

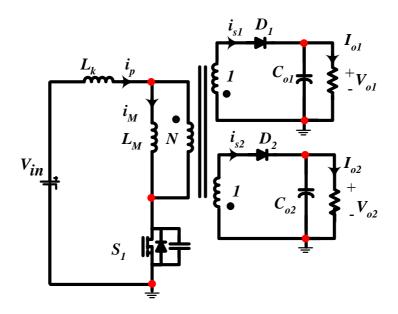

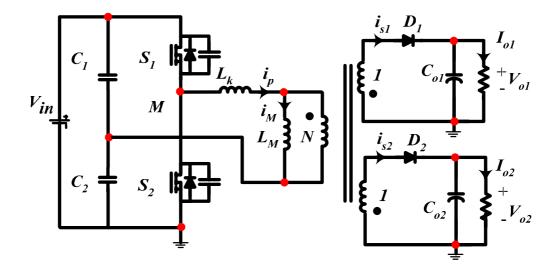

| Figure 4.1 Proposed current tripler rectification topology                                   |

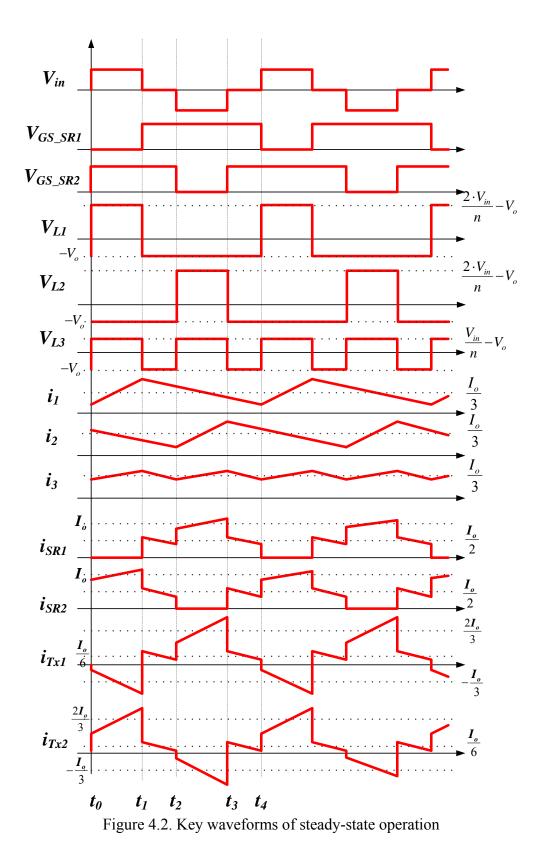

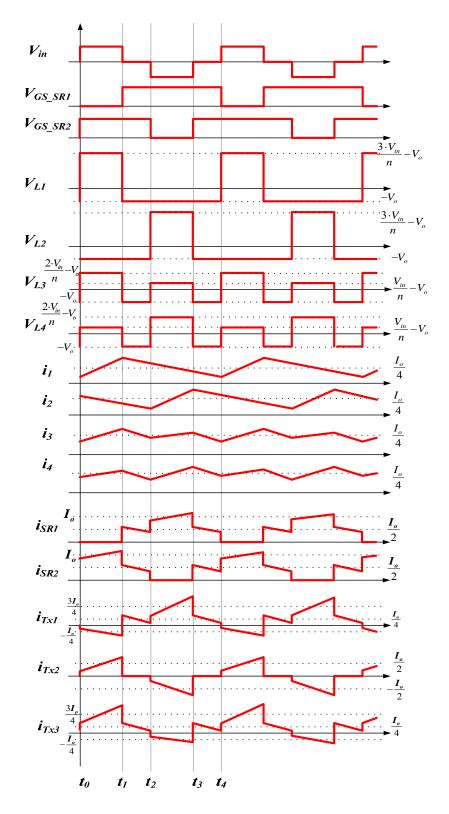

| Figure 4.2 Key waveforms of steady-state operation                                           |

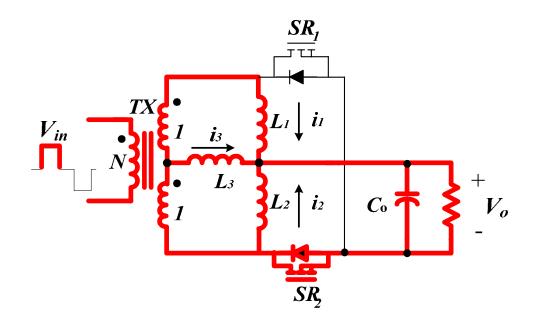

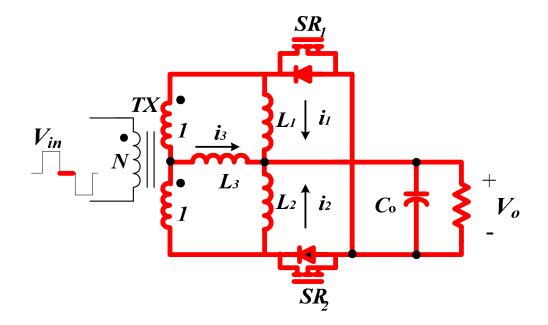

| Figure 4.3 Equivalent circuits of operational modes                                          |

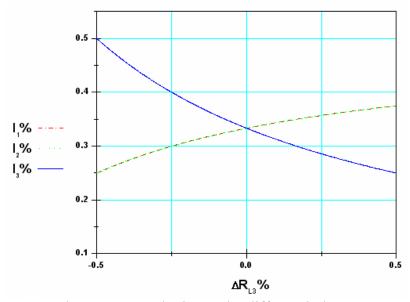

| Figure 4.4 Inductor current sharing under different inductor DCR values                      |

| Figure 4.5 Current quadrupler topology                                                       |

| Figure 4.6 Key operation waveforms of current quadrupler topology                            |

| Figure 4.7 Current N-tupler topology                                                           |

|------------------------------------------------------------------------------------------------|

| Figure 4.8 Experimental prototype                                                              |

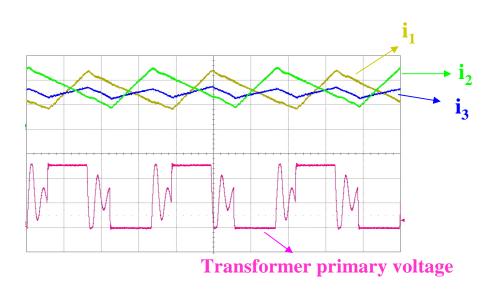

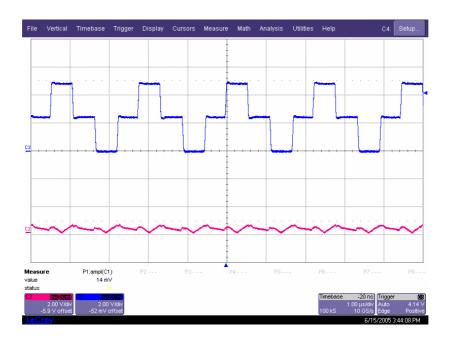

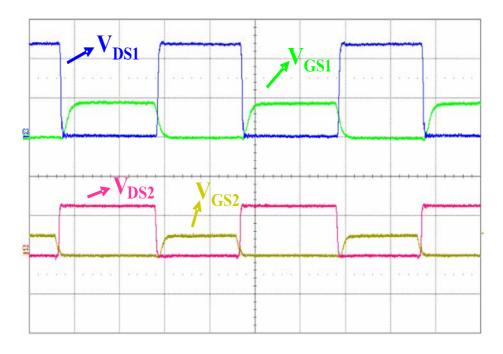

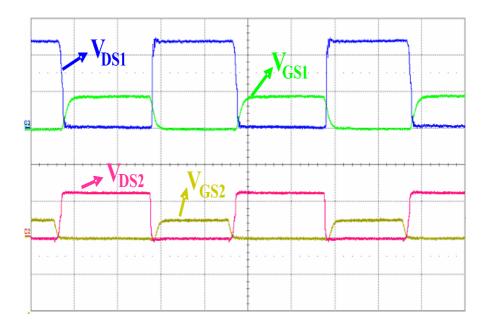

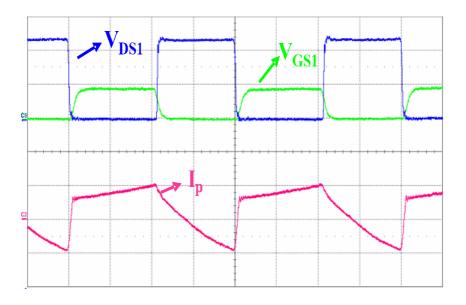

| Figure 4.9 Experimental waveforms for Vin =48V, Io=10A                                         |

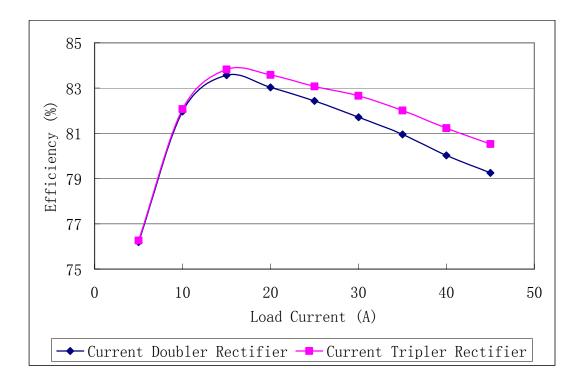

| Figure 4.10 Efficiency comparison for Vin =48V                                                 |

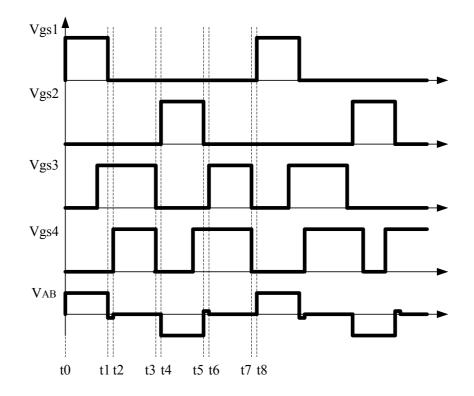

| Figure 5.1 The active-clamp half-bridge dc-dc converter with current doubler rectifier 93      |

| Figure 5.2 Key operation waveforms for the proposed active-clamp half-bridge with current      |

| doubler rectifier                                                                              |

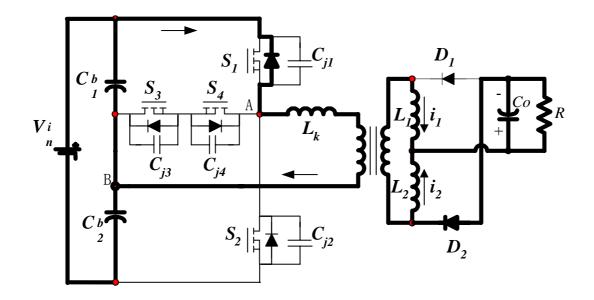

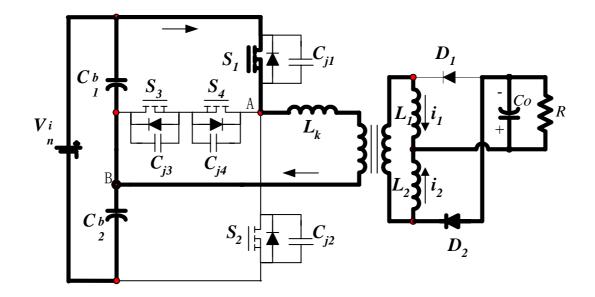

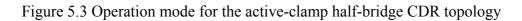

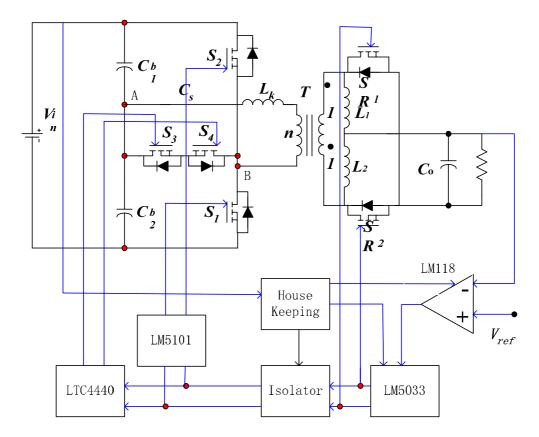

| Figure 5.3 Operation mode for the active-clamp half-bridge CDR topology                        |

| Figure 5.4 Experimental prototype                                                              |

| Figure 5.5 Prototype schematics                                                                |

| Figure 5.6 Experimental waveforms for V <sub>in</sub> =48V and I <sub>o</sub> =0A102           |

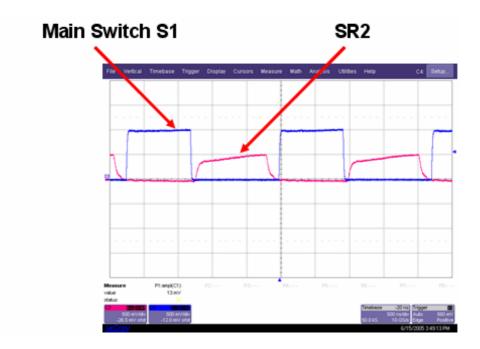

| Figure 5.7 Driving waveforms for S <sub>1</sub> and SR <sub>2</sub>                            |

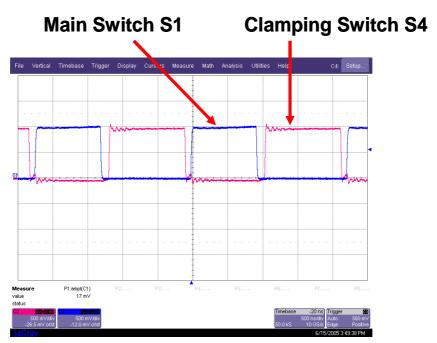

| Figure 5.8 Driving waveforms for S <sub>1</sub> and S <sub>4</sub>                             |

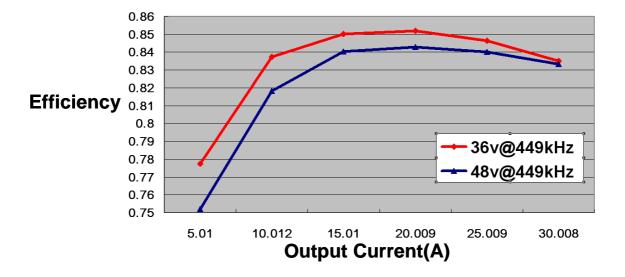

| Figure. 5.9 Efficiency curves for different line input voltage                                 |

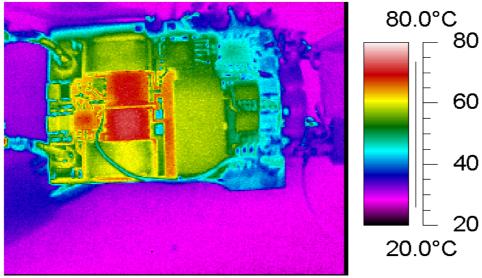

| Figure 5.10 Infrared thermal picture under condition: Vin= 48V, Vo=1V, $I_0$ = 30A, $f_s$ =450 |

| kHz                                                                                            |

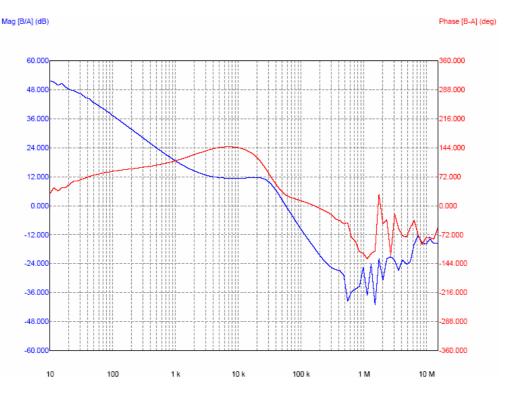

| Figure 5.11 Close-loop bode plot before optimization under the condition: Vin=36 V and         |

| Io=5A                                                                                          |

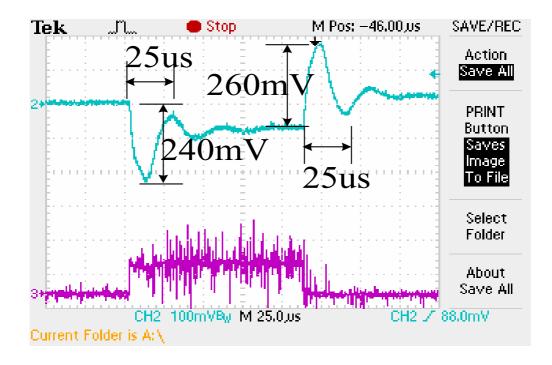

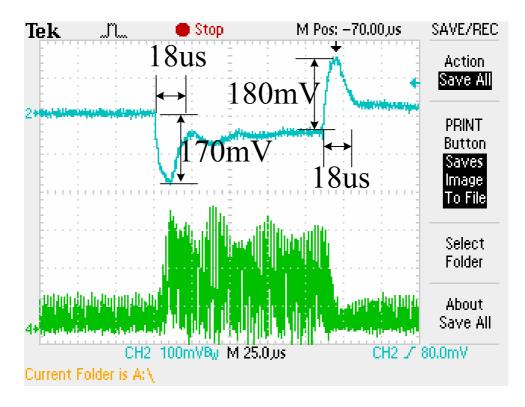

| Figure 5.12 Initial transient response test for Vin=36 V 107                                   |

| Figure 5.13 Close-loop bode plot after optimization under the condition: Vin=36 V and          |

| Io=5A:                                                                                         |

| Figure 5.14 Transient response test after optimization for Vin=36 V 108                        |

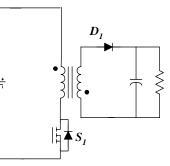

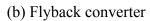

| Figure 6.1 Conventional flyback converter with multi-outputs                          | 110     |

|---------------------------------------------------------------------------------------|---------|

| Figure 6.2 Active-clamp flyback converter with multi-outputs                          | 111     |

| Figure 6.3 Asymmetrical half-bridge flyback converter with multi-outputs              | 111     |

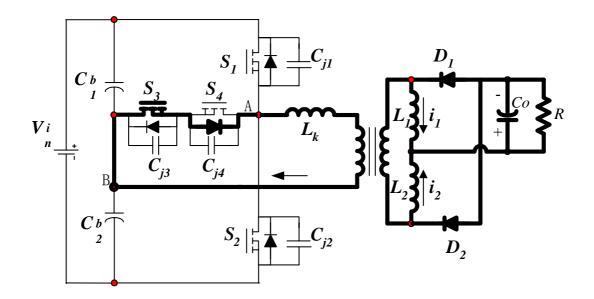

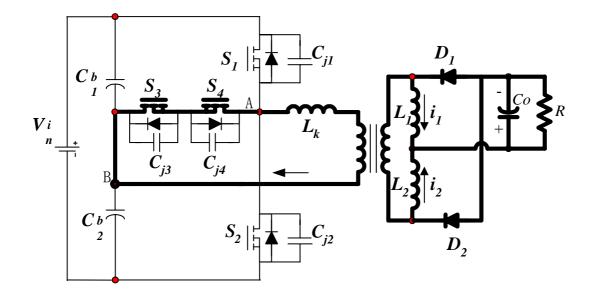

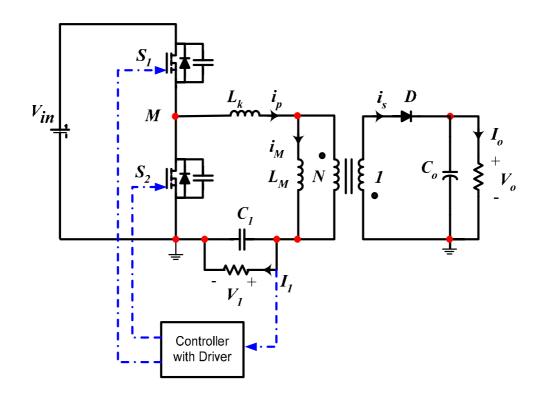

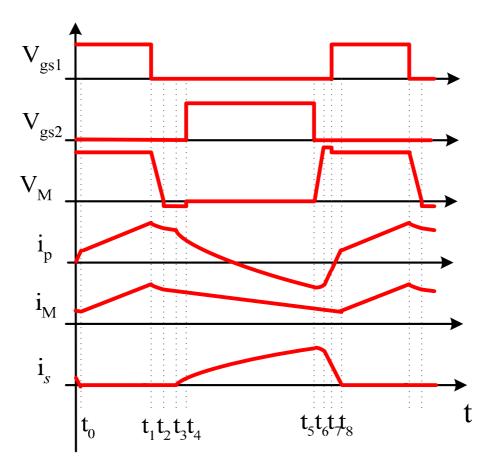

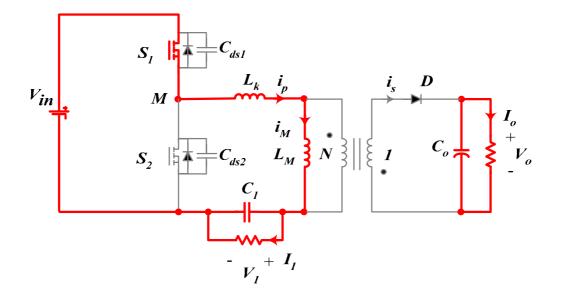

| Figure 6.4 ZVS buck-flyback converter and key operation waveforms                     | 113     |

| Figure 6.5 Operation modes                                                            | 125     |

| Figure 6.6 Equivalent circuits of typical operation modes                             | 127     |

| Figure 6.7 Experimental prototype                                                     | 136     |

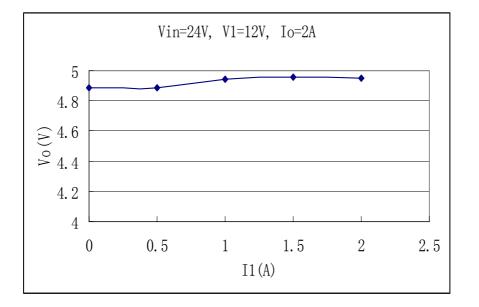

| Figure 6.8 Secondary-side output voltage vs. primary-side load change                 | 136     |

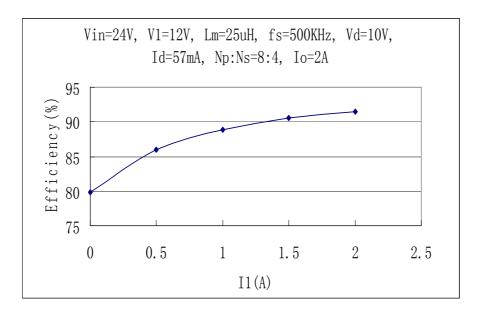

| Figure 6.9 Efficiency curve with constant secondary-side load                         | 137     |

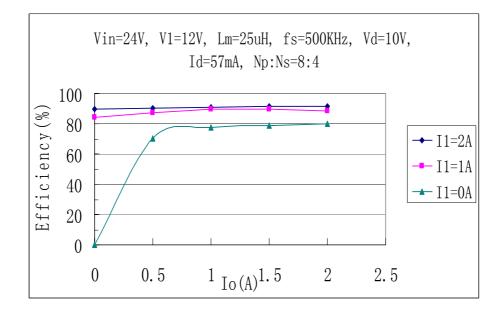

| Figure 6.10 Efficiency curve with constant primary-side load                          | 137     |

| Figure 6.11 ZVS waveforms at I <sub>1</sub> =0A and Io=2A                             | 138     |

| Figure 6.12 ZVS waveforms at I <sub>1</sub> =2A and Io=2A                             | 138     |

| Figure 6.13 $S_1$ ZVS waveform and $i_p$ waveform at $I_1$ =1A and Io=2A              | 139     |

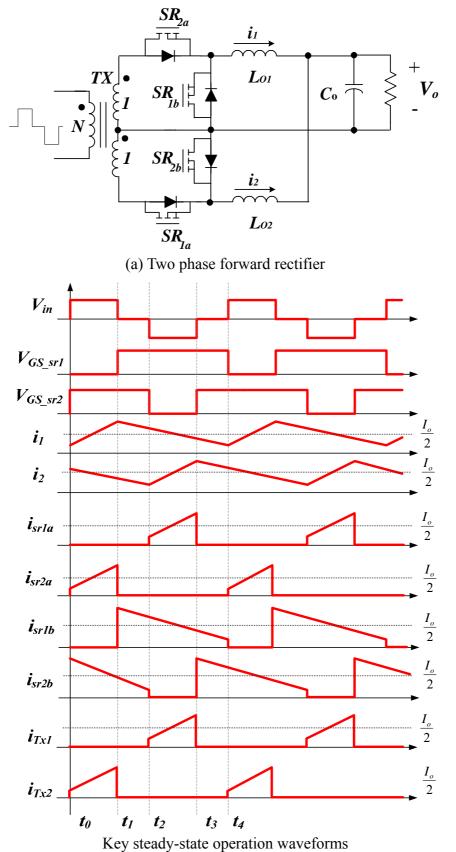

| Figure. 7.1 Two phase forward rectifier and its key waveforms for steady-state operat | ion 143 |

# LIST OF TABLES

| Table 2-1 Transfer functions for analog controlled half bridge current doubler conve  | erters |

|---------------------------------------------------------------------------------------|--------|

| with different control schemes                                                        | 27     |

| Table 2-2 Transfer functions for digital controlled half bridge current doubler conve | erters |

| with different control schemes                                                        | 31     |

| Table 4-1 Current tripler rectifier comparison with center-tapped and current do      | ubler  |

| rectifiers                                                                            | 91     |

#### **CHAPTER ONE: INTRODUCTION**

#### 1.1 DC-DC Switching Power Converter

Dc-dc converters are used in power electronics systems that convert system voltages from one dc level to another dc level.

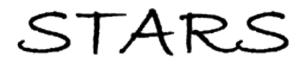

Today dc-dc switching power converters are very popular and prevail in the power supply systems market. Prior to the 1970s, a majority of commercially available power supplies were the linear regulator type. Figure 1.1 shows a typical block diagram of a linear regulator power supply [1]. The front end of the linear regulator is a 60 Hz transformer,  $T_1$ , used to provide input electrical isolation and to step up or step down the line voltage, and this is followed by a full-wave bridge rectifier to convert the ac input to a dc input

Figure 1.1 Typical block diagram of a linear regulator power supply [1]

by adding a large filtering capacitor at the input of the linear regulator. The input to the linear regulator,  $V_{in}$ , is unregulated dc and cannot be used to drive the load directly. Using a linear circuit that provides a stable dc output regulates the dc voltage at the output,  $V_0$ . The linear regulator is simple to use and provide tight control, good output voltage ripples and a low components count, but its main disadvantage for practical use is high power loss, hence, low power efficiency.

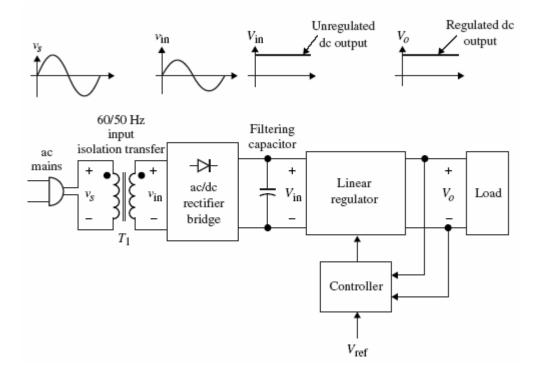

In the early 1970s, dc-dc switch mode converters entered the market. Because of high power efficiencies compared with linear regulators, traditional linear regulator power supplies gradually replaced for medium and high power applications. Unlike linear regulators, switching converters use power semiconductor devices to operate in either the on-state (saturation or conduction) or the off-state (cutoff or no conduction). Since either state will lead to low switching voltage or low switching current, it is possible to convert dc to dc with higher efficiency using a switching regulator. Figure 1.2 shows a simplified block diagram for a switched mode ac-to- dc power converter with multi-output application. Compared with the block diagram of Figure. 1.1, a switching network and high frequency output electrical isolation transformer  $T_2$  are added.

Figure 1.2 Block diagram of a switch mode power supply with multiple outputs [1]

The dc-dc switching converters can be classified as either non-isolated or isolated converter, depending on whether high frequency transformers are added between the power stage and output. The non-isolated converters have three basic topologies: buck, boost and buck-boost. There are also some other high order non-isolated topologies: CUK, SEPIC and ZETA.

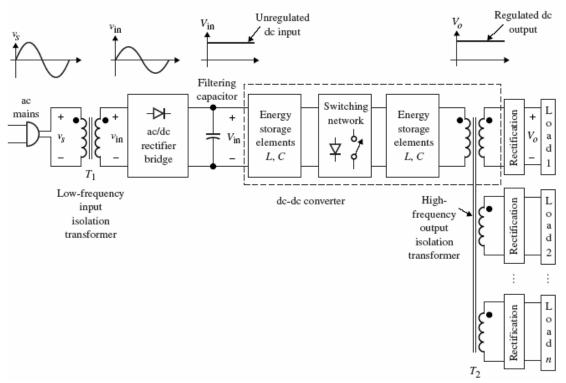

The output voltage of non-isolated fixed frequency dc-dc converters is determined by the duty ratio D. For the application with high input voltage level and low output level, the converters must operate with very small duty cycles and asymmetrical transient responses. As a result, transformers are added in dc-dc switching converters and therefore becoming isolated dc-dc topologies. The conventional isolated PWM dc-dc converter structure is shown in Figure 1.3, which consists of three parts: PWM converter, isolated transformer and rectifier. The PWM converter behaves as an inverter to generate ac voltage or current which is applied to the transformer primary winding. The transformer delivers ac voltage or current from the primary side to the secondary side and provides electrical isolation. With a transformer turns ratio, the converter may work at a desirable duty cycle and achieve good efficiency. ac voltages or currents are delivered to the transformer's secondary side, and through the rectifier, a dc voltage can be obtained from the output. Hence, the procedure in energy processing in a dc - dc converter is:  $dc \rightarrow ac \rightarrow transformer \rightarrow ac \rightarrow dc$ .

Figure 1.3 Block diagram of conventional PWM isolated dc-dc converters

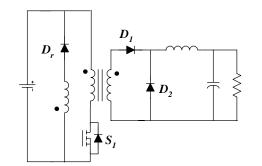

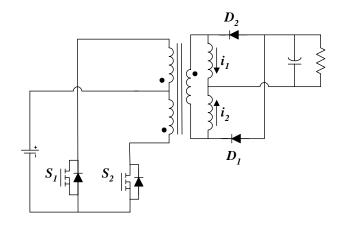

PWM converters, like the one shown in Figure 1.3, can be realized in a variety of state-of-the-art topologies, such as forward, flyback, two-switch forward, push pull, half bridge,

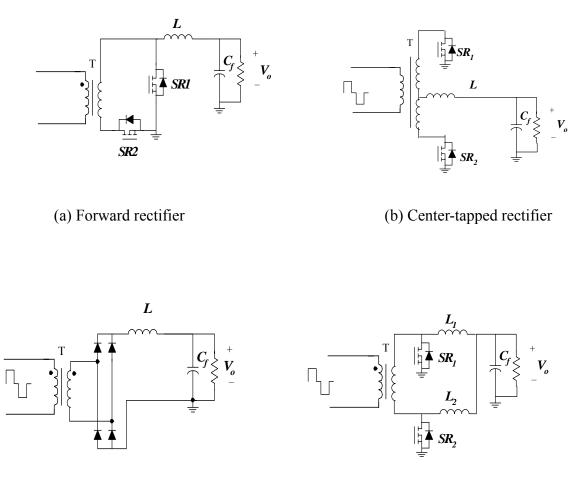

and full bridge. The rectifier topologies can be forward rectifier, center tapped, full bridge and current doubler rectifier as shown in Figure 1.4. Figure 1.5 shows the isolated dc-dc topologies.

(c) Full-bridge rectifier

(d) Current-doubler rectifier

Figure 1.4 Various types of rectifier topologies

(a) Forward converter

(c) Half bridge converter

(d) Full bridge converter

(e) Push pull converter

Figure 1.5 Examples of isolated dc-dc topologies

#### 1.2 Low Voltage High Current DC-DC Converter

As the top largest consuming industries of dc-dc converters, telecom/datacom and computing systems have similar requirements for the power supplies: low voltage high current dc-dc conversion. Ever-higher level of integration offered by unprecedented advancement of semiconductor technology is enabling telecom and computing systems to incorporate more and more functions in increasingly smaller dimensions, which implies larger number of transistors on the silicon. As a result, the power level and current powering these ICs keep increasing. Since smaller-geometry processes drives the ICs' operating voltage to decrease and thus less power consumption due to the fact that the IC power consumption is proportional to the operating voltage, the output voltage of the power supplies in these applications continue to be lower. Another trend for the power requirements in these applications is fast transient response since the IC operation frequency is higher and higher. For example, based on the historical data of INTEL CPUs, Intel's CPU core voltage decreased from 2 volts in 1999 to 1 volt in 2005, while the supply current increased from 20A in 1999 to up to 100A in 2005, and the CPU power almost doubles around every 36 months till more than 100W today; the load current transient slew rate increased to 400A/us in 2005 from less than 50A/us in 1999.

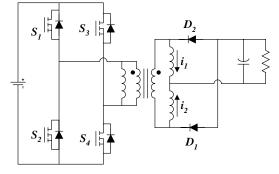

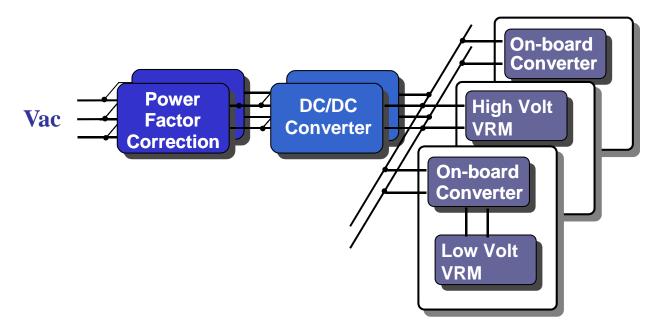

The distributed power systems (DPS) is a popular and widely-used power solution in industry for telecom/datacom applications because it can generate high quality output voltage, and has improved reliability as well as easy thermal management[86-90]. The DPS basic architecture is shown in Figure 1.6 and the power conversion is achieved in multi-stage. The ac voltage from power grid is first converted and processed to high dc voltage through an offline ac-dc power supply and power factor correction circuit. Then an intermediate voltage bus is

generated from the high dc voltage by a bus dc-dc converter and the nominal bus voltage is typically 48V or 12V depending on different applications [58]. This DC bus supplies power to the load through different DC-DC converters, located on the same board where the supplied circuits are connected. These DC-DC converters are normally referred as on-board converters. The close proximity of the DC-DC regulator to the high slew-rate load reduces distribution impedances permitting more precise and easier to control regulation and faster transient response.

Figure 1.6 Basic architecture of a distributed power system [86]

High power-density is a continual demand for power supplies in telecom and computing systems since reduced parasitic elements in the control loop, lower voltage drop across the PCB power planes and a cost savings for distribution cables and connectors are obtained. Therefore, power converter size is a major challenge since the power level is ever-increasing as discussed above. One solution is high switching frequency operation since the passive components' size is smaller as the switching frequency. However, power dissipation of the power converter may be higher in high frequency operation, so high efficiency topology and control techniques are always demanded for high frequency operation. However the size reduction and power density improvement of the power converter also depend on the thermal management which implies high frequency due to narrow pinch between the pc boards, otherwise bulky heat sink have to be added to the system and lower the converter power density correspondingly.

For the on-board converters, it can be non-isolated or isolated dc-dc converter depending on the applications. The dissertation focuses mainly on the high efficiency low-voltage high-current isolated dc-dc converter with fast transient response for telecom and computing systems. As shown in Figure 1.3, isolated dc-dc converter typically consists of three part, primary-side topology, secondary-side rectification topology and power transformer. Among the primary-side topologies, push-pull, half-bridge and full bridge are suited for low-voltage high-current applications. Considering lower component count and overall simplicity as well as an additional half step-down ratio due to the input capacitors, half-bridge is a preferred primary-side topology candidate for on board modules. In the traditional secondary-side rectifiers as shown in Figure 1.4, synchronous rectifiers are always used to replace the diode in the rectifier topologies for low voltage applications. The center-tapped rectifier and current doubler rectifier are commonly used in industry for low-voltage high-current application since in full-bridge rectifier, there are double voltage drop across the synchronous rectifiers (SRs) and SR driving is floating as well as the transformer utilization is bad; the half-wave rectifier has bad transformer utilization and current ripple frequency of output capacitor is switching frequency.

Compared to full-bridge and half-wave rectifier, both center-tapped and current doubler rectfiers have better transformer utilization and the twice current ripple frequency on the output capacitors which has potential for cost reduction and power-density improvement. However, center-tapped is better than current doubler in terms of single inductor structure while current doubler is better in lower conduction loss, simple inductor and transformer design.

#### **1.3 Compensation for DC-DC Converter**

The objective of dc-dc converters is to deliver a stable and regulated dc output voltage from an unregulated dc input voltage. The pulse width modulation (PWM) regulation method is used in switching converters, which controls the on time of the power switch devices to regulate the dc output voltage.

Based on the implementation of the PWM control method and compensator, the controller can be classified as either an analog controller or a digital controller.

Power control schemes have been revolutionized over the past few decades. Compared with analog controllers, the digital controller is gaining more attention because of its stable performance, flexibility, and ability to handle more complicated control techniques.

The advent of programmable digital signal processors (DSP) is creating thriving opportunities in the field of power electronics. The special architecture and high performance of DSP make it possible to implement a wide variety of control and measurement algorithms at a high sampling rate and reasonable cost. Power electronics systems are typically a complex combination of linear, nonlinear and switching elements. High-frequency converters add another dimension of complexity because of their fast dynamics.

Modern power electronics systems, therefore, demand the use of high-speed data-acquisition and real-time control. High performance DSP could meet these processing requirements imposed by such systems.

#### 1.3.1 Analog Controller for DC-DC Converter

A typical switching power converter is shown above in Figure. 1.7 [2]. An analog control system provides output voltage regulation by comparing a scaled representation of the output voltage to a reference voltage and amplifying the difference. The "error voltage", applied to an analog Pulse Width Modulator, results in a variable width driving pulse that has an average value equal to the desired output voltage. After power amplification by the power stage, driving pulses are averaged by the filter to yield a dc output voltage.

Figure 1.7 Typical switching power converter architecture with analog controller [2] As a closed loop system, this circuit requires a control mechanism to ensure that the

gain around the loop (from output sensing back to the filter) does not exceed unity at any frequency where phase shift around the loop reaches 360 degrees. In addition to the built-in 180 degrees phase shift necessary for regulation, the phase shift around the control loop is also caused by delays introduced by reactive elements (capacitors or inductors) and to a smaller degree by operational delays in amplifiers, modulators and switching devices.

Adjustments, or compensations, for gain variation and phase shift over a range of frequencies is usually incorporated into error amplifier circuitry to assure that the circuit will be stable when operating under anticipated conditions.

Isolation between input and output may be included in the design, but even with isolation, conceptually. Most power converters operate as shown in Figure 1.7.

It is possible to incorporate digital devices, such as "micro-controllers", into an analog control system like that of Figure. 1.7. A microprocessor control unit (MCU) can be set up to adjust and manage operation of an analog PWM (change switching frequency, for example) but that sort of control is still classified as an analog controlled dc-dc switching converter. Digital controlled switching converters are classified as a control system in which the feedback process is managed entirely by digital techniques. Specifically, the PWM functions, error signals, and compensator functions are performed in digital mode.

#### 1.3.2 Digital Controller for DC-DC Converter

A digital control system, equivalent to that shown in Figure. 1.7, is depicted in Figure. 1.8 [2]. Notice that voltage sensing, compensator and pulse width modulator functions are still present but appear under different names. Power switching, scaling, and filtering functions are

exactly the same as in the analog design shown in Figure. 1.7.

Working back from the power switching stage, the Digital Pulse Width Modulator (DPWM) performs the same drive signal generation function as its analog counterpart. However, it does so by "calculating" and then "timing" the desired duration of ON and OFF periods of its output signal. In contrast, the analog PWM usually operates by triggering ON at a clock transition and triggering OFF when a fixed voltage "ramp" reaches a pre-set trip voltage. The distinction is important because it leads to many of the advantages and challenges associated with digital control.

Located before the DPWM, is a "control law" processor. Typically a PI or PID style subsystem is used to perform the task of translating a digital representation of output voltage into pulse duration (duty-cycle) information used by the DPWM. It is the job of the PID control element to center the output voltage on a pre-set value and adjust the pulse width, in real-time, to provide voltage regulation. It must do so by compensating for gain and phase-shift factors around the control loop, as seen in the analog version. In digital systems, there are additional phase shift factors arising from time delays in processing the control data stream. The major gain and phase-shift factors present in an analog system (mostly from the output filter), are also present in digital mode, with calculation and A/D conversion delay factors added.

Figure 1.8 Typical switching power converter architecture with digital controller [2]

Moving farther upstream, an Analog-to-Digital (A/D) converter produces digital data that represents output voltage. Each binary "word" containing upwards of 8 bits of data, is sent at a high clock rate to the PID control law processor. Word length and A/D reference voltages set the precision at which the output voltage can be maintained. In digital systems, analog quantities such as voltage must be represented as a range of discrete values. Spacing between values, or the size of each "bucket" is set by the number of data bits divided into the total range of voltage over which the A/D conversion stage operates.

The digitally controlled switching power converters have the following advantages over traditional analog controlled converters [2-11]:

- Generate flexible power switch drive waveforms with programmable relationships to one another

- Implement sophisticated control laws

- Potential space saving and less component counts

- Offer precision that can counter the effects of component tolerance, parametric drift, aging, etc.

- Adapt to changing environmental conditions

- Store data for operational purposes and/or record keeping

- Communicate with the external digital world.

However, the digital controllers have their own disadvantages: high resolution is a must to satisfy the converters' tight regulation requirements and high speed is also a must in order to satisfy the converter dynamic requirements [7-8] [11]. These two requirements result in cost increase.

Generally, there are several implementation approaches for digital controllers today, which include Microprocessor/DSP's (Digital Signal Processors), FPGA (Field Programmed Gates Array) and Custom IC. The features of these approaches are compared as follows:

#### **DSP:**

- DSP chips can be reprogrammed;

- The speed is generally slower than ICs;

- Implementation is exceedingly complex for the intended application;

- DSP is costly over custom IC design;

- High frequency power converters have to use high performance DSP.

#### FPGA:

- FPGA can be programmed on site;

- The processing is faster than a general purpose DSP;

- For FPGA design there is no physical manufacturing step, which results in a very short design time;

• FPGA's typical price is higher than DSP.

#### **Custom IC Design:**

- Due to physical design consideration, custom IC's typically have better performance than FPGA;

- However it results in much longer design time than FPGA since there is a layout step;

- Custom IC design has lower price than FPGA and DSP.

#### **1.4 Dissertation Outline**

The dissertation consists of seven chapters.

Chapter One briefly discusses the research background and motivation of this work. After introduction of the history of switch-mode dc-dc converters, the dc-dc switching converters are categorized as non-isolated and isolated converters. In telecom and computing systems, low voltage high current dc-dc converters are needed. Major trend and challenges are discussed for low-voltage high current dc-dc conversion and typical architecture distributed power systems is shown. In this chapter, traditional analog control and digital control are also discussed and compared, and different implementations of digital control are presented as well.

Chapter Two focuses on the modeling and digital control of half-bridge dc-dc converters with current doubler rectification. Since half-bridge current-doubler dc-dc converter is widely used in industry and is a good topology suitable for high-current low-voltage applications, There're three control schemes for half-bridge dc-dc converters and in order to provide a valid unified analog model for optimal compensator design, unified analog and

digital state-space and analog small signal model are derived respectively. A digital compensator is designed for half bridge dc-dc converter with current doubler rectifier and implemented by TI DSP chip.

In Chapter Three, the current sharing in current doubler rectifier is discussed and compared with multi-phase non-isolated buck converter. Although duty cycle adjustment is widely used in current balancing for multi-phase buck converter, the analytic and experimental results show that this method can not effectively adjust the current distribution in the current doubler rectifier. Then a modified current doubler rectification topology is proposed to achieve passive current sharing without additional circuitry as duty cycle adjustment method.

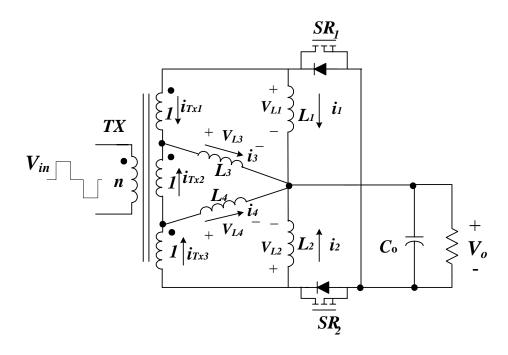

Current tripler and current N-tupler rectification topologies are proposed in Chapter Four for future high current applications in telecom and computing systems. The proposed rectification technique features good thermal management and well-distributed power dissipation, simplified magnetic design and low copper loss for inductors and transformer due to the fact that the load current is better distributed in three inductors and the rms current in transformer windings is reduced. The operation principle and dc analysis are presented and the proposed rectification topology is compared with state-of-the-art rectification topologies.

Chapter Five discusses another major challenge in telecommunication and computing applications, which is the fast transient response of the converter to the increasing slew-rate of load current change. In isolated dc-dc converters, primary-side control is widely used in industry and low-speed optocoupler is commonly used for feedback signal. But typically optocoupler only has 10 to 30 KHz bandwidth and therefore limits the low close-loop bandwidth for the system resulting in slow transient response. Secondary-side control

technique can eliminate the delay of optocoupler to increase the system bandwidth and achieve fast transient response. Active-clamp half bridge dc-dc converter with secondary-side control is presented and one industry standard 16<sup>th</sup> prototype is built and tested; good efficiency and transient response are achieved.

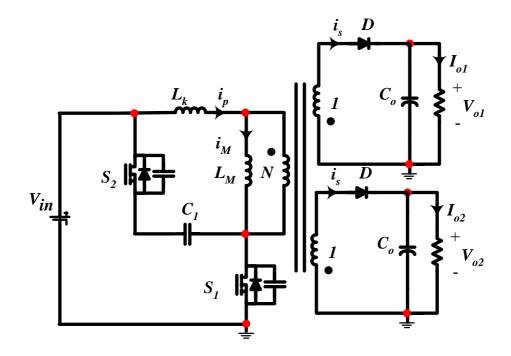

In Chapter Six, a novel hybrid zero-voltage-switching buck-flyback isolated dc-dc converter with synchronous rectification is proposed for multi-output applications. It can be used not only as house-keeping power supplies and standalone power supplies requiring multi-outputs, but also provide solution for start-up issue for secondary-side controlled converter. The operation modes are analyzed quantitatively and dc analysis is discussed, and the design guideline is also provided.

Chapter Seven summaries the work and presents some future work.

### CHAPTER TWO: HALF BRIDGE DC-DC CONVERTER WITH CURRENT DOUBLER RECTIFIER

To further increase the processing speed and decrease the power consumption in VLSI (Very Large Scale Integration) circuits, the operating voltages of ICs keep decreasing with operation current increasing. Therefore the study of an isolated dc-dc topology suitable for low voltage high current applications is a must.

Among the four conventional rectification topologies shown in Figure 1.5, current doubler rectifier (CDR) can minimize transformer secondary-side winding *rms* current and has good transformer utilization. Since only half of the load current flows through each output inductor, the thermal management and inductor magnetic design for the current doubler rectifier is easier than the other three counterparts. Moreover, the current doubler rectifier can step down more voltage than full-bridge and center-tapped rectifiers. In addition, CDR minimizes the number of high current interconnections that simplify secondary side layout and further reduce layout-related losses. Therefore, current doubler rectification is very suitable for low voltage high current applications [12-13].

For the half bridge (HB) topology, the voltage rating of switching devices is half of that required by push-pull and forward converters. Besides, HB has good transformer utilization, and the leakage inductance energy can be recycled to the input capacitors. Due to the input bridge capacitors, HB has an additional 1/2 voltage step-down ratio as compared with forward, flyback, push-pull and full bridge topologies, from the line voltage to the transformer primary-side. For the primary-side topology of isolated dc- dc converters, half-bridge is a good candidate for low-voltage applications. Since current doubler rectifier can be used with half

bridge topology, the half bridge dc-dc converter with current doubler rectifier is a suitable isolated dc-dc switching converter topology for high current low voltage applications [14].

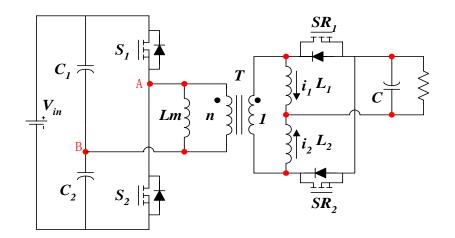

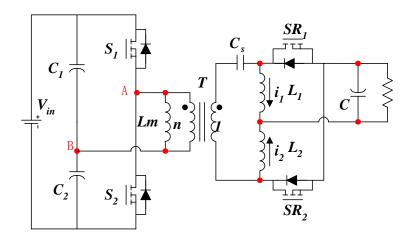

So far there are three control methods for half bridge dc-dc converter with current doubler rectifier: symmetrical control, asymmetrical (complementary) control and duty cycle shifted (DCS) control schemes [16], [33-35]. They all have their own advantages and disadvantages. When the conventional symmetric control is used for the half-bridge converter, its two switches operate at hard-switching with symmetric components stresses. When the asymmetric (complimentary) control is used, the two half-bridge switches operate at soft-switching, but unfortunately causing asymmetric stresses on the converter components which is not desirable especially for wide input voltage range. Moreover, the dc gain is not linear which degrades the converter performance. A recently proposed half-bridge control scheme, the DCS control, results in achieving soft-switching for one of the two half-bridge switches while maintaining symmetric duty cycle and hence symmetric components stresses.

To analyze and design a regulated current doubler rectified half bridge (CDRHB) dc-dc converter, modeling is a must. For optimal analog compensator design, small signal modeling is always necessary. However, few literatures discussed the unified modeling of half-bridge dc-dc converter with current doubler rectifier, which is applicable for all three control methods aforementioned. In addition, recently digital control becomes a hot topic in the power electronics area due to the ease of re-programmability and integration and implementation of nonlinear control laws. Similar to the analog control, a valid digital small signal model is needed for optimal design of digital compensator. However, no literature has derived and discussed the digital small signal model for digitally regulated CDRHB.

In this chapter, the operation and control schemes of half bridge topology with current doubler rectifier is discussed. Then unified state-space model of CDRHB is derived valid for symmetric, asymmetric and DCS control. Based on state-space model, both unified analog and digital small signal models for HB dc-dc converter with CDR are developed respectively.

### **2.1 Topology and Operation**

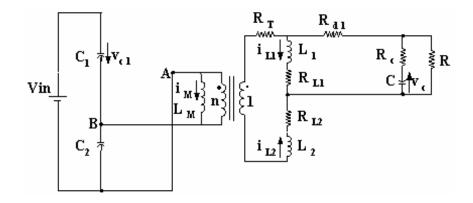

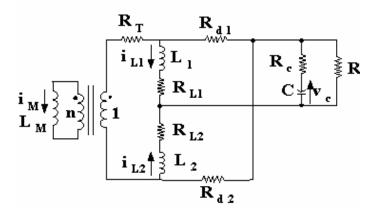

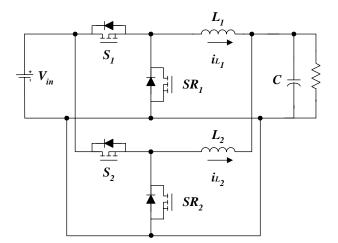

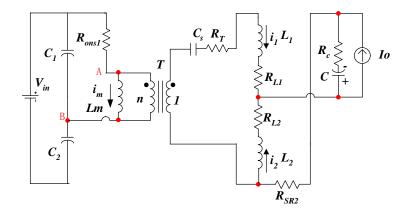

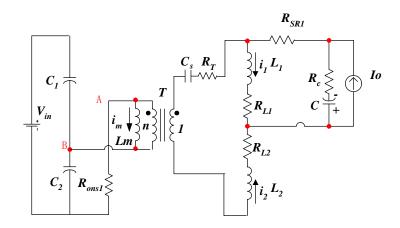

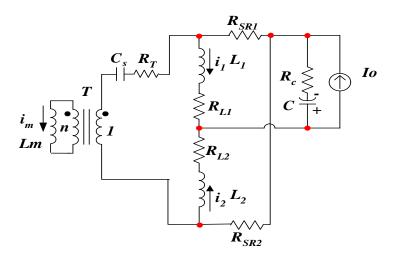

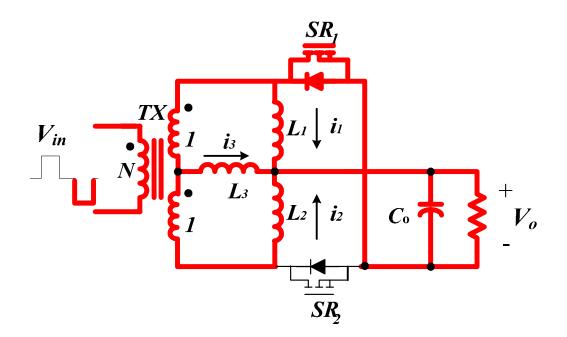

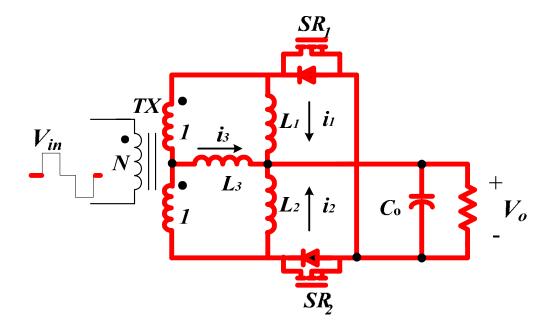

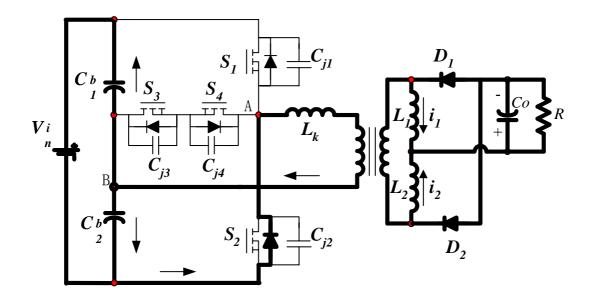

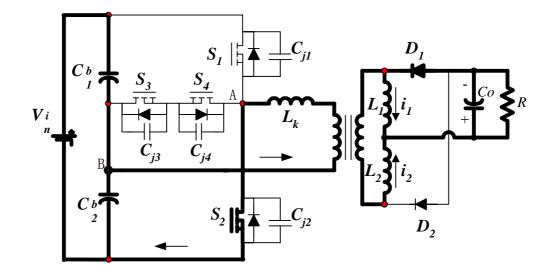

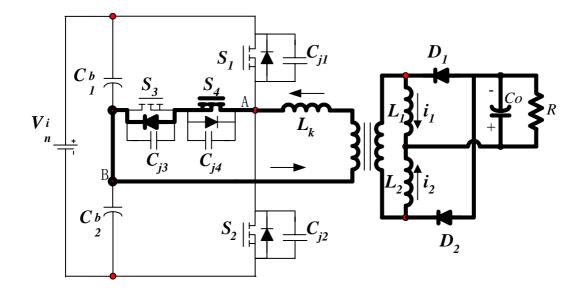

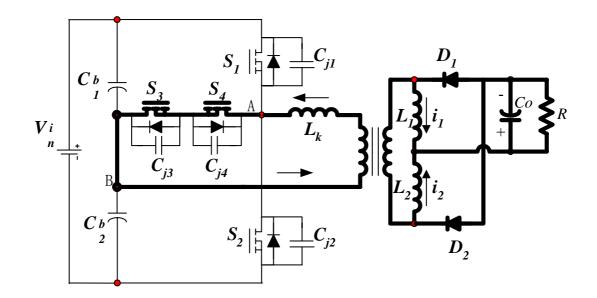

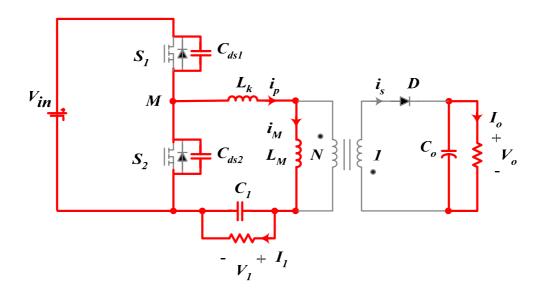

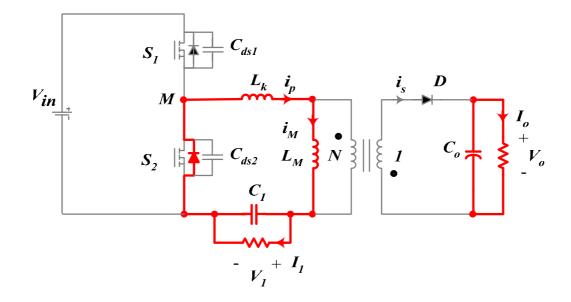

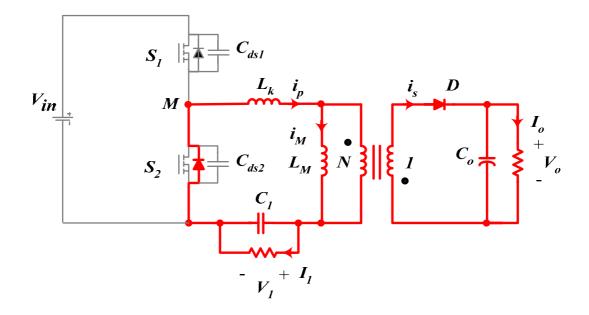

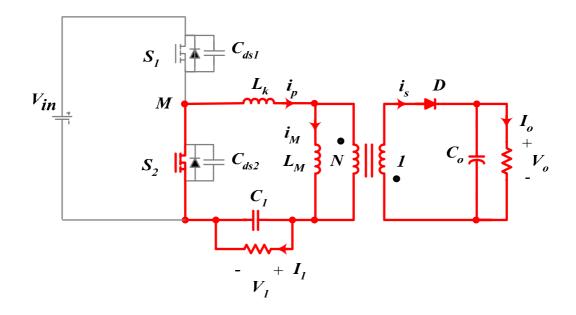

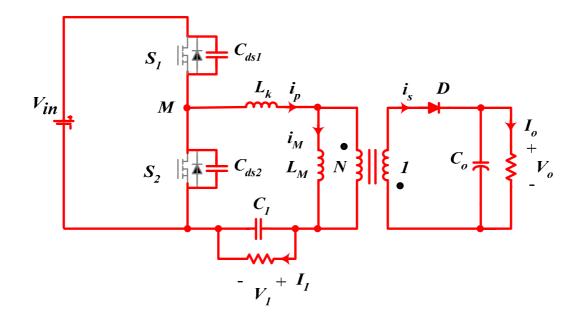

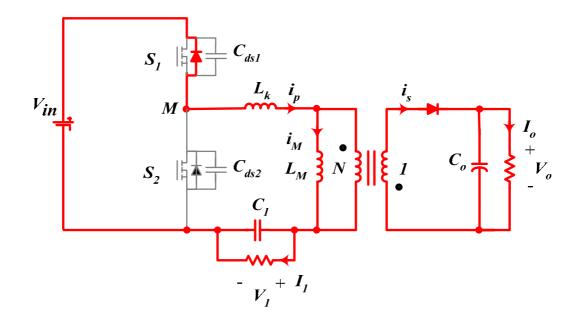

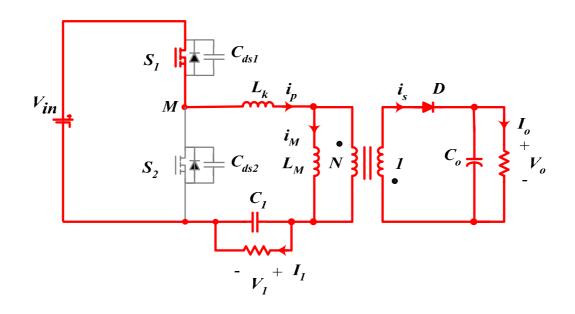

Figure 2.1 shows the half bridge dc-dc converter topology with current doubler rectifier.

Figure 2.1 Half bridge dc-dc converters with current doubler rectifier

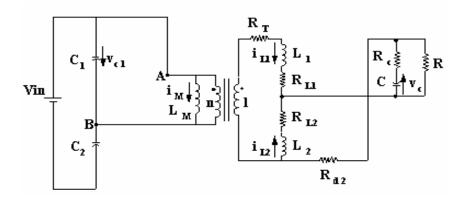

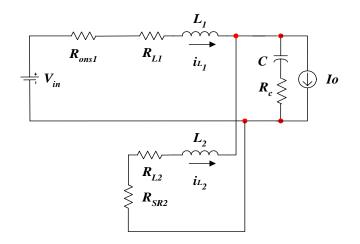

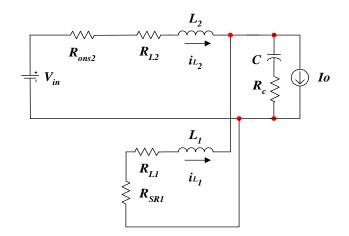

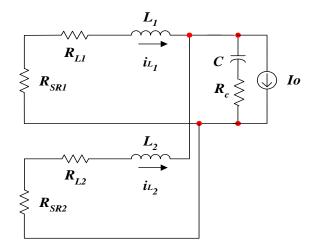

No matter which control scheme is applied, there are three typical operation modes shown in Figure 2.2, supposing the converter operates in continuous conduction mode (CCM) and neglecting transformer leakage energy and transient commutation [15]. In Figure 2.2,  $R_T$  is the equivalent resistance of the reflected switches on-resistance and DCR of the transformer windings,  $R_{L_1}$  and  $R_{L_2}$  are equivalent DCR's of inductor  $L_1$  and  $L_2$ , respectively, and  $R_c$  is the ESR (Equivalent Series Resistance) of the output capacitor

(a) Mode 1:  $S_1$  is on,  $S_2$  is off

(b) Mode 2:  $S_2$  is on,  $S_1$  is off

(c) Mode 3: Both  $S_1$  and  $S_2$  are off

Figure 2.2 Operation modes

#### 2.2 Unified State Space Model for HB Converter with Current Doubler Rectifier

State space equations can be derived according to three different operation modes shown in Figure 2.2 in terms of  $\dot{x} = A_m \cdot x + B_m \cdot u$  and  $y = C_m \cdot x$ , where *m* denotes the corresponding operation mode. The state variable *x* is chosen as  $x = \begin{bmatrix} v_{c_1} & i_1 & i_2 & v_c & i_M \end{bmatrix}^T$ , input  $u = V_{in}$ ,  $\dot{x} = \begin{bmatrix} \frac{dv_{c_1}}{dt} & \frac{di_1}{dt} & \frac{di_2}{dt} & \frac{dv_c}{dt} & \frac{di_M}{dt} \end{bmatrix}^T$  and output is the voltage across the load *R*.

During the on time of switch  $S_1$ ,  $A_1$  and  $B_1$  are as shown in (2-1):

$$A_{1} = \begin{bmatrix} 0 & -\frac{1}{n \cdot (C_{1} + C_{2})} & 0 & 0 & -\frac{1}{C_{1} + C_{2}} \\ \frac{1}{n \cdot L_{1}} & -\frac{R_{r} + R_{L_{1}} + R_{d_{2}} + \frac{R \cdot R_{c}}{R + R_{c}}}{L_{1}} & -\frac{R_{d_{2}} + \frac{R \cdot R_{c}}{R + R_{c}}}{L_{1}} & -\frac{R}{L_{1} \cdot (R + R_{c})} & 0 \\ 0 & -\frac{R_{d_{2}} + \frac{R \cdot R_{c}}{R + R_{c}}}{L_{2}} & -\frac{R_{L_{2}} + R_{d_{2}} + \frac{R \cdot R_{c}}{R + R_{c}}}{L_{2}} & -\frac{R}{L_{2} \cdot (R + R_{c})} & 0 \\ 0 & \frac{R}{C \cdot (R + R_{c})} & \frac{R}{C \cdot (R + R_{c})} & -\frac{1}{C \cdot (R + R_{c})} & 0 \\ \frac{1}{L_{M}} & 0 & 0 & 0 & 0 \end{bmatrix},$$

$$B_{1} = \begin{bmatrix} 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \end{bmatrix}, \quad C_{1} = \begin{bmatrix} 0 & \frac{R_{c} \cdot R}{R + R_{c}} & \frac{R_{c} \cdot R}{R + R_{c}} & \frac{R}{R + R_{c}} & 0 \end{bmatrix}$$

$$(2-1)$$

During the on time of switch S<sub>2</sub>,  $A_2$  and  $B_2$  are as shown in (2-2):

$$A_{2} = \begin{bmatrix} 0 & 0 & \frac{1}{n \cdot (C_{1} + C_{2})} & 0 & -\frac{1}{C_{1} + C_{2}} \\ 0 & -\frac{R_{L_{1}} + R_{d_{1}} + \frac{R \cdot R_{c}}{R + R_{c}}}{L_{1}} & -\frac{R_{d_{1}} + \frac{R \cdot R_{c}}{R + R_{c}}}{L_{1}} & -\frac{R}{L_{1} \cdot (R + R_{c})} & 0 \\ -\frac{1}{n \cdot L_{2}} & -\frac{R_{d_{1}} + \frac{R \cdot R_{c}}{R + R_{c}}}{L_{2}} & -\frac{R_{T} + R_{L_{2}} + R_{d_{1}} + \frac{R \cdot R_{c}}{R + R_{c}}}{L_{2}} & -\frac{R}{L_{2} \cdot (R + R_{c})} & 0 \\ 0 & \frac{R}{C \cdot (R + R_{c})} & \frac{R}{C \cdot (R + R_{c})} & -\frac{1}{C \cdot (R + R_{c})} & 0 \\ \frac{1}{L_{M}} & 0 & 0 & 0 & 0 \end{bmatrix},$$

$$B_{2} = \begin{bmatrix} \frac{1}{n \cdot L_{2}} \\ 0 \\ -\frac{1}{L_{M}} \end{bmatrix}, \quad C_{2} = \begin{bmatrix} 0 & \frac{R_{c} \cdot R}{R + R_{c}} & \frac{R_{c} \cdot R}{R + R_{c}} & \frac{R}{R + R_{c}} & 0 \end{bmatrix}$$

(2-2)

During the off time of both S<sub>1</sub> and S<sub>2</sub>, (2-3) shows the corresponding  $A_3$  and  $B_3$ :

$$B_{3} = \begin{bmatrix} 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & -\frac{R_{L_{1}} + R_{d_{1}} + \frac{R \cdot R_{c}}{R + R_{c}}}{L_{1}} & -\frac{R \cdot R_{c}}{L_{1} \cdot (R + R_{c})} & -\frac{R}{L_{1} \cdot (R + R_{c})} & -\frac{n \cdot R_{d_{1}}}{L_{1}} \\ 0 & -\frac{R \cdot R_{c}}{L_{2} \cdot (R + R_{c})} & -\frac{R_{L_{2}} + R_{d_{2}} + \frac{R \cdot R_{c}}{R + R_{c}}}{L_{2}} & -\frac{R}{L_{2} \cdot (R + R_{c})} & -\frac{n \cdot R_{d_{2}}}{L_{2}} \\ 0 & \frac{R}{C \cdot (R + R_{c})} & \frac{R}{C \cdot (R + R_{c})} & -\frac{1}{C \cdot (R + R_{c})} & 0 \\ 0 & -\frac{n \cdot R_{d_{1}}}{L_{M}} & \frac{n \cdot R_{d_{2}}}{L_{M}} & 0 & -\frac{n^{2} \cdot (R_{T} + R_{d_{2}} + R_{d_{1}})}{L_{M}} \end{bmatrix} \end{bmatrix}$$

$$B_{3} = \begin{bmatrix} 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \end{bmatrix} \quad C_{3} = \begin{bmatrix} 0 & \frac{R_{c} \cdot R}{R + R_{c}} & \frac{R_{c} \cdot R}{R + R_{c}} & \frac{R}{R + R_{c}} & 0 \end{bmatrix}$$

$$(2-3)$$

In order to obtain a unified state space averaged model [33], let the switching cycle be T, the on time of switch S<sub>1</sub> and S<sub>2</sub> are  $d_1 \cdot T$  and  $d_2 \cdot T$ , respectively. Then the unified state space averaged model for half bridge current doubler converter can be derived as follows:

where,

$$A = d_1 A_1 + d_2 A_2 + (1 - d_1 - d_2) A_3$$

(2-5)

$$B = d_1 B_1 + d_2 B_2 + (1 - d_1 - d_2) B_3$$

(2-6)

and

$$C = \begin{bmatrix} 0 & \frac{R_c \cdot R}{R + R_c} & \frac{R_c \cdot R}{R + R_c} & \frac{R}{R + R_c} & 0 \end{bmatrix}$$

(2-7)

#### 2.3 Unified Analog Small Signal Model for HB Current Doubler Converter

Based on the unified state space averaged model derived in section 2.2, the analog small signal model is further developed in this section. In general, let  $x = X_{ss} + \hat{x}$ ,  $y = Y_{ss} + \hat{y}$ ,  $u = V_{in} + \hat{v_{in}}$ ,  $d_1 = D_1 + \hat{d}_1$ , and  $d_2 = D_2 + \hat{d}_2$ , where  $X_{ss}$ ,  $Y_{ss}$ ,  $V_{in}$ ,  $D_1$  and  $D_2$  are the steady state values of  $x, y, v_{in}, d_1$  and  $d_2$  respectively, and  $\hat{x}, \hat{y}, \hat{v_{in}}, \hat{d}_1$  and  $\hat{d}_2$  represent the small signal disturbances. In the steady state,  $\hat{x} = A \cdot X_{ss} + B \cdot V_{in} = 0$ , then the following can be determined:

$$X_{ss} = -A_{ss}^{-1} \cdot B_{ss} \cdot V_{in} \tag{2-8}$$

From (2-4), (2-9) can be derived as follows:

$$\frac{\partial \hat{x}}{\partial t} \approx \frac{\partial f}{\partial x} \cdot \hat{x} + \frac{\partial f}{\partial v_{in}} \cdot \hat{v}_{in} + \frac{\partial f}{\partial d_1} \cdot \hat{d}_1 + \frac{\partial f}{\partial d_2} \cdot \hat{d}_2$$

(2-9)

Based on (2-4) and (2-8)  $\sim$  (2-9), we can conduct unified small signal analysis for CDRHB converters.

| Control<br>Scheme   | Duty Cycle          | $G_{vg}(s) = \frac{\stackrel{\wedge}{v}_{o}}{\stackrel{\vee}{v}_{in}}$ | $G_{vd} (s) = \frac{\hat{v}_o}{\hat{d}}$                                                                              |

|---------------------|---------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Symmetric           | $D_1 = D_2 = D$     | $C \cdot (s \cdot I - A_{ss})^{-1} \cdot B_{ss}$                       | $C \cdot (s \cdot I - A_{ss})^{-1} [(A_1 + A_2 - 2 \cdot A_3) \cdot X_{ss} + (B_1 + B_2 - 2 \cdot B_3) \cdot V_{in}]$ |

| Asymmetric          | $D_1 = 1 - D_2 = D$ | $C \cdot (s \cdot I - A_{ss})^{-1} \cdot B_{ss}$                       | $C \cdot (s \cdot I - A_{ss})^{-1} [(A_1 - A_2) \cdot X_{ss} + (B_1 - B_2) \cdot V_{in}]$                             |

| Duty Cycle<br>Shift | $D_1 = D_2 = D$     | $C \cdot (s \cdot I - A_{ss})^{-1} \cdot B_{ss}$                       | $C \cdot (s \cdot I - A_{ss})^{-1} [(A_1 + A_2 - 2 \cdot A_3) \cdot X_{ss} + (B_1 + B_2 - 2 \cdot B_3) \cdot V_{in}]$ |

Table 2-1 Transfer functions for analog controlled half bridge current doubler converters with different control schemes

## 2.4 Unified Digital Small Signal Model for HB Current Doubler Converter

For developing the linear time invariant (LTI) digital model of the half bridge dc-dc converter with current doubler rectification in Figure 2.1, the following assumptions should be made:

- ➤ The converter operates in CCM;

- >  $V_{in}$  is constant within each switching cycle;

> There is no ripple in the inductors currents and output capacitor voltage.

For simplicity, the digital model of the symmetric half bridge converter with current doubler rectifier will be derived first.

Assuming that the derivation starts from the k<sup>th</sup> switching cycle, using the Forward

Euler approximation method as follows:

$$x(t_0 + \varepsilon) \approx x(t) + \varepsilon \frac{dx(t_0)}{dt}$$

(2-10)

When  $kT < t \le kT + d_1T$ , converter operates in mode 1 (switch S<sub>1</sub> is on), according to Forward Euler approximation, we can get

$$x(kT + d_1T) \approx x(kT) + d_1T \cdot (A_1 \cdot x(kT) + B_1 \cdot V_{in}[k])$$

(2-11)

After reformatting (2-11),

$$x(kT + d_1T) \approx [I + d_1T \cdot A_1]x(kT) + d_1T \cdot B_1 \cdot V_{in}[k]$$

(2-12)

When  $kT + d_1T < t \le kT + d_1T + \frac{1 - d_1 - d_2}{2}T$ , the converter operates in

mode 3 (both  $S_1$  and  $S_2$  is off), so after Forward Euler approximation:

$$x(kT + d_1T + \frac{1 - d_1 - d_2}{2}T) \approx x(kT + d_1T) + \frac{1 - d_1 - d_2}{2}T \cdot (A_3 \cdot x(kT + d_1T) + B_3 \cdot V_{in}[k])$$

(2-13)

After reformatting (2-13), the following is obtained:

$$x(kT + d_{1}T + \frac{1 - d_{1} - d_{2}}{2}T) \approx [I + \frac{1 - d_{1} - d_{2}}{2}T \cdot A_{3}]x(kT + d_{1}T) + \frac{1 - d_{1} - d_{2}}{2}T \cdot B_{3} \cdot V_{in}[k]$$

(2-14)

When

$$kT + d_1T + \frac{1 - d_1 - d_2}{2}T < t \le kT + d_1T + \frac{1 - d_1 - d_2}{2}T + d_2T$$

,

converter operates in mode 2 (S<sub>2</sub> is on),

$$x(kT + (d_1 + d_2)T + \frac{1 - d_1 - d_2}{2}T) \approx x(kT + d_1T + \frac{1 - d_1 - d_2}{2}T) + d_2T \cdot (A_2 \cdot x(kT + d_1T + \frac{1 - d_1 - d_2}{2}T) + B_2 \cdot V_{in}[k])$$

(2-15)

After reformatting (2-15),

$$x(kT + (d_1 + d_2)T + \frac{1 - d_1 - d_2}{2}T) \approx [I + d_2T \cdot A_2]x(kT + d_1T + \frac{1 - d_1 - d_2}{2}T) + d_2T \cdot B_2 \cdot V_{in}[k]$$

(2-16)

When  $kT + d_1T + \frac{1 - d_1 - d_2}{2}T + d_2T < t \le kT + T$ , converter operates

in mode 3 (both  $S_1$  and  $S_2$  is off), so:

$$x(kT+T) \approx x(kT + (d_1 + d_2)T + \frac{1 - d_1 - d_2}{2}T) + \frac{1 - d_1 - d_2}{2}T \cdot (A_3 \cdot x(kT + (d_1 + d_2)T + \frac{1 - d_1 - d_2}{2}T) + B_3 \cdot V_{in}[k])$$

(2-17)

After reformatting, (2-18) can be written as follows:

$$x(kT+T) \approx \left[I + \frac{1 - d_1 - d_2}{2}T \cdot A_3\right] x(kT + (d_1 + d_2)T + \frac{1 - d_1 - d_2}{2}T) + \frac{1 - d_1 - d_2}{2}T \cdot B_3 \cdot V_{in}[k]$$

(2-18)

Then substitute (2-12), (2-14) and (2-16) to (2-18) and neglect the terms including  $T^N$  ( $N \ge 2$ ), a state space digital model is developed as follows:

$$x[k+1] = [I + A \cdot T]x[k] + B \cdot T \cdot V_{in}[k] = \phi(x[k], v_{in}[k], d_1, d_2)$$

(2-19)

In order to derive the LTI digital model, linearization of the digital model (2-19) at the steady state operation point is taken to obtain:

$$\hat{x}[k+1] \approx \frac{\partial \phi}{\partial x} \hat{x}[k] + \frac{\partial \phi}{\partial v_{in}} v_{in} \hat{k}] + \frac{\partial \phi}{\partial d_1} \hat{d_1} + \frac{\partial \phi}{\partial d_2} \hat{d_2}$$

$$y \hat{k} = C \cdot x \hat{k}$$

(2-20)

And in steady state,  $x[k+1] = x[k] = X_{ss}$ , from (2-19), it can be derived as follows:

$$X_{ss} = -A_{ss}^{-1} \cdot B_{ss} \cdot V_{in}$$

(2-21)

The deviations in (2-22) can also be derived from (2-19) to obtain the LTI digital model:

$$\hat{x}[k+1] \approx (I + A_{ss} \cdot T) \hat{x}[k] + B_{ss} \cdot T \cdot v_{in}[k] + [(A_1 - A_3)X_{ss} + (B_1 - B_3)V_{in}] \cdot T \cdot \hat{d}_1 + [(A_2 - A_3)X_{ss} + (B_2 - B_3)V_{in}] \cdot T \cdot \hat{d}_2 \hat{y}[k] = C \cdot \hat{x}[k]$$

(2-22)

Although the above derivations are based on the symmetric controlled half bridge current doubler dc-dc converter, the linearized digital model (2-20) is unified, and only different in derivatives in (2-20) according to the different control schemes.

Different transfer functions can also be derived based on different control schemes from the LTI digital model in (2-22), and they are listed in table 2-2.

| control schemes     |                     |                                                  |                                                                                                                                             |  |

|---------------------|---------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

| Control             | Duty Cycle          | ^                                                | Λ                                                                                                                                           |  |

| Scheme              |                     | $G_{vg}(z) = \frac{v_o}{\frac{1}{N}}$            | $G_{vd}$ $(z) = \frac{v_o}{\hat{d}}$                                                                                                        |  |

| Symmetric           | $D_1 = D_2 = D$     | $C \cdot (s \cdot I - A_{ss})^{-1} \cdot B_{ss}$ | $C \cdot (z \cdot I - A_{ss} \cdot T)^{-1} \cdot T \cdot [(A_1 + A_2 - 2 \cdot A_3) \cdot X_{ss} + (B_1 + B_2 - 2 \cdot B_3) \cdot V_{in}]$ |  |

| Asymmetric          | $D_1 = 1 - D_2 = D$ | $C \cdot (s \cdot I - A_{ss})^{-1} \cdot B_{ss}$ | $C \cdot (z \cdot I - A_{ss} \cdot T)^{-1} \cdot T \cdot [(A_1 - A_2) \cdot X_{ss} + (B_1 - B_2) \cdot V_{in}]$                             |  |

| Duty Cycle<br>Shift | $D_1 = D_2 = D$     | $C \cdot (s \cdot I - A_{ss})^{-1} \cdot B_{ss}$ | $C \cdot (z \cdot I - A_{ss} \cdot T)^{-1} \cdot T \cdot [(A_1 + A_2 - 2 \cdot A_3) \cdot X_{ss} + (B_1 + B_2 - 2 \cdot B_3) \cdot V_{in}]$ |  |

Table 2-2

Transfer functions for digital controlled half bridge current doubler converters with different control schemes

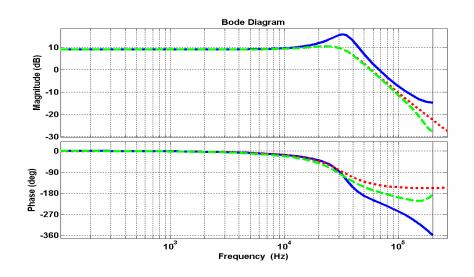

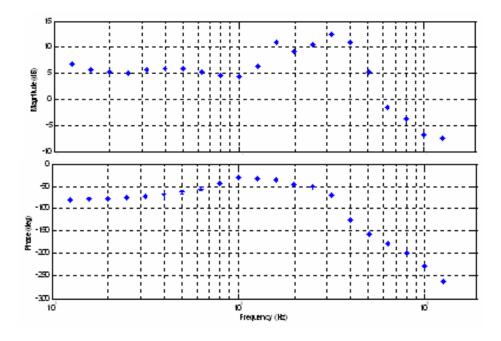

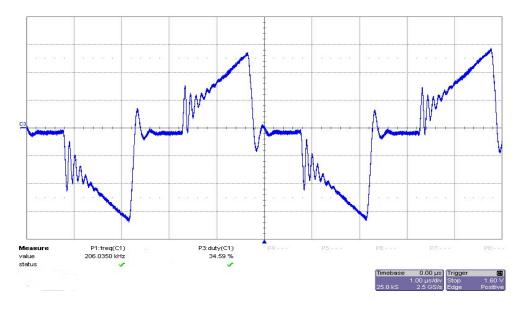

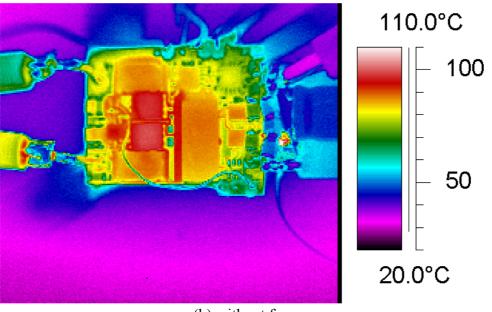

For comparison, bode plot of the derived digital small signal model is depicted in Figure 2.3 together with bode plots of analog small signal model and discretized analog model. The converter's specifications are Vin =48V, n=6, Vo=1V, Io= 50A, Co=1000 uF, Lo= 90 nH, and switching frequency of 400 KHz. It can be found that differences exist among these three models at high frequencies. Because digital systems will have additional phase shift compared to analog systems, a difference between the analog model and the digital model can be noticed at the high frequencies. Furthermore, it can be noticed that the discretized analog model starts to alias as it approaches half of the sampling frequency. Therefore, it can be concluded that the derived digital model is more valid than the other two models for digital compensator design

of the digitally controlled half bridge dc-dc converter.

Figure 2.3 Bode diagrams of three converter models

(Dot trace: analog model, dash trace: discretized analog model,

solid trace: digital model)

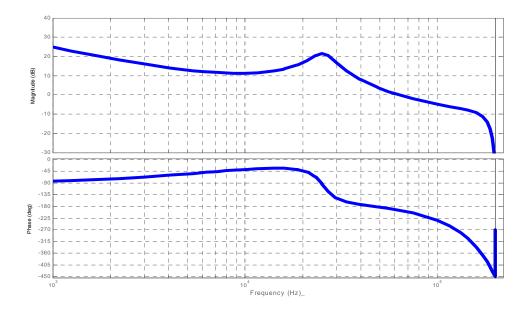

A digital compensator based on the digital model of the converter is designed and the bode plot of its loop gain is shown in Figure 2.4. A prototype with the same design specification is built and the close loop bode plot is shown in Figure 2.5. The experimental results match theoretical design and therefore verify the derived digital model.

Figure 2.4 Close loop gain of theoretical design

Figure 2.5 Close loop gain of experimental result

#### 2.5. Digital Control of HB DC-DC Converter with Current Doubler Rectifier

The specifications of the half-bridge dc-dc converter prototype with current doubler rectification are listed as follows:

Based on the small signal model of HB dc-dc converter and digital controller design theory, the digital controller is designed as follows:

$$Hc(z) = \frac{0.6113z^3 - 0.2847z^2 - 0.5968z + 0.2992}{z^3 - 1.418z^2 + 0.4619z - 0.04364}$$

(2-23)

The corresponding difference equation representation of the designed compensator is D [n] = 1.418 D [n-1] - 0.4619 D [n-2] + 0.0436 D [n-3]+0.6113 e[n] -0.2847e [n-1]-0.5968 e [n-2] + 0.2992e [n-3] (2-24)

The digital compensator is implemented by TMS320F2812 DSP chip with DSP program with C language. A 12 bit ADC with 80 ns conversion time is set up for the digital controller in TMS320F2812 DSP chip. The DPWM can support 16 bit maximum resolution [24-27].

The DPWM generators in the DSP chip can generate symmetrical, asymmetrical and DCS PWM control signals for the half-bridge power stage.

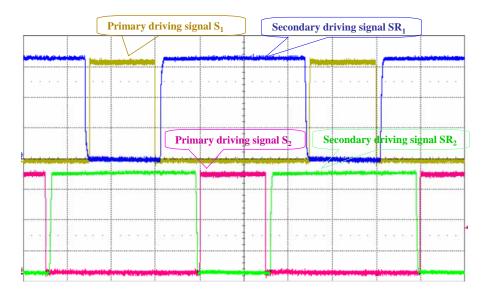

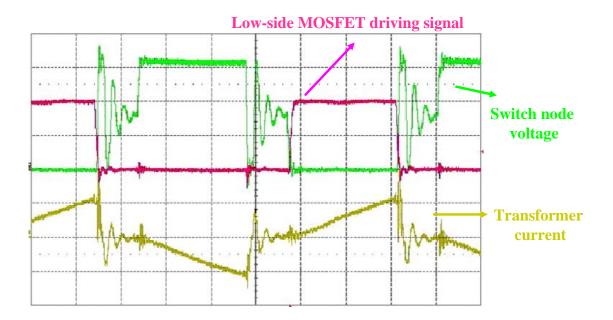

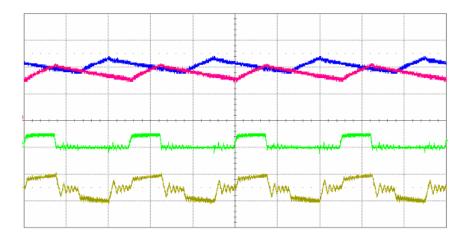

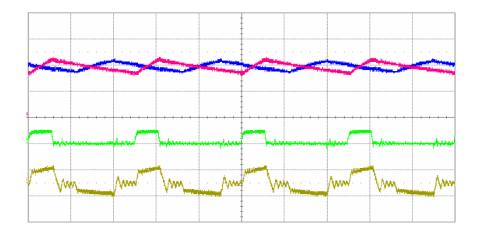

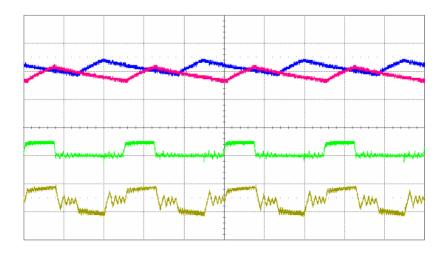

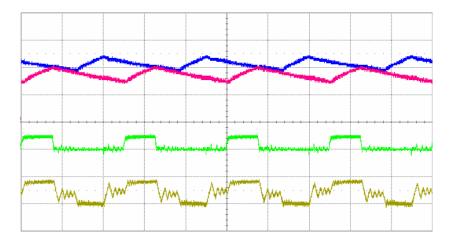

Figure 2.6 shows the primary and secondary gate driving signals with 100ns dead time for HB with symmetrical control, which is generated by the DSP chip TMS320F2812. The two primary-side driving signals have the same duty cyle with a 180-degree phase shift, and the secondary-side driving signals are the complementary signals of the primary-side signals with a programmable dead time. In Figure 2.7, the asymmetrical primary-side gate driving signals are shown with 100ns dead-time. Actually, the dead-times mentioned above are adjustable and programmable with DSP compensation program.

Figure 2.6: The primary-side and secondary-side gate driving signals with 100ns dead-time in

symmetrical control case

Figure 2.7: The gate signals with 100ns dead-time in asymmetrical control case.

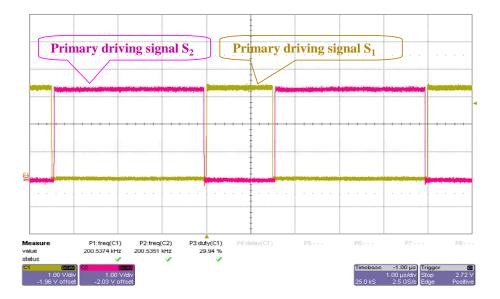

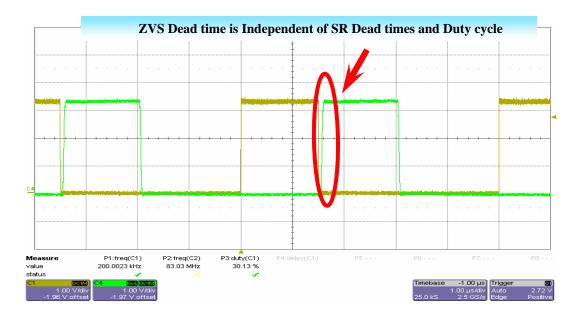

Figure 2.8 shows the primary-side driving signals with 100ns dead-time in DCS control case. DCS control is used to reduce primary-side ringing of the signals. In DCS case, the two primary-side driving signals have the same duty cycle and shifted next to each other but with a fixed dead-time as compared with the traditional symmetrical control scheme. This dead-time is independent of the duty cycle and SR dead-time. Figure 2.9 shows the output voltage with significant noise and in this case the output is hard to regulate.

Figure 2.8: The primary signals with 100ns dead time in a DCS case

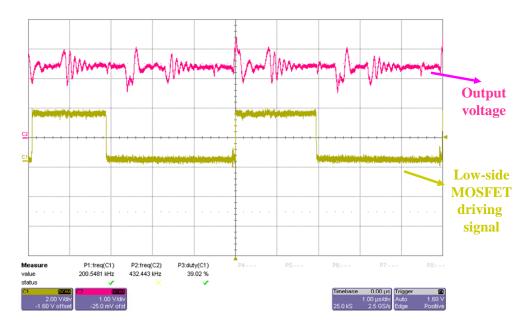

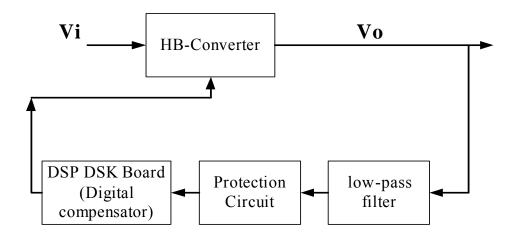

In the actual experiments, the close loop system was set up with the DSP-controlled HB power train as shown in Figure 2.10. The low-pass filter was used between the output of power stage and ADC input of the DSP board to filter out the switching noise. This filter also behaves as an anti-liaising filter for the sampling of the ADC. The protection circuit is used to give a voltage limit from 0 volts to 3 volts for the input signal of the DSP since that is the

range the DSP can accept.

Figure 2.9: The output voltage with significant noise

Figure 2.10: Close loop diagram with power stage and DSP controller

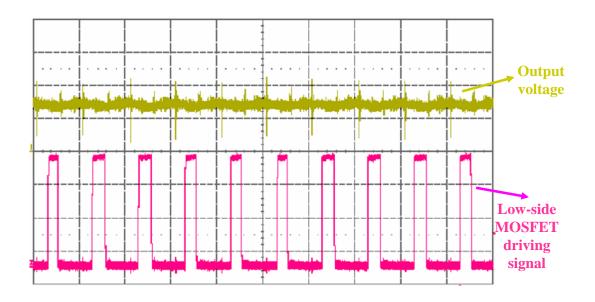

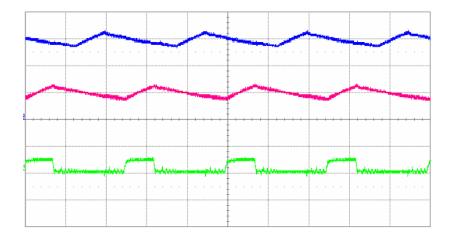

Figure 2.11 shows the output voltage and the gate signal for the closed-loop DSP

controller. In this case, the input voltage is 48 volts. It can be seen that the output voltage is regulated to the reference voltage of 1.5 volts, which is actually set up by the DSP program. The duty cycle is regulated at D=0.26, which is the calculation result of a digital PI compensator based on the error difference compared to the reference voltage. Figure 2.12 and 2.13 show the transformer primary-side current at steady state.

Figure 2.11: The output voltage 1.5 volt and gate signal with 0.26 duty cycle at steady state with a DSP controller (digital PI compensator) in symmetrical control case

Figure 2.12: The transformer primary current waveform for symmetrical control case

Figure 2.13: The transformer primary-side current and switch-node voltage

## CHAPTER THREE: CURRENT SHARING ANALYSIS OF CURRENT DOUBLER RECTIFIER

With the increased output currents in both isolated and non-isolated Point-of-Load (POL) converters, the number of phases in a converter and the number of paralleled converters have been increasing. For high output current and low output voltage, the current sharing among paralleled channels is highly demanded, because uneven current distribution causes inductor saturation, thermal stresses and degraded converter performance [45-50]. Current sharing control with paralleled converters is generally implemented with external load sharing circuitry [45]. In voltage regulators (VRs) for microprocessors, multi-phase interleaved synchronous-rectifier (SR) buck converters are controlled by dedicated ICs with built-in current-sharing circuitry [45-47]. Various current sharing methods and circuitry have been documented and utilized in industry [45-50]. However, the original numerical analysis of the current sharing in multi-phase interleaved buck converters is not investigated in depth and open-loop current sharing steady-state models are not established in term of various parameters in the converters.

For isolated dc-dc converters, the interleaving concept enables converter topologies to operate at increased power levels. Other benefits include: reduced input and output voltage/current ripples, better thermal management and improved transient response [51]. Current Doubler Rectifier (CDR) is a good topology for low output voltage high output current applications. Actually, CDR is similar to an interleaved two-phase buck converter in term of rectification architecture. The current sharing issue between two inductors in CDR is brought up and the generalized current-sharing dc model is established in [52-53].

In this chapter, the current sharing characteristic in an interleaved buck converter is analyzed and compared with the current sharing model of the CDR in isolated dc-dc converters. Design guidelines are provided based on numerical analyses. Furthermore, a new CDR topology is proposed to achieve passive current sharing without additional current sharing control circuitry, which is verified by mathematical model and experimental results.

#### 3.1 DC Current Sharing Analysis in the Interleaved Two-phase Buck Converters

A two-phase buck converter is shown in Figure. 3.1. Assuming driving signals of the two channels are interleaved with 180<sup>°</sup> phase difference, and under ideal conditions, two phases' parameters are absolutely symmetric. This means filter inductance, FET on-resistance and inductor DCR values in channel 1 and 2 are identical. Besides, actual duty cycles for each channel are identical.

In practice, the two channels of the converter are asymmetric, and even the actual duty cycle values of each channel may not be equal due to different driver propagation and FETs turn-on and turn-off delays. In this case, it is unlikely the two inductors carry equal average currents because of possible asymmetry parameters. dc modeling under asymmetric conditions will be provided thorough analytic equations below.

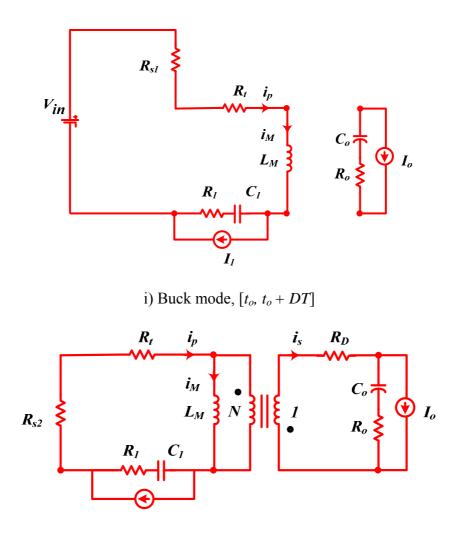

Figure 3.1. Two-phase buck converter

Average modeling method in [52-55] can be applied to the analysis. Assuming steady-state duty cycles  $D_1 < 0.5$ ,  $D_2 < 0.5$ , and the converter modes of operation can be concluded in three modes as shown in Figure. 3.2 (a), (b) and (c).

For each mode during the period, the converter can be denoted using a set of linear state-space equations. Corresponding to three modes of operation, three sets of state-space equations are expressed as (3-1), where *x* is the vector of state variables, u is the vector of independent sources;  $A_1$ ,  $B_1$ ,  $A_2$ ,  $B_2$ ,  $A_3$  and  $B_3$  are respective system matrices for each of the three switched networks.

$$x = A_m x + B_m u \quad (m = 1, 2, 3)$$

(3-1)

The state-space variables are defined as follows:

$$\mathbf{\dot{x}} = \begin{bmatrix} \frac{di_{L1}}{dt} & \frac{di_{L2}}{dt} & \frac{dv_C}{dt} \end{bmatrix}^T$$

(3-2)

$$x = \begin{bmatrix} i_{L1} & i_{L2} & v_C \end{bmatrix}^T;$$

$$u = \begin{bmatrix} V_{in} & I_o \end{bmatrix}^T$$

(3-3)

$A_1$ ,  $B_1$ ,  $A_2$ ,  $B_2$ ,  $A_3$  and  $B_3$  can be derived from modes of operation in Figure. 3.2(a), (b) and (c), respectively. Assuming the duty cycle of the switch S<sub>1</sub> and S<sub>2</sub> are d<sub>1</sub> and d<sub>2</sub>, respectively. The key concept in state-space averaging is the replacement of the above three sets of state-space equations by a single equivalent set [54]

where the equivalent matrices are defined by

$$A = d_1 A_1 + d_2 A_2 + (1 - d_1 - d_2) A_3$$

$$B = d_1 B_1 + d_2 B_2 + (1 - d_1 - d_2) B_3$$

(3-5)

where,  $A_1$ ,  $B_1$  are state-space matrices of Mode 1;  $A_2$  and  $B_2$  are state-space matrices of Mode 2;  $A_3$  and  $B_3$  are state-space matrices of Mode 3. All these matrices can be derived from Figure. 3.2 as follows:

$$A_{1} = \begin{bmatrix} -\frac{R_{C} + R_{L1} + R_{onS1}}{L_{1}} & -\frac{R_{C}}{L_{1}} & -\frac{1}{L_{1}} \\ -\frac{R_{C}}{L_{2}} & -\frac{R_{L2} + R_{C} + R_{SR2}}{L_{2}} & -\frac{1}{L_{2}} \\ \frac{1}{C} & \frac{1}{C} & 0 \end{bmatrix}$$

$$A_{2} = \begin{bmatrix} -\frac{R_{C} + R_{L1} + R_{SR1}}{L_{1}} & -\frac{R_{C}}{L_{1}} & -\frac{1}{L_{1}} \\ -\frac{R_{C}}{L_{2}} & -\frac{R_{L2} + R_{C} + R_{onS2}}{L_{2}} & -\frac{1}{L_{2}} \\ \frac{1}{C} & \frac{1}{C} & 0 \end{bmatrix}$$

$$A_{3} = \begin{bmatrix} -\frac{R_{C} + R_{L1} + R_{SR1}}{L_{1}} & -\frac{R_{C}}{L_{1}} & -\frac{1}{L_{1}} \\ -\frac{R_{C}}{L_{2}} & -\frac{R_{L2} + R_{C} + R_{SR2}}{L_{2}} & -\frac{1}{L_{2}} \\ \frac{1}{C} & \frac{1}{C} & 0 \end{bmatrix}$$

$$B_{1} = \begin{bmatrix} \frac{1}{L_{1}} & \frac{R_{C}}{L_{1}} \\ 0 & \frac{R_{C}}{L_{2}} \\ 0 & -\frac{1}{C} \end{bmatrix}; \quad B_{2} = \begin{bmatrix} 0 & \frac{R_{C}}{L_{1}} \\ \frac{1}{L_{2}} & \frac{R_{C}}{L_{2}} \\ 0 & -\frac{1}{C} \end{bmatrix}; \quad B_{3} = \begin{bmatrix} 0 & \frac{R_{C}}{L_{1}} \\ 0 & \frac{R_{C}}{L_{2}} \\ 0 & -\frac{1}{C} \end{bmatrix};$$

The steady-state solution, with dc values indicated by capital letters, is obtained by setting  $\dot{x} = 0$

$$X = -A^{-1}B U$$

(3-6)

Through (3-1)  $\sim$  (3-6), the steady-state dc quiescent points can be derived and the

inductor dc currents are:

$$I_{L1} = \frac{(D_1 - D_2)V_{in} + [(1 - D_2)R_{SR2} + D_2R_{onS2} + R_{L2}]I_o}{D_1R_{onS1} + D_2R_{onS2} + (1 - D_1)R_{SR1} + (1 - D_2)R_{SR2} + R_{L1} + R_{L2}}$$

(3-7)

$$I_{L2} = \frac{(D_2 - D_1)V_{in} + [(1 - D_1)R_{SR1} + D_1R_{onS1} + R_{L1}]I_o}{D_1R_{onS1} + D_2R_{onS2} + (1 - D_1)R_{SR1} + (1 - D_2)R_{SR2} + R_{L1} + R_{L2}}$$

(3-8)

(a) Mode 1:  $S_1$ ,  $SR_2$  on;  $S_2$ ,  $SR_1$  off

(b) Mode 2:  $S_2$ ,  $SR_1$  on;  $S_1$ ,  $SR_2$  off

Mode 3: SR<sub>1</sub>, SR<sub>2</sub> on; S<sub>1</sub>, S<sub>2</sub> off

Figure 3.2. Modes of operation

To simplify the above equations, we define the equivalent resistance of phase 1 and phase 2, respectively:

$$R_{eq\_ch1} = (1 - D_1)R_{SR1} + D_1R_{onS1} + R_{L1}$$

(3-9)

$$R_{eq\_ch2} = (1 - D_2)R_{SR2} + D_2R_{onS2} + R_{L2}$$

(3-10)

Equation (3-7) and (3-8) are reformed as:

$$I_{L1} = \frac{(D_1 - D_2)V_{in}}{R_{eq\_ch1} + R_{eq\_ch2}} + \frac{R_{eq\_ch2}}{R_{eq\_ch1} + R_{eq\_ch2}} I_o$$

(3-11)

$$I_{L2} = \frac{(D_2 - D_1)V_{in}}{R_{eq\_ch1} + R_{eq\_ch2}} + \frac{R_{eq\_ch1}}{R_{eq\_ch1} + R_{eq\_ch2}}I_o$$

(3-12)

From (3-11) and (3-12), we may conclude:

(a) Inductance and capacitance values have no effect on current sharing between two

filter inductors.

- (b) Current sharing can be achieved if the two channels operate under both equal duty cycle and balanced resistance.

- (c) Under asymmetric dc resistances ( $R_{eq\_ch1} \neq R_{eq\_ch2}$ ), current sharing can be achieved by adjusting duty cycle values. Increasing duty cycle value in one channel leads to an increase in average current of this channel. This current sharing technique has been widely utilized in current sharing of VR (M)s.

- (d) To achieve balanced current sharing, duty cycles has to be adjusted to satisfy:

$$D_1 - D_2 = \frac{R_{eq\_ch1} - R_{eq\_ch2}}{V_{in}} \frac{I_o}{2}$$

(3-13)

#### 3.2 Current Sharing of Current Doubler Rectifier in Isolated DC-DC Converters

As shown above, the analytic results show that all dc parameters in an interleaved buck converter have effect on current sharing, and, fortunately, imbalance of average phase currents can be calibrated by adjusting phase duty cycles.

Current doubler rectifier shows good performance in low-voltage double-ended isolated dc-dc converters, such as full bridge and push pull. In such isolated topologies, peak current mode control can be implemented to achieve balanced dc currents. However, for half bridge topology with a current doubler rectifier, peak current mode control cannot be implemented due to collapse of an input capacitor voltage [56]. Therefore, current sharing in the topology is worth investigating. Figure 3.3 shows a half bridge dc-dc converter with a current doubler rectifier. Compared with interleaved two-phase buck converters, the primary

switches are corresponding to upper switches in the buck converter. Assuming the converter operates under asymmetric dc parameters and duty cycles. Transformer primary winding resistance is  $R_{Tp}$  and secondary winding resistance is  $R_{Ts}$ ;  $R_{L1}$  and  $R_{L2}$  are inductor DCR values. Like in an interleaved buck converter,  $S_1$  gate signal and  $SR_1$  gate signal are complementary as in a channel; and  $S_2$  and  $SR_2$  gate signals are complementary in the other channel.

Applying the same analytic method for the buck converter as described above to the half bridge dc-dc converter in Figure. 3.3, average currents in the three magnetic components can be derived:

$$I_{L1} = \frac{R_{L2} + \frac{D_2 R_{Ts}}{D_1 + D_2}}{R_{Ts} + R_{L1} + R_{L2}} I_o$$

(3-14)

$$I_{L2} = \frac{R_{L1} + \frac{D_1 R_{Ts}}{D_1 + D_2}}{R_{Ts} + R_{L1} + R_{L2}} I_o$$

(3-15)

$$I_{M} = \frac{\frac{D_{2}}{D_{1} + D_{2}} R_{L1} - \frac{D_{1}}{D_{1} + D_{2}} R_{L2}}{R_{Ts} + R_{L1} + R_{L2}} \frac{I_{o}}{n}$$

(3-16)

where  $I_0$  is the converter output current;  $D_1$  and  $D_2$  are steady-state duty cycle values for  $S_1$  and  $S_2$ , respectively.

Figure 3.3 Half-bridge dc-dc converter with current doubler rectifier

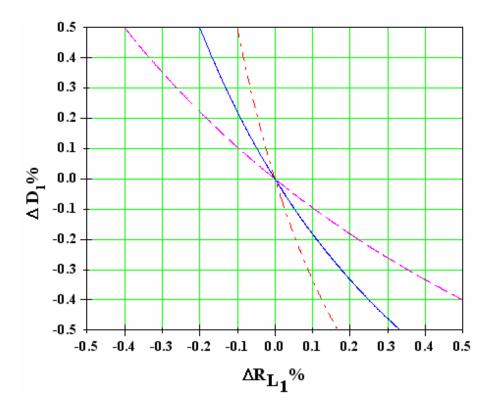

From  $(3-14) \sim (3-16)$ , we may conclude: