University of Central Florida

Electronic Theses and Dissertations, 2004-2019

2007

# Steady State And Dynamic Analysis And Optimization Of Singlestage Power Factor Correction Converters

Khalid Rustom University of Central Florida

Part of the Electrical and Electronics Commons Find similar works at: https://stars.library.ucf.edu/etd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS Citation**

Rustom, Khalid, "Steady State And Dynamic Analysis And Optimization Of Single-stage Power Factor Correction Converters" (2007). *Electronic Theses and Dissertations, 2004-2019.* 3326. https://stars.library.ucf.edu/etd/3326

## STEADY STATE AND DYNAMIC ANALYSIS AND OPTIMIZATION OF SINGLE-STAGE POWER FACTOR CORRECTION CONVERTERS

By

### KHALID W. RUSTOM

B.S. Princess Sumaya University for Technology, 2000 M.S. University of Central Florida, 2002

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Fall Term 2007

Major Professor: Issa Batarseh

© 2007 Khalid Rustom

#### ABSTRACT

With the increased interest in applying Power Factor Correction (PFC) to off-line AC-DC converters, the field of integrated, single-stage PFC converter development has attracted wide attention. Considering the tens of millions of low-to-medium power supplies manufactured each year for today's rechargeable equipment, the expected reduction in cost by utilizing advanced technologies is significant.

To date, only a few single-stage topologies have made it to the market due to the inherit limitations in this structure. The high voltage and current stresses on the components led to reduced efficiency and an increased failure rate. In addition, the component prices tend to increase with increased electrical and thermal requirements, jeopardizing the overarching goal of price reduction. The absence of dedicated control circuitry for each stage complicates the power balance in these converters, often resulting in an oversized bus capacitance. These factors have impeded widespread acceptance of these new techniques by manufacturers, and as such single stage PFC has remained largely a drawing board concept.

This dissertation will present an in-depth study of innovative solutions that address these problems directly, rather than proposing more topologies with the same type of issues. The direct energy transfer concept is analyzed and presented as a promising solution for the majority of the single-stage PFC converter limitations. Three topologies are presented and analyzed based on this innovative structure. To complete the picture, the dynamics of a variety of single-stage converters can be analyzed using a proposed switched transformer model.

To my wife and parents

for their love, support, and inspiration

#### ACKNOWLEDGMENTS

I wish to thank all my professors who have contributed to the work presented in this dissertation. In particular, I would like to thank my advisor Dr. Issa Batarseh for our numerous discussions in which he provided the suggestions and the inspiration which made this work possible. In addition, I would like to express my gratitude to Drs. Chris Iannello, Weihong Qiu, and Shiguo Luo for spending many hours helping me. I also wish to thank the other members of my committee, Drs. John Shen, Takis Kasparis and Thomas Wu for serving on my committee and providing helpful comments.

Finally, I wish to thank my colleagues C. Jourdan, O. Abdel, and H. Al-Atrash for being there beside me at all times.

# TABLE OF CONTENTS

| LIST | OF FIGURESXI                                                                                               |

|------|------------------------------------------------------------------------------------------------------------|

| LIST | OF TABLES XVII                                                                                             |

| CHAF | TER 1 INTRODUCTION 1                                                                                       |

| 1.1  | Introduction 1                                                                                             |

| 1.1  | Definition of Power Factor and Harmonic Distortion2                                                        |

| 1.2  | Harmonics Standards and Regulations                                                                        |

| 1.3  | Classification of Power Factor Correction Approaches 10                                                    |

| 1.4  | Research Motivations                                                                                       |

| 1.5  | Dissertation Outline                                                                                       |

|      | PTER 2 OVERVIEW OF SINGLE-STAGE POWER FACTOR<br>RECTION TECHNIQUES                                         |

| 2.1  | Introduction                                                                                               |

| 2.2  | Original Single-Stage Topologies                                                                           |

| 2.3  | DC Bus Voltage Feedback                                                                                    |

| 2.4  | CCM Operation of the PFC Cell                                                                              |

| 2.5  | Direct Energy Processing Approach                                                                          |

| SWIT | TER 3 IMPROVED ASYMMETRIC HALF-BRIDGE SOFT-<br>CHING PFC CONVERTER USING DIRECT ENERGY TRANSFER<br>INIQUES |

| 3.1  | Introduction                                                                                               |

| 3.2  | The Original Asymmetric Half-Bridge Converter                                                              |

| 3.3  | The Proposed Soft-Switching Topology 49                                                                    |

| 3.3.1        | Principle of Operation                      | 50  |

|--------------|---------------------------------------------|-----|

| 3.3.2        | Steady-State Analysis                       | 58  |

| 3.3.3        | Design Curves                               | 67  |

| 3.3.4        | Design Examples                             | 73  |

| 3.3.5        | Simulation and Experimental Results         | 76  |

| 3.4 Summa    | ry                                          | 78  |

|              | ANALYSIS, DESIGN, AND OPTIMIZATION OF THE E |     |

| 4.1 Introdu  | ction                                       | 80  |

| 4.2 Principl | e of Operation                              |     |

| 4.2.1        | Flyback Operation Mode                      |     |

| 4.2.2        | Boost Operation Mode                        |     |

| 4.3 Steady   | State Analysis                              |     |

| 4.3.1        | Duty Cycle                                  | 95  |

| 4.3.2        | Intermediate Bus Voltage                    |     |

| 4.3.3        | DCM Condition for the PFC Cell              |     |

| 4.3.4        | CCM Condition for the DC-DC Cell            |     |

| 4.4 Design   | Equations and Methodology                   |     |

| 4.4.1        | Main Equations and Design Curves            | 100 |

| 4.4.2        | Stress Equations                            | 110 |

| 4.4.3        | Design Example                              | 111 |

| 4.5 Simulat  | ion Results                                 | 112 |

| 4.6 Experin  | nental Results                              | 115 |

| 4.7 Summa    | ry                                          | 122 |

|        |           | ERAGE MODELING AND AC ANALYSIS OF PFC                           | 124 |

|--------|-----------|-----------------------------------------------------------------|-----|

| 5.1 Ir | ntroducti | on                                                              | 124 |

| 5.2 T  | he Switc  | hed Transformer Model (STM) Principle of Operation              | 130 |

| 5.3 T  | he Switc  | hed Transformer Model (STM) Operation Modes                     | 133 |

| 5.4 U  | nified M  | odel Equations                                                  | 141 |

| 5.5 A  | verage N  | Iodeling Applied to the Bi-Flyback Converter                    | 147 |

| 5.6 E  | xperime   | ntal Results                                                    | 153 |

| 5.7 S  | ummary    |                                                                 | 156 |

|        |           | ALYSIS, DESIGN, AND OPTIMIZATION OF THE<br>ED FLYBACK CONVERTER | 158 |

| 6.1 Ir | ntroducti | on                                                              | 158 |

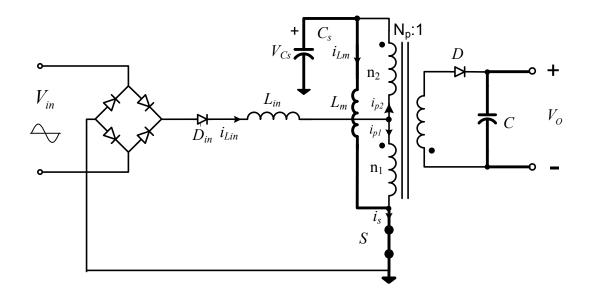

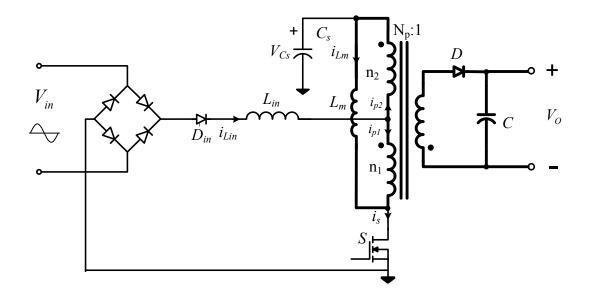

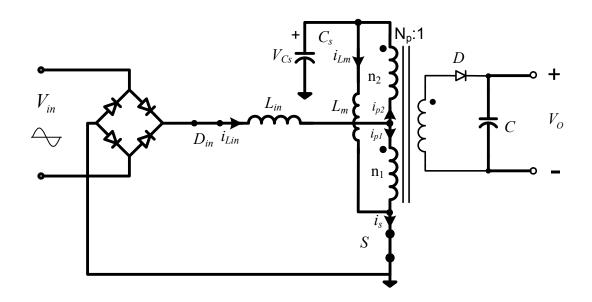

| 6.2 P  | rinciple  | of Operation                                                    | 158 |

|        | 6.2.1     | Mode 1 Operation                                                | 162 |

|        | 6.2.2     | Mode 2 Operation                                                | 165 |

| 6.3 St | teady Sta | ate Analysis                                                    | 170 |

|        | 6.3.1     | Duty Cycle                                                      | 171 |

|        | 6.3.2     | Intermediate Bus Voltage                                        | 172 |

|        | 6.3.3     | DCM Condition for the Input boost inductor                      | 173 |

|        | 6.3.4     | CCM Condition for the DC-DC Cell                                | 174 |

| 6.4 D  | esign Eq  | uations and Methodology                                         | 175 |

|        | 6.4.1     | Main Equations and Design Curves                                | 176 |

|        | 6.4.2     | Stress Equations                                                | 185 |

|        | 6.4.3     | Design Example                                                  | 189 |

| 6.5 S  | imulatio  | n Results                                                       | 191 |

| 6.6 Experimental Results          |     |

|-----------------------------------|-----|

| 6.7 Summary                       |     |

| CHAPTER 7 SUMMARY AND FUTURE WORK |     |

| 7.1 Summary and Conclusions       | 203 |

| 7.2 Future Research               |     |

| LIST OF REFERENCES                | 210 |

## LIST OF FIGURES

| Figure 1-1 The European Standard (IEC) Divisions                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1-2 Class D Special Waveform                                                                                                 |

| Figure 1-3 General Structures of the Passive PFC Approaches 11                                                                      |

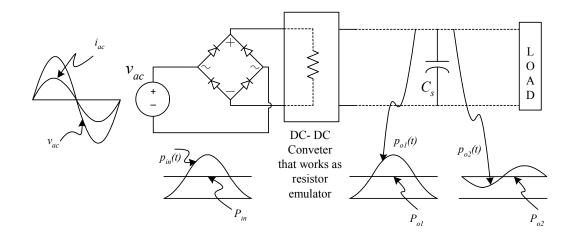

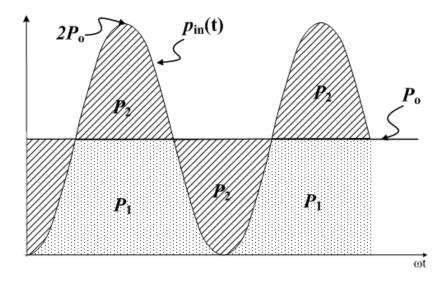

| Figure 1-4 Power Waveforms Associated with Resister Emulator PFC Stage                                                              |

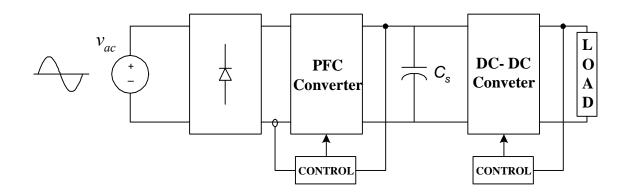

| Figure 1-5 System Configuration of Two-stage PFC Power Supply                                                                       |

| Figure 1-6 System Configuration of Single-stage PFC Power Supply15                                                                  |

| Figure 2-1 the BIFRED Converter                                                                                                     |

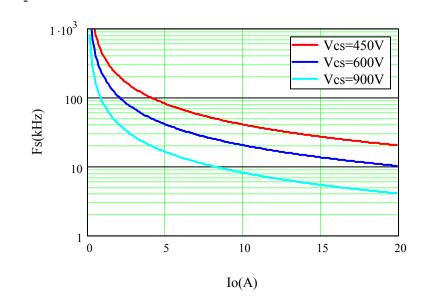

| Figure 2-2 Switching Frequency vs. Load Current                                                                                     |

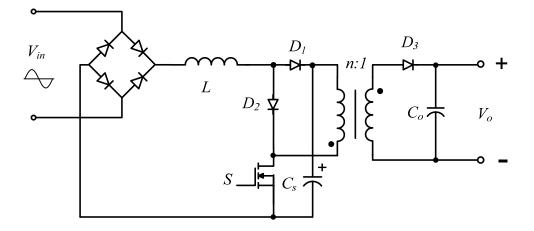

| Figure 2-3 Single-stage Boost/Flyback Combination Circuit                                                                           |

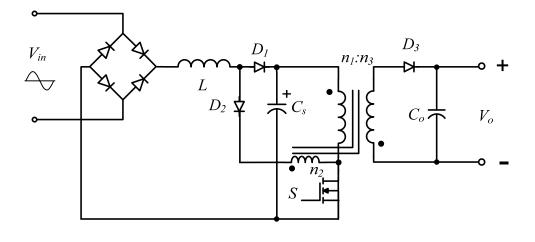

| Figure 2-4 Single-stage PFC converter: (a) Boost/Flyback with DC-bus<br>Voltage Feed-back, (b) BIFRED with DC-bus Voltage Feed-back |

| Figure 2-5 Modes of Operations in the DC-bus Voltage Feedback Topologies29                                                          |

| Figure 2-6 Current Source CCM PFC Circuit                                                                                           |

| Figure 2-7 Effective Duty Cycle in Single-Stage PFC                                                                                 |

| Figure 2-8 Voltage Source CCM PFC Circuit                                                                                           |

| Figure 2-9 Power Relationship in Single-Phase PFC Converters                                                                        |

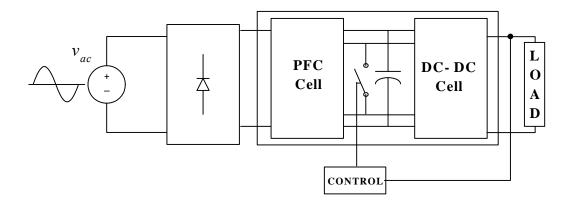

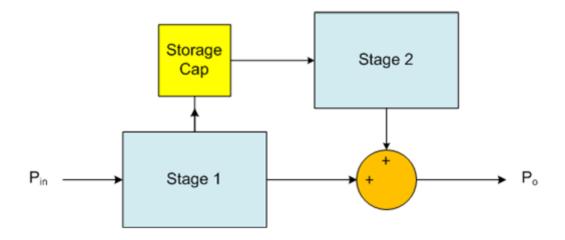

| Figure 2-10 Block Diagram for the Direct PFC Scheme                                                                                 |

| Figure 2-11 Parallel Power PFC Converter                                                                                            |

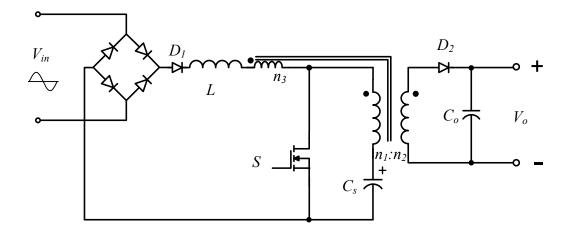

| Figure 2-12 Single-switch PFC Converter with Inherent Load Current<br>Feedback                                                      |

| Figure 2-13 Boundary Modes of Operation during Half-line Cycle                                                                      |

| Figure 2-14 Energy Transfer Paths during the two Modes of Operation 39                                                              |

| Figure 2-15 Power flow Diagram of the Proposed Scheme                                                                               |

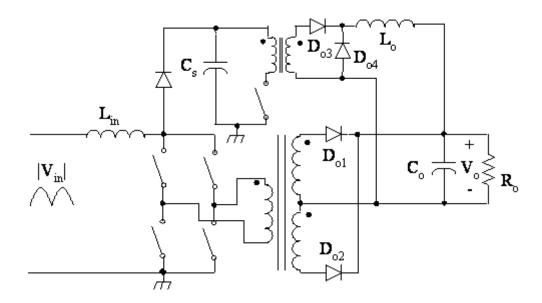

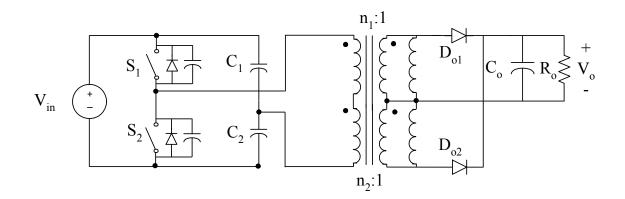

| Figure 2-16 Basic Circuit Schematic of the AHBC Converter Proposed in<br>Chapter 3                                                                                                            | 41 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3-1 Half-Bridge Forward Converter                                                                                                                                                      | 44 |

| Figure 3-2 Switching Waveforms: (a) Symmetric witching, (b) Asymmetric switching                                                                                                              | 45 |

| Figure 3-3 The DC-DC Conversion Characteristics of the Asymmetric converter                                                                                                                   | 46 |

| Figure 3-4 Asymmetric Half Bridge Forward Converter with unbalanced magnetic and current doubler                                                                                              | 47 |

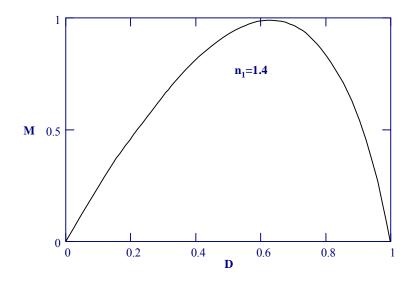

| Figure 3-5 M vs. D for the Asymmetric Converter with Unbalanced Magnet                                                                                                                        |    |

| Figure 3-6 Single Capacitor Asymmetric Converter                                                                                                                                              | 49 |

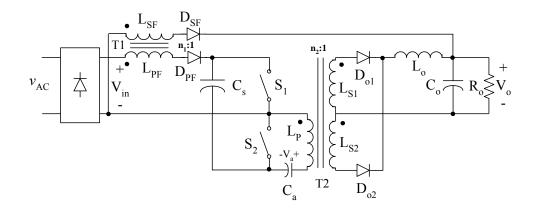

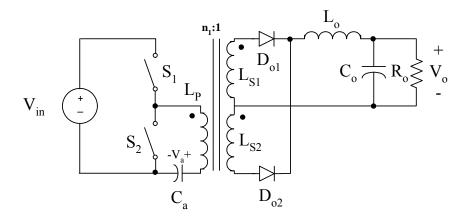

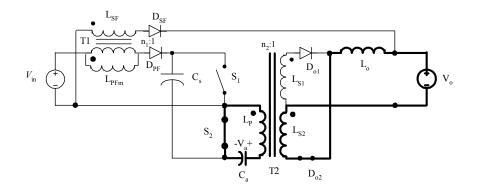

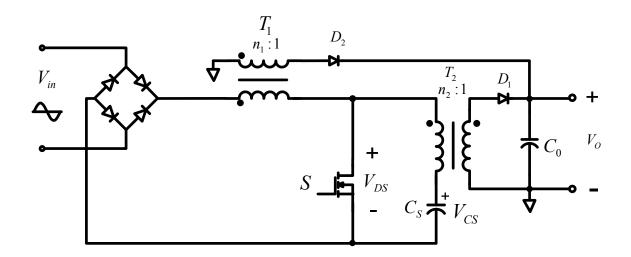

| Figure 3-7 Basic circuit schematic of the proposed Asymmetric Converter                                                                                                                       | 51 |

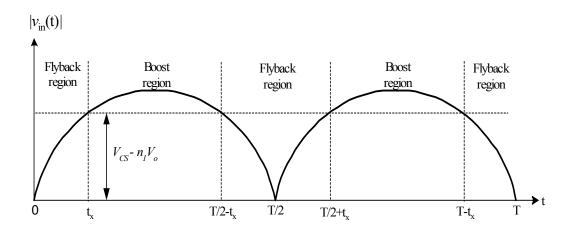

| Figure 3-8 Regions of Operation During one Line Cycle                                                                                                                                         | 52 |

| Figure 3-9 Equivalent Topologies for the Three Switching Modes                                                                                                                                | 57 |

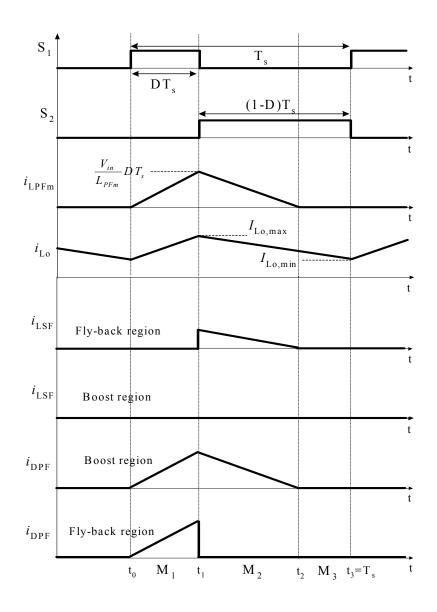

| Figure 3-10 Operation Waveforms                                                                                                                                                               | 58 |

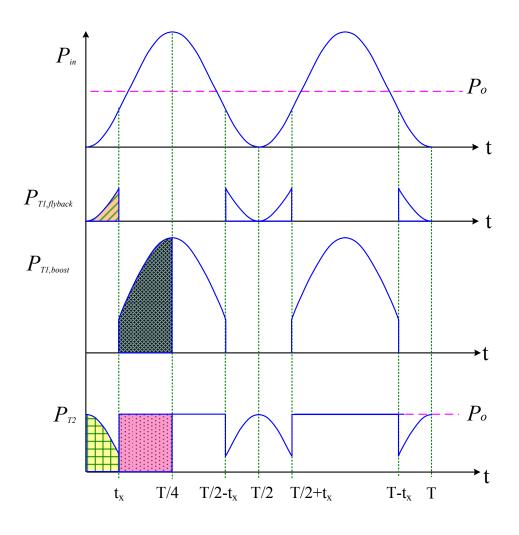

| Figure 3-11 Power Flow over the Line Period                                                                                                                                                   | 60 |

| Figure 3-12 MathCAD Numerical Solve Block                                                                                                                                                     | 69 |

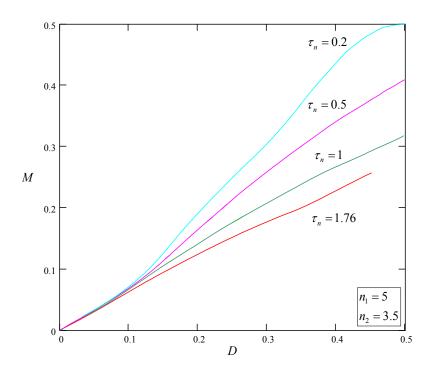

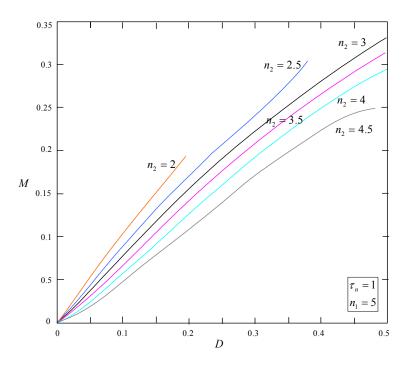

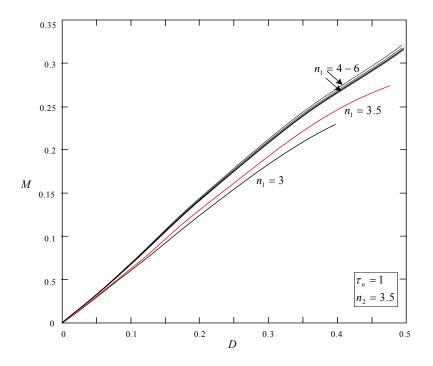

| Figure 3-13 M vs. D under different $\tau_n$ values                                                                                                                                           | 70 |

| Figure 3-14 M vs. D under different $n_2$ values                                                                                                                                              | 71 |

| Figure 3-15 M vs. D under different n1 values                                                                                                                                                 | 71 |

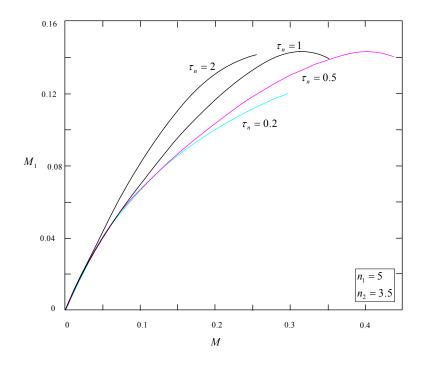

| Figure 3-16 Storage capacitor voltage of the converter                                                                                                                                        | 72 |

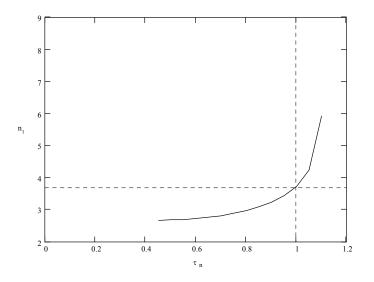

| Figure 3-17 Numerical Solution for $n_1 vs.\tau_n$                                                                                                                                            | 74 |

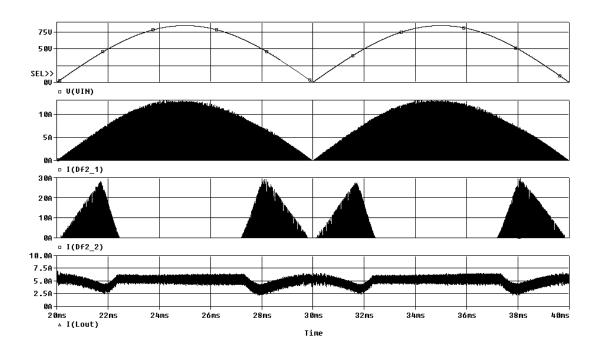

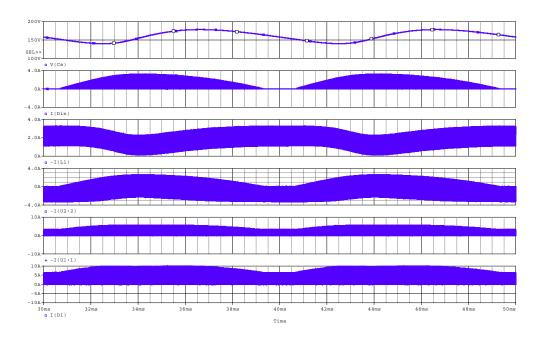

| Figure 3-18 Simulation Waveforms of the Proposed Converter, First trace:<br>Line Voltage, Second trace: Input Current, Third trance: Flyback Current,<br>Fourth trace Output Inductor Current | 77 |

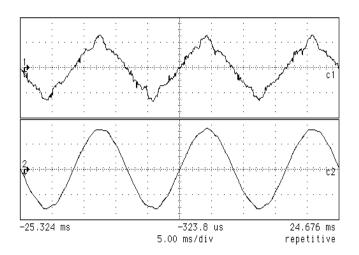

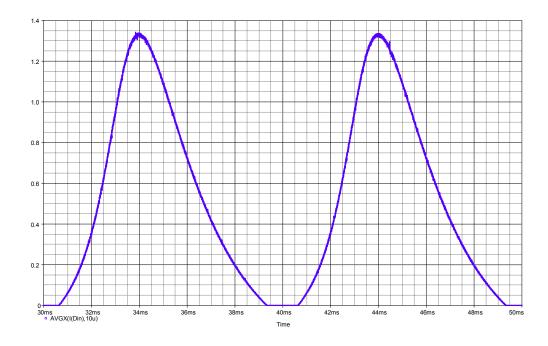

| Figure 3-19 Line current (upper trace) and Line voltage (lower trace)                                                                                                                         | 77 |

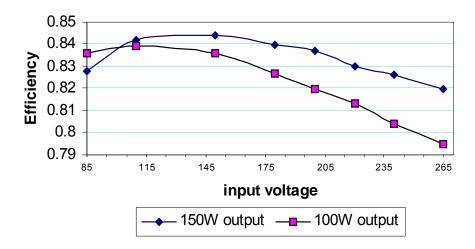

| Figure 3-20 Efficiency versus Line voltage                                                                                                                                                    | 78 |

| Figure 4-1 BIFRED Topology for Single-stage PFC Applications                                                  | . 81 |

|---------------------------------------------------------------------------------------------------------------|------|

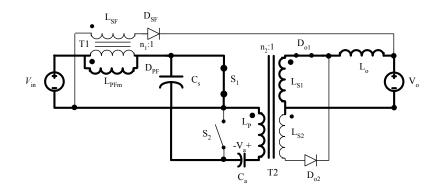

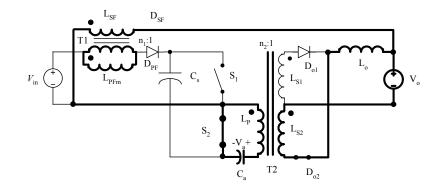

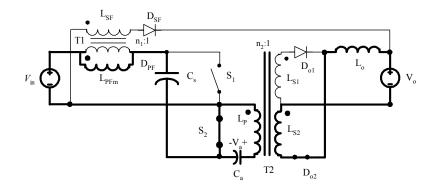

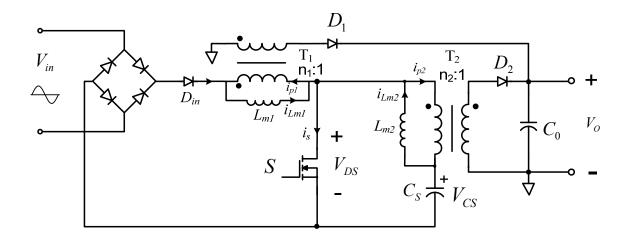

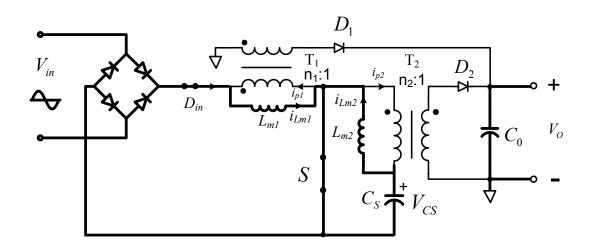

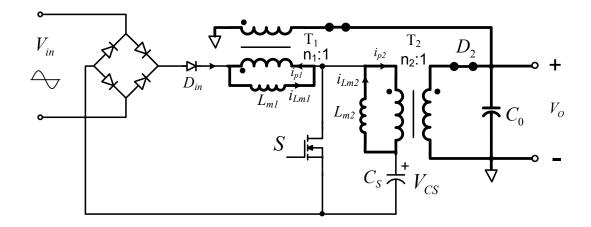

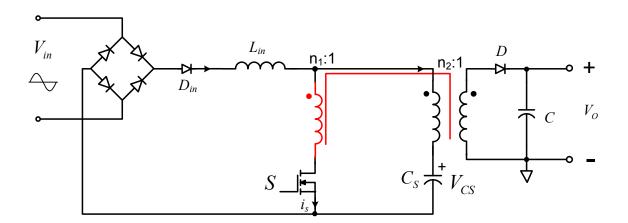

| Figure 4-2 The Bi-flyback Topology                                                                            | . 83 |

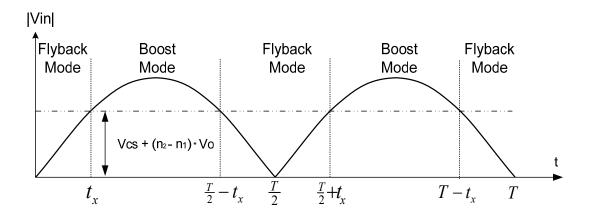

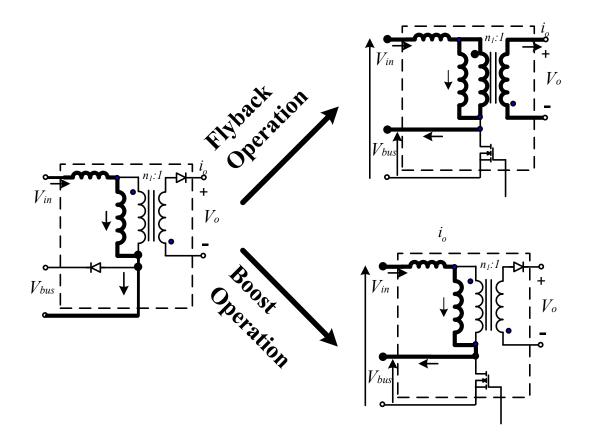

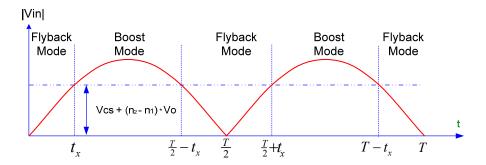

| Figure 4-3 Modes of Operation during a Line Cycle                                                             | . 84 |

| Figure 4-4 Equivalent Circuits for the Three Intervals during the Flyback<br>Mode                             | . 86 |

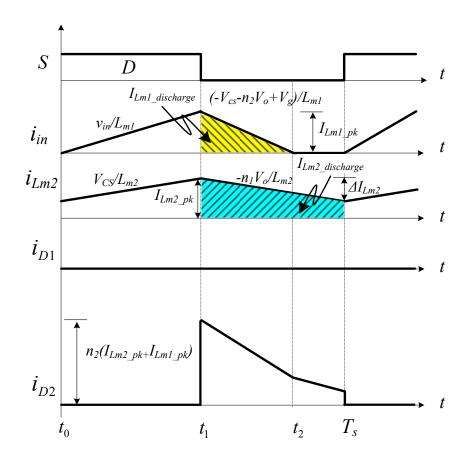

| Figure 4-5 Key Waveforms during Flyback Mode Operation                                                        | . 87 |

| Figure 4-6 Equivalent Circuits for the Three Intervals during the Boost Mo                                    |      |

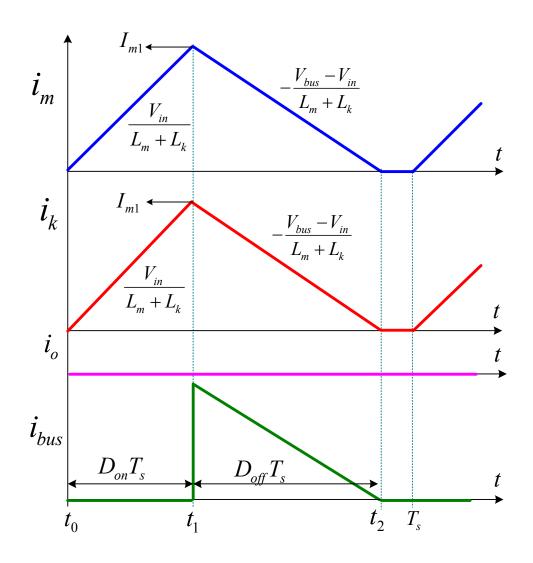

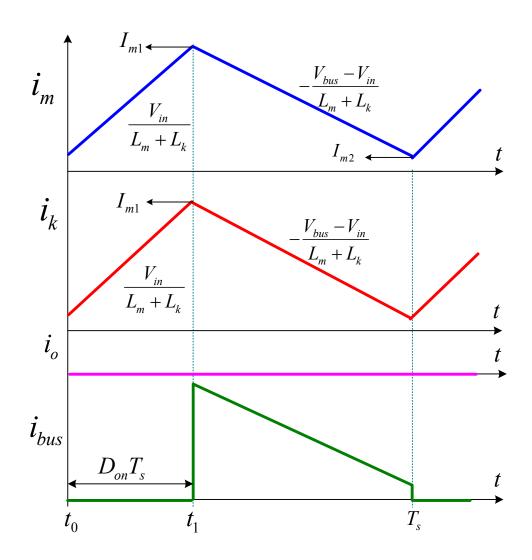

| Figure 4-7 Key Waveforms during Boost Mode Operation                                                          | . 91 |

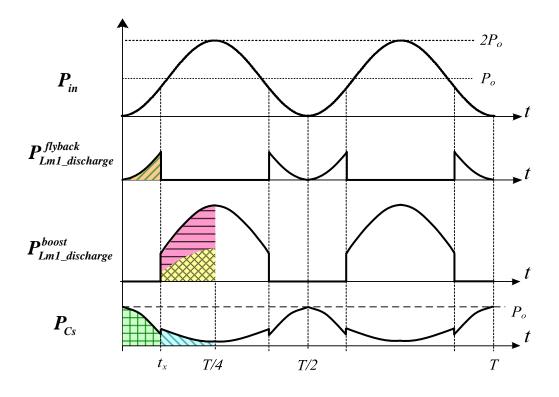

| Figure 4-8 Power Flow Over a line cycle                                                                       | . 94 |

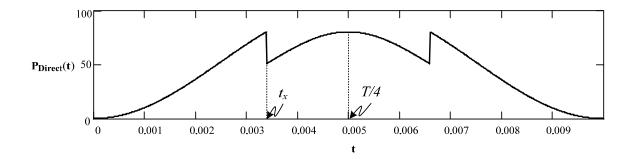

| Figure 4-9 Direct Transferred Power to the Output during Line Cycle                                           | 100  |

| Figure 4-10 MathCAD Solve Block                                                                               | 103  |

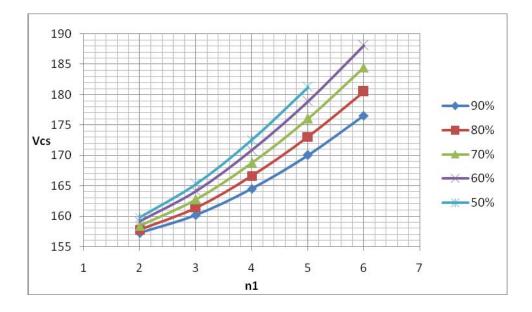

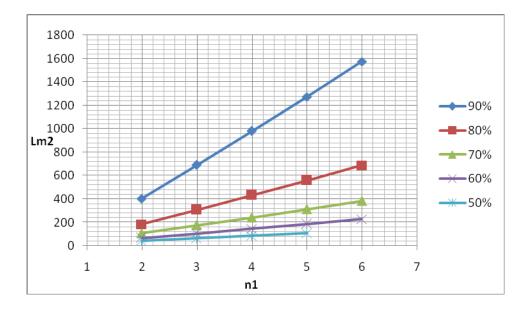

| Figure 4-11 Bus Capacitor Voltage versus $n_1$ for Different $P_D$ Values                                     | 105  |

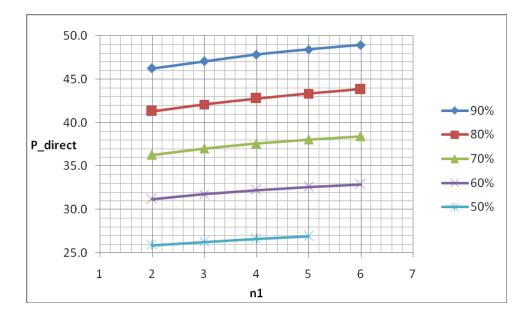

| Figure 4-12 Average Power Percentage Directly Delivered to the Output versus $n_1$ for Different $P_D$ Values | 105  |

| Figure 4-13 RMS value of the Switch Current versus $n_1$ for Different $P_D$ Values                           | 106  |

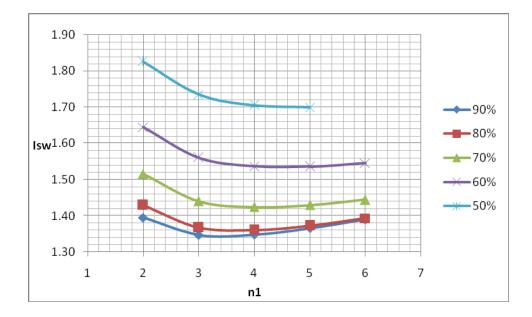

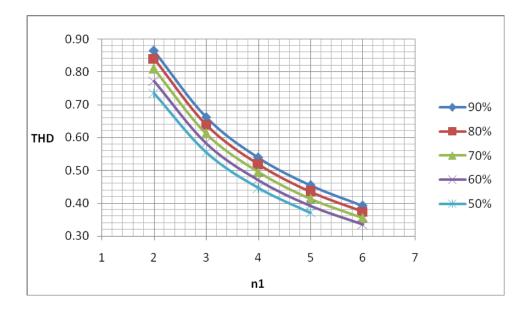

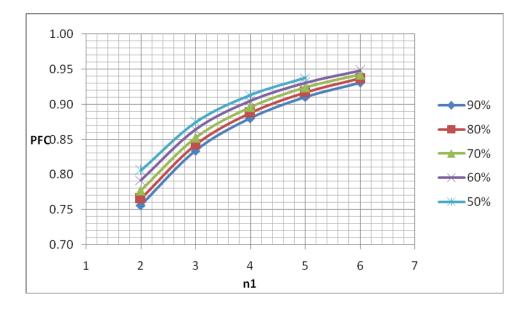

| Figure 4-14 THD versus $n_1$ for Different $P_D$ Values                                                       | 107  |

| Figure 4-15 PF versus $n_1$ for Different $P_D$ Values                                                        | 107  |

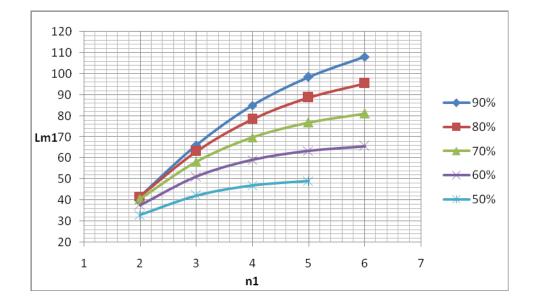

| Figure 4-16 $L_{m1}$ versus $n_1$ for Different $P_D$ Values                                                  | 108  |

| Figure 4-17 $L_{m2}$ versus $n_1$ for Different $P_D$ Values                                                  | 109  |

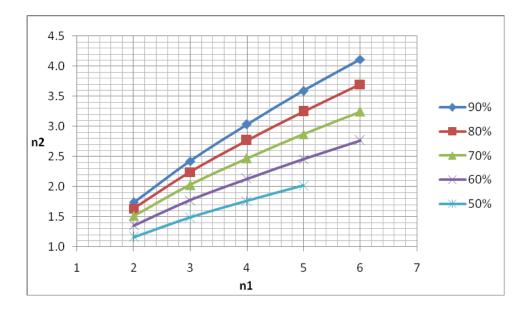

| Figure 4-18 $n_2$ versus $n_1$ for Different $P_D$ Values                                                     | 109  |

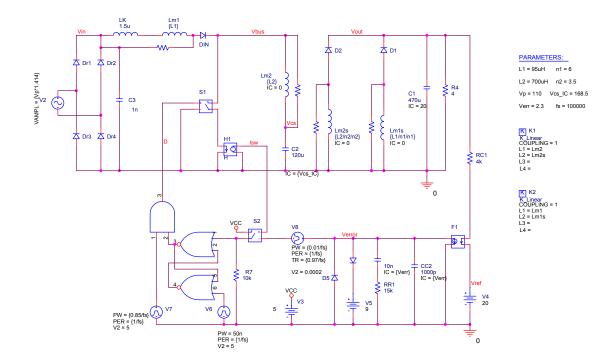

| Figure 4-19 Simulation Schematics for the Bi-flyback Converter                                                | 113  |

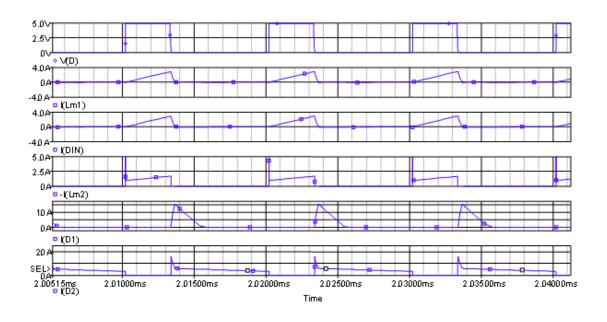

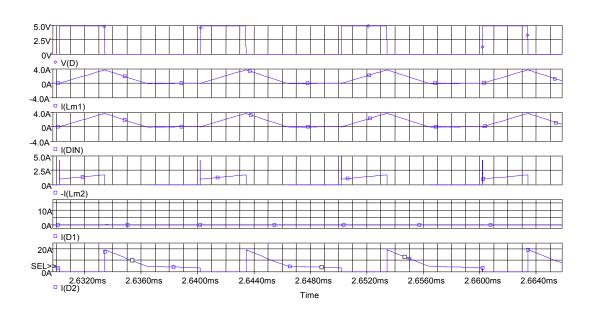

| Figure 4-20 Simulation Waveforms during the Flyback Mode                                                      | 114  |

| Figure 4-21 Simulation Waveforms during the Boost Mode                                                        | 114  |

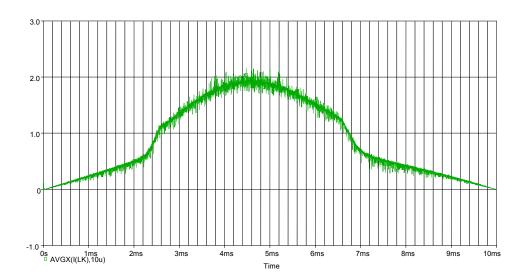

| Figure 4-22 Input Current Simulation Waveforms over Switching Cycles.                                         | 115  |

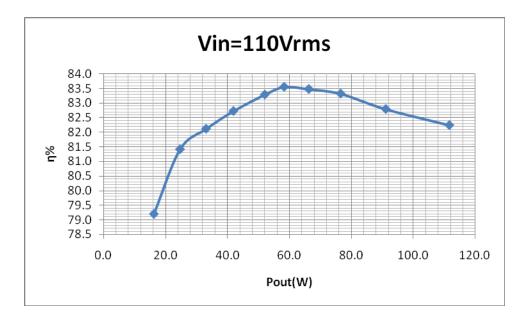

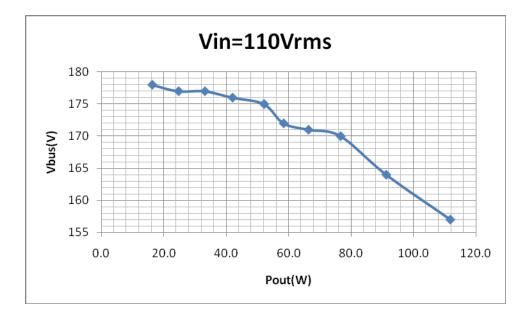

| Figure 4-23 Measured Efficiency versus Output Power at 110Vrms 118                                          |

|-------------------------------------------------------------------------------------------------------------|

| Figure 4-24 Measured Bus Voltage versus Output Power at 110Vrms 118                                         |

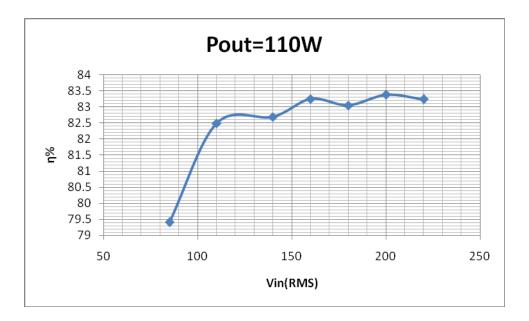

| Figure 4-25 Measured Efficiency when the Input Voltage Varies between 85-<br>220Vrms at Rated Output Power  |

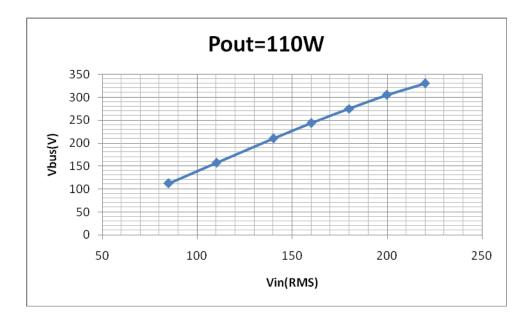

| Figure 4-26 Measured Bus Voltage versus Input Voltage at Rated Output<br>Power                              |

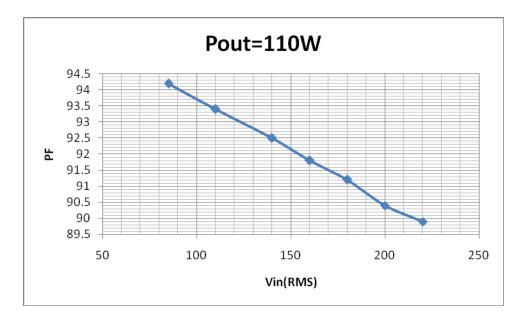

| Figure 4-27 Measured Power Factor versus Input Voltage at Rated Output<br>Power                             |

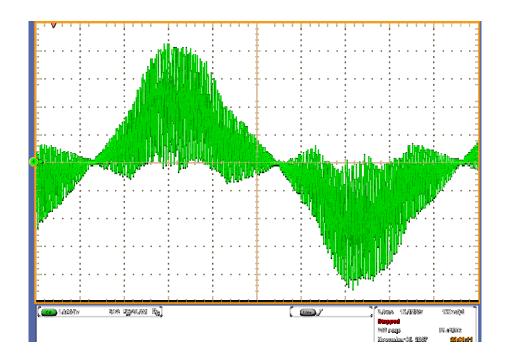

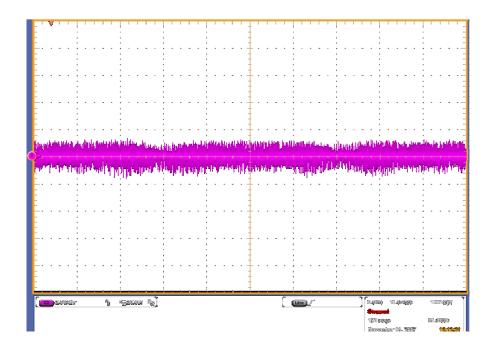

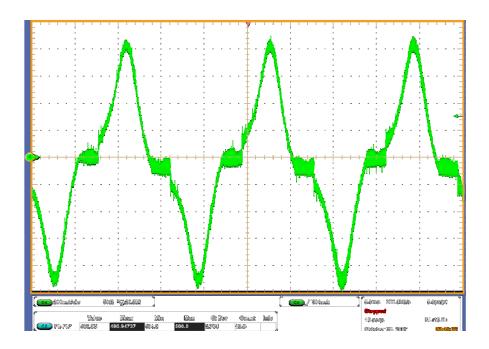

| Figure 4-28 Measured Input Current at rated Output Power, 110Vrms 120                                       |

| Figure 4-29 Measured output voltage (AC coupled) at rated power, 110Vrms<br>121                             |

| Figure 4-30 Measured output voltage (AC coupled) at rated power, 180Vrms<br>121                             |

| Figure 5-1 Switch Models (a) PWM Switch, (b) GSIM 126                                                       |

| Figure 5-2 The Bi-flyback PFC Converter 128                                                                 |

| Figure 5-3 The Proposed Five-terminal Switched Transformer Model 129                                        |

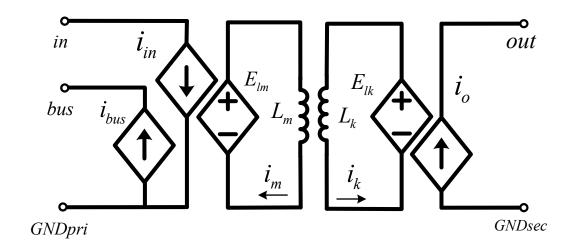

| Figure 5-4 Flyback versus Boost Operation                                                                   |

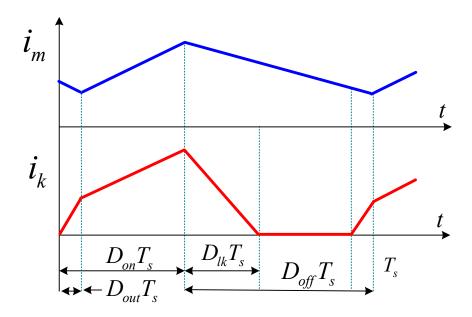

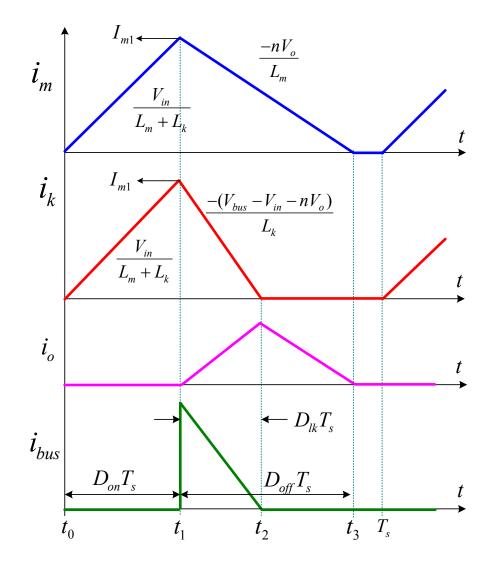

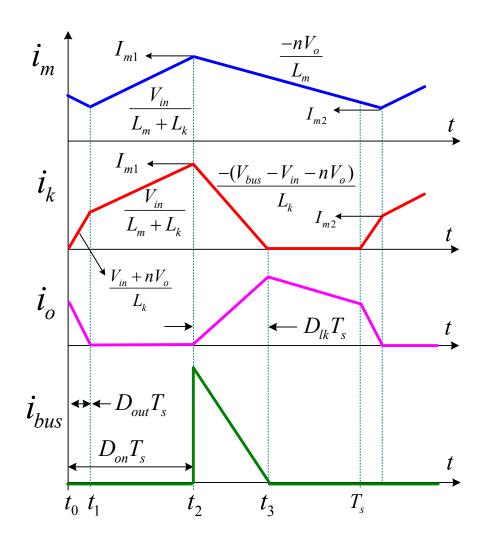

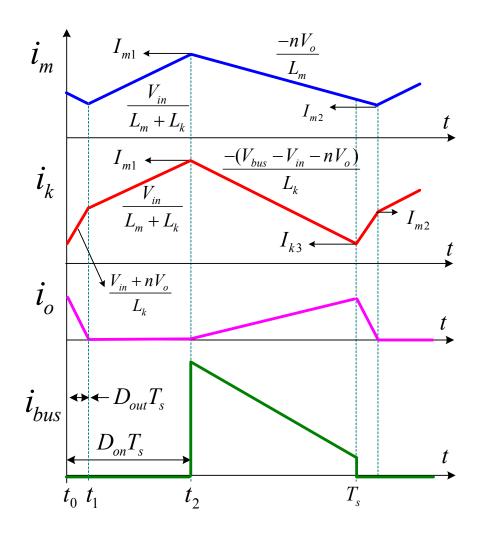

| Figure 5-5 Time Duration Definition of the Proposed Model133                                                |

| Figure 5-6 Primary and Secondary Current Waveforms in the Flyback and<br>Boost Modes                        |

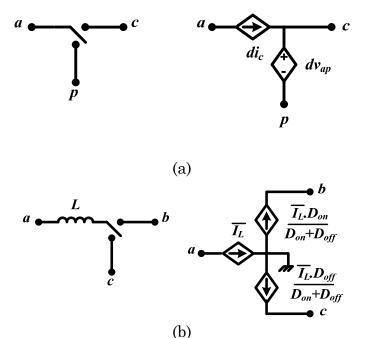

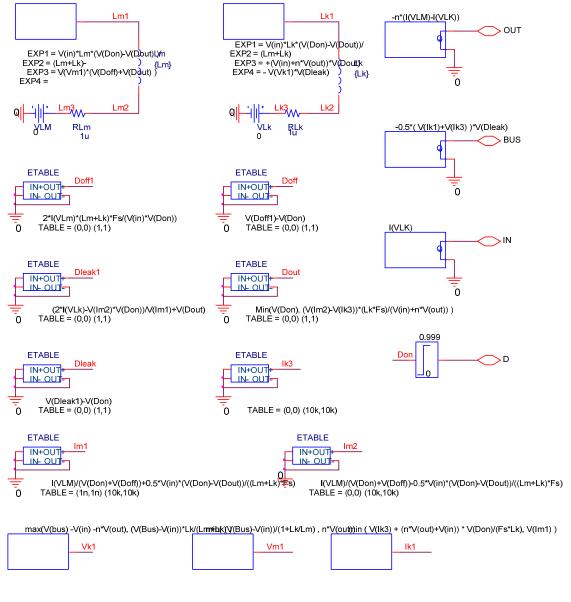

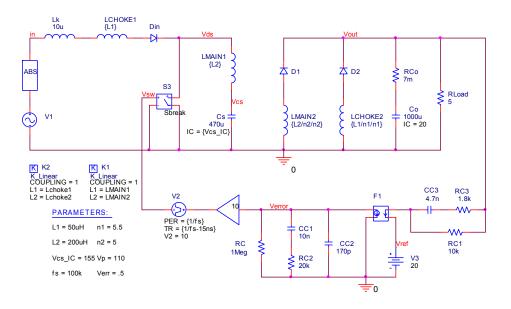

| Figure 5-7 Average Model implementation in Pspice                                                           |

| Figure 5-8 Operational Modes of the Bi-flyback Converter during One Line<br>Period                          |

| Figure 5-9 The Bi-flyback PFC Converter Switching and Average Simulation<br>Models                          |

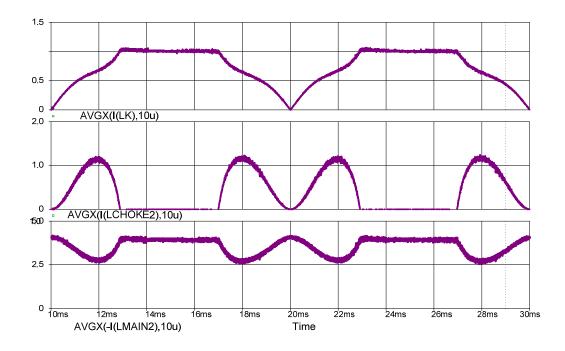

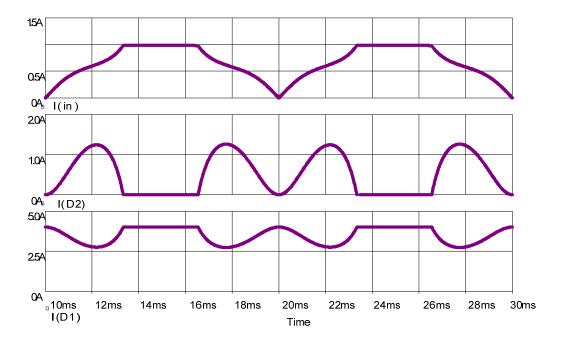

| Figure 5-10 The Bi-flyback PFC Converter Simulation Results                                                 |

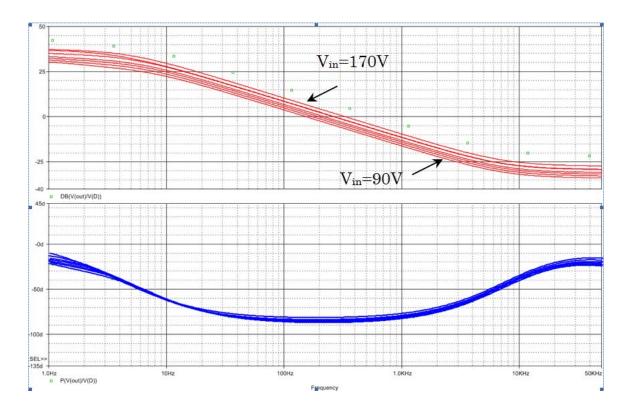

| Figure 5-11 Control to Output ( $V_0$ /d) Frequency Response Simulation Results Bi-Flyback by Average Model |

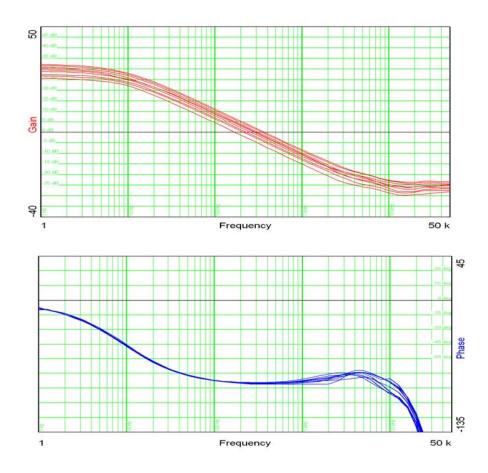

| Figure 5-12 Experimental Control to Output Voltage (V <sub>o</sub> /d) Frequency<br>Response measured for the Bi-flyback PFC converter |

|----------------------------------------------------------------------------------------------------------------------------------------|

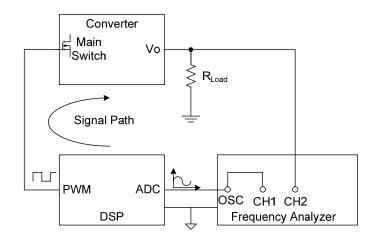

| Figure 5-13 Frequency Response Measurement Setup                                                                                       |

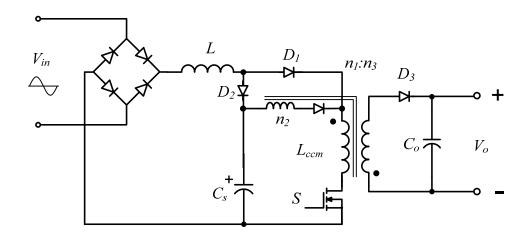

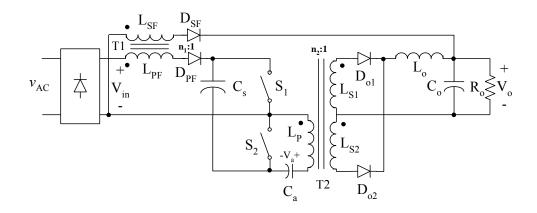

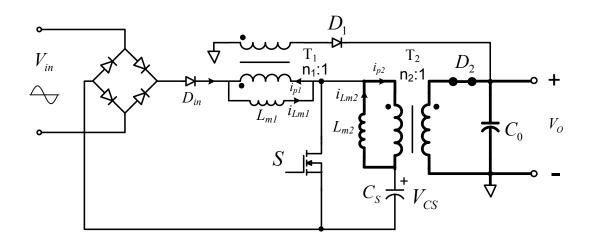

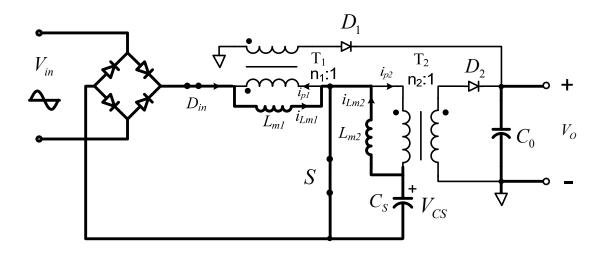

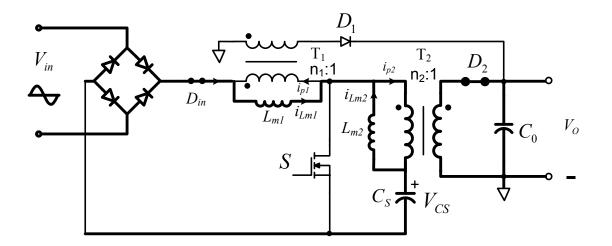

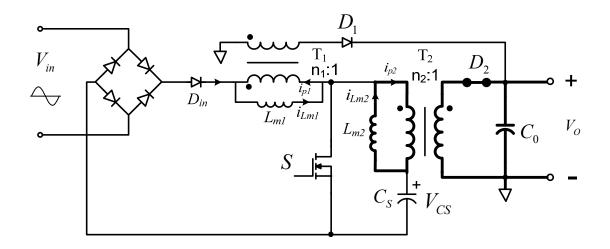

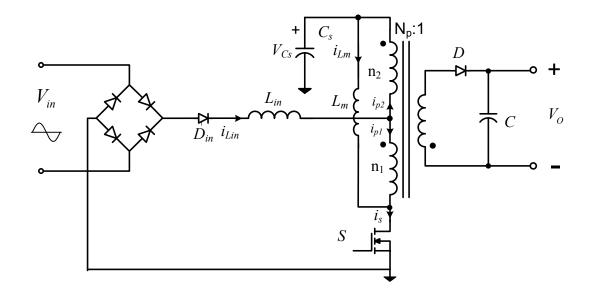

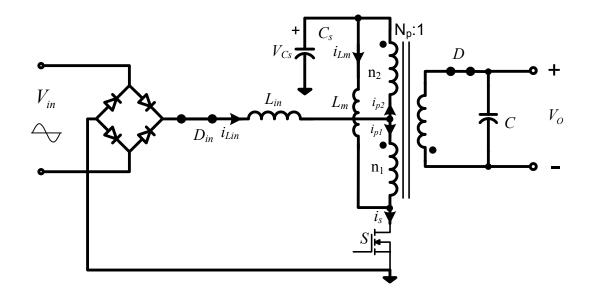

| Figure 6-1 The Center-Tapped Flyback Topology 160                                                                                      |

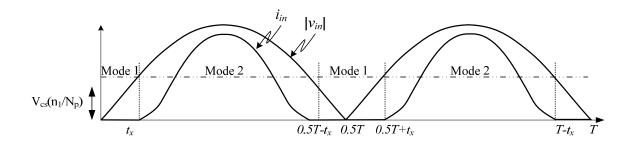

| Figure 6-2 Modes of Operation during a Line Cycle 161                                                                                  |

| Figure 6-3 Equivalent Circuits for the Three Intervals during Mode 1 163                                                               |

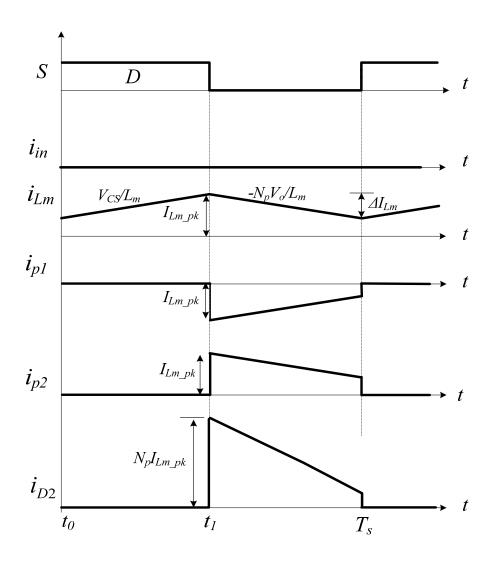

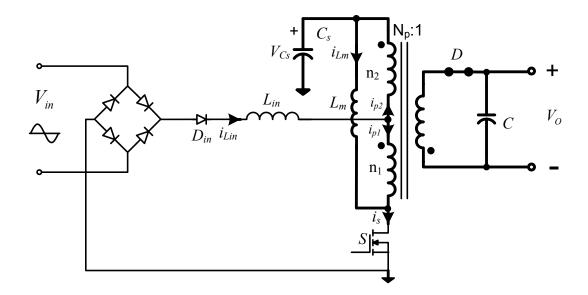

| Figure 6-4 Key Waveforms during Mode 1 Operation 164                                                                                   |

| Figure 6-5 Equivalent Circuits for the Three Intervals during Mode 2 167                                                               |

| Figure 6-6 Key Waveforms during Mode 2 Operation 168                                                                                   |

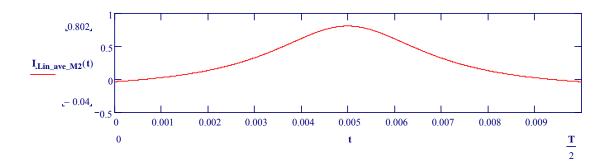

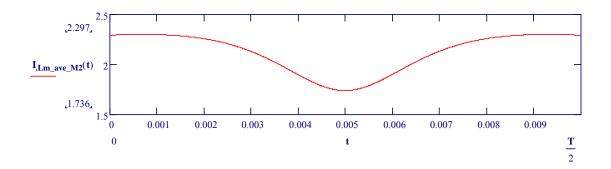

| Figure 6-7 Average Input Current during Line Cycle 174                                                                                 |

| Figure 6-8 Average Flyback Magnetizing Current during Line Cycle 175                                                                   |

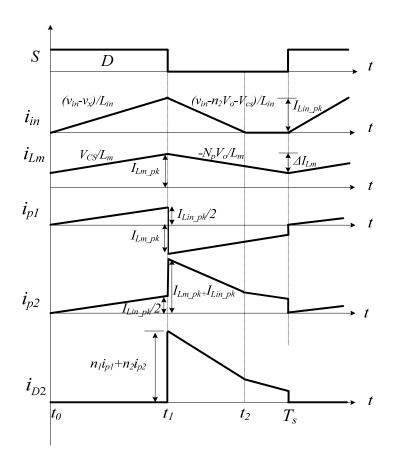

| Figure 6-9 MathCAD Solve Block 177                                                                                                     |

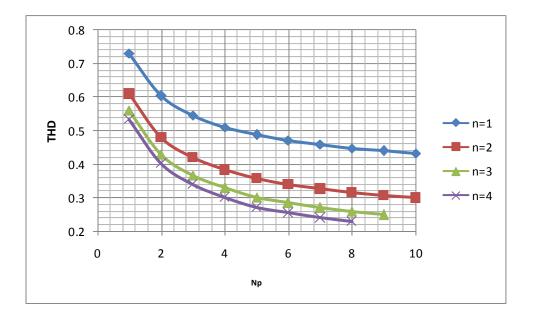

| Figure 6-10 THD versus $N_p$ for Different N Values                                                                                    |

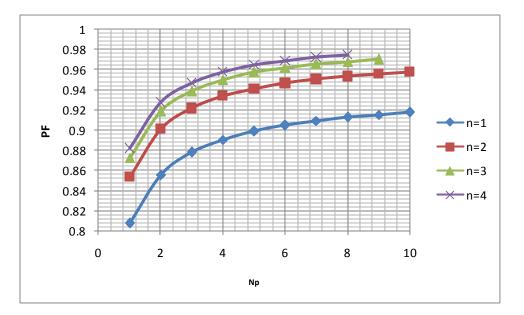

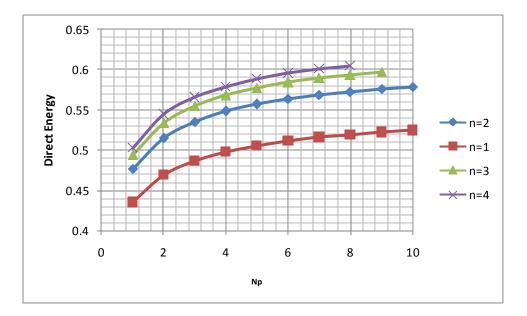

| Figure 6-11 PF versus $N_p$ for Different <i>n</i> Values                                                                              |

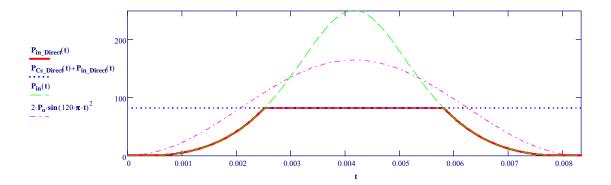

| Figure 6-12 Direct Energy Transferred to the Output over Half Line Cycle181                                                            |

| Figure 6-13 Direct Energy Transferred to the Output versus $N_p$ for Different $n$ Values                                              |

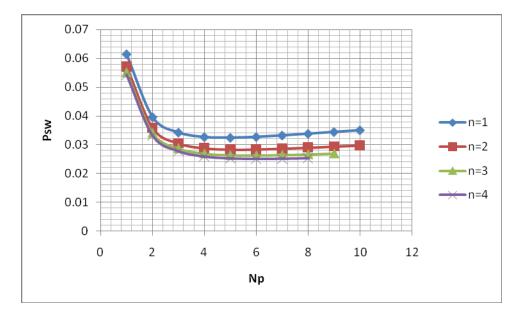

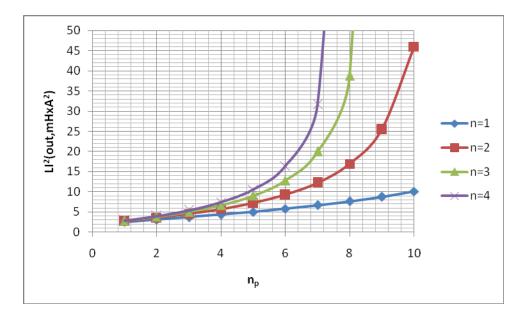

| Figure 6-14 Main Switch Conduction Losses versus $N_p$ for Different <i>n</i> Values                                                   |

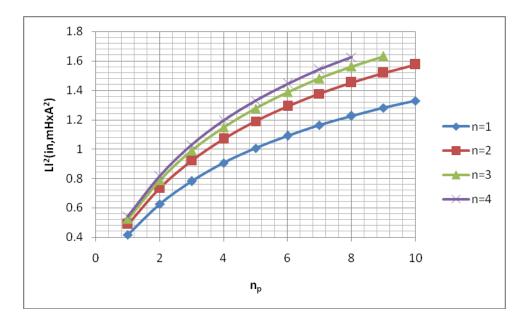

| Figure 6-15 $L_{in}$ Energy versus $N_p$ for Different <i>n</i> Values                                                                 |

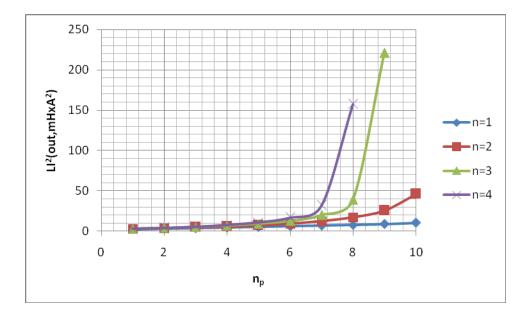

| Figure 6-16 $Lm$ Energy versus $N_p$ for Different $n$ Values                                                                          |

| Figure 6-17 Zoomed-in from Figure 6-16 185                                                                                             |

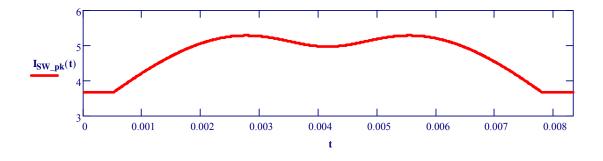

| Figure 6-18 Maximum Switch Current during a Line Cycle 186                                                                             |

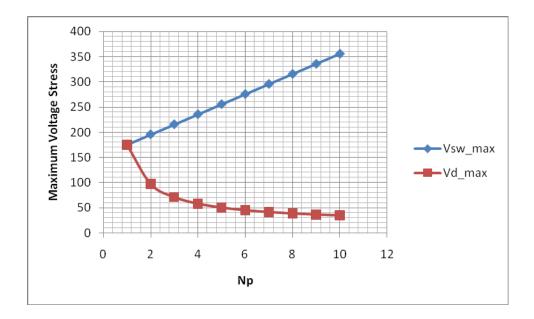

| Figure 6-19 MOSFET and Diode Voltage Stress versus $N_p$                                                                               |

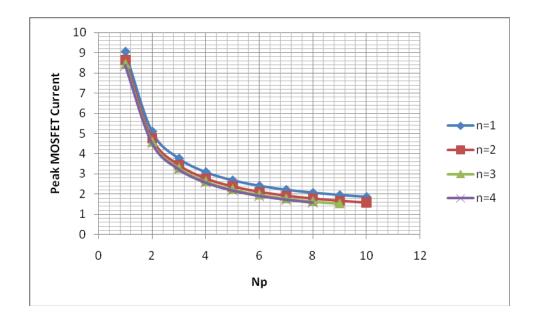

| Figure 6-20 MOSFET Peak Current Stress versus $N_p$ for Different <i>n</i> Values<br>188                                               |

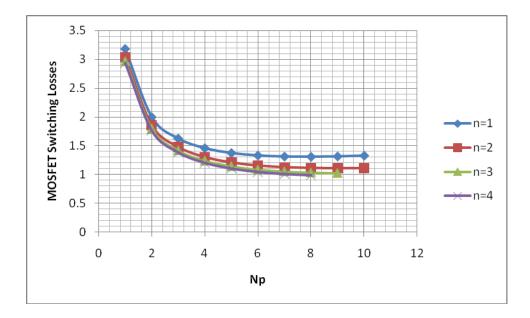

| Figure 6-21 MOSFET Estimated Switching Losses versus $N_p$ for Different $n$ Values189                     |

|------------------------------------------------------------------------------------------------------------|

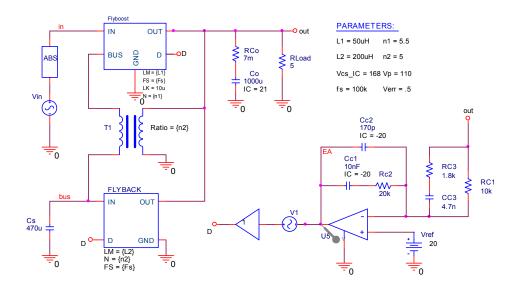

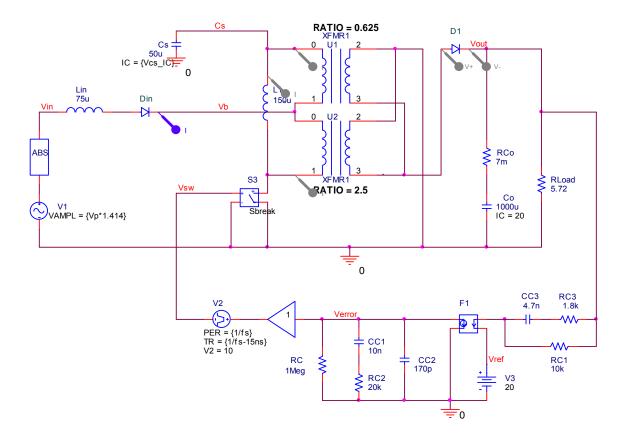

| Figure 6-22 Circuit Schematics of the Simulated Center-tapped Flyback<br>Converter                         |

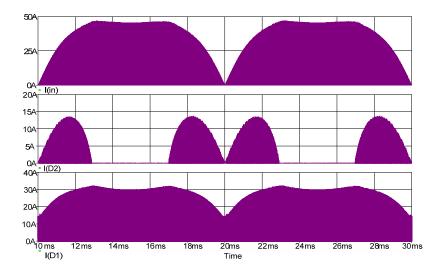

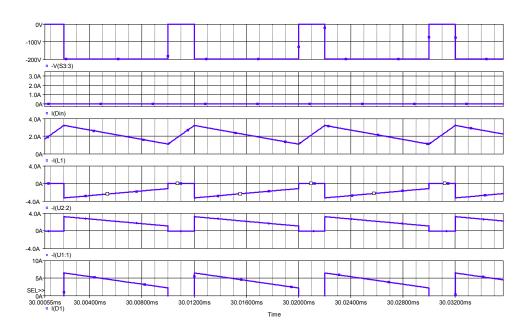

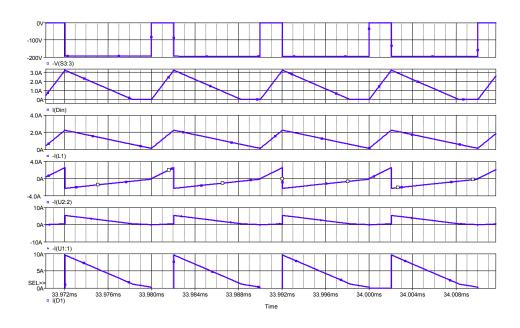

| Figure 6-23 Simulation Waveforms during Mode 1 Operation 193                                               |

| Figure 6-24 Simulation Waveforms during Mode 2 Operation 193                                               |

| Figure 6-25 Simulation Waveforms during Line Cycle 194                                                     |

| Figure 6-26 Simulation Result for the filtered Input Current Waveform 194                                  |

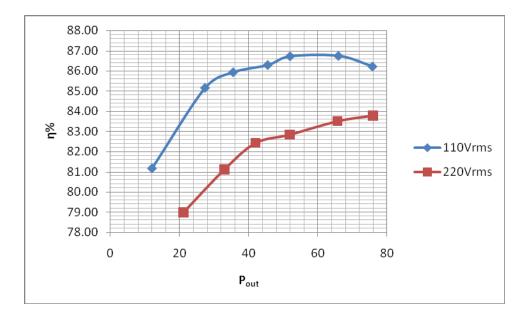

| Figure 6-27 Measured Efficiency versus Output Power for 110Vrms and 220Vrms Input Voltages                 |

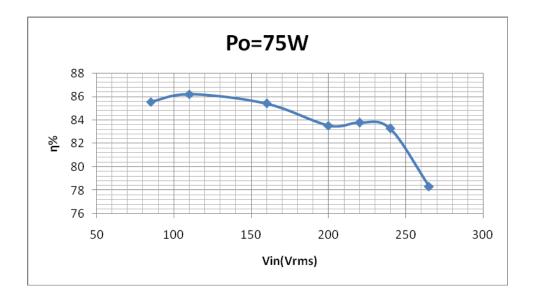

| Figure 6-28 Measured Efficiency when the Input Voltage Varies between 85-<br>265Vrms at Rated Output Power |

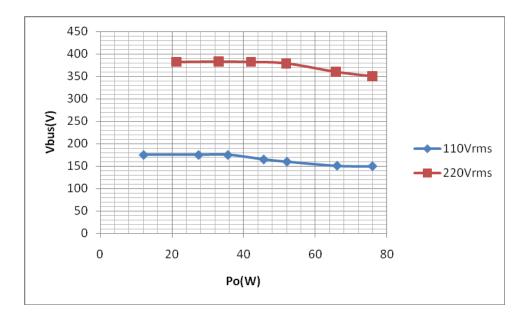

| Figure 6-29 Measured Bus Voltage versus Output Power for 110Vrms and 220Vrms Input Voltages                |

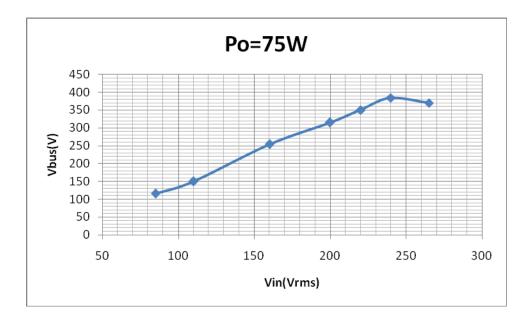

| Figure 6-30 Measured Bus Voltage when the Input Voltage Varies between<br>85-265Vrms at Rated Output Power |

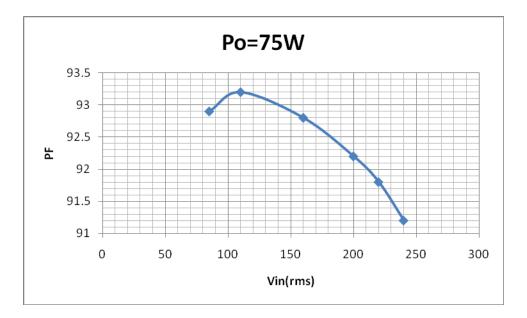

| Figure 6-31 Measured Power Factor when the Input Voltage Varies between 85-265Vrms at Rated Output Power   |

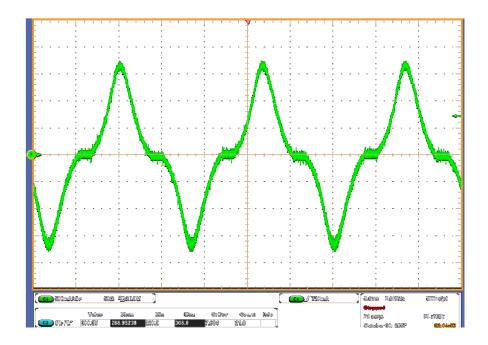

| Figure 6-32 Input Current Waveform at 110Vrms under Full Load                                              |

| Figure 6-33 Input Current Waveform at 220Vrms under Full Load                                              |

## LIST OF TABLES

| Table 1-1 Harmonic Emission Limits for IEC 61000-3-2 and IEC 555-2                        |

|-------------------------------------------------------------------------------------------|

| Table 1-2 Relative Performance Comparison of Three PFC Approaches 18                      |

| Table 3-1 Switching Modes: time intervals and status of devices                           |

| Table 4-1: Bi-flyback Design Specifications    111                                        |

| Table 4-2: Bi-flyback Design Example Calculation Results                                  |

| Table 4-3: Prototype Measurement Results for 110Vrms Input Voltage 117                    |

| Table 4-4: Prototype Measurement Results when the Input Voltage ischanged from 85-220Vrms |

| Table 5-1 Converter Specification and Performance    154                                  |

| Table 6-1: Center-tapped flyback Converter Design Specifications                          |

| Table 6-2: Summary of Design Results    191                                               |

| Table 6-3: Experimental Testing Data at 110Vrms                                           |

| Table 6-4: Experimental Testing Data at 110Vrms                                           |

| Table 6-5: Experimental Testing Data between 85-265Vrms                                   |

#### **CHAPTER 1 INTRODUCTION**

#### 1.1 Introduction

In recent years, new regulations have fostered interest in Power Factor Correction (PFC) techniques. The demand for PFC has been increasing for today's off-line power supplies and even those at low power levels. The offline AC-DC power converters employed in most of today's electrical equipment have been a significant source of harmonic distortion drawing distorted current waveforms, polluting the mains, and thereby degrading power quality. Today, a manufactured converter should satisfy acceptable power quality metrics. Power quality issues have always been a significant topic in power engineering, but, in recent years, this topic has drawn a special attention due to the increased use of high performance electronic devices [1, 2].

The majority of the Modern PFC converters either utilize a simple and economical passive filtering technique (low power), which cannot meet the full range of power quality requirements, or use an additional front-end converter for the PFC function (resulting in a two stage approach). With the help of advanced research in this field, a new approach attracted more attention, namely the integrated single-stage converters. By integrating the two-stage converter into a single-stage, which performs both the PFC and DC-DC conversion simultaneously, this new field promises regulation compliant converters that cost less, are more reliable by using fewer components, and employ a simpler structure.

The research proposed for this dissertation is intended to assist the development of new, advanced AC-DC power converters with PFC to be used mainly in low power applications. Referring to the standards and regulations on harmonic emission, these converters are classified as Power Factor Correction (PFC) AC-DC converters. In this Chapter, the definition of power factor and harmonic distortion will be reviewed, followed by a summary of the effects of power electronics pollution. After which, the new power quality regulations will be summarized. In addition, the motivation and research objectives will be introduced at the end of this chapter.

#### 1.1 Definition of Power Factor and Harmonic Distortion

During the transmission and distribution of electrical power, the utility voltage waveform maybe distorted by a number of factors, some of which occur within the customer's own installations. This waveform distortion, when steady state and periodic, is a result of harmonic and means the voltage waveform is no longer a perfect sinusoid. In the development that follows, this distortion will be expressed mathematically. If we assume a periodic waveform, f(t), then the Fourier series expansion representation for this waveform will be [3],

$$f(t) = F_0 + f_1(t) + f_2(t) + \dots + f_n(t) = F_0 + \sum_{n=1}^{\infty} (a_n \cos n\omega t + b_n \sin n\omega t)$$

(1.1)

where,  $F_{\theta}$  represents the average (*DC*) value of f(t), n represent the order of the harmonic and the coefficient  $a_n$  and  $b_n$  are evaluated from the following integrals,

$$a_n = \frac{2}{T} \int_0^T f(t) \cos n \, \omega t dt \quad n = 1, 2, 3, ..., \infty$$

(1.2)

$$b_n = \frac{2}{T} \int_0^T f(t) \sin n \omega t dt \quad n = 1, 2, 3, ..., \infty$$

(1.3)

where T is the period of the waveform and equal to  $2\pi/\omega$ .

The definition of the power factor is the ratio of the real power (average) to the apparent power, as described in Eq. (1.4).

$$PowerFactor(PF) = \frac{Real \ Power(Average)}{Apparent \ Power}$$

(1.4)

In practice, power electronics systems have nonlinear behavior due to switching devices. Applying the definition of power factor to a distorted current and voltage we can express the power factor as,

$$PF = \frac{\frac{1}{T} \int_{0}^{T} v(t)i(t)dt}{\sqrt{\frac{1}{T} \int_{0}^{T} v(t)^{2} dt} \sqrt{\frac{1}{T} \int_{0}^{T} i(t)^{2} dt}} = \frac{\sum_{n=1}^{\infty} I_{sn,rms} V_{sn,rms} \cos \theta_{n}}{I_{s,rms} V_{s,rms}}$$

(1.5)

where,  $V_{sn,rms}$  and  $I_{sn,rms}$  are the *rms* values of the n<sup>th</sup> harmonic voltage and current, respectively, and  $\theta_n$  is the phase shift between the n<sup>th</sup> harmonic voltage and n<sup>th</sup> harmonic current.

For off-line power supplies where the input voltage is almost a purely sinusoidal, Eq. (1.5) can be further simplified to,

$$PF = \frac{I_{s1,rms}}{I_{s,rms}} \cos \theta_1 = k_d \cdot k_\theta$$

(1.6)

where,

$I_{s1,rms}$ : *rms* value of the fundamental component in line current;

$k_d = I_{s1,rms}/I_{s,rms}$ : distortion factor;

$k_{\theta} = \cos \theta_1$ : displacement factor.

Another important term that is used to measure the quality of the waveform is the *Total Harmonic Distortion* (THD). Again assuming the typical nearly sinusoidal voltage input, the input current THD, is defined as:

$$THD_{i} = \sqrt{\frac{\sum_{n=2}^{\infty} I_{sn,rms}^{2}}{I_{s1,rms}^{2}}} = \sqrt{\frac{1}{k_{d}^{2}} - 1}$$

(1.7)

There are many negative effects caused by the existence of the harmonic content. This distortion has several detrimental effects, including but not limited to the following:

- Heat and losses: the current harmonics cause an increase in the copper losses (conduction), and the voltage harmonics result in an increase in iron losses (core magnetic).

- Inefficient power utilization: the current harmonics increase the *rms* value of the total current but they do not deliver any real power in Watts to the load, resulting in inefficient use of capacity and unnecessary over rating of the distribution.

- Protection failure and safety risks: Fuses and relays can also be affected in the present of harmonics and they may cause nuisance tripping.

- Changing the network impedance: all the network components present complex impedances that will vary when presented with the harmonic frequencies.

- Exhausting the power cables: harmonics will lead to the increase in the ac resistance of a cable is caused by two phenomena, skin

effect and proximity effect. This can result in increasing the losses and may cause insulation failure in the cable.

• Electro-Magnetic Interference (EMI) Problems: The high frequency disturbances often categorized as EMI can be radiated to free space as electromagnetic waves or conducted though the power lines in a differential or common mode. EMI's effect on electronic systems is commonly the subject of power engineer's study.

In order to maintain harmonic distortion at reasonable levels and to comply with the regulatory standards on distortion there are solutions which are applicable to both the supply system and to the harmonics sources themselves. These solutions will be presented thoroughly in the next chapter.

#### 1.2 Harmonics Standards and Regulations

The added circuitry to improve the power factor and overcome the harmonics problem will add extra cost to the original power supply, typically 20 to 30 percent more cost. This extra cost has made the power supply manufacturers less interested in implementing these circuits. On the other hand, the power company wants its consumers to draw clean current waveforms from its mains. Thus international and national standards have come into force to limit the level of harmonic injection into the system and to maintain good power quality [4, 5].

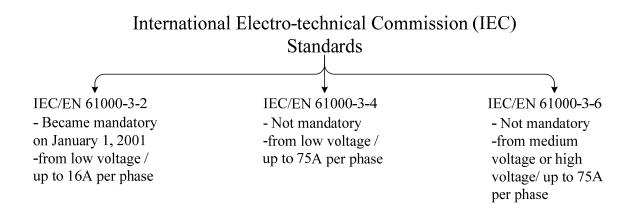

Figure 1-1 The European Standard (IEC) Divisions

The IEEE-Std-519: 1992, recognized as recommended practice in the U.S., is mainly used in the American market for guidance in the design of power systems with non-linear loads. This standard contains, in a single publication, all the topics related to the analysis and control of harmonics in the power system. On the other hand, the European standard (International Electro-technical Commission) IEC presents standards on electromagnetic compatibility in several publications that cover many disturbance phenomena: harmonics, inter-harmonics, voltage fluctuations, voltage imbalance, mains signaling, power frequency variation and DC components. Figure 1-1 shows the divisions of the European standards that superseded the old IEC 555-2/EN 60555-2. These divisions depend on the load,

equipments' connections, and whether it is low, medium, or high voltage and it also depends on the maximum current drawn per phase by the equipment.

| Harmonic   | Class A              | Class B              | Class C             | Class D             | IEC 555-2           |

|------------|----------------------|----------------------|---------------------|---------------------|---------------------|

| Number (n) | Limits <sup>**</sup> | Limits <sup>**</sup> | Limits <sup>*</sup> | Limits <sup>*</sup> | limits for          |

|            |                      |                      |                     |                     | TV(>165W)           |

|            | (A <sub>rms</sub> )  | (A <sub>rms</sub> )  | % Of                | mA/W of             | (A <sub>rms</sub> ) |

|            |                      |                      | fundamental         | input power         | Max DC              |

|            |                      |                      |                     | (50-600W)           | current<0.05A       |

| 2          | 1.080                | 1.620                | 2                   | n/a                 | 0.300               |

| 3          | 2.300                | 3.450                | 30 x PF             | 3.4                 | 0.800               |

| 4          | 0.430                | 0.645                | n/a                 | n/a                 | 0.150               |

| 5          | 1.440                | 2.160                | 10                  | 1.9                 | 0.600               |

| 6          | 0.300                | 0.450                | n/a                 | n/a                 | n/a                 |

| 7          | 0.770                | 1.155                | 7                   | 1.0                 | 0.450               |

| 8          | 0.230                | 0.345                | n/a                 | n/a                 | n/a                 |

| 9          | 0.400                | 0.600                | 5                   | 0.5                 | 0.300               |

| 10         | 0.184                | 0.276                | n/a                 | n/a                 | n/a                 |

| 11         | 0.330                | 0.495                | 3                   | 0.35                | 0.170               |

| 12         | 0.153                | 0.230                | n/a                 | n/a                 | n/a                 |

| 13         | 0.210                | 0.315                | 3                   | 0.296               | 0.120               |

| Even 14-40 | 1.84/n               | 2.760/n              | n/a                 | n/a                 | n/a                 |

| Odd 15-39  | 2.25/n               | 3.338/n              | 3                   | 3.85/n              | 1.5/n               |

Table 1-1 Harmonic Emission Limits for IEC 61000-3-2 and IEC 555-2

\* EC 61000-3-2 only

$^{\ast\ast}$  Both IEC 61000-3-2 and IEC 555-2

The IEC 1000-3-2 sets limits for the harmonic currents generated by electrical and electronic equipment drawing input current up to 16A/phase. The standard categorizes the equipment into four classes:

- Class B for portable tools.

- Class C for lighting equipment including dimmers.

- Class D for equipments having the special waveform, shown in Figure 1-2, of input current and an active input power less than or equal to 600W, except phase angle controlled motor driven equipment.

- Class A for everything else and balanced three-phase equipment.

Table 1-1 shows the harmonic limits for these classes.

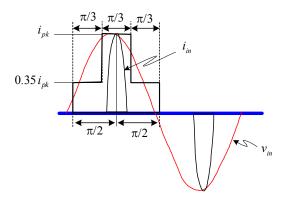

An envelope, shown in Figure 1-2, defines the special wave-shape for Class D. Equipment is deemed to be Class D if the input current waveform for each half period is within the envelope for at least 95% of the duration of its half cycle. The centerline of the envelope coincides with the peak of the input current, which may be not the same position of the peak line voltage. The envelope is divided into three equal periods of  $\pi/3$  with the amplitude of the center period is equal to the peak of the input current and the amplitude of the two sides is equal to 0.35 of that peak value. If the input current is approximately a sinusoid it will fall outside of that envelope for 40% of the cycle. Note that if the power above 600W, it is not a Class D product and hence should be tested for Class A limits. If the power is below 75W, no limits apply.

Figure 1-2 Class D Special Waveform

#### 1.3 Classification of Power Factor Correction Approaches

The general approaches to improve power factor can be widely classified as passive and active approaches. The passive approaches uses capacitive inductive filters to achieve PFC, while the active approaches use a switched-Mode power supply to shape the input current. In this section both approaches will be discussed and some of the common circuits will be presented.

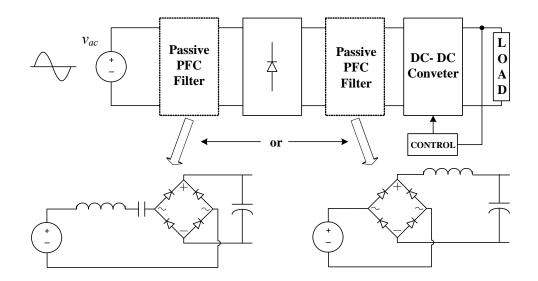

### A. Passive Approaches

In this approach, a full bridge rectifier with an LC filter is used to meet the line current harmonic limits. Generally, the LC filter can be placed on the AC-side or the DC-side of the rectifier as shown in Figure 1-3. Placing the LC filter on the ac-side will result in purely sinusoidal input current.

Figure 1-3 General Structures of the Passive PFC Approaches

Passive PFC can meet the regulation with high efficiency, superior reliability, low cost, and low EMI. On the other hand, the filter capacitor voltage varies with the line voltage, which has a detrimental effect on the performance and efficiency of the DC-DC converter. When considering the hold-up time for the power supply, the capacitance of the bulk capacitor has to be increased and become very bulky compared to what it would have been without this varying voltage. As a result of this trade, the passive approaches seem to be more attractive in low power applications, up to 300Watts. This lack of voltage regulation and poor dynamic response make passive PFC more suitable for applications with a narrow line voltage range. Other drawbacks are the size and weight of the filter choke inductor. This inductor is heavy, bulky, and requires careful design consideration. Even with these limiting factors, the majority of power supplies manufactured in low power and cost sensitive applications have adopted this passive technique.

#### B. Active Approaches

In active PFC, a switched-mode converter is employed to overcome the limitations of the passive approaches. As seen in Figure 1-4, the ideal result from this PFC stage, is to achieve a unity power factor. Assuming unity power factor, the line current should be sinusoidal and in phase with the line voltage. That will result in pulsating output power than contains in addition to the real (average power), an alternating component with double the line frequency. Since the power demanded by most loads is constant, an energy storage element is needed. Since the inductor-stored energy cannot supply this amount of energy, another storage component is needed. The storage capacitor,  $C_s$ , which will handle the double line frequency ripple component, is introduced. This capacitor is usually large and bulky.

Figure 1-4 Power Waveforms Associated with Resister Emulator PFC Stage

The double line frequency problem that presents itself on the output of the PFC stage cannot be internally solved. Usually a compromise between PFC and output voltage ripple can be made, but most of the time this output voltage is not good enough to supply the load. As a result, another DC-DC converter, or the so called post regulator, is required to solved this problem and achieve tight output regulation. The result is the most flexible PFC configuration that is called the active, two-stage PFC, shown in Figure 1-5.

Figure 1-5 System Configuration of Two-stage PFC Power Supply

The boost converter is widely used in the PFC stage due to its advantages such as good power factor, grounded switch, input inductor and simplicity. Usually this PFC converter has a low bandwidth control which implies a loosely regulated output voltage across the storage capacitor. In universal line voltage applications, the DC bus voltage may vary between 380-400V. Because of the relative high voltage on the storage capacitor, the value of the capacitance can be optimized to provide the necessary hold-up time. The DC-DC converter is connected to the storage capacitor to provide the necessary output voltage regulation with the appropriate gain and often provides isolation.

Another family under the active approach is the single-stage configuration. This configuration was introduced as a way to reduce the cost and complexity of the two-stage structure [6]. In reality, it can be viewed more as a modification of the conventional two-stage PFC rather than as a class by itself. As can be seen in Figure 1-6, the PFC and the DC-DC cell share the control circuit and may also share the switches in this configuration. The energy storage capacitor between the two stages serves as a buffer and to provide the converter with the necessary hold up time. However, in the single-stage configuration, the voltage across the storage capacitor is not regulated, because the controller is used to regulate the output voltage. As a result this voltage can vary greatly, usually between 130-1000V in universal line applications, depending on the topology. This will have a negative impact on the design and cost of the PFC converter as will be discussed in the following Chapters.

Figure 1-6 System Configuration of Single-stage PFC Power Supply

#### C. Approach Comparisons

Generally, in low power applications and especially when designing to meet the minimum regulation requirements, if line voltage can be considered fairly invariant, the passive approach should be considered. However, a major drawback of the passive approach is the size and weight of the filtering components. On the other hand, when unity power factor is required, or when size is a key objective, or if the application requires high power, the active PFC is the only practical solution.

At low power levels, the active single-stage offers a great advantage over the passive approaches due to its simple structure, low cost, minimum weight and better PFC performance, even still, its performance, size, and cost are questionable when it compared to the two-stage approach. The following are the major problems associated with the single-stage active PFC approach:

# ✤ Intermediate Bus Voltage and Power Balance Issue: As mentioned before, the single-stage converter has only one

feedback control circuit to tightly regulate the output voltage. As a result, the intermediate bus voltage is kept unregulated and its voltage level depends on PFC cell topology. Since most likely the boost topology will be selected, this voltage may reach values of 1000V in a typical design depending on the line and load condition due to power balance requirements. To illustrate this condition, assuming that the DC-DC cell operates in CCM for enhanced performance, then the duty cycle will not change with load changes. When the load demand decreases, the input power will not change and all the power difference will be stored in the intermediate bus, raising its voltage to high levels. This condition will continue until a new power balance condition is achieved, since with the increase in the bus voltage, the duty cycle will be reduced to keep the output voltage regulated. More about the high intermediate bus voltage can be found in [7]. Since the intermediate bus capacitor should be selected to handle a high voltage rating, this will increase the converter cost considerably since capacitors with voltage ratings higher than 450V are uncommon. The MOSFET voltage rating will also be increased affecting its losses and price as well.

High current ratings: One way to get around the increased bus voltage is to use DCM operation for the DC-DC cell. In DCM, the

duty cycle depends on the load condition and hence the bus voltage will not increase is the same manner as in the previous case. On the other hand, the DCM operation comes with its own set of disadvantages. In particular, a requirement for higher peak current ratings for the components in the DCM converter resulting in device selection with higher cost and lower efficiency.

Sometimes a selector switch (110-220V) will limit some of these problems, but generally, a trade-off between improving the size and cost using single switch and one controller, to the cost and size of the storage capacitor should always be considered. In addition, a more expensive EMI filter in needed when operating the PFC cell in DCM to achieve automatic current shaping.

Unity power factor and tight output regulation for any power range can be achieved using the two-stage, active PFC. This structure is fully capable of compliance with regulations and is compatible with universal line voltage applications. Some negative factors include the increased cost and size associated with the two staged approach and sometimes the reduced efficiency associated with processing the power through two stages versus one.

In specific applications, all of the three options are capable of regulation compliances. Table 2-1 provides a general relative performance comparison for the passive and active single and two-stage approaches with the current available technologies [8].

| Performance<br>Review | Passive Scheme | Active Two-stage | Active Single-<br>Stage |

|-----------------------|----------------|------------------|-------------------------|

| THD                   | High           | Low              | Medium                  |

| Power Factor          | Low            | High             | Medium                  |

| Efficiency            | High           | High             | medium                  |

| Size                  | Large          | Medium           | Medium-Small            |

| Bulk Cap Voltage      | Variation      | Constant         | Variation               |

| Control               | Simple         | Complex          | Medium                  |

| Component Count       | Least          | Medium           | Medium-Low              |

| Power Range           | < 300 W        | Any              | < 300 W                 |

| Design Difficulty     | Low            | Medium           | High                    |

Table 1-2 Relative Performance Comparison of Three PFC Approaches

#### 1.4 Research Motivations

In this section, the motivations behind this work are outlined.

The existing PFC techniques, utilized in the marketplace today, are either a two stage structure that provides a unity power factor with high efficiency, or using passive components that cannot meet the regulation requirements. While the first solution has flexible structure that can lead to superior performance, it exceeds regulatory requirements on harmonic content while adding a 30% increase in the component count, and increasing the cost and the size of the converter. No other solution can compete with the

performance of the two stage approach, but at the same time, this performance is not required to meet the regulations and it comes with a higher price tag.

- All the previous attempts to integrate the two stage converter in to a single-stage were not completely successful due to several factors. First, the uncontrolled bus voltage was high, demanding an expensive capacitor. Second, high voltage and current stresses inherent in the design resulted in over-sized, expensive components and low conversion efficiency. Finally, in order to overcome these drawbacks, complex single-stage structures were proposed that have even more components than the two stage converters. Clearly these proposed schemes missed the underlying attraction to single stage PFC – potential cost reduction.

- Much literature has been devoted to single-stage converters with a direct energy transfer technique to solve the limitation of the single-stage approach. None of these papers quantified the amount of direct energy transferred to the output. In addition, due to the operation and topology complexity, no clear design curve or trade-off analyses were performed to make it easier for the practicing engineer to develop these topologies into an economically viable product.

Based on these motivations the objectives of this dissertation are:

- To review and investigate various recent techniques in harmonic reduction and power factor correction related to the single-stage structure, and in particular, to topologies with a direct energy transfer mechanism.

- To develop cost and performance justified topologies that adopt these improving techniques

- To perform a comprehensive analyses of these converters, and produce the design procedure and curves need for development.

- To compare the performance and draw conclusion for future research

## 1.5 Dissertation Outline

Chapter 2 will include a comprehensive review of single-stage power factor schemes and highlight some recent techniques that can be adapted to improve performance. In Chapter 3, the improved asymmetric half bridge converter with a parallel energy transfer branch will be introduced and analyzed. Chapter 4 will introduce the bi-flyback topology as a candidate topology to compete with current state of art converters. Operation, topology analysis, and design curves will be provided and the key relationships will be derived. Chapter 5 will focus on the average modeling. A new five-terminal general average model will be defined and its terminal relations will be derived. The new model will be used to obtain the frequency response of the proposed bi-flyback converter. In Chapter VI, the center-tapped flyback converter will be proposed to overcome some of the limitations of the biflyback topology. Chapter VII will summarize the results obtained in this dissertation and propose some future work.

# CHAPTER 2 OVERVIEW OF SINGLE-STAGE POWER FACTOR CORRECTION TECHNIQUES

## 2.1 Introduction

This of various topological chapter presents overview an implementations of the single-stage power factor correction converter [9] that has been recently published in the open literature. The discussion in this chapter includes commonly used strategies and various types of converter topologies. A comparison between these strategies and converter topologies will be given. Since object of the work is to improve mainly the efficiency and reduce the stress on the PFC converters while keeping cost competitive, only relevant topologies are discussed. While the literature is rich with publications on this topic, only few address a truly feasible solution. The direct energy transfer capability of these topologies is considered a major improvement technique offering a promising efficiency advantage. This approach will be used in the topologies proposed in later Chapters.

# 2.2 Original Single-Stage Topologies

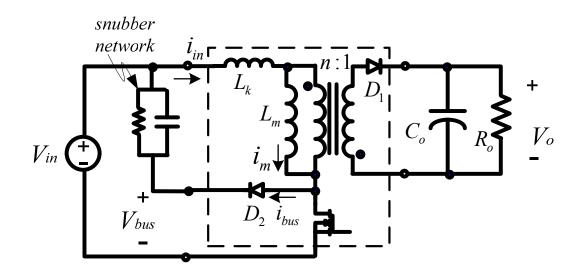

One of the earliest converters proposed to alleviate the component count, cost, and complexity issues of the two-stage approach was the BIFRED converter [6]. The BIFRED is an integrated boost-flyback converter using a single-switch and a single-controller to achieve both high input PFC and tight output voltage regulation simultaneously, as shown in Figure 2-1. The main advantage of this structure lies in the fact that the transformer primary side is in series with the bus capacitor. As a result, the capacitor voltage is reduced by the amount of the reflected output voltage. The converter's proposed operation was DCM for the input boost inductor and CCM for the flyback output DC-DC converter. This is done in order to achieve both automatic PFC at the input and to reduce RMS current at the output. The main disadvantage of this topology is the high storage capacitor voltage due to the power imbalance. This voltage can be as high as 1000V at light load conditions, and this solution becomes impractical when considering the commercial 450V capacitors and 600V MOSFETS.

Figure 2-1 the BIFRED Converter

To alleviate the stress on the bus capacitor, variable frequency operation was proposed in [10]. In this contribution, it was noted that the DC-DC converter gain depends only on the duty cycle, while the input PFC circuit gain depends on the frequency but not duty cycle, as shown in Eq. (2.1).

$$V_{cs} = \frac{V_{in}}{2} \left( 1 + \sqrt{\frac{1 + n^2 V_o}{L f_s I_o}} \right) - n V_o$$

$$\tag{2.1}$$

As a result, increasing the switching frequency at lighter load can regulate the bus capacitor voltage. While this method can effectively regulate the bus voltage, the implementation faces many difficulties due to the required frequency variation. These difficulties include the following:

- The frequency has to vary up to 10 times to maintain the bus voltage at 450V as the load decreases to 10%, as shown in Figure 2-2. This high switching frequency will lead to efficiency degradation due to switching losses.

- Complex magnetic design including the main transformer and the filter.

Figure 2-2 Switching Frequency vs. Load Current

In order to overcome the limitation in the DCM-CCM operation, a family of Single-Stage Isolated Power-factor-correction Power supply (SSIPP) was proposed in [11, 12], shown in Figure 2-3. The basic principle of operation is that both the PFC and the DC-DC cells always operate in DCM to alleviate the power balance issue. While the proposed method was effective in reducing the bus voltage, it was not possible to use the 450V capacitor because the voltage is still higher than 500V under high line voltage. In addition, the proposed DCM operation for the DC-DC stage will result in high peak current on the secondary side of the transformer, which will have the added consequence of reduced efficiency due to conduction losses. The high ripple current in the secondary side will also lead to an increase in filter size at the output.

Figure 2-3 Single-stage Boost/Flyback Combination Circuit

## 2.3 DC Bus Voltage Feedback

One of the most effective techniques to solve the excessive DC bus voltage is called DC bus voltage feedback [13-18]. In this technique a coupled inductor to the DC-DC transformer is added in the charging path on the boost inductor, as shown in Figure 2-4. By inspection, this coupled inductor will act as a negative feedback branch that feeds scaled bus voltage to the charging path of boost inductor and steady state balance can keep the bus voltage below 450V, while the DC-DC converter is operating in CCM.

(a)

(b) Figure 2-4 Single-stage PFC converter: (a) Boost/Flyback with DC-bus Voltage Feed-back, (b) BIFRED with DC-bus Voltage Feed-back

In addition to the reduced bus voltage stress, this topology can reduce the current stress on the main switch. This is as a result of the aid given by the introduced winding in charging the magnetizing inductor of the DC-DC transformer. This leads to less current discharged from the bus capacitor and less current processed by the switch. This topology also includes a direct energy transfer period since the discharging current from the boost inductor will be coupled directly to the output without the need to be processed twice. The same technique is used in the proposed converter in Chapter 6.

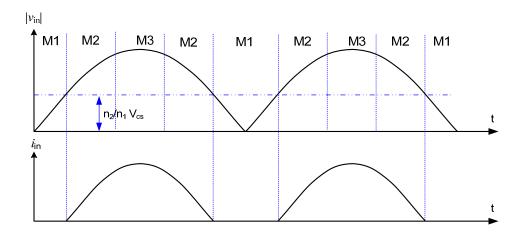

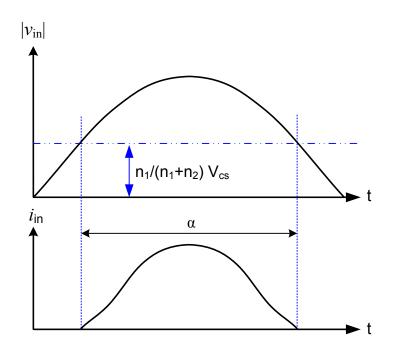

On the other hand, the operation of this topology includes a Mode that does not allow the full conduction angle of the input line current as shown in Figure 2-5. Mode 1 happens when the reflected bus voltage is higher than the rectified input voltage and depends on the amount of the bus voltage feedback  $(n_2/n_1 \text{ ratio})$ . The limited conduction angle will deteriorate the Power Factor (PF) performance of the converter and increase distortion. In order to comply with the regulations, the amount of voltage feedback has to be limited, and as a result the reduced switch losses and the amount of direct energy transfer have to be limited as well. This tradeoff between performance and PF results in low efficiency, approximately 71% as reported in [17]. This type of feedback is indirect because the feedback occurs after the bulk capacitor voltage increases. In conclusion, while this topology can limit the bus voltage to a reasonable value, the PF and THD requirements limit the direct energy transferred and the amount of efficiency improvements that can be expected with the voltage feedback feature.

Figure 2-5 Modes of Operations in the DC-bus Voltage Feedback Topologies

# 2.4 CCM Operation of the PFC Cell

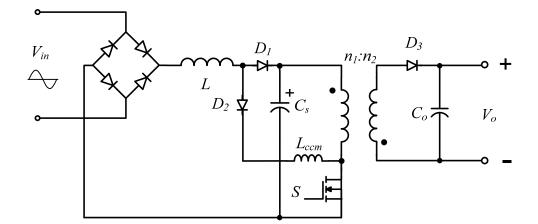

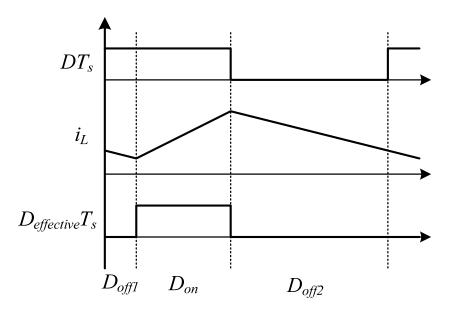

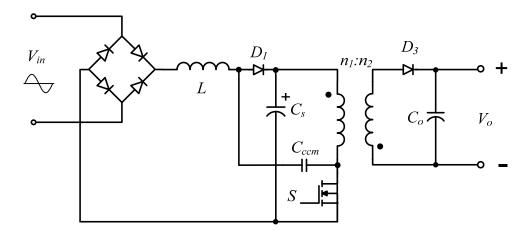

To enhance the efficiency in higher power applications, CCM operation of the single-stage PFC converter was proposed in [18-20]. While CCM operation is usually employed in the two-stage approach, a dedicated controller is necessary to modulate the duty cycle in the PFC stage. Enlarging the boost inductor size to force CCM operation in the single-stage approach will only result in high current distortion. This is a result of the fact that the constant duty cycle condition for PFC is only valid during DCM operation. As a result, a new modulation scheme is necessary to modulate the effective duty cycle across the boost inductor, while the actual duty cycle stays constant.

To accomplish this task, the topology in Figure 2-6 was proposed in [18, 19]. The principle of operation for this circuit is based on changing the effective duty cycle on the boost inductor without changing the actual duty cycle of the converter. The needed effective duty cycle is given by[20],

$$d_{pfc} \approx 1 - \frac{V_{in}}{V_{Cs}} \left| Sin(\omega t) \right|$$

(2.2)

According to this equation, the duty cycle has to change inversely with the line voltage. The circuit in Figure 2-6 accomplishes this task by adding an inductor in the charging path. As shown in Figure 2-7, the added inductor will prevent the main boost inductor from charging up until the currents in both inductors are the same. This action will modify the effective duty cycle to be  $D_{on}$ - $D_{off1}$ . At the same time,  $D_{off1}$  depends on the line voltage. When the line voltage increases, the discharge rate will decrease leading to a longer discharge time and reduced effective duty cycle. The same concept can be applied by employing a capacitor in changing path as shown in Figure 2-8.

Figure 2-6 Current Source CCM PFC Circuit

Figure 2-7 Effective Duty Cycle in Single-Stage PFC

Figure 2-8 Voltage Source CCM PFC Circuit

While the proposed CCM operation might offer a reduction in the size of the EMI filter and reduced current ripple in the bus capacitor, the following should be noted when evaluating this solution:

- CCM operation might offer enhanced efficiency for medium and high power applications. However, the reverse recovery losses of the boost diode present a serious threat in low power applications, where the single-stage approach is especially attractive.

- The exact equation that describes the unity power factor condition requires a time varying inductance, and as a result, these topologies cannot claim unity power factor operation.

- The PFC condition previously discussed only applies to CCM operation. While the converter will be designed for CCM operation, it will enter DCM operation each switching cycle at low line voltage. This behavior will create similar effects to the reduced conduction angle in voltage feedback topologies discussed earlier.

- This topology has a higher RMS current through the single switch when compared to 2 stage topologies. This will result in efficiency reduction.

## 2.5 Direct Energy Processing Approach

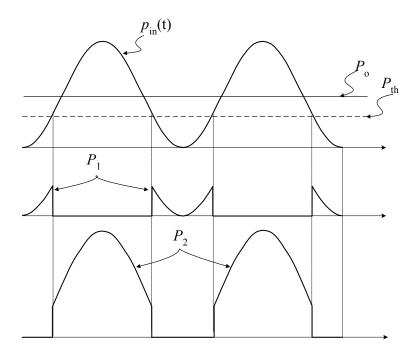

Single-stage and two-stage approaches adapt the simple cascade configuration, where two converters are separated by an energy decoupling element, the bus capacitor. To understand the nature of energy transfer and the real need for the decoupling element, the instantaneous input power and the average output power waveforms in a single-phase, PFC converter are shown in Figure 2-9.

Figure 2-9 Power Relationship in Single-Phase PFC Converters

The input power is a square sin function with double the line frequency,

$$p_{in}(t) = V_{in}I_{in}\sin^2\omega t = 2P_o\sin^2\omega t$$

(2.3)

As we can see, the converter has to process a peak power that is twice the output power. At the same time this power has to be stored and then delivered to the output. Typically, the output capacitor is not the correct choice to store this energy for two reasons. First, the output voltage will fluctuate with double line frequency because tight output voltage regulation will require a small output capacitor. The second reason is the required holdup time of the converter. As a result an energy decoupling capacitor is needed in the circuit. The location of the energy storage element becomes critical and general configuration of the topology will play an important role. If we analyze the power waveforms in Figure 2-9, solving for the time when the instantaneous input power is equal to the output power, then integrating the input power to find the relationship between  $P_1$  and  $P_2$ , we can find that 68% of the energy can be transferred directly to the output, and only 32% of the energy has to be stored and then reprocessed to the output. If  $P_1$  energy is directly transferred to the output, the output voltage ripple will not see the double frequency, primarily a result of excesses in power storage. As a result of these findings, a new family of converters adapted the direct energy transfer scheme or parallel energy transfer scheme. The main focus is now changed to the topology structure that can accomplish this task with a minimum number of components while delivering maximum energy directly to the output for enhanced efficiency. Figure 2-10 shows the block diagram that illustrates this direct PFC scheme.

Figure 2-10 Block Diagram for the Direct PFC Scheme

Many circuit implementations have been suggested to implement the direct energy transfer scheme[21-27]. Earlier publications were directed more toward two-stage implementation to improve the efficiency [21, 26]. An example of the two stage implementation is shown in Figure 2-12. While the direct energy transfer mechanism is clear in this topology, the implementation scheme itself involves many components and might not be a good practical implementation.

Figure 2-11 Parallel Power PFC Converter

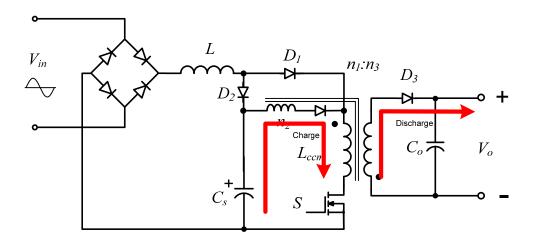

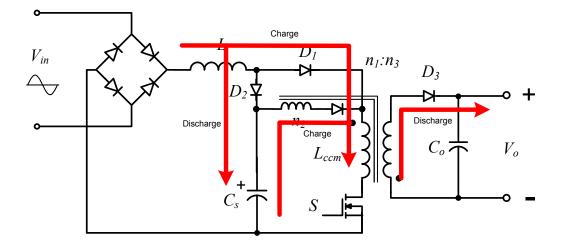

The direct energy transfer scheme was later adapted in the singlestage implementation. An example of the single-stage implementation is the topology shown in Figure 2-12 [28], which features the direct energy transfer mechanism. This topology utilizes an extra winding on the main flyback transformer to create a voltage course in series with the storage capacitor. Depending on the value of this voltage, the converter will have a limited conduction angle as shown in Figure 2-13. Before the converter starts to draw current from the input, all the power will be processed from the storage capacitor, as shown in Figure 2-14 (a). After the input voltage reaches a predetermined value, the energy will be processed from the input to the output directly through the flyback converter, and the remainder of the needed energy will be processed from the storage capacitor, as shown in Figure 2-14 (b). At the same time, the input inductor will be charging the storage capacitor. While the input voltage continues to increase, more energy will be processed from the input to the output and to the storage capacitor. Near the peak input voltage, the input inductor will change operation from DCM to CCM as a direct result of the increased current processed through the input. Switching between DCM and CCM leads to more line distortion and control difficulties. And as in the majority of the published papers, there was no clear design procedure nor quantified trade-offs between direct energy transfer, PF, and bus voltage.

Figure 2-12 Single-switch PFC Converter with Inherent Load Current Feedback

Figure 2-13 Boundary Modes of Operation during Half-line Cycle

(a)

(b)

Figure 2-14 Energy Transfer Paths during the two Modes of Operation

A simple implementation scheme was proposed in [29] through the flyboost cell. The mechanism of operation in this scheme relies on introducing a threshold power level  $P_{th}$ , as shown in Figure 2-15, and when the input power is lower than this threshold value the power will be transferred directly to the output, portion  $P_1$ , otherwise it will be processed twice by both stages, portion  $P_2$ .

Figure 2-15 Power flow Diagram of the Proposed Scheme

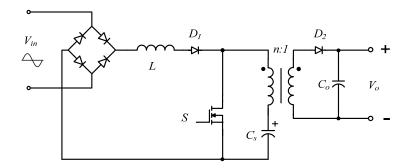

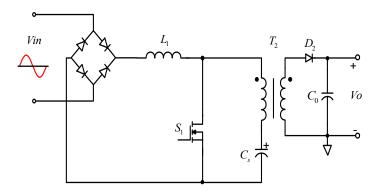

The flyboost cell can be implemented in any boost-based PFC converter, by adding another winding to boost inductor and feed it to the output capacitor [30, 31] as shown in Figure 2-16. Unlike the previous implementation, the flyboost implementation is simple [32, 33] and can be adapted in many single-stage converters. In general, to implement the parallel energy path for any boost-based PFC converter, we can add another winding to boost inductor and feed it to the output capacitor. On the other hand, the power flow analysis of these converters is more complicated and requires several measures in the design procedure as described in the proceeding chapters.

Figure 2-16 Basic Circuit Schematic of the AHBC Converter Proposed in Chapter 3

# CHAPTER 3 IMPROVED ASYMMETRIC HALF-BRIDGE SOFT-SWITCHING PFC CONVERTER USING DIRECT ENERGY TRANSFER TECHNIQUES

#### 3.1 Introduction

Of course, the ideal PWM converter is lossless. In reality, power dissipation is due to the non-idealities in the power components and mainly the semiconductor switches themselves. With the improvements in semiconductor technologies, switch performance has become more reliable and the switching losses have been considerably reduced. With these improvements, the converter can be operated at a higher switching frequency, resulting in reduce size and weight of passive components. Switching losses had become the main concern with the current trend of increasing the switching frequency. For certain applications, resonant converters were a promising solution. Resonant converters eliminate nearly all the switching losses and leave the path open for an even higher switching frequency, but still, they too have their drawbacks. During the resonant process, the switch current or voltage reach high values, higher than those in the regular PWM converters, this drawback increases the conduction losses.

The Asymmetric Half Bridge Converter (AHBC) provides a good method for soft switching. In this chapter, the development of the original Asymmetric Half Bridge Converter (AHBC) will be presented. In addition, the new, improved AHBC will also be discussed including with a discussion of the detailed analysis and design considerations followed by simulation and experimental results.

## 3.2 The Original Asymmetric Half-Bridge Converter

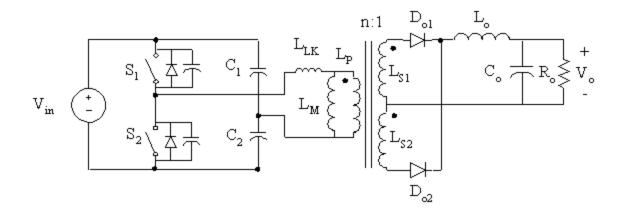

Soft switching can be achieved in any transformer-coupled PWM converter with half or full bridge configuration operating at 50% duty cycle. By allowing a small, controlled dead time between the two conduction periods, the leakage inductance of the transformer can resonate with the parasitic capacitors in the switches and soft switching can be achieved. The original half bridge forward converter is shown in Figure 3-1[34]. In addition to the potential soft switching, the half bridge configuration allows more power handling capabilities than the single switch topology, and has fewer components than the full bridge configuration making it a good choice for medium power applications. The dead time between the switches can be noticed in Figure 3-2(a). Soft switching can be achieved only at 50% duty ratio. Soft switching will be lost if the converter operates at any other duty ratio because the voltage across the switch will rise back again before the turn ON time of that switch. As a result, no output regulation can be achieved.

Figure 3-1 Half-Bridge Forward Converter

In Figure 3-2(b) we can see how the asymmetric switching scheme can alleviate that problem by operating each switch at a different duty cycle. By using asymmetric switching with a small dead time between switching to achieve lossless switching, we can effectively regulate the output by changing the duty cycle of the switches. Beyond the complementary duty ratio, the main difference between the symmetric and asymmetric switching is the different voltage levels on the upper and lower bridge capacitors,  $C_1$  and  $C_2$  in Figure 3-1. To find the voltage of each capacitor we can write the input voltage loop equation, Eq. (3.1), and the volt-second balance equation on the primary magnetizing inductor  $L_M$ , Eq. (3.2). Note that Eq. (3.2) ignores the leakage inductor's effect.

$$V_{C1} + V_{C2} = V_{in} \tag{3.1}$$

$$-V_{C1}D + V_{C2}(1-D) = 0 (3.2)$$

By solving Eq. (3.1) and Eq. (3.2) we find,

$$V_{C1} = V_{in}(1 - D) \tag{3.3}$$

$$V_{C2} = V_{in}D \tag{3.4}$$

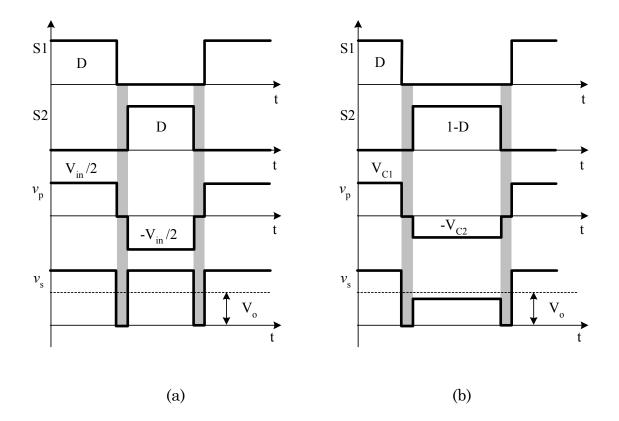

Using the volt-second balance equation on the output inductor  $L_o$ , we can find the gain equation of the asymmetric half bridge converter as,

$$M = \frac{V_{in}}{V_o} = \frac{2D(1-D)}{n}$$

(3.5)

Figure 3-2 Switching Waveforms: (a) Symmetric witching, (b) Asymmetric switching

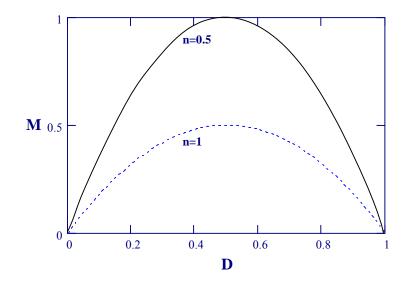

The plot of the quadratic relationship in Eq. (3.5) is shown in Figure 3-3. The gain is at maximum at a duty ratio of 50% and reaches zero at zero or 100% duty ratio. It is therefore possible to regulate the output voltage by varying the duty ratio while, at the same time, maintain soft switching.

Figure 3-3 The DC-DC Conversion Characteristics of the Asymmetric converter

The above analysis shows that the AHBC is advantageous in terms of the high operating frequency and soft switching, which allow a simple and small output filter. On the other hand, due to the complementary control mechanism, the switches experience very different levels of stress. Due to the nature of the conversion characteristics shown in Figure 3-3, the converter's duty ratio should be chosen far from the ideal 50% to allow regulation to take place. When the duty cycle is small, one switch suffers very high stress, which deteriorates the performance. To solve this problem, the unbalanced magnetic was introduced to bring the duty cycle back closer to the 50%. Figure 3-4 shows the implementation of this solution with a current doubler at the output side [35]. Another realization of the AHBC in the PFC converter can be found in [36] where coupled input inductors were used.

Figure 3-4 Asymmetric Half Bridge Forward Converter with unbalanced magnetic and current doubler

It can be shown that the new DC gain equation for this converter is given by,

$$M = \frac{V_o}{V_{in}} = \frac{D(1-D)}{n_1 D + n_2 (1-D)}$$

(3.6)

This formula is plotted in Figure 3-5, and shows that the curve is simply tilted from its previous shape. The maximum gain is approximately at D=0.6 now. With this modification the converter can operate closer to 50% duty

cycle (more nearly a DC input current) over the normal range of the input voltage.

Many other attempts to improve the performance of the AHBC were cited in the open literature [37, 38]. The AHBC can also be simplified as show in Figure 3-6. We still can get the asymmetric operation after eliminating the upper capacitor. The DC voltage  $V_a$  across the asymmetric capacitor, or sometimes refer to it as the balance capacitor, will compensate for the unbalanced transistor timing. This voltage guarantees that the power transformer is evenly excited in both directions. The parasitic capacitor of the switches and the magnetizing inductor was not drawn in Figure 3-6, but the operation assumes their existence.

Figure 3-5 M vs. D for the Asymmetric Converter with Unbalanced Magnetics

The final gain equation for this structure is,

$$\frac{V_o}{V_{in}} = \frac{2D(1-D)}{n}$$

(3.7)

We can notice that Eq. (3.7) and Eq. (3.6) are similar. The advantage of eliminating one capacitor comes at the expense of a higher difference in the switches stress levels. However, the circuit shown in Figure 3-6 will be used as the output cell in the improved asymmetric power factor correction converter discussed in the coming section.

Figure 3-6 Single Capacitor Asymmetric Converter

# 3.3 The Proposed Soft-Switching Topology