## Formal Design of Cryptographic Hardware

| 著者     | Ueno Rei                             |

|--------|--------------------------------------|

| 学位授与機関 | Tohoku University                    |

| 学位授与番号 | 11301甲第18186号                        |

| URL    | http://hdl.handle.net/10097/00122854 |

### Tohoku University

#### **Graduate School of Information Sciences**

# Formal Design of Cryptographic Hardware

### Rei Ueno

Supervisor:

Prof. Takafumi Aoki

Prof. Naofumi Homma

Dissertation presented in partial fulfillment of the requirements for the degree of *Doctor of Philosophy*

# Formal Design of Cryptographic Hardware Rei Ueno

# Acknowledgments

I wrote this thesis as the summarizing compilation of my study at Aoki Laboratory. Although the road was steep and complicated, many amazing people led me to a better direction with their support, which made me possible to reach such a honorable goal (and a starting point of new road as a researcher).

First of all, I would like to show the greatest appreciation to my supervisor Professor Takafumi Aoki. He has greatly encouraged me in my learning and study, and has always trusted me even when I had made mistakes and failures. He has also taught me the importance of challenging myself to everything, and let me find delight in study, research, and modern computer games.

I am awfully grateful to Professor Hiroki Shizuya and Professor Masanori Hariyama. I could surely improve my thesis thanks to their insightful and valuable comments.

I owe a very important debt of gratitude to my supervisor Professor Naofumi Homma. I could not have written this thesis as readily as I had done unless he had supervised me. I have always had the honor of asking him about both research and off-research problems, which was essential for pursuing my daily study and living. I believe that what he taught should offer the promise of a brilliant future for me.

I have really enjoyed collaborative research and discussions with many outstanding researchers, which brought expertised knowledge and a remarkable outcome to me. While it would be hard to count everyone, a part of the people who especially helped me write my thesis and journal/conference papers is listed here with great appreciation: Dr. Sumio Morioka, Professor Yasuyuki Nogami, Dr. Kazuhide Fukushima, Dr. Shinsaku Kiyomoto, Dr. Yuto Nakano, Professor Jean-Luc Danger, Professor Sylvain Guilley, Dr. Yves Mathieu, Professor Makoto Nagata, Dr. Noriyuki Miura, Professor Kazuo Sakiyama, Dr. Takeshi Sugawara, Professor Yu-ichi Hayashi, Dr. Daisuke Fujimoto, and Dr. Kazuhiko Minematsu.

I had fortune to be a member of Tohoku University's Aoki Laboratory and Homma Laboratory, which gave me the good opportunity to share offices with many teachers and friends whom I esteem. I would like to thank them who made me have the fulfilling time of my life. Further-

more, I would like to extend my respect and gratitude to my seniors and friends graduated from the laboratory. Please let me introduce my lovely teachers, friends, and seniors here with great admiration: Dr. Koichi Ito, Mr. Ville Yli-Mäyry, Ms. Manami Suzuki, Mr. Hirokazu Oshida, Mr. Shota Hishinuma, Mr. Ryuichi Fufimoto, Mr. Akira Ito, Mr. Sora Endo, Mr. Kohei Koiwa, Mr. Hayato Mori, Mr. Daisuke Miyata, Mr. Kouya Yodokawa, Mr. Takehisa Okano, Mr. Jun-ichi Hata, Mr. Shotaro Sawataishi, Mr. Kohei Kazumori, Mr. Shuto Funakoshi, Dr. Sho Endo, Mr. Takafumi Hibiki, Mr. Kotaro Okamoto, Mr. Hajime Uno, Mr. Yukihiro Sugawara, Mr. Shoei Nashimoto, Mr. Daisuke Ishihata, and Mr. Wataru Kawai.

I was also lucky to study in such a beautiful city, where it is easy to find refreshments, restaurants, and amusements to get away from my work. I want to thank such shops, in particular, coffee shop To-mon, Chinese restaurant Fukuraien, Japanese soba restaurants Myouan and Koushouan, tonkatsu restaurant Katsusei, washu bar RAMBLE, and wine bar Clos de la Barre. They provided me the mental energy to pursue my (sometimes hard) work with their fine dishes and beverages.

Finally, special thanks to my dearest family, who have kindly supported me with their understanding, encouragement, sacrifice, and endless love.

Rei Ueno January 2018, Sendai

## **Abstract**

Cryptography has been widely deployed for secure information systems with secret communication, authentication, and digital signature. As a result of rapidly increasing LSI systems, hardware implementation of cryptographic algorithms is being essential to realize cryptographic operations efficiently from only transaction servers to resource-constraint embedded devices. In addition, there is high demand of cryptographic hardware resistant to tampering attacks such as Side-Channel Attacks (SCAs), because cryptographic hardware is used as a security primitive and root-of-trust for information systems. Thus, rapid design and verification methods for various cryptographic hardware are strongly required as more and more cryptographic algorithms, hardware architectures, and countermeasures against tampering attacks are being developed.

On the other hand, the conventional Electronic Design Automation (EDA) tools with Hardware Description Languages (HDLs) have difficulty in designing cryptographic hardware. While most modern cryptography is based on Galois-Field (GF) arithmetic, the conventional EDA tools have not supported high-level description and automatic synthesis of GF arithmetic circuits. The lack of high-level design methodology for GF arithmetic circuits forces designers to describe the structural details of cryptographic hardware with massive low-level logical expression by hand, which makes it difficult to design, debug, and optimize cryptographic hardware. To make matters worse, the difficulties with the verification are more serious than those with the design itself. We cannot verify circuits with input bit length greater than 128 bits by the common logic simulation while cryptographic hardware frequently have more than 128-bit operands for the resistance to cryptanalysis attacks. Moreover, it is basically difficult to apply the conventional high-level synthesis and formal verification methods to practical GF arithmetic circuits because they have been basically developed for integer and floating-point arithmetic. Nevertheless, complete verification of cryptographic hardware is quite important because they are frequently used for mission-critical and high-security systems.

To address these problems, a formal design method for GF arithmetic circuits was presented. The method describes GF arithmetic circuits with a hierarchical mathematical graph called *GF*

Arithmetic Circuit Graph (GF-ACG). Since GF-ACG hierarchically represents functions of GF arithmetic circuits by GF equations, the circuit function can be formally verified by equivalence checking of the GF equations between hierarchies. It was shown that we could completely verify a 128-bit GF multiplier and a 128-bit Advanced Encryption Standard (AES) hardware using Gröbner basis and polynomial reduction techniques for the equivalence checking.

However, it is still challenging to apply the formal design method to practical cryptographic hardware. The above method was applied to only standard and straight-forward architectures without optimization techniques nor higher-degree functions. For example, while redundant GF representations and pipelining techniques are sometimes useful for high-performance and/or SCA-resistant cryptographic hardware design, the conventional GF-ACG cannot describe them. In addition, the computation time for a Gröbner basis heavily depends on the degree and number of variables derived from the target circuit function, and therefore the algebraic techniques have difficulty in verifying functions of higher-degree (e.g., AES decryption hardware and efficient AES encryption hardware with resister-retiming techniques) and circuits optimized at logic-level (e.g., tamper-resistant AES hardware). Thus, design methodology that can be applied to a wider variety of cryptographic hardware is quite necessary in the fields of EDA and information security.

This dissertation studies a formal design of cryptographic hardware. The contribution of this dissertation is threefold.

Firstly, we propose a new formal design methodology for cryptographic hardware. We propose a new GF-ACG which can represent a wider variety of GF arithmetic circuits for practical cryptographic hardware including those with redundant GF representations and with pipeline architectures. We also propose two new equivalence checking methods for GF-ACGs and then present a verification algorithm combining three equivalence checking methods with the conventional one. The proposed algorithm can verify circuits with higher-degree functions and logic-level optimization in a systematic manner. The effectiveness and efficiency of the proposed algorithm are demonstrated through its applications to various GF arithmetic circuits and cryptographic hardware. For example, we successfully verify AES decryption hardware and tamper-resistant AES hardware while the conventional methods fail.

Secondly, we present an automatic generation system of GF multipliers for cryptographic hardware design developed based on the proposed method. The system generates verified HDL codes from multiplier specification. The system supports automatic synthesis of  $GF(p^m)$  multipliers where p=2,3,5,7,11 and  $2 \le m \le 256$ . In addition, the system can also generate SCA-resistant GF multipliers based on Generalized Masking Scheme (GMS). The SCA-resistance of generated circuits is verified by new algorithms proposed in this dissertation. As a result of experimental generation, we confirm that the system can generate large GF multipliers (e.g., whose

input bit length is  $256 \times 77$ ) within a practical time. The system generates compatible HDL codes which can be used in the conventional EDA tools, and therefore the proposed formal design methodology and the conventional EDA tools are connectable through the system.

Thirdly, in order to show the significance of the proposed methodology, we design highly efficient cryptograhic hardware architectures focusing on AES. We first present a highly area-time efficient  $GF(2^8)$  inversion circuit and AES S-box based on a combination of redundant and non-redundant GF arithmetic. We then present a high throughput/gate AES hardware compressing encryption and decryption datapaths. Finally, we present an efficient SCA-resistant AES hardware architecture based on a variation of GMS. The proposed AES hardware achieves approximately 20-50% higher area-time efficiency (i.e., lower energy) than the conventional best ones. While the proposed design utilize some practical techniques such as redundant GF arithmetic, pipelining, resister-retiming (resulting in higher-degree function), and/or logic-level optimization, we confirm that the proposed formal design methodology is applicable to such practical and state-of-the-art cryptographic hardware.

# Contents

| Ack  | nowl  | edgme   | ents                                         | i   |

|------|-------|---------|----------------------------------------------|-----|

| Abst | tract |         |                                              | iii |

| Con  | tents |         |                                              | vii |

| List | of Fi | gures   |                                              | xi  |

| List | of Ta | bles    |                                              | xv  |

| 1    | Intro | oducti  | ion                                          | 1   |

|      | 1.1   | Backg   | round                                        | 1   |

|      | 1.2   | Contril | butions                                      | 5   |

|      | 1.3   | Thesis  | Overview                                     | 7   |

| 2    | Preli | imina   | ries                                         | 9   |

|      | 2.1   | Introdu | uction                                       | 9   |

|      | 2.2   | Galois  | -Field Arithmetic                            | 10  |

|      |       | 2.2.1   | Overview                                     | 10  |

|      |       | 2.2.2   | GF representations                           | 11  |

|      | 2.3   | Crypto  | ography and Its Implementation               | 15  |

|      |       | 2.3.1   | Overview of cryptography                     | 15  |

|      |       | 2.3.2   | Cryptographic algorithms                     | 18  |

|      |       | 2.3.3   | Block ciphers and modes of operation         | 20  |

|      |       | 2.3.4   | Cryptographic implementation                 | 24  |

|      |       | 2.3.5   | Implementation attacks and countermeasures   | 26  |

|      | 2.4   | Design  | n of Arithmetic Circuits                     | 27  |

|      |       | 2.4.1   | Overview                                     | 27  |

|      |       | 2.4.2   | Problems on designing cryptographic hardware | 29  |

|   | 2.5 | Functio | anal Verification of Arithmetic Circuits                                 | 30 |

|---|-----|---------|--------------------------------------------------------------------------|----|

|   |     | 2.5.1   | Overview                                                                 | 30 |

|   |     | 2.5.2   | Related works                                                            | 30 |

|   |     | 2.5.3   | Problems on verifying cryptographic hardware                             | 33 |

|   | 2.6 | Formal  | Design of GF Arithmetic Circuits                                         | 34 |

|   |     | 2.6.1   | Overview                                                                 | 34 |

|   |     | 2.6.2   | Automatic generation system for GF arithmetic circuit                    | 35 |

|   |     | 2.6.3   | Issues on formal design of cryptographic hardware                        | 36 |

|   | 2.7 | Conclu  | sion                                                                     | 37 |

| 3 | For | mal De  | sign Methodology of Cryptographic Hardware                               | 39 |

|   | 3.1 | Introdu | ction                                                                    | 39 |

|   | 3.2 | Previou | s Work                                                                   | 40 |

|   |     | 3.2.1   | Formal Description of GF Arithmetic Circuits                             | 40 |

|   |     | 3.2.2   | Formal Verification of GF-ACG                                            | 43 |

|   |     | 3.2.3   | Example                                                                  | 47 |

|   | 3.3 | Propose | ed Method                                                                | 50 |

|   |     | 3.3.1   | Proposed Formal Description                                              | 50 |

|   |     | 3.3.2   | Proposed Formal Verification                                             | 59 |

|   | 3.4 | Applica | ations                                                                   | 75 |

|   |     | 3.4.1   | $GF(2^m)$ parallel multipliers                                           | 75 |

|   |     | 3.4.2   | $GF(2^8)$ inversion circuits $\ldots \ldots \ldots \ldots \ldots \ldots$ | 79 |

|   |     | 3.4.3   | AES hardware                                                             | 82 |

|   |     | 3.4.4   | Masked AES hardware                                                      | 85 |

|   |     | 3.4.5   | LED hardware resistant to DPAs based on pipeline                         | 87 |

|   | 3.5 | Discuss | sion                                                                     | 92 |

|   |     | 3.5.1   | Comparison with conventional formal verification methods                 | 92 |

|   |     | 3.5.2   | Applicability and generality                                             | 94 |

|   | 3.6 | Conclu  | sion                                                                     | 94 |

| 4 | Aut | omatic  | Generation System for Cryptographic Hardware                             | 97 |

|   | 4.1 | Introdu | ction                                                                    | 97 |

|   | 4.2 | System  | Overview                                                                 | 98 |

|   | 4.3 | Automa  | atic generation of $GF(p^m)$ multipliers                                 | 99 |

|   |     | 4.3.1   | Extension of GF-ACG to $GF(p^m)$ arithmetic circuit                      | 99 |

|   |     | 4.3.2   | Generation of $GF(p^m)$ parallel multipliers                             | 02 |

| ЫD       | liogr | apny           |                                                                                   | 165 |

|----------|-------|----------------|-----------------------------------------------------------------------------------|-----|

| 6<br>D:b |       | nclusio        | on                                                                                | 163 |

|          |       |                |                                                                                   | 101 |

|          | 5.5   |                | usion                                                                             |     |

|          |       | 5.4.3<br>5.4.4 | Our design                                                                        |     |

|          |       | 5.4.2          | GMS with $d+1$ input shares                                                       |     |

|          |       | 5.4.1          | Overview                                                                          |     |

|          | 5.4   |                | ent DPA-resistant AES hardware                                                    |     |

|          | F 4   | 5.3.4          | Performance evaluation                                                            |     |

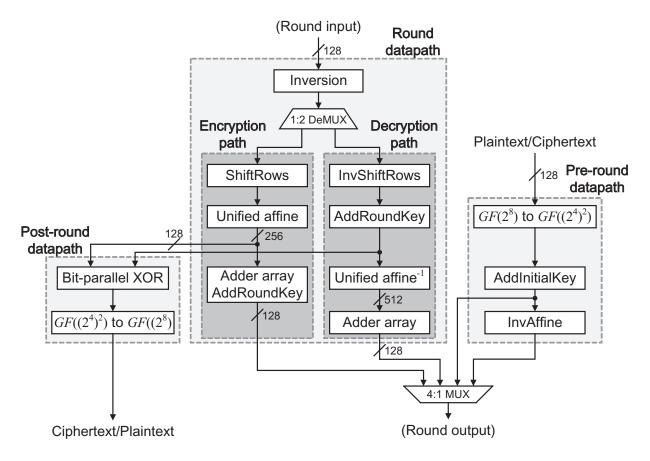

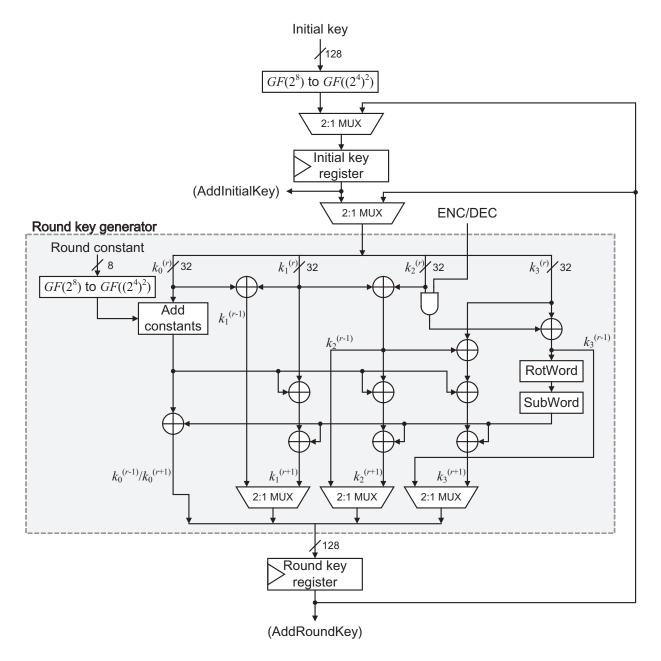

|          |       | 5.3.3          | Designed AES hardware                                                             |     |

|          |       | 5.3.2          | Related works to unified AES detapath for encryption and decryption.              |     |

|          |       | 5.3.1          | Overview                                                                          |     |

|          | 5.3   | _              | chroughput/gate AES hardware                                                      |     |

|          |       | 5.2.5          | Application to AES S-box design                                                   |     |

|          |       | 5.2.4          | Performance evaluation                                                            |     |

|          |       | 5.2.3          | Proposed $GF(2^8)$ inversion circuit                                              |     |

|          |       | 5.2.2          | Related works                                                                     |     |

|          |       | 5.2.1          | Overview                                                                          |     |

|          | 5.2   | Efficie        | ent $GF(2^8)$ inversion circuit and AES S-box                                     |     |

|          | 5.1   | Introd         | uction                                                                            | 121 |

| 5        | Des   | _              | Efficient AES Hardware                                                            | 121 |

|          | 1.5   | Conci          |                                                                                   | 11) |

|          | 4.5   |                | usion                                                                             |     |

|          |       | 4.4.5          | Discussion                                                                        |     |

|          |       | 4.4.4          | Functional verification and GMS property checking                                 |     |

|          |       | 4.4.4          |                                                                                   |     |

|          |       | 4.4.2          | Construction of GMS-based circuit                                                 |     |

|          |       | 4.4.1          | GMS properties                                                                    |     |

|          | 4.4   | 4.4.1          | natic generation of DPA-resistant $GF(2^m)$ multipliers based on GMS Attack model |     |

|          | 4.4   |                | -                                                                                 |     |

|          |       | 4.3.3          | Experimental generation                                                           | 108 |

# List of Figures

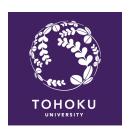

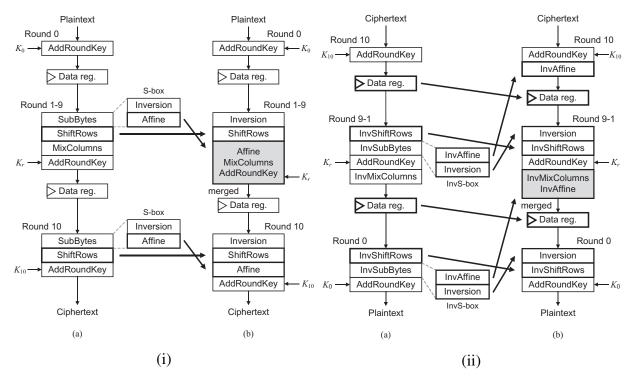

| 2.1  | (a) Encryption and (b) decryption flows of AES                                    | 21 |

|------|-----------------------------------------------------------------------------------|----|

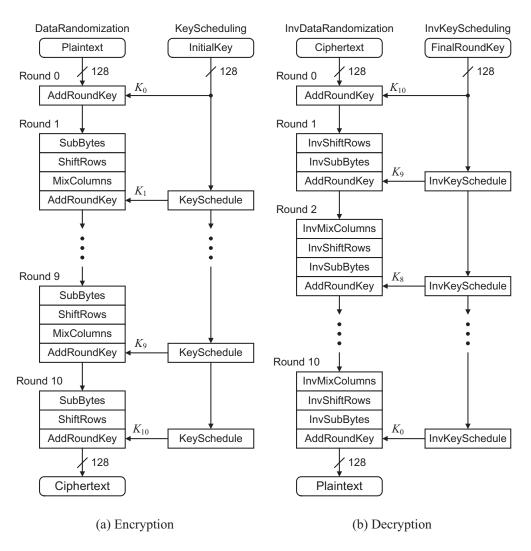

| 2.2  | LSI design flow                                                                   | 28 |

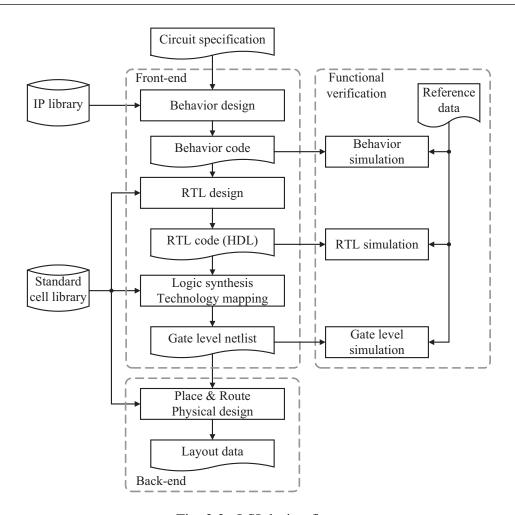

| 2.3  | Overvew of functional verification using reference                                | 31 |

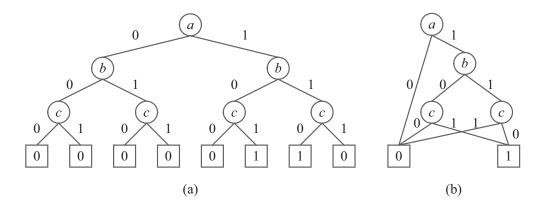

| 2.4  | (a) BDD and (b) ROBDD for $a \wedge (b \oplus c)$                                 | 32 |

| 2.5  | Block diagram of GF-AMG                                                           | 35 |

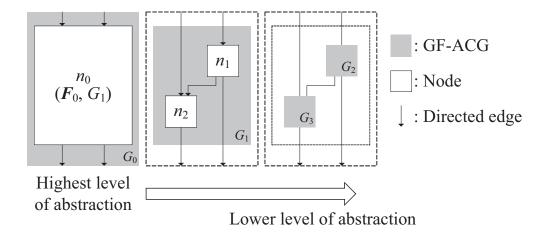

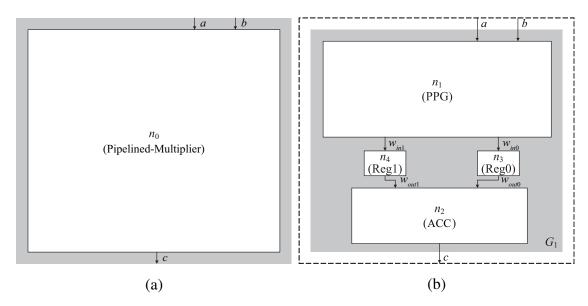

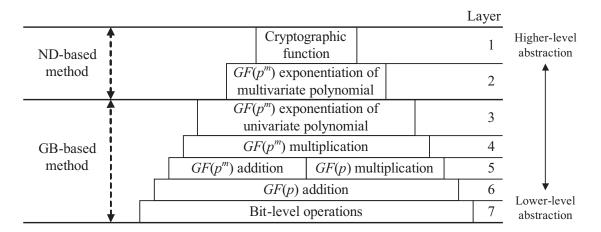

| 3.1  | Overview of GF-ACG                                                                | 40 |

| 3.2  | Decomposition nodes with functional assertion given by (a) Eq. 3.5and (b) Eq.     |    |

|      | 3.6                                                                               | 42 |

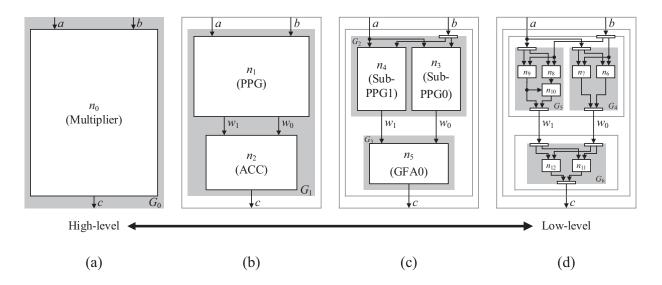

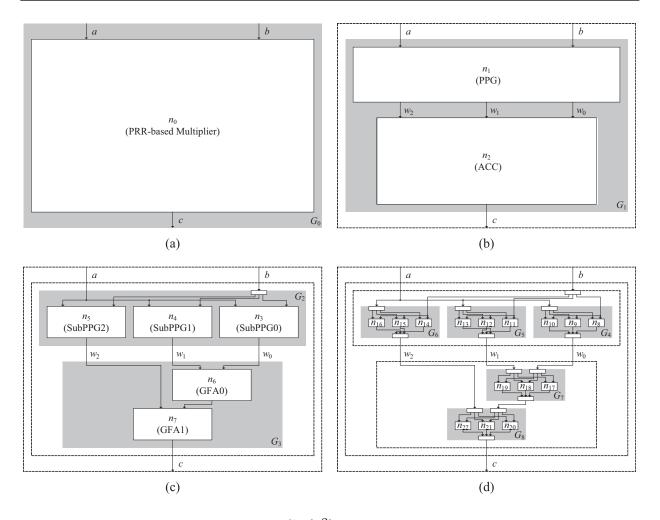

| 3.3  | GF-ACG for full-tree multiplier over PB-based $GF(2^2)$ : (a) highest- to (d)     |    |

|      | lowest-level of abstraction                                                       | 48 |

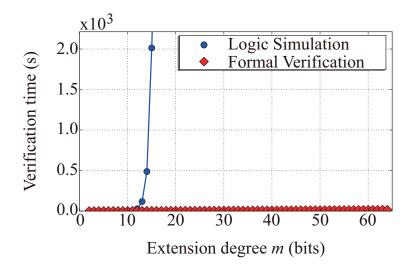

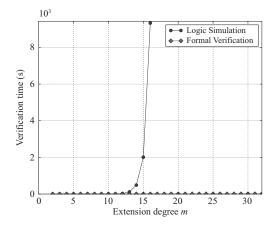

| 3.4  | Verification time of $GF(2^m)$ full-tree multipliers for $2 \leq m \leq 64.\dots$ | 50 |

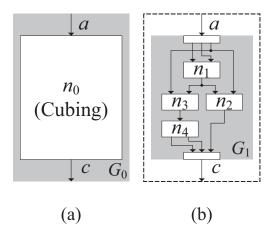

| 3.5  | GF-ACG for PRR-based $GF(2^2)$ cubing circuit                                     | 53 |

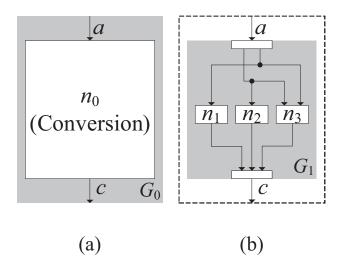

| 3.6  | GF-ACG for circuit converting from PB-based $GF(2^2)$ to PRR-based one            | 54 |

| 3.7  | GF-ACG for pipelined $GF(2^2)$ multiplier: (a) top- and (b) second-level of ab-   |    |

|      | straction                                                                         | 57 |

| 3.8  | Proof figures for inference rules of proposed method: (a) axiom of equal sign     |    |

|      | and (b) rule of equal sign                                                        | 60 |

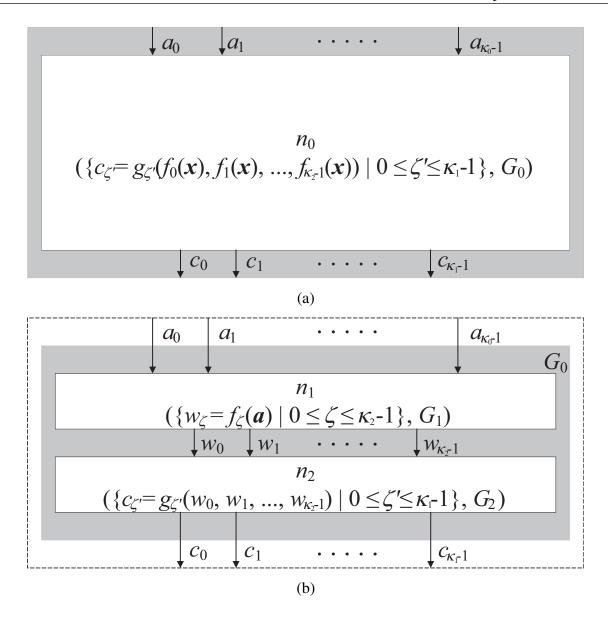

| 3.9  | Example of GF-ACG for ND-based method: (a) top-level and (b) second-level         |    |

|      | description                                                                       | 61 |

| 3.10 | Proof figure for verification of $n_0$ in Fig. 3.9                                | 62 |

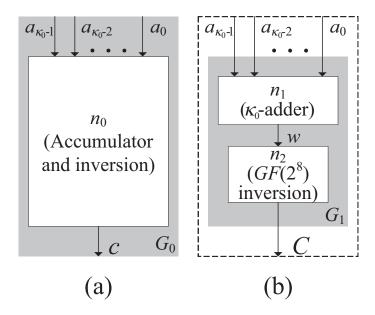

| 3.11 | GF-ACG for circuit connecting $\kappa_0$ -input adder and inversion in serial     | 64 |

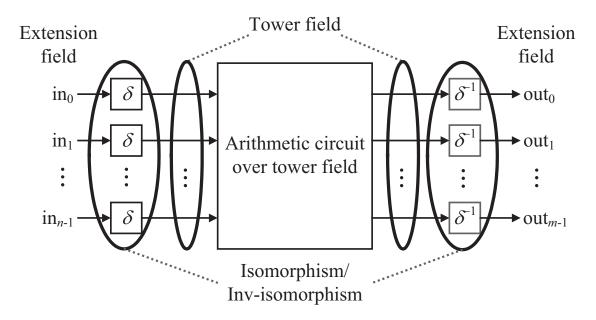

| 3.12 | Typical circuit structure of tower-field operation                                | 70 |

| 3.13 | Classification of circuit functions                                               | 73 |

| 3.14 | GF-ACG for PRR-based $GF(2^2)$ full-tree multiplier: (a) top- to (d) lowest-level |    |

|      | of abstraction                                                                    | 76 |

| 3.15 | Verification time of PRR-based full-tree multipliers                              | 76 |

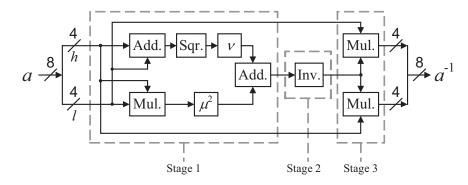

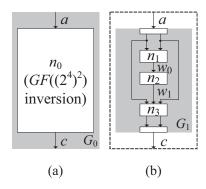

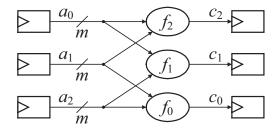

| 3.16 | Typical datapath of $GF(2^8)$ composite field inversion                           | 80 |

| 3.17 | GF-ACG for $GF((2^4)^2)$ inversion circuit based on combination of redundant                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | and non-redundant GF arithmetic: (a) top- and (b) second-levels of abstraction.                                                                             | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

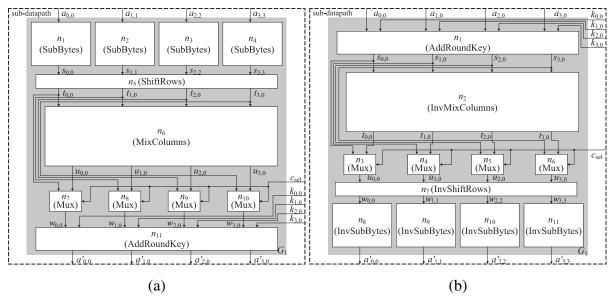

| 3.18 | GF-ACG for sub-datapath of AES (a) encryption and (b) decryption hardware 8                                                                                 | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.19 | Additional property of DPA-resistant operations                                                                                                             | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

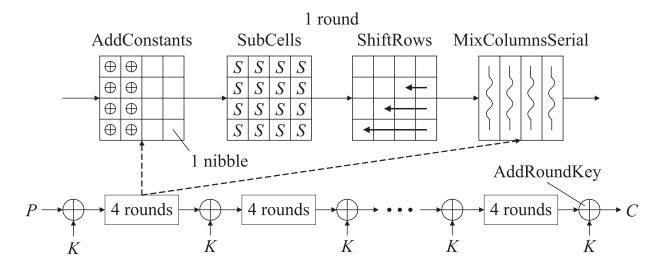

| 3.20 | LED encryption flow                                                                                                                                         | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

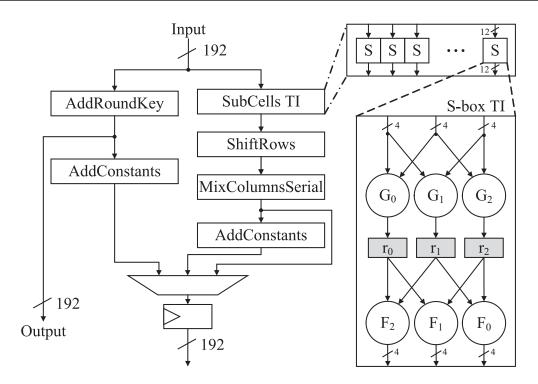

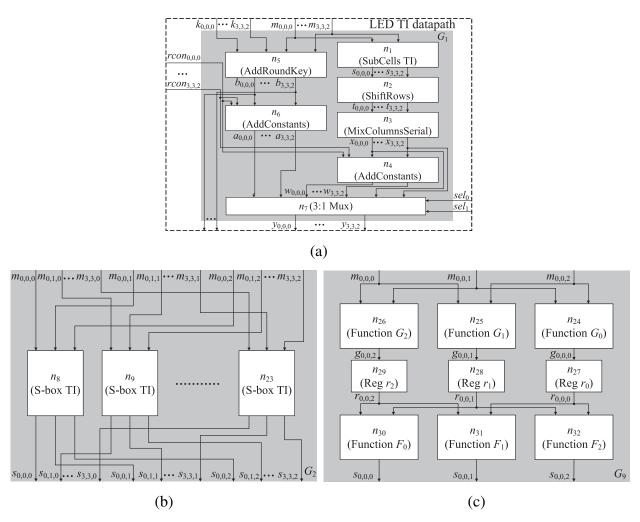

| 3.21 | Architecture of TI-based LED hardware and S-box                                                                                                             | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.22 | GF-ACG for TI-based LED hardware: (a) top-level node and internal structure                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | of (b) SubCells TI and (c) S-box TI                                                                                                                         | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

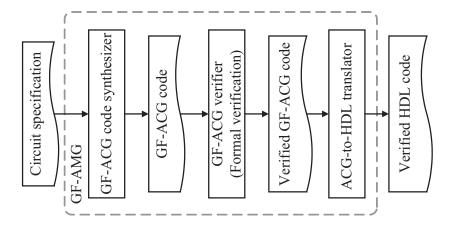

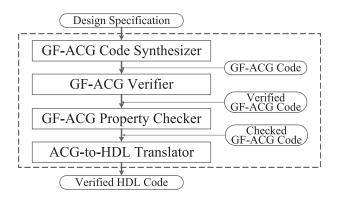

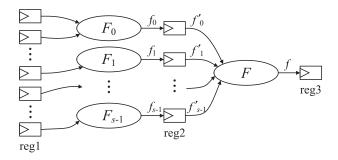

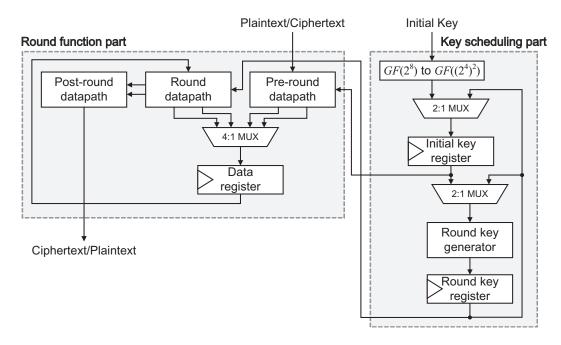

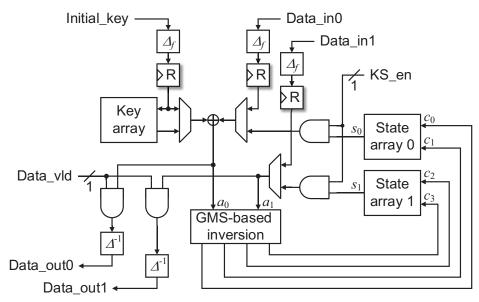

| 4.1  | Block diagram of GF-AMG                                                                                                                                     | )8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

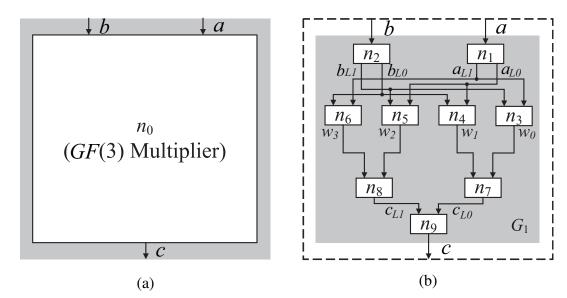

| 4.2  | GF-ACGs for $GF(3)$ multiplier                                                                                                                              | )1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

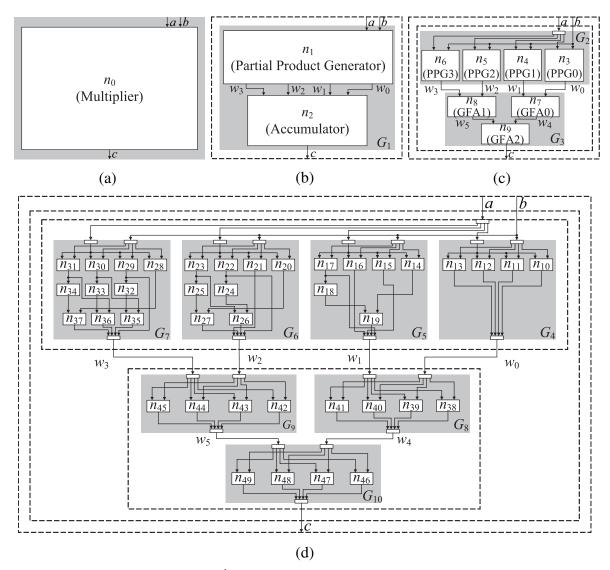

| 4.3  | GF-ACGs for $GF(3^4)$ parallel multipliers of (a) the top-level to (d) the 4th-level. 10                                                                    | )3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

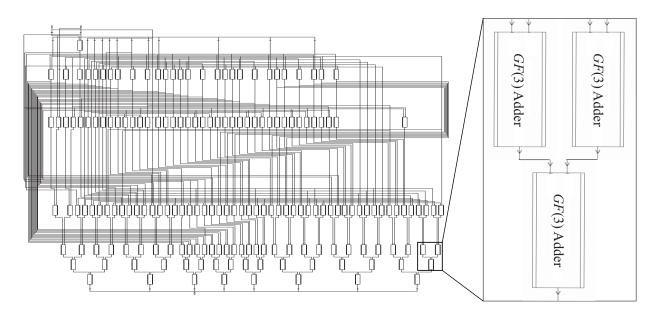

| 4.4  | Schematic of $GF(3^8)$ multiplier obtained from GF-AMG                                                                                                      | )6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

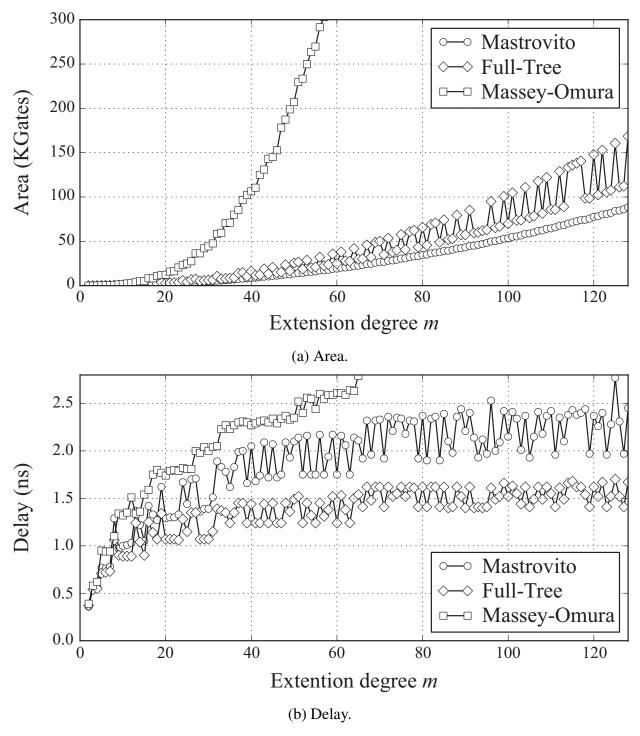

| 4.5  | Comparison of three types of $GF(2^m)$ multiplier for different extension de-                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | grees                                                                                                                                                       | )8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4.6  | Example of $d$ th-order probing model                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

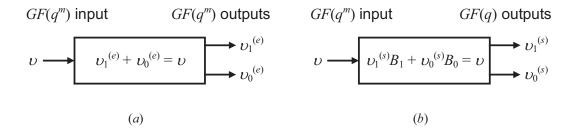

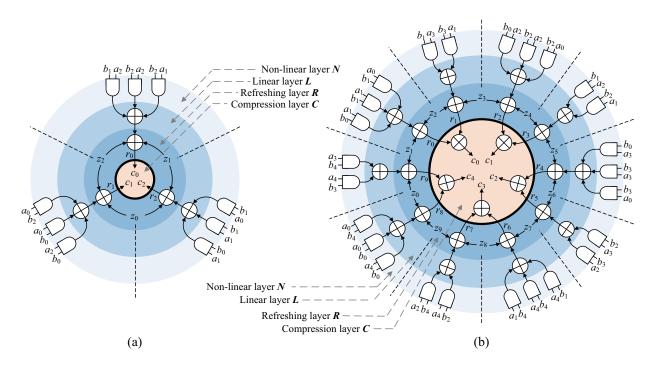

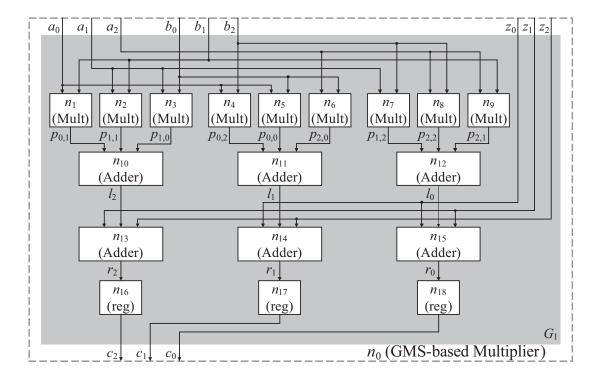

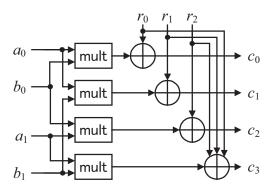

| 4.7  | GMS-based $GF(2^m)$ multipliers in [122]: (a) first- and (b) second-order 11                                                                                | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.8  | GF-ACG for GMS-based GF parallel multiplier: top- and second-levels of ab-                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | stractions                                                                                                                                                  | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

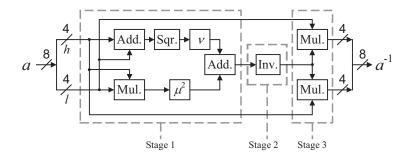

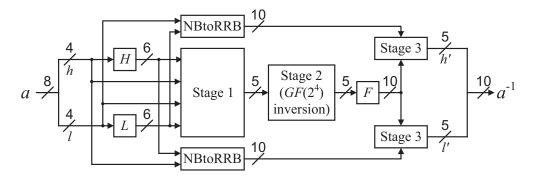

| 5.1  | Inversion circuit over $GF(((2^2)^2)^2)$ in [33] (Same as Fig. 3.16)                                                                                        | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

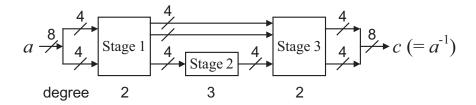

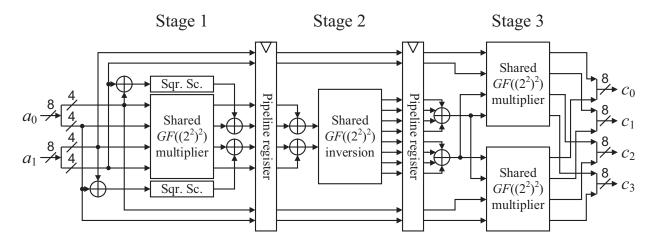

| 5.2  | Proposed inversion circuit                                                                                                                                  | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

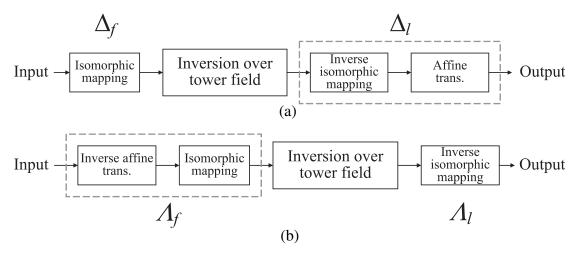

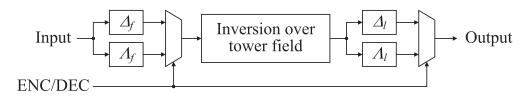

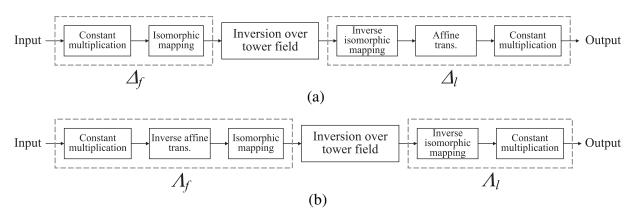

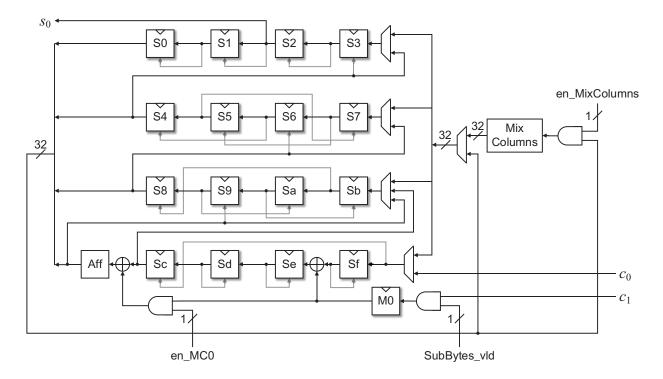

| 5.3  | Overview of AES (a) S-box and (b) inverse S-box based on tower field arithmetic.13                                                                          | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.4  | Typical architecture of unified S-box                                                                                                                       | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.5  | AES (a) S-box and (b) inverse S-box with proposed technique for optimizing                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | linear mappings                                                                                                                                             | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

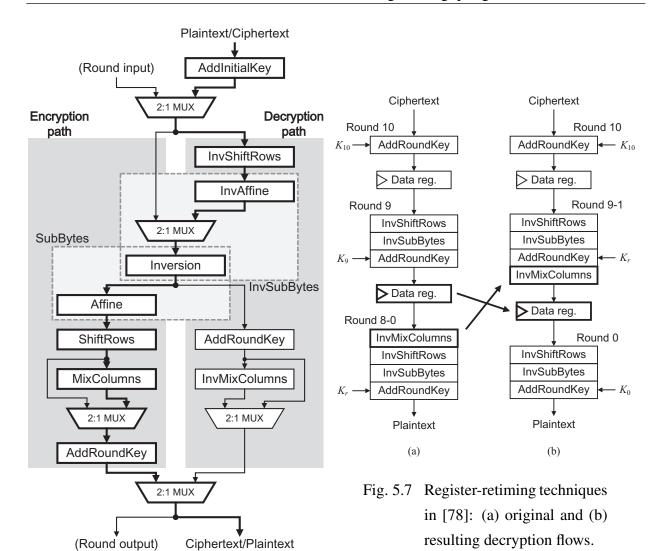

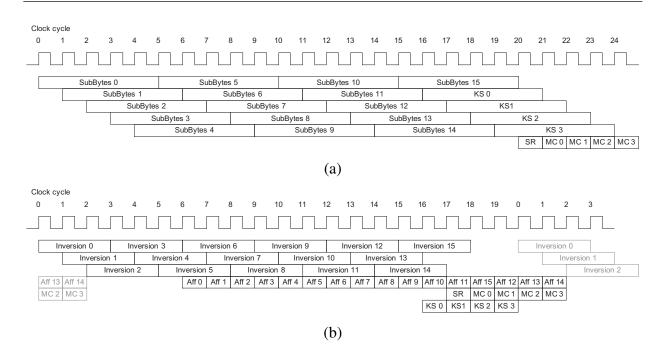

| 5.6  | Conventional parallel datapath in [78]                                                                                                                      | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.7  | Register-retiming techniques in [78]: (a) original and (b) resulting decryption                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | flows                                                                                                                                                       | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

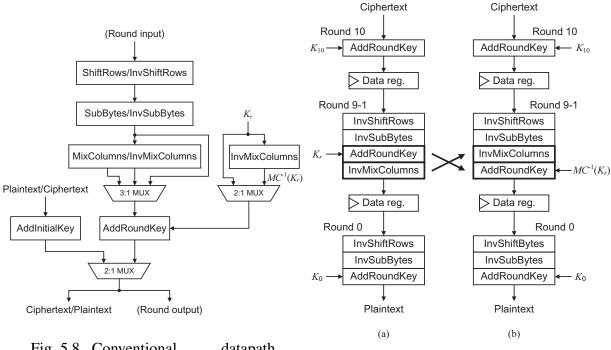

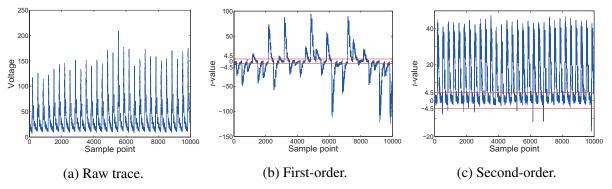

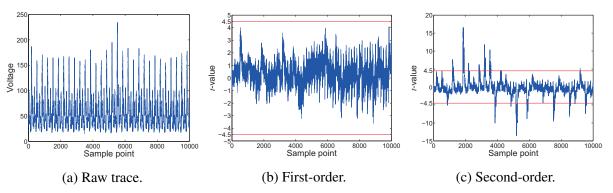

| 5.8  | Conventional datapath in [127], where encryption and decryption paths are com-                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |