## Mechanical Properties and Reliability of Lead-Fee Solder Joints with Various Surface Finishes

| 著者     | Kim Kyoung-Ho                        |

|--------|--------------------------------------|

| 学位授与機関 | Tohoku University                    |

| 学位授与番号 | 11301甲第17587号                        |

| URL    | http://hdl.handle.net/10097/00121581 |

## 博士學位論文

Mechanical Properties and Reliability of Lead-free Solder Joints with Various Surface Finishes

2016年

金 勁鎬

#### **Doctoral Dissertation**

## submitted in partial fulfillment of the requirements for the degree of

#### **DOCTOR of ENGINEERING**

in the Department of Materials Processing,

Graduate School of Engineering,

#### TOHOKU UNIVERSITY

#### Kyoung-Ho Kim

Thesis Committee: Professor Junichi Koike, Chair

Professor Hiroyuki Kokawa

Professor Akira Kawasaki

Professor Akihiko Chiba

Associate Professor Yuji Sutou

Associate Professor Yutaka S. Sato

## **CONTENTS**

| Cl | hapter 1  | Introduction                                                            | 14  |

|----|-----------|-------------------------------------------------------------------------|-----|

|    | 1.1 Elect | ronic packaging                                                         | 14  |

|    | 1.2 Lead  | l-free solder                                                           | 15  |

|    | 1.3 Surfa | ace finishes                                                            | 16  |

|    | 1.4 Mech  | hanical properties                                                      | 18  |

|    | 1.5 Liter | ature review                                                            | 19  |

|    | 1.5.1     | Electronic packaging                                                    | 19  |

|    | 1.5.2     | Lead-free solder alloy                                                  | 21  |

|    | 1         | .5.2.1. Sn                                                              | 22  |

|    | 1         | .5.2.2. Sn-Ag                                                           | 23  |

|    | 1         | .5.2.3. Sn-Cu                                                           | 23  |

|    | 1         | .5.2.4. Sn-Bi                                                           | 23  |

|    | 1         | .5.2.5. Sn-In                                                           | 24  |

|    | 1         | .5.2.6. Sn-Zn                                                           | 24  |

|    | 1         | .5.2.7. Sn-Ag-Cu                                                        | 24  |

|    | 1         | .5.2.8. Sn-Ag-Bi                                                        | 25  |

|    | 1         | .5.2.9. Sn-Ag-Zn                                                        | 25  |

|    | 1.5.3     | Surface finish types                                                    | 26  |

|    | 1         | .5.3.1. Hot air solder leveling (HASL)                                  | 27  |

|    | 1         | .5.3.2. Organic solderability preservative (OSP)                        | 27  |

|    | 1         | .5.3.3. Electroless Ni immersion Au (ENIG) and electroless Ni electrole | ess |

| Pd immersion Au (ENEPIG)                                                       | 28 |

|--------------------------------------------------------------------------------|----|

| 1.5.3.4. Electroless Ni auto-catalytic Au (ENAG)                               | 29 |

| 1.5.3.5. Immersion Sn and Ag                                                   | 30 |

| 1.5.4 Chemistry of ENIG and ENEPIG surface finishes                            | 30 |

| 1.5.5 Interfacial reactions                                                    | 38 |

| 1.5.5.1. Sn-Ni-based reaction                                                  | 38 |

| 1.5.5.2. Sn-Cu-based reaction                                                  | 40 |

| 1.5.5.3. Sn-Ag-Cu/Ni-based reactions                                           | 41 |

| 1.5.5.4. Sn-Ag-Cu/Cu-based reaction                                            | 42 |

| 1.5.6 Black pad formation during ENIG surface finishing                        | 42 |

| 1.5.6.1. Black pad mechanism                                                   | 43 |

| 1.5.6.2. Factors influencing black pad formation                               | 45 |

| 1.6 Thesis structure                                                           | 48 |

| 1.7 Figures                                                                    | 50 |

| 1.8 References                                                                 | 70 |

| Chapter 2 Effect of Ni-Sn interfacial microstructure on brittle fracture joint |    |

| 2.1 Introduction                                                               | 79 |

| 2.2 Experimental                                                               | 81 |

| 2.2.1 PCB design and surface finish                                            | 81 |

| 2.2.2 Metal turn over (MTO)                                                    | 82 |

| 2.2.3 Soldering process                                                        | 82 |

| 2.2.4 Mechanical properties                                                    | 83 |

| 2.2.4.1. Solder joint strength and brittle fracture                            | 83 |

| 2.2.4.2. Drop shock reliability                                 | 84              |

|-----------------------------------------------------------------|-----------------|

| 2.3 Results and discussion                                      | 85              |

| 2.3.1 HSS strength and brittle fracture behavior                | 85              |

| 2.3.1.1. ENIG surface finish                                    | 85              |

| 2.3.1.2. ENEPIG surface finish                                  | 86              |

| 2.3.1.3. Main effect and interaction                            | 87              |

| 2.3.2. Microstructure and IMC thickness                         | 88              |

| 2.3.2.1. Nanovoids                                              | 90              |

| 2.3.3 Brittle fracture mechanism of ENIG surface finish with    | •               |

| 2.3.4 Dependence of brittle fractures on nanovoid size          | 94              |

| 2.3.5 Drop shock reliability                                    | 94              |

| 2.4 Summary                                                     | 95              |

| 2.5 Figures                                                     | 97              |

| 2.6 Bibliography                                                | 127             |

| Chapter 3 Effect of multiple heat-treatments on Sn-Cu interfaci | al reactions131 |

| 3.1 Introduction                                                | 131             |

| 3.2 Experimental                                                | 133             |

| 3.2.1 PCB design and surface finishes                           | 133             |

| 3.2.2 Wetting force and time                                    | 134             |

| 3.2.3 Soldering and multiple heat treatments                    | 135             |

| 3.2.4 Mechanical properties                                     | 136             |

| 3.3 Results and discussion                                      | 136             |

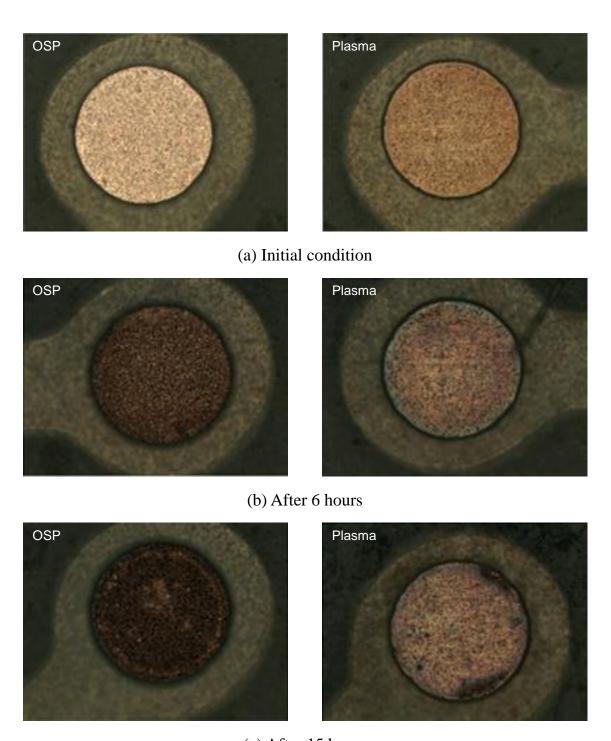

| 3.3.1 Corrosion resistance with multiple heat treatments        | 136             |

|                    | strength and brittle fracture behavior with | •                      |

|--------------------|---------------------------------------------|------------------------|

| 3.3.3 Evalua       | ation of wettability                        | 138                    |

| 3.3.4 Micros       | structural observations                     | 140                    |

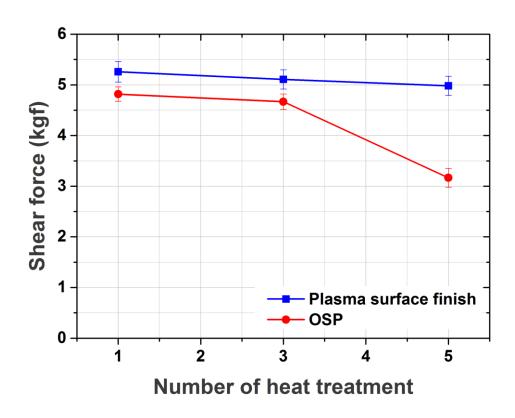

| 3.3.5 Effect       | of multiple heat treatment on shear force   | and soldering area 142 |

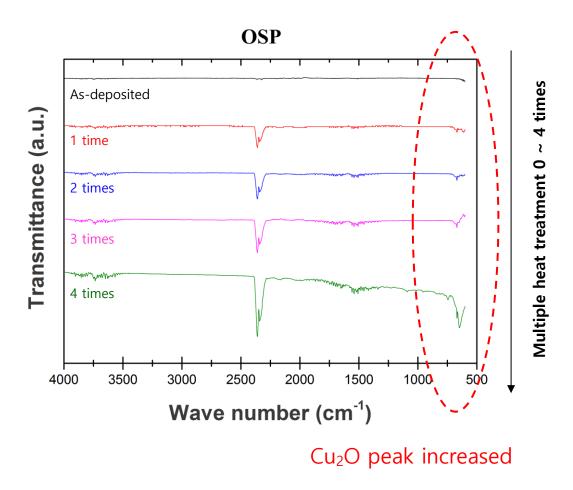

| 3.3.6 Cu ox        | idation resistance of plasma surface finish | 144                    |

| 3.4 Summary        |                                             | 146                    |

| <b>3.5</b> Figures |                                             | 148                    |

| 3.6 References     |                                             | 171                    |

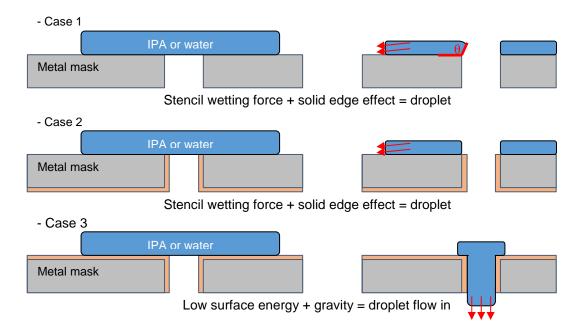

| <del>-</del>       | r printability of a stencil with a hydro    | -                      |

|                    | on                                          |                        |

|                    |                                             |                        |

| _                  | tal procedures                              |                        |

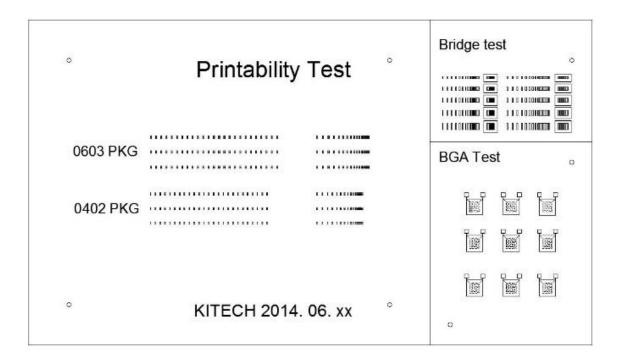

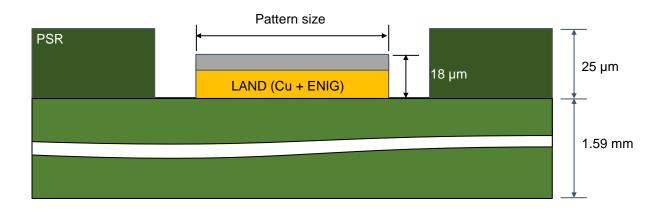

| 4.2.1 PCB d        | lesign and hydrophobic coating              | 177                    |

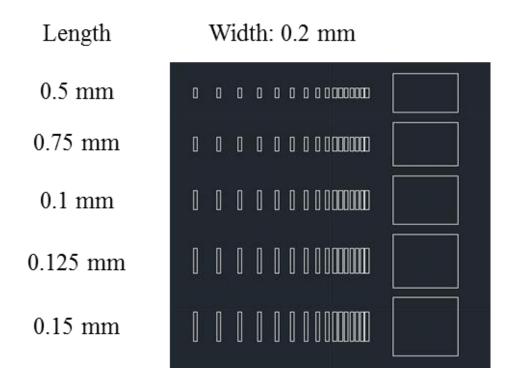

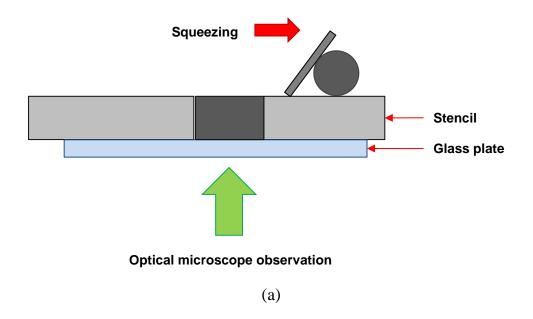

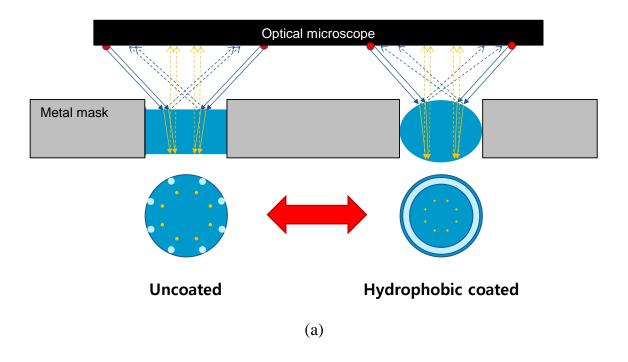

| 4.2.2 Printin      | ng process and solder volume measuremen     | ts178                  |

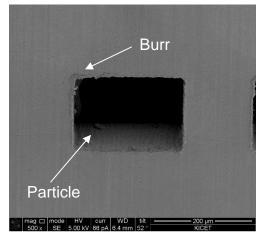

| 4.2.3 Micros       | structural observation of stencil aperture  | 179                    |

| 4. 3 Results and   | d discussion                                | 179                    |

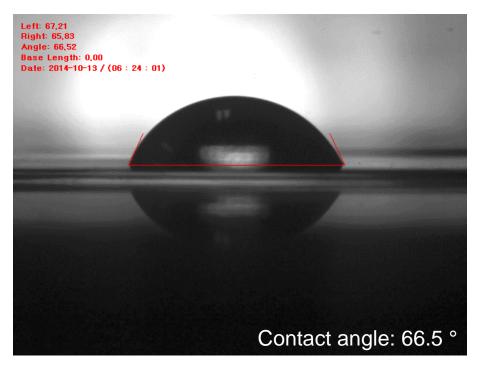

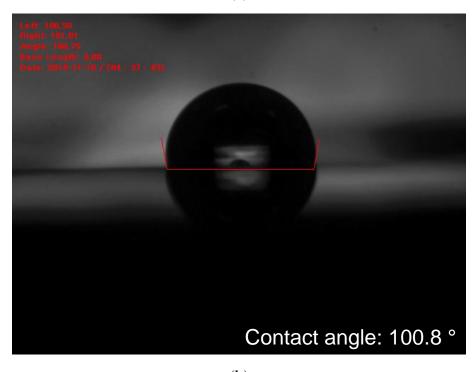

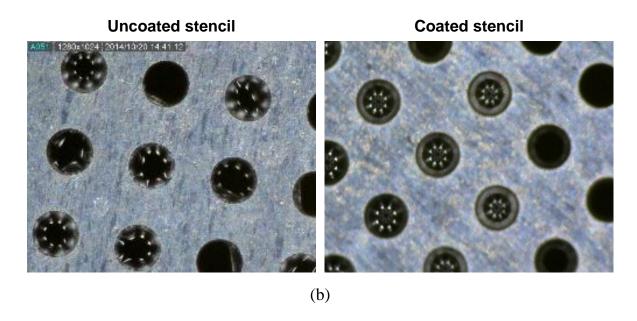

| 4.3.1 Hydro        | phobic coating on stencil                   | 179                    |

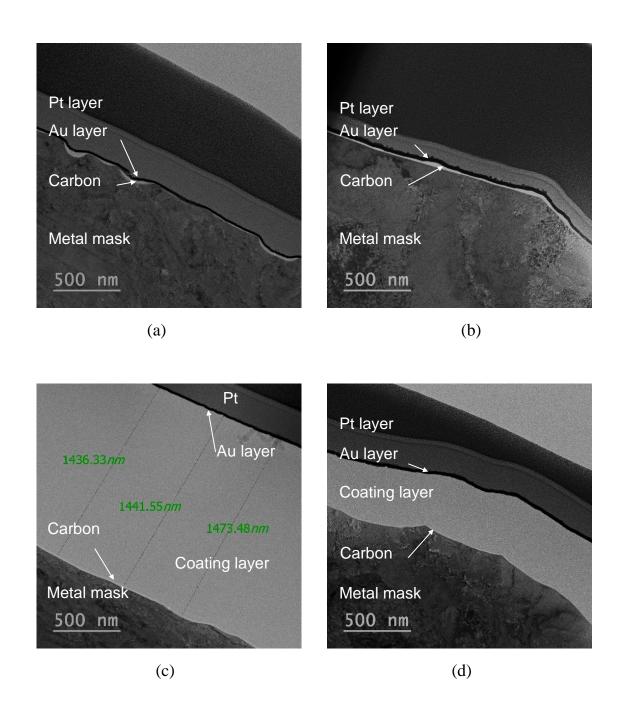

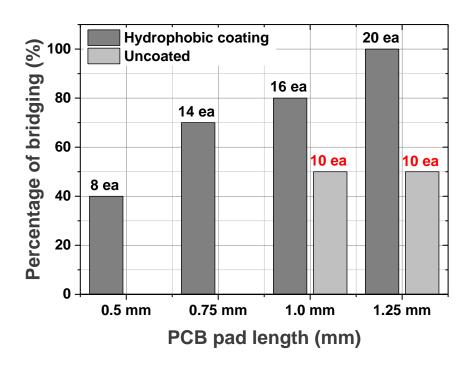

| 4.3.2 Impro        | vement of bridging rate                     | 180                    |

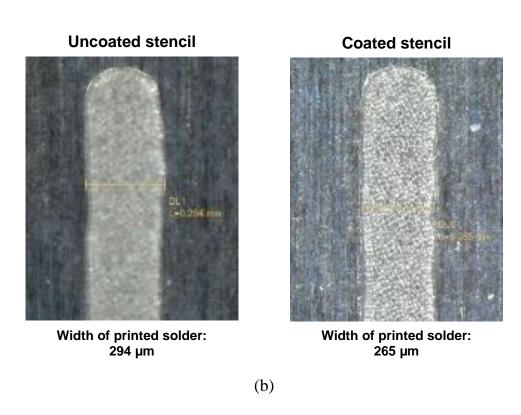

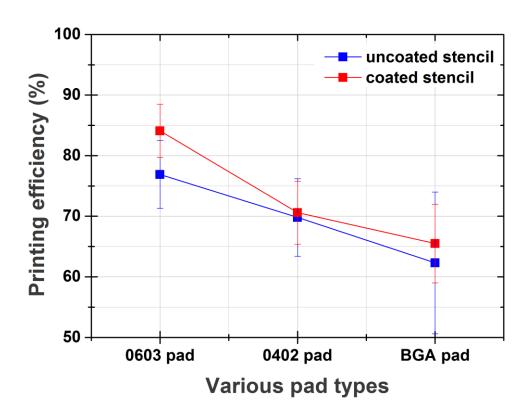

| 4.3.3 Printin      | ng efficiency                               | 181                    |

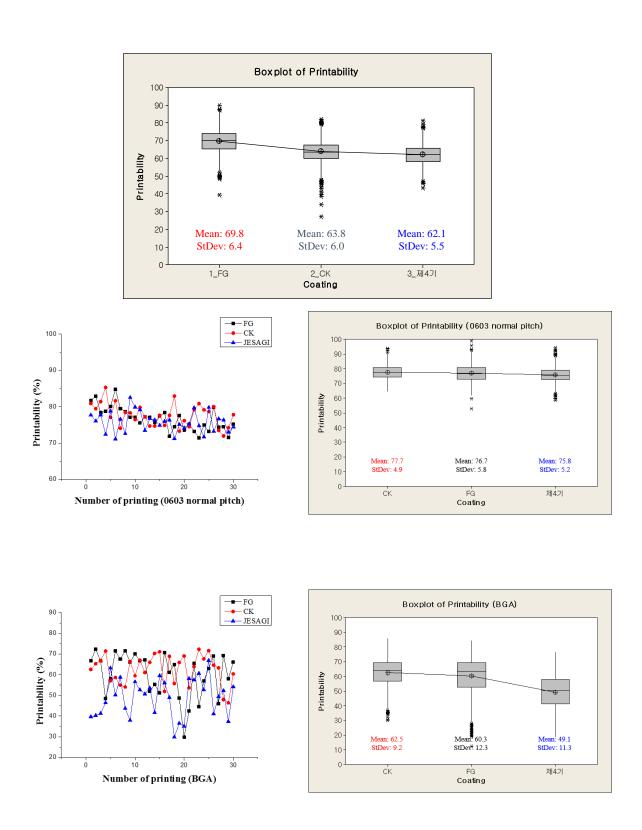

| 4.3.4 Contin       | nuous printing                              | 182                    |

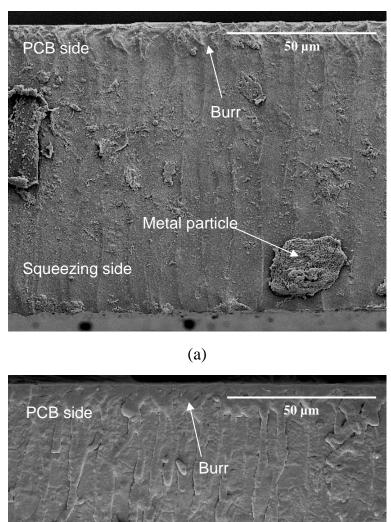

| 4.3.5 Hydro        | phobic stencil                              | 183                    |

| 4.3.6 Lifetir      | ne of the hydrophobic stencil               | 184                    |

| 4.4 Summary        |                                             | 186                    |

| <b>4.5 Figures</b> | 188 |

|--------------------|-----|

|                    |     |

| 4.6 Bibliography   | 205 |

## **List of Tables**

| Chapter 1                                                                                             |

|-------------------------------------------------------------------------------------------------------|

| Table 1.1 Mechanical properties of selected binary alloys [6]51                                       |

| Table 1.2 Comparison of thermal properties of lead-free solder alloys [39]52                          |

| Table 1.3 Properties of different PCB surface finishes53                                              |

| Table 1.4 Ionization trend and standard reduction potential of reactions commonly observed in plating |

| Table 1.5 Typical characteristics of the ENIG surface finish method [50]55                            |

| Table 1.6 Composition of electroless Pd solutions56                                                   |

| Table 1.7 Room temperature properties of intermetallic compounds determined here                      |

| Chapter 2  Table 2.1 Experimental conditions and equations for drop tests103                          |

| Chapter 4                                                                                             |

| Table 4.1 Printing parameters                                                                         |

| Table 4.2 Surface roughness of the aperture wall measured by AFM for uncoated and coated stencils     |

## **List of Figures**

### Chapter 1

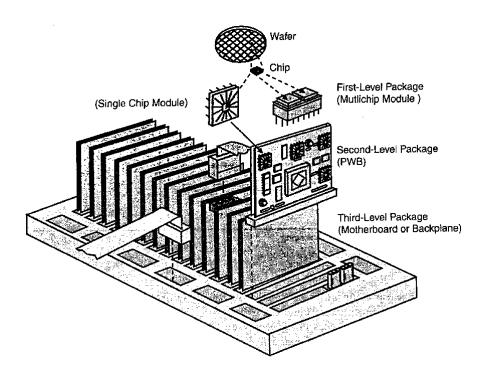

| Figure 1.1 The hierarchy of electronic packaging. Reproduced from Tummala, 2001 [34]                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

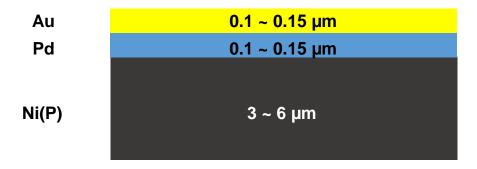

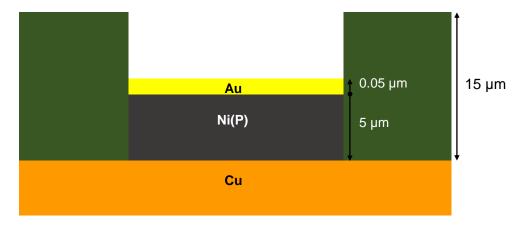

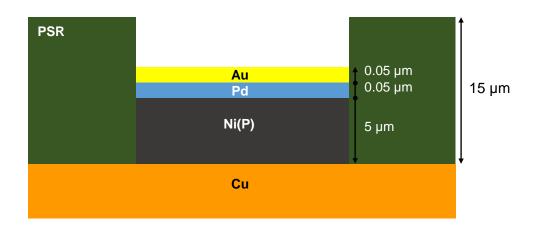

| Figure 1.2 Plating thickness of surface finishes                                                                                                                                                                                                                                                                               |

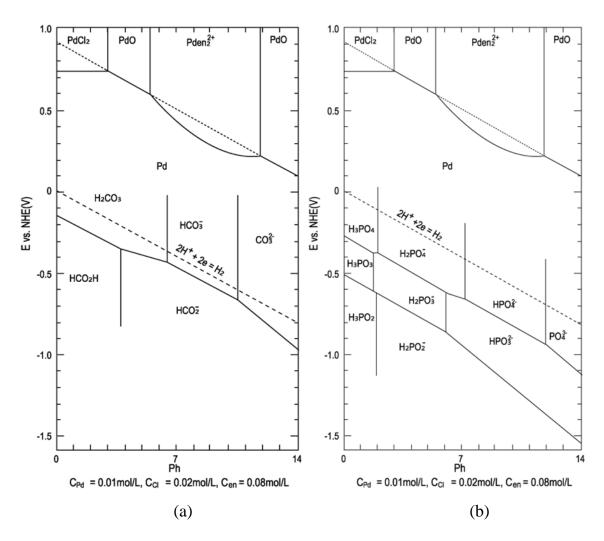

| Figure 1. 3 Potential-pH diagram; (a) HCOO <sup>-</sup> -HCO <sup>3</sup> and (b) H <sub>2</sub> PO <sub>2</sub> <sup>-</sup> , HPO <sub>3</sub> <sup>2</sup> -, and PO <sub>4</sub> <sup>3</sup>                                                                                                                              |

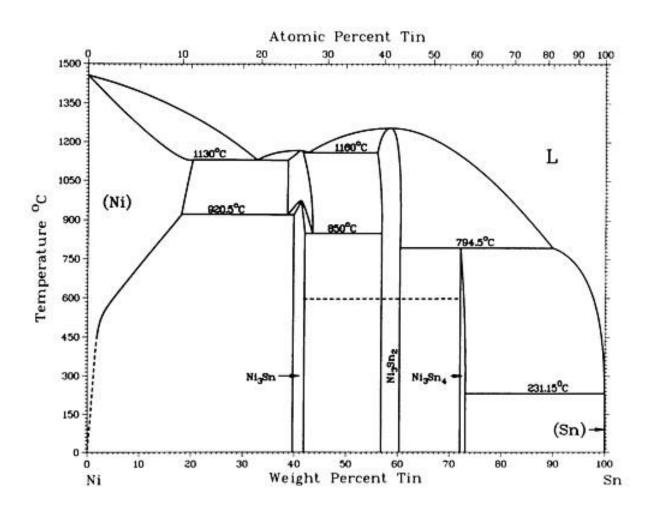

| Figure 1. 4 Sn-Ni binary phase diagram                                                                                                                                                                                                                                                                                         |

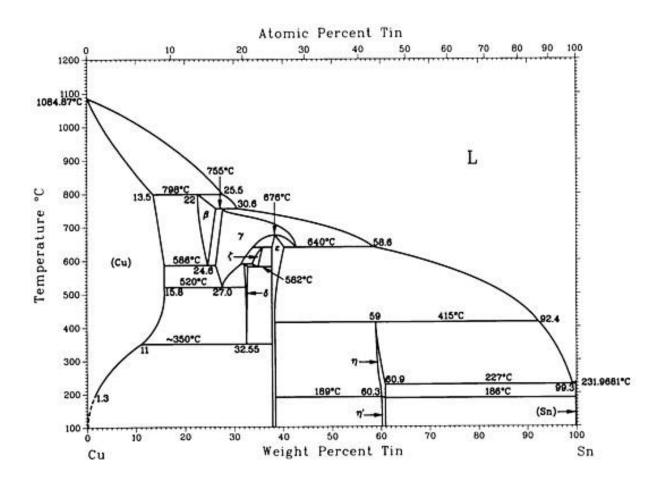

| Figure 1. 5 Sn-Cu binary phase diagram                                                                                                                                                                                                                                                                                         |

| Figure 1.6 Schematic diagrams showing black pad formation mechanisms; (a) voltage induced black pad formation, and (b) micro-galvanic cell formation at sharp nodule boundaries [31]                                                                                                                                           |

| Figure 1.7 Schematic diagram showing the size-effect induced concentration cell formation [32]                                                                                                                                                                                                                                 |

| Figure 1.8 Schematic diagrams showing corrosion induced by secondary-phase precipitation during Ni(P) film growth [58]63                                                                                                                                                                                                       |

| Figure 1.9 Simulated Au layer growth modes at (a) high reactivity and (b) low reactivity. The values shown on both the x and y axes are of arbitrary dimensionless form, where only the relative geometric ratio is important. Cross-sectional SEM images (20k×) of the corresponding Ni-P/Au interfaces are also shown. [59]. |

| Figure 1.10 TEM image showing micro-galvanic corrosion induced by concentration gradients in P across Ni(P) nodules [60]                                                                                                                                                                                                       |

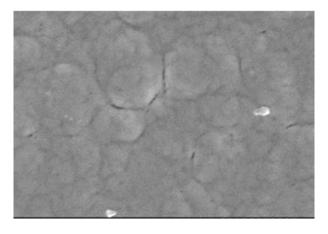

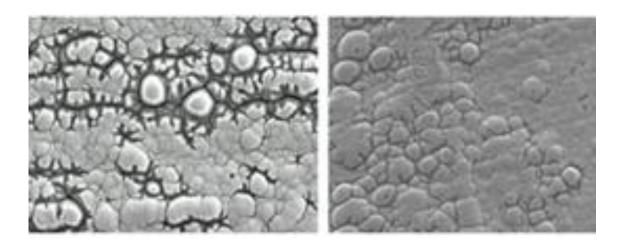

| Figure 1.11 Changes in the surface morphology of Ni(P) as a function of P concentration                                                                                                                                                                                                                                        |

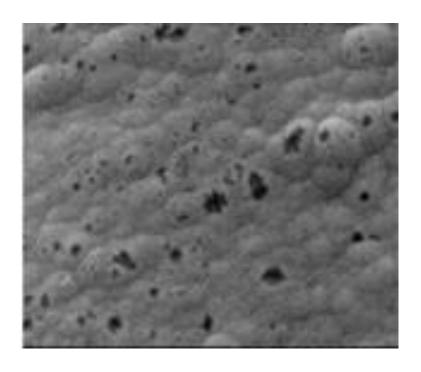

| Figure 1.12 SEM micrographs showing contamination induced by Ni(P) oxidation                                                                                                                                                                                                                                                   |

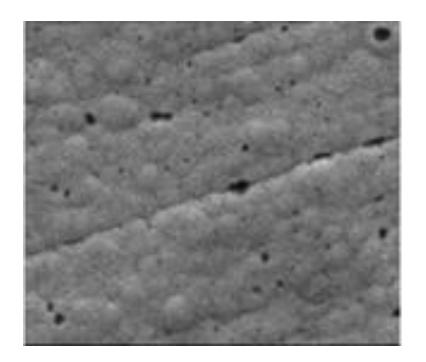

| Figure 1.13 TEM images showing corrosion of the Ni(P) layer resulting from organic impurities. (a) Surface morphology and (b) cross-sectional image |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.14 Changes in the Cu substrate morphology as a result of organic impurities                                                                |

| napter 2                                                                                                                                            |

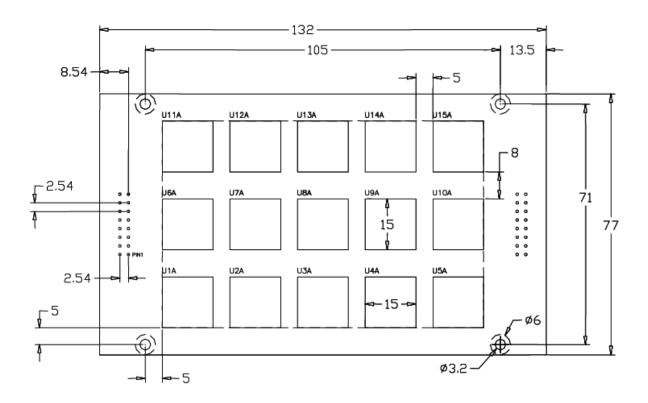

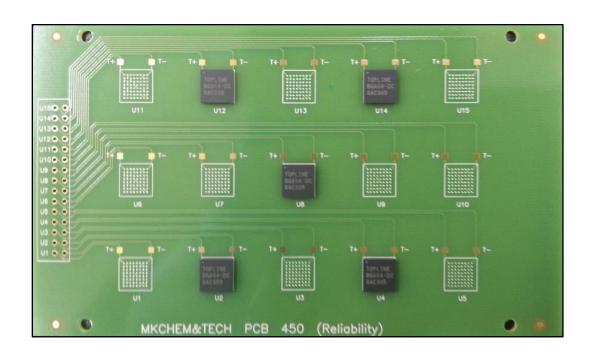

| Figure 2.1 Photograph of the PCB tested for joint strength measurements97                                                                           |

| Figure 2.2 Schematic images of the test substrates. (a) ENIG surface finish, and (b) ENEPIG surface finish                                          |

| Figure 2.3 Schematic diagram of the PCB used for the drop shock tests99                                                                             |

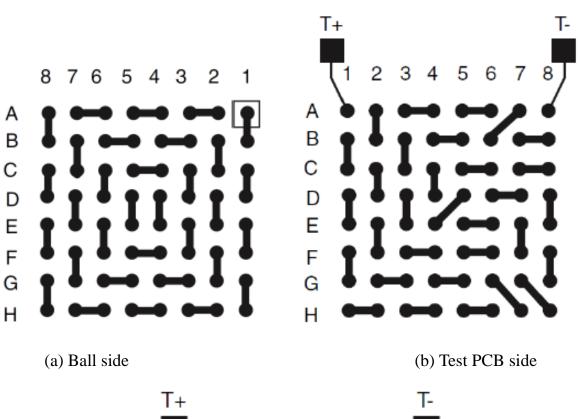

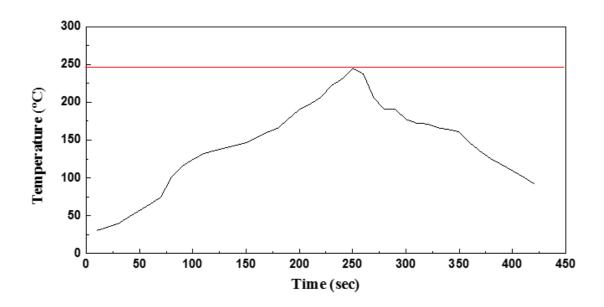

| Figure 2.4 Schematic diagrams of the daisy chains in this study. (a) Ball side (b) test PCB side, and (c) after mounting to the PCB                 |

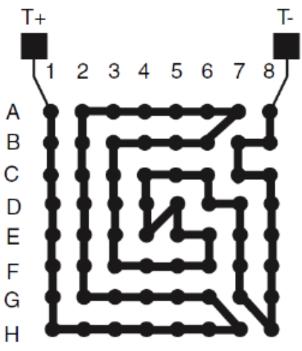

| Figure 2.5 Schematic showing the metal turn over (MTO) of the plating solution                                                                      |

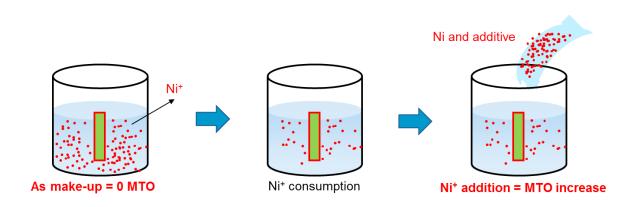

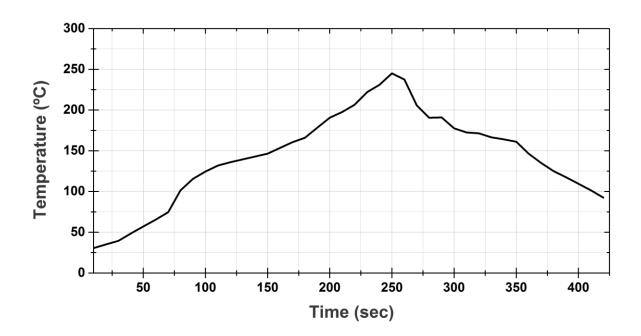

| Figure 2.6 Temperature vs. time reflow profile for the Sn-3.0Ag-0.5Cu solder                                                                        |

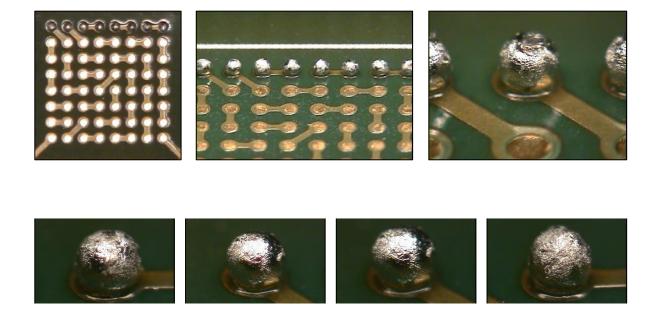

| Figure 2.7 Optical micrographs of the SAC305 solder balls on the surface-finished test PCB                                                          |

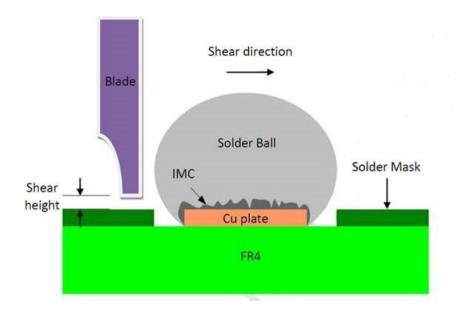

| Figure 2.8 Schematic showing the HSS test setup102                                                                                                  |

| Figure 2.9 Definition of the percentage of brittle fracture ranges                                                                                  |

| Figure 2.10 Photograph showing the BGA mounting configuration on the test PCB                                                                       |

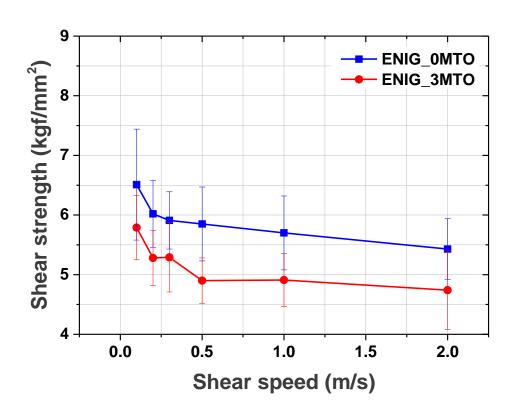

| Figure 2.11 High-speed shear strength as a function of shear speed for SAC/ENIG samples with different bath lives of Ni(P)                          |

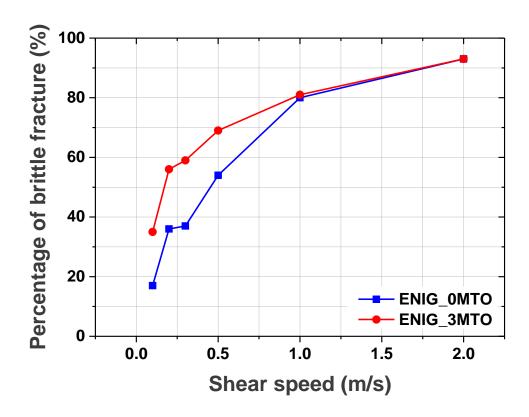

| Figure 2.12 Percentage of brittle fracture rate as a function of shear speed for the SAC/ENIG samples with different bath lives of Ni(P)106         |

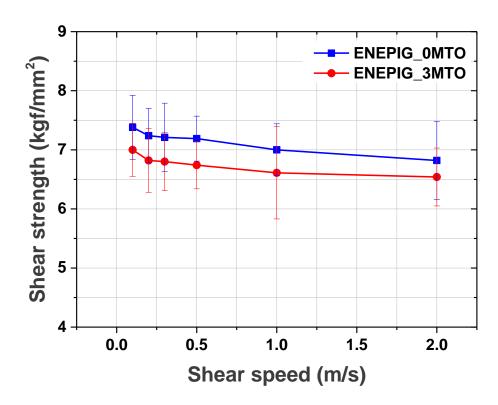

| Figure 2.13 High-speed shear strength as a function of shear speed fo SAC/ENEPIG samples with different bath lives of Ni(P)           |

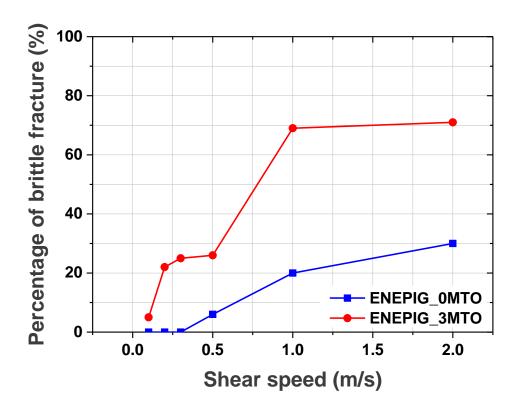

|---------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.14 Percentage of brittle fracture as a function of shear speed for the SAC/ENEPIG samples with different bath lives of Ni(P) |

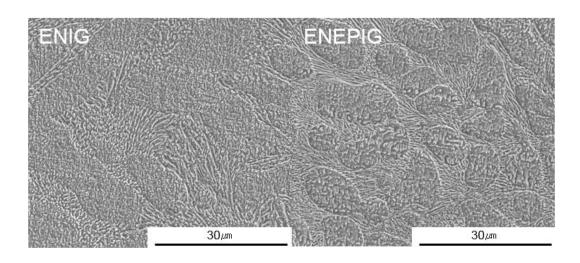

| Figure 2.15 SEM images showing the microstructure of bulk solder for the ENIG and ENEPIG samples                                      |

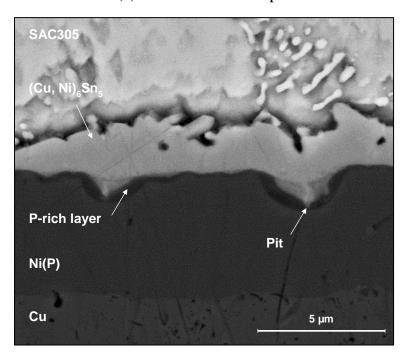

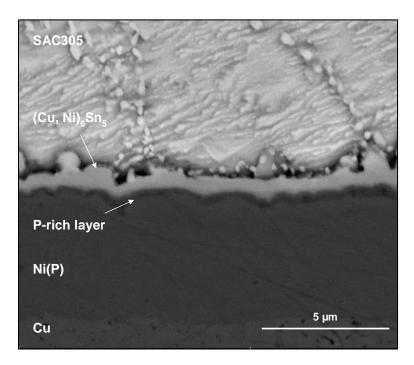

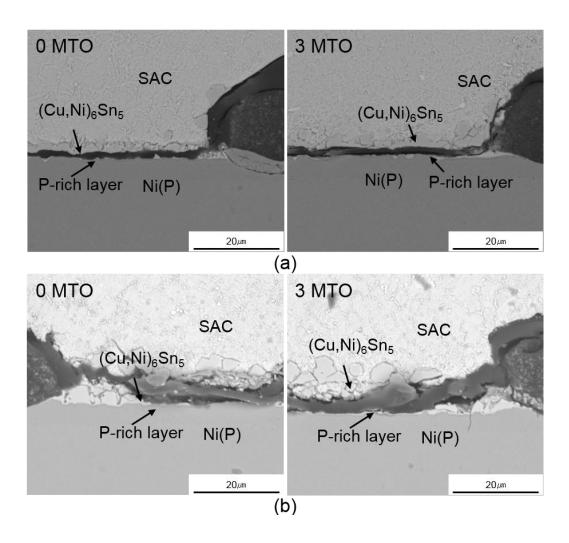

| Figure 2.16 Cross-sectional SEM micrographs of the SAC/ENIG for a bath life of (a) 0 MTO and (b) 3 MTO                                |

| Figure 2.17 Cross-sectional SEM micrographs of the SAC/ENIG for a bath life of (a) 0 MTO and (b) 3 MTO                                |

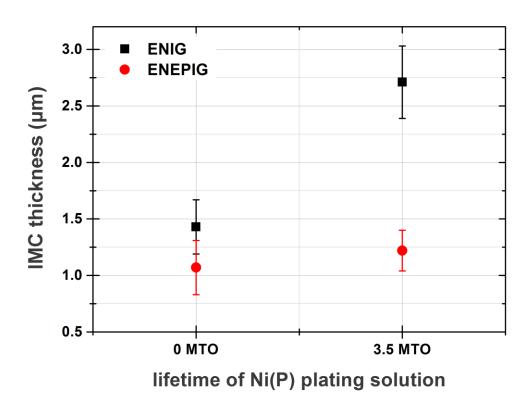

| Figure 2.18 Comparison of IMC thickness for ENIG and ENEPIG sample with different plating solution lifetimes                          |

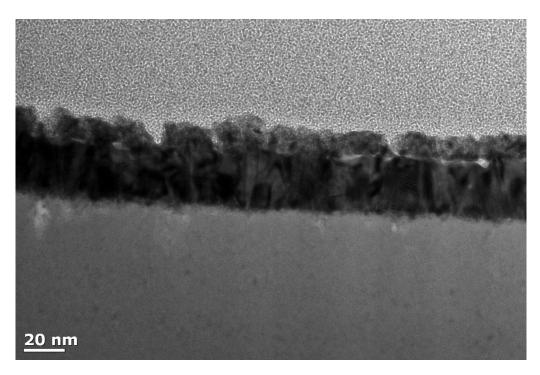

| Figure 2.19 Cross-sectional TEM micrographs of as-deposited ENIG samples (a) 0 MTO and (b) 3 MTO                                      |

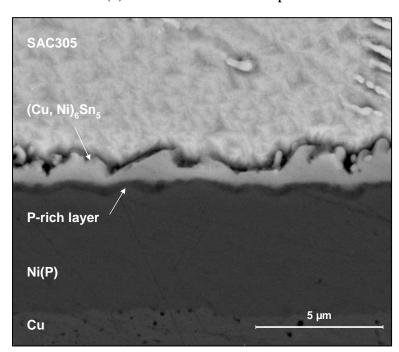

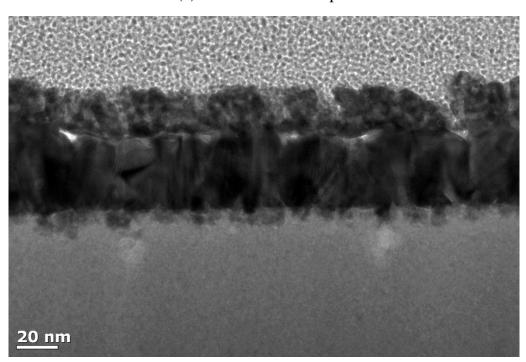

| Figure 2.20 Cross-sectional TEM micrographs of as-deposited ENEPIC samples. (a) 0 MTO and (b) 3 MTO                                   |

| Figure 2.21 Cross-sectional TEM micrographs of SAC/ENIG samples. (a) 0 MTO and (b) 3 MTO                                              |

| Figure 2.22 Cross-sectional TEM micrographs of SAC/ENEPIG samples. (a) 0 MTO and (b) 3 MTO                                            |

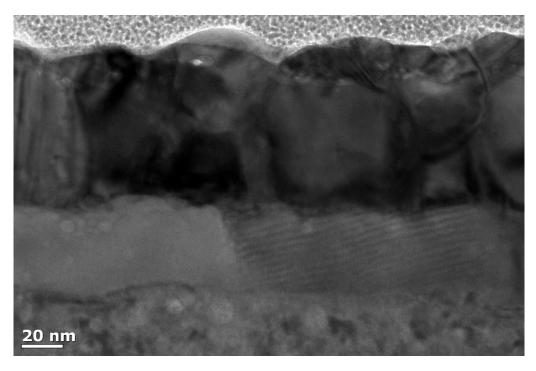

| Figure 2.23 Cross-sectional TEM micrographs of SAC/ENIG after therma aging at 150 °C for 100 h. (a) 0 MTO and (b) 3 MTO               |

| Figure 2.24 Cross-sectional TEM micrographs of SAC/ENEPIG after therma aging at 150 °C for 100 h. (a) 0 MTO and (b) 3 MTO             |

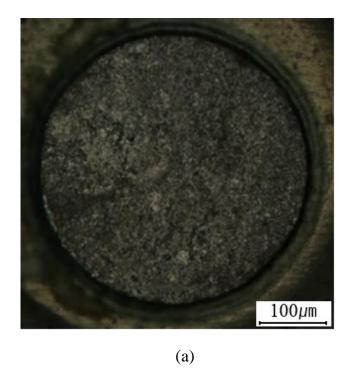

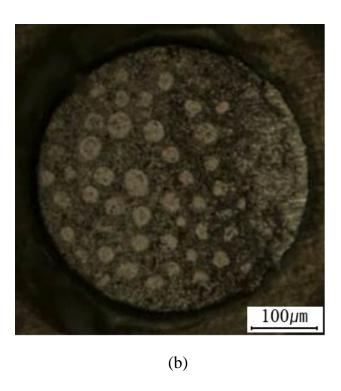

| Figure 2.25 Optical micrographs of the fracture surfaces after HSS testing fo (a) 0 MTO and (b) 3 MTO samples                         |

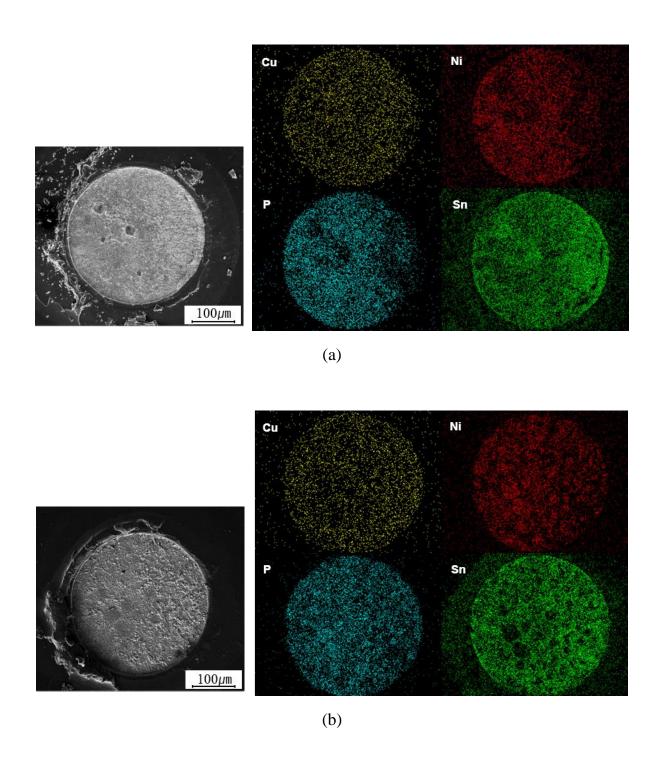

| Figure 2.26 SEM images and EDS maps of the fracture surfaces after HSS testing for (a) 0 MTO and (b) 3 MTO samples                    |

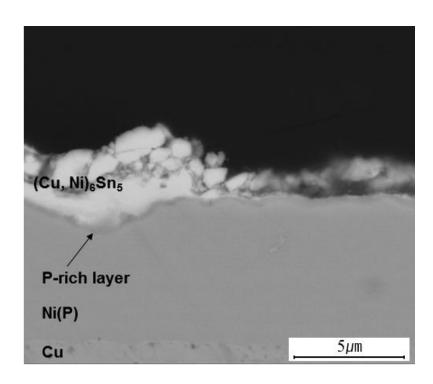

| Figure 2.27 Cross-sectional SEM image of a representative section of the fracture surface (away from the circular features)                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

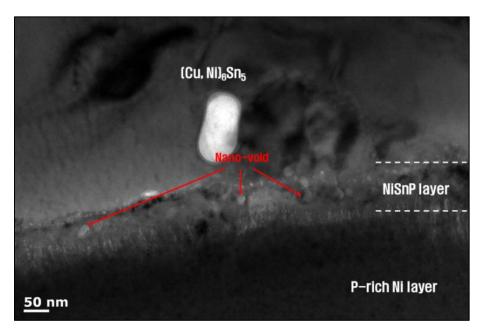

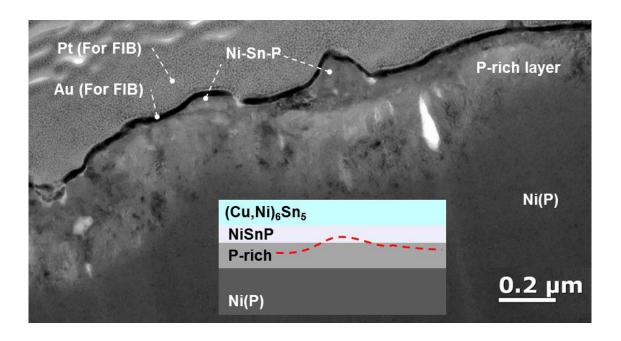

| Figure 2.28 Cross-sectional TEM micrograph of a circular feature on the fracture surface shown in Fig. 6                                                     |

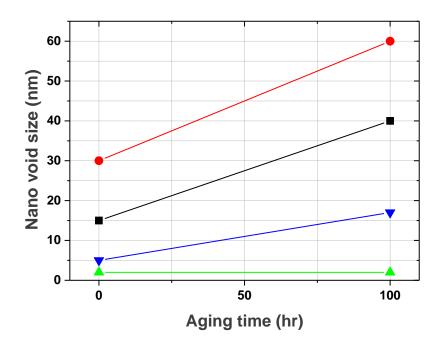

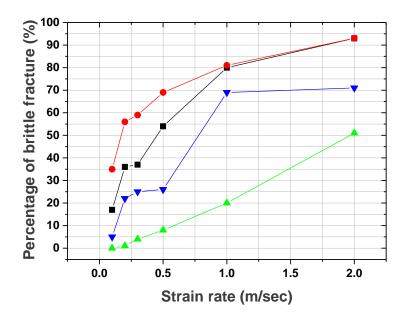

| Figure 2.29 (a) Nanovoid size as a function of thermal aging time. (by Percentage of brittle fracture with increasing strain rate                            |

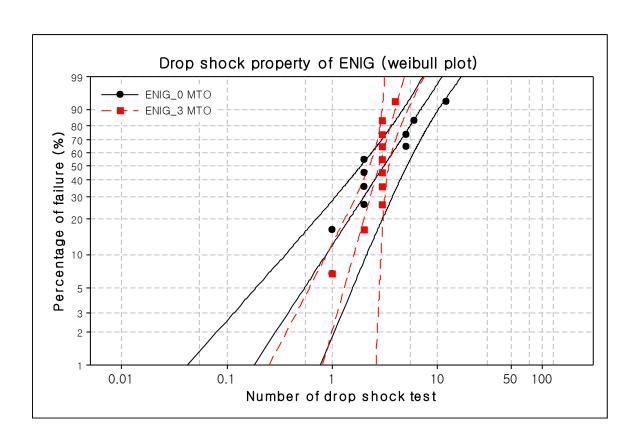

| Figure 2.30 Results of drop shock tests of ENIG samples                                                                                                      |

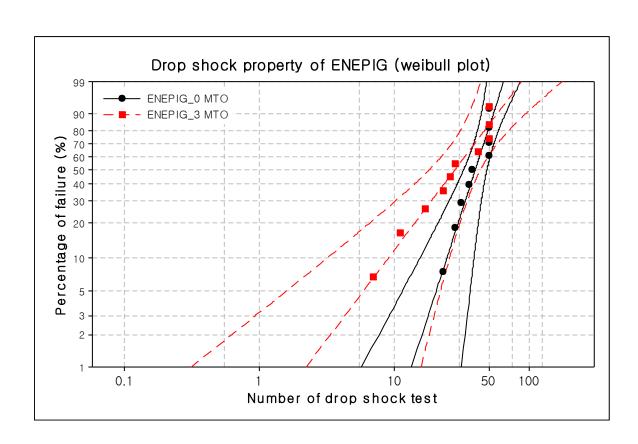

| Figure 2.31 Results of drop shock tests of ENEPIG samples                                                                                                    |

| Figure 2.32 Cross-sectional SEM images of the fractures generated after dro shock tests of (a) ENIG and (b) ENEPIG samples under 0 MTO and MTO conditions.   |

| Chapter 3                                                                                                                                                    |

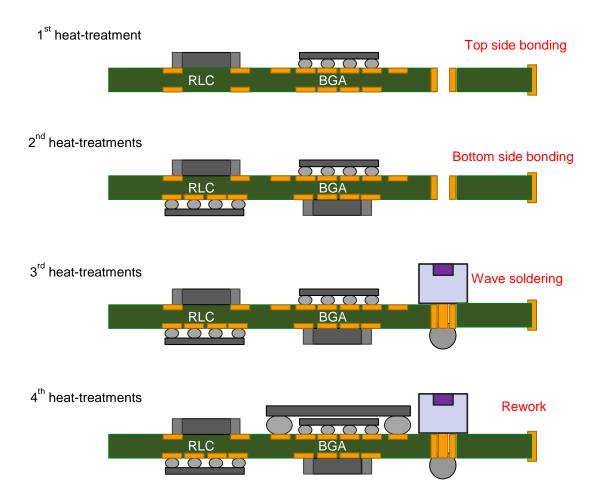

| Figure 3.1 Schematics showing the multiple heat treatment process14                                                                                          |

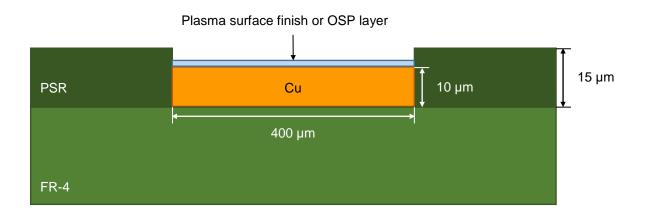

| Figure 3.2 Schematic illustration of the test samples used in this study showing the FR-4 PCB, photo solder resist (PSR), Cu pads, and surfact finish layers |

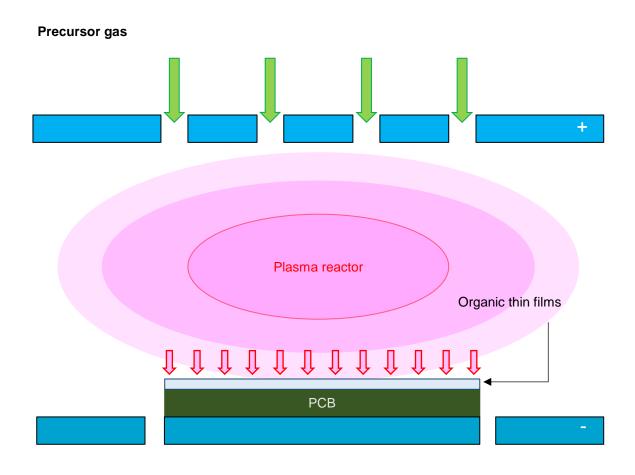

| Figure 3. 3 Schematic of the plasma surface finish process                                                                                                   |

| Figure 3.4 Temperature vs. time reflow profile for the Sn-3.0Ag-0.5Cu solde                                                                                  |

| Figure 3.5 Optical microscopy images of the Cu pad after salt spray test for OSP and plasma samples, after (a) 0, (b) 6, and (c) 15 h                        |

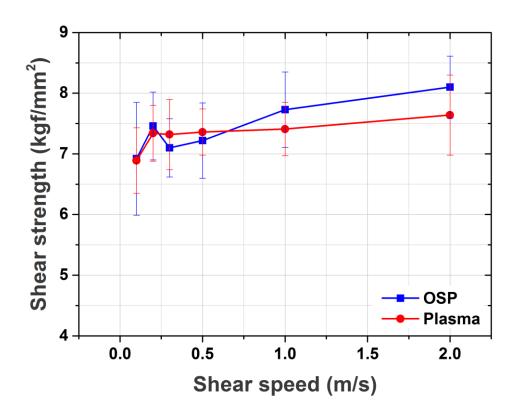

| Figure 3.6 Shear strength as a function of shear speed for OSP- and plasma finished samples after a single heat treatment                                    |

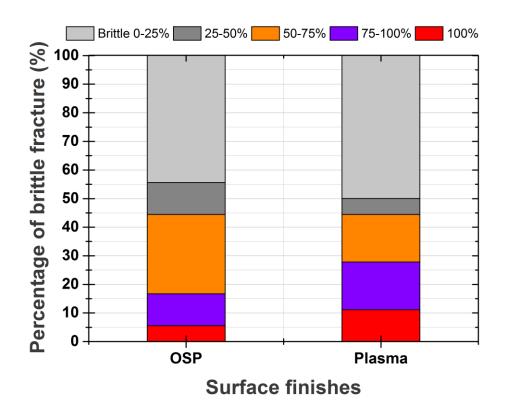

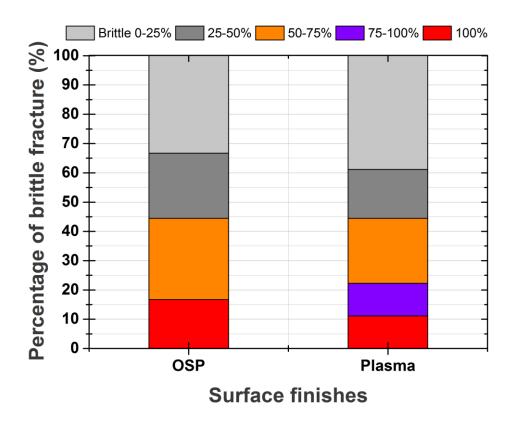

| Figure 3. 7 Brittle fracture rate of OSP- and plasma-finished sample after single reflow                                                                     |

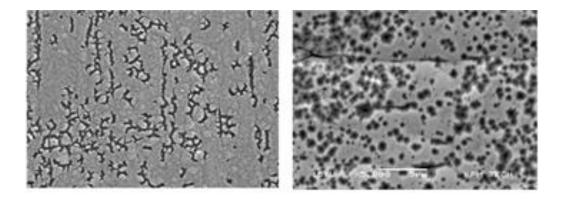

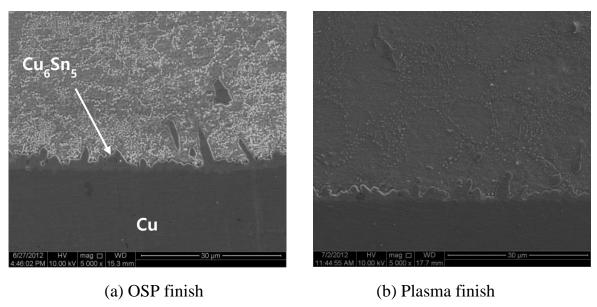

| Figure 3.8 SEM micrographs comparing the morphology of the IMC layers of the (a) OSP- and (b) plasma-finished samples after a single heat treatment          |

| Figure 3.9 Comparison of high-speed shear strengths of OSP- and plasma-finished samples as a function of shear speed after five heat treatment cycles                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.10 Percentage of brittle fracture of OSP- and plasma-finished sample after five reflow cycles                                                                                                       |

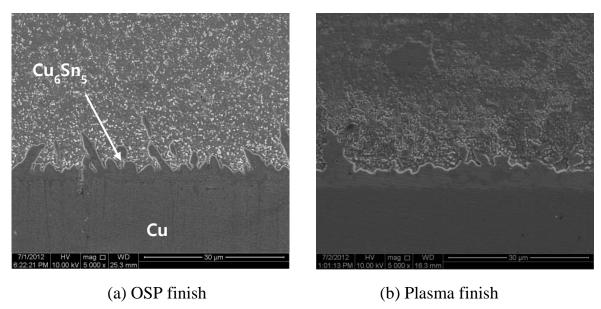

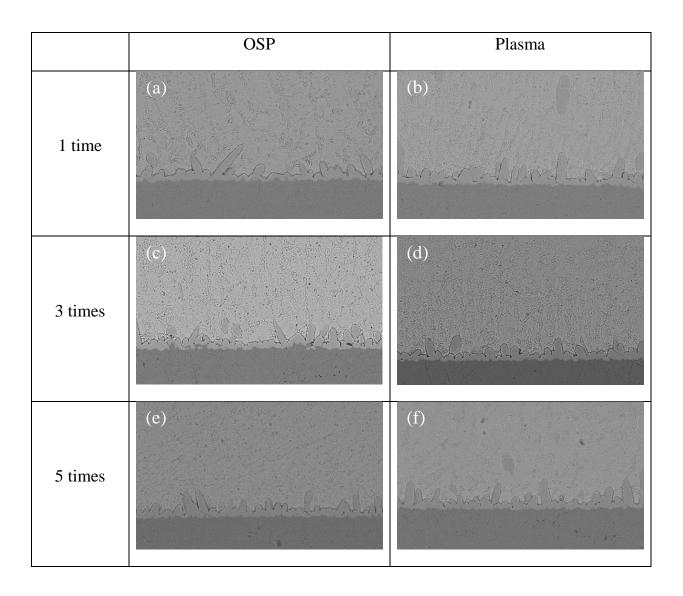

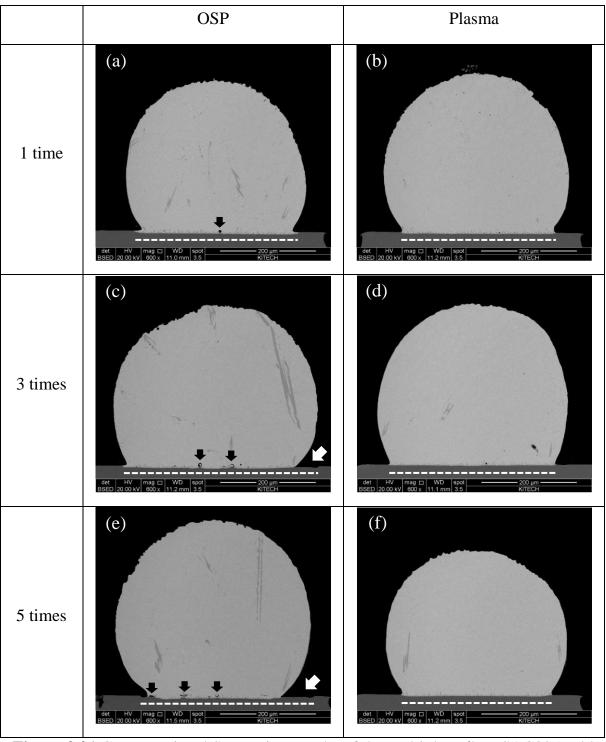

| Figure 3.11 Cross-sectional SEM micrographs comparing the IMC layers of the OSP- and plasma-treated samples after multiple heat treatments 156                                                               |

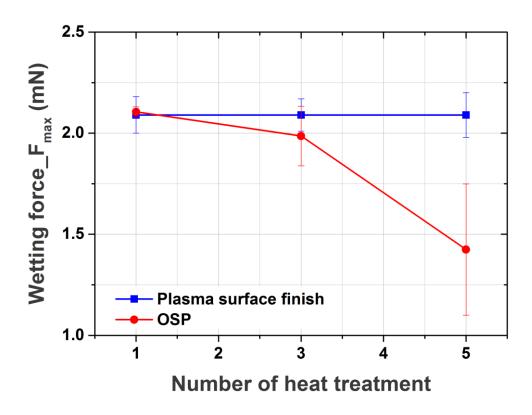

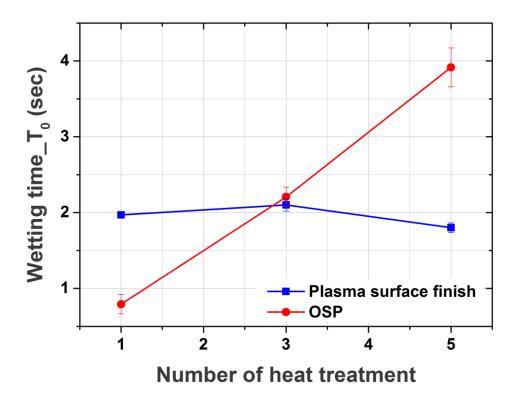

| Figure 3.12 Wetting forces of the plasma and OSP surface finishes as a function of heat treatment cycle                                                                                                      |

| Figure 3.13 Wetting times of the plasma and OSP surface finishes as a function of heat treatment cycle                                                                                                       |

| Figure 3.14 OM images of the test coupons after wetting tests. (a) OSP and (b) plasma surface finishes subjected to 0, 2, or 4 heat treatment cycles before wetting                                          |

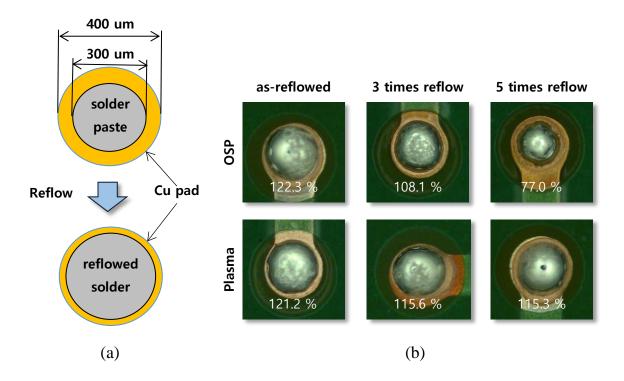

| Figure 3.15 (a) Schematic illustration of the solder spreadability test. (b) OM images of the soldered PCBs after spreading tests for OSP- and plasma-finished samples subjected to multiple heat treatments |

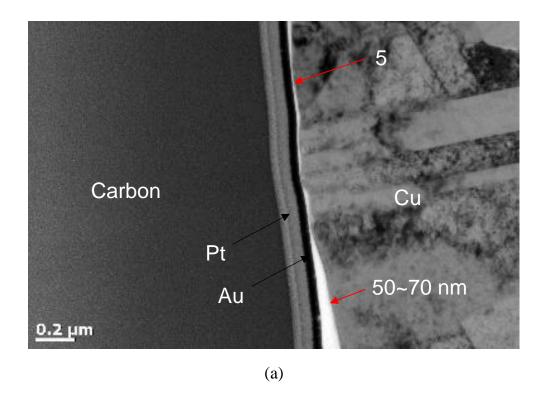

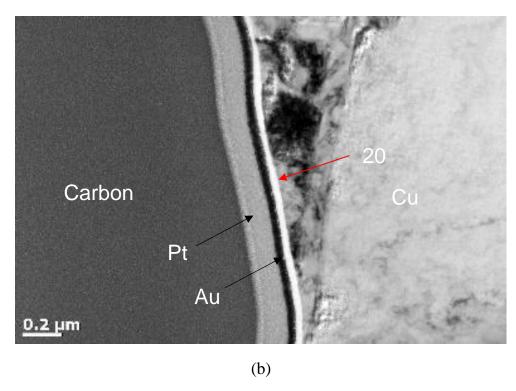

| Figure 3.16 Cross-sectional TEM micrographs of the (a) OSP and (b) plasma surface finished Cu substrates, where the surface finish layers are the white films                                                |

| Figure 3.17 Cross-sectional TEM images of the (a) OSP and (b) plasma surface finished samples after soldering showing the formation of IMC grains162                                                         |

| Figure 3.18 Cross-sectional SEM micrographs of the SAC305 solder joints with different surface finishes after multiple reflows                                                                               |

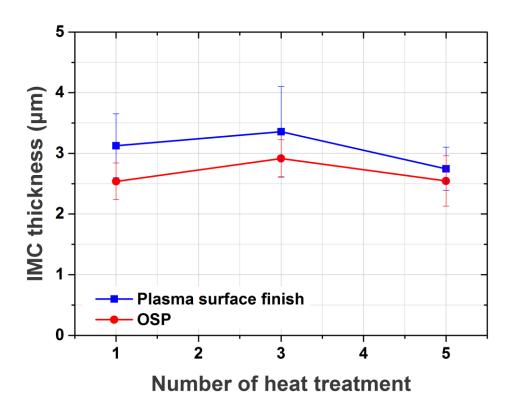

| Figure 3.19 Average thicknesses of the IMC layers within the SAC305 solder joints for the OSP and plasma surface finishes as a function of reflow heat treatments                                            |

| Figure 3.20 Average shear force of the SAC305 solder joints with different                                                                                                                                   |

| surface finishes after multiple reflows16                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.21 Cross-sectional SEM micrographs of the multiple-reflow SAC30 solder joints with different surface finishes. The white dashed lines indicate the Cu pad, the white arrows indicate the unreacted area of the Cu pad, and the black arrows indicate voids developed at the interfaces |

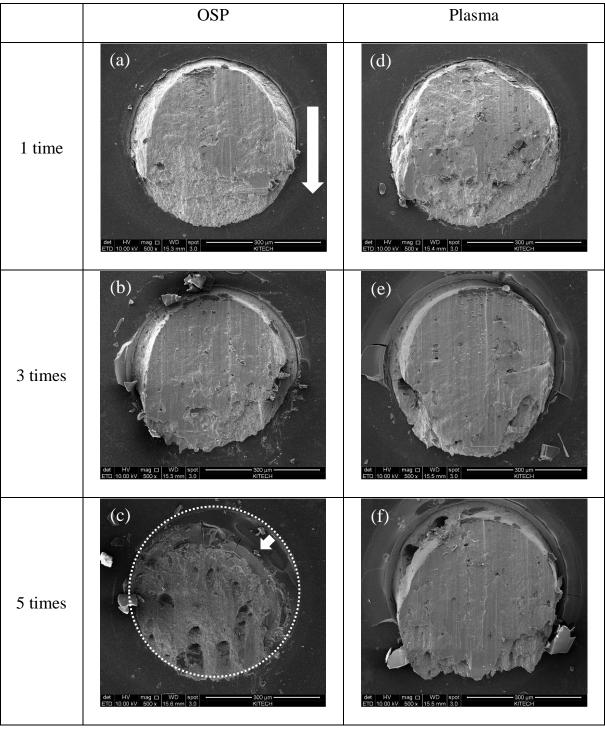

| Figure 3.22 SEM micrographs of the fracture surfaces of the solder joints after shear testing. The white dashed circle indicates the area of the Cu pad, the white arrows indicate the unreacted area with the Cu pad, and the black arrow indicates the direction of shear.                    |

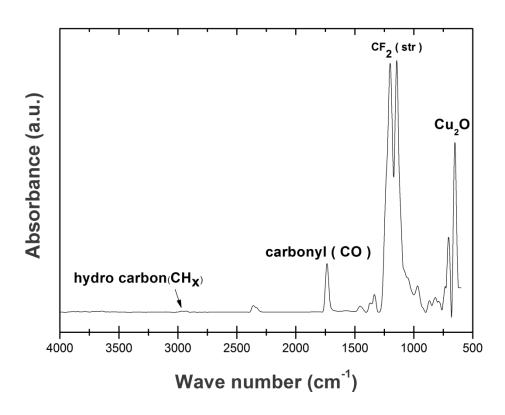

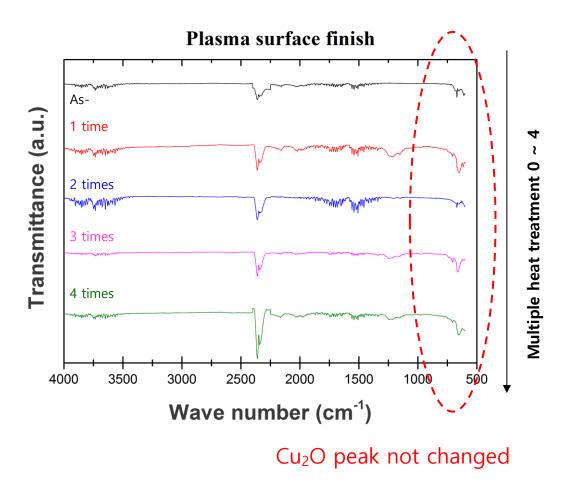

| Figure 3.23 FITR analysis of the plasma surface finish layer                                                                                                                                                                                                                                    |

| Figure 3.24 FTIR analysis of the Cu <sub>2</sub> O peaks for the OSP-finished sample after multiple heat treatments                                                                                                                                                                             |

| Figure 3.25 FTIR analysis of the Cu <sub>2</sub> O peaks for the plasma surface finish after multiple heat treatments                                                                                                                                                                           |

| Chapter 4                                                                                                                                                                                                                                                                                       |

| Figure 4.1 Schematic showing the design of the test PCB for the solde printability, bridging, and BGA tests                                                                                                                                                                                     |

| Figure 4.2 Schematic showing the design of the PCB pads for the solde bridging test                                                                                                                                                                                                             |

| Figure 4.3 Schematic of the cross-section of the test PCB                                                                                                                                                                                                                                       |

| Figure 4.4 Water droplet test images of the (a) uncoated and (b) coated stencils showing the contact angles.                                                                                                                                                                                    |

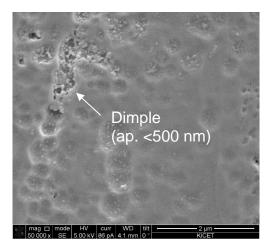

| Figure 4.5 Cross-sectional TEM micrographs of the SUS304 laser-cut stencil (a) uncoated stencil surface, (b) uncoated stencil aperture wall, (c) coate stencil surface, and (d) coated stencil aperture wall                                                                                    |

| Figure 4.6 Optical micrograph of the solder bridging test sample19                                                                                                                                                                                                                              |

| Figure 4.7 Percentage of bridged pads as a function of pad length for uncoate and coated stencils.                                                                                                                                                                                              |

| 12                                                                                                                                                                                                                                                                                              |

| Figure 4.8 (a) Schematic showing observation of solder paste printing through the glass plate. (b) Micrographs of the printed solder paste observed through the glass plate for uncoated and coated stencils       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

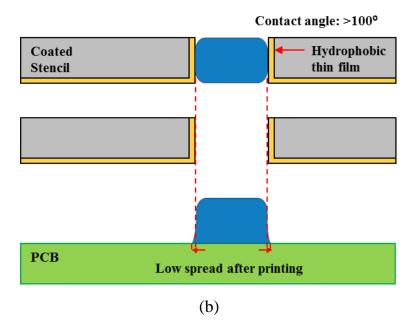

| Figure 4.9 Schematics showing the solder printing process through (a) an uncoated stencil and (b) a coated stencil                                                                                                 |

| Figure 4.10 Printing efficiency for uncoated and coated stencils as a function of pad type                                                                                                                         |

| Figure 4.11 Results of continuous printing with various pad types198                                                                                                                                               |

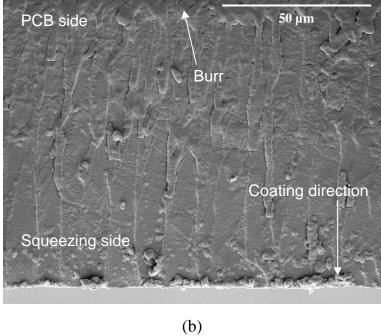

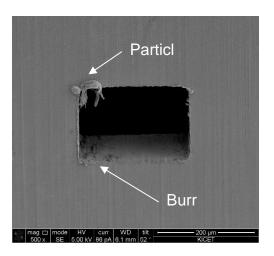

| Figure 4.12 SEM micrographs of the microstructure of the side walls of the aperture for (a) uncoated and (b) coated stencils                                                                                       |

| Figure 4.13 SEM micrograph showing solder paste adhering to the squeezing side of the aperture                                                                                                                     |

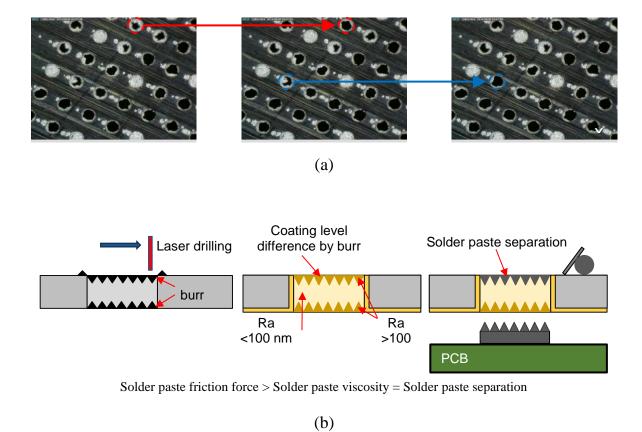

| Figure 4.14 (a) SEM micrographs of (b) Schematic of solder paste separation                                                                                                                                        |

| Figure 4.15 SEM micrographs of the surface and aperture of (a) uncoated and (b) coated SUS stencils.                                                                                                               |

| Figure 4.16 (a) Schematic of the method for verifying the quality of the hydrophobic coating using an LED lamp. (b) SEM micrographs showing the different optical patterns for the uncoated and coated stencils203 |

| Figure 4.17 Schematic diagram showing the method for verifying the quality of the hydrophobic coating based on the solid edge effect204                                                                            |

#### Chapter 1

#### Introduction

#### 1.1 Electronic packaging

Since the invention of the transistor in 1947, electronic packaging technology has had a great influence on modern society. It has grown into a large industry with a market of more than one trillion USD with very rapid growth and development compared to other industries. The development of electronic packaging technology followed Moore's law until the 1990s. Recently, it has reached the physical limit of semiconductor integration processes due to the miniaturization of electronic products, such as smartphones. Thus, current semiconductor package technology needs to satisfy miniaturization, and be multifunctional, highly integrated, low cost, and have excellent electrical properties.

Wire bonding and tape automated bonding (TAB) methods have been adapted for chip bonding in conventional semiconductor and electronic packaging fields. However, these methods have been reported to exhibit reliability problems, such as low chip integration, delay in the transmission of electrical signals, and high heat generation rates. To overcome these problems, the flip-chip bonding method has been studied worldwide to increase the number of I/Os and enable high-speed signal processing

using solder bumps [1-2]. The ball grid array (BGA) package, which is mainly used in the flip-chip bonding method, accounts for a significant portion of the market share [3]. Due to the high importance of the BGA package as an interconnection material, many studies have investigated solder joint properties, interfacial reactions with the metal layer, mechanical deformation behavior of solder joints, thermal-mechanical properties, and thermal fatigue properties of the solder [4].

#### 1.2 Lead-free solder

In the early days of electronic packaging development, 63Sn-37Pb and Pb-Sn-based alloys were extensively used as materials for mechanical, thermal, and electrical connections. However, now Pb and its compounds are subjected to environmental regulations (such as the restriction of hazardous substances (RoHS), waste electrical and electronic equipment (WEEE), and end-of-life vehicles (ELV) directives) due to their toxicity and environmental pollution problems [4]. Hence, an eco-friendly and high performance lead-free solder alloy should be employed to replace the Sn-Pb-based solder. The melting point, wetting properties, and economic feasibility of the solder alloy should be considered for solder joint applications, which are critical for the quality of electronics parts. According to Kang [5] and Glazer [6], the Sn-52In alloy has the advantages of a low melting point and outstanding ductility, while it has the disadvantage of high cost due to the scarcity of In. The Sn-57Bi alloy achieved joint formation at low temperature, but it resulted in low contact. The Sn-3.5Ag alloy

exhibits excellent mechanical and creep properties. However, many studies have been conducted to add a third element, such as Bi, In, Cu, and Zn, to fabricate a three-element alloy in an attempt to lower the melting point and improve wetting properties [7-10].

In addition to the solder alloy, it is important to study the under bump metallization (UBM) method. Cu-based UBM is most commonly employed in conventional Pb-Sn solder bonding technology. However, the Cu is rapidly diffused into the solder, resulting in a highly brittle intermetallic compound (IMC) in the current lead-free solder bonding technology. The interfacial reaction between the solder and UBM has a significant effect on the mechanical properties of electronic packaging and many reports of this phenomenon have been published [11]. In addition, studies regarding methods to replace the Cu-based UBM have been conducted. It has been revealed that Ni-based UBM have relatively low diffusion into the solder and can replace the conventional Cu-based UBM [12]. Currently, much research is being conducted on electroless Ni(P) and interest in this material is growing [13].

#### 1.3 Surface finishes

ENIG, a Ni-based surface finish, has been used extensively in ball grid array (BGA) packaging for the past fifteen years. However, an increase in brittle fractures at the solder joint with an ENIG surface finish has been reported when the Pb-Sn solder was replaced with lead-free solders [14-16]. Such brittle fractures originated from thermal

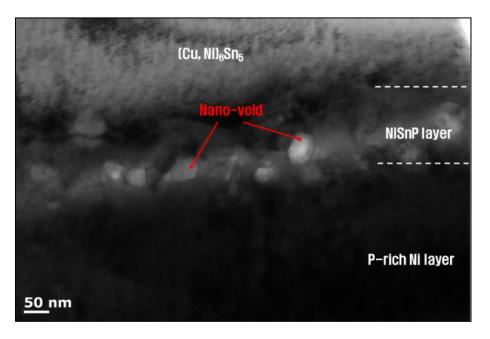

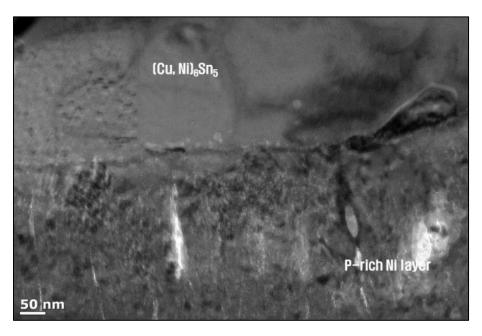

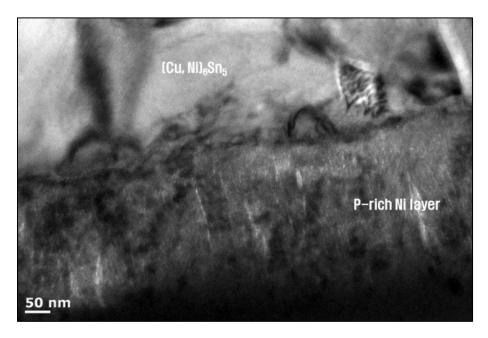

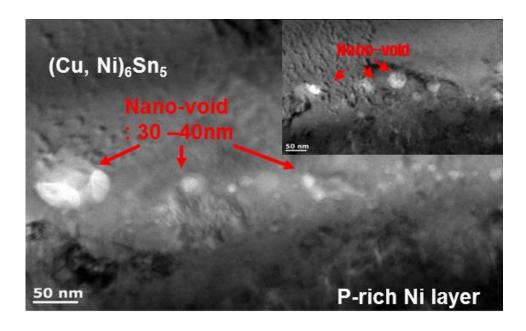

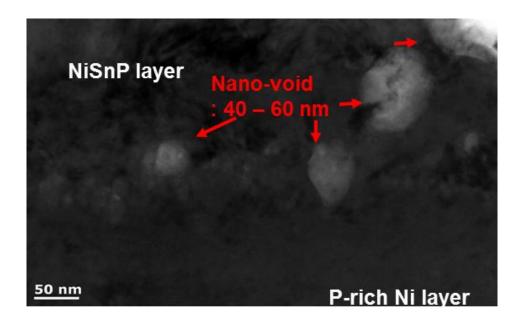

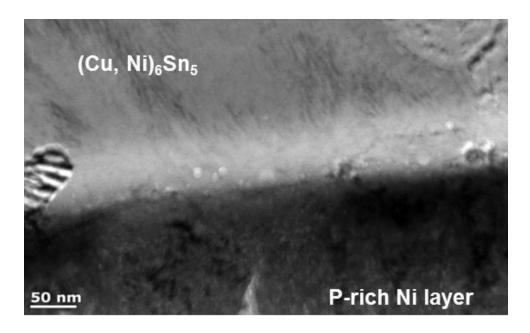

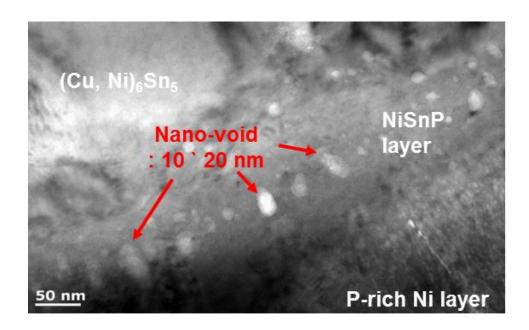

stresses occurring at the solder joint as a result of the accelerated IMC growth and low creep rate of the lead-free solder with increasing soldering temperature. Much research continues to be devoted to solving this problem. Recently, many studies on PCB surface finishes were performed in order to reduce brittle fractures; the surface finish significantly affects the mechanical and electrical reliability of a solder joint. Mei et al. [17] reported the fracture mechanism in the IMC region of an SAC/ENIG joint. The three proposed mechanisms of failure were (1) weakening of the inner joint due to P segregation, (2) weakening of the joint due to defects from contamination and oxidation during or after plating process, and (3) continuous nanovoid formation at the interface between the Ni(P) and IMC layers. In general, Ni<sub>3</sub>P, Ni<sub>12</sub>P<sub>5</sub> + Ni<sub>3</sub>P, Ni<sub>12</sub>P<sub>5</sub>, Ni<sub>2</sub>Pn, Ni<sub>2</sub>SnP, and Ni<sub>3</sub>Sn were formed as IMCs during interfacial reactions between Ni(P) and Sn [18-19]. Since nanovoids existed in the Ni<sub>2</sub>SnP layer located between the Ni<sub>3</sub>Sn<sub>4</sub> and Ni<sub>3</sub>P layers, it was highly vulnerable to failure via crack propagation through the voids [20-21]. To suppress nanovoid formation and P segregation, ENEPIG surface finishes have been prepared by plating an electroless Pd layer onto an electroless Ni layer, which can reduce Ni diffusion [22-23]. ENEPIG surface finishes, unlike ENIG systems, have a Pd layer between the Ni (P) and Au layers which inhibits Ni from diffusing toward the solder during the soldering process. Thus, the ENEPIG layer deters overgrowth of the IMC and gives it high levels of reliability [24-26]. This type of surface treatment also makes wire bonding possible [27]. Currently, a soft Au process is used for wire bonding, but since the formed Au layer must be thick, it makes the process costly. Since Au and Al wire bonding and solder bonding can be used simultaneously [28], it is possible to reduce the cost by replacing Au with Al. There are several studies which have highlighted stability problems with the palladium compound, and further research is needed to improve the durability [29-30].

#### 1.4 Mechanical properties

In addition to investigating solder compounds in the electronic packaging field, many studies have evaluated the mechanical properties. Since electronic devices have recently evolved from desktop to hand-held products, the importance of good drop shock properties of portable products, such as smartphones, is increasing [31]. The drop shock characteristics of solder joints in mobile devices are reduced with miniaturization and high integration. Thus, the demand for devices with drop shock resistance is increasing. Brittle fractures are generally observed as the failure mode of solder joints during drop shock [32]. The conventional shear strength test has been performed at velocities below 300 µm/s. Only low strain rates can be used to characterize bulk solder properties at solder joints. Song reported that the high-speed shear test can adequately simulate drop shock [11]. With increasing strain rate, the failure mode transitioned from ductile fracture in the solder to brittle fracture in the IMC region. The shock that occurs when actual electronic devices are dropped is instantaneous. Thus, many studies have been performed in accordance with the increasing interest in high-speed shear strength tests to determine the mechanical properties of electronic packaging of small mobile electronic devices by applying rapid impacts (unlike conventional test methods) [11, 33].

#### 1.5 Literature review

#### 1.5.1 Electronic packaging

The term "electronic packaging" refers to all hardware in the electronics industry, except for internal chips (ICs). Meanwhile, it means to fill the box and organize the form according to the dictionary. Electronic packaging can also be defined as the final commercialization stage of semiconductor and electronic devices that are packed with plastic resin and ceramics for mounting the microcircuit chip on a substrate. There are four main functions of electronic packaging in the field of semiconductor and electronic devices: (1) The packaging protects the ICs from the external environment. For example, it is difficult to maintain a stable state when even small changes in environmental conditions are present, since the ICs, having the size about 1/1000 the thickness of a human hair, contain a patterned microcircuit. Therefore, the packaging is required to protect the microcircuit. (2) The electronic packaging acts as an electrical connection between the ICs and other components. A direct electrical connection is difficult due to the small chip, which cannot be discriminated by the naked eye. (3) The packaging acts as a heat conductor to cool the internal circuitry during chip operation. Internal heating is directly responsible for the deterioration in

performance and reliability in electronic devices. When the temperature of a chip increases by 10 °C, the lifetime and switching delay were decreased by 50% and 2%, respectively. Hence, optimum performance cannot be achieved and the electronic devices cannot be used for long periods when the internal heat generated by highly integrated large-capacity chips is not effectively released to the external environment. (4) The electric packaging supplies power to operate the chip.

In the past, advanced electronic packaging was not required as its main purpose was to provide an electrical connection and protect the chip from the external environment. Over time, the demand for highly integrated high-performance chips has been increasing. Accordingly, high thermal and electrical performances are also required. Currently, complete systems consisting of the chip, packaging, and device are common and the growing demand is not limited to high performance and miniaturization of the previously mentioned electronic devices. In addition, a low production cost is desired.

To fulfill these requirements, through-hole mountings were replaced by highly integrated surface mountings for semiconductor packages. At the same time, the fine pitch of the internal pin gap was developed based on the demand for small and lightweight pins to enable a higher number of pins with increasing I/O number and facilitate high integration. Electronic packaging can be classified into four levels, as shown in Figure 1.1. The zeroth level packaging refers to the interconnection at the chip level, while the first level packaging is the interconnection forming a single- or multi-chip module [34]. Second level packaging refers to bonding the first level

packaging on a printed circuit board (PCB), and third level packaging is the final stage of bonding to a mother board. As previously mentioned, electronic devices such as smartphones and main frames of computers are examples of electronic packaging.

#### 1.5.2 Lead-free solder alloy

After the first development of lead-free solder, various kinds of solder alloys have been proposed. Most studies have been conducted on binary and ternary metals alloy [35-37] with a few investigating quaternary metals alloy [38]. The lead-free solder alloy material must be environmentally friendly and have a similar melting point to the conventional Pb-Sn solder. In addition, the material should possess outstanding wettability, electrical and thermal conductivity, and have similar mechanical strength and reliability to the conventional Pb-Sn solder. In terms of cost, an inexpensive material is preferred. The requirements for lead-free solder materials in the electronic packaging field are as follows.

- 1) Melting point: the temperature of reflow should not exceed 255 °C, in order to maintain thermal stability of the components and PCB materials.

- 2) Process suitability: the selected materials should be easily made into bars, paste, and wire.

- 3) Toxicity: it should not pose any threats to human health or the environment.

- 4) Physical, mechanical and electrochemical properties: the material should have

outstanding electrical and thermal conductivity, high wettability on the metal substrate, and excellent mechanical properties (e.g. fatigue properties). In addition, it should have outstanding corrosion and oxidation resistance.

5) Cost: the solder alloy material should be inexpensive, as higher costs in the electronic device and electronic packaging industries will increase the product cost.

Sn-based lead-free solder, which is produced by the addition of small amount of various elements (e.g. In, Bi, Zn, Ag, Sb, and Cu) into Sn, is the most-studied lead-free solder alloy for substituting the existing Pb-Sn solder. The characteristics of the candidate solder alloys mentioned in the literature and the potential candidates for lead-free solder compositions are presented in Table 1.1 and 1.2, respectively [39]. These will be described in detail here.

#### 1.5.2.1. Sn

Sn has outstanding wetting properties and hence has been traditionally used as the main component of most solder materials for electronic components. Sn has a melting point of 231 °C and two different crystal structures in the solid state. The stable diamond structure of  $\alpha$ -Sn can be found at temperatures below 13 °C. When the temperature drops below 1 °C, a phase transition known as 'tin-pest' occurs, to  $\beta$ -Sn (a body-centered tetragonal structure).

#### 1.5.2.2. Sn-Ag

The eutectic composition of Sn-Ag-based alloys is Sn-3.5Ag. Compared to the conventional Pb-Sn solder, it has a higher melting point of 221 °C. The microstructure of Sn-3.5Ag solder is composed of Sn dendrites and a Ag<sub>3</sub>Sn IMC. The tensile strength is higher than that of Pb-Sn eutectic solder and its susceptibility to deformation has been reported to be low [6]. Recently, Sn-3.5Ag has been actively studied as the most promising candidate to substitute Pb-Sn-based alloys. However, it has the disadvantage of lower wettability compared to the Pb-Sn eutectic solder. To overcome this problem, ternary solders are being developed [5].

#### 1.5.2.3. Sn-Cu

The eutectic composition of Sn-Cu-based alloys is Sn-0.7Cu and the melting point is 227 °C, which is slightly higher than the common Pb-Sn solder. There are only few studies related to this alloy to date, most being performed by companies such as Motorola. Although the creep properties are lower compared to the conventional Pb-Sn solder, it has an outstanding fatigue life and low cost [5-6, 40]

#### 1.5.2.4. Sn-Bi

The eutectic composition of Sn-Bi-based alloys is Sn-58Bi. It is a low-temperature

solder alloy with a melting point of 138 °C. The solubility is reduced with decreasing temperature and the Bi forms coarse precipitates during solidification, which has adverse effects on the mechanical properties [5-6].

#### 1.5.2.5. Sn-In

The eutectic composition of Sn-In-based alloys is Sn-52In and it has a very low melting point of 117 °C. It has excellent ductility and wettability, but widespread commercialization is difficult due to the scarcity and high cost of In [5].

#### 1.5.2.6. Sn-Zn

The eutectic composition of Sn-Zn-based alloys is Sn-9Zn and it has a melting point of 198 °C, which is similar to the common Pb-Sn eutectic solder. It has disadvantages of low wettability [41] and high reactivity (easy oxidization of Zn). To improve the wettability and mechanical properties, many studies are being conducted to add third, fourth, and fifth elements [42-43].

#### 1.5.2.7. Sn-Ag-Cu

The melting point of the Sn-3.5Ag alloy can be lowered, while the wettability and mechanical strength can be improved, by the addition of Cu. Thus, this alloy has become one of the most commonly used solders. In the case of the Sn-3.5Ag-0.7Cu

solder, the melting point (217 °C) is lower than Sn-3.5Ag. Moreover, the mechanical properties, such as tensile strength, thermal fatigue and creep, are superior to the Pb-Sn eutectic solder [10]. It has also been shown that the formation of the Ag<sub>3</sub>Sn IMC within the solder can be inhibited by optimizing the amount of added Ag [44].

#### 1.5.2.8. Sn-Ag-Bi

The addition of Bi into the Sn-3.5Ag alloy has the advantage of lowering the melting point and improving the wettability and mechanical properties [10]. In particular, Bi concentrations less than 2% can significantly improve the strength through solid-solution strengthening. When the Bi concentration was increased, fine precipitates of Bi, which was not incorporated into Sn, were formed within the solder alloy during cooling, resulting in higher brittleness and lower ductility.

#### 1.5.2.9. Sn-Ag-Zn

In the case of the Sn-3.5Ag alloy, a Ag<sub>3</sub>Sn IMC was formed within the solder. When stress was focused on the IMC, the mechanical properties deteriorated due to crack generation between the solder matrices. In order to prevent this phenomenon, many studies are being performed where Zn is added into the Sn-Ag-based solder. The most promising composition among the Sn-Ag-Zn-based alloys is Sn-3.5Ag-1.0Zn, with a melting point of about 217 °C. Zn can be used to improve the strength and creep resistance of the Sn-3.5Ag solder alloy with a low mutual solubility; it has good

solubility in Ag and negligible solubility in Sn. However, its application for soldering is limited due its low corrosion resistance and wettability, since Zn is readily oxidized in an ambient atmosphere. Recently, soldering using this material has been performed under a nitrogen gas atmosphere and flux manufacturing technology was developed to overcome the Zn oxidation problem. Thus, the applicability of this material has increased. It has also been reported that the addition of Zn into Sn-3.5Ag can result in excellent mechanical properties by suppressing dendrite formation and refining Ag<sub>3</sub>Sn [8].

#### 1.5.3 Surface finish types

Surface finishing can be defined as the surface processing (before the router process or after shipment inspection in the PCM manufacturing) to achieve specific objectives. Surface finishing is carried out for preventing oxidation of the Cu pad in the insert mount technology (IMT) and surface mount technology (SMT) processes and improving the mounting of components. In addition, it enhances the solderability by removing the heat and flux in the soldering process. Surface finish technologies that are currently employed in the electronic component industries can be classified as either hot air solder leveling (HASL), organic solderability preservative (OSP), electroless Ni immersion Au (ENIG), electroless Ni electroless Pd immersion Au (ENEPIG), electroless Ni auto-catalytic Au (ENAG), immersion Sn, or immersion Ag. A comparison of the characteristics and cost according to the type of surface finish is

shown in Table 1.3, and these technologies will be discussed in more detail in the following sections.

#### 1.5.3.1. Hot air solder leveling (HASL)

HASL is one of the common surface finish methods for the process using Pb-Sn-based alloys. After melting, the alloy is buried in the substrate which is moved using a conveyor belt under a stream of hot air to produce a solder layer with uniform thickness. However, it is difficult to control the thickness of Sn-Ag-Cu-based alloy using hot air since its melting point is higher than the Pb-Sn-based alloy. When using hot air, the thickness of the surface finish film deposited on the Cu pad of a PCB is not uniform, preventing mounting of the components with defects in the SMT process. Moreover, the problem of solder bridging occurs with narrow pad spacings due to the high circuit density of substrates with fine pitch patterns [45-47].

#### 1.5.3.2. Organic solderability preservative (OSP)

OSP surface finishing has been widely used to replace the HASL technique. In this method, an organic compound (such as alkyl imidazole) is selectively deposited with a thickness of 0.2–0.5 µm on the Cu pad to prevent oxidation. Since the organic compound is similar to flux, it also can be referred to as a pre-flux finish. This surface finish method is highly suitable for fine pitch patterns since the film is selectively formed on the Cu pad. As the use of mobile devices, such as smart phones, personal

digital assistants (PDA), and portable multi-media players (PMP) increases, superior impact resistance is required. The OSP method has been widely used owing to its low cost and relatively low waste generation during surface finishing with the plating method, which is an advantage in terms of environmental impacts.

When a scratch was generated on a Cu pad with organic compound deposited onto it from careless handling of the products, the exposed Cu easily oxidized in ambient air. This results in reliability problems for long term storage [45-47]. Moreover, it is highly vulnerable to multiple heat treatments when mounting different types of packages.

# 1.5.3.3. Electroless Ni immersion Au (ENIG) and electroless Ni electroless Pd immersion Au (ENEPIG)

ENIG surface finishing is generally carried out by plating an electroless Ni(P) layer with a thickness of 3–6 μm on a Cu pad. Subsequently, a thin Au layer with a thickness of 50–100 nm was plated on top of the nickel layer. This method overcomes some of the disadvantages of HASL and OSP methods and has outstanding handleability, storability, and solderability. It accounts for about 15% of the current surface finish market and the market share is still gradually increasing. The plated Ni(P) layer is used to prevent the rapid diffusion into Cu layer during Au substitution plating. In addition, it helps to prevent reliability problems due to IMC overgrowth since it suppresses the diffusion reaction between Cu and Sn. Brittle fractures were

observed at the interface of the solder and Ni/Au layer originating from the black pad defect phenomenon due to galvanic corrosion of Ni in the P-rich layer formed between the IMC and the Ni(P) layer during soldering [16-19]. According to Jang [19], an increase in P concentration can be observed when the amount of impurities in the Ni(P) plating solution increases due to partial segregation of P atoms. Accordingly, this affects the solderability by promoting the oxidation of Au and Ni atoms during Au substitution plating. A recent international standard recommended a minimum plating thickness of 3 µm and P concentration of 8–10% for the electroless plated Ni(P) layer.

In an attempt to resolve the black pad problem, the ENEPIG surface finish method is being actively studied to replace ENIG. The ENEPIG method involves plating a Au layer with a thickness of 50–100 nm over an electroless Pd layer of 50–100 nm plated on a 3–6 µm electroless Ni(P). This method has the advantage of wide applicability as both Au and Al wire bonding and soldering can be performed. However, due to stability problems with Pd compounds, many studies are being focused on improving the reliability and up-scaling this technique [22-23].

#### 1.5.3.4. Electroless Ni auto-catalytic Au (ENAG)

The ENAG surface finish method is carried out by plating a 0.1–0.3 µm Au layer on top of an ENIG Au layer using an auto-catalytic method. The Au layer of ENAG is a suitable surface finish for wire bonding. As a cyanide-free process, it can improve the corrosion resistance by inhibiting void formation. However, there exist only few

studies reporting the effect of Ni(P) plating, P concentration, and Au thickness on the reliability of the xxxx.

#### 1.5.3.5. Immersion Sn and Ag

The immersion Sn surface finish method can generate a film with uniform surface roughness. It is suitable for high-density circuit applications since Sn, with good wettability, is used. However, typical problems, such as Sn plating and the formation of whiskers, cannot be prevented, resulting in a cavity or temporary short circuit. Several limitations of this method have been reported in previous studies, related to the components falling out of the PCB after the SMT process and soldering not being possible due to very poor wetting behavior after multiple heat treatments. If the surface is touched due to careless handling, oxidation occurs rapidly due to salt from the hands and scratches can be easily formed due to the low strength of Sn [45-47]. Moreover, it has limited practical application due to the high cost of Ag.

#### 1.5.4 Chemistry of ENIG and ENEPIG surface finishes

Methods to form a metal film on a substrate by reducing metal ions from a metal salt solution can be categorized as electroplating, where metal ions are deposited by means of an external power supply, or electroless plating, which does not require an external power supply. Depending on the mechanism through which metal ions

acquire electrons, electroless plating can be subcategorized into immersion plating (galvanic displacement), in which electrons are acquired by substitution reactions, and autocatalytic plating (commonly called electroless plating because it is a representative electroless plating method), in which electrons are acquired from a reducing agent.

Electroless plating has the following advantages: it enables plating on a nonconductive surface, it does not require an external power supply, the target surface can be plated with a uniform thickness regardless of the current distribution, it lends itself well to mass production, and it has excellent adhesion and wear resistance. The main drawbacks are a high production cost, because the source of metal ions is chemical precursors, and the short service life of the plating solution due to contamination by the reaction byproducts [48-49]. Electroless nickel plating (EN) was introduced by Brenner and Riddell in 1946. While a range of reducing agents, such as sodium hypophosphite (NaH<sub>2</sub>PO<sub>2</sub>·H<sub>2</sub>O),sodium boron (NaBH<sub>4</sub>), boronized and dimethylamine (DMAB), can be used for EN, sodium hypophosphite is the most commonly used due to its low cost and convenient handling [50-51]. Characteristics of the two aforementioned methods of electroless plating are as follows.

#### 1) Immersion plating

If two metals with different ionization tendencies are in contact, the metal with higher ionization tendency emits electrons, thereby being oxidized into metal ions, while ions of the metal with lower ionization tendency gain electrons and are reduced into metal [48]. The larger the difference in standard reduction potential values between the two materials, the greater the plating rate. Immersion plating is based on this mechanism of electron transfer between metals triggered by different ionization tendencies. Since an immersion plating bath does not need any extra reducing agent, its main components are metal ions, acid, complexing agent, antioxidant, and pH adjusting agent. As the thickness of the plating film increases, the plating rate decreases towards zero. Table 1.4 shows the ionization tendencies of some metals commonly used in immersion plating.

#### 2) Electroless plating

In the electroless plating technique, the plating metal is deposited onto the target surface catalyzed by reducing metal ions, i.e. transferring electrons, in a plating solution using a reducing agent. The mechanism of electroless plating can be divided into an oxidization stage, in which the reducing agent loses electrons to the plating solution and becomes oxidized, and the deposition stage in which metal ions receive electrons and are deposited onto the target surface forming a metal film [48].

reducing agent  $\rightarrow$  oxide (of the reducing agent) + xe<sup>-</sup> (electron)

$M^{x+}$  (metal ion) +  $xe^{-}$  (electron)  $\rightarrow M$  (metal film)

The above two equations are combined as follows:

$M^{x+}$  (metal ion) + reducing agent  $\rightarrow$  M (metal film) + oxide (of the reducing agent)

An electroless plating solution is composed of metal ions, reducing agent, pH adjusting agent, and catalytic poison (to prevent the plating tank and pump from being plated) [49].

#### 3) Chemical reactions involved in electroless Ni(P) plating

The equations below show the chemical reactions taking place during the ENIG and ENEPIG surface finish methods using sodium hypophosphite as the reducing agent.

Main reactions:

$$Ni^{2+} + H_2PO_2^- + H_2O \rightarrow Ni + H_2PO_3^- + 2H^+$$

(1)

$$H_2PO_2^- + H_2O \rightarrow H_2PO_3^- + H_2$$

(2)

2<sup>nd</sup>-order reactions:

$$2H^+ + 2e^- \rightarrow H_2 \tag{3}$$

$$H_2PO_2^- + H \rightarrow P + OH^- + H_2O$$

(4)

Equations (1)–(4) represent Ni reduction, sodium hypophosphite consumption, hydrogen generation, and P generation, respectively. The potential and pH at which electroless plating occurs can be predicted by examining the reduction potential of Ni and sodium hypophosphite given in Equation (1) using the Pourbaix diagram [52]. The pH and potential ranges where Ni and H<sub>2</sub>PO<sub>3</sub><sup>-</sup> ions are in a stable state are pH 2–7 and -0.3–0.8 vs. SHE, respectively, as can be determined from Equation (1), whereby the utilization efficiency of sodium hypophosphite is lower than 50% (not all of the H<sub>2</sub>PO<sub>3</sub><sup>-</sup> ions are consumed for reducing Ni). Table 1.5 summarizes the advantages and disadvantages of the ENIG surface finish method [50].

# 4) Chemical reactions involved in electroless Pd plating

In the ENEPIG surface finish method, the plating solution in contact with the Ni(P) layer is an autocatalytic electroless Pd plating solution based on an ethylenediamine-Pd complex using salts of formate, phosphite, or hypophosphite and a reducing agent. Table 1.6 shows an example of a standard composition of electroless Pd plating solution, and Figure 1.2 compares the thickness of the plating film of each surface finish method.

#### a) Electroless Pd plating using formate as reducing agent

Figure 1.3(a) shows a potential—pH diagram for an electroless plating solution of ethylenediamine with formic acid (HCOOH) as reducing agent. It

can be seen that Pd ions are in a stable state, bound with ethylenediamine, in the range of pH 5.5–12. This suggests that it is thermodynamically possible to implement electroless Pd plating using formic acid as the reducing agent. Factors influencing the deposition rate are Pd concentration and the temperature of the plating solution. In this plating solution, carbonate is generated as a result of a side reaction which depends on the progress of the plating reaction. However, even when hydrogen carbonate ions are accumulated, the deposition rate is rarely affected. Consequently, a film with uniform surface finish and high density is formed and the plating solution exhibits excellent stability. The equations below show the chemical reactions involved in Pd plating using formate as the reducing agent.

$$RCOOH + H2O \rightarrow CO2 + ROH + 2H+ + 2e-$$

(5)

$$Pd^{2+} + 2e^{-} \rightarrow Pd \tag{6}$$

#### b) Electroless Pd plating using phosphite as reducing agent

In the electroless Pd-P plating solution using phosphite as the reducing agent, the P content is lower than that in the solution using hypophosphite as the reducing agent. The P content is positively correlated with the deposition rate. A decrease in the deposition rate with increasing hypophosphite

concentration results in both a decrease in adsorption of  $Na_2PO_3$  on the precipitate and in the activity of the precipitate, due to an increase in P content.

Figure 1.3 (b) shows the potential-pH diagram of hypophosphite along with hypophosphite. The equations below show the chemical reactions involved in the Pd plating using phosphite as the reducing agent.

$$H_3PO_3 + H_2O \rightarrow H_3PO_4 + 2H^+ + 2e^-$$

(7)

$$H_3PO_2 + 3H^+ + 3e^- \rightarrow P + 3H_2O$$

(8)

$$Pd^{2+} + 2e^{-} \rightarrow Pd \tag{9}$$

#### c) Electroless Pd-P plating using hypophosphite as reducing agent

Figure 1.3 (b) shows the potential–pH diagram showing the electroless Pd plating solution of ethylenediamine using hypophosphite as reducing agent. It can be seen that Pd ions exist as compounds with ethylenediamine in the range of pH 5.5–12. Hence, electroless Pd plating is thermodynamically possible using hypophosphite and phosphite as reducing agents. While the deposition rate increases with increasing Pd concentration, the P content decreases. In contrast, while the deposition rate is not significantly influenced by pH, the P content decreases as pH increases. In addition, the pH affects the surface quality of the plated film; uniform films are formed under

normal conditions and cracks are likely to occur under low concentrations of reducing agent or high pH conditions. The equations below show the chemical reactions involved in Pd plating using hypophosphite as the reducing agent.

$$H_3PO_2 + H_2O \rightarrow H_3PO_3 + 2H^+ + 2e^-$$

(10)

$$H_3PO_2 + H^+ + e^- \rightarrow P + 2H_2O$$

(11)

$$Pd_2^+ + 2e^- \rightarrow Pd \tag{12}$$

In the above redox reactions, the standard potential of the reducing agent (formic acid) is -0.20 V, the reduction potential of phosphite is -0.28 V, and the potential of the hypophosphite-type reducing agent is -0.50 V. Hypophosphite has the highest reactivity because it has the lowest potential. In addition to the reduction reaction, P is generated when phosphite or hypophosphite is used as the reducing agent, and a Pd–P alloy layer is formed during Pd plating as a result of the eutectoid reaction. When a carboxylic acid (e.g. formic acid) is used, a pure Pd plating layer is formed.

## d) Chemistry of immersion Au plating

The equation below shows the chemical reaction involved in immersion Au plating.

$$2Au^{+} + 2e^{-} \rightarrow 2Au0 \tag{13}$$

#### 1.5.5 Interfacial reactions

An IMC is generally formed between UBM and Sn-based solder by the interdiffusion of Sn and UBM atoms. The UBM is classified as Cu- or Ni-based. When the UBM reacts with the solder in reflow, Sn-Cu and Sn-Ni IMCs are generated. The Sn-Ni binary phase diagram is presented in Figure 1.4 and the Sn-Cu binary phase diagram is presented in Figure 1.5. The characteristics of each IMC are shown in Table 1.7.

#### 1.5.5.1. Sn-Ni-based reaction

The IMCs formed by the interfacial reaction between Sn and Ni are  $Ni_3Sn$ ,  $Ni_3Sn_2$ , and  $Ni_3Sn_4$ , and these are discussed in detail in the following text.

- 1) Ni<sub>3</sub>Sn: As shown in Figure 1.4, this IMC is divided into high-temperature Ni<sub>3</sub>Sn and low-temperature Ni<sub>3</sub>Sn. The low-temperature Ni<sub>3</sub>Sn exists at room temperature and has a regular Mg<sub>3</sub>Cd(D019)-type hexagonal close packed (hcp) structure with lattice constants a=0.4286 Å and c=0.4242 Å. The high-temperature Ni<sub>3</sub>Sn occurs above 920.5 °C and has an Fe<sub>3</sub>Al(D03) type cubic structure.

- 2) Ni<sub>3</sub>Sn<sub>2</sub>: This IMC has a NiAs-type hexagonal structure at room temperature with

lattice constants a=0.4081 Å and c=0.5174 Å. At high temperature, the presence of either hexagonal or orthorhombic structures has been reported in the literature.

3) Ni<sub>3</sub>Sn<sub>4</sub>: This compound has a CoSn(B35)-type monoclinic structure consisting of 14 atoms per unit cell. The lattice constants are a = 1.2222 Å, b = 0.4064 Å, c = 0.5225 Å, and  $\beta = 103.48$ °.

Following Ni<sub>3</sub>Sn<sub>4</sub> formation by reaction between Sn and Ni, Ni<sub>3</sub>Sn<sub>2</sub> is formed from the reaction between Ni<sub>3</sub>Sn<sub>4</sub> and Ni. Finally, Ni<sub>3</sub>Sn is formed by the reaction between Ni<sub>3</sub>Sn<sub>2</sub> and Ni. However, the Ni<sub>3</sub>Sn<sub>4</sub> IMC is mostly found as the result of an interfacial reaction between Sn-based solder and Ni UBM. According to Haimovich [53], this phenomenon is related to the higher driving force for Ni<sub>3</sub>Sn<sub>2</sub> and Ni<sub>3</sub>Sn formation compared to Ni<sub>3</sub>Sn<sub>4</sub> at 250 °C. However, Ni<sub>3</sub>Sn<sub>4</sub> is generally formed and grown at the interface between Ni and Sn-3.5Ag solder due to the significant effect of the interfacial energy with the matrix generated during nucleation growth and the thermodynamic driving force during formation of Ni-Sn intermediates. The activation energy barrier for nucleation growth is proportional to  $(3 \times \text{interfacial energy})/(2 \times \text{driving force})$ .

#### 1.5.5.2. Sn-Cu-based reaction

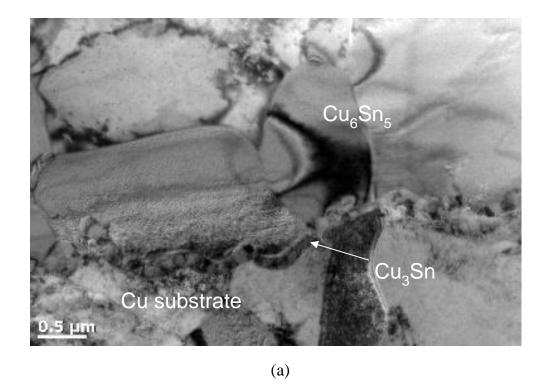

The IMCs formed through interfacial reactions between Sn and Cu are Cu<sub>6</sub>Sn<sub>5</sub> and Cu<sub>3</sub>Sn, which are discussed in detail here.

- 1) Cu<sub>6</sub>Sn<sub>5</sub> ( $\eta$ -phase): As can be seen in Figure 1.5, the  $\eta$ '-phase is the  $\eta$ -phase at room temperature. At temperatures above 186 °C, this compound has a simple superlattice of NiAs(B81)-type hexagonal symmetry with a = 4.2 Å and c = 5.09 Å, consisting of 20% copper and 80% vacancies. In addition, a long period superlattice  $\eta$ '-phase having a five times larger lattice constant is formed at temperatures below 186 °C. The melting point of the  $\eta$ -phase is 676 °C and metal bonding is mainly formed between Cu and Sn.

- 2) Cu<sub>3</sub>Sn ( $\epsilon$ -phase): The high temperature phase has a structure with Cu<sub>0</sub>Ti-type orthorhombic symmetry with lattice constants of a = 2.755 Å and b = 4.722 Å. The melting point is 415 °C and the rules for a long period superlattice are as = 2a, bs = 8b, and cs = c.

Cu<sub>6</sub>Sn<sub>5</sub> is likely to grow inwards towards the solder rather than towards the UBM Cu. Tu [54] showed that the rearrangement for Cu<sub>6</sub>Sn<sub>5</sub> growth took place at the Cu<sub>6</sub>Sn<sub>5</sub>/Sn interface and the IMC growth occurred within the solder due to interstitial diffusion of Cu inside Sn and the higher diffusion of Cu compared to Sn in Cu<sub>6</sub>Sn<sub>5</sub>. Cu<sub>3</sub>Sn was not observed due to difficult nucleation during room temperature aging, while Cu<sub>6</sub>Sn<sub>5</sub> was observed. When the two layer specimen was aged for a long period

at 150 °C (after Sn was completely consumed at room temperature), the  $Cu_3Sn$  infiltrated the layer  $Cu_6Sn_5$  at the interface of the two layers and grew with a parabolic dependence on time. The growth of  $Cu_3Sn$  is a diffusion-controlled reaction.

# 1.5.5.3. Sn-Ag-Cu/Ni-based reactions

The IMC formed between Sn-Ni is usually Ni<sub>3</sub>Sn<sub>4</sub>. However, Hwang, et al. [55] reported a very thin (around 50 nm) Ni<sub>3</sub>Sn<sub>2</sub> IMC below a Ni<sub>3</sub>Sn<sub>4</sub> layer resulting from the interfacial reaction between electrolytic Ni and Sn-3Ag-6Bi. Kao and Duh [12] observed the effect of Cu addition on the interfacial reaction between electrolytic Ni UBM by fixing the Ag amount at 3.9 wt%. When 0.2 wt% Cu was added, only (Ni<sub>1-</sub> <sub>x</sub>Cu<sub>x</sub>)<sub>3</sub>Sn<sub>4</sub> IMC was observed. Two types of IMC, (Ni<sub>1-x</sub>Cu<sub>x</sub>)<sub>3</sub>Sn<sub>4</sub> and (Cu<sub>1-y</sub>Ni<sub>y</sub>)<sub>6</sub>Sn<sub>5</sub>, could be obtained by the addition of 0.4 wt% Cu and (Cu<sub>1-v</sub>Ni<sub>v</sub>)<sub>6</sub>Sn<sub>5</sub> was observed with the addition of more than 0.6 wt% Cu. In the case of electroless Ni(P)/Au UBM, a (Ni<sub>1-x</sub>Cu<sub>x</sub>)<sub>3</sub>Sn<sub>4</sub> IMC was formed when the Cu within the solder was less than 0.5 wt%. Two types of IMC,  $(Ni_{1-x}Cu_x)_3Sn_4$  and  $(Cu_{1-y}Ni_y)_6Sn_5$ , were found for 0.5 wt% Cu addition and the (Cu<sub>1-v</sub>Ni<sub>v</sub>)<sub>6</sub>Sn<sub>5</sub> IMC was observed for more than 0.5 wt% Cu. Sohn et al. [56] investigated the dependence of the morphology of the IMC layer and spalling phenomena on the solder deposition method, P concentration in Ni(P), and solder thickness. A higher P concentration enhanced spalling due to increased solder volume. Needle-shaped IMC morphologies exhibited higher spalling compared to chunkshaped ones due to the increasing number of channels for Sn penetration in needleshaped structures. The Sn that penetrated into the IMC reacted with Ni<sub>3</sub>P, resulting in a Ni<sub>3</sub>SnP layer. On the other hand, Ni<sub>3</sub>Sn<sub>4</sub> delaminated from the Ni<sub>3</sub>SnP surface.

#### 1.5.5.4. Sn-Ag-Cu/Cu-based reaction

For Sn-Ag and Sn-Ag-Cu solder, the IMCs formed by the interfacial reaction with the Cu UBM are Cu<sub>6</sub>Sn<sub>5</sub> and Cu<sub>3</sub>Sn. Only Cu<sub>6</sub>Sn<sub>5</sub> was observed at room temperature, while Cu<sub>3</sub>Sn was generated in the Cu UBM and Cu<sub>6</sub>Sn<sub>5</sub> was formed within the solder during high-temperature aging. In addition, voids were generated in the Cu<sub>3</sub>Sn intermetallic compound when the reaction temperature was high. As the volume of the solder became larger, the consumption of Cu increased and the thickness of the IMC reduced [57].

# 1.5.6 Black pad formation during ENIG surface finishing

With increasing demand for ENIG as a PCB surface finish, related problems have increasingly been reported (accompanied by extensive research activities to address such limitations). Among the problems reported thus far, the most serious one is the black pad phenomenon occurring in the Ni(P) layer, which results in brittle fractures and is the major factor lowering package reliability [31-32, 58-60]. The name "black pad" comes from the black color observed on the Ni(P) layer [31]. This phenomenon has been investigated for about a decade by a consortium in the PCB industry in an

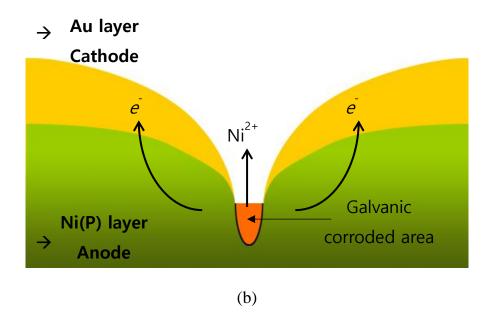

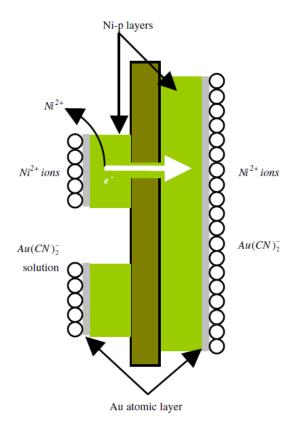

attempt to eliminate the problem by identifying the mechanism and root causes. Kim [32] demonstrated that the black pad phenomenon is ascribable to enhanced corrosion occurring during the immersion Au process. The difference in potential between Au<sup>+</sup> ions on the Ni(P) layer leads to the formation of Ni<sub>2</sub><sup>+</sup> ions. Excessive generation of Ni<sub>2</sub><sup>+</sup> ions while bonding to Au<sup>+</sup> ions results in corrosion. Excessive consumption of Ni ions while bonding can also induce corrosion. Furthermore, excessive consumption of Ni ions on the Ni(P) layer causes the P content to increase accordingly. In the subsequent soldering process, the elevated P content deteriorates wettability and adhesion.

# 1.5.6.1. Black pad mechanism

Currently known causes of the black pad defects can be summarized as follows:

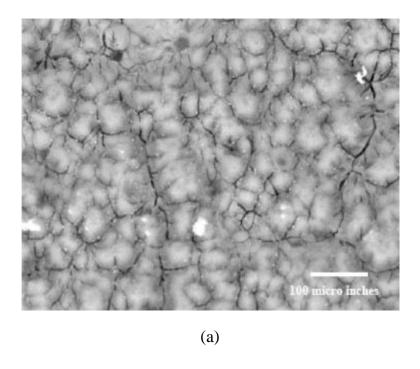

1) According to Biunno [31], the rate of Au grain growth is relatively slow at a nodule boundary or junction. Since the concentration of Au ions is not homogeneous in a nodule boundary, crevices are formed along the boundaries or at junctions. Therefore, the Au layer grows non-uniformly, and micro-galvanic cells are formed between the Ni(P) and Au layers, making the boundaries prone to corrosion. Figure 1.6(a) shows a schematic of black pad formation and Figure 1.6(b) shows how black pads can be formed by applying a 1 V potential. Furthermore, excessive consumption of the Ni ions from the Ni(P) layer in the immersion Au process results in increasing the P content in the consumed region.

From these results, it was concluded that the current flowing through the PCB increases the corrosion activity at the Ni(P) layer, thus accelerating oxidation.

- 2) Kim et al. [32] noted that corrosion starts at a nodule boundary as it is the place where substitution of Ni atoms for Au atoms occurs more intensely; the corrosion then expands towards the interior of the nodule. Accordingly, major and minor spikes are found at the nodule boundaries and interiors, respectively. In the immersion Au plating process, it was also observed that concentration cells are formed when the plating solution circulates, and corrosion occurs in the pad spikes. The smaller the pad area, the larger the region where the plating solution cannot circulate, resulting in a growth of the black pad. Figure 1.7 is a schematic of the size-effect induced concentration cell formation.

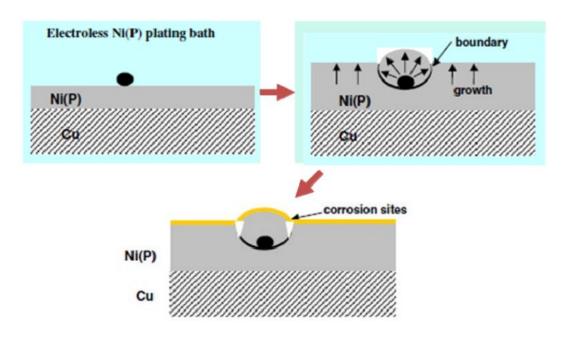

- 3) Osenbach et al. [58] stated that low-density interfaces are formed during the Ni(P) growth due to secondary-phase precipitation, and corrosion occurs during the immersion Au process, resulting in mud cracks appearing on the Ni(P) surface. Figure 1.8 shows a schematic of the corrosion caused by secondary-phase precipitation.

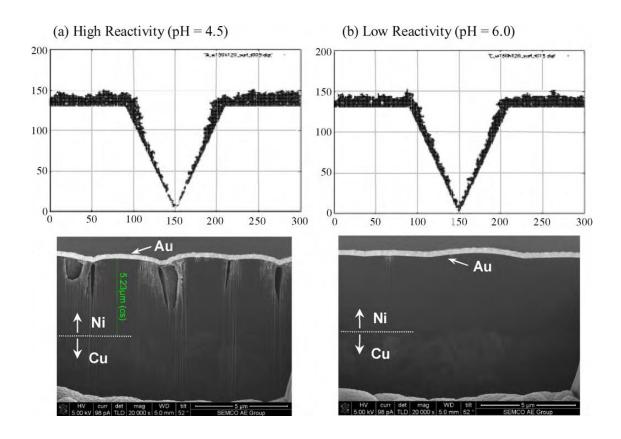

- 4) Won et al. [59] reported that an uneven Au layer is formed due to the adsorption of excess citrate ions along the nodule boundary, resulting in black spots. It was

also noted that this tendency increased as the pH of the Au plating solution decreased. Figure 1.9 depicts the phenomenon of an uneven Au layer leading to black pad formation.

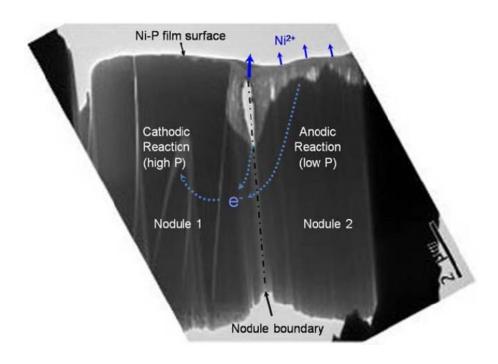

5) Kim et al. [60] reported that nodules on a Ni(P) layer having different P contents induced the formation of micro-galvanic cells, whereby a nodule with lower P content undergoes corrosion during the immersion Au process. Figure 1.10 depicts this process of micro-galvanic corrosion.

# 1.5.6.2. Factors influencing black pad formation

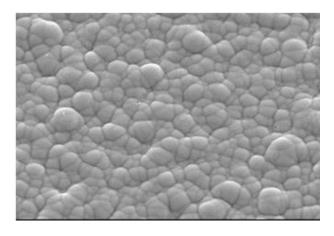

The following outlines the causative factors for black pad formation [32, 60-61]. Variables such as the amount of Ni(P) plating solution used, P concentration, oxidation of Ni (P) layer, organic impurities, and galvanic reaction, are known to be associated with black pad formation.