Journal of University of Babylon for Engineering Sciences, Vol. (27), No. (2): 2019.

# **Review: Recent Directions in ECG-FPGA Researches**

#### Mohammed Khalid Ibrahim

Department of Electrical Engineering, College of Engineering, University of Babylon, Iraq

DR.mohammed.khalid2019@gmail.com

### Ahmed A. Hamad

Department of Electrical Engineering, College of Engineering, University of Babylon, Iraq ahmedbabel@gmail.com

#### **Murad Obaid Abed**

Department of Electrical Engineering, College of Engineering, University of Babylon, Iraq muradalhelo1962@yahoo.com

## Riyadh Abdulhamza Mohammed

Department of Electrical Engineering, College of Engineering, University of Babylon, Iraq alwaniriyad@gmail.com

#### **Abstract**

The last few years witnessed an increased interest in utilizing field programmable gate array (FPGA) for a variety of applications. This utilizing derived mostly by the advances in the FPGA flexible resource configuration, increased speed, relatively low cost and low energy consumption. The introduction of FPGA in medicine and health care field aim generally to replace costly and usually bigger medical monitoring and diagnostic equipment with much smaller and possibly portable systems based on FPGA that make use of the design flexibility of FPGA. Many recent researches focus on FPGA systems to deal with the well-known yet very important electrocardiogram (ECG) signal aspects to provide acceleration and improvement in the performance as well as finding and proposing new ideas for such implementations. The recent directions in ECG-FPGA are introduced in this paper.

**Keywords**: FPGA, ECG, Security, Compression, Denoising, Detection, Diagnose, Medicine and Health Care.

#### 1- Introduction

The electrocardiogram (ECG) signal is a recording related to the heart electrical activity. The ECG signal provides critical information for heart health state and even heart diseases. The ECG signal preprocessing and analyzing take a large deal of the past and recent health and medical researches due to its important role and influence over the diagnose decision which can make the difference of saving patient life in many situations, The ECG signal give an information about heartbeat rate, heart abnormalities as well as biometric identification [1-3].

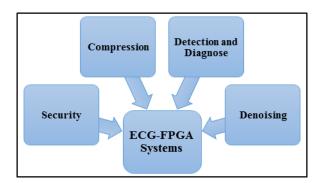

The last few years have shown an evolution in the utilization of FPGA for a variety of applications in many fields. For example, FPGA was implemented to deal with pedestrian detection for the monocular detection system [4], transient disturbance detection in the power system [5], dual three-phase induction machine (DTPIM) simulator implementation in machine systems [6] and many other fields. Meanwhile, the researchers in health care and medical field give great attention to FPGA due to its promising performance, affordable price alongside with its design flexibility, relatively low power consumption and lightweight. Due to these reasons, the FPGA based implementations in health care and medical field was widely adopted mainly to provide a high-speed hardware approach. Nevertheless, another direction was focused on utilizing FPGA to introduce a suitable wearable device capable of wirelessly transmitting updated information of patient health. The recent research directions in ECG-FPGA systems focus on many important aspects of ECG signals, which include security, compression, denoising, detection and diagnose as illustrated in Figure (1).

Figure (1) the recent research directions in ECG-FPGA systems.

The rest of the paper is organized as follows: Section 1 includes the recent methods applied in the ECG-FPGA security field. The ECG-FPGA compression implementation methods are included in Section 2. In Sections 3, the denoising implementation of ECG-FPGA is reviewed. Section 4 focused on the detection and diagnostic implementation of the ECG-FPGA. Lastly, the conclusions of the paper are presented.

#### 2- Recent ECG-FPGA Research Directions

# 1) Security Implementation

In recent years, a part of the ECG researches interest was focused on the security issues related to the secure transmission of ECG information, the protecting of personal patients' ECG information, and in general preventing the unauthorized access to ECG signals records. In turn, some of these researches introduce and suggest FPGA based systems to provide efficient solutions that can deal with these security issues in hardware efficient manner.

The researchers in [7] suggest a simple partial selective encryption scheme for the ECG signal security purposes. The proposed encryption scheme applied on half of the total number of ECG sampled data and utilize algebraic addition and subtraction to perform frequency band separation in manner similar to filter bank technique of DWT. The other half of ECG sampled data remain unencrypted and used alongside the encryption part to construct the final encrypted ECG signal. The proposed scheme was implemented on Xilinx Virtex4 and Xilinx Spartan 3 XC3S50 FPGA platforms. The results suggest that a

noise like behavior is obtained for the final encrypted ECG signal with correlation coefficient very close to zero. The research suggests that the proposed scheme simplicity lower the required computation effort cost of the FPGA implementation as well as boosting the processing speed of encryption.

The researchers in [8] presents FPGA-based implementation based on the Advanced Encryption Standard (AES) algorithm and ECG identification system that aims to transmit and save ECG signals securely in real-time manner. The proposed system was implemented on the Xilinx ZC702 evaluation board. The obtained results suggest the proposed implementation provide a fast response with low resource usage and power consumption.

In [9], the research deal with the encryption and decryption of patient ECG signals records to provide a fast and secure transmission of ECG signals that block the access of non-allowed persons. The research suggests an improved architecture of AES Algorithm that reduces the time required to generate sub-keys of the key expansion process. The improved architecture of AES is simulated and then realized on a Virtex 5 XC5VLX50T FPGA platform to get better security with respect to that of based on software. The results obtained by [9] suggest the improved architecture applied to FPGA was faster and reduce the time to about half comparing to that of original AES while the resource area and consumed power are almost the same.

#### 2) Compression Implementation

The compression and transmission challenges related to a large amount of ECG signals data, which required relatively large processing resources and time, draw increasing attention. Approaches based on FPGA were proposed to obtain sufficient hardware implementations that provide a fast ECG data compression.

The researchers in [10] suggest an improvement to existing fast linear approximation distance threshold (LADT) that reduce computation complexity of ECG signal compression in real-time manner. The suggested improved fast LADT was simulated in Matlab and then realized on FPGA XC3s400 platform. The results shown in [10] suggest a good performance of the FPGA implementation.

In [11], the research presents a simple structure compression approach for ECG signal. The compression utilize delta coding with a separation and rotation mechanism to provide a reduction in values variation of the ECG signal. The delta coding is followed by run length encoding (RLE) for zero bit that eliminates the zero level sections in the ECG signal. The researchers claim that the proposed approach implementation on FPGA give a correct compression performance while the FPGA resource usage kept low.

#### 3) Denoising Implementation

The ECG signals usually suffer from different types of noise and interference that make it difficult to extract reliable information of them. This in turn motivated several researchers to introduce variety of approaches to remove, or at least reduce, the noise effect effectively alongside hardware implementation based on FPGA that provide flexibility in design and performance.

In [12], a FPGA implementation was proposed to filtering the ECG signal using dual FIR filter to improve the ECG filtering performance. The proposed implementation was realized on a ALTERA's cyclone EP1C12Q240C8 FPGA platform.

The researchers in [13] utilize wavelet transformation along with Fast Fourier Transform (FFT) to perform filtering operation over the ECG signal. The work was realized on Altera Cyclone III 3C16 FPGA platform. The obtained results suggest that Fast Fourier Transform and Wavelet Threshold De-noising can reduce the noise as desired.

The researchers in [14] used FIR filter based on distributed algorithm approach to perform filtering over the ECG signal. The distributed FIR filter implemented based on Alter Cyclone III FPGA platform and simulated by the Quartus II and Matlab. The research results suggest that the approach provide good filtering to the ECG signal.

The researchers in [15] introduce a real-time FPGA-based implementation with parallel architecture that utilizes the Least Mean Square (LMS) algorithm to remove power-line interference from ECG signal. The implementation was realized over on Xilinx XUPV5 Development Board.

With the aim of eliminating the power line interferences from the ECG signal, the research in [16] present a FPGA realization for an adaptive filter based on the LMS algorithm. The filter was realized on DE2 board that contains a Cyclone II FPGA chip. The results obtained of the proposed FPGA realization suggest that it is suitable for real-time robust ECG filtering.

In [17], a hardware approach based on FPGA was introduced that firstly perform denoising to ECG signal using FIR filter, then detect of heartbeat using a modified Pan and Tompkins algorithm proposed in [18]. The approach was carried on ALTERA DE II FPGA platform. The research results suggest that the approach detection performance has high level of accuracy in real-time manner.

In [19], show a cascade implementation of FIR filter that utilizes hamming and rectangular windowing methods to perform ECG signal denoising. The cascade implementation was carried on Vertex-6 FPGA platform. The researchers suggest that the FPGA realization performance is better in removing the baseline wanders (BLW) and the power line noise within an acceptable power and resource usage range.

The researchers in [20] show an FPGA realization that utilizes a single multiband FIR least squares type filter to eliminate interference signals related to power system, respiration, muscle and white noise at different frequencies. The FIR filter realized on Terasic DE2-70 board that contains Alter Cyclone II EP2C70F896C6 FPGA chip.

In [21], a pipelined-based delayed error normalized LMS adaptive filtering approach is applied to denoise the ECG signal. The presented approach was realized over Virtex5 XC5LVX330 FPGA platform. The results presented in this research suggest that the FPGA realization of the proposed approach give a fast enhanced denoising performance with lower power consumption but in an expanse of the need for greater area resources and slightly increase in computational complexity comparing to conventional algorithms.

#### 4) Detection and Diagnostic Implementation

A great deal of ECG research efforts was directed to enhance the detection and diagnostic of ECG monitoring systems. Many researchers suggest FPGA based systems that can achieve high detection sensitivity and fast response alongside with ability to provide portability, real-time performance as well as low affordable cost.

The researchers in [22] presents FPGA implementation to monitor ECG signal in real-time manner that include the functionality of filtering and QRS detection. The proposed system was implemented on a Spartan-3 XC3S400-4TQ144C FPGA platform. The results obtained by [22] suggest the proposed FPGA implementation provide a stable real-time ECG signal monitoring performance.

In [23], the researchers propose a FPGA implementation for QRS complexes detection based on wavelet signal processing method called an Adaptive Lifting Scheme (ALS). The FPGA used in this work was Xilinx's Virtex II Pro XC2VP30 FPGA platform. The obtained results of FPGA implementation was compared to that obtained by implement ALS method over TI's DSP TMS320VC5509A system in C language. Based on the results, the research gives a conclusion that the QRS detection performance using ALS-FPGA approach introduce an effective time reduction compared to the ALS-DSP system approach while maintaining the highly accurate detection rate.

In [24], show a hardware/software implementation based on FPGA that perform QRS detection and beat classification of ECG signal. The proposed implementation was carried out over Virtex II PRO XC2VP30-FF896-7 FPGA platform. The hardware QRS detection part is based on an algorithm that utilizes a phase-space portrait of ECG signal, while another algorithm from the Open Source ECG Analysis Software (OSEA) is used to carry out the beat classification part. The reported results show a high sensitivity and positive productivity performance in QRS detection and premature ventricular beat detection and also claim that the hardware/software implementation processes the ECG data in a much higher processing speed compared to that depending only on software implementation.

In [25], the researchers present an online R and T peak detection method based on their previous work proposed in [26] that deal with the QRS detection from ECG signal. The R and T detection method based on slope detection was realized on Xilinx Spartan3 xc3s400tq144-5. The results of the work indicate that performance obtained by the FPGA realization was fast with highly promising detection sensitivity for both R and T peak detection.

The researchers in [27] present an online portable monitoring system aim to analyses the heart rate variability (HRV) of ECG complex signal. The architecture of the proposed system divided into two sides (patient side and pc mobile side) that connected wirelessly via Bluetooth. The proposed ECG monitoring system was realized with Cheetah ARM SoC platform solution as System on Chip - Field Programmable Gate Array (SoC-FPGA) embedded computing platform. The research results conclude that the system realization provides highly integrated performance with wireless capability at low cost.

The researchers in [28] show a real-time FPGA implementation for QRS detection that utilizes a pipeline architecture and based on ALS. The system was realized on Virtex 5 XUPV5-LX110T evaluation FPGA platform. The work results indicate that FPGA implementation performance has high detection accuracy while maintain low power consumption.

In [29], present a FPGA approach to deal with ECG signal processing and R peak detection of cloud clients connected to tele-health server. The research results suggest that proposed approach offer efficient FPGA resource reduction and fast response suitable for real-time implementation.

In [30], propose FPGA realization that utilizes the Discrete Wavelet Transform (DWT) based on Mallat algorithm to minimize the required resource usage and speed out the computations. The proposed approach was applied to detect QRS complex and remove the BLW. Due to resources limitations, the entire system was simulated on Xilinx ARTIX 7 XC7Al00T and the BLW suppression part was tested using JTAG Hardware co-simulation on Spartan-6 XC6SLX16 FPGA platform. The results of [30] were visually evaluated and the research suggests that the BLW part was carried successfully while claiming that despite of the good performance of QRS detection part it wasn't able overcome yet the batter performance of linear filtering implementation obtained by their past work in [31].

With the aid of the previous work in [31], the research in [32] presents an FPGA-based Multiprocessor System on Chip (MPSoC) implementation in master-slave fashion to detect QRS complex of the ECG signal. The research utilizes and tests a reduced 3-processor configuration that consists of a master processor that provide the system control and two slave processors that handle the 12-lead ECG standard. The proposed configuration was carried out over Xilinx Spartan6 XC6SLX16 FPGA platform.

In [33], present FPGA realization aims to detect QRS complex and utilized it for ventricular and supraventricular tachycardia diagnosis in real-time manner. The research applies the fuzzy entropy measure of high resolution ECG sample values to neural network. The suggested diagnostic system based on fuzzy neural is realized on Altera EP1C6Q240C8 FPGA platform to take advantage of FPGA low cost and flexibility to map changes in the proposed algorithm. According to the results obtained by [33], the applied fuzzy neural FPGA based realization was fast with very high detection accuracy comparing to other QRS methods detection.

The work presented in [34] focuses on providing a hardware FPGA-based realization that performs preprocessing to the ECG complex signal as well as detecting R wave and heart beat value. The proposed FPGA realization firstly performs denoising ECG signal using bandpass FIR filter followed by corrosion and inflation operations as morphology transform of the ECG signal and then R wave detection stage with an updated threshold set is carried out. The FPGA implementation is realized on Xilinx Spartan-6 XC6SLX45T FPGA platform. The obtained results suggest that the performance and the detection of R wave was fast, accurate and consume small amount of power.

The researchers in [35] suggest an alternative approach to that of [32] which consist of a three stages algorithm inspired by [36] to detect the QRS of the ECG complex signal. The first stage of proposed algorithm performs filtering operation using high-pass and low-pass FIR filters to eliminate noise, interference as well as P and T waves from the ECG signal. To reduce the rate of misleading detection, the second stage performs differentiation, non-linear transformation and integration. The final stage uses a

fixed window size to maximums search with amplitude and time thresholds to perform the QRS detection. The algorithm is tested using Matlab and realized on Altera DE2-115 board that contains a cyclone IV 4CE115 FPGA chip. The results in [35] claim a high rate of successful detection that overcome the FPGA-based performance of [32] without excluding the challenging ECG signals of the same tested database.

The researchers in [37] propose an adaptive window size detection approach to enhance the work in [35].

In [38], a Bluetooth wireless heart rate and body temperature monitoring FPGA-based system were introduced. The Pan Tompkins algorithm is used for QRS complex detection and the resulted heart rate calculations. The proposed system realizes over SoC FPGA-based Zynq development board. The results suggest that the system is reliable with successful extract performance.

In [39], a remote ECG monitoring system was proposed that utilize the Two-level Load-balance Monitoring Strategy (TLLBMS) to lower delay time and increase reliability performance. To carry this task, the ECG monitoring system realizes parallel Principal Component Analysis - Independent Component Analysis (PCA-ICA) algorithm and Message Digest Hash Algorithm MD5 over the System-on-Chip A2F500 FPGA-based board. The research results suggest that the system has high level of practicality in providing reliable performance with very small delay time.

FPGA realization was presented in [40] that based on a low complexity detection and identification approach of P, R and T peaks from a noise free ECG signal using histogram algorithm. The FPGA implementation is carried on Virtex-5 XC5VLX50TFF G1136C FPGA platform. The researchers suggest that the implementation make use of the proposed approach simplicity to give a fast performance with better and accurate values comparing to the other approaches.

In [41], the researchers present a study on FPGA implementation based on artificial neural network (ANN) to perform an ECG anomaly detection. The resilient backpropagation (RPROP) is used as neural network training algorithm for its generalization ability. The Principal Component Analysis method is carried out by Matlab to perform the feature reduction part and the resulted feature vector is then transmitted to the Zynq FPGA to perform training and implementation of the multi-layer perceptron that performs the classification part.

#### **3- Conclusions**

The recent directions dealt with a ECG-FPGA systems is introduced in this paper. These directions involve the utilization of the FPGA-based hardware solutions to address several problems in medicine and health care field, especially those related to the ECG signal field aspects, which in turn give a great design and implementation flexibility. The benefits of this were clearly visible in purposing different FPGA-based hardware solutions that might be able to replace costly and bigger medical equipment with relatively cheap, much lighter and possibly portable systems that based on FPGA while maintain or even enhance high performance and response speed.

On the other hand, the implementation of ECG-FPGA systems makes it possible to deal with variety of ECG aspects. For instant, recent approaches focus on aspects related to security issues of ECG access and transmission, efficient ECG data compression, noise and interference effect removal, as well as improving detection and diagnose.

In addition, it's clear that FPGA high design flexibility and fast performance will provide the ability to address a new research aspect and present efficient solutions for a future ECG systems enchantments and challenges.

#### **CONFLICT OF INTERESTS.**

- There are no conflicts of interest.

#### References

- [1] Li Y. and Cui W., "Identifying the mislabeled training samples of ECG signals using machine learning". Biomedical Signal Processing and Control, Vol. 47, pp. 168–176, 2018.

- [2] Dar M. N.; Akram M. U.; Shaukat, A. and Khan, M. A., "ECG Based Biometric Identification for Population with Normal and Cardiac Anomalies Using Hybrid HRV and DWT Features", the 5th International Conference on IT Convergence and Security (ICITCS), pp. 1-5, 2015.

- [3] Wieclaw L.; Khoma Y.; Fałat P.; Sabodashko D. and Herasymenko V., "Biometric identification from raw ECG signal using deep learning techniques", IEEE 9th International Conference on Intelligent Data Acquisition and Advanced Computing Systems: Technology and Applications (IDAACS), pp. 129-133, 2017.

- [4] Guo A.; Xu M.; Ran F. and Li A., "FPGA Implementation of a Real-Time Pedestrian Detection Processor Aided by E-HOG IP", Journal of Computers, Vol. 28, No. 2, pp. 87-103, 2017.

- [5] Li L. and Shi K., "Research and Realization of Transient Disturbance Detection Algorithm Based Coiflet Wavelets and FPGA", International Journal of Future Generation Communication and Networking (IJFGCN), Vol. 9, No. 2, pp. 133-142, 2016.

- [6] Gregor R.; Valenzano G.; Rodas J.; Rodríguez-Piñeiro J. and Gregor D., "Design and Implementation of an FPGA-based Real-time Simulator for a Dual Three-Phase Induction Motor Drive", Journal of Power Electronics (JPE), Vol. 16, No. 2, pp. 553-563, 2016.

- [7] Izharuddin M.; Farooq O. and Rafiq M. Q., "Partial encryption of ECG with reduced complexity and its FPGA implementation", International Journal of Biomedical Engineering and Technology, Vol. 17, No. 4, pp. 398-417, 2015.

- [8] Zhai X.; Ait Si Ali A.; Amira A. and Bensaali F., "ECG Encryption and Identification based Security Solution on the Zynq SoC for Connected Health Systems", Journal of Parallel and Distributed Computing, Vol. 106, pp. 143-152, 2017.

- [9] Kumar T. M. and Karthigaikumar P., "FPGA implementation of an optimized key expansion module of AES algorithm for secure transmission of personal ECG signals", Springer, Design Automation for Embedded Systems, Vol. 22, Issue 1-2, pp. 13-24, 2018.

- [10] Yongming Y.; Jungang L. and Jianmin W., "LADT Arithmetic Improved and Hardware Implementation for FPGA-Based ECG Data Compression", 2nd IEEE conference on industrial electronics and applications, pp. 2230-2234, 2007.

- [11] Chen W.; Lu C.; Jiang Y. and Fang H., "FPGA design and verification for lossless ECG coding compression", 6th IEEE International Symposium on Next Generation Electronics (ISNE), pp. 1-3, 2017.

- [12] Mu-hua Z. and Shi-sheng W., "The Design of ECG Signals Dually Filtering Based on FPGA", 2nd International Conference on Industrial Mechatronics and Automation (ICIMA), pp. 87-90, 2010.

- [13] Nianqiang L.; Yongbing W. and Guoyi Z., "A Preferable Method on Digital Filter in ECG Signal's Processing Based on FPGA", Third International Symposium on Intelligent Information Technology and Security Informatics, pp. 184-187, 2010.

- [14] Li N.; Hou S. and Cui S., "Application of Distributed FIR filter based on FPGA in the analyzing of ECG signal", International Conference on Intelligent System Design and Engineering Application, pp. 335-338, 2010.

- [15] Zhou Z.; He J. and Liu Z., "FPGA-Implementation of LMS Adaptive Noise Canceller for ECG Signal Using Model Based Design", International Symposium On Bioelectronics and Bioinformations, pp. 127-130, 2011.

- [16] Tudosa I. and Adochiei N., "FPGA Approach of an Adaptive Filter for ECG Signal Processing", International Conference and Exposition on Electrical and Power Engineering (EPE), pp. 571-576, 2012.

- [17] Alhelal D.; Aboalayon K. A. I.; Daneshzand M. and Faezipour M., "FPGA-Based Denoising and Beat Detection of the ECG Signal", Proceeding of IEEE Long Island Systems Applications and Technology conference (LISAT), pp. 1-5, 2015.

- [18] Faezipour M.; Tiwari T. M.; Saeed A.; Nourani M. and Tamil L. S., "Wavelet-Based Denoising and Beat Detection of ECG Signal", in IEEE Life Science Systems and Applications Workshop (LISSA), pp. 100-103, 2009.

- [19] Bhaskar P. C. and Uplane M. D., "FPGA Based Digital FIR Multilevel Filtering for ECG Denoising", International Conference on Information Processing (ICIP), pp. 733-738, 2015.

- [20] Aboutabikh K. and Aboukerdah N., "Design and implementation of a multiband digital filter using FPGA to extract the ECG signal in the presence of different interference signals", Elsevier, An International Journal of Computers in Biology and Medicine, Vol. 62, pp. 1-13, 2015.

- [21] Venkatesan C.; Karthigaikumar P. and Varatharajan R., "FPGA implementation of modified error normalized LMS adaptive filter for ECG noise removal", Springer, Cluster Computing, pp. 1-9, 2018.

- [22] Yang Y.; Huang X. and Yu X., "Real-Time ECG Monitoring System Based on FPGA", The 33rd Annual Conference of the IEEE Industrial Electronics Society (IECON), pp. 2136-2140, Taiwan, 2007.

- [23] Li Y.; Yu H.; Jiang L.; Ma L. and Ji Z., "Adaptive Lifting Scheme for ECG QRS Complexes Detection and its FPGA implementation", 3rd International Conference on Biomedical Engineering and Informatics (BMEI), Vol. 2, pp. 721-724, 2010.

- [24] Cvikl M. and Zemva A., "FPGA-oriented HW/SW implementation of ECG beat detection and classification algorithm", Digital Signal Processing, Vol. 20, No. 1, pp. 238-248, 2010.

- [25] Chatterjee H. K.; Gupta R. and Mitra M., "Real time P and T wave detection from ECG using FPGA", Procedia Technology, Vol.4, Elsevier, pp. 840-844, 2012.

- [26] Chatterjee H. K.; Gupta R.; Bera J. N. and Mitra M., "An FPGA implementation of real-time QRS detection", 2nd IEEE International conference on Computer and Communication Technology (ICCCT), pp. 274-279, 2011.

- [27] Chou C.; Fang W. and Huang H., "A Novel Wireless Biomedical Monitoring System with Dedicated FPGA-based ECG Processor", IEEE 16th International Symposium on Consumer Electronics (ISCE), pp. 1-4, 2012.

- [28] Yu H.; Ma L.; Wang R.; Jiang L.; Li Y.; Ji Z.; Pingkun Y. and Fei W., "A FPGA-Based Real Time QRS Complex Detection System Using Adaptive Lifting Scheme", Springer, F.L. Gaol (Ed.): Recent Progress in Data Engineering and Internet Technology Vol. 1, Lecture Notes in Electrical Engineering (LNEE 156), pp. 497–504, 2013.

- [29] Zhou S.; Zhu Y.; Wang C.; Gu X.; Yin J.; Jiang J. and Rong G., "An FPGA-Assisted Cloud Framework for Massive ECG Signal Processing", IEEE 12th International Conference on Dependable, Autonomic and Secure Computing, pp. 208-213, 2014.

- [30] El Mimouni E. and Karim M., " An FPGA-Based Implementation of a Pre-Processing Stage for ECG Signal Analysis Using DWT", Second World Conference On Complex Systems (WCCS), pp. 649-654, 2014.

- [31] El Mimouni E. and Karim M., "Novel real-time FPGA-based QRS detector using adaptive threshold with the previous smallest peak of ECG signal," in Journal of Theoretical and Applied Information Technology (JATIT), Vol. 50, No. 1, pp. 33-43, 2013.

- [32] El Mimouni E.; Karim M. and Amarouch M., "An FPGA-Based MPSoC for Real-Time ECG Analysis", IEEE 3rd World Conference on Complex Systems (WCCS), pp. 1-4, 2015.

- [33] Chowdhury S. R., "High-resolution detection of sustained ventricular and supraventricular tachycardia through FPGA-based fuzzy processing of ECG signal", Springer, Medial & Biological Engineering Computing, Vol. 53, Issue 10, pp. 1037 1047, 2015.

- [34] Liang Y.; Su W.; Li M. and Li Y., "Field Programmable Gate Array Implementation Method of Electrocardiogram Signal Processing and Analysis", 2015 8th International Conference on BioMedical Engineering and Informatics (BMEI), pp. 521-525, 2015.

- [35] El-Hassen A.; Histace A.; Terosiet M. and Romain O., "FPGA-Based Detection of QRS Complexes in ECG Signal", 2015 Conference on Design and Architectures for Signal and Image Processing (DASIP), pp. 1-7, 2015.

- [36] Dubois R.; Maison-Blanche P.; Quenet B. and Dreyfus G., "Automatic ECG wave extraction in long-term recordings using Gaussian mesa function models and nonlinear probability estimators", Computer Methods and Programs in Biomedical, Vol. 88, Issue 3, pp. 217–233, 2007.

- [37] Habiboullah A.; Terosiet M.; Histace A. and Romain O., "Improvement of a FPGA-based Detection of QRS Complexes in ECG Signal using an Adaptive Windowing Strategy", SciTePress, in Proceedings of The 9th International Joint Conference on Biomedical Engineering Systems and Technologies Volume 4: Smart -BIODEV (BIOSTEC 2016), pp. 327-332, 2016.

- [38] Joaquinito R. and Sarmento H., "A Wireless Biosignal Measurement System using a SoC FPGA and Bluetooth Low Energy", IEEE 6th International Conference on Consumer Electronics-Berlin (ICCE-Berlin), pp. 36-40, 2016.

- [39] Chen H. and Liu H., "A remote electrocardiogram monitoring system with good swiftness and high reliablility", Elsevier, in Journal of Computers and Electrical Engineering, Vol. 53, pp. 191-202, 2016.

- [40] Agrawal A. and Gawali D. H., "FPGA-based Peak Detection of ECG Signal using Histogram Approach", Proceeding International Conference on Recent Innovations in Signal Processing and Embedded Systems (RISE), pp. 463-468, 2017.

- [41] Wess M.; Sai Manoj P. D. and Jantsch A., "Neural Network based ECG Anomaly Detection on FPGA and Trade-off Analysis", IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1-4, 2017.

# بحث استقصائي: الاتجاهات الحديثة في بحوث ال ECG-FPGA

محمد خالد ابراهيم

قسم الهندسة الكهر بائية، كلية الهندسة، جامعة بابل، العراق

DR.mohammed.khalid2019@gmail.com

احمد عبد الكاظم حمد

قسم الهندسة الكهر بائية، كلية الهندسة، جامعة بابل، العراق

ahmedbabel@gmail.com

مراد عبيد عبد

قسم الهندسة الكهر بائية، كلية الهندسة، جامعة بابل، العراق

muradalhelo1962@yahoo.com

رياض عبد الحمزة محمد

قسم الهندسة الكهر بائية، كلية الهندسة، جامعة بابل، العراق

alwaniriyad@gmail.com

#### الخلاصة

لقد شهدت السنوات القليلة الماضية اهتماماً متزايداً نحو استخدام مصفوفة البوابات المنطقية القابلة للبرمجة FPGA في التطبيقات المختلفة. لقد أدى التقدم الحاصل في مرونة التعامل مع الموارد بالاضافة الى الزيادة في سرعة الاداء وانخفاض الثمن للله FPGA وكذلك الاستهلاك القليل للطاقة الى هذا الاهتمام المتزايد بالله FPGA. ان استخدام الله FPGA في مجالات الطب والصحة يهدف بشكل عام الى استبدال اجهزة المراقبة الطبية كبيرة الحجم وغالية الثمن باخرى أصغر حجماً مع امكانية تصميمها لكي تكون الجهزة محمولة اعتماداً على مرونة التصميم التي يوفرها اله FPGA. إنصب الاهتمام في العديد من البحوث الحالية على استخدام نظام FPGA لمعالجة الجوانب المتعلقة بإشارة تخطيط القلب وذلك لتوفير التحسينات في الاداء وزيادة السرعة بالاضافة الى أيجاد وإقتراح افكار جديدة لمثل هذه التطبيقات. ان هذا البحث يوفر نظرة عامة عن الاتجاهات الحالية في انظمة ECG-FPGA.

الكلمات الداله: - الأمن، ضغط، تقليل الضوضاء، الكشف، التشخيص.