## Fine-Grain Multiple-Valued Reconfigurable VLSI Architecture Based on High Utilization of Hardware Resources

| 著者     | Bai Xu                            |

|--------|-----------------------------------|

| 学位授与機関 | Tohoku University                 |

| 学位授与番号 | 11301甲第15922号                     |

| URL    | http://hdl.handle.net/10097/58719 |

## **Doctoral Thesis**

# Fine-Grain Multiple-Valued Reconfigurable VLSI Architecture Based on High Utilization of Hardware Resources

(ハードウェアリソースの高稼働率化に基づく細粒度 多値リコンフィギャラブル VLSI アーキテクチャ)

#### Xu Bai

Intelligent Integrated Systems Laboratory

Department of Computer and Mathematical Sciences

Graduate School of Information Sciences

Tohoku University, Japan

January, 2014

# **Contents**

| 1 | IIItr | baucho   | II                                                 | U  |

|---|-------|----------|----------------------------------------------------|----|

| 2 | High  | 1-perfor | mance multiple-valued logic block using current-   |    |

|   | sour  | ce-shar  | ing differential-pair circuits                     | 14 |

|   | 2.1   | Overvi   | ew                                                 | 14 |

|   | 2.2   | Reviev   | v of the multiple-valued fine-grain reconfigurable |    |

|   |       | VLSI     |                                                    | 15 |

|   | 2.3   | Binary   | -controlled current-steering technique             | 22 |

|   |       | 2.3.1    | Review of the MOS current-mode logic               | 22 |

|   |       | 2.3.2    | Design of the binary-controlled differential-pair  |    |

|   |       |          | circuit                                            | 24 |

|   |       | 2.3.3    | Evaluation of the binary-controlled differential-  |    |

|   |       |          | pair circuit                                       | 36 |

|   | 2.4   | Curren   | it-source sharing technique                        | 47 |

|   |                   | 2.4.1                                                        | Design of the current-source-sharing differential-                               |                   |

|---|-------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------|

|   |                   |                                                              | pair circuit                                                                     | 47                |

|   |                   | 2.4.2                                                        | Evaluation of the current-source-sharing differentia                             | 1-                |

|   |                   |                                                              | pair circuit                                                                     | 60                |

|   | 2.5               | Dual-s                                                       | upply voltage technique for low-power multiple-                                  |                   |

|   |                   | valued                                                       | source-coupled logic circuits                                                    | 63                |

|   | 2.6               | Design                                                       | and evaluation of the multiple-valued cell using                                 |                   |

|   |                   | curren                                                       | t-source-sharing differential-pair circuits                                      | 69                |

|   | 2.7               | Conclu                                                       | ision                                                                            | 86                |

| 3 | Area              | a-efficie                                                    | nt switch block based on a multiple-valued X-net                                 |                   |

|   |                   |                                                              |                                                                                  |                   |

|   | data              | transfe                                                      | er scheme                                                                        | 88                |

|   | data              |                                                              | er scheme                                                                        |                   |

|   |                   | Overvi                                                       |                                                                                  |                   |

|   | 3.1               | Overvi<br>Multip                                             | ew                                                                               | 88                |

|   | 3.1               | Overvi<br>Multip<br>on the                                   | le-valued fine-grain reconfigurable VLSI based                                   | 88                |

|   | 3.1               | Overvi<br>Multip<br>on the<br>Multip                         | le-valued fine-grain reconfigurable VLSI based binary X-net data transfer scheme | 88                |

|   | 3.1<br>3.2<br>3.3 | Overvi<br>Multip<br>on the<br>Multip<br>on the               | le-valued fine-grain reconfigurable VLSI based binary X-net data transfer scheme | 88                |

|   | 3.1<br>3.2<br>3.3 | Overvi<br>Multip<br>on the<br>Multip<br>on the<br>Evalua     | le-valued fine-grain reconfigurable VLSI based binary X-net data transfer scheme | 88                |

|   | 3.1<br>3.2<br>3.3 | Overvi<br>Multip<br>on the<br>Multip<br>on the<br>Evaluation | le-valued fine-grain reconfigurable VLSI based binary X-net data transfer scheme | 888<br>899<br>988 |

| 4  | High-performance long-distance data transfer using a dy- |                                                         |     |  |  |  |  |  |  |

|----|----------------------------------------------------------|---------------------------------------------------------|-----|--|--|--|--|--|--|

|    | nam                                                      | nic tree network                                        | 112 |  |  |  |  |  |  |

|    | 4.1                                                      | Overview                                                | 112 |  |  |  |  |  |  |

|    | 4.2                                                      | Long-distance data transfer in the multiple-valued re-  |     |  |  |  |  |  |  |

|    |                                                          | configurable VLSI using only the X-net network          | 113 |  |  |  |  |  |  |

|    | 4.3                                                      | Design of the multiple-valued fine-grain reconfigurable |     |  |  |  |  |  |  |

|    |                                                          | VLSI using the global tree local X-net network          | 117 |  |  |  |  |  |  |

|    | 4.4                                                      | Evaluation of the multiple-valued fine-grain reconfig-  |     |  |  |  |  |  |  |

|    |                                                          | urable VLSI using the global tree local X-net network   | 123 |  |  |  |  |  |  |

|    | 4.5                                                      | Conclusion                                              | 129 |  |  |  |  |  |  |

| 5  | Con                                                      | clusion                                                 | 130 |  |  |  |  |  |  |

| Bi | bliog                                                    | raphy                                                   | 134 |  |  |  |  |  |  |

| A  | cknov                                                    | vledgment                                               | 140 |  |  |  |  |  |  |

## Chapter 1

## Introduction

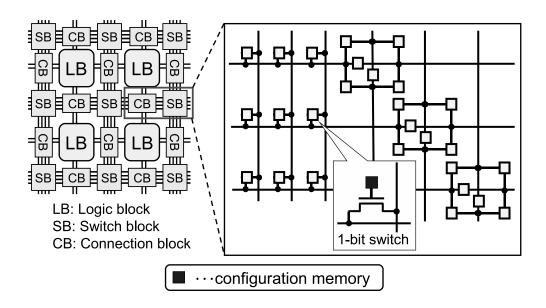

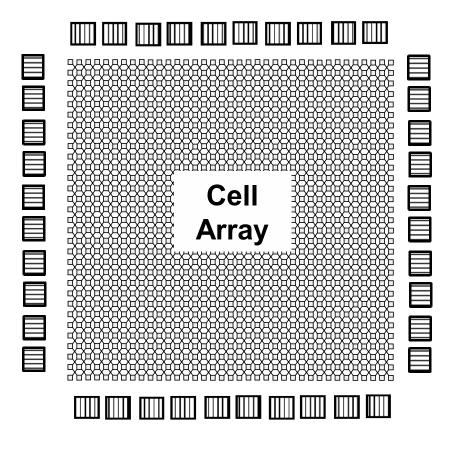

A key challenge in the integrated circuit (IC) scaling era is delivering high-performance solutions while minimizing power and cost. Programmable logic devices such as field-programmable gate arrays (FP-GAs) are cost-effective from low- to mid-volume applications because functions and interconnections of logic resources can be directly programmed by end users[1]. Figure 1.1 shows the architecture of the conventional FPGA composed of logic blocks, switch blocks and connection blocks. Despite their design cost advantage, it is well understood that FPGAs suffer in terms of area, performance and power consumption relative to full-custom ICs because of the extremely complex switch blocks and connection blocks. The overhead incurred to make FPGAs both general purpose and field-programmable often limits integrations of FPGAs into real-world intelligent systems such as mobile phones,

Figure 1.1: Architecture of the conventional Field-Programmable Gate Arrays (FPGA)

digital cameras, televisions, robots and vehicles[2].

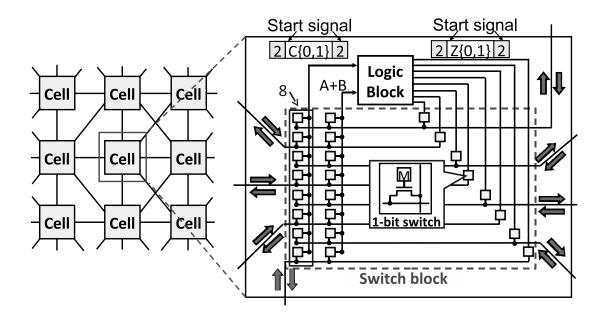

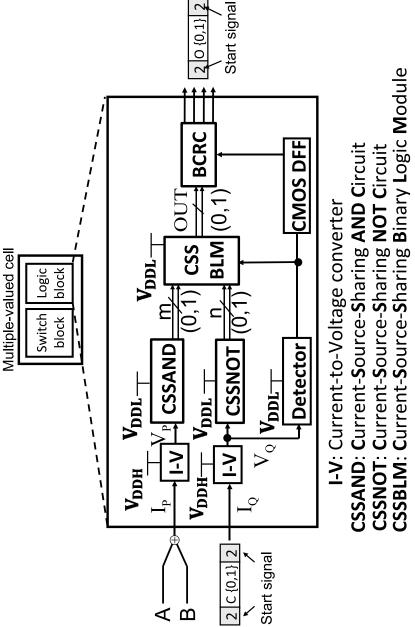

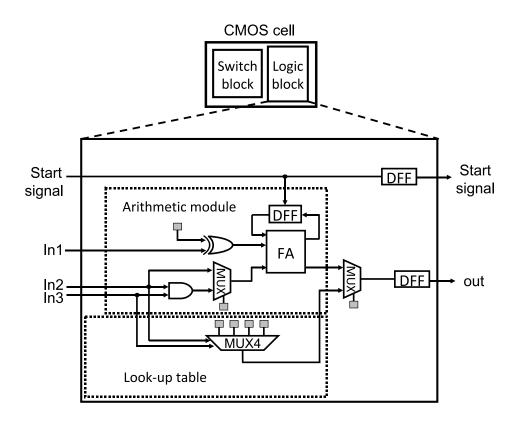

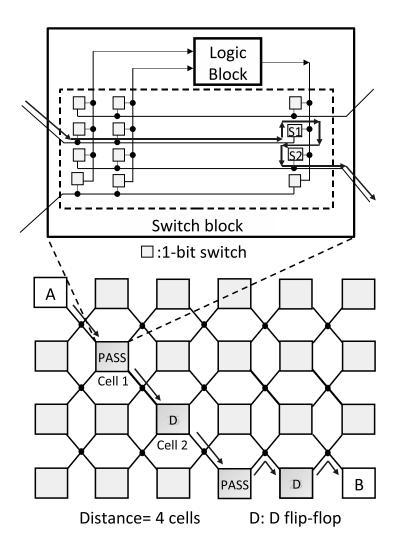

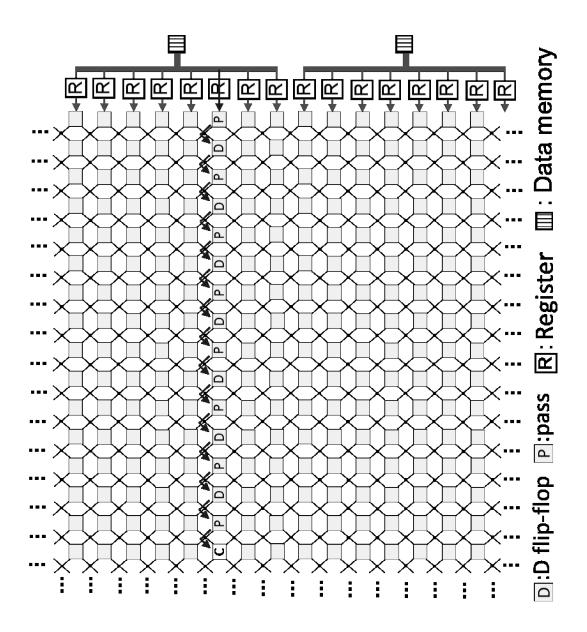

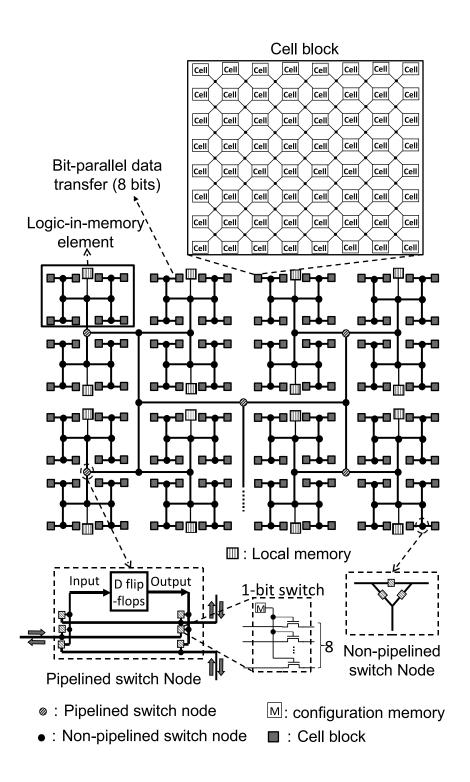

A multiple-valued fine-grain reconfigurable VLSI (MVFG-RVLSI) using an eight nearest-neighbor mesh network (8-NNM) shown in Fig. 1.2 has been proposed to solve these problems[3][4]. Fine-grain pipelining and high utilization of a cell make the performance and parallelism high, respectively[5][6]. Also, localized data transfer architecture and multiple-valued signaling are effectively employed for reduction of switch blocks[3]. Moreover, in the multiple-valued reconfigurable VLSI cell, a quaternary-controlled differential-pair circuit is shared as common hardware resource to generate a full-adder sum or implement an arbitrary 2-variable binary function to realize a compact logic block[7].

Figure 1.2: Architecture of the multiple-valued fine-grain reconfigurable VLSI using an eight nearest-neighbor mesh network

However, there are still many problems which limit the integration of the MVFG-RVLSI into the real-world intelligent systems. The first problem is that the MVFG-RVLSI cell has relative lower speed and larger power consumption in comparison with an equivalent CMOS reconfigurable VLSI cell of the same architecture[7]. A binary-to-quaternary converter composed of two differential-pair circuits (DPCs) is utilized to generate the quaternary signal for the quaternary-controlled differential-pair circuit, which results in low speed and large power consumption. The quaternary-controlled differential-pair circuit using a fixed reference voltage is not so fast due to the small voltage difference in the gate

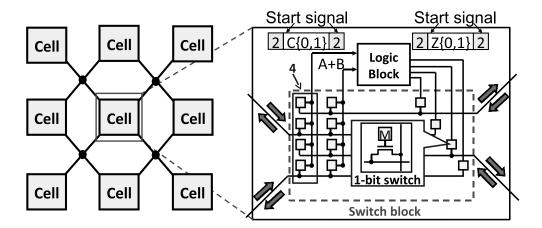

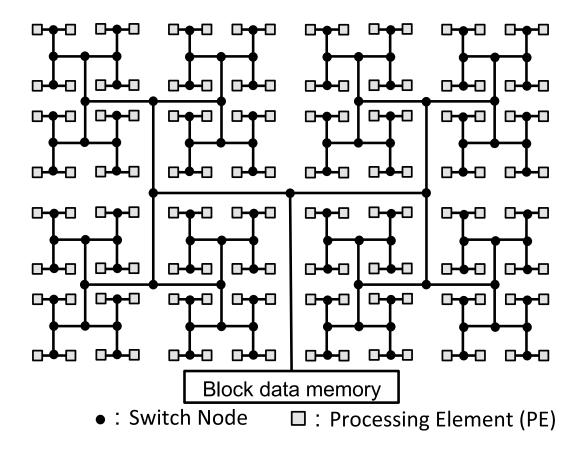

Figure 1.3: Architecture of the multiple-valued reconfigurable VLSI using the X-net

inputs. Also, its noise margin is very small due to the small voltage difference of the dual-rail output. Moreover, to realize the fine-grain bit-serial pipelined operation, many current sources are used to implement current-mode D flip-flops (CMDFFs), which results in large power consumption.

To solve the first problem, Chapter 2 proposes three circuit-level techniques including a binary-controlled current-steering technique, a current-source sharing technique and a dual-supply voltage technique for multiple-valued source-coupled logic circuits.

The binary-controlled current-steering technique is introduced to use a three-level DPC to implement a high-performance arbitrary 2-variable binary function. Also, the voltage difference of the dual-rail output is larger than that of the previous quaternary-controlled differential-pair circuit, which increases the noise margin. The power consumption and the delay can be greatly reduced without using the binary-to-quaternary converter. HSPICE simulation of the binary-controlled differential-pair circuit is done using a 65nm CMOS design rule. As a result, the delay, the power consumption and the area of the binary-controlled differential-pair circuit are reduced to 33%, 26% and 68%, respectively, in comparison with the previous quaternary-controlled differential-pair circuit with the binary-to-quaternary converter. In comparison with a conventional 2-input look-up table (LUT) [1], the delay and the area of the binary-controlled differential-pair circuit become 83% and 88%, respectively. Also, the binary-controlled differential-pair circuit has lower power consumption when the operating frequency is more than 1.6GHz.

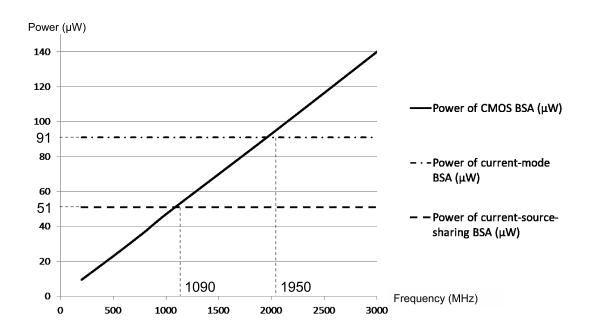

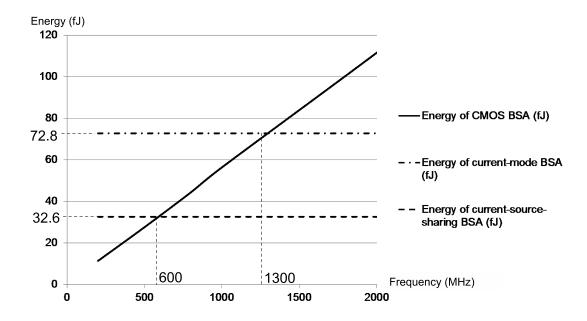

In a proposed current-source-sharing differential-pair circuit, only one current source is shared to implement a logic function and store its result, so that the high utilization of the current source leads to low power consumption. Also, the delay is reduced because the sample stage in the current-mode D-latch is omitted. To demonstrate the advantage of the current-source sharing technique, HSPICE simulation of a current-source-sharing bit-serial adder is done using a 65nm CMOS design rule. The power consumption, the delay and the area of the proposed current-source-sharing bit-serial adder are reduced to 56%, 70% and 83%, re-

spectively, in comparison with the current-mode bit-serial adder. The area and the delay become 88% and 47% of those of the CMOS bit-serial adder, respectively. Also, the proposed current-source-sharing bit-serial adder has lower power consumption when the operating frequency is more than 1.09GHz.

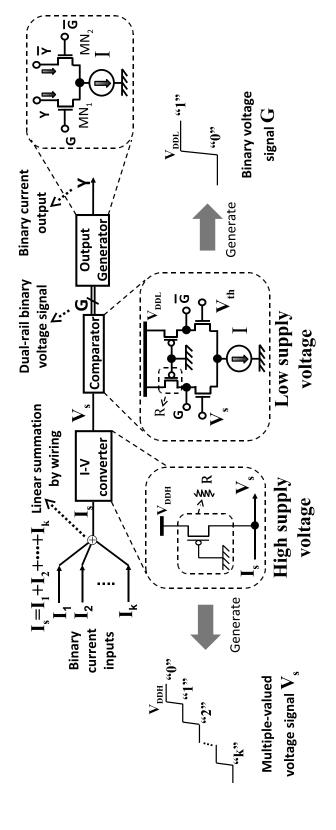

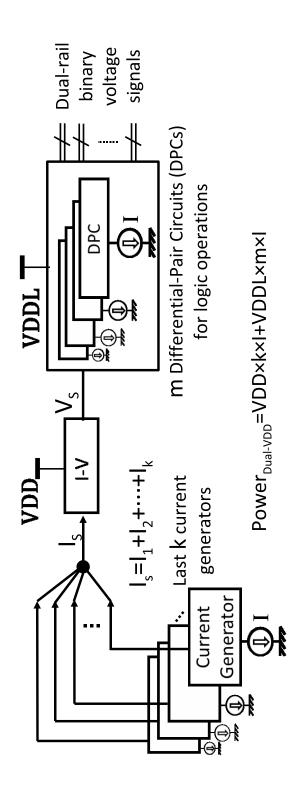

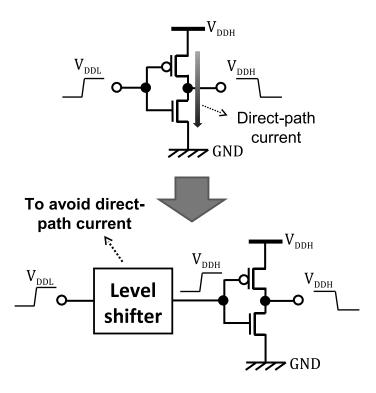

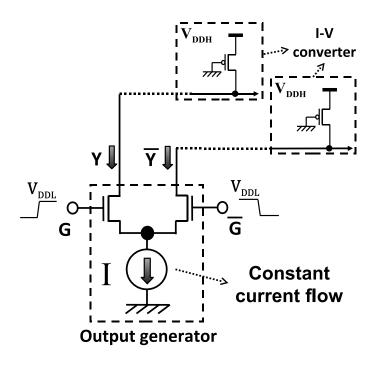

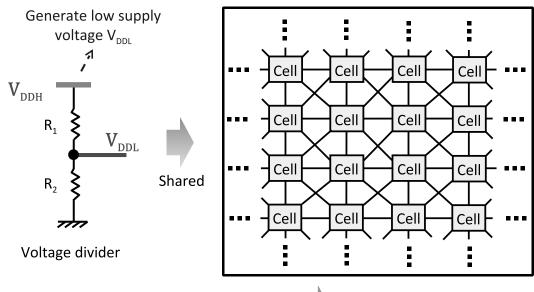

In the dual- $V_{DD}$  multiple-valued source-coupled logic (MVSCL) circuit, a current-voltage (I-V) converter is used to convert a multiple-valued current signal to a multiple-valued voltage signal, and a comparator implemented by the DPC is used to realize a threshold operation. In the I-V converter,  $V_{DDH}$  is required for multiple voltage levels  $V_{DDH}$ ,  $V_{DDH} - \Delta V$ , ...,  $V_{DDH} - K \times \Delta V$  corresponding to multiple logic values "0", "1", ..., "K", respectively. In the DPC with a binary dual-rail voltage output,  $V_{DDL}$  is used for two voltage levels  $V_{DDL} - \Delta V$  and  $V_{DDL}$  corresponding to two logic values "0" and "1", respectively. The speed of the DPC is not decreased by  $V_{DDL}$  because it is independent of the supply voltage [9][10]. Moreover, it is different from the conventional dual- $V_{DD}$  CMOS circuit that level shifters are not necessary to be provided to prevent direct-path currents in the dual- $V_{DD}$  MVSCL circuit, because the current flow in the DPC is fixed by a current source.

The second problem is that the MVFG-RVLSI still has complex switch blocks in comparison with full-custom ICs. In the MVFG-RVLSI using

the 8-NNM shown in Fig. 1.2, each cell composed of a switch block and a logic block is connected to eight adjacent cells[8]. The switch block is not so compact because eight nMOS pass transistors and eight configuration memories are provided at each input/output (I/O) of the cell to realize an eight-near neighborhood data transfer.

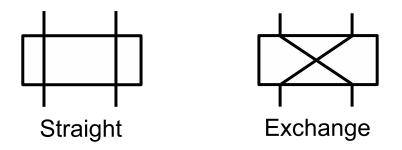

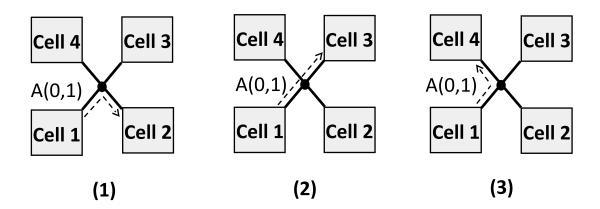

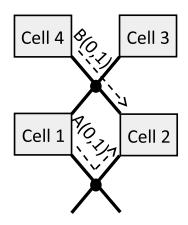

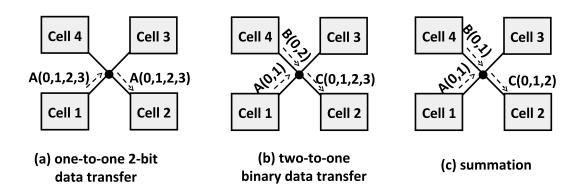

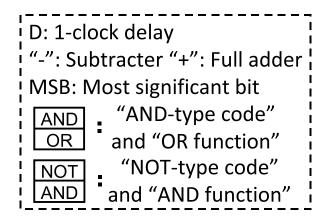

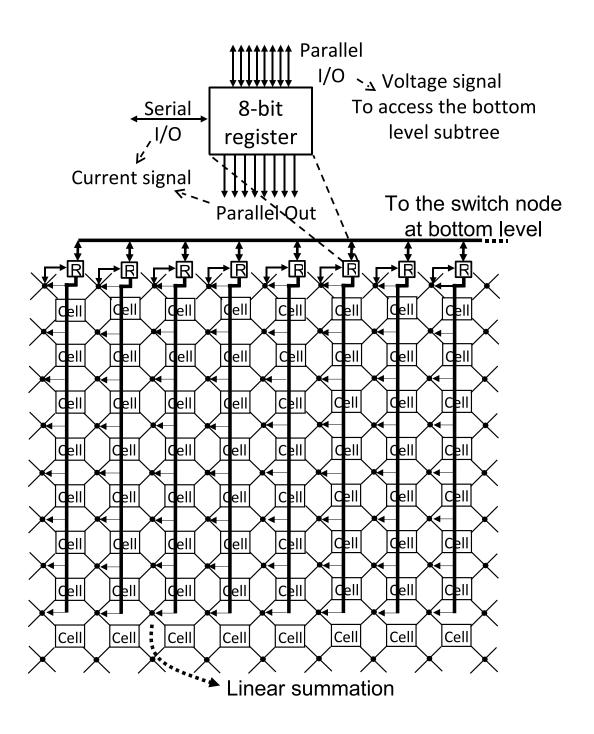

To solve the second problem, Chapter 3 proposes a multiple-valued X-net data transfer shown in Fig. 1.3 for area-efficient switch blocks. An X-net network is more sufficient than the 8-NNM to realize the eight-near neighborhood data transfer[11]. The X-net network is employed for implementing area-efficient switch blocks without decreasing performance. In the X-net network, one cell is connected to four "X" intersections and each "X" intersection is connected to the other three adjacent cells. Therefore, only four nMOS pass transistors and four configuration memories are provided at each I/O of the cell to realize the eight-near neighborhood data transfer. The high utilization of the nMOS pass transistor and the configuration memories leads to the area-efficient switch block. Moreover, a multiple-valued data transfer scheme is proposed to realize the high utilization of the X-net network, where linear summation of current signals transferred between cells can be realized at each "X" intersection[12][13].

The third problem is that it is necessary to use many cells to real-

ize long-distance data transfer by the nearest-neighbor network, which results in low speed and large power consumption.

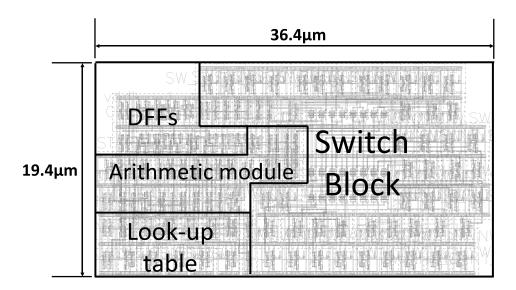

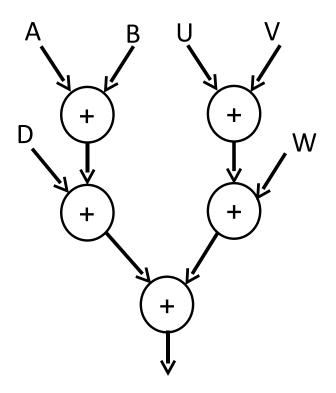

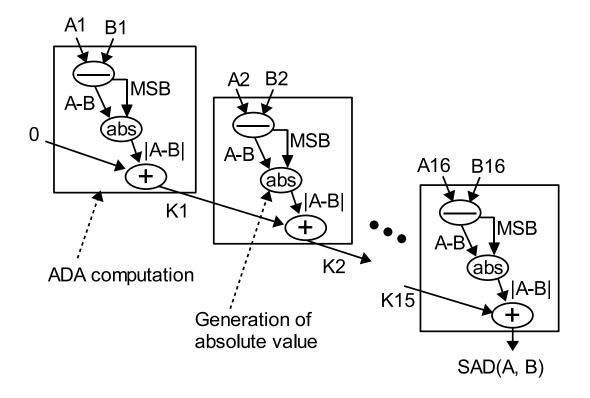

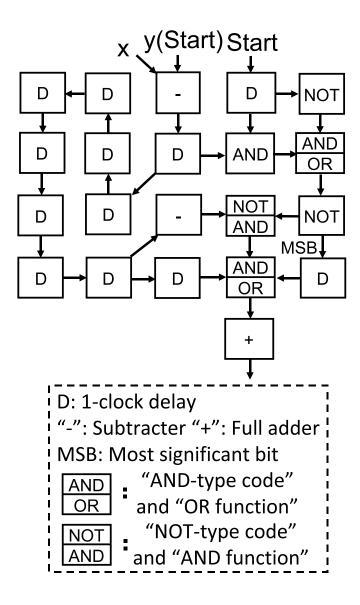

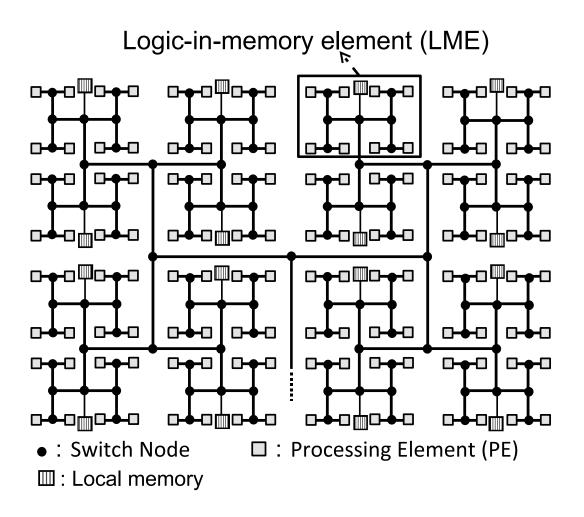

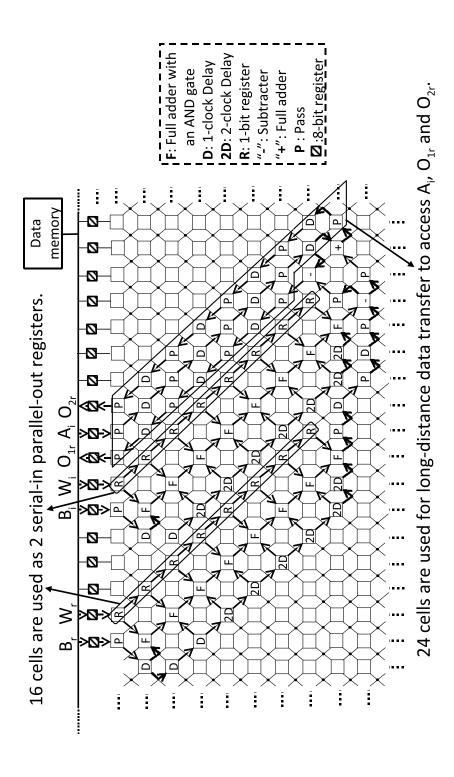

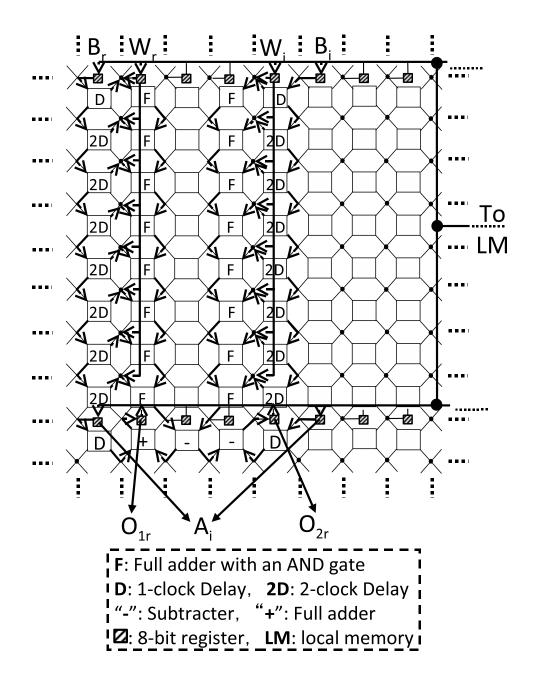

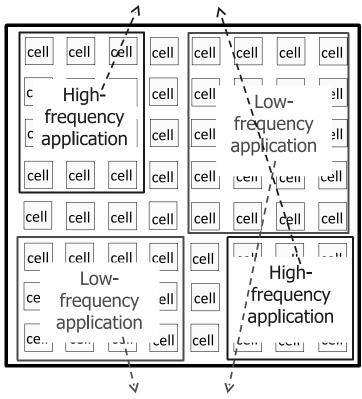

In Chapter 4, to solve the third problem, a global dynamic tree network is employed for high-performance bit-parallel long-distance data transfer. In practical applications such as a sum-of-absolute-difference operation (SAD) [12], the local X-net network is frequently used for inter-cell neighborhood data transfer, and the global dynamic tree network is occasionally used for long-distance data transfer between a cell and a data memory. Therefore, the global dynamic tree network is connected not to each cell, but to multiple-cell blocks composed of many cells. To realize highly parallel memory access, a logic-in-memory architecture is introduced, where data transfer between a local memory and the multiple-cell block can be done in each logic-in-memory element (LME). Moreover, to solve speed problems in comparison with a multiple bus and a crossbar network, pipelined switch nodes are provided to improve data transfer throughput.

## Chapter 2

High-performance multiple-valued logic block using current-source-sharing differential-pair circuits

#### 2.1 Overview

This chapter presents three circuit-level techniques for a high-speed low-power multiple-valued fine-grain logic block.

A binary-controlled current-steering technique is proposed to use a three-level differential-pair circuit for implementing a high-performance arbitrary two-variable binary function without using a binary-to-quaternary converter. A current-source-sharing technique is proposed to improve utilization of current sources for low power consumption. One current source can be shared to implement a logic function and store its result for lowpower current-mode pipeline.

A dual-supply voltage technique is proposed for low-power multiple-valued source-coupled logic circuits without increasing delay. A high supply voltage is used for multiple voltage levels, and a low supply voltage is used for binary voltage levels. In the differential-pair circuits (DPCs) using the low supply voltage, the delay is not increased because it is independent of the supply voltage[9][10].

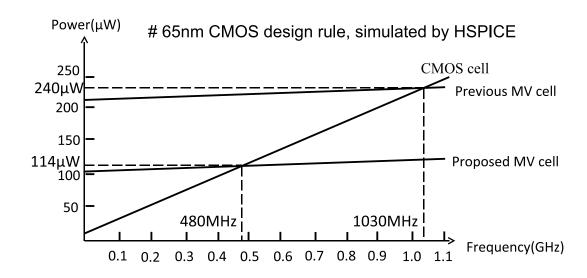

As a result, in comparison with the previous multiple-valued cell, the power consumption and the delay of the proposed multiple-valued cell are reduced to 49% and 72%, respectively, without increasing the area and the configuration memory size.

## 2.2 Review of the multiple-valued fine-grain reconfigurable VLSI

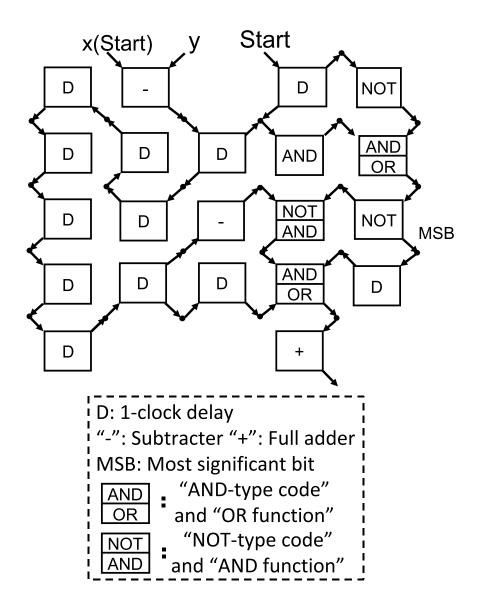

In the multiple-valued fine-grain reconfigurable VLSI (MVFG-RVLSI) using the eight-nearest neighbor mesh network (8-NNM) shown in Fig. 1.2, each cell is composed of a logic block and a switch block, and can be

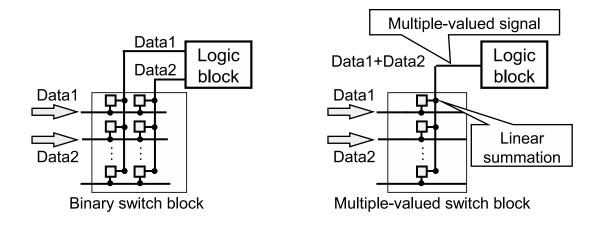

Figure 2.1: Compact multiple-valued switch block

connected to its eight adjacent cells through one-bit switches. Multiple-valued signaling is introduced to implement a compact switch block as shown in Fig. 2.1. In the binary switch block, if there are two binary inputs, 16 one-bit switches are necessary to control data transfer to the logic block. In the multiple-valued switch block, two binary current inputs linearly summed by wiring can be transferred on one line, therefore only eight one-bit switches are used to control data transfer. The complexity of the switch block can be reduced to half by the multiple-valued logic technique.

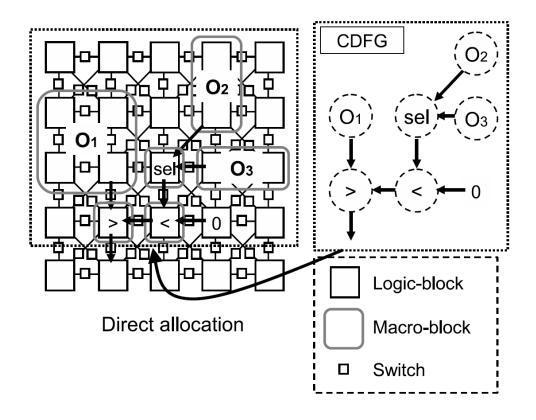

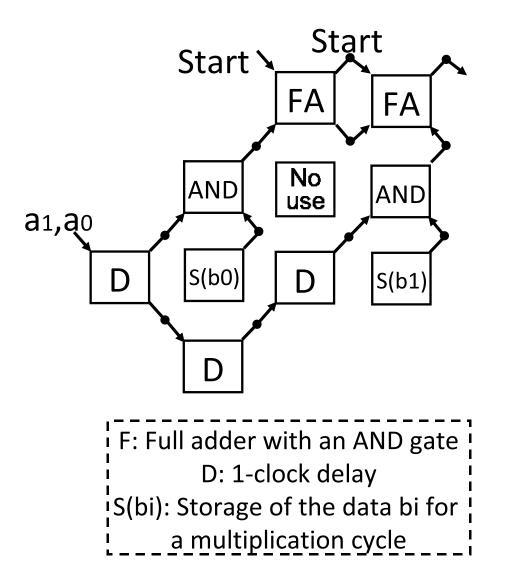

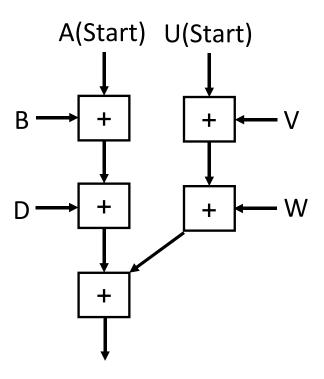

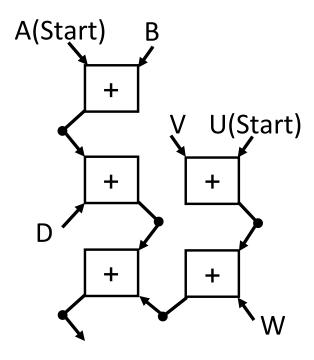

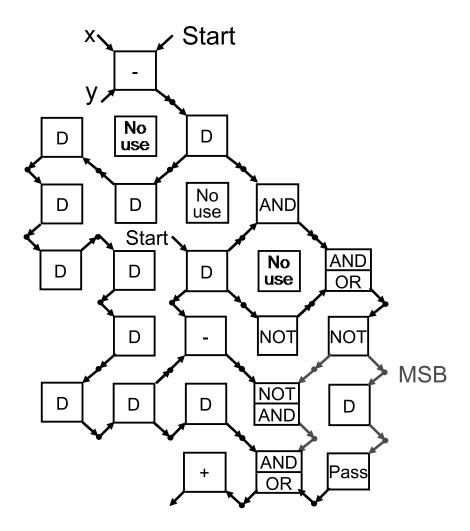

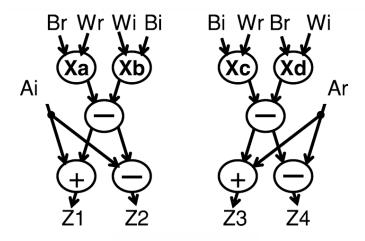

The behavioral description is given by a control/data flow graph. In the direct allocation of the control/data flow graph shown in Fig. 2.2, each node in the control/data flow graph corresponds to a macro-block in the MVFG-RVLSI and each edge corresponds to a data transfer path

Figure 2.2: Direct allocation of a control/data flow graph

between the macro-blocks, where the macro-block consists of multiple cells. The complexity of logical connections between the macro-blocks becomes almost the same as that of the control/data flow graph. The architecture for the localized data transfer can be effectively employed for reducing the complexity of interconnections and delay due to data transfer between cells[14].

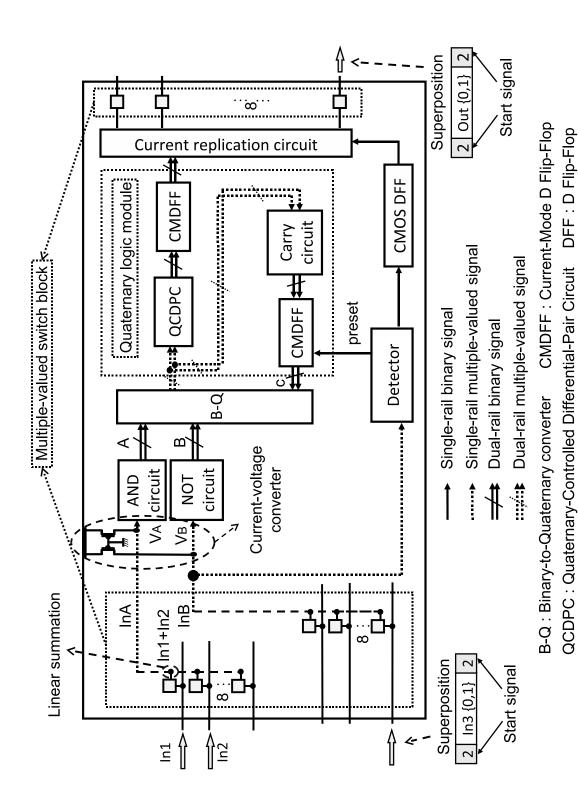

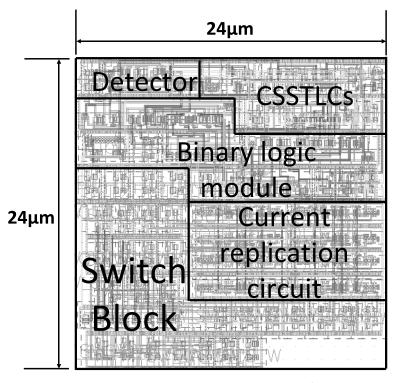

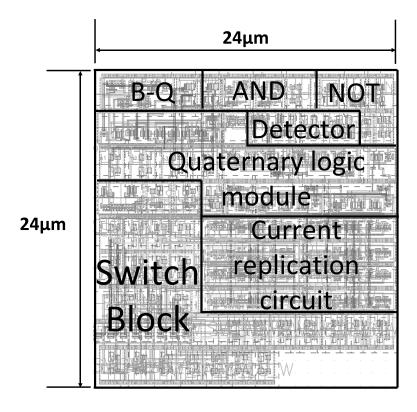

As shown in Fig. 2.3, a multiple-valued cell has been proposed for the MVFG-RVLSI[7]. The cell consists of a multiple-valued switch block,

Figure 2.3: Multiple-valued cell using a quaternary-controlled differential-pair circuit

an AND circuit, a NOT circuit, a binary-to-quaternary converter, a quaternary logic module, and a current replication circuit. The inputs and outputs of the cell are represented by single-rail binary current signals. In the multiple-valued switch block, the binary current inputs In1 and In2 are linearly summed by wiring, so that an input InA of a current-voltage converter becomes a three-valued data. In a bit-serial operation, a start signal indicating a head of a one-word data is required to initialize the D flip-flops used for state memory. Superposition of the data and start signal in a single interconnection is introduced to realize compact switch blocks, where the logic value "2" is defined as the start signal to distinguish from data "0" and "1". Both of the number of interconnections between the cells and the number of switches are reduced to half in comparison with those of a binary representation.

Figure 2.4: Threshold logic circuits

Table 2.1: Programmable operations of the AND circuit (b) AND-type dual-rail code

| (a)_l | Dua   | l-rail code         |  | $\frac{\mathcal{U}_{i}}{\mathcal{U}_{i}}$ | $(x, \overline{x})$ |

|-------|-------|---------------------|--|-------------------------------------------|---------------------|

|       | $V_A$ | $(x, \overline{x})$ |  | <i>V A</i>                                | $\frac{(x,x)}{}$    |

| =     |       | (0, 1)              |  | 0                                         | (0, 1)              |

| _     | 0     | (0, 1)              |  | 1                                         | (0, 1)              |

|       | 1     | (1, 0)              |  |                                           |                     |

| _     |       |                     |  | 2                                         | (1,0)               |

Table 2.2: Programmable operations of the NOT circuit

(a) Dual-rail code

(b) NOT-type dual-rail code

| $V_B$ | $(y, \overline{y})$ | $V_I$ | 3 | $(y, \overline{y})$ |

|-------|---------------------|-------|---|---------------------|

| 0     | (0, 1)              | 0     |   | (1, 0)              |

| 1     | (1, 0)              | 1     |   | (0, 1)              |

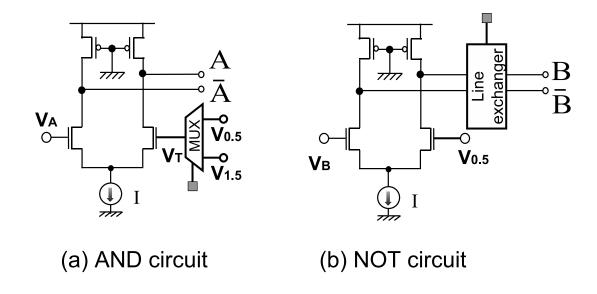

Both the AND circuit and NOT circuit are constructed by a basic one-level differential-pair circuit shown in Fig. 2.4. In the AND circuit, two operations of Table 2.1 can be programmed. The AND-type dual-rail code is used to generate a partial product in a multiplication and the dual-rail code is used in other cases. In the NOT circuit, two operations of Table 2.2 can be programmed. The NOT-type dual-rail code is used to convert a subtrahend to a 2's complement number in a subtraction and the dual-rail code is used in other cases.

In the quaternary logic module composed of the quaternary-controlled differential-pair circuit, a quaternary-controlled carry circuit and two current-mode D-flip-flops, an arbitrary 2-variable binary function can be realized, and a bit-serial adder can be implemented. However, the binary-to-quaternary converter is required to convert the dual-rail binary voltage signals into a dual-rail quaternary voltage signal, which results in large power consumption and low speed. Also, the quaternary-controlled differential-pair circuit and the quaternary-controlled carry circuit are not so fast due to the small voltage difference in the gate inputs. To overcome the problems, I introduce the binary-controlled differential-pair circuits to implement the high-performance low-power arithmetic logic operations without using the binary-to-quaternary converter.

Also, the current-mode D-flip-flop composed of two current-mode D-latches is used as a register for the bit-serial pipelined operation. To reduce the power consumption of the register, the current-source sharing technique between a series-gating differential-pair circuit and a current-mode D-latch is introduced.

### 2.3 Binary-controlled current-steering technique

#### 2.3.1 Review of the MOS current-mode logic

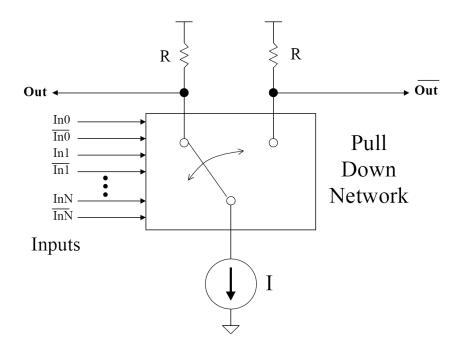

In the MVFG-RVLSI, MOS current-mode logic (MCML) is used to perform arithmetic logic operations. The MCML is a differential logic style, and in general consists of three parts which include a load resistor, the pull-down network (PDN) and a current source shown in Fig. 2.5[9].

The load resistor R is pMOS device with fixed gate voltage and is designed to be operated in triode (linear) region in order to model a resistor. The PDN is implemented with standard nMOS differential pairs which are operated in saturation region controlled by dual-rail binary voltage inputs. The current source is an nMOS device with a fixed gate voltage and is designed to be operated in the saturation region to produce relatively constant current.

The MCML does not provide a rail-to-rail output swing. The MCML

Figure 2.5: General MOS current-mode logic structure

circuits are faster than other logic families, because it uses nMOS transistors only. Due to its differential nature, it is highly immune to common mode noise. It has almost flat power curve over a wide range of frequency as opposed to other logic styles where power consumption increases directly with frequency. Therefore at very high frequencies its power consumption is lower than other logic styles. This makes it a good choice for high-speed and low-power integrated circuit design.

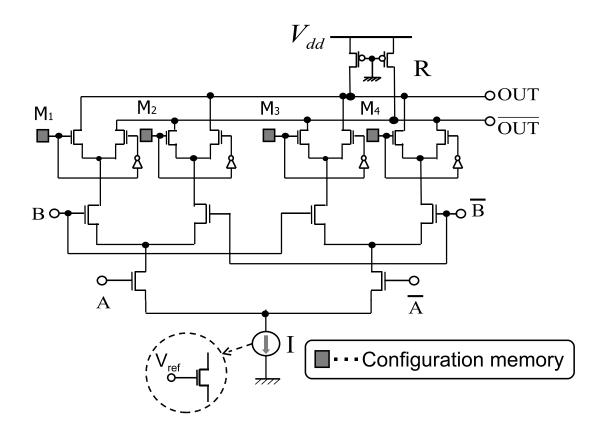

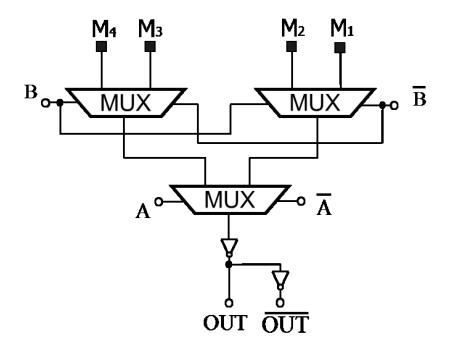

Figure 2.6: Binary-controlled differential-pair circuit

#### 2.3.2 Design of the binary-controlled differential-pair circuit

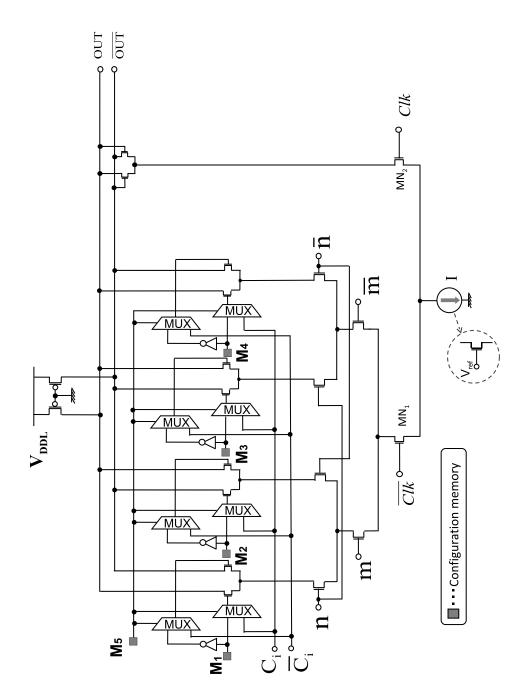

As shown in Fig. 2.6, the binary-controlled differential-pair circuit is introduced to improve the performance as well as to reduce the power consumption. The dual-rail binary voltage signals generated by the AND circuit and the NOT circuit can be directly connected to the binary-controlled differential-pair circuit without using the binary-to-quaternary converter.

Only one current source constructed by an nMOS transistor in the

saturation region is necessary to drive the binary-controlled differential-pair circuit, which makes power consumption low. The current I produced by the current source is steered into one of the branches in the binary-controlled differential-pair circuit according to the dual-rail binary voltage inputs. The two values of a dual-rail output are  $V_{dd}$  and  $V_{dd}$ - $\Delta V$ , where  $\Delta V$  is the output voltage swing and is equals to  $I \times R$ . R is the equivalent resistance of the pMOS load transistor.

Configuration memories  $M_1$ ,  $M_2$ ,  $M_3$  and  $M_4$  are programmed to steer the current I flow through the third-level differential pairs for an arbitrary two-variable binary function shown in Table 2.3. The values of  $M_1$ ,  $M_2$ ,  $M_3$  and  $M_4$  and the corresponding function are shown in Table 2.4.

Table 2.3: Arbitrary two-variable binary function

| A | В | $f_0$ | $f_1$ | $f_2$ | $f_3$ | $f_4$ | $f_5$ | $f_6$ | $f_7$ | $f_8$ | $f_9$ | $f_{10}$ | $f_{11}$ | $f_{12}$ | $f_{13}$ | $f_{14}$ | $f_{15}$ |

|---|---|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|----------|----------|----------|----------|----------|----------|

| 0 | 0 | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 1        | 1        | 1        | 1        | 1        | 1        |

| 0 | 1 | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 1     | 0     | 0     | 0        | 0        | 1        | 1        | 1        | 1        |

| 1 | 0 | 0     | 0     | 1     | 1     | 0     | 0     | 1     | 1     | 0     | 0     | 1        | 1        | 0        | 0        | 1        | 1        |

| 1 | 1 | 0     | 1     | 0     | 1     | 0     | 1     | 0     | 1     | 0     | 1     | 0        | 1        | 0        | 1        | 0        | 1        |

Table 2.4: Programming of an arbitrary two-variable binary function

| Function | $M_1$ | $M_2$ | $M_3$ | $M_4$ |

|----------|-------|-------|-------|-------|

| $f_0$    | 0     | 1     | 1     | 0     |

| $f_1$    | 0     | 1     | 1     | 1     |

| $f_2$    | 0     | 1     | 0     | 0     |

| $f_3$    | 0     | 1     | 0     | 1     |

| $f_4$    | 0     | 0     | 1     | 0     |

| $f_5$    | 0     | 0     | 1     | 1     |

| $f_6$    | 0     | 0     | 0     | 0     |

| $f_7$    | 0     | 0     | 0     | 1     |

| $f_8$    | 1     | 1     | 1     | 0     |

| $f_9$    | 1     | 1     | 1     | 1     |

| $f_{10}$ | 1     | 1     | 0     | 0     |

| $f_{11}$ | 1     | 1     | 0     | 1     |

| $f_{12}$ | 1     | 0     | 1     | 0     |

| $f_{13}$ | 1     | 0     | 1     | 1     |

| $f_{14}$ | 1     | 0     | 0     | 0     |

| $f_{15}$ | 1     | 0     | 0     | 1     |

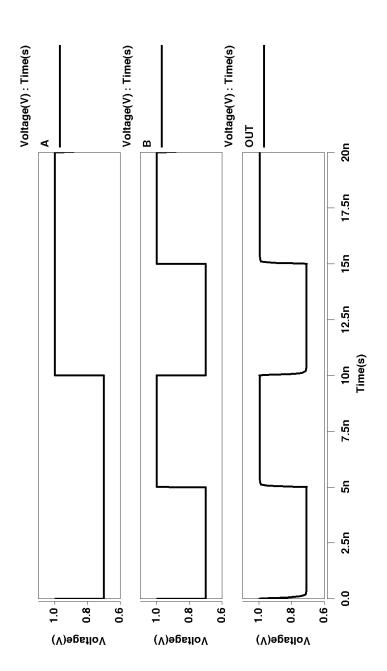

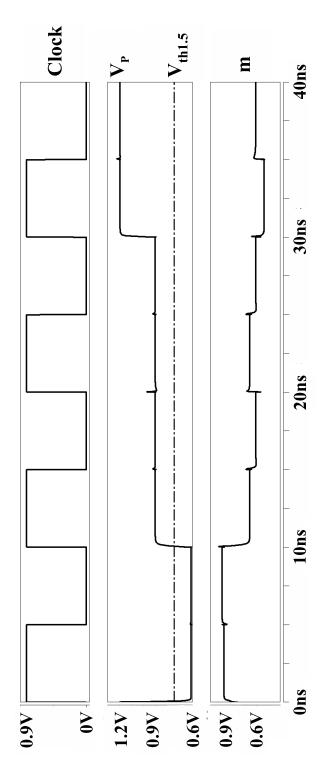

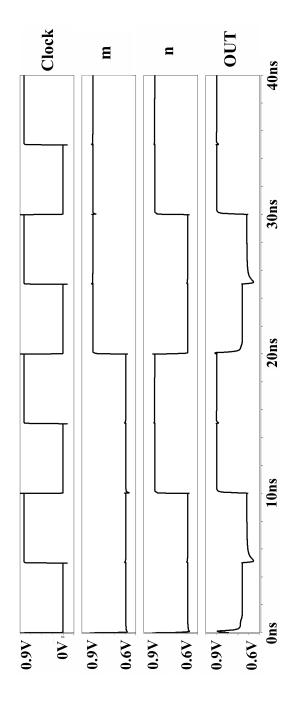

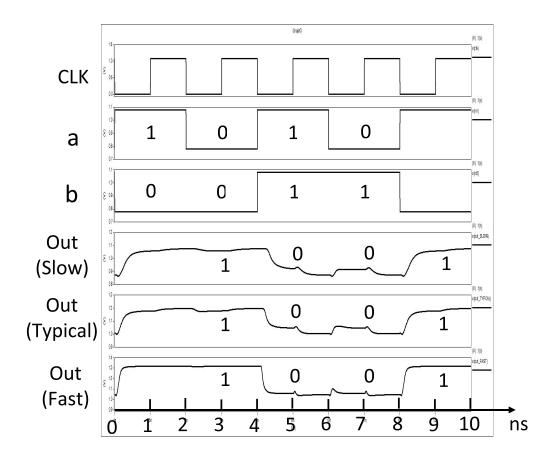

Figure 2.7 shows the input and output waveforms of the binary-controlled differential-pair circuit which is programmed to implement the two-

Figure 2.7: Input and output waveforms of the binary-controlled differential-pair circuit (The two-variable binary function  $f_5$  in

Table 2.3 is implemented)

variable binary function  $f_5$  in Table 2.3. The configuration memories  $M_1, M_2, M_3$  and  $M_4$  are configured as "0", "0", "1" and "1", respectively. If the input data (A,B) is (0,1) or (1,1), the OUT becomes 1.0V corresponding to the logic value "1". On the other hand, if the input data (A,B) is (0,0) or (1,0), the OUT becomes 0.7V corresponding to the logic value "0".

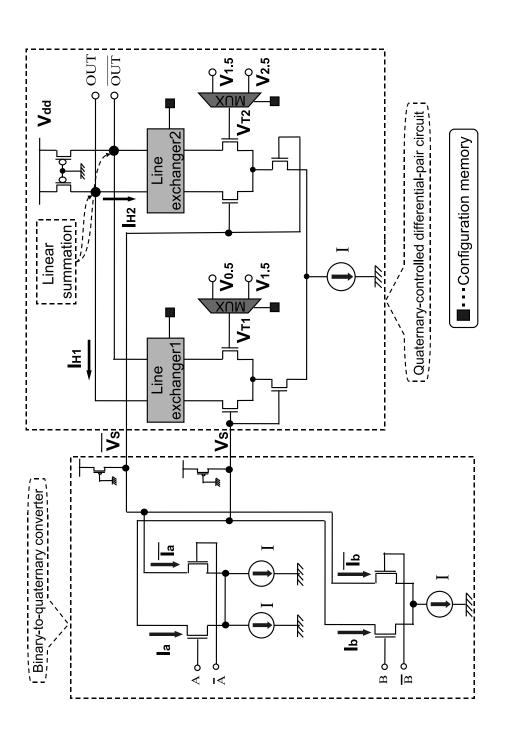

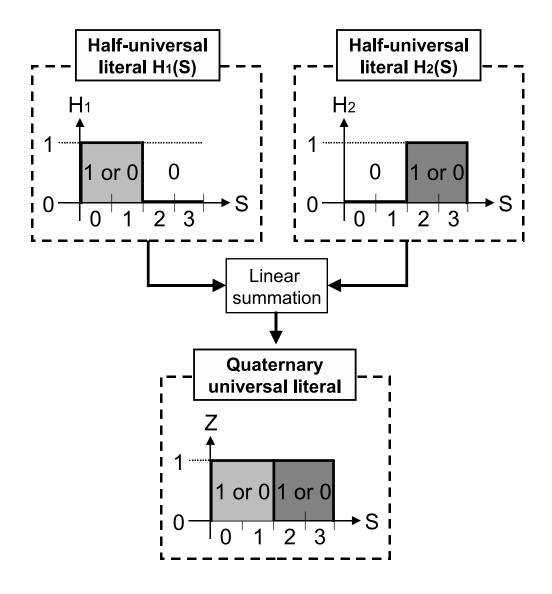

Noise margins represent "safety margins" that prevent the digital circuit from producing erroneous outputs in the presence of noisy inputs [15][16]. Figure 2.8 shows the previous 2-variable binary function circuit composed of the binary-to-quaternary converter and the quaternary-controlled differential-pair circuit. The quaternary-controlled differential-pair circuit is used to implement the quaternary universal literal realized by linear summation of two half-universal liters  $H_1(S)$  and  $H_2(S)$  shown in Fig. 2.9. In the quaternary-controlled differential-pair circuit, a complementary quaternary signal  $(V_S, \overline{V_S})$  and fixed reference voltages  $V_{T1}$  and  $V_{T2}$  are applied, which results in the small voltage difference of the dual-rail output as shown in Fig. 2.10. The noise margin of the quaternary-controlled differential-pair circuit is not so large, due to the small output difference.

Figure 2.8: Two-variable binary function circuit composed of the binary-to-quaternary converter and the quaternary-controlled differential-pair circuit

Figure 2.9: Design of a quaternary universal literal using two half-universal literals

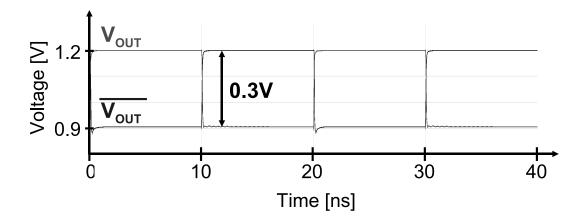

In contrast, the dual-rail binary voltage signals generated by the AND circuit and the NOT circuit can be directly connected to the proposed binary-controlled differential-pair circuit. Therefore, the output difference becomes larger than that of the quaternary-controlled differential-pair circuit as shown in Fig. 2.11, which increases the noise margin. The

quaternary-controlled differential-pair circuit and the binary-controlled differential-pair circuit are programmed as inverters to measure noise margins. Noise margins are defined for high and low input levels use the following equations:

$$High \ noise \ margin: \ NM_H = V_{OH} - V_{IH}$$

(2.1)

$Low \ noise \ margin: \ NM_L = V_{IL} - V_{OL}$

where  $V_{OH}$  is the minimum allowable output voltage that can be recognized as logic "1",  $V_{OL}$  is the maximum allowable output voltage that can be recognized as logic "0",  $V_{IH}$  is the minimum allowable input voltage that can be recognized as logic "1", and  $V_{IL}$  is the maximum allowable input voltage that can be recognized as logic "0".

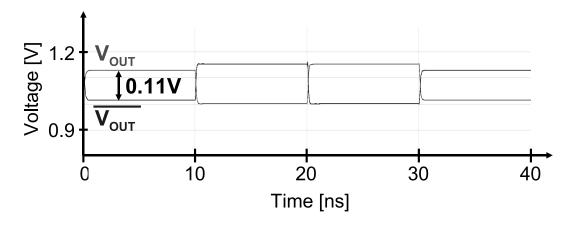

Figure 2.10: Dual-rail output waveform of the quaternary-controlled differential-pair circuit

Figure 2.11: Dual-rail output waveform of the binary-controlled differential-pair circuit

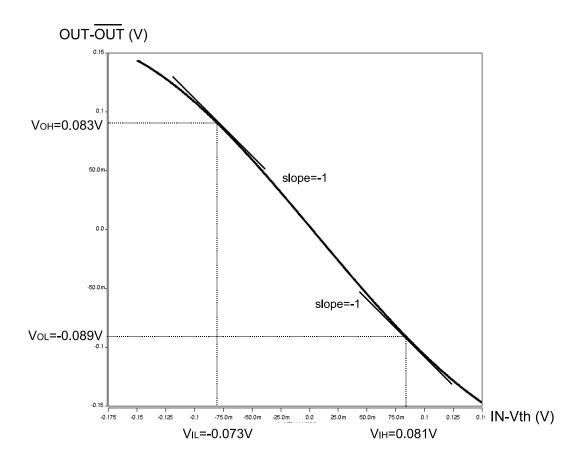

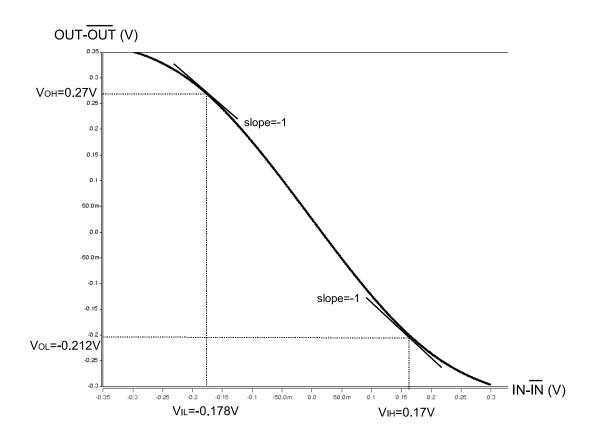

Figure 2.12 shows the voltage transfer characteristic of the quaternary-controlled differential-pair circuit.  $V_{OH}$ ,  $V_{OL}$ ,  $V_{IH}$  and  $V_{IL}$  are 0.083V, -0.089V, 0.081V and -0.073V, respectively. Therefore, the  $NM_H$  and  $NM_L$  become 0.002V and 0.016V, respectively. Figure 2.13 shows the voltage transfer characteristic of the binary-controlled differential-pair circuit.  $V_{OH}$ ,  $V_{OL}$ ,  $V_{IH}$  and  $V_{IL}$  are 0.27V, -0.212V, 0.17V and -0.178V, respectively. Therefore, the  $NM_H$  and  $NM_L$  become 0.1V and 0.034V, respectively. The  $NM_H$  and  $NM_L$  in the binary-controlled differential-pair circuit are greatly increased in comparison with the quaternary-controlled differential-pair circuit.

Figure 2.12: Output voltage versus input voltage in the quaternary-controlled differential-pair circuit

Figure 2.13: Output voltage versus input voltage in the binary-controlled differential-pair circuit

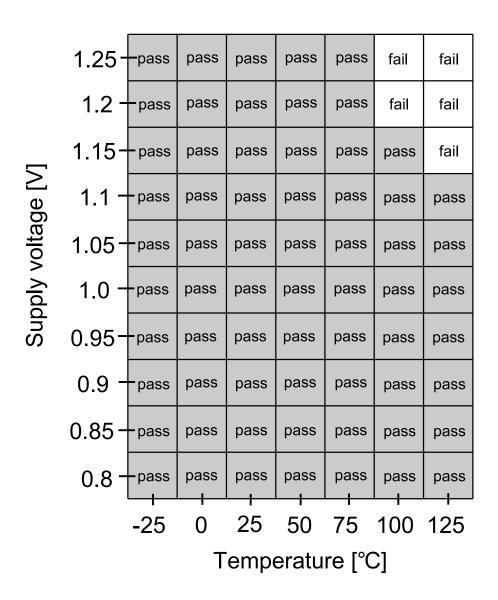

Figure 2.14: Shmoo plot of the binary-controlled differential-pair circuit under threshold-voltage, temperature, and supply voltage variations

Figure 2.14 shows a shmoo plot of the binary-controlled differential-pair circuit under threshold-voltage, temperature, and supply-voltage variations. The temperature and supply voltage vary from -25°C to 125°C and from 0.8V to 1.25V, respectively, and are set up for simulation in the binary-controlled differential-pair circuit uniformly. The range of threshold-voltage variation is  $\pm 10\%$  of the threshold voltage, and is set up for simulation in each transistor randomly. As a result, the binary-controlled differential-pair circuit can work correctly from -25°C to 75°C and from 0.8V to 1.25 under  $\pm 10\%$  threshold-voltage variation. The lower limit of the supply voltage is 0.6V.

#### 2.3.3 Evaluation of the binary-controlled differential-pair circuit

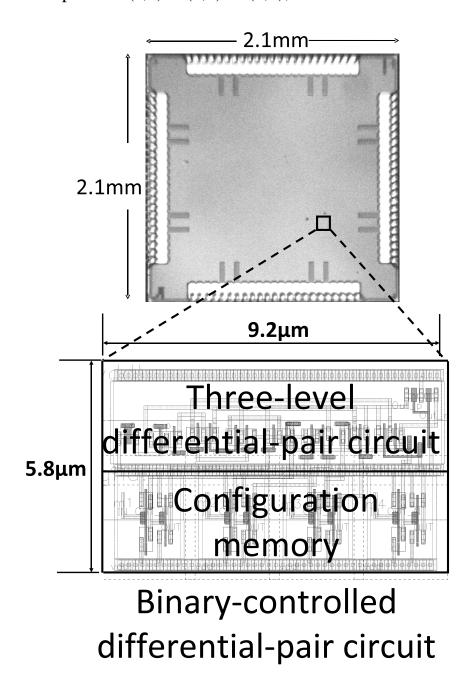

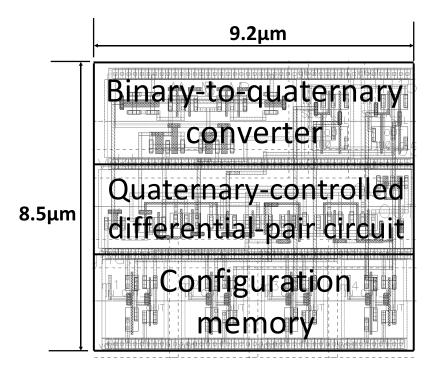

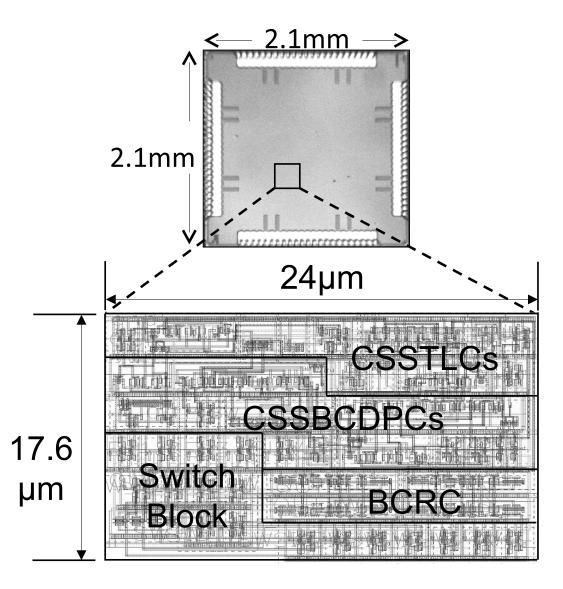

The binary-controlled differential-pair circuit is fabricated using a 65 nm CMOS process. The supply voltage is 1.2V. Figure 2.15 shows the chip photomicrograph and the layout of the binary-controlled differential-pair circuit. The area is  $53.36\mu m^2$ .

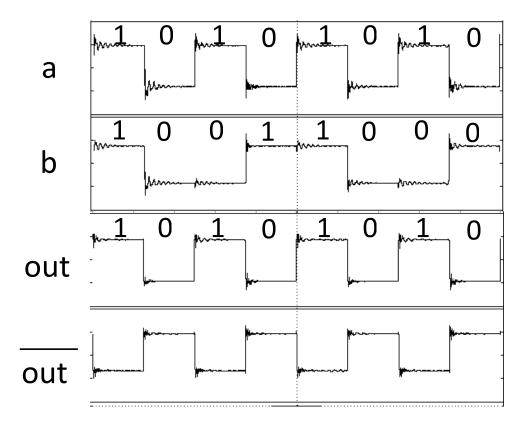

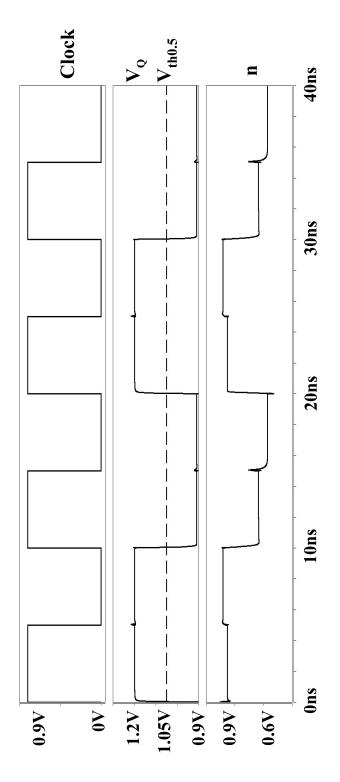

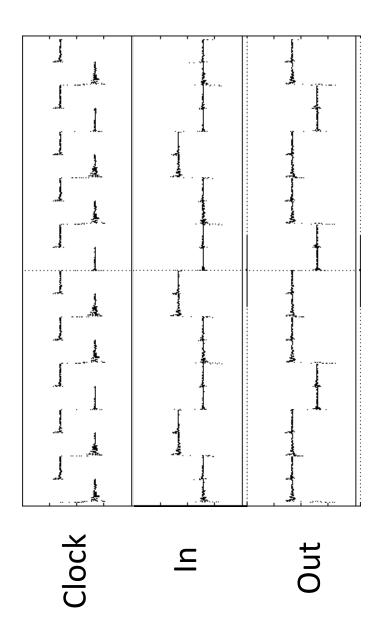

Figure 2.16 shows the inputs and outputs waveforms of the binary-controlled differential-pair circuit in the chip. The circuit is programmed to implement the two-variable binary function  $f_3$  in Table 2.3. The values of  $M_1, M_2, M_3$  and  $M_4$  are "0", "1", "0" and "1", respectively. If the input data (a,b) is (0,0) or (0,1), the OUT becomes "0". On the other

hand, if the input data (a,b) is (1,0) or (1,1), the OUT becomes "1".

Figure 2.15: Chip photomicrograph and the layout of the binary-controlled differential-pair circuit

Figure 2.16: Inputs and outputs waveforms of the binary-controlled differential-pair circuit in the chip

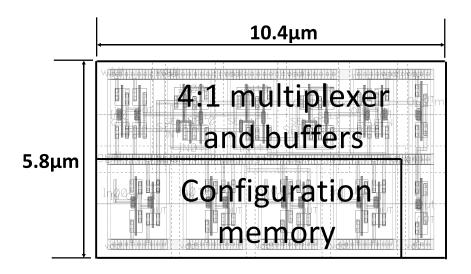

The evaluation of the binary-controlled differential-pair circuit is done based on HSPICE simulation using a 65 nm CMOS design rule. The binary-controlled differential-pair circuit is compared with the previous two-variable binary function circuit shown in Fig. 2.8, and with the two-input LUT shown in Fig. 2.17. The LUT is used in the typical commercially available FPGAs as function generators. An n-input LUT can be used to implement an arbitrary n-variable binary function [1][17].

Figure 2.17: Two-input LUT

Figure 2.18: Layout of the previous two-variable binary function circuit

Figure 2.19: Layout of the two-input LUT

Table 2.5: Comparison of the two-variable binary function circuits

|                            | QCDPC with      | Two-input       | BCDPC           |  |

|----------------------------|-----------------|-----------------|-----------------|--|

|                            | a B-Q converter | LUT             | всрес           |  |

| Supply voltage             | 1.2V            | 1.2V            | 1.0V            |  |

| Delay                      | 0.15ns          | 0.06 ns         | 0.05 ns         |  |

| Area                       | $78.2 \mu m^2$  | $60.32 \mu m^2$ | $53.36 \mu m^2$ |  |

| Configuration memory count | 4               | 4               | 4               |  |

QCDPC: Quaternary-Controlled Differential-Pair Circuit

B-Q converter: Binary-to-Quaternary converter

BCDPC: Binary-Controlled Differential-Pair Circuit

Figures 2.18 and 2.19 show the layouts of the previous two-variable binary function circuit and the two-input LUT, respectively. The areas of the circuits are  $78.2 \mu m^2$  and  $60.32 \mu m^2$ , respectively.

Table 2.5 shows the comparison results. The area and the delay of the proposed binary-controlled differential-pair circuit are reduced to 68% and 33%, respectively, in comparison with those of the previous two-variable binary function circuit. The area and the delay become 88% and 83% of those of the 2-input LUT, respectively.

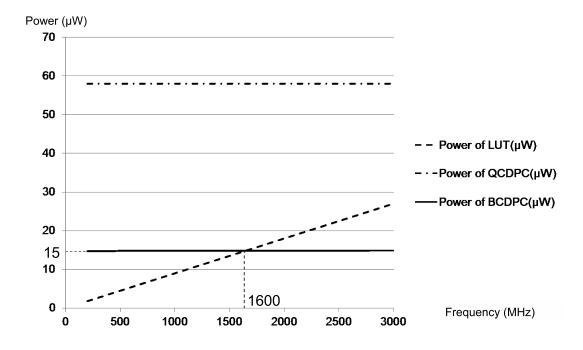

Figure 2.20: Power consumption versus operating frequency in the two-variable binary function circuits

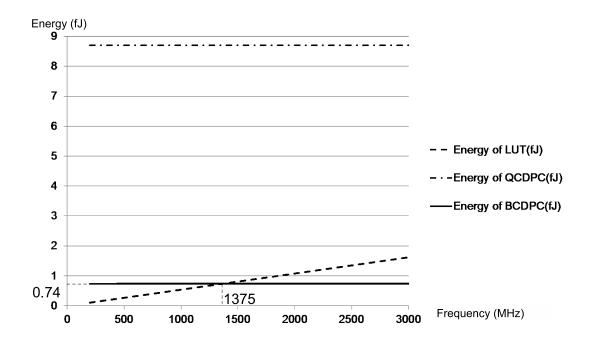

Figure 2.21: Energy consumption versus operating frequency in the two-variable binary function circuits

Figure 2.20 shows the characteristics of power consumption versus operating frequency in the two-variable binary function circuits. The power consumptions of the previous two-variable binary function circuit and the binary-controlled differential-pair circuit are almost constant and equal to  $58\mu W$  and  $15\mu W$ , respectively, when the operating frequency increases. The binary-controlled differential-pair circuit has lower power consumption than the two-input LUT when the operating frequency is more than 1.6GHz.

Figure 2.21 shows the characteristics of energy consumption versus operating frequency in the two-variable binary function circuits which are used to implement  $f_5$  in Table 2.3. The energy consumptions of the previous two-variable binary function circuit and the binary-controlled differential-pair circuit are almost constant and equal to 8.7fJ and 0.74fJ, respectively, when the operating frequency increases. The binary-controlled differential-pair circuit has lower energy consumption than the two-input LUT when the operating frequency is more than 1.375GHz.

The power consumption and energy consumption of the binary-controlled differential-pair circuit are dramatically reduced in comparison with the previous two-variable binary function circuit. Also, the binary-controlled differential-pair circuit is suitable for high-frequency operations in comparison with the two-input LUT.

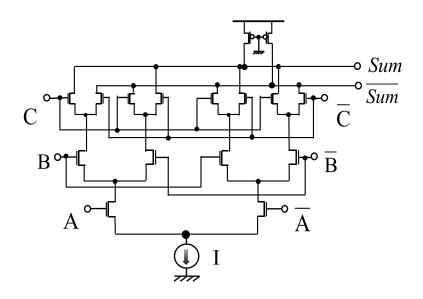

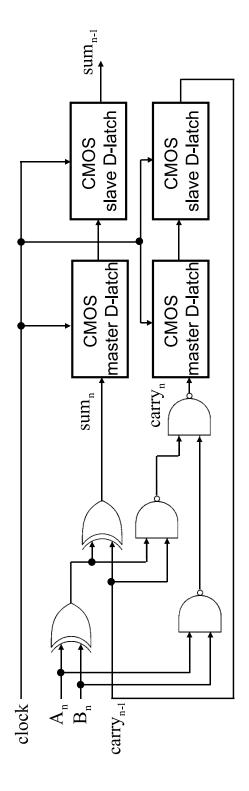

Figure 2.22 shows a current-mode sum circuit and a current-mode carry circuit that construct a full adder in binary current-mode logic[9]. Similar to the binary-controlled differential-pair circuit, either the sum circuit or the carry circuit is constructed by a three-level differential-pair circuit.

### Current-mode sum circuit

## Current-mode carry circuit

Figure 2.22: Current-mode full-adder circuit

Figure 2.23: Sum-type binary-controlled differential-pair circuit

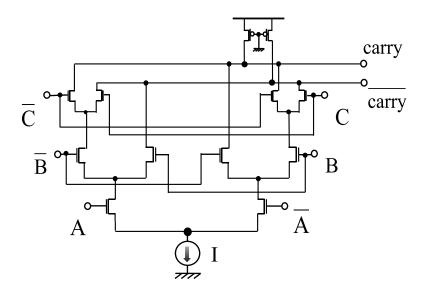

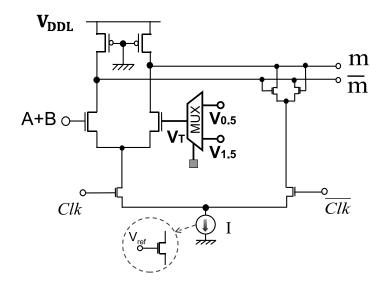

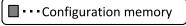

Therefore, I can share the binary-controlled differential-pair circuit and the current-mode sum (carry) circuit using multiplexers which are controlled by a configuration memory  $M_5$  as shown in Fig. 2.23 (Fig. 2.24). A sum (carry)-type binary-controlled differential-pair circuit can be used to implement an arbitrary two-variable binary function or generate the full-adder sum (carry). An arbitrary two-variable binary function

can be implemented, if multiplexers are used to switch configuration memories  $M_1, M_2, M_3$  and  $M_4$  as the inputs of the third-level differential pairs. The full-adder sum (carry) can be generated, if the multiplexers are used to switch a carry signal  $(c, \overline{c})$  as the input of the third-level differential pairs.

Figure 2.24: Carry-type binary-controlled differential-pair circuit

#### 2.4 Current-source sharing technique

#### 2.4.1 Design of the current-source-sharing differential-pair circuit

DPC: Differential-Pair Circuit

Figure 2.25: Current-source sharing technique in differential-pair circuits

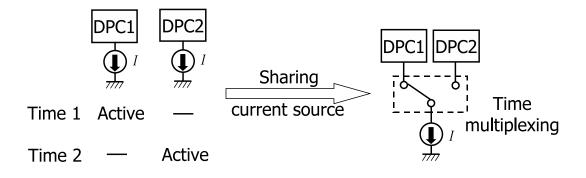

The current-source sharing technique is proposed to improve the utilization of the current sources to implement low-power current-mode logic circuits. If only one of the differential-pair circuits is active at a time, one current source can be shared to drive the differential-pair circuits by time multiplexing, as shown in Fig. 2.25 [8].

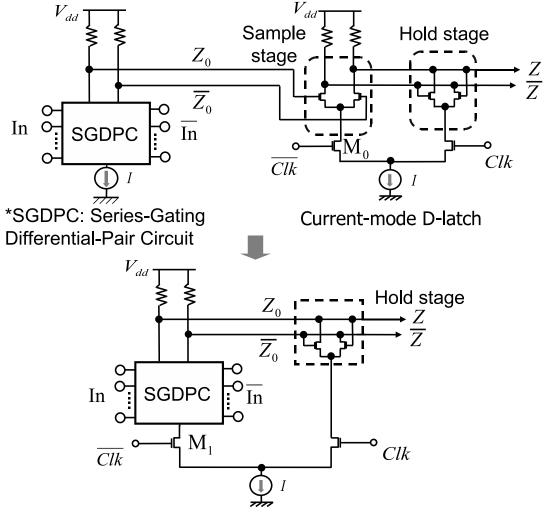

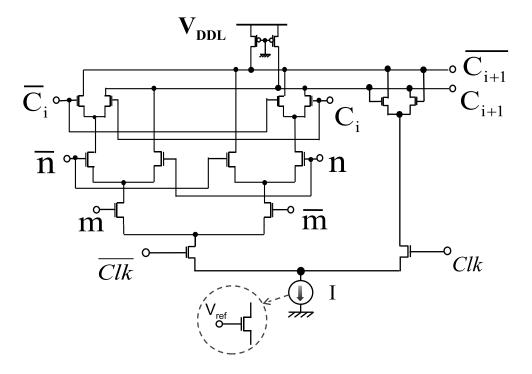

Figure 2.26 shows the current-source sharing between a series-gating differential-pair circuit and a current-mode D-latch. The current-mode D-latch consists of a current source, a sample stage and a hold stage[9][18]. A complementary clock signal  $(Clk, \overline{Clk})$  is used to steer the current I produced by the current source. The sample stage implemented by two

nMOS transistors is used to sample the logic function results  $Z_0$  and  $\overline{Z_0}$ , whereas the hold stage implemented by two cross-coupled nMOS transistors is used to store that data.

In the current-mode D-latch, if Clk is low, the hold stage is inactive and the sample stage is turned "ON" to sample the  $Z_0$  and  $\overline{Z_0}$ . To implement the same operation,  $\overline{Clk}$  can be used to turn "ON" the current source of the series-gating differential-pair circuit to generate the  $Z_0$  and  $\overline{Z_0}$ . In that case, the current source of the current-mode D-latch is not useful to drive the sample stage to sample the  $Z_0$  and  $\overline{Z_0}$ . On the other hand, if Clk is high, the hold stage is active and the sample stage is cut off. Therefore, the  $Z_0$  and  $\overline{Z_0}$  are not sampled, and the current source of the series-gating differential-pair circuit is not useful to generate the  $Z_0$  and  $\overline{Z_0}$ . As a result, one current source can be shared to drive a current-source-sharing differential-pair circuit to implement a logic function and store its result. Also, the delay can be reduced because the sample stage in the current-mode D-latch is omitted by the current-source sharing technique.

Current-source-sharing differential-pair circuit

Figure 2.26: Current-source sharing technique between a series-gating differential-pair circuit and a current-mode D-latch

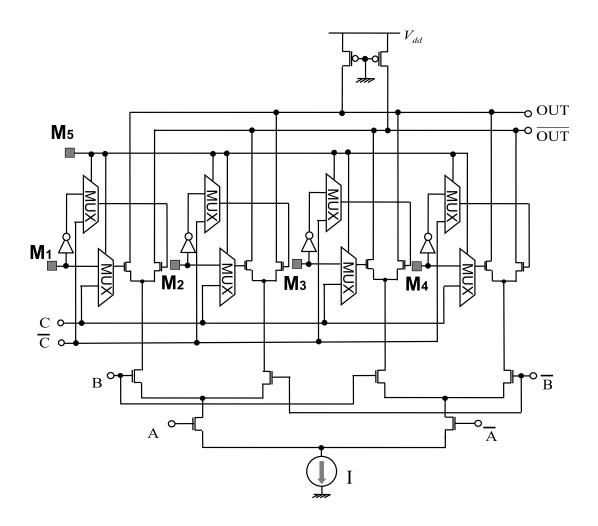

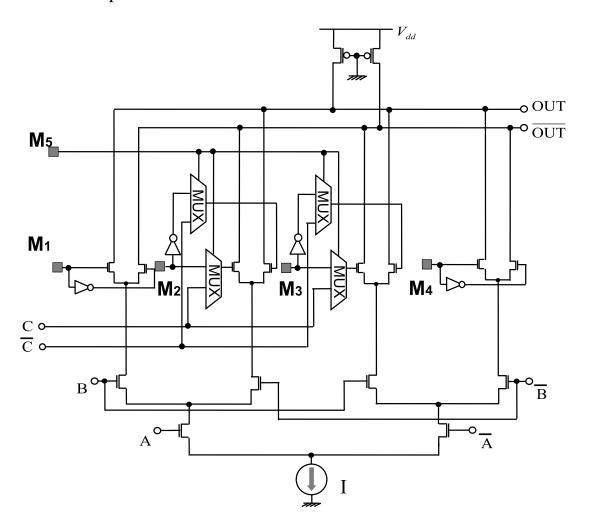

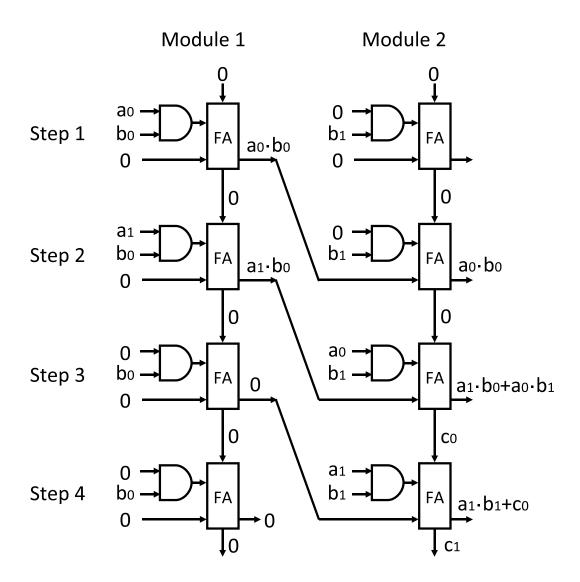

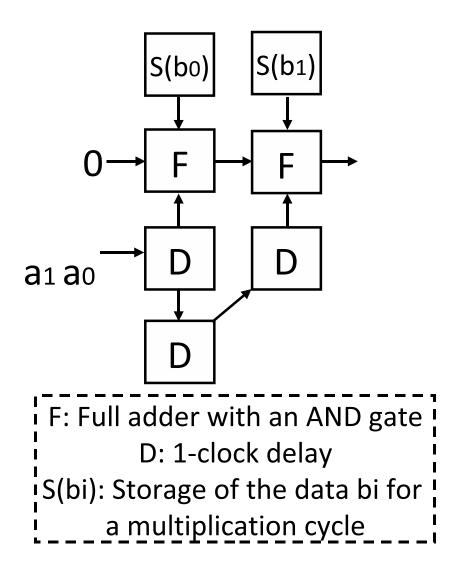

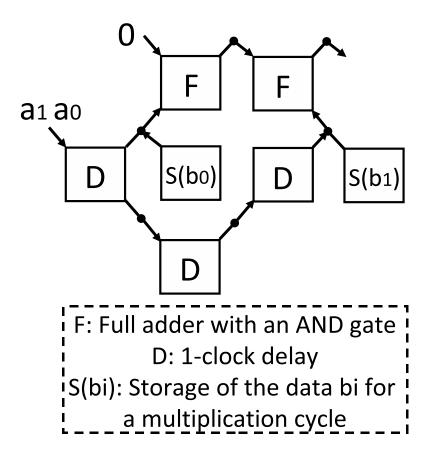

To demonstrate the advantage of the current-source sharing technique, I compare the performance of a current-source-sharing bit-serial adder shown in Fig. 2.27 with those of the current-mode bit-serial adder shown in Fig. 2.28 and the CMOS bit-serial adder shown in Fig. 2.29 based on HSPICE simulation using a 65 nm CMOS design rule.

Figure 2.27: Design of the current-source-sharing bit-serial adder

Figure 2.28: Design of the current-mode bit-serial adder

Figure 2.29: Design of the CMOS bit-serial adder

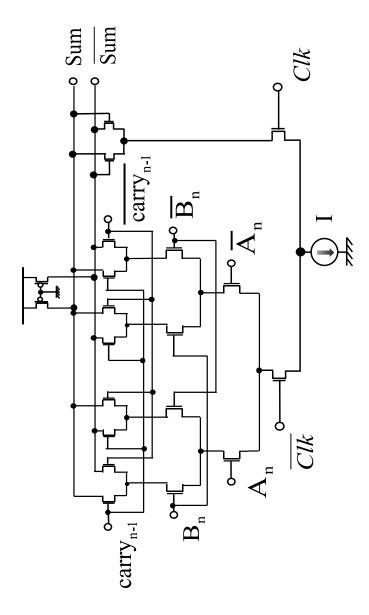

Figure 2.30: Current-source-sharing sum circuit

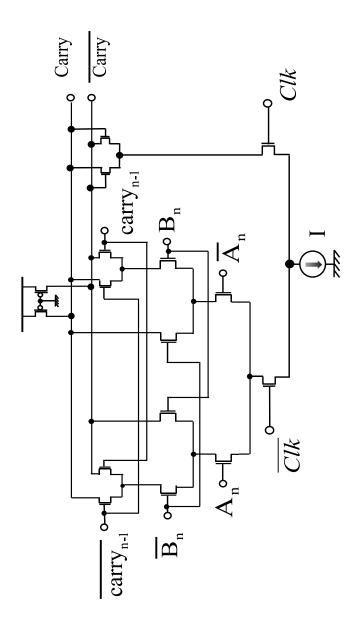

Figure 2.31: Current-source-sharing carry circuit

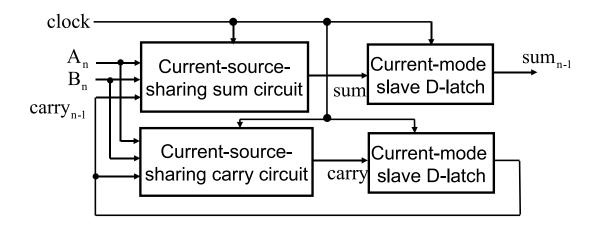

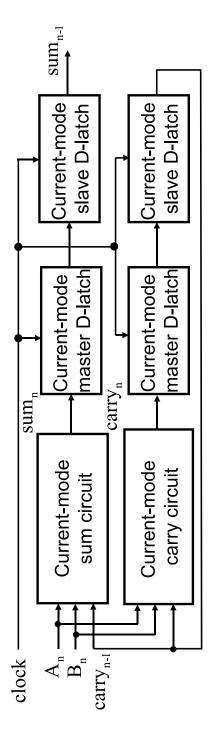

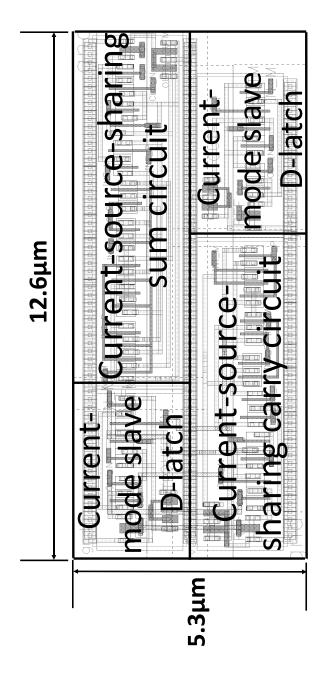

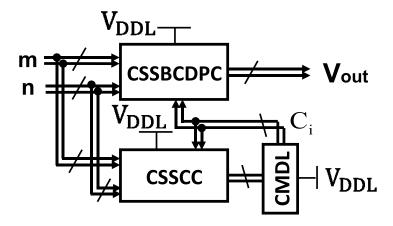

The current-mode bit-serial adder consists of the current-mode sum circuit, the current-mode carry circuit shown in Fig. 2.22, two current-mode master D-latches and two current-mode slave D-latches. The current-source-sharing bit-serial adder consists of a current-source-sharing sum circuit shown in Fig. 2.30, a current-source-sharing carry circuit shown in Fig. 2.31 and two current-mode slave D-latches.

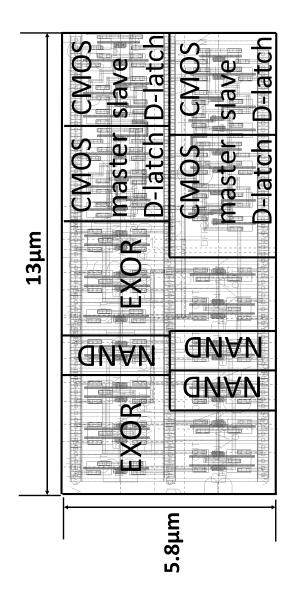

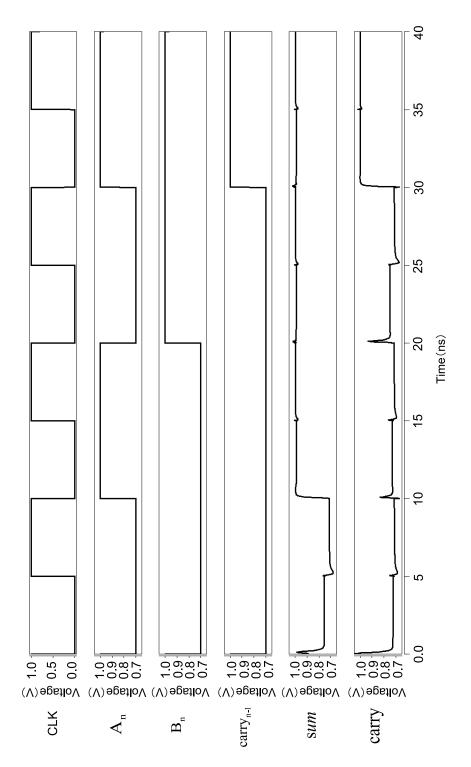

Figures 2.32, 2.33 and 2.34 show the layouts of the current-source-sharing bit-serial adder, the current-mode bit-serial adder and the CMOS bit-serial adder, respectively. The areas of the bit-serial adders are  $66.78\mu m^2$ ,  $80.56\mu m^2$  and  $75.4\mu m^2$ , respectively. In the current-source-sharing sum (carry) circuit, one current source can be shared to generate the full-adder sum (carry) and store the result. Figure 2.35 shows the input and output waveforms of the current-source-sharing sum and carry circuits. If Clk is low, the current I generated by the current source flows through the sum (carry) circuit. If Clk is high, the current I flows through the hold stage, the sum (carry) result is stored.

Figure 2.32: Layout of the current-source-sharing bit-serial adder

| 1          | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|            | Gurrent  Ode masternode slave  Platch  Gufrent  Master mode slave  atch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|            | urrent<br>le slav<br>ave                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|            | Gurrent<br>De slav<br>D-latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|            | de mas<br>D-latch<br>nastern<br>tch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| ے          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 크          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 15.2µm     | e mas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| -          | Current Curren |  |  |  |  |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|            | Sument-mode<br>Fry circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |