# Fully Source-Coupled Logic Based Multiple-Valued VLSI

Tsukasa Ike, Takahiro Hanyu and Michitaka Kameyama Department of Computer and Mathematical Sciences, Graduate School of Information Sciences, Tohoku University

Aoba-yama 05, Sendai 980-8579, Japan tiles@kameyama.ecei.tohoku.ac.jp

#### **Abstract**

A novel source-coupled logic (SCL) style using multiple-valued signals, called multiple-valued source-coupled logic (MVSCL), which operates with an input voltage swing of about 0.3V, is proposed for high-speed and low-power VLSI systems. A multiple-valued comparator, which is a key component, is realized by using differential-pair circuits (DPCs), so that its power dissipation can be greatly reduced while maintaining high-speed switching. Moreover, the current-source control allows steady current flow to cut off when the circuit is not active, thereby saving power dissipation. A 54×54-bit signed-digit multiplier based on MVSCL is designed in a 0.35-µm CMOS technology, and its performance is superior to both corresponding binary static CMOS and multiple-valued current-mode (MVCM) implementation.

### 1. Introduction

In the recent deep-submicron VLSI era, low-power circuit design while maintaining a high-speed switching capability at a small signal voltage swing is needed not only for battery-powered portable applications, but also to reduce the power dissipation of dedicated special-purpose VLSI processors because the extra current density in wires causes temporal or permanent malfunction due to voltage drops or electromigration [1]-[5].

A differential-pair circuit (DPC) is one of the most effective circuit technologies to reduce a signal voltage swing with maintaining high current-driving capability. In fact, DPC-based binary logic circuits have been proposed for high-speed operation with small signal voltage swing [6], [7]. However, the number of transistors required for DPC-based binary logic circuits becomes twice as many as that of a corresponding binary static CMOS realization, because pair of complementary voltage inputs together with complementary input-driving circuits are required for switching.

Since the number of basic components and associated transistor counts can be generally reduced in multiple-

valued logic (MVL) circuits, it is possible that a judicious combination of DPC and MVL will make it possible to perform high-speed operations with reduced device and interconnect counts at low-power dissipation. Using partially DPC-based basic components, we have developed a dual-rail multiple-valued current-mode (MVCM) circuit, and its performance is superior to binary static CMOS circuit with almost the same transistor counts [8], [9]. However, the use of current comparator increases power dissipation due to the large steady current.

This paper presents the design and the implementation of a novel multiple-valued logic circuit called "multiple-valued source-coupled logic (MVSCL) circuit" for high-performance arithmetic in VLSI systems. In MVSCL integrated circuits, a DPC-based voltage comparator is used and operates with small signal voltage swing, so that low-power operation can be realized while maintaining high-speed switching. Moreover, controlling the gate voltages of current sources and current-to-voltage converters, the steady current flowing through inactive circuits can be cut off while maintaining short critical path.

As a typical application to arithmetic and logic VLSI systems, an MVSCL multiplier based on radix-2 signed-digit (SD) addition algorithm is designed. It is demonstrated that the power dissipation of the proposed multiplier is reduced to 69% of that of a dual-rail MVCM implementation under the normalized switching delay. Moreover, a prototype CMOS integrated circuit for the proposed circuit is fabricated in a 0.35-µm standard CMOS technology, and its basic operation is confirmed.

### 2. Principle of MVSCL Integrated Circuits

### 2.1 Basic components

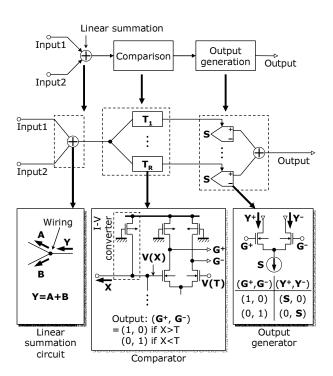

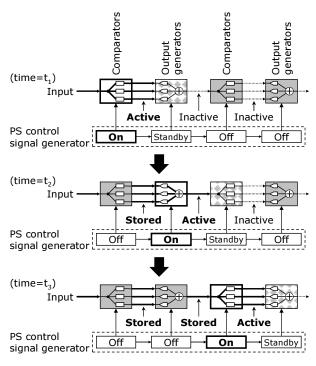

Figure 1 shows the general structure of the MVSCL circuit which consists of three basic components.

1) Linear summation circuit: Using multiple-valued

Figure 1. Basic components

| X                                                                                                                                                                                                     | V(X)                                                                                                                                                               | I+      | I-      | V(G+)                        | V(G-)                        | (G+, G-) |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|------------------------------|------------------------------|----------|

| >T                                                                                                                                                                                                    | <v(t)< td=""><td>0</td><td><math>I_{C}</math></td><td>V<sub>DD</sub></td><td><math>V_{DD}</math>-<math>R_{C}</math>·<math>I_{C}</math></td><td>(1, 0)</td></v(t)<> | 0       | $I_{C}$ | V <sub>DD</sub>              | $V_{DD}$ - $R_{C}$ · $I_{C}$ | (1, 0)   |

| <t< td=""><td>&gt;V(T)</td><td><math>I_{C}</math></td><td>0</td><td><math>V_{DD}</math>-<math>R_{C}</math>·<math>I_{C}</math></td><td><math>V_{\scriptscriptstyle DD}</math></td><td>(0, 1)</td></t<> | >V(T)                                                                                                                                                              | $I_{C}$ | 0       | $V_{DD}$ - $R_{C}$ · $I_{C}$ | $V_{\scriptscriptstyle DD}$  | (0, 1)   |

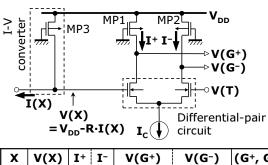

Figure 2. Multiple-valued voltage-mode comparator

current signals, arithmetic summation can be performed by wiring without active devices, so that the resulting arithmetic circuits become simple.

- 2) *Comparator:* A comparator is to compare an input value X with a threshold value T, and to generate binary differential-pair outputs  $(G^+, G^-)$ .

- 3) *Output generator:* An output generator is to generate multiple-valued differential-pair outputs (Y<sup>+</sup>, Y<sup>-</sup>) in accordance with binary differential-pair inputs (G<sup>+</sup>, G<sup>-</sup>) where its function is defined in Figure 1.

The logic functions of these components are the same

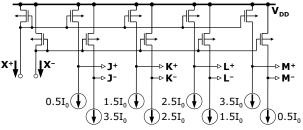

(a) Dual-rail MVCM comparator

Figure 3. 5-valued comparators

Table 1. Comparison of 5-valued comparators

|                   | Dual-rail<br>MVCM | MVSCL  |

|-------------------|-------------------|--------|

| Supply voltage    | 1.0 V             | 3.3 V  |

| Delay             | 620 ps            | 620 ps |

| Power dissipation | 496 μW            | 256 μW |

HSPICE simulation under a 0.35-µm standard CMOS technology

as those of dual-rail MVCM logic circuits. On the other hand, in dual-rail MVCM logic circuits, the comparator compares the input current signal directly with the threshold current level, which causes large power dissipation. Consequently, it is important to develop a new low-power comparator.

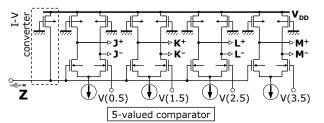

### 2.2 Multiple-valued voltage-mode comparator

Figure 2 shows the principle underlying low-power operation in a multiple-valued voltage-mode comparator. In R-valued comparators, the current I(X), corresponding to the multiple-valued input X, is described as

$$\begin{cases} I(X) = X \cdot I_0 \\ 0 \le X \le R - 1 \end{cases}$$

(1)

where  $I_0$  is the unit current. Since the pMOS transistor MP3 always operates in the linear region, I(X) is converted into the voltage V(X) as follows:

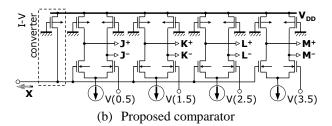

Figure 4. Current source control in the proposed circuit

$$\begin{cases} V(X) = k - \sqrt{k^2 - \frac{2}{\beta} \cdot I(X)} \\ k = V_{DD} - V_{T} \end{cases}$$

(2)

where  $V_T$ ,  $\beta$ , and  $V_{DD}$  are the threshold voltage of MP3, the gain constant of MP3 and the supply voltage of the comparator, respectively.

When the supply voltage of the MVSCL circuit is 3.3V, the minimum voltage swing to be detected is about 0.3V. A differential-pair circuit (DPC) is useful for the detection of such small voltage. A DPC is to compare V(X) and V(T), and generates the binary output currents,  $I^+$  and  $I^-$ , where V(T) is the voltage corresponding to T. The output currents are converted into binary voltages by the pMOS transistors MP1 and MP2, thereby results in the binary output voltages V( $G^+$ ) and V( $G^-$ ).

Table 1 summarizes the comparison between the proposed 5-valued comparator and the corresponding dual-rail MVCM comparator shown in Figure 3. The supply voltage of the dual-rail MVCM comparator is smaller than that of the proposed comparator, however the average of the steady current is over  $10I_0$ , where  $I_0$  is about  $40\mu A$ , so that it causes large power dissipation. In the proposed voltage-mode comparator, the total amount of steady current is  $4I_C$ , where  $I_C$  is about  $20\mu A$ , so that the power dissipation of the proposed comparator can be reduced to about 51% in comparison with that of the

Figure 5. Circuit diagram of the proposed current source control

corresponding dual-rail MVCM one.

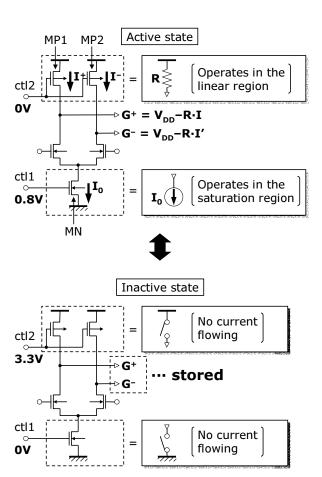

## 2.3 Low-power circuit design using currentsource control

Figure 4 shows the current-source control scheme of the proposed MVSCL circuit. To reduce the power dissipation, the current of inactive components is cut off, which greatly reduces the power dissipation with maintaining high-speed operation [10].

Figure 5 shows the principle of current-source control for MVSCL circuits without additional active devices. When the component is active, the transistors MP1 and MP2 operate in the linear region and MN operates in the saturation region. When the component is inactive, no current flows through MP1, MP2 and MN. The difference between these states is only the gate voltages, ctl1 and ctl2. Consequently, using the above control scheme, the power dissipation of a MVSCL circuit can be greatly reduced without any increased critical path by direct gate-voltage control of the current source.

Table 2. Current level

| Logic value                  | -2 | -1    | 0      | 1      | 2      |

|------------------------------|----|-------|--------|--------|--------|

| X(i), Y(i), W(i), C(i), S(i) | _  | 0     | $I_0$  | $2I_0$ | _      |

| Z(i)                         | 0  | $I_0$ | $2I_0$ | $3I_0$ | $4I_0$ |

(I<sub>0</sub>: Unit current)

Figure 6. Radix-2 SD adder

# 3. Design of a Multiplier Based on Multiple-Valued Source-Coupled Logic

## 3.1 Radix-2 SD addition algorithm

The radix-2 SD number representation using a symmetrical digit set  $\{-1, 0, 1\}$  is defined as follows:

$$\mathbf{X} = (X(n-1)\cdots X(1)\ X(0)) = \sum_{i=0}^{n-1} X(i) \cdot 2^{i}$$

(3)

where  $X(i) \in \{-1,0,1\}$ . The redundancy allows totally parallel arithmetic operations. The addition of two numbers,  $\mathbf{X} = (X(n-1)\cdots X(1)X(0))$  and  $\mathbf{Y} = (Y(n-1)\cdots Y(1)Y(0))$  is performed by three successive steps in each digit as

$$Z(i) = X(i) + Y(i) \tag{4}$$

$$2C(i) + W(i) = Z(i)$$

(5)

$$S(i) = W(i) + C(i-1)$$

(6)

where the arithmetic sum  $\mathbf{Z} = (Z(n-1)\cdots Z(1)Z(0))$ , the intermediate sum  $\mathbf{W} = (W(n-1)\cdots W(1)W(0))$ , the carry  $\mathbf{C} = (C(n-1)\cdots C(1)C(0))$  and the final sum  $\mathbf{S} = (S(n)\cdots S(1)S(0))$  are  $Z(i) \in \{-2, -1, 0, 1, 2\}$ ,

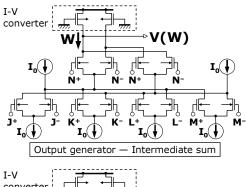

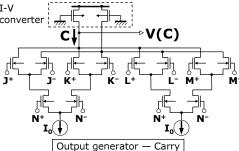

Figure 7. Circuit diagram of the proposed SDFA

$W(i) \in \{-1, 0, 1\}, C(i) \in \{-1, 0, 1\} \text{ and } S(i) \in \{-1, 0, 1\},$  respectively.

To retain the final sum S(i) within the set  $\{-1, 0, 1\}$ , C(i) and W(i) are determined by Z(i-1) together with Z(i) as follows:

$$\begin{cases} C(i) = 1, \ W(i) = 0 & \text{if } \ Z(i) = 2 \\ C(i) = 1, \ W(i) = -1 & \text{if } \ Z(i) = 1 \ \text{and } \ Z(i-1) \ge 1 \\ C(i) = 0, \ W(i) = 1 & \text{if } \ Z(i) = 1 \ \text{and } \ Z(i-1) < 1 \\ C(i) = 0, \ W(i) = 0 & \text{if } \ Z(i) = 0 \\ C(i) = 0, \ W(i) = -1 & \text{if } \ Z(i) = -1 \ \text{and } \ Z(i-1) \ge 1 \\ C(i) = -1, \ W(i) = 1 & \text{if } \ Z(i) = -1 \ \text{and } \ Z(i-1) < 1 \\ C(i) = -1, \ W(i) = 0 & \text{if } \ Z(i) = -2. \end{cases}$$

The final sum is independent of the word length n because the carry-propagation chain is limited to one digit to left. Therefore the addition speed of the SD adder is higher than that of ordinary binary adders [11].

## 3.2 Design of an SD multiplier

In the proposed MVSCL circuits, each digit of the SD

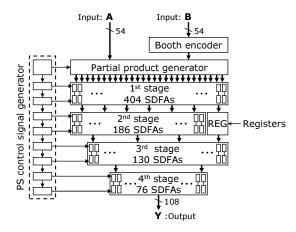

Figure 8. Block diagram of the proposed 54×54-bit multiplier

Figure 9. Chip photomicrograph

numbers corresponds to a multiple-valued current signal. Two adder inputs, the linear sum of two inputs, the intermediate sum, the carry and the final sum are represented as X(i), Y(i), Z(i), W(i), C(i) and S(i), respectively, whose current levels are given in Table 2.

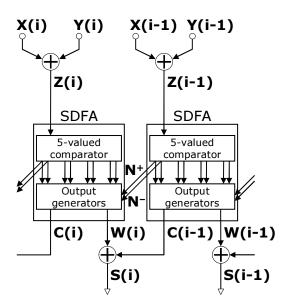

The radix-2 SD adder can be designed as shown in Figure 6. The linear summation of (4) and (6) can be obtained by wiring without active devices. The operation of (5) is performed with an SD full adder (SDFA). The signals  $N^+$  and  $N^-$  are used as the control signals to give the condition of  $Z(i-1) \ge 1$  and Z(i-1) < 1 in (7). The linear sum Z(i) takes 5 values and decoded by a 5-valued voltage comparator. As a result, the SDFA circuit can be designed using 54 MOS transistors as shown in Figure 7.

A low-power multiple-valued multiplier is designed

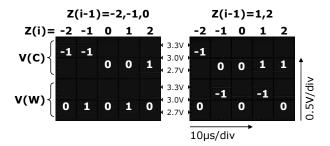

Figure 10. Measured waveforms

Table 3. Comparison of multipliers

|                   | Binary static<br>CMOS | Dual-rail<br>MVCM | MVSCL                |

|-------------------|-----------------------|-------------------|----------------------|

| Supply voltage(s) | 2.8 V                 | 1.8 V, 1.0 V      | 3.3 V                |

| Delay             | 7.64 ns               | 6.24 ns           | 6.24 ns              |

| Power dissipation | 106 mW                | 153 mW            | 106 mW               |

| Area              | 5.32 mm <sup>2</sup>  | _                 | 4.99 mm <sup>2</sup> |

HSPICE simulation under a 0.35-µm standard CMOS technology

using the SDFAs as shown in Figure 8. Using the Booth algorithm, 27 partial products for 54-bit multiplication are generated from the partial product generator. Since SD addition can be performed by a binary-adder-tree scheme, 27 partial products are added in parallel by just four addition stages. Because of the proposed switched-current control scheme, only one of nine divided stages in the multiplier is controlled to be active.

### 4. Evaluation

### 4.1 Implementation of a prototype chip

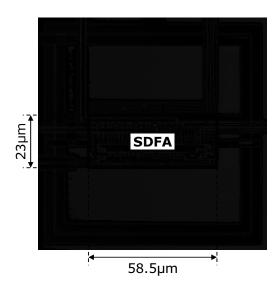

To confirm the operation of the proposed MVSCL circuit, a prototype SDFA circuit is implemented using a 0.35- $\mu$ m standard CMOS technology as shown in Figure 9. The effective size of the SDFA is  $58.5\mu$ m  $\times$   $23\mu$ m. The typical transfer characteristics of the SDFA for the case of  $-2 \le Z(i) \le 2$  are shown in Figure 10.

### 4.2 Comparison of performance

Table 3 summarizes the comparison of SDFAs in terms of the delay and the power dissipation. The performance is estimated by HSPICE simulation based on a 0.35-µm standard CMOS technology. Using DPC-based MV

voltage comparators, the power dissipation of the proposed multiplier can be reduced to 69 % of a corresponding MVCM implementation under the condition of the same multiplication time. Moreover, under the same power dissipation, the operating speed of the proposed multiplier is 1.2 times faster than that of a binary CMOS multiplier.

#### 5. Conclusion

The key technologies that realize low-power dissipation as well as high-speed switching have been presented. The use of SCL and MVL style makes the voltage swing for switching small with maintaining small hardware. Moreover, the use of current source control technique makes the waste steady current flow cut off, so that the static power dissipation becomes zero in this circuit. As a typical application to large-scale arithmetic systems, it is demonstrated that the maximum operating delay of the proposed  $54\times54$ -bit multiplier is evaluated to be 6.24ns under a 0.35- $\mu$ m standard CMOS technology, whose performance is superior to that of a corresponding binary static one.

As a future problem, it is also important to save the static power dissipation still more while maintaining high-speed operation. One approach is the use of dynamic logic circuits. In the proposed circuit, the steady current becomes zero by using dynamic logic circuits. If the problem is successfully solved, we may well see an ultra-low-power multiple-valued VLSI chip for ultra-high-speed arithmetic and logic operations.

#### References

- [1] W. Nebel and J. Mermet, Low power Design in Deep Submicron Electronics, Kluwer Academic Publishers, Dortrecht, 1997.

- [2] A. Bellaouar and M. I. Elmasry, Low-power Digital Design: Circuits and Systems, Kluwer Academic Publishers, Boston, 1995.

- [3] H. Iwai, "CMOS technology Year 2010 and beyond," IEEE J. Solid-State Circuits, Vol.34, No.3, pp-357-366, Mar. 1999.

- [4] S.Malhi and P.Chatterjee, "1-V microsystems Scaling on schedule for personal communications," IEEE Circuits and Devices, 10, 2, pp.13-17, 1994.

- [5] D.P.Foty and E.J.Nowak, "MOSFET technology for low-voltage/low-power applications," IEEE Micro, 14, 3, pp.68-76, 1994.

- [6] M. Yamashina and H. Yamada, "MOS current mode logic MCML circuit for low-power GHz processors," NEC Res. Develop., vol.36, no.1, pp.54-63, Jan.1995.

- [7] M. W. Allam and M. I. Elmasry, "Dynamic current mode logic (DyCML): A new low-power high-performance logic style," IEEE J. Solid-State Circuits, Vol.36, No.3, pp.550-558, Mar. 2001.

- [8] T. Hanyu and M. Kameyama, "A 200 MHz pipelined multiplier using 1.5 V-supply multiple-valued MOS current-mode circuits with dual-rail source-coupled logic," IEEE J. Solid-State Circuits, Vol.30, No.11, pp.1239-1245, Nov. 1995.

- [9] T. Ike, T. Hanyu, and M. Kameyama, "Dual-rail multiple-valued current-mode VLSI with biasing current sources," Proc. 31st IEEE Int. Symposium on Multiple-Valued Logic, no.31, pp.21-26, Warsaw, Poland, May 2001.

- [10] T. Hanyu, S. Kazama and M. Kameyama, "Design and implementation of a low-power multiple-valued currentmode integrated circuit with current-source control," IEICE Trans. Electron., Vol.E80-C, No.7, pp.941-947, Jul. 1997.

- [11] A. Avizienis, "Signed-digit number representations for fast parallel arithmetic," IRE Trans. Electron. Computers, Vol.EC-10, pp.389-400, Sep. 1961.