## Memory characteristics of

metal-oxide-semiconductor capacitor with high density cobalt nanodots floating gate and HfO2 blocking dielectric

| 著者                     | Pei Yanli, Yin Chengkuan, Kojima Toshiya,<br>Nishijima Masahiko, Fukushima Takafumi,<br>Tanaka Tetsu, Koyanagi Mitsumasa |

|------------------------|--------------------------------------------------------------------------------------------------------------------------|

| journal or             | Applied Physics Letters                                                                                                  |

| publication title      |                                                                                                                          |

| volume                 | 95                                                                                                                       |

| number                 | 3                                                                                                                        |

| page range             | 033118                                                                                                                   |

| year                   | 2008                                                                                                                     |

| URL                    | http://hdl.handle.net/10097/51827                                                                                        |

| doi: 10 1063/1 3189085 |                                                                                                                          |

doi: 10.1063/1.3189085

## Memory characteristics of metal-oxide-semiconductor capacitor with high density cobalt nanodots floating gate and HfO<sub>2</sub> blocking dielectric

Yanli Pei,<sup>1,a)</sup> Chengkuan Yin,<sup>2</sup> Toshiya Kojima,<sup>3</sup> Masahiko Nishijima,<sup>4</sup> Takafumi Fukushima,<sup>2</sup> Tetsu Tanaka,<sup>2</sup> and Mitsumasa Koyanagi<sup>2</sup> <sup>1</sup>International Advanced Research and Education Organization, Tohoku University, 6-6-03 Aza-Aoba,

Aramaki, Aoba-ku, Sendai 980-8578, Japan

<sup>2</sup>Department of Bioengineering and Robotics, Tohoku University, 6-6-01 Aza-Aoba, Aramaki, Aoba-ku, Şendai 980-8579, Japan

<sup>3</sup>Technical Division, School of Engineering, Tohoku University, 6-6-04 Aza-Aoba, Aramaki, Aoba-ku, Sendai 980-8579, Japan

<sup>4</sup>Institute for Materials Research, Tohoku University, 2-1-1 Katahira, Aoba, Sendai 980-8577, Japan

(Received 14 May 2009; accepted 7 July 2009; published online 24 July 2009)

In this letter, cobalt nanodots (Co-NDs) had been formed via a self-assembled nanodot deposition. High resolution transmission electron microscopy and x-ray photoelectron spectroscopy analyses clearly show that the high metallic Co-ND is crystallized with small size of  $\sim 2$  nm and high density of  $(4-5) \times 10^{12}$ /cm<sup>2</sup>. The metal-oxide-semiconductor device with high density Co-NDs floating gate and high-*k* HfO<sub>2</sub> blocking dielectric exhibits a wide range memory window (0–12 V) due to the charge trapping into and distrapping from Co-NDs. After 10 years retention, a large memory window of  $\sim 1.3$  V with a low charge loss of  $\sim 47\%$  was extrapolated. The relative longer data retention demonstrates the advantage of Co-NDs for nonvolatile memory application. © 2009 American Institute of Physics. [DOI: 10.1063/1.3189085]

Memory device structures with metal nanodots floating gate have been considered as a possible solution to scale down nonvolatile memories (NVMs). Compared to semiconductor nanodots,<sup>1,2</sup> metal nanodots with a high work function can provide better data retention due to the formation of a deep quantum well.<sup>3–5</sup> Another advantage is that metal nanodots have higher density of states around Fermi level so that the requirement of high charge storage capacity can be realized. However, some challenges have to be faced, such as the formation of high density nanodots to overcome the electrical fluctuation between memory cells and the prevention of metal oxidation.<sup>6,7</sup> In previous work, we had fabricated tungsten nanodots (W-NDs) with small size and high density by self-assembled nanodot deposition (SAND).<sup>8</sup> However, for the small sized W-NDs, the quantum size effect cannot be neglected, which presumably leads to the degradation of data retention. The metal nanodots with high work function are required to compensate the conduction band upshift caused by quantum size effect. Compared to the tungsten with middle work function ( $\sim 4.5$  eV), the cobalt with high work function of  $\sim 5.0$  eV is considered as a good candidate.<sup>9,10</sup> In addition, the enthalpy of Co-O bond is 384 kJ/mol, which is much lower than of Si-O (799 kJ/mol), and forming high metallic nanodots in silicon oxide is considered to be easy.<sup>1</sup> In this letter, we have investigated the memory characteristics of high density Co-NDs dispersed in silicon oxide. Here, we employed high dielectric HfO<sub>2</sub> as blocking layer to improve the controllability of gate to write/erase data.

2 in. *p*-type Si wafers with (100) orientation were cleaned with standard Radio Corporation of America (RCA) process, followed by thermal oxidation to form a 5 nm thick tunneling oxide. Subsequently, Co-NDs film with 2 nm thick was deposited onto the tunneling oxide by SAND. In this

method, cobalt chips placed on a silicon oxide target were cosputtered in high-vacuum rf sputtering equipment. The size of cobalt chip is in a length of 5 mm, a width of 5 mm, and a thickness of 2.0 mm. To obtain uniform dot size and dot density, the silicon substrate was rotated at a rate of 75 rpm. Subsequently, the postdeposition annealing (PDA) was performed in situ at 800 °C for 1 h to improve the quality of Co-ND and silicon oxide matrix. Then, the HfO<sub>2</sub> as thick as 40 nm was sputtered as blocking gate oxide. To prevent the interdiffusion of HfO<sub>2</sub> and Co-NDs, 1 nm thick sputtered SiO<sub>2</sub> was sandwiched between Co-NDs film and HfO<sub>2</sub>. The blocking layer was annealed at 600 °C in nitrogen ambient for 30 min. The dielectric constant of HfO<sub>2</sub> was estimated as  $\sim 20\varepsilon_0$ . Finally, in order to fabricate the metal-oxidesemiconductor (MOS) memory device, Al electrode with a diameter of  $\sim 0.3$  mm was evaporated. As a reference, the MOS capacitor with 2 nm thick sputtered silicon oxide without Co-NDs was fabricated simultaneously. The physical characteristics of Co-NDs were evaluated by high-resolution transmission electron microscopy (HRTEM) and x-ray photoelectron spectroscopy (XPS). The memory properties were measured at room temperature using an Agilent B1500A semiconductor parameter analyzer.

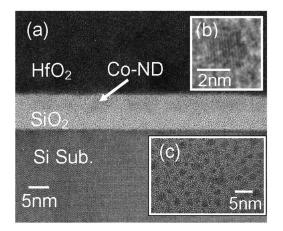

Figure 1(a) shows a cross-sectional HRTEM image of  $HfO_2/Co-NDs/SiO_2/Si$  structure. It was clearly observed that the Co-NDs with high density were dispersed in the sputtered silicon oxide matrix. The average size of Co-NDs is about 2 nm. The crystallized Co-ND with obviously visible lattice fringes was evident in Fig. 1(b). To confirm the Co-NDs density exactly, the TEM plane-view image was shown in Fig. 1(c). After PDA, the density of Co-NDs is as high as  $(4-5) \times 10^{12}/cm^2$ .

The chemical composition of Co-NDs film annealed at 800 °C for 1 h is demonstrated by XPS analysis using an Al  $K\alpha$  (1486.6 eV) x-ray radiation. To prevent the oxidation of Co-NDs film in atmosphere, 1 nm thick silicon oxide was

## **95**, 033118-1

## © 2009 American Institute of Physics

Downloaded 30 Aug 2011 to 130.34.134.250. Redistribution subject to AIP license or copyright; see http://apl.aip.org/about/rights\_and\_permissions

<sup>&</sup>lt;sup>a)</sup>Electronic mail: peiyanli@sd.mech.tohoku.ac.jp.

FIG. 1. (a) HRTEM cross-sectional image of  $HfO_2/Co-ND_8/SiO_2/Si$  structure. (b) An enlarged HRTEM image of Co-ND, (c) HRTEM plane-view of Co-NDs film with 800 °C PDA.

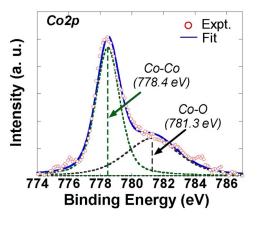

sputtered on 2 nm thick Co-NDs film as cap layer for XPS measurement. Figure 2 shows the Co 2p core level XPS spectrum. The peaks at 778.4 and 781.3 eV were obtained by fitting this spectrum. These binding energy values are very close to the values reported for Co-Co and Co-O as references.<sup>12,13</sup> It is worthy to note that the proportion of Co-Co to Co-O bonds is about 2, which was estimated from the XPS spectrum fitting. These results indicate that the Co-ND is a high metallic structure. Some oxidized cobalt is present, which presumably bonds to the silicon oxide matrix. We have reported that W-NDs dispersed in silicon oxide were oxidized seriously.<sup>7</sup> Here, the enthalpy of W–O bond (672 kJ/mol) is close to that of Si–O (799 kJ/mol).<sup>9</sup> In comparison, the enthalpy of Co-O bond (384 kJ/mol) is much lower than that of Si–O.<sup>9</sup> It suggests that the oxygen bonds easier to silicon than to cobalt. Therefore, the high metallic Co-ND was self-assembly dispersed into the silicon oxide matrix.

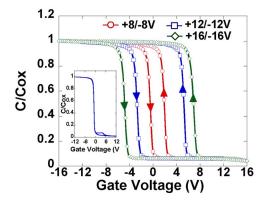

Figure 3 shows the high-frequency (1 MHz) capacitance-voltage (C-V) characteristics with different sweeping gate voltages for MOS capacitor with Co-NDs floating gate and HfO<sub>2</sub> blocking dielectric. The holding time in these measurements is 1 s. Memory windows with counterclockwise hysteresis were observed clearly. The memory window is independent of the measurement frequency (not shown here). In addition, as shown in the insert of Fig. 3, for the reference sample with 2 nm thick sputtered silicon oxide

FIG. 3. (Color online) High-frequency C-V curves measured at different sweep biases for Co-ND MOS capacitor. The inset is the result of MOS capacitor with 2 nm thick sputtered silicon oxide without Co-NDs.

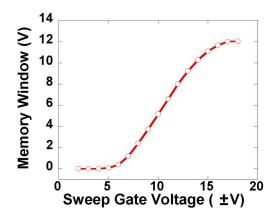

without Co-NDs, no hysteresis was obtained even at gate voltage sweeping from +12 to -12 V. These results indicate that the memory window is induced by the charge trapping into and distrapping from Co-NDs to silicon substrate. Memory window as a function of sweep gate voltages was summarized in Fig. 4 based on a series of C-V measurements. These C-V measurements were carried out by applying stress voltages to the gate with holding time of 1 s, followed by bidirectional voltages sweeping. As shown in Fig. 4, the memory window appeared at +5/-5 V sweep gate voltage, and increased with increasing the sweep gate voltage. Finally, it tends to saturation, suggesting that at high electric field region, the current through tunneling oxide to Co-NDs is equivalent with the leakage current from Co-NDs to control gate through blocking oxide. Under low sweep gate voltage of +8/-8 V, a memory window of  $\sim 2.45$  V was obtained. The maximum memory window of  $\sim 12.0$  V was observed at sweep gate voltage of +17/-17 V. We had calculated the charge density in Co-NDs by formula as reference.<sup>14</sup> At memory window of 12 V, the trapped charge density was estimated to be  $\sim 2.8 \times 10^{13}$ /cm<sup>2</sup>. Considering the density of Co-NDs, it suggests that one Co-ND can store five or more charges.

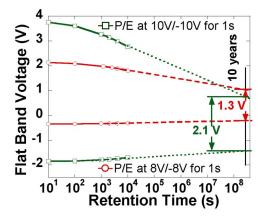

Retention characteristics of Co-ND MOS memory capacitor were also investigated at room temperature. Figure 5 shows the data retention characteristics after program/erase (P/E) at  $\pm 8$  V and  $\pm 10$  V for 1 s, respectively. As is observed, after  $\pm 10$  V P/E, the memory window of ~4.5 V remained at retention time of  $10^4$  s, namely the charge loss of

FIG. 2. (Color online) Co 2p core level XPS spectrum of Co-NDs film.

FIG. 4. (Color online) Memory window as a function of sweep gate voltages for Co-ND MOS memory capacitor.

Downloaded 30 Aug 2011 to 130.34.134.250. Redistribution subject to AIP license or copyright; see http://apl.aip.org/about/rights\_and\_permissions

FIG. 5. (Color online) Retention characteristics at zero gate bias and room temperature for Co-ND MOS memory capacitor. The program/erase was done at  $\pm 8$  and  $\pm 10$  V for 1 s.

~20%. The logarithmic dependence of the retention characteristics has been observed by various groups.<sup>15,16</sup> Using this extrapolation, a large memory window of 2.1 V and a charge loss of 62% can be estimated after 10 years retention. On the other hand, for the case with lower P/E voltage of ±8 V, the rate of charge loss becomes moderate. At 10<sup>4</sup> s, the memory window of 2.1 V remained with the charge loss of ~15%. After 10 years data retention, a memory window of 1.3 V with a charge loss of 47% was estimated. In previous study, we have reported the retention characteristics of high density W-NDs.<sup>8</sup> In this case, the memory window disappeared at  $6 \times 10^7$  s.<sup>8</sup> In comparison, relative longer data retention was realized in Co-NDs. It is presumably due to the higher workfunction of cobalt.

In conclusion, high metallic Co-NDs dispersed in silicon oxide were formed by SAND method, followed by 800 °C PDA. The high density of  $(4-5) \times 10^{12}/\text{cm}^2$  and small size of  $\sim 2$  nm were confirmed by HRTEM. The *C-V* characteristics of MOS capacitor with Co-NDs floating gate and HfO<sub>2</sub> blocking dielectric shows a wide range memory window of

0–12 V. The retention characteristics were also investigated. After 10 years data retention, a memory window of  $\sim$ 1.3 V with a charge loss of  $\sim$ 47% was obtained. The relative longer data retention shows that the Co-NDs with high work function is a good candidate for the next generation NVM application.

This work was partly supported by a Grant-in-Aid for Scientific Research on Priority Area (Grant No. 18063002) from the Ministry of Education, Culture, Sports, Science, and Technology of Japan.

- <sup>1</sup>S. Choi, H. Yang, M. Chang, S. Baek, H. Hwang, S. Jeon, J. Kim, and C. Kim, Appl. Phys. Lett. **86**, 251901 (2005).

- <sup>2</sup>J. Lu, Z. Zuo, Y. Chen, Y. Shi, L. Pu, and Y. Zheng, Appl. Phys. Lett. **92**, 013105 (2008).

- <sup>3</sup>W. R. Chen, T. C. Chang, J. L. Yeh, S. M. Sze, and C. Y. Chang, Appl. Phys. Lett. **92**, 152114 (2008).

- <sup>4</sup>S.-S. Yim, M.-S. Lee, K.-S. Kim, and K.-B. Kim, Appl. Phys. Lett. **89**, 093115 (2006).

- <sup>5</sup>J. H. Kim, J. Y. Yang, J. S. Lee, and J. P. Hong, Appl. Phys. Lett. **92**, 013512 (2008).

- <sup>6</sup>L. Perniola, B. D. Salvo, G. Ghibaudo, A. F. Para, G. Pananakakis, V. Vidal, T. Baron, and S. A. Lombardo, IEEE Trans. Nanotechnol. **2**, 277 (2003).

- <sup>7</sup>Y. Pei, T. Fukushima, T. Tanaka, and M. Koyanagi, Jpn. J. Appl. Phys. **47**, 2680 (2008).

- <sup>8</sup>Y. Pei, C. Yin, M. Nishijima, T. Kojima, T. Fukushima, T. Tanaka, and M. Koyanagi, Appl. Phys. Lett. **94**, 063108 (2009).

- <sup>9</sup>C.-W. Hu, T.-C. Chang, C.-H. Tu, P.-K. Shueh, C.-C. Lin, S. M. Sze, T.-Y. Tseng, and M.-C. Chen, Appl. Phys. Lett. **94**, 102106 (2009).

- <sup>10</sup>D. Zhao, Y. Zhu, and J. Liu, Solid-State Electron. **50**, 268 (2006).

- <sup>11</sup>D. R. Lide, *CRC Handbook of Chemistry and Physics*, 81st ed. (CRC, Boca Raton, 2000).

- <sup>12</sup>I. Alstrup, I. Chorkendorff, R. Candia, B. S. Clausen, and H. Topsoe, J. Catal. 77, 397 (1982).

- <sup>13</sup>B. J. Tan, K. J. Klabunde, and P. M. A. Sherwood, J. Am. Chem. Soc. 113, 855 (1991).

- <sup>14</sup>H. Hanafi, S. Tiwari, and I. Khan, IEEE Trans. Electron Devices **43**, 1553 (1996).

- <sup>15</sup>P. Normand, E. Kapetanakis, P. Dimitrakis, and D. Tsoukalas, Appl. Phys. Lett. 83, 168 (2003).

- <sup>16</sup>M.-Y. Hao, H. Hwang, and J. C. Lee, Appl. Phys. Lett. 62, 1530 (1993).