# Advanced Development Process for Ultrafine Photoresist Patterns

| 著者                | 大見忠弘                               |

|-------------------|------------------------------------|

| journal or        | IEEE Transactions on Semiconductor |

| publication title | Manufacturing                      |

| volume            | 6                                  |

| number            | 3                                  |

| page range        | 269-273                            |

| year              | 1993                               |

| URL               | http://hdl.handle.net/10097/48007  |

doi: 10.1109/66.238177

IEEE TRANSACTIONS ON SEMICONDUCTOR MANUFACTURING, VOL. 6, NO. 3, AUGUST 1993

# Reply to Comments on "Dose Perturbation by Wafer Charging During Ion Implantation"

#### Yoshiyuki Sato, Kazunori Anzai, and F. Tadokoro

This is our reply to comments on our paper "Dose Pertubation by Wafer Charging During Ion Implantation." To our understanding, four issues have been raised: 1) There is nothing in the paper about the use of the electron shower. 2) Consistency between our results and those in [1]. 3) The contention that dose nonuniformity is an issue which has already been solved by the use of the electron shower, and that the current problem is the charge-up on a device structure level; and 4) the suitability of our implantation condition for CMOS fabrication.

As for point 1), we mention the use of the electron shower at the end of Section III in our paper.

In response to the second point, we do not insist on inconsistency between our results and those in [1]. On the contrary, our results are consistent with [1]'s in terms of the mechanism of beam blowup. A larger beam leads to marked undesirable effects because of its blow-up in the vicinity of the charge-up wafer. This is first clarified experimentally in our paper and it is not based on a new mechanism. This problem has not been reported yet in spite of its importance. Reference [1] is an excellent study and the blow-up mechanism mentioned in it is of course correct. However, it emphasizes that a bare wafer adjacent to the charge-up wafer shows no anomalies. In addition, nothing about the contrary case or about the undersirable effect on a fatal dose control system caused by wafer charging is mentioned in it. This is probably because it does not address what happens to the incident ion beam, nonchargeable wafers in the batch, or the dose control system, when a large incident beam entering a chargeable wafer is still irradiating the nonchargeable neighboring region and still not entering the chargeable wafer perfectly. Accordingly, it is irrelevant that our results are a priori derived from [1] because the time-constants of the blow-up and contraction of the ion beam is clarified in [1].

In regards to the third point, it is correct that the beam blow-up is inhibited by the use of the electron shower (which is also mentioned in our paper) and that recent interest is focused on what type of electron shower should be used to circumvent the charge-up problem on a specified device structure. Many people are now competing to develop an electron shower that can be applied to any device. In other words, present-day electron showers are not almighty, and there are still some cases in which we do not apply them. Two examples are (a) in ion implanatation in devices whose structure is too charge-up susceptible to be affected by existing electron showers or whose charge-up is unknown; and (b) in ion implantation in devices which are free from charge-up. In case (a), ion implantation current is often reduced to avoid beam blow-up. In case (b), no special attention has been given to ion implantation current. Our paper suggests, however, that it should be taken into account when dummy wafers are used in the same batch. This is because oxide on the dummy wafers may lead to dose error, especially in low energy implantation. As shown above, beam blow-

Manuscript received January 26, 1993.

The authors are with NTT LSI Laboratories, Atsugi, Kanagawa 243-01, Japan.

IEEE Log Number 9212064.

up without using an electron shower is an important issue even today.

Finally, to address the fourth point, our implanation condition is an experimental one and not intended for CMOS fabrication.

#### References

M. E. Mack, G. Ryding, D. H. Douglas-Hamilton, K. Steeples, M. Farley, V. Gillis, N. White, A. Wittkower, R. Lambracht, "Wafer charging and beam interactions in ion implantation," in *Nucl. Intr. and Meth. B6* 405-411, 1985.

# Advanced Development Process for Ultra Fine Photoresist Patterns

Hisayuki Shimada, Masanobu Onodera, Toru Nonaka, Kouichi Hirose, and Tadahiro Ohmi

Abstract—Addition of appropriate surfactant to developer will improve wettability of the developer, thus promoting dissolution uniformity of exposed photoresist. Surface smoothness of the Si substrate is also improved when developer contains surfactant. The only disadvantage is that surfactant is adsorbed onto the water surface; however, it can be removed by a  $Pt-H_2O_2$  treatment without degrading the photoresist pattern.

The optimal tetramethylammonium hydroxide (TMAH) concentration in the developer was investigated by measuring the developing selectivity of the photoresist against various TMAH concentration levels. The developing selectivity is considered to directly affect the photoresist profile and resolution in the development process.

#### I. INTRODUCTION

As the dimensions of semiconductor devices continue to shrink, it is becoming increasingly essential to improve wet processing and the wettability of chemicals [1], [2]. In the photolithography area, the wettability of developer is also gaining more attention. To improve the wettability of developer, many surfactant species have been injected into developer [3]; in the past, its main purposes were to reduce the volume of developer and the development time in the puddle development process. However, additional benefits have since been found. This article will present the effects of surfactant addition to developer: the improvement of Si surface smoothness as well as photoresist patterns.

One of the major problems [1] brought on by the introduction of surfactant is that it remains adsorbed in the silicon and photoresist even after ultrapure water rinsing, the final step in the development

Manuscript received April 25, 1991; revised October 9, 1992.

The authors are with the Department of Electronics, Faculty of Engineering, Tohoku University, Sendai 980, Japan.

Nonaka's permanent address is Tokuyama Soda Co., Ltd., Tokuyamashi, Yamaguchi-ken 745, Japan.

K. Hirose's permanent address is Japan Synthetic Rubber Co., Ltd., Tokyo Research Laboratory, Asao-ku, Kawasaki 215, Japan. IEEE Log Number 9209575.

0894-6507/93\$03.00 © 1993 IEEE

Fig. 1.

process. Postbaking at 130°C does not remove the surfactant from the bare silicon surface, although it does desorb it from the photoresist. However, hydrogen peroxide  $(H_2O_2)$  with platinum (Pt) catalyst [4] was found to effectively remove surfactant from the bare silicon surface.

Since positive, Novolak/quinonediazide-type photoresist will remain as one of the main photoresist materials, its dissolution mechanism is being actively researched [5]-[7]. In this study, we investigated the dissolution characteristics of the photoresist in order to improve developing selectivity between the exposed region and the unexposed region with various levels of TMAH concentration in the developer.

# II. EXPERIMENTAL METHOD

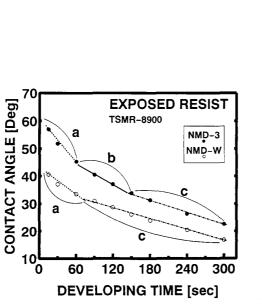

Wettabilities of two developers were compared: NMD-3 and NMD-W [Tokyo Ohka Kogyo]. There was only one difference between the two developers: surfactant was contained in NMD-W but not in NMD-3. The contact angle of a droplet of developer was measured [8] to indicate wettability; it was measured 25 s after landing in the substrate. The volume of developer was set at 2  $\mu$ l, and the humidity was maintained at 24% during the measurements. The change in the contact angle of the developer with the passage of time was examined in the exposed region of the photoresist.

Next, the effect of surfactant on Si surface microroughness was studied. Si wafers were immersed in either NMD-3 (developer without surfactant) or NMD-W (developer with surfactant) for 70 s. Developer temperature was maintained at 23°C. Surface roughness was observed with a scanning tunneling microscope (STM) [SAM3100: Seiko Instruments Inc.] to compare the samples.

The dependence of developing selectivity on TMAH concentration was also studied. Thirteen developers were prepared, with TMAH concentrations ranging from 1.5% to 3.0%, to measure the decrease in photoresist thickness with time. The developing selectivity, the ratio of the photoresist dissolution rate in the exposed region to that in the unexposed region, was plotted. Maximum developing selectivity leads to high performance in resists. Since the dissolution rate of exposed photoresist changes with the passage of time, the dissolution rate at 5 s after starting development was recorded in this experiment. The dependence of developing selectivity on TMAH concentration was also studied for a post-exposurebake process [9].

#### **III. RESULTS AND DISCUSSIONS**

#### A. Wettability of Developers

Fig. 1 shows a graph and photos of how the contact angle of the two developers, NMD-3 and NMD-W, changes with time. In the case of NMD-3, the developer without surfactant, three periods can be observed during the course of time: a, b, and c. Photos show the development progress after 60 s, 150 s, and 300 s in NMD-3; the appearance of the droplet after 150 s indicates that development does not proceed in a uniform manner. However, in the case of NMD-W, the surfactant-added developer, only two distinct periods, a and c, can be seen. Partial development is not observed, suggesting that the addition of surfactant promotes uniform development.

# IEEE TRANSACTIONS ON SEMICONDUCTOR MANUFACTURING, VOL. 6, NO. 3, AUGUST 1993

Fig. 2.

# B. Microroughness on Si Surface Caused by Developer

Surface microroughness was examined on (100) Si wafers dipped in NMD-3 (developer without surfactant) and NMD-W (developer with surfactant). Fig. 2 presents the STM images of the Si wafer after 70-second immersion in NMD-3 and NMD-W. For the reference, the NMD-3 sample and the NMD-W sample, the average surface microroughness (Ra) was 4.17 Å, 4.92 Å, and 3.89 Å, respectively. Therefore, the deviations of microroughness for these samples were 2.83 Å, 7.12 Å, and 3.0 Å, respectively. In the case of a short time span, this figure indicates that the Si surface is smoother when dipped into surfactant-added developer than when dipped into developer without surfactant. This result suggests that the surfactant adsorbed on the Si surface protects the Si from attack by hydroxide ions which anisotropically etch Si. The smoothness of the Si surface can be maintained in a similar manner, with lim-

ited microroughness, when  $SiO_2$  film is etched with buffered hydrofluoric acid (BHF) and surfactant [1], [2].

Surface microroughness is one of the main factors affecting the reliability and the performance of ULSI devices. It has been confirmed that if the average surface microroughness (Ra) is reduced from 8 Å to 2 Å, the breakdown electric field intensity ( $E_{BD}$ ) of very thin oxides (100 Å or less) is improved by about 30% while the time-dependent dielectric breakdown ( $Q_{BD}$ ) is improved by one order of magnitude [10]. Moreover, the transconductance ( $g_m$ ) and the speed performance of the MOS transistor are improved by approximately 50% [11].

The reason why the Si surface smoothness can be preserved after immersion in developer with wettability improved by adding surfactant, is as follows: the surfactant is adsorbed into the Si surface, consequently suppressing Si etching by the hydroxide ion and eliminating the crystal orientation dependence of the etch rate.

#### C. Removal of Surfactant Adsorbed on Substrate

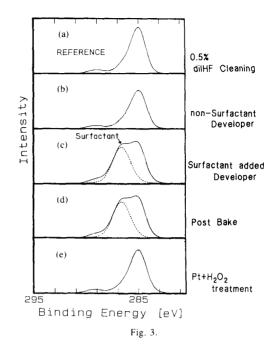

We have confirmed by contact angle measurements that the surfactant adsorbed on the Si surface after development is not removed even by a 30-minute postbake at 130°C. The presence of residual surfactant has also been confirmed with X-ray photoelectron spectroscopy (XPS) [WP-100: Surface Science]. Fig. 3(a) shows the peak of carbon 1s ( $C_{1s}$ ) adsorbed into the reference bare silicon surface. Figs. 3(b) and (c) show the  $C_{1s}$  spectra after the 60-s ultrapure water rinsing following the 70-s immersion into developer without surfactant and with surfactant, respectively. The spectra in Fig. 3(b) closely match those in Fig. 3(a). However, in Fig. 3(c), there is a sub-peak of  $C_{1s}$  observed together with the main C<sub>1s</sub> peak. From these findings, it is conjectured that this subpeak is generated by surfactant. Judging from the energy value of the chemical shift from the main C<sub>1s</sub> peak to the sub-peak, this subpeak is assumed to be  $-C_nH_mO_1$ . Fig. 3(d), which shows the  $C_{1s}$ spectra after an additional 30-minute postbake at 130°C, confirms that the surfactant is still not removed by the postbake.

In order to eliminate the surfactant adsorbed into the Si surface, the decomposition of hydrogen peroxide caused by a platinum catalyst is employed [9]. The high-purity, stabilizer-free hydrogen peroxide (30%), triggered by the catalytic action of platinum, is dissociated into  $(H^+ + HO_2^-)$ . Then, due to the oxidizing action of HO<sub>2</sub>, the surfactant adsorbed on the Si surface is decomposed and removed. The native oxide formed in the course of this treatment can be removed with diluted HF (0.5%). This series of treatments to remove the surfactant from the Si surface will be referred to as " $Pt + H_2O_2$ " treatment. Fig. 3(e) shows the  $C_{1s}$  peak of XPS after the "Pt+H2O2" treatment. The sub-peak signifying residual surfactant disappears, proving that the surfactant is successfully eliminated by this treatment. We have already confirmed that this treatment does not distort or transform the photoresist pattern. Hence, surfactant adsorption on the substrate, the only disadvantage of surfactant-added developer, can be overcome by the " $Pt + H_2O_2$ " treatment.

# D. Developing Selectivity

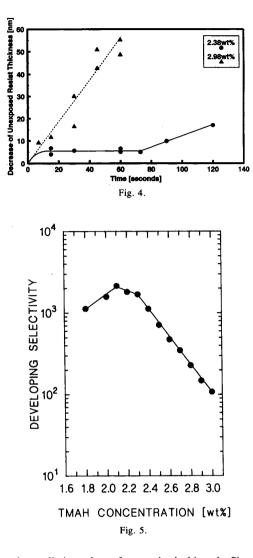

Fig. 4 shows the decrease in thickness of unexposed photoresist on a practical time scale. A Nanospec [Nanometrics Japan] was

employed to measure the thickness. In the case of developer with TMAH concentration of 2.98%, the decrease in film thickness is linear with immersion time. However, in the case of the developer with 2.38% TMAH, there is some delay in the reduction of the film thickness. This results from the formation of a surface-modified layer on the unexposed photoresist by TMAH [12].

Fig. 5 shows the developing selectivity of the dissolution rate between the exposed and unexposed photoresist. It reaches a peak of 2100 around the TMAH concentration of 2.1%; before and after this peak, the developing selectivity changes exponentially. Therefore, the developing selectivity is optimized at the TMAH concentration of 2.1%. Fig. 6 presents the profiles of the 0.8  $\mu$ m lineand-space resist patterns, formed by developers with TMAH concentrations of 1.8%, 2.1%, 2.4%, and 2.8%. At 2.1% TMAH, a sufficient profile is obtained.

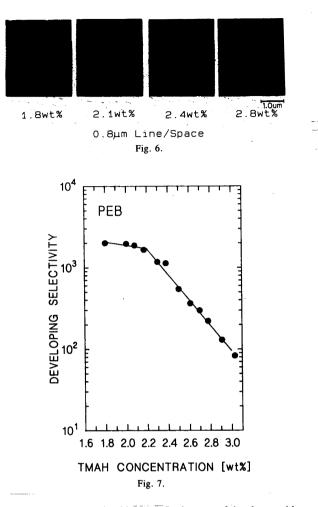

Fig. 7 exhibits the developing selectivity dependence on TMAH concentration when the PEB step is included. Unlike the developing selectivity of the conventional process, no peak is detected within the concentration range of 1.8%-3.0%. Instead, a gradual decrease is observed in the developing selectivity even when the concentration is below 2.2%.

# **IV.** CONCLUSIONS

It has been demonstrated that wettability of developer on photoresist can be improved by adding surfactant to the developer. This leads to the uniform dissolution of exposed photoresist and the maintenance of the Si surface smoothness. The uniform dissolution of exposed photoresist significantly improves the uniformity of the resist pattern on the entire wafer. In addition, surface smoothness of the Si substrate is crucial in the formation of thin oxides and shallow junctions. Surfactant injection to the developer left one single disadvantage: surfactant remains on the surface even after ultrapure water rinsing. This problem has been overcome by introducing the "Pt+H<sub>2</sub>O<sub>2</sub>" treatment. It has also been found that addition of the surfactant to the developer is essential in defining the fine photoresist patterns with sufficient reproducibility.

The developing selectivity of the dissolution rate in the exposed and unexposed regions is maximized when the TMAH concentration of the developer is 2.1%. The change in the reaction mechanism of dissolution has been detected around the TMAH concentration of 2.1% in the case of exposed photoresist, and around 2.3%in the case of unexposed photoresist. In the PEB process, the developing selectivity gradually goes up as the TMAH concentration drops below 2.2%. Therefore, in both the conventional photoresist process flow and the process flow with the PEB step included, the TMAH concentration of the developer is found to be optimized around 2.1%.

#### ACKNOWLEDGMENT

This study was carried out at the Super Clean Room of the Laboratory for Microelectronics, Research Institute of Electrical Communication, Tohoku University.

#### REFERENCES

- [1] H. Kikuyama, N. Miki, K. Saka, J. Takano, I. Kawanabe, M. Miyashita, and T. Ohmi, "Surface active buffered hydrogen fluoride having excellent wettability for ULSI processing," *IEEE Trans. Semicond. Manufact.*, vol. 3, pp. 99-108, Aug. 1990.

- [2] —, "Principle of wet chemical processing of ULSI micro fabrication," *IEEE Trans. Semicond. Manufact.*, vol. 4, Feb. 1991.

- [3] W. M. Moreau, Semiconductor Lithography. New York: Plenum, 1988, ch. 10.

- [4] M. Morita, T. Ohmi, E. Hasegawa, and A. Teramoto, "Native oxide growth on silicon surface in wet ambient," *Ext. Abs. of 22nd Int. Conf. on Solid State Devices and Materials*, Sendai, 1990, pp. 1063-1066.

- [5] T. Ohfuji, K. Yamanaka, and M. Sakamoto, "Characterization and modeling of high resolution positive photoresist," SPIE, vol. 920, Advances in Resist Technology and Processing V, 1988.

- [6] S. Kishimura, S. Uoya, A. Yamaguchi, and H. Nagata. "Photobleaching and dissolution characteristics of Novolak Naphtoquinonediazide type photoresist," *J. Photopolymer Sci. Technol.*, vol. 1, no. 1, pp. 104-113, 1988.

- [7] M. Hanabata, Y. Uetani, and A. Furuta, "Novolak design for high resolution positive photoresists (II): Stone wall model for positive photoresist development," SPIE, vol. 920, Advances in Resist Technology and Processing V, 1988.

- [8] W. A. Zisman, "Contact angle: Wettability and adhesion," F. M. Fowkkes Ed., Advances in Chemistry Series, vol. 43, ch. 1, American Chemical Society, Washington, D.C., 1967.

- [9] E. J. Walker, "Reduction of photoresist standing-wave effects by postexposure bake," *IEEE Trans. Electron Devices*, vol. ED-22, pp. 464– 466, July 1975.

- [10] T. Ohmi, M. Miyashita, M. Itano, T. Imaoka, and I. Kawanabe, "Dependence of thin oxide film quality on surface microroughness," *IEEE Trans. Electron Devices*, vol. 39, pp. 537-545, Mar. 1992.

- [11] T. Ohmi, K. Kotani, A. Teramoto, and M. Miyashita, "Dependence of electron channel mobility on Si-SiO<sub>2</sub> interface microroughness," *IEEE Electron Devices Lett.*, vol. 12, pp. 652-654, 1991.

[12] M. Endo, M. Sasago, K. Matsuoka, and N. Nomura, "High-aspect ratio resist pattern fabrication by alkaline surface treatment," J. Vac. Sci. Technol., vol. B7, no. 5, pp. 1076–1079, Sept.–Oct. 1989.

# Model-Based Emissivity Correction in Pyrometer Temperature Control of Rapid Thermal Processing Systems

# F. Yates Sorrell and Ronald S. Gyurcsik

Abstract—Single wavelength pyrometers are most often used to infer wafer temperature in Rapid-Thermal Processing (RTP) systems. A constant wafer emissivity is assumed with a pyrometer, but a variation in the wafer's surface emissivity can result in an error in the inferred temperature which effects the temperature control of the RTP system. A time-dependent variation is evident in Rapid Thermal Chemical Vapor Deposition where the emissivity is a function of the film type and thickness. This paper describes an approach which uses a physically based model of the emissivity variation as part of the feedback control loop.

#### I. INTRODUCTION

Rapid Thermal Processing (RTP) is a versatile, cold-wall, single-wafer approach suitable for several applications including annealing (RTA) [1], cleaning (RTC) [2], Chemical Vapor Deposition (RTCVD) [3], Oxidation (RTO) [4], and Nitridation (RTN) [2]. Single-wafer systems have an inherent advantage in wafer-towafer uniformity. In addition, the low thermal mass of a single wafer (as compared to a batch) allows the RTP system to rapidly increase wafer temperatures; the cold-wall system allows the wafer to be cooled at a greater rate as well. Overall, RTP is an attractive alternative as thermal budgets are reduced.

Rapid Thermal Processing (RTP) equipment typically use a single wavelength pyrometer to infer wafer temperature. The temperature is determined from the radiated intensity of the wafer which the pyrometer measures and the emissivity of the wafer at the specified wavelength of the pyrometer. The pyrometer is part of the RTP's control system; the lamp power is adjusted to keep the wafer at a desired temperature.

The wafer emissivity is a function of the composition and roughness of the wafer surface. For many applications such as rapid thermal annealing, the surface emissivity remains a constant throughout the process. However, for the applications where the characteristics of the surface are being changed, such as RTCVD, the emissivity is varying as a function of the type of film being deposited, the thickness of the film, and the composition of the

Manuscript received July 24, 1991; revised October 29, 1992. This work has been supported by the Semiconductor Research Corporation (Contract 88-MP-132), by the NSF Engineering Research Centers Program through the Center for Advanced Electronic Materials Processing (Grant CDR-8721505), and the North Carolina SEMATECH Center of Excellence (Contract 88-MC-809).

F. Y. Sorrell is with the Mechanical and Aerospace Department, North Carolina State University, Raleigh NC 27695.

R. S. Gyurcsik is with the Electrical and Computer Engineering Department, North Carolina State University, Raleigh NC 27695.

0894-6507/93\$03.00 © 1993 IEEE