# 40-Gb/s ICs for future lightwave communications systems

| 著者                | 尾辻泰一                                 |

|-------------------|--------------------------------------|

| journal or        | IEEE Journal of Solid-State Circuits |

| publication title |                                      |

| volume            | 32                                   |

| number            | 9                                    |

| page range        | 1363-1370                            |

| year              | 1997                                 |

| URL               | http://hdl.handle.net/10097/47717    |

doi: 10.1109/4.628741

## 40-Gb/s IC's for Future Lightwave Communications Systems

Taiichii Otsuji, Member, IEEE, Yuhki Imai, Member, IEEE, Eiichi Sano, Member, IEEE, Shunji Kimura, Member, IEEE, Satoshi Yamaguchi, Member, IEEE, Mikio Yoneyama, Member, IEEE, Takatomo Enoki, Member, IEEE, and Yohtaro Umeda, Member, IEEE

Abstract—This paper describes the device, circuit design, and packaging technologies applicable to 40-Gb/s-class future lightwave communications systems. A 0.1- $\mu$ m gate InAlAs/InGa-As high electron mobility transistors (HEMT's) with InP recess etch stopper was adopted mainly for IC fabrication. Fabricated IC's demonstrate excellent data-multiplexing, demultiplexing, and amplifying operation at 40 Gb/s.

*Index Terms*—Demultiplexing, distributed amplifiers, flip-flops, MODFET integrated circuits, multiplexing, optical fiber communication.

#### I. INTRODUCTION

**THERE** is an urgent need to expand transmission capacity because of the movement toward broadband integrated services digital network (ISDN) and multimedia services. Capacity will surely increase to terabits per second in the next century. At present, electrical time-division multiplexing and demultiplexing (ETDM), is the most mature system. Systems of 10 Gb/s are about to be brought into commercial use [1]. The record bit rate now exceeds 20 Gb/s/channel [2]. With the emergence of wavelength-division-multiplexing (WDM) technology, total transmission throughput has dramatically increased to beyond 1 Tb/s with 55 [3] and 132 [4] WDM channels. However, it is also true that the development of practical, dense WDM systems requires further technological advances in photonic components. Meanwhile, optical time division multiplexing (OTDM) systems are potential candidates for overcoming current performance limits [5], [6]. However, their applicability to commercial-level systems has yet to be studied.

In terms of system practicality, reliability, and cost, we still have to improve the speed of electronic IC's to around 40 Gb/s and more even though WDM and OTDM technologies relax the demands on the single-channel bit rate. Recently, several 40-Gb/s class IC's have been developed by using GaAs heterojunction bipolar transistors (HBT's) [7]–[9] and Si bipolar transistors [10], [11]. A 50-Gb/s Si bipolar multiplexer (MUX) [10] is an excellent result because of its relatively low transistor speed. But, a 40-Gb/s amplifier is really difficult to

Publisher Item Identifier S 0018-9200(97)05751-X.

Transmitter Receiver LD . MOD DRV: driver DRV MUX: multiplexer DIF Pre: preamplifier Base: baseband amp DEC REC Dist: distributor DEC: decision IC uх MUX DEMUX: demultiplexer DIF: differentiator DEMUX LD: laser diode Rec: Rectifier MOD: optical modulator RES: microwave resonator EDFA: fiber amp. Limit: Limiting amp. PD: photo detector DIV: frequency divider : Optical device Newly developed electronic device : Commercially available electronic device : Not necessary

Fig. 1. Basic transmitter and receiver configuration for lightwave communications systems.

make with Si bipolars. Even if we put decision circuits aside, no single process is yet able to cover all the key components.

This paper describes novel 40-Gb/s class analog and digital IC technologies along with their packaging technology for future lightwave communications systems. A 0.1- $\mu$ m gate InP-based high electron mobility transistor (HEMT) is mainly used for IC fabrication. In combination with high-speed, mature device technology and advanced circuit/package design technology, all the key components in the transmitter and the receiver achieve 40-Gb/s operation.

#### II. REQUIREMENTS FOR OPTICAL COMMUNICATION IC's

Fig. 1 depicts the basic transmitter and receiver configuration for lightwave communications systems. The functionality required for transmitter and receiver electronic IC's is basically the same (multiplexing, amplifying, retiming, regenerating, and demultiplexing) for all TDM and WDM transmission systems with the small exception of extra blocks (e.g., exclusive-OR or wideband mixer) for coherent systems. The transmitter block consists of a laser diode (LD), an optical modulator (MOD), a modulator driver (DRV), and multiplexers (MUX's). The receiver block consists of a photodiode (PD), a preamplifier (Pre), a baseband amplifier (Base), a decision circuit (DEC), demultiplexers (DEMUX's), and a clock recovery circuit that includes a differentiator (DIF), a rectifier (REC), a resonator (RES), and a limiting amplifier (Limit). The transmitter and receiver IC's, except for the clock recovery block, require broadband operation from near dc to the maximum bit rate with good eye openings.

0018-9200/97\$10.00 © 1997 IEEE

Manuscript received January 13, 1997; revised March 31, 1997.

T. Otsuji, Y. Imai, E. Sano, S. Kimura, S. Yamaguchi, T. Enoki, and Y. Umeda are with the NTT System Electronics Laboratories, Atsugi, Kanagawa, 243-01 Japan.

M. Yoneyama is with the NTT Optical Network Systems Laboratories, Yokosuka, Kanagawa, 239 Japan.

TABLE I LISTS OF OUR HIGH-END FRONT-END IC'S FOR HIGH-SPEED LIGHTWAVE COMMUNICATIONS SYSTEMS

| Circuit, Ref.           | Bandwidth/<br>Bit rate | Gain    | Output  | Power  | Device / Gate length      |

|-------------------------|------------------------|---------|---------|--------|---------------------------|

| 2:1 Multiplexer, [24]   | 46 Gbit/s              |         | 1.2 Vpp | 1.7 W  | InP HEMT / 0.1 µm         |

| Preamp., [17]           | DC - 32 GHz            | 9 dB    | 1.0 Vpp | 440 mW | InP HEMT / 0.1 $\mu$ m    |

| Baseband amp., [19]     | DC - 47 GHz            | 16 dB   | 1.2 Vpp | 1.1 W  | InP HEMT / 0.1 $\mu$ m    |

| Sig. distributor, [22]  | DC - 100 GHz           | -2.5 dB | 0.5 Vpp | 1.1 W  | InP HEMT / 0.1 µm         |

| Decision, [27]          | 8 - 24 Gbit/s          |         | 1.2 Vpp | 1.8 W  | GaAs MESFET / 0.2 $\mu$ m |

| 1:2 Demultiplexer, [24] | 1 - 40 Gbit/s          |         | 1.2 Vpp | 1.9 W  | InP HEMT / 0.1 $\mu$ m    |

| Freq. divider, [16]     | DC - 40.4 GHz          |         | 0.4 Vpp | 550 mW | InP HEMT / 0.1 $\mu$ m    |

| Limiting amp., [17]     | 34 - 40 GHz            | 17 dB   | 10 dBm  | 70 mW  | InP HEMT / 0.1 µm         |

|                         | 1                      |         | 1       | 1      |                           |

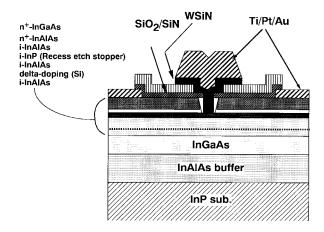

Fig. 2. Schematic of 0.1-µm gate InAlAs/InGaAs/InP HEMT.

#### III. DEVICE

For the device technology, InP-based HEMT's and HBT's are considered to be the best candidates for 40-Gb/s applications in terms of their speed performance [12], [13]. AlGaAs/GaAs HBT's [14] and 0.1-µm-class GaAs MESFET's [15] are the next best because of their relatively lower speed, but much greater maturity. A  $0.1-\mu m$  gate InAlAs/InGaAs HEMT [16] was adopted mainly for IC fabrication in this paper. Fig. 2 shows a schematic of the HEMT structure. We developed nonalloyed ohmic contacts using n<sup>+</sup>-InGaAs/n<sup>+</sup>-InAlAs layers and a T-shaped gate with a 0.1- $\mu$ m footprint to reduce the parasitic resistances. We also inserted a thin InP layer in the InAlAs barrier as a recess etch stopper. It greatly improved the threshold voltage uniformity because it enables the precise control of the barrier thickness. The average threshold voltage was -0.5 V and the standard deviation was less than 40 mV in a 2-in wafer. The average  $f_T$ ,  $f_{\text{max}}$ , and transconductance were 169 GHz, 264 GHz, and 1.0 S/mm, respectively. Moreover, low-loss pn-junction level-shift diodes were integrated instead of Schottky diodes using HEMT's, which reduced the turn-on resistance by a factor of two, resulting in faster circuit operation.

#### IV. CIRCUIT DESIGN

Table I summarizes the function blocks and corresponding performances of the electronic IC's we developed. All the analog and digital IC's, except the decision IC, achieved 40-Gb/s operation. In this section, we discuss the circuit design

100 Board PHYSICAL LENGTH (mm) Conventional Hybrid MMIC & MIC 10 LSI Distributed design  $L/\lambda = 1$ IC ventior vnthesis  $L/\lambda = 0.1$ 0.1 Tr Cool Cool Lumped desian  $(at \epsilon_r = 13)$ 0.01 DC 50 100 150 **FREQUENCY** (GHz)

Fig. 3. Ratio of physical length to wavelength for GaAs devices. It also shows the concept for ultra-broadband analog IC design.

technologies along with several IC fabrication results using InP HEMT's. We also describe the IC's using GaAs MESFET's for some cases.

#### A. Analog IC's

Fig. 3 shows the ratio of the physical length to the wavelength for GaAs devices. As data rates increase beyond 10 Gb/s, the wavelength of the signal approaches the physical size of IC chips, which gives rise to substantial difficulties in designing broadband IC's: 1) numerous parasitics, 2) cavity resonance, and 3) bandwidth limitation due to lumped-circuit treatment. Another difficulty is the requirement of broadbandwidth operation from dc to the maximum bit rate. These are the major reasons that transistor performance no longer directly reflects the circuit and module performance.

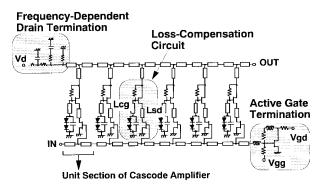

One approach to overcoming the performance limit is the synthesis of distributed and lumped-circuit design techniques. Fig. 4 shows the basic circuit diagram of our distributed amplifier for use in baseband operation [18]. Distributed amplifiers are commonly used in millimeter wave applications. Their great merit is that they can significantly widen the bandwidth. Each unit is a simple, small-sized cascode amplifier. The parasitic capacitance of FET's is effectively utilized as a circuit element to enable velocity-matched signal transmission between the gate input and drain output lines. However, we run into a serious problem when we try to apply this design to baseband amplifiers; namely, the drain conductance

Fig. 4. Basic circuit diagram of distributed amplifier for broadband application.

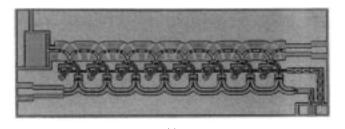

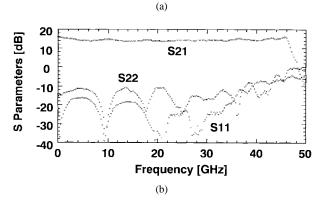

Fig. 5. (a) 16-dB gain, dc-to-47-GHz baseband amplifier chip microphoto and (b) measured S parameters.

of the FET's degrades the dc gain. To cope with this, a novel frequency-dependent bias termination was devised to compensate for the dc gain. Another wideband design we devised is the loss compensation circuit. The two additional transmission lines  $(L_{\rm cg}, L_{\rm sd})$  inserted here act as inductors to increase the negative resistance and thereby compensate for the loss at high frequencies. The active gate termination improves the noise figure at low frequencies.

A typical example is a dc-to-47-GHz, 16-dB distributed baseband amplifier IC using 0.1- $\mu$ m gate InP HEMT's [19]. The chip microphoto and its performance are shown in Fig. 5. The IC consumes 1.1 W. Its excellent gain-bandwidth product of 297 GHz owes to the loss-compensation circuit. We designed several baseband amplifier IC's with different gainbandwidth specs [20], [21].

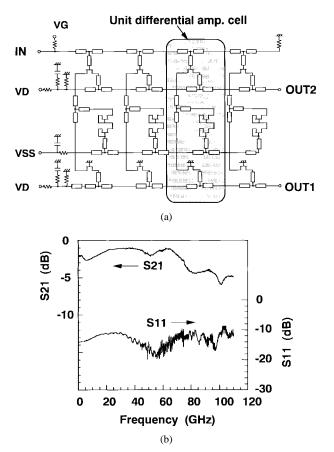

Another example of the distributed design is a dc-to-100-GHz 1:2 signal distributor IC using the 0.1- $\mu$ m-gate HEMT's [22]. The circuit diagram and its performance are shown in Fig. 6. One feature of the circuit design is the application of a distributed amplification technique to

Fig. 6. (a) DC-to-100-GHz, 1:2 signal distributor circuit diagram and (b) measured S parameters.

a differential circuit to enhance wideband performance. Conversion loss between the input and each output port is less than 2.5 dB below 70 GHz and less than 5 dB over the bandwidth. Another trial of distributed nonlinear baseband circuit is a dc-to-38-GHz distributed analog multiplier using the InP HEMT's [23].

#### B. Digital IC's

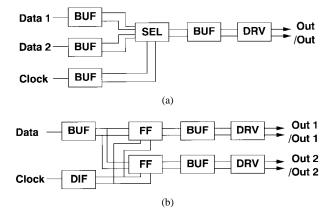

High-speed multiplexer (MUX) and demultiplexer (DE-MUX) IC's are key digital elements in transmitter and receiver hardware. We developed a 46-Gb/s 2:1 multiplexer IC and a 40-Gb/s 1:2 demultiplexer IC using the 0.1- $\mu$ m HEMT's [24]. The block diagrams of the MUX and DEMUX IC's are shown in Fig. 7. Both IC's are based on source-coupled FET logic (SCFL) circuitry and employ single-ended input and complementary output interfaces. So, the data and clock input buffer, output buffer, and driver circuit are integrated with the core cells. The SCFL configuration is best suited to InAlAs/InGaAs HEMT's that can provide only normally-on FET's (DFET's). This is because the SCFL circuit is configured with DFET's as well as with EFET's while keeping its high-speed potential.

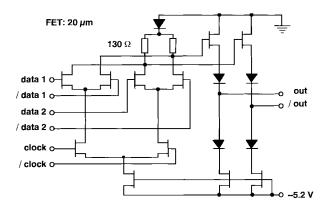

The core of the MUX has a simple SCFL series-gated selector circuitry with source followers at the output stage (shown in Fig. 8). Internal differential circuitry consists of 20- $\mu$ m FET's and 130- $\Omega$  load resistors. These conditions are the best for minimizing the gate propagation delay while

Fig. 7. Block diagrams of (a) MUX and (b) DEMUX IC's.

Fig. 8. Core SCFL selector circuit of 2:1 MUX.

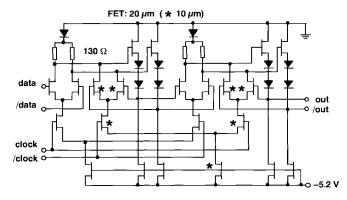

Fig. 9. Core HLO-type D-FF circuit of 1:2 DEMUX.

maintaining an SCFL output signal swing. The core of the DEMUX is a high-speed latching operation (HLO)-type D-FF (shown in Fig. 9) [25]. Although the reading circuit of the D-FF consists of 20- $\mu$ m FET's, the gate width of the latching differential pairs is reduced to 10  $\mu$ m. This results in 20% higher operation than when using a conventional master–slave D-FF and maintains a wide, quasi-static operation from 1 Gb/s.

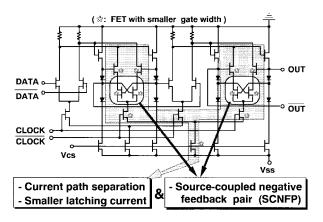

Improving the speed of an FF is the key to obtaining faster digital circuits. The trend indicates that the conventional master–slave FF can operate at speeds of one-fifth to one-fourth the transistor  $f_T$  for FET devices [26]. This means that a conventional master–slave D-FF needs 200-GHz transistors for 40-Gb/s operation. Even if we adopt an HLO-D-FF, the speed margin is insufficient. To overcome this, we devised

Fig. 10. Circuit diagram of super-dynamic D-FF circuit that can operate 30% faster than previously-reported D-FF's.

Fig. 11. Appearance of the chip-size-cavity packages for (a) analog IC's and (b) digital IC's.

a super-dynamic FF circuit that can operate 30% higher than previously-reported FF's [27]. Fig. 10 shows the circuit diagram. The circuit features 1) separation of the current path of the reading and latching circuits, 2) a smaller latching current than the reading current, and 3) a source-coupled negative feedback pair inserted in the latching differential pair. These circuit configurations boost the speed beyond the conventional-design limit because they reduce the load capacitance and effective logic swing without any degradation of the signal transition slew rate. The SD-FF provided a 24-Gb/s decision IC using production-level 0.2- $\mu$ m gate-length GaAs MESFET's having a  $f_T$  of 55 GHz [27].

A super-dynamic decision IC was also fabricated using the 0.1- $\mu$ m InP HEMT's. The simulated circuit speed exceeded 60 Gb/s. A 40-Gb/s error-free operation was confirmed. The details will be presented in [28].

#### C. Packaging

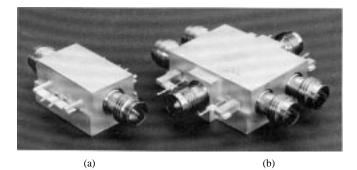

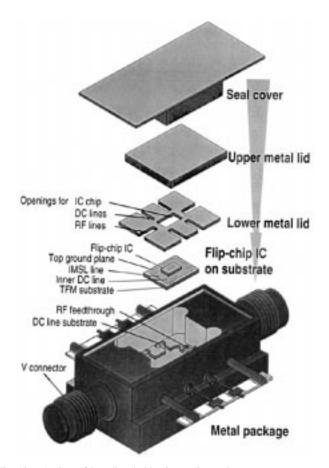

Packaging is another key technology for attaining ultrabroadband signal transmission without undesirable losses due to cavity and/or parasitic resonance and coupling. The basic structure we adopted is the so-called "chip-size cavity" package that minimizes the inner cavity [29]. We developed an improved version of the IC packages [30]. Fig. 11 shows the package views, one for (a) analog IC's and one for (b) digital IC's. The RF ports are made with V-band coaxial connectors. The digital-type package can accommodate up to six RF ports. Fig. 12 shows the package structure. A die is mounted on an

Fig. 12. A view of broadband chip-size cavity package.

inner thin-film multilayer interconnection substrate by means of flip-chip bonding or ribbon bonding. The upper and lower metal lids reduce the size of the inner cavity so as to shift undesirable cavity resonance out of the transmission band. The module with metal lids had a high isolation of more than 60 dB up to 50 GHz. The result agrees well with electromagnetic field analysis [30]. One feature of this module structure is flexibility. If you mount a different type of chip, the design of only the core substrate and the lower lid is subject to change.

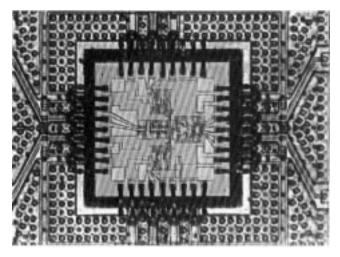

The HEMT baseband amplifier was mounted in the analogtype package using ribbon bonding. Both the MUX and DEMUX chips were mounted in the digital-type package using ribbon bonding. The top view of the ribbon-bonded MUX chip is shown in Fig. 13.

#### V. 40-Gb/s TRANSMISSION EXPERIMENTS

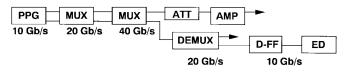

Amplifying, multiplexing, and demultiplexing operations of the packaged IC's were tested at 40-Gb/s and higher. Fig. 14 shows the experimental setup. A complementary pair of fundamental pseudorandom data streams (PN  $2^7 - 1$  to  $2^{23} - 1$ ) up to 11.5 Gb/s were generated from a pulse pattern generator (PPG). These were duplexed with appropriate delay against each other by using a GaAs MESFET MUX unit [31] to obtain complementary data streams up to 25 Gb/s, and then input to the MUX module, also with appropriate delay against each other. One MUX output was used as the input of the HEMT amplifier or the DEMUX data input, while

Fig. 13. Top view of the ribbon-bonded MUX chip on a thin-film multilayer substrate.

Fig. 14. Experimental set up. PPG: pulse pattern generator; ATT: attenuator; AMP: amplifier; and ED: error detector.

the other was monitored by an HP 54124T digitizing scope. The DEMUX output was again demultiplexed down to the fundamental data rate, and then input to a bit error rate test system. Clock signals for the MUX and the DEMUX were generated by synthesized signal sources whose time bases (10 MHz) were synchronized to the PPG.

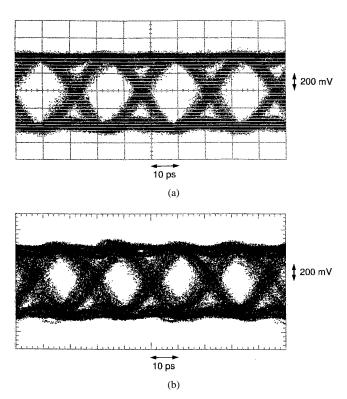

The output eye diagrams of the MUX at 40 Gb/s and 46 Gb/s are shown in Fig. 15. There is no waveform deterioration at 40 Gb/s and very clear eye opening was obtained. At 46 Gb/s the output eye is still open. The flat low- and high-level traces demonstrate the flat and broadband performances of the packaging technology.

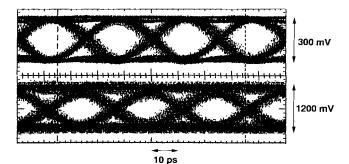

The output eye diagrams of the amplifier at 40 Gb/s are shown in Fig. 16. When the input data (from the MUX output) was attenuated to 300 mVp-p, an output amplitude of 1200 mVp-p was obtained with a good eye opening.

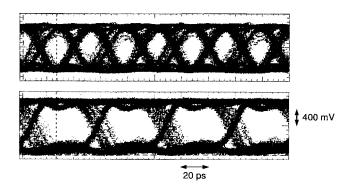

Fig. 17 shows that when the 40-Gb/s data input from the MUX module was intentionally distorted (equivalent input phase deviation was  $\pm$  60°), clear eye opening was obtained from the DEMUX output although the jitter was increased at the fall transition. Under the above conditions, stable MUX and DEMUX operation at 40 Gb/s was obtained and error-free operation was confirmed.

The MUX module was utilized for the first experiment of electrically multiplexed 40-Gb/s  $\times$  4 channel WDM transmission over a 320-km dispersion-shifted fiber [32], and error-free operation with sensitivity degradation of less than 1 dB was successfully achieved. Furthermore, the MUX can directly drive a recently developed MQW electroabsorption optical modulator [33] at bit rates up to 40 Gb/s. The MUX module also verified 40-Gb/s operation of recently developed light source module where a distributed feedback (DFB) laser

Fig. 15. Output eye patterns of the MUX module at (a) 40 Gb/s and (b) 46 Gb/s.

Fig. 16. Output eye patterns of the amplifier module.

Fig. 17. Output eye patterns of the DEMUX module. Input eye patterns are intentionally degraded to demonstrate the retiming performance of the DEMUX.

and an electroabsorption MQW modulator are monolithically integrated [34]. By using the MUX and DEMUX module, the first experiment of 40-Gb/s fully electrical time-division multiplexed and demultiplexed transmission over 40-km dispersionshifted fiber was successfully performed [35].

### VI. CONCLUSION

We discussed device, circuit design, and package design technologies applied to future very-high-speed optical communications systems. The synthesis of distributed and lumped circuit design is the key to analog IC's. The digital IC's stay in a relatively lower stage and making full use of analog circuit design in digital IC's is the key to obtaining faster speeds. In fact, introduction of distributed design into digital IC's (especially for sequential circuits such as flip-flops) is really difficult because propagation delay time along with critical signal path limits speed performance. The chip-size cavity structure we developed is quite simple and brought parasitic-free, broadband circuit operation from dc to beyond 50 GHz. Even in the early development stage, the developed IC's and modules show promising performance suited to 40-Gb/s applications. We are now ready to establish fully electrically multiplexed and demultiplexed 40-Gb/s data transmission systems. We are continuing to push toward higher speed operations as well as the further integration of several functional blocks into a single or multichip module. We believe the IC design technology described here will have a great impact on future lightwave communications systems.

#### ACKNOWLEDGMENT

The authors would like to thank S. Horiguchi, J. Yoshida, Y. Ishii, Y. Akazawa, and K. Hagimoto for their direction and encouragement. They also thank T. Shibata, M. Nakamura, and H. Kimura for their contribution throughout this work.

#### References

- K. Hagimoto, "Experimental 10 Gbit/s transmission systems and its IC technology," in *GaAs IC Symp. Tech. Dig.*, 1993, pp. 7–10.

A. H. Gnauck, R. M. Derosier, F. Forghieri, R. W. Tkach, A. M.

- [2] A. H. Gnauck, R. M. Derosier, F. Forghieri, R. W. Tkach, A. M. Vengsarkar, D. W. Peckham, J. L. Zyskind, J. W. Sulhoff, and A. R. Chraplyvy, "Transmission of 8 20-Gb/s channels over 232 km of conventional fiber," in *OFC'95 Tech. Dig.*, 1995, PD23.

- [3] H. Onaka, H. Miyata, G. Ishikawa, K. Otsuka, H. Ooi, Y. Kai, S. Kinoshita, M. Seino, H. Nishimoto, and T. Chikama, "1.1 Tb/s WDM transmission over a 150 km, 1.3 μm zero-dispersion single-mode fiber," in *OFC'96 Tech. Dig.*, 1996, PD19-1.

- [4] Y. Yano, T. Ono, K. Fukuchi, T. Ito, H. Yamazaki, M. Yamaguchi, and K. Emura, "2.6 Terabit/s WDM transmission experiment using optical duobinary coding," in *ECOC'96 Tech. Dig.*, 1996, pp. 5.3–5.6.

- [5] S. Kawanishi, H. Takara, T. Morioka, O. Kamatani, K. Takiguchi, T. Kitoh, and M. Saruwatari, "Single channel 400 Gbit/s time-division-multiplexed transmission of 0.98 ps pulses over 40 km employing dispersion slope compensation," *IEE Electron. Lett.*, vol. 32, no. 10, pp. 916–918, 1996.

- [6] M. Nakazawa, E. Yoshida, K. Suzuki, T. Kitoh, and M. Kawachi, "80 Gbit/s soliton data transmission over 500 km with unequal amplitude solitons for timing clock extraction," *IEE Electron. Lett.*, vol. 30, no. 21, pp. 1777–1778, 1994.

- [7] Y. Kuriyama, M. Asaka, T. Sugiyama, N. Iizuka, and M. Obara, "Over 40 Gbit/s ultra-high-speed multiplexer IC implemented with high fmax AlGaAs/GaAs HBT's," *IEE Electron. Lett.*, vol. 30, no. 5, pp. 401–402, 1994.

- [8] Y. Kuriyama, T. Sugiyama, S. Hongo, J. Akagi, K. Tsuda, N. Iizuka, and M. Obara, "A 40 GHz D-type flip-flop using AlGaAs/GaAs HBT's," in *GaAs IC Symp. Tech. Dig.*, 1994, pp. 189–192.

- [9] K. Runge, R. L. Pierson, P. J. Zampardi, P. B. Thomas, J. Yu, and K. C. Wang, "40 Gbit/s AlGaAs/GaAs HBT 4:1 multiplexer IC," *IEE Electron. Lett.*, vol. 31, no. 11, pp. 876–877, 1995.

- [10] A. Felder, M. Möller, J. Popp, J. Bock, and H.-M. Rein, "46 Gb/s DEMUX, 50 Gb/s MUX, and 30 GHz static frequency divider in silicon bipolar technology," *IEEE J. Solid-State Circuits*, vol. 31, no. 4, pp. 481–486, 1996.

- [11] J. Bock, A. Felder, T. F. Meister, M. Franosch, K. Aufinger, M. Wurzer, R. Schreiter, S. Boguth, and L. Treitinger, "A 50 GHz implanted base silicon bipolar technology with 35 GHz static frequency divider," in *Symp. VLSI Tech. Dig. Tech. Papers*, 1996, pp. 108–109.

- [12] Y. Ishii, "Fabrication technologies of InP-based digital IC's and MMIC's," in 8th Int. Conf. InP and Related Materials, Proc., 1996, pp. 53–56.

- [13] S. Yamahata, K. Kurishima, H. Ito, and Y. Matsuoka, "Over-220-GHz- $f_T$ -and- $f_{max}$  InP/InGaAs double-heterojunction bipolar transistors with a new hexagonal-shaped emitter," in *GaAs IC Symp. Tech. Dig.*, 1995, pp. 163–166.

- [14] Y. Matsuoka and E. Sano, "High-speed AlGaAs/GaAs HBT's and their applications to 40-Gbit/s-class IC's," in *GaAs IC Symp. Tech. Dig.*, 1994, pp. 185–188.

- [15] Y. Yamane, K. Nishimura, K. Inoue, and M. Tokumitsu, "0.1-μm GaAs MESFET's fabricated using ion-implantation and photolithography," in *GaAs IC Symp. Tech. Dig.*, 1993, pp. 185–188.

- [16] T. Enoki, Y. Úmeda, K. Ösafune, H. Ito, and Y. Ishii, "Ultra-high-speed InAlAs/InGaAs HEMT IC's using pn-level-shift diodes," in *IEDM Tech. Dig.*, pp. 193–196, 1995.

- [17] Y. Imai, M. Nakamura, S. Kimura, Y. Umeda, and T. Enoki, "40-Gb/sclass InP HEMT IC's for very-high-speed optical communications," in *7th Int. Conf. InP and Related Materials, Proc.*, 1995, pp. 89–92.

- [18] S. Kimura and Y. Imai, "DC-to-40-GHz GaAs MESFET distributed baseband amplifier IC," in Asia Pacific Microwave Conf. Tech. Dig., 1994, pp. 249–252.

- [19] S. Kimura, Y. Imai, Y. Umeda, and T. Enoki, "A DC-to-50-GHz InAlAs/InGaAs HEMT distributed baseband amplifier using a new loss compensation technique," in *GaAs IC Symp. Tech. Dig.* 1994, pp. 96–99.

- compensation technique," in *GaAs IC Symp. Tech. Dig.*, 1994, pp. 96–99.

[20] S. Kimura, Y. Imai, and Y. Miyamoto, "Novel distributed baseband amplifying techniques for 40-Gbit/s optical communication," in *GaAs IC Symp. Tech. Dig.*, 1995, pp. 193–196.

- [21] H. Tsuda, Y. Miyamoto, A. Kano, K. Kato, Y. Imai, and K. Hagimoto, "40-Gb/s baseband-type optical receiver module using a waveguide photodetector and a GaAs MESFET distributed amplifier IC," in OECC'96, 19A1-2.

- [22] Y. Imai, S. Kimura, T. Enoki, and Y. Umeda, "A DC-to-100-GHz InP HEMT 1:2 distributor IC using distributed amplification," *IEEE Microwave Guided Wave Lett.*, vol. 6, no. 7, pp. 256–258, 1996.

- [23] Y. Imai, S. Kimura, Y. Umeda, and T. Enoki, "A DC to 38-GHz distributed analog multiplier using InP HEMT's," *IEEE Microwave Guided Wave Lett.*, vol. 4, no. 12, pp. 399–402, 1994.

- [24] T. Otsuji, M. Yoneyama, Y. Imai, S. Yamaguchi, T. Enoki, Y. Umeda, and E. Sano, "46 Gbit/s multiplexer and 40 Gbit/s demultiplexer IC modules using InAlAs/InGaAs/InP HEMT's," *IEE Electron. Lett.*, vol. 32, no. 7, pp. 685–686, 1996.

- [25] K. Murata, T. Otsuji, M. Ohhata, M. Togashi, E. Sano, and M. Suzuki, "A novel high-speed latching operation flip-flop (HLO-FF) circuit and its application to a 19 Gb/s decision circuit using 0.2 μm GaAs MESFET," in *GaAs IC Symp. Tech. Dig.*, 1994, pp. 193–196.

- [26] E. Sano, Y. Matsuoka, and T. Ishibashi, "Device figure-of-merits for high-speed digital IC's and baseband amplifiers," *IEICE Trans. Electron.*, vol. E78-C, no. 9, pp. 1182–1188, 1995.

- [27] T. Otsuji, M. Yoneyama, K. Murata, and E. Sano, "A super-dynamic flip-flop circuit for broadband applications up to 24-Gbit/s utilizing production-level 0.2-μm GaAs MESFET's," in *GaAs IC Symp. Tech. Dig.*, 1996, pp. 145–148.

- [28] M. Yoneyama, A. Sano, H. Hagimoto, T. Otsuji, K. Murata, Y. Imai, S. Yamaguchi, T. Enoki, and E. Sano, "Optical repeater circuits using 40-Gbit/s InAlAs/InGaAs HEMT's digital IC chipset," in *IEEE MTT-S Int. Microwave Symp. Tech. Dig.*, 1997.

- [29] T. Shibata, S. Kimura, H. Kimura, Y. Imai, Y. Umeda, and Y. Akazawa, "A design technique for a 60 GHz bandwidth distributed baseband amplifier IC Module," *IEEE J. Solid-State Circuits*, vol. 29, no. 12, pp. 1537–1543, 1994.

- [30] S. Yamaguchi, Y. Imai, S. Kimura, and H. Tsunetsugu, "New module structure using flip-chip technology for high-speed optical communication IC's," in *IEEE MTT-S Int. Microwave Symp. Tech. Dig.*, 1996, pp. 243-246.

- [31] M. Ohhata, M. Togashi, K. Murata, S. Yamaguchi, "25 Gbit/s selector module using 0.2 μm GaAs MESFET technology," *Electron. Lett.*, vol. 29, pp. 950–951, 1993.

- [32] S. Kuwano, N. Takachio, K. Iwashita, T. Otsuji, Y. Imai, T. Enoki, K. Yoshino, and K. Wakita, "160 Gbit/s (4 ch × 40 Gbit/s electrically

multiplexed data) WDM transmission over 320 km dispersion-shifted fiber," in *OFC'96 Tech. Dig.*, 1996, PD10.

- [33] K. Yoshino, K. Wakita, I. Kotaka, S. Kondo, Y. Noguchi, S. Kuwano, N. Takachio, T. Otsuji, Y. Imai, and T. Enoki, "40-Gbit/s operation of polarization-independent InGaAs/InAlAs MQW electroabsorption modulator with very low driving-voltage," in *ECOC'96 Tech. Dig.*, 1996, pp. 3.203–3.206.

- [34] H. Takeuchi, K. Tsuzuki, K. Sato, M. Yamamoto, Y. Itaya, A. Sano, M. Yoneyama, and T. Otsuji, "NRZ Operation at 40 Gbit/s of a compact module with an MQW electroabsorption modulator integrated DFB laser," in *ECOC'96 Tech. Dig.*, 1996, pp. 5.55–5.58.

- [35] K. Hagimoto, M. Yoneyama, A. Sano, A. Hirano, T. Kataoka, T. Otsuji, K. Sato, and K. Noguchi, "Limitations and challenges of single carrier full 40-Gbit/s repeater system based on optical equalization and new circuit design," in *OFC'97 Tech. Dig.*, 1997, pp. 242–243.

Taiichi Otsuji (M'91), for a photograph and biography, see this issue, p. 1362.

Yuhki Imai (M'92) was born in Tokyo, Japan, in 1955. He received the B.S., M.E., and Dr. Eng. degrees in applied physics from Waseda University, Tokyo, Japan, in 1977, 1979, and 1991, respectively.

In 1979 he joined the NTT Electrical Communication Laboratories, Atsugi, Japan. He has been engaged in the research of microwave GaAs and InP MESFET fabrication technologies, low-current GaAs MMIC design for mobile communications, and high-speed GaAs IC design for 10 Gb/s lightwave communications. He is now engaged in the

research of future very high-speed IC design using GaAs and InP-based devices.

Dr. Imai is a member of the Institute of Electronics, Information and Communication Engineers (IEICE) of Japan.

Eiichi Sano (M'84), for a photograph and biography, see this issue, p. 1362.

Shunji Kimura (M'92) was born in Tokyo, Japan, on January 28, 1967. He received the B.S. and M.S. degrees in electrical engineering from Waseda University, Tokyo, Japan, in 1989 and 1991, respectively.

In 1991 he joined Nippon Telegraph and Telephone Corporation (NTT) LSI Laboratories, Kanagawa, Japan, and is now with NTT System Electronics Laboratories, Atsugi, Japan. He has been engaged in design and evaluation of microwave and millimeter-wave monolithic integrated circuits for

optical transmission systems.

Mr. Kimura received the Japan Microwave Prize at the 1994 Asia-Pacific Microwave Conference. He is a member of the Institute of Electronics, Information and Communication Engineers (IEICE) of Japan and the Japan Physical Society.

Satoshi Yamaguchi (M'92) was born in Yamagata, Japan, on August 31, 1963. He received the B.S. and M.S. degrees in metallurgy from the University of Tohoku, Sendai, Japan, in 1986 and 1988, respectively.

In 1988, he joined the NTT LSI Laboratories, Nippon Telegraph and Telephone Corporation, Atsugi, Japan, where he has been engaged in research on the design of high-speed digital IC's and their module for optical communication systems.

Mr. Yamaguchi is a member of the Institute of Electronics, Information and Communication Engineering (IEICE) of Japan.

Mikio Yoneyama (M'93), for a photograph and biography, see this issue, p. 1362.

**Takatomo Enoki** (M'91) was born in Tottori, Japan, on November 19, 1959. He received the B.S. and M.S. degrees in physics and the Ph.D. degree in electronic and electrical engineering from the Tokyo Institute of Technology, Tokyo, Japan, in 1982, 1984, and 1996, respectively.

He joined the Atsugi Electrical Communications Laboratories of NTT, Kanagawa, Japan, in 1984. Since then, he has been engaged in research and development work on fabrication technologies for high-frequency and high-speed GaAs MESFET's

and IC's. Since 1989, he has studied and developed ultra-high speed and low noise heterojunction FET's and their IC's on an InP substrate. He is currently a Senior Research Engineer of the NTT System Electronics Laboratories.

Dr. Enoki is a member of the Institute of Electronics, Information and Communication Engineers (IEICE) of Japan and the Japan Society of Applied Physics.

**Yohtaro Umeda** (M'89) was born in Kanagawa, Japan, on September 1, 1957. He received the B.S. and M.S. degrees in physics from the University of Tokyo, Japan, in 1982 and 1984, respectively.

In 1984 he joined Nippon Telegraph and Telephone Corporation. He is currently with NTT System Electronics Laboratories, Kanagawa, Japan, engaged in the study on microwave characteristics of HEMT's on InP and its application to MMIC's and digital IC's.

Mr. Umeda is a member of the Institute of Electronics, Information and Communication Engineers (IEICE) of Japan.