# Suppression of SiN-induced boron penetration by using SiH-free silicon nitride films formed by tetrachlorosilane and ammonia

| 著者                | 田中 徹                                  |

|-------------------|---------------------------------------|

| journal or        | IEEE Transactions on Electron Devices |

| publication title |                                       |

| volume            | 49                                    |

| number            | 9                                     |

| page range        | 1526-1531                             |

| year              | 2002                                  |

| URL               | http://hdl.handle.net/10097/47475     |

doi: 10.1109/TED.2002.802630

# Suppression of SiN-Induced Boron Penetration by Using SiH-Free Silicon Nitride Films Formed by Tetrachlorosilane and Ammonia

Masayuki Tanaka, Shigehiko Saida, Ichiro Mizushima, Fumihiko Inoue, Manabu Kojima, Tetsu Tanaka, Toshiro Nakanishi, Kyoichi Suguro, and Yoshitaka Tsunashima

Abstract—Applications of SiH-free silicon nitride (SiN) films, formed by tetrachlorosilane (TCS) and ammonia, have been proved to effectively suppress the SiN-induced boron penetration. The SiN-induced boron penetration has been investigated in detail by using boron-doped polysilicon gated capacitors with several kinds of thick SiN films. It was clarified for the first time that the SiN-induced boron penetration becomes worse with SiH content in SiN films and deposition technique of SiH-free TCS-SiN films is essential for realization of the high-performance PMOSFETs.

Index Terms—Boron penetration, hydrogen, silicon nitride.

#### I. INTRODUCTION

■ HE BORON penetration from p<sup>+</sup> doped polysilicon gates through the gate oxide and into the channel region is a serious problem for realization of high-performance devices with scaled technology [1]. It is known that the boron penetration is enhanced by the existence of conventional SiN films [1]. However, the SiN film is necessary for realization of next-generation devices since it is useful with a wide variety of applications. For example, in the case of next-generation DRAMs, high density and high performance should be realized by the structure of the CMOS system with the thick SiN films. Thick SiN films are necessary as a hard mask for a self-align contact process [2], [3] to increase the density. Dual-gate CMOS systems should be applied to improve the performance, where a boron-doped polysilicon is used for a gate electrode of PMOSFETs. In addition, many high-temperature process steps are performed after SiN deposition. These are all needed for realization of next-generation DRAMs, but they increasingly enhance the boron penetration by the existence of thick conventional SiN films. This SiN-induced boron penetration is becoming an increasingly serious problem.

There are possible countermeasures to suppress this SiN-induced boron penetration, but they have negative effects on the

Manuscript received March 12, 2002; revised June 7, 2002. The review of this paper was arranged by Editor J. Vasi.

F. Inoue is with Fujitsu Limited, Kamagawa, Japan.

M. Kojima, T. Tanaka, and T. Nakanishi are with Fujitsu Laboratories Limited Kamagawa Janan

Publisher Item Identifier 10.1109/TED.2002.802630.

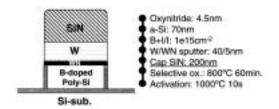

Fig. 1. Sample structure and fabrication process.

device performance. For example, decrease of the boron concentration increases gate depletion. Lowering of the process temperature decreases activation efficiency. Increase of nitrogen concentration of gate oxynitride decreases transconductance of PMOSFETs. Therefore, the most intrinsic and effective solution is to develop new SiN films without the SiN-induced boron penetration.

The phenomenon of the SiN-induced boron penetration was reported in 1990 [1], but there has been no report about its origin or an effective means of suppression yet. This paper clarifies the cause of the SiN-induced boron penetration, and also demonstrates the realization of high-performance PMOSFETs without the SiN-induced boron penetration by using SiH-free SiN films formed by tetrachlorosilane and ammonia.

### II. SAMPLE STRUCTURE AND FABRICATION PROCESS

Fig. 1 shows a schematic drawing of a sample structure. Polymetal gate was used for transistor devices [4]. Pure p<sup>+</sup> polysilicon gate was used for capacitor devices fabricated on P-type substrate.

Sample fabrication flow is also shown in Fig. 1. Gate oxynitride was formed by NO oxynitridation of a base oxide. Final ellipsometric film thickness was 4.5 nm. Polysilicon of 175-nm thickness was formed by the LP-CVD technique for capacitor devices, whereas amorphous silicon of 70-nm thickness was formed for transistor devices. Then, boron of 1e15 cm<sup>-2</sup> was implanted in both devices with dose energy of 5 keV for PMOS devices, whereas phosphorous of 1e15 cm<sup>-2</sup> with dose energy 10 keV for NMOSFETs. SiN films of 200-nm thickness were formed with the LP-CVD technique on the gates. Detailed deposition condition and film properties will be described in the following paragraph. After gate electrode formation by using a conventional RIE technique, post-oxidation was performed at 800 °C, 60 min, and activation anneal at 1000 °C, 10 s.

M. Tanaka is with the Process and Manufacturing Engineering Center, Semiconductor Company, Toshiba Corp., Kanagawa 235-8522, Japan (e-mail: masayuki7.tanaka@toshiba.co.jp).

S. Saida, I. Mizushima, K. Suguro, and Y. Tsunashima are with Toshiba Corporation, Kanagawa 235-8522, Japan.

| Si-source | Deposition<br>Temperature<br>(°C) | Gas flow<br>NH3/Si-source<br>(sccm/sccm) | Pressure<br>(Pa) | Deposition<br>rate<br>(nm/min.) | Refractive index | N/Si<br>ratio | Density | CI<br>content<br>(cm <sup>-3</sup> ) |

|-----------|-----------------------------------|------------------------------------------|------------------|---------------------------------|------------------|---------------|---------|--------------------------------------|

|           |                                   |                                          |                  |                                 |                  |               | (g/cm³) |                                      |

| DCS       | 780                               | 800/80                                   | 67               | 4.8                             | 2.00             | 1.30          | 2.76    | 8x10 <sup>19</sup>                   |

| TCS       | 780                               | 800/80                                   | 67               | 1.2                             | 1.97             | 1.34          | 2.62    | 1x10 <sup>20</sup>                   |

| HCD       | 650                               | 1000/10                                  | 67               | 3.0                             | 2.03             | 1.24          | 2.44    | 8x10 <sup>20</sup>                   |

TABLE I

DEPOSITION CONDITION AND PROPERTIES OF SIN FILM

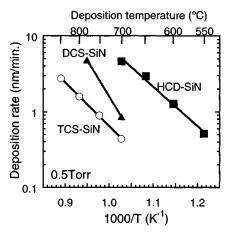

Fig. 2. Deposition rate of DCS-, TCS-, and HCD-SiN films.

#### III. DEPOSITION CONDITION AND PROPERTIES OF SiN FILMS

Three silicon sources were used for SiN deposition with a wide range of deposition temperature from 650 °C to 780 °C. With the use of these various deposition conditions, SiN films show a wide variety of properties. The three Si sources were: dichlorosilane (DCS, SiH<sub>2</sub>Cl<sub>2</sub>) a conventional Si source for mass production, tetrachlorosilane (TCS, SiCl<sub>4</sub>) a fully chlorine terminated Si source [5], and hexachlorodisilane (HCD, Si<sub>2</sub>Cl<sub>6</sub>) a fully chlorine terminated Si source for a low temperature deposition [6], [7].

Deposition conditions, deposition characteristics and film properties of SiN films are summarized in Table I. SiN films were formed on device samples under the conditions listed in the table. Deposition temperature dependences of deposition rates are shown in Fig. 2. TCS-SiN film shows the lowest deposition rate, with a deposition rate one-fourth that of DCS-SiN film at 780 °C under the same deposition condition. HCD-SiN film shows the highest deposition rate, because of its disilane-compound nature [8]. Activation energy of DCS, TCS, and HCD-SiN film deposition was deduced to be 1.9 eV, 1.1 eV, and 1.0 eV, respectively. Obtained values are almost the same as reported ones [6], [9].

As shown in Table I, TCS-SiN film shows the smallest refractive index because of its nitrogen-rich composition and smaller density than DCS-SiN film. DCS-SiN film shows the highest density with intermediated refractive index and N/Si ratio between TCS- and HCD-SiN films. HCD-SiN film shows the largest refractive index because of its Si-rich composition

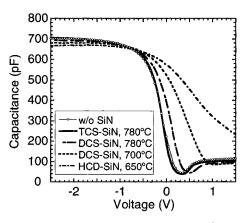

Fig. 3. Capacitance–voltage (C-V) characteristics of the p<sup>+</sup> polysilicon gated capacitors with DCS-, TCS-, and HCD-SiN films formed with the deposition temperature ranging from 650 °C to 780 °C.

and it shows the smallest density with the largest chlorine content because of insufficient thermal budget; the lowest deposition temperature and the largest deposition rate.

# IV. BORON PENETRATION OF p<sup>+</sup> POLYSILICON-GATED CAPACITORS WITH SEVERAL TYPES OF SiN FILMS

It is clarified for the first time from the capacitor measurements of p<sup>+</sup> polysilicon gated capacitors with several types of SiN films that the SiN-induced boron penetration is suppressed by the application of TCS-SiN films, and it becomes worse with decreasing deposition temperature.

Fig. 3 shows capacitance–voltage (C-V) characteristics of  $p^+$  polysilicon gated capacitors with several types of SiN films measured with a rectangle area of 0.1 mm<sup>2</sup> using 100 kHz frequencies. In Fig. 3, the result for the sample without SiN film is also shown as a reference, showing ideal characteristics without the SiN-induced boron penetration.

As shown in Fig. 3, the SiN-induced boron penetration has been successfully suppressed by the sample with TCS-SiN films showing almost the same characteristics as the sample without SiN film. On the other hand, the sample with DCS-SiN films apparently shows the boron penetration with positive stretch-out of C-V characteristics resulting in positive flat-band voltage  $(V_{fb})$  shift, and also gate depletion at accumulation region. In addition, the sample with DCS-SiN films clearly shows deposition temperature dependence, namely the SiN-induced boron penetration becomes worse with decreasing deposition temperature,

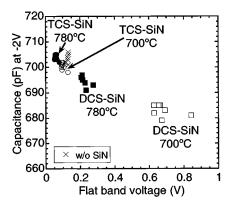

Fig. 4. Relationships between  $V_{fb}$  and capacitance of seven capacitors within wafer.

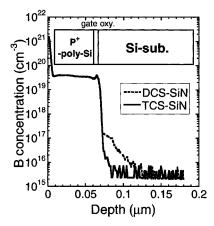

Fig. 5. Boron depth profiles of p<sup>+</sup> polysilicon gated capacitors with DCS- or TCS-SiN film analyzed by backside SIMS.

showing larger positive  $V_{fb}$  shift and the gate depletion compared with the sample with DCS-SiN films formed at 780 °C and 700 °C. HCD-SiN film formed at the lowest deposition temperature of 650 °C shows the worst characteristics.

The variation of  $V_{fb}$  within wafer has also been suppressed by the application of TCS-SiN films. Fig. 4 shows  $V_{fb}$  values of seven capacitors within wafer. High performance is realized for the smaller  $V_{fb}$  with the larger capacitance, indicating better characteristics with the smaller boron penetration. As is clear from Fig. 4, application of TCS-SiN films has realized high performance of  $p^+$  gated capacitor, suppressing the  $V_{fb}$  shift, gate depletion, and also deviation of  $V_{fb}$ .

The sample with TCS-SiN film shows no significant amount of boron in channel region, confirmed by backside secondary ion mass spectroscopy (SIMS) measurements, as shown in Fig. 5. Sample structure and fabrication process are the same as for the capacitor sample. The sample with DCS-SiN film, showing the positive  $V_{fb}$  shift, gate depletion and the variation of  $V_{fb}$ , apparently shows large amount of boron in channel region.

## V. THE ORIGIN OF THE SiN-INDUCED BORON PENETRATION

The SiN-induced boron penetration has been investigated with special attention to the hydrogen content in SiN films, since a hydrogen gas annealing has been reported to enhance the boron penetration [10]–[12].

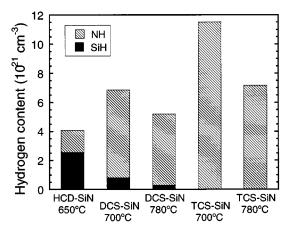

Fig. 6. SiH and NH content of various SiN films analyzed by FT-IR.

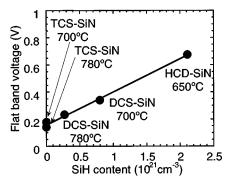

Fig. 7. Relationships between  $V_{fb}$  and SiH content in SiN films.

Hydrogen exists in SiN films as two types of bonding species, namely, SiH and NH. Fig. 6 shows hydrogen content and ratio of SiH and NH for various SiN films analyzed by the FT-IR method. Content of SiH and NH is derived from the respective signal by using the FT-IR method [13]. TCS-SiN film shows the largest hydrogen content but does not show detectable SiH. The content of SiH is supposed to be below 1e20 cm<sup>-3</sup>. DCS-SiN film shows a total hydrogen amount about 40% smaller than that of TCS-SiN film, with 5–10% of SiH content among the total hydrogen. HCD-SiN film shows the smallest hydrogen content with largest SiH content of 2e21 cm<sup>-3</sup>, corresponding to 60% of the total hydrogen.

Results in Fig. 6 are presented in descending order of boron penetration, from left to right. Since the SiN-induced boron penetration is thought to become worse with increase of the total amount of hydrogen, it has been discussed only in terms of the correlation between the amounts of hydrogen. However, it is clarified for the first time from Fig. 6 that the SiN-induced boron penetration in SiN films does not depend on total amount of hydrogen and NH content, but it does clearly depend on the SiH content in SiN films. The SiN-induced boron penetration becomes monotonically worse with the SiH content in SiN films. Fig. 7 shows SiH content dependence of  $V_{fb}$  values of the comb-patterned capacitors with several types of SiN films. Under the experimental conditions of this study, increase of 1e20 cm<sup>-3</sup> of SiH content resulted in positive  $V_{fb}$  shift of about 24 mV.

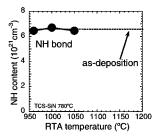

This SiH content dependence on the SiN-induced boron penetration is caused by the less stable binding of SiH bond than NH bond. Namely, only SiH bond releases hydrogen under rapid

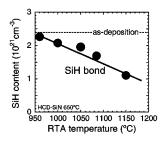

Fig. 8. RTA temperature dependence of residual SiH or NH content in SiN films.

thermal annealing (RTA) condition, which is the highest temperature process of this study and the main cause of the SiN-induced boron penetration. Fig. 8 shows residual SiH and NH content after an RTA process evaluated by the FT-IR method. HCD-SiN and TCS-SiN films were used for this experiment because of the largest content of SiH for HCD-SiN and NH for TCS-SiN, as shown in Fig. 6. A broken line shows the value of as-deposited SiN film. SiH bond monotonically released hydrogen with increase of RTA temperature. On the other hand, NH bond showed no decrease up to 1050 °C. These results indicate that SiH bonds more easily release hydrogen than NH bonds, which is ascribed to the less stable binding of SiH bond, 3.1 eV than that of NH bond, 3.5 eV [14]. This thermally lessstable characteristic of SiH bond is one reason for the strong impact of SiH on the SiN-induced boron penetration. However, further investigation should be needed to clarify the microscopic view of this phenomenon, because desorption mechanism of hydrogen from SiH or NH bond, and its electronic state and chemical species, have not been clear yet.

It is clear that the boron penetration from p<sup>+</sup> gate to silicon substrate is limited by the gate dielectrics, because of its small diffusion coefficient with the order of  $10^{-17}$  cm<sup>2</sup>/s [12]. Therefore, our experimental results of which the boron penetration is accelerated by the desorption hydrogen would indicate that the desorption hydrogen from SiN films, diffused through gate electrode of W/WN/poly-Si layers, affects on gate dielectrics, possibly in accordance with a proposed mechanism reported by Fair [15].

## VI. CONTRIBUTION OF FILM STRESS TO THE SIN-INDUCED BORON PENETRATION

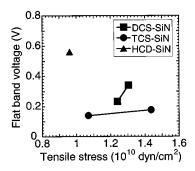

It has been speculated that the large film stress of SiN film may affect the device performance [16]. However, it is clarified that film stress of SiN film does not contribute to the SiN-induced boron penetration.

Film stress of as-deposited SiN film shows no correlation with  $V_{fb}$  of capacitor samples, as shown in Fig. 9. All SiN films show large tensile film stress of the order of  $10^{10}$  dyn/cm<sup>2</sup>. Film stress was deduced from the curvature of substrate by using the scanning laser method [17].

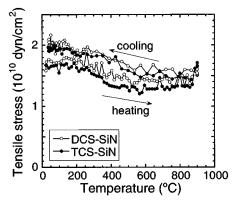

No significant difference is observed between film stress of DCS- and TCS-SiN films even under the annealing process at high temperature of around 900 °C where the boron penetration occurs. Fig. 10 shows the annealing temperature dependence of film stress of both TCS- and DCS-SiN films, measured up to 900 °C under nitrogen atmosphere. They showed similar characteristics with small hysteresis. Film stress becomes slightly smaller with increase of annealing temperature because of the

Fig. 9. Relationships between  $V_{fb}$  and film stress of as-deposited SiN films.

Fig. 10. Temperature dependence of film stress of DCS- or TCS-SiN film.

Fig. 11. Gate-length dependence of  ${\cal V}_{th}$  of PMOSFETs with DCS- or TCS-SiN film.

relaxation of thermal stress and it shows small hysteresis caused by film shrinkage. These two results indicate that the film stress does not contribute to the SiN-induced boron penetration.

## VII. REALIZATION OF HIGH-PERFORMANCE PMOSFETS BY THE APPLICATION OF TCS-SiN FILMS

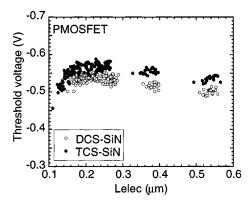

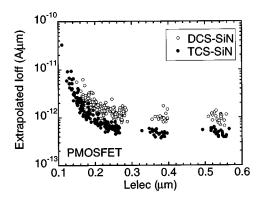

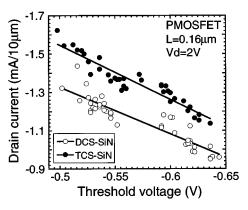

Several advantages of TCS-SiN films have been realized in the PMOSFETs, as indicated in Figs. 11, 13, and 14. DCS- or TCS-SiN film was formed at 780 °C as a cap SiN on the polymetal gate electrodes of PMOSFETs, as shown in Fig. 1.

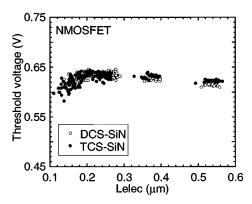

Suppression of the boron penetration has been confirmed by the gate-length dependence of threshold voltage  $(V_{th})$  of PMOSFETs, as shown in Fig. 11. Gate-length was electrically deduced by measuring the gate resistance. The sample with TCS-SiN film shows deeper threshold voltages, indicating suppression of the boron penetration. On the other hand, as shown in Fig. 12, NMOSFETs shows the same gate-length dependence

Fig. 12. Gate-length dependence of  $V_{th}$  of NMOSFETs with DCS- or TCS-SiN film.

Fig. 13. Gate-length dependence of  $I_{\rm off}$  of PMOSFETs with DCS- or TCS-SiN film.

Fig. 14. Relationships between  $V_{th}$  and drain current of PMOSFETs with DCS- or TCS-SiN film.

of Vth for both samples with DCS-SiN and TCS-SiN cap films. As clear from the Figs. 11 and 12, TCS-SiN film improves the characteristics of PMOSFETs without disadvantageous effect on NMOSFETs. Smaller off current and larger drain current have been obtained for the sample with TCS-SiN films, as shown in Figs. 13 and 14. Fig. 13 shows gate-length dependence of off current. Fig. 14 shows the relationships between Vth and drain currents. Off current becomes about half and drain current was improved about 20% by the application of TCS-SiN film on PMOSFETs. These advantages of TCS-SiN films are supposed to be caused by the suppression of the SiN-induced boron penetration and also the gate depletion, but

more detailed investigation should be needed for clarification. These results clearly indicate that TCS-SiN film is necessary for realization of high-performance PMOSFETs.

#### VIII. CONCLUSION

It is clarified for the first time that the SiN-induced boron penetration becomes worse with SiH content in SiN films and an application of SiH-free SiN films, formed by TCS and ammonia, has been proved to effectively suppress the SiN-induced boron penetration and realize the high-performance of PMOS devices.

#### REFERENCES

- [1] J. R. Pfiester, F. K. Baker, T. C. Mele, H.-H. Tseng, P. J. Tobin, J. D. Hayden, J. W. Miller, C. D. Gunderson, and L. C. Parrillo, "The effect of boron penetration on p+ polysilicon gated PMOS devices," *IEEE Trans. Electron Devices*, vol. 37, pp. 1842–1851, Aug. 1990.

- [2] Y. Kohyama, T. Ozaki, S. Yoshida, Y. Ishibashi, H. Nitta, S. Inoue, K. Nakamura, T. Aoyama, K. Imai, and N. Hayasaka, "A fully printable, self-aligned and planarized stacked capacitor DRAM cell technology for aGbit DRAM and beyond," in VLSI Tech. Dig., 1997, pp. 17–18.

- [3] T. Miyashita, H. Nitta, H. Nomura, K. Nakajima, A. Sakata, T. Katata, T. Mizutani, H. Minakata, M. Tanaka, H. Tomita, T. Kurahashi, Y. Watanabe, T. Kubota, A. Hatada, K. Hosaka, K. Hashimoto, and Y. Kohyama, "A novel bit-line process using Poly-Si masked dual-damascene (PMDD) for 0.13 μ m DRAMs and beyond," in *IEDM Tech. Dig.*, 2000, pp. 361–364.

- [4] Y. Akasaka, S. Suehiro, K. Nakajima, T. Nakasugi, K. Miyano, K. Kasai, H. Oyamatsu, M. Kinugawa, M. Takayanagi-Takagi, K. Agawa, F. Matsuoka, M. Kakumu, and K. Suguro, "Low-resistivity poly-metal gate electrode durable for high-temperature processing," *IEEE Trans. Elec*tron Devices, vol. 43, pp. 1864–1869, Nov. 1996.

- [5] S. Saida, T. Sato, I. Mizushima, Y. Ozawa, and Y. Tsunashima, "Single layer nitride capacitor dielectric film and high concentration doping technology for 1Gb/4Gb trench-type DRAMs," in *IEDM Tech. Dig.*, 1997, pp. 265–268.

- [6] R. C. Taylor and B. A. Scott, "LPCVD of silicon nitride films from hexachlorodisilane and ammonia," in *Mat. Res. Soc. Symp.*, vol. 105, 1988, pp. 319–324.

- [7] M. Tanaka, S. Saida, and Y. Tsunashima, "Film properties of low-k silicon nitride films formed by hexachlorodisilane and ammonia," *J. Electrochem. Soc.*, vol. 147, no. 6, pp. 2284–2289, June 2000.

- [8] R. Henda, E. Scheid, and D. Bielle-Daspet, "Kinetics of the low pressure chemical vapor deposition of stoichiometric silicon nitride at low temperature from disilane and ammonia," *J. Chem. Vapor Deposition*, vol. 1, pp. 300–314, Jan. 1993.

- [9] K. F. Roenigk and K. F. Jensen, "Low pressure CVD of silicon nitride," J. Electrochem. Soc., vol. 134, pp. 1777–1785, July 1987.

- [10] A. S. Grove, O. Leistiko, Jr., and C. T. Sah, "Redistribution of acceptor and donor impurities during thermal oxidation of silicon," *J. Appl. Phys.*, vol. 35, pp. 2695–2701, Sept. 1964.

- [11] Y. Shacham-Diamand and W. G. Oldham, "The effect of hydrogen on boron diffusion in SiO2," *J. Electron. Mater.*, vol. 15, pp. 229–233, 1986.

- [12] T. Aoyama, K. Suzuki, H. Tashiro, Y. Tada, Y. Kataoka, H. Arimoto, and K. Horiuchi, "Hydrogen-enhancing boron penetration in P-MOS devices during SiO2 chemical vapor deposition," in *Ext. Abst. Solid State Device Meeting*, 1998, pp. 16–17.

- [13] W. A. Lanford and M. J. Rand, "The hydrogen content of plasma-deposited silicon nitride," *J. Appl. Phys.*, vol. 49, pp. 2473–2477, Apl. 1978

- [14] K. P. Hubert and G. Herzberg, Molecular Spectra and Molecular Structure Constants of Diatomic Molecules. New York: Van Nostrand, 1979.

- [15] R. B. Fair, "Physical models of boron diffusion in ultrathin gate oxide," J. Electrochem. Soc., vol. 144, pp. 708–717, Feb. 1997.

- [16] S. Ito, H. Namba, K. Yamaguchi, T. Hirata, K. Ando, S. Koyama, S. Kuroki, N. Ikezawa, T. Suzuki, T. Saitoh, and T. Horiuchi, "Mechanical stress effect of etch-stop nitride and its impact on deep sub-μm transistor design," in *IEDM Tech. Dig.*, vol. 247, 2000.

- [17] R. Hezel and W. Hearn, "Mechanical stress and electrical properties of MNOS devices as a function of the nitride deposition temperature," *J. Electrochem. Soc. Solid State Sci. Tech.*, vol. 125, pp. 1848–1854, Nov. 1978.

Masayuki Tanaka was born in Saitama, Japan, in 1968. He received the B.S. and M.S. degrees in chemistry in 1992 and 1994, respectively, from Hokkaido University, Hokkaido, Japan, and the Ph.D. degree from University of Tokyo, Tokyo, Japan, in 1997.

He joined the Microelectronics Engineering Laboratory, Toshiba Corporation, Yokohama, Japan, in 1997, where he has been engaged in the research and development of CVD process for advanced LSI.

Dr. Tanaka is a member of the Japan Society of Applied Physics.

**Tetsu Tanaka** (M'90) received the B.S. and M.S. degrees in electrical engineering from Tohoku University, Tohoku, Japan, in 1987 and 1990, respectively.

He joined Fujitsu Laboratories, Ltd., Kawasaki, Japan, in 1990, where he has been engaged in research on highly scaled MOS devices, including SOI devices. From 1994 to 1995, he was a Visiting Industrial Fellow with the University of California, Berkeley, where he studied the device physics of MOSFETs. From 1999 to 2001, he worked on the Fujitsu–Toshiba–Winbond DRAM Development Project. He is currently working on the development of 90-nm node CMOS technology.

**Shigehiko Saida** was born in Aichi, Japan, on September 24, 1967. He received the B.S. degree in physics from the University of Tokyo, Tokyo, Japan in 1990.

He joined the Toshiba ULSI Research Center in 1990, where he has been engaged in the research and development of the CVD processes for ULSI.

Mr. Saida is a member of the Japan Society of Applied Physics.

Ichiro Mizushima was born in Tokyo, Japan, in 1962. He received the B.S., M.S., and Ph.D. degrees in electrical engineering from Keio University, Yokohama, Japan, in 1984, 1986, and 1989, respectively. His Ph.D. work involved the solid-phase crystallization of amorphous silicon.

He joined the ULSI Research Center, Toshiba Corporation, Kawasaki, Japan, in 1990, where he was engaged in the research of doping technologies of silicon. He is currently with the Process and Manufacturing Engineering Center, Semiconductor Company,

Toshiba Corporation, Yokohama, Japan, and has been engaged in the research and development for front-end process technology of advanced LSI, especially in hot-process technology.

Dr. Mizushima is a member of the Japan Society of Applied Physics, the Institute of Electronics, Information and Communication Engineers, and the Surface Science Society of Japan.

**Fumihiko Inoue** was born in Yamaguchi, Japan, in 1960. He received the B.S. degree in electrical engineering from Tokyo Institute of Technology, Tokyo, Japan.

He joined Fujitsu Limited, Kawasaki, in 1983, where he has been engaged in the development of CMOS processes. He joined Fujitsu AMD Semiconductor Limited in 2002.

Manabu Kojima was born in Kanagawa, Japan, in 1963. He received the B.S. and M.S. degrees in electronics and communication engineering from Yokohama National University, Yokohama, Japan, in 1986 and 1988, respectively.

In 1988, he joined Fujitsu Laboratories, Ltd., Atsugi, Japan, where he worked on the research and developmenet of device technologies for logic and DRAM LSI devices. From 1998 to 2000, he participated in a 0.13-μm DRAM project involving Toshiba, Winbond, and Fujitsu, at Advanced

Microelectoronics Center, Toshiba Corporation, Yokohama, Japan. Since 2001, he has been with Fujitsu Laboratories Ltd., Akiruno, Japan, engaged in the development of high-end CMOS logic devices.

Mr. Kojima is a member of the Japan Society of Applied Physics.

development.

**Toshiro Nakanishi** was born in Hyogo, Japan, in 1958. He received the B.S. and M.S. degrees in electronics from Kobe University, Kobe, Japan, in 1981 and 1983, respectively, and the D.Eng. degree from Tohoku University, Japan, in 1998.

In 1983, he joined Fujitsu Laboratories, Ltd., Kawasaki, Japan, where he was engaged in the research of Si and SiO2. He was responsible for the development of hot process at the Fujitsu/Toshiba DRAM joint development project from 1999 to 2001. Currently, he is engaged in system memory

**Kyoichi Suguro** received the B.S. and M.S. degrees in electronics and the Ph.D. degree in metallization in ULSIs, all from Waseda University, Tokyo, Japan, in 1979, 1981, and 1992, respectively.

He joined Toshiba Corporation, Kawasaki, in 1981. He is now a Section Leader with the High-Performance Transistor Process Group. He has worked in the research and development of advanced process module technology including source/drain/gate/metallization, high-k gate dielectrics, advanced ion implantation, flash-lamp annealing, and ultralow

resistivity contact.

Dr. Suguro is now a member of the Japanese Society of Applied Physics.

Yoshitaka Tsunashima was born in Tokyo, Japan, in 1956. He received the B.S. degree in metallurgical engineering and the M.S. degree in materials science from Tokyo Institute of Technology, Tokyo, Japan, in 1980 and 1982, respectively.

In 1982, he joined the Research and Development Laboratory, Toshiba Corporation, Kawasaki, Japan, where he worked on the research and development of process technologies for VLSIs. In 1993, he participated in the 256-Mb DRAM Joint Development Project at the Advanced Semiconductor Technology

Center, IBM Corporation, East Fishkill, NY. In 1996, he joined the Microelectronics Engineering Laboratory, Semiconductor Company, Toshiba Corporation, Yokohama, Japan, and has been engaged in research and development of fabrication process of memory and logic LSIs. Since 2000, he has been Manager of the front end of the line process development group. He is currently involved in the area of high-k gate dielectric formation, silicon epitaxy and its surface migration related process, and the novel precursors thermal CVD process.

Mr. Tsunashima is a member of the IEEE Electron Devices Society and the Japan Society of Applied Physics.