# Tunneling Through ultrathin GaAs n++-p++-n++ Barrier Grown by Molecular Layer Epitaxy

| 著者                | 小山 裕                                  |  |  |

|-------------------|---------------------------------------|--|--|

| journal or        | IEEE Transactions on Electron Devices |  |  |

| publication title |                                       |  |  |

| volume            | 45                                    |  |  |

| number            | 12                                    |  |  |

| page range        | 2551-2554                             |  |  |

| year              | 1998                                  |  |  |

| URL               | http://hdl.handle.net/10097/46452     |  |  |

doi: 10.1109/16.735735

- [2] T. Hashizume *et al.*, "CMOS self-aligned low temperature poly-Si TFT's fabricated by laser annealing of poly-Si films," in *Ext. Abstr. SSDM'91*, pp. 638–640.

- [3] K. Sera *et al.*, "High performance TFT's fabricated by XeCl excimer laser annealing of hydrogenated amorphous silicon film," *IEEE Trans. Electron Devices*, vol. 36, pp. 2868–2872, 1989.

- [4] Y. Matsueda *et al.*, "Low temperature poly-Si TFT-LCD with integrated 6-bit digital data drivers," in *SID'96 Dig.*, 1996, pp. 21–24.

- [5] T. Sameshima, M. Hara, and S. Usui, "XeCl excimer laser annealing used to fabricate poly-Si TFT's," *Jpn. J. Appl. Phys.*, vol. 28, pp. 1789–1793, 1989.

- [6] M. Yuki, K. Masumo, and M. Kunigita, "A full-color LCD addressed by poly-Si TFT's fabricated below 450°C," *IEEE Trans. Electron Devices*, vol. 36, pp. 1934–1939, 1989.

- [7] A. Kohno et al., "High performance poly-Si TFT fabricated using pulsed laser annealing and remote plasma CVD with low temperature processing," *IEEE Trans. Electron Devices*, vol. 42, pp. 251–257, 1995.

- [8] J. I. Ryu, H. C. Kim, S. K. Kim, and J. Jang, "A novel self- aligned polycrystalline silicon thin-film transistor using silicide layers," *IEEE Electron. Device Lett.*, vol. 18, pp. 272–274, 1997.

- [9] Y. Yoshida, K. Setsune, and T. Hirao, "Formation of source and drain region for a-Si: H thin-film transistors by low-energy ion doping technique," *IEEE Electron. Device Lett.*, vol. 9, pp. 90–93, 1988.

- [10] K. H. Lee, Y. M. Jhon, H. J. Cha, and J. Jang, "Low temperature polycrystalline silicon thin film transistor with silicon nitride ion stopper," *IEEE Electron. Device Lett.*, vol. 17, p. 258, 1996.

- [11] M. Yazaki, S. Takenaka, and H. Oshima, "Conduction mechanism of leakage current observed in metal-oxide-semiconductor transistors and poly-Si thin film transistors," *Jpn. J. Appl. Phys.*, vol. 31, pp. 206–209, 1992.

- [12] S. M. Sze, *Physics of Semiconductor Devices*. New York: Wiley, 1981, ch. 8.

- [13] I.-W. Wu *et al.*, "Crystallization of silicon ion implanted LPCVD amorphous silicon films for high performance poly-TFT," *Mat. Res. Soc. Proc.*, vol. 182, pp. 107–113, 1990.

- [14] N. M. Johnson *et al.*, "Single-crystal silicon transistors in lasercrystallized thin films on bulk glass," *IEEE Electron. Devices Lett.*, vol. EDL-3, pp. 369–372, 1982.

- [15] M. Hatano, H. Akimoto, T. Sakai, and H. Ishida, "Sub-μm poly-Si TFT's for low-voltage circuit applications," in *Tech. Dig. AMLCD*'97, Tokyo, Japan, pp. 95–98.

- [16] J. G. Fossum, A. O. Conde, H. Shichijo, and S. K. Banerjee, "Anomalous leakage current in LPCVD polysilicon MOSFET's," *IEEE Trans. Electron. Devices*, vol. ED-32, pp. 1878–1885, 1985.

- [17] C. H. Kim, K. S. Sohn, and J. Jang, "Temperature dependent leakage currents in polycrystalline silicon thin film transistors," J. Appl. Phys., vol. 81, pp. 8084–8090, 1997.

- [18] S. D. S. Malhi et al., "Characteristics and three-dimensional integration of MOSFET's in small-grain LPCVD polycrystalline silicon," *IEEE Trans. Electron Devices*, vol. ED-32, pp. 258–281, 1985.

# Tunneling Through Ultrathin GaAs n<sup>++</sup>-p<sup>++</sup>-n<sup>++</sup> Barrier Grown by Molecular Layer Epitaxy

Yong-Xun Liu, Piotr Plotka, Ken Suto, Yutaka Oyama, and Jun-ichi Nishizawa

Abstract—The I-V characteristics of ultrathin GaAs  $n^{++}-p^{++}-n^{++}$ barrier structures with a 45 Å thick  $p^{++}$  layer grown by molecular layer epitaxy (MLE) have been measured at room temperature and 77 K. The tunneling probability for this structure has been calculated as a function of effective tunneling width. It was found that good agreement between experiment and calculation is obtained when the effective tunneling width is assumed to be 75 Å, which is much smaller than the depletion width about 190 Å measured by C-V method. This fact indicates that the depletion width approximation cannot be used to measure the exact tunneling width for ultrathin barrier devices.

*Index Terms*—Effective tunnelling width, molecular layer epitaxy, ultrathin barrier.

## I. INTRODUCTION

Molecular layer epitaxy (MLE) [1] is a crystal growth method that is able to produce thin crystal films controlled with a single molecular layer precision. This method has been applied to preparation of ideal static induction transistor (ISIT) in which electrons transport in the crystal without collision [2]-[4]. The operation of the ISIT with tunneling has been reported [5]. The I-V characteristics of planar doped barrier (PDB) n<sup>+</sup>-i-p<sup>+</sup>-i-n<sup>+</sup> structures with source-drain distances larger than 460 Å have been explained with thermionic emission theory at and above room temperature [6]-[8] and by tunneling theory at 77 K [9]. In the calculation of tunneling probability for PDB structures, the design source-drain distance was used as an effective tunneling width at zero bias because the depletion width measured by C-V method is almost equal to the design source-drain distance. However, discrepancies occur between the measured depletion width and the design source-drain distance with thinning of the sourcedrain distance. For example, the depletion width measured by C-Vmethod for a PDB structure with design source-drain distance 110 Å was about 320 Å [9].

In this work, we compare the measured and calculated I-V characteristics of the ultrathin  $n^{++}-p^{++}-n^{++}$  structure with a 45 Å thick  $p^{++}$  layer grown by MLE. The tunneling probability and current for this structure are calculated by using triangular barrier model. The differences between the effective tunneling width and the depletion width measured by C-V method are simply discussed by considering the electron distribution tails from the  $n^{++}$  source and drain regions into the depleted channel region.

#### II. EXPERIMENTAL RESULTS AND DISCUSSION

The ultrathin GaAs  $n^{++}-p^{++}-n^{++}$  barrier structure with a design metallurgical  $p^{++}$  layer thickness of 45 Å was grown by MLE,

Manuscript received September 15, 1997; revised August 10, 1998. The review of this brief was arranged by Editor N. Moll.

Y. X. Liu, K. Suto, and Y. Oyama are with the Department of Materials Science and Engineering, Faculty of Engineering, Tohoku University, Sendai 980-8579, Japan.

P. Plotka, K. Suto, Y. Oyama, and J. Nishizawa are with the Semiconductor Research Institute, Sendai 980-0862, Japan, and the Telecommunications Advancement Organization of Japan, Sendai Research Center, Sendai 980-0968, Japan.

Publisher Item Identifier S 0018-9383(98)09030-3.

#### 0018-9383/98\$10.00 © 1998 IEEE

TABLE I Designed Layer Parameters in MLE

| Source    | n**              | 300Å       | 5×10 <sup>19</sup> cm <sup>-3</sup> |

|-----------|------------------|------------|-------------------------------------|

| Gate      | p''              | 45Å        | $9 \times 10^{19} \text{ cm}^{-3}$  |

| Drain     | n**              | 180Å       | 5×10 <sup>19</sup> cm <sup>-3</sup> |

| Buffer    | $\mathbf{n}^{+}$ | 425Å       | 5×10 <sup>18</sup> cm <sup>-3</sup> |

| Substrate | $\mathbf{n}^{+}$ | GaAs (100) | 2×10 <sup>18</sup> cm <sup>-3</sup> |

using selenium and zinc as  $n^{++}$  and  $p^{++}$  dopants, respectively. After growth of the structure, the device mesa was etched with  $H_2SO_4: H_2O_2: H_2O = 4:1:90$  solution. About 40 diodes with an area  $S = 100 \times 100 \ \mu\text{m}^2$  were formed on a wafer. A lift-off Ti/Au metallization was used for nonalloyed contact to the top layer and Au/Ge was used for back contact. The design parameters in MLE are listed in Table I. The doping concentrations of both  $n^{++}$  layers are the same,  $N_D = 5 \times 10^{19} \text{ cm}^{-3}$ . The thickness  $W_{p0} = 45$  Å and doping level  $N_A = 9 \times 10^{19} \text{ cm}^{-3}$  of the  $p^{++}$  layer are designed so that the thin  $p^{++}$  layer is completely depleted. The doping levels of each layer have been determined by Hall effect with about 1500 Å thick layers and the thicknesses for each layer have been determined by the growth rate (Å/cycle) in the MLE [1]. The  $p^{++}$  and  $n^{++}$  doping profiles have been found to be nearly abrupt, by a dynamic SIMS instrument with depth resolution of 30 Å.

At thermal equilibrium, the relation of space charge neutrality  $N_A \times W_{p0} = 2N_D \times W_{n0}$  should be valid, where  $W_{n0}$  is the depletion width on one side  $n^{++}$  region. The value of  $W_{n0}$  can be calculated to be 40.5 Å. Thus, the total depletion width is obtained as  $W_0 = W_{p0} + 2W_{n0} = 126$  Å. The measured depletion width by C-V method is about 190 Å. The potential distribution at the thermal equilibrium can be calculated from Poisson equation, and the barrier height is obtained as  $\Psi_{00} = 0.88$  V. This analysis is based on the depletion width approximation, which neglects the electron distribution tails from  $n^{++}$  regions into the depleted channel region.

The schematic diagram of the ultrathin  $n^{++}-p^{++}-n^{++}$  barrier structure is presented in Fig. 1(a), where the black circles illustrate the electron distribution tails from both  $n^{++}$  regions into the depleted channel region. The potential distribution taking into account the electron distribution tails is calculated, and the zero bias barrier height is obtained as  $\Phi_{00} = 0.91$  V. In this calculation, the electron distribution tails are expressed as  $n(x) = N_D \exp[-q\Phi(x)/k_{\rm B}T]$ , where  $\Phi(x)$  is potential, q is elementary charge,  $k_{\rm B}$  is Boltzmann constant, T is absolute temperature. Two dashed lines in Fig. 1(b) correspond to the calculated potential distributions at zero bias and  $V_{DS} = 0.5$  V. It can be seen from these profiles that the position of potential maximum moves to the source direction with increasing bias (the substrate biased positively with respective to the top). Considering these factors, the triangular barrier model is adopted to simplify the calculation of tunneling probability for our structure. Two solid lines in Fig. 1(b) represent the triangular potential distribution at zero bias and  $V_{DS} = 0.5$  V, where  $W_{gs}$  and  $W_{gd}$  are the effective source-gate and gate-drain distances,  $W_{\rm eff 0}$  is the effective tunneling width at zero bias, a and b are the effective classical turning points,  $\Phi_0$  and  $\Phi_1$  are the effective barrier heights with respect to the source Fermi level  $E_{FS}$  at zero and  $V_{DS}$  biases,  $E_C$  is the energy at the bottom of conduction band,  $V_{ns} = (E_{FS} - E_C)/q$  is degeneracy which is small [10], [11].

The tunneling current at zero absolute temperature is easily calculated by using this triangular potential barrier model, and can be expressed as [9]

$$I \approx S \cdot A' \cdot qV_{DS} \cdot (2qV_{ns} - qV_{DS})$$

$$\cdot \exp\left(-\alpha \cdot \sqrt{\Phi_1} \cdot W_{\text{eff}}\right) V_{DS} \leq V_{ns}$$

(1)

Fig. 1. (a) Schematic diagram of the ultrathin n<sup>++</sup>-p<sup>++</sup>-n<sup>++</sup> barrier structure. Black circles illustrate the electron distribution tails from both the n<sup>++</sup> regions into the depleted channel region. (b) Potential distributions from calculation (dashed lines) and triangular barrier model (solid lines) at zero bias and  $V_{DS} = 0.5$  V. The parameters are assumed as  $\Phi_0 = 1.15$  V,  $W_{gs} = 25$  Å,  $W_{gd} = 50$  Å, and  $\mu_F^* = 3$ .

$$I \approx S \cdot A' \cdot (qV_{ns})^2$$

$$\cdot \exp\left(-\alpha \cdot \sqrt{\Phi_1} \cdot W_{\text{eff}}\right) V_{DS} > V_{ns}$$

(2)

where S is device area,  $A' \approx 2\pi m^* q/h^3 \approx 5.5 \times 10^8$  [A cm<sup>-2</sup> (eV)<sup>-2</sup>],  $\alpha \approx 8\pi (2m^*q)^{0.5}/3h \approx 0.178$  [Å<sup>-1</sup> V<sup>-0.5</sup>],  $m^*$  is effective mass of an electron, h is Planck constant.  $\Phi_1$  can be expressed as  $\Phi_1 \approx \Phi_0 - V_{DS}/\mu_F^*$ , where  $\mu_F^* (\approx 1 + W_{gd}/W_{gs})$  is the intrinsic voltage amplification factor [2], [8].  $W_{\rm eff}$  can be expressed as  $W_{\rm eff} \approx W_{gs} + W_{gd}/(1 + V_{DS}/\Phi_1)$  [9].

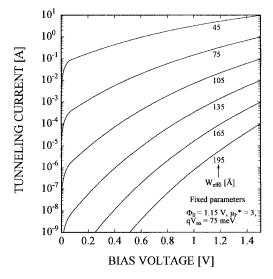

Fig. 2 shows the calculated tunneling current from (1) and (2) with the effective tunneling width  $W_{\text{eff}\ 0}$  at zero bias as a single parameter. The other parameters  $qV_{ns}$ ,  $\mu_F^*$  and  $\Phi_0$  are fixed to 75 meV, 3 and 1.15 V, respectively. As mentioned before, the design metallurgical thickness of p<sup>++</sup> layer is 45 Å, the depletion width from the space charge neutrality is 126 Å, and is about 190 Å by C-V measurement. It is clear from Fig. 2 that the tunneling current magnitude and shape is very different as  $W_{\text{eff}\ 0}$  changes from 45 to 195 Å.

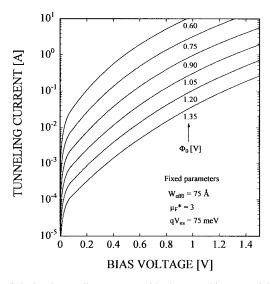

Fig. 3 shows the calculated tunneling current from (1) and (2) with the zero bias barrier height  $\Phi_0$  as a parameter. The other parameters  $qV_{ns}$ ,  $\mu_F^*$  and  $W_{\text{eff }0}$  are fixed to 75 meV, 3 and 75 Å, respectively.  $\Phi_0 = 0.9$  V corresponds to the calculated barrier height at thermal equilibrium. The tunneling current does not strongly depend on the  $\Phi_0$ , as compared with  $W_{\text{eff }0}$ .

We have also calculated the tunneling current with  $\mu_F^*$  ranging from 2–4, and  $qV_{ns}$ ,  $\Phi_0$ , and  $W_{\text{eff }0}$  are fixed to 75 meV, 1.15 V, and 75 Å, respectively. There are no pronounced changes in the calculated I-V characteristics.

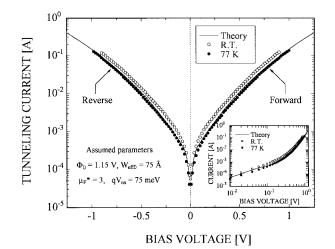

Fig. 4 compares the calculated tunneling current from (1) and (2) and the experimental data at room temperature and 77 K. It is found that the best fit between the experimental data and calculated one is obtained when the parameters are assumed as  $W_{\rm eff 0} = 75$  Å,

Fig. 2. Calculated tunneling current with the effective tunneling width at zero bias as a single parameter.

Fig. 3. Calculated tunneling current with the zero bias potential barrier height as a single parameter.

$\Phi_0 = 1.15$  V,  $qV_{ns} = 75$  meV, and  $\mu_F^* = 3$ . Although there are some differences in the potential distributions between the triangular barrier model and the calculated one, as solid lines and dashed lines in Fig. 1(b), the triangular barrier model explains our experimental data. The insert in Fig. 4 shows a logarithmic plot of the experimental and calculated I-V characteristics. The current in the vicinity of zero bias is approximately ohmic. This result is reasonable because the product of the  $\Phi_1^{0.5} \times W_{\rm eff} \approx \Phi_0^{0.5} \times W_{\rm eff 0}$  is almost a constant for small bias ( $V_{DS} < V_{ns}$ ), and the current should be determined by (1) with a nearly linear dependence on the bias voltage  $V_{DS}$ .

The parallel capacitance  $C_p$  and resistance  $R_p$  of our sample were measured at different frequencies using **hp**-impedance/gain-phase analyzer, and obtained as  $C_p \approx 60$  pF and  $R_p \approx 140 \Omega$ . These values are independent of frequency up to 10 MHz. The estimated series resistance is about 1  $\Omega$ . The depletion width from the capacitance, 190 Å, is much larger than the effective tunneling width, 75 Å. Because of the electron distribution tails shown as black circles in Fig. 1(a), the classical abrupt space-charge edge approximation is not adequate

Fig. 4. Comparison between experiment and calculation at forward and reverse biases. The insert is a logarithmic I-V characteristics.

[12], [13], and the depletion width from the C-V data can not be referred to the blocking distance of electrons. Moreover, because the main contribution to the tunneling current is due to electrons with the energy near  $E_{FS}$ , the effective tunneling width should be smaller than the depletion width. However, for the PDB structures with a few hundred Angstrom long channels, this effect is not important and the design source-drain distance can be used as a tunneling barrier width [9]. The more precise expression of tunneling current with exact potential distribution requires further study.

### III. CONCLUSION

The I-V characteristics for ultrathin GaAs  $n^{++}-p^{++}-n^{++}$  barrier structures with a 45 Å thick  $p^{++}$  layer grown by molecular layer epitaxy (MLE) have been measured at room temperature and 77 K. The tunneling current for this structure has been calculated as a function of effective tunneling width. Good agreement between the experimental and calculated I-V characteristics is obtained when the effective tunneling width is assumed 75 Å, much smaller than the depletion width of about 190 Å measured by C-V method. The depletion width for ultrathin barrier devices. When the metallurgical source-drain distance is about 45 Å, the diode current is tunneling current even at room temperature.

#### ACKNOWLEDGMENT

The authors would like to thank Dr. T. Kurabayashi, H. Kikuchi, and M. Henmi for processing of the MLE sample wafers.

#### REFERENCES

- J. Nishizawa, H. Abe, and T. Kurabayashi, "Molecular layer epitaxy," J. Electrochem. Soc., vol. 132, pp. 1197–1200, 1985.

- [2] J. Nishizawa, T. Terasaki, and J. Shibata, "Field-effect transistor versus analog transistor (static induction transistor)," *IEEE Trans. Electron Devices*, vol. ED-22, pp. 185–197, 1975.

- [3] P. Plotka, T. Kurabayashi, Y. Oyama, and J. Nishizawa, "Ideal static induction transistor implemented with molecular layer epitaxy," *Appl. Surf. Sic.*, vol. 82–83, pp. 91–96, 1994.

- [4] Y. Oyama, P. Plotka, and J. Nishizawa, "Selective MLE growth of GaAs and surface treatment for ideal static induction transistor (ISIT) application," *Appl. Surf. Sci.*, vol. 82–83, pp. 41–45, 1994.

- [5] J. Nishizawa and P. Plotka, "Molecular layer epitaxy for ultra high frequency integrated circuits and electron device," in *Proc. 5th. Int. Symp. Recent Advances in Microwave Technol.*, Kiev, Ukraine, Sept. 11–16, 1995, pp. 54–58.

- [6] R. J. Malik et al., "Planar-doped barriers in GaAs by molecular beam epitaxy," *Electron. Lett.*, vol. 16, pp. 836–837, 1980.

- [7] A. C. Gossard, R. F. Kazarinov, S. Luryi, and W. Wigmann, "Electric properties of unipolar GaAs structures with ultrathin triangular barriers," *Appl. Phys. Lett.*, vol. 40, no. 9, pp. 832–833, 1982.

- [8] Y. X. Liu, P. Plotka, K. Suto, Y. Oyama, and J. Nishizawa, "Carrier injection by static induction mechanism in MLE-grown planar-doped barrier n<sup>+</sup>-i-p<sup>+</sup>-i-n<sup>+</sup> structures," *IEEE Trans. Electron Devices*, vol. 44, pp. 195–197, 1997.

- 44, pp. 195–197, 1997. [9]  $\frac{1}{n^+}$ , "Tunneling current in very thin planar-doped barrier n<sup>+</sup>-i-p<sup>+</sup>-i-n<sup>+</sup> structures," unpublished.

- [10] G. Borghs *et al.*, "Band-gap narrowing in highly doped n- and p-type GaAs studied by photoluminescence spectroscopy," *J. Appl. Phys.*, vol. 66, pp. 4381–4386, 1989.

- [11] D. A. Cusano, "Radiative recombination from GaAs directly excited by electron beam," *Solid State Comm.*, vol. 2, pp. 353–358, 1964.

- [12] B. R. Chawla and H. K. Gummel, "Transition region capacitance of diffused p-n junctions," *IEEE Trans. Electron Devices*, vol. ED-18, pp. 178–195, 1971.

- [13] W. C. Johnson and P. T. Panousis, "The influence of Debye length on the C-V measurement of doping profiles," *IEEE Trans. Electron Devices*, vol. ED-18, pp. 965–973, Oct. 1971.