Available online at www.sciencedirect.com

### SciVerse ScienceDirect

Procedia Engineering 53 (2013) 368 - 375

## Procedia Engineering

www.elsevier.com/locate/procedia

Malaysian Technical Universities Conference on Engineering & Technology 2012, MUCET 2012 Part 1- Electronic and Electrical Engineering

# Design of Low Power Wideband Low Noise Amplifier for Software Defined Radio at 100 MHz to 1 GHz

A. Salleh<sup>a,\*</sup>, K. S. Yong<sup>a</sup>, M. Z. A. Abd Aziz<sup>a</sup>, M. H. Misran<sup>a</sup>, N. R. Mohamad<sup>a</sup>

<sup>a</sup>Faculty of Electronic & Computer Engineering Universiti Teknikal Malaysia Melaka Melaka, Malaysia

#### Abstract

This paper describes the design of wideband low noise amplifier (LNA) for mobile software defined radio (SDR) application which targeted to be applied in two-way communication mobile system architecture. The technical specification was deduced from the TIA-603C standard receiver system sensitivity and intermodulation. The proposed LNA exhibit low power consumption and adopts a negative feedback wideband amplifier topology, operated from 100 MHz to 1 GHz which covers the whole Land Mobile FM Communication Equipment (136 – 941 MHz) frequency band. The proposed topology solve the RF tracing problem inherited in the targeted frequency and also the problem of economically impractical PCB size rendered by other wideband amplifier methods. The Advanced Design System software is used to perform the simulations. The measured result show the proposed LNA has a stable gain of more than 15 dB, noise figure less than 1.5 dB, S<sub>11</sub> and S<sub>22</sub> less than -10 dB, with current consumption of 8 mA from voltage supply at 1.8 V.

© 2013 The Authors. Published by Elsevier Ltd.

Selection and peer-review under responsibility of the Research Management & Innovation Centre, Universiti Malaysia Perlis

Keywords: negative feedback wideband LNA; low power consumption; Software Defined Radio.

#### 1. Introduction

Conventional amplifiers operate on a single frequency band, in which it is easier to design the amplifier to meet all the specified goals. However, the Software Defined Radio (SDR) is a wideband radio which operates from Very Large Frequency, VHF (136 MHz) to Ultra High Frequency, UHF (940 MHz), making it harder to design the Receiver Front End (RXFE) LNA. SDR radio applications require the amplifiers to operate at wider spectrum while maintaining low noise, high linearity, and unconditionally stable. Traditionally, the system uses single band at the repeater [1], but to implement multiband technology, having separate single band repeaters is not economically producible. Another solution is to have a repeater to have a few separate RXFE sections that is joined by a switch, but this will result in a greater board size and extra cost. Hence, a single RXFE chain which can covers all frequency is a desirable choice.

Software-defined radio (SDR) is a radio communication system that implements software defined wireless communication protocols instead of hardwired implementation. The SDR RXFE hardware critical blocks will be the variable filter, wideband LNA and high dynamic range mixer. Although, SDR radio is emphasized on the software modulations or demodulations, but the major hardware components must be able to provide the wideband capability to the radio before it convert the RF signals into baseband signals.

<sup>\*</sup> Corresponding author. E-mail address: azahari@utem.edu.my

#### 2. Technical Specification

From the TIA-603C standard compliances, based on the radio receiver specifications, a tabulated data for all individual substations in the receiver system is shown in Table 1. There are two LNAs in the specifications for the whole radio receiver system. Since LNA2 is a second stage Intermediate Frequency (IF) amplifier and not in the RXFE, hence only LNA1 will be describe in this paper. LNA1 has a significant contribution in determining the receiver sensitivity as well as the actual RF frequency application. The frequency range is chosen based on the TIA-603C standard. Those frequency include 136MHz - 174MHz, 217MHz - 224MHz, 381MHz - 519MHz, 766MHz - 774 MHz, 851MHz - 869 MHz and 935MHz - 940 MHz [2].

|                         | <b>~</b> ∕ ⊸ |         | \%\     | $\triangle$ |         | $\triangleright$ | $\otimes$ | =       | $\triangleright$ | BP<br>□U |

|-------------------------|--------------|---------|---------|-------------|---------|------------------|-----------|---------|------------------|----------|

| Stage<br>Specifications | ANT SW       | FL1     | ATTEN   | LNA1        | FL2     | LNA2             | MIXER     | XTAL    | IF AMP           | BK END   |

| G (dB)                  | -1           | -1.5    | -0.3    | 11          | -2.2    | 8                | -6.5      | -3      | 14               | N/A      |

| NF (db)                 | 1            | 1.5     | 0.3     | 1.5         | 2.2     | 2                | 7         | 3       | 2.5              | 10       |

| IIP3 (dBm)              | 20           | 20      | 40      | 11          | 35      | 15               | 20        | 15      | -15              | -10      |

| IIP2 (dBm)              |              |         |         |             |         |                  | 40        |         |                  |          |

| Sel@50 kHz<br>(dB)      | 0            | 0       | 0       | 0           | 0       | 0                | 0         | 25      | 0                | 0        |

| Sel@100 kHz<br>(dB)     | 0            | 0       | 0       | 0           | 0       | 0                | 0         | 30      | 0                | 0        |

| DC Current<br>(mA)      | 0            | 0       | 0       | 100         | 0       | 75               | 25        | 0       | 50               | 250      |

|                         |              |         |         |             |         |                  |           |         |                  |          |

| Stage<br>Calculations   |              |         |         |             |         |                  |           |         |                  |          |

| G (linear)              | 0.79         | 0.71    | 0.93    | 12.59       | 0.6     | 6.31             | 0.22      | 0.5     | 25.12            | N/A      |

| F (linear)              | 1.26         | 1.41    | 1.07    | 1.41        | 1.66    | 1.58             | 5.01      | 2       | 1.78             | 10       |

| IIP3 (dBm)              | 20           | 20      | 40      | 11          | 35      | 15               | 20        | 15      | -15              | -10      |

| System<br>Calculations  |              |         |         |             |         |                  |           |         |                  |          |

| Fsys (linear)           | 3.68         | 2.92    | 2.07    | 1.93        | 7.52    | 4.53             | 19.59     | 4.26    | 2.14             | 10       |

| NFsys (dB)              | 5.66         | 4.66    | 3.16    | 2.86        | 8.76    | 6.56             | 12.92     | 6.3     | 3.3              | 10       |

| S (dBm)@12<br>dB SINAD  | -122.01      | -123.01 | -124.51 | -124.81     | -118.91 | -121.11          | -114.75   | -121.37 | -124.37          | -117.67  |

| S (dBm)@20<br>dB SINAD  | -177.71      | -118.71 | -120.21 | -120.51     | -114.61 | -116.81          | -110.45   | -117.07 | -120.07          | -117.67  |

| IIP3sys<br>(dBm)        | 1.73         | 0.8     | -0.65   | -0.95       | 10.16   | 7.97             | 16.94     | 13.39   | -24.51           | -10      |

| IMR3 (dB)               | 82.49        | 82.54   | 82.57   | 82.57       | 86.04   | 86.05            | 87.79     | 89.84   | 66.57            | 71.78    |

| IMR3 TIA-<br>603 (dB)   | 80.99        | 81.04   | 81.07   | 81.07       | 84.54   | 84.55            | 86.29     | 88.34   | 65.07            | 70.28    |

| IIP2sys<br>(dBm)        | 50           | 49      | 39.5    | 39.2        | 50.2    | 40               | 40        | N/A     | N/A              | N/A      |

| ½ IF Rej (dB)           | 86.01        | 86.01   | 82.01   | 82.01       | 84.55   | 80.55            | 77.37     | N/A     | N/A              | N/A      |

| ½ IF TIA-603<br>(dB)    | 83.76        | 83.76   | 79.76   | 79.76       | 82.3    | 78.3             | 75.12     | N/A     | N/A              | N/A      |

| (uD)                    |              |         |         |             |         |                  |           |         |                  |          |

Table 1. Typical RXFE system specifications for tia-603c compliance [1]

Traditionally, all of these separated frequency band would require its own system with unique frequency operation. However, an SDR system would finally combine all these separate system into a single system which is capable to switch frequencies and with less count parts and cost. In this paper, only the design of wideband LNA to achieve multiband frequency requirement of SDR radio is describe, since the difficulties in multi modulation is more depend on the software implementation of the SDR.

The wideband LNA is required to be in single stage, low power consumption, minimum components and easily mass produced in minimum cost. The technical requirements of the proposed design are shown in Table 2.

< -10

| Parameter                               | Value      |  |  |

|-----------------------------------------|------------|--|--|

|                                         |            |  |  |

| Operating Frequency (MHz)               | 100 - 1000 |  |  |

| Noise figure (dB)                       | < 1.5      |  |  |

| Gain (dB)                               | > 15       |  |  |

| Input Third Order Inception, IIP3 (dBm) | > 5        |  |  |

| Stability Factor (K)                    | > 1        |  |  |

| Current (mA)                            | < 10       |  |  |

| Voltage (V)                             | < 1.8      |  |  |

|                                         |            |  |  |

Input and Output Return Loss (dB)

Table 2. Specifications of LNA

#### 3. Wideband LNA Design

Wideband LNA design presents a considerable challenge, as we know conjugate matching will give maximum gain only over relatively narrow bandwidth, while designing for less maximum gain will improve the gain bandwidth, but the input and output part of the amplifier will be poorly matched [3]. For this reason negative feedback technique is proposed to simultaneously achieve improvement in bandwidth and also on its gain, noise figure and return loss. The conventional LNA suffers from the problem that the input matching network can be tuned for low noise figure or low VSWR (conjugate match) but not both parameters simultaneously [4]. The negative feedback technique can be used in wideband amplifier to provide a flat gain response and to reduce the input and output VSWR. It also controls the amplifier performance due to variations in the S-parameters from transistor to transistor and furthermore, in-band stability is also improved by employing negative feedback [2]. Furthermore, the LNA must utilize only one LNA to ensure minimum part count, hence cascaded topology were excluded in this design. Another factor is space consumptions; at < 400 MHz, it is unpractical for balanced amplifier design due to the long trace length.

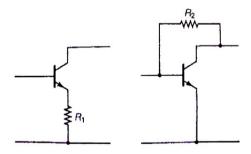

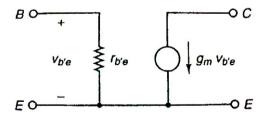

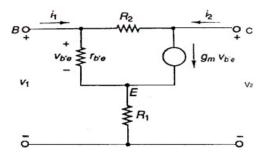

Table 3 shows the comparison of related works of LNA design. BJT is selected to design the wideband low noise amplifier due to its higher gain at low power consumption, with reasonable low noise figure. The most common technique in applying feedback is to have a series or shunt resistor configuration as shown in Fig. 1. The BJT can be represented by the equivalent circuit in Fig. 2. The resulting negative feedback equivalent network (with both series and shunt feedback) is shown in Fig. 3 [2].

Fig. 1. BJT with series and shunt feedback resistor

Fig. 2. BJT equivalent network

Fig. 3. BJT negative feedback model

Table 3. Comparison of reported LNA with other LNA design

| Reference    | Frequency<br>(GHz) | Gain<br>(dB) | NF<br>(dB) | IIP3<br>(dBm) | P1dB<br>(dBm) |  |

|--------------|--------------------|--------------|------------|---------------|---------------|--|

| This<br>Work | 0.1-1              | >15          | <1.5       | >5            | -             |  |

| [5]          | 2.44               | 15.3         | 3.34       | -10           | -18           |  |

| [6]          | 2.4-6              | 13.0         | 2.5        | -3.9          | -             |  |

| [7]          | 0.1-8              | 16           | 3.4-5.8    | -9            | -             |  |

| [8]          | 0.92               | 13           | 1          | -1.5          | -             |  |

| [9]          | 2.14               | 20.5         | 0.47       | 18            | -             |  |

| [10]         | 1.9                | 17.5         | 1.6        | 10.7          | -             |  |

The admittance matrix for the circuit model shown in Fig. 3 can be written as:

$$\begin{bmatrix} i_1 \\ i_2 \end{bmatrix} = \begin{bmatrix} \frac{1}{R_2} & -\frac{1}{R_2} \\ \frac{g_m}{1 + g_m R_1} - \frac{1}{R_2} & \frac{1}{R_2} \end{bmatrix} \begin{bmatrix} v_1 \\ v_2 \end{bmatrix}$$

(1)

By converting the y parameters of (1) to S parameter yield [11]:

$$S_{11} = S_{22} = \frac{1}{D} \left( 1 - \frac{g_m Z_o^2}{1 + g_m R_1} \right) \tag{2}$$

$$S_{21} = \frac{1}{D} \left( \frac{-2g_m Z_o}{1 + g_m R_1} + \frac{2Z_o}{R_2} \right) \tag{3}$$

and

$$S_{12} = \frac{2Z_o}{DR_2} \tag{4}$$

where

$$D = 1 + \frac{2Z_o}{R_2} \frac{g_m Z_o^2}{R_2 (1 + g_m R_1)}$$

(5)

From (2), the conditions are satisfied when  $S_{11} = S_{22} = 0$  are satisfied when

$$1 + g_m R_1 = \frac{g_m Z_o^2}{R_2} \tag{6}$$

or

$$R_1 = \frac{Z_o^2}{R_2} - \frac{1}{g_m} \tag{7}$$

From (7), it can be observed that with positive value of  $R_1$  and large value for transconductance value,  $g_{m_1}$   $S_{11} = S_{22} = 0$  can be achieved. Hence, the designer can have a range of values for  $R_1$ ,  $R_2$  and  $g_m$  for good matching. Substituting (7) into (3) and (4) gives

$$S_{21} = \frac{Z_o - R_2}{Z_o} \tag{8}$$

and

$$S_{12} = \frac{Z_o}{R_2 Z_o} \tag{9}$$

From (7), the minimum transconductance can be achieved while  $R_1 = 0$  ( $g_{m(min)} = \frac{R_2}{Z_o^2}$ ) and it follows from (8) that

$$g_{m(\min)} = \frac{1 - S_{21}}{Z_2} \tag{10}$$

For instance, in the LNA that needs to provide  $|S_{21}|^2 = 15 \text{ dB}$

$$g_{m(\text{min})} = \frac{1 - (-5.62)}{50} = 132.4 \text{ms}$$

And the required R<sub>2</sub> (feedback resistor) calculated from the (7) is

$$R_2 = 132.4x10^{-3}(50)^2 = 331\Omega$$

Equation (8) can also be expressed as

$$R_2 = Z_0 (1 + |S_{21}|) \tag{11}$$

From (11), it is noticeable that  $S_{21}$  depend only on the value of  $R_2$  and none of the transistor S-parameters, thus gain flattening can be achieved by utilizing the negative feedback technique [2]. Another consideration in the feedback design is at certain frequency, the phase of  $S_{21}$  will sometimes have a portion where the output voltage will in phase with the input voltage, and to prevent the positive feedback, an inductor is often added in series with  $R_2$  to decrease the feedback phase as to ensure the feedback is always negative.

#### 4. LNA Circuit and Prototype

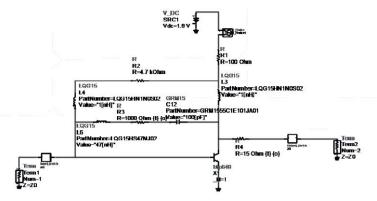

The transistor SPICE model is readily available for simulation purposes. To meet the specification with the restriction of low power consumption, the transistor is biased at 8mA ( $I_{DS}$ ) and 1.8V ( $V_{CC}$ ). The feedback resistor,  $R_2$  is initially set to 331 $\Omega$ . The circuit is being simulated and optimized to enhance the NF, IIP3, input and output return loss. To meet the strict requirement,  $R_2$  is being tuned and optimize to  $1000\Omega$  due to the matching condition and parasitic effect of the PCB board. The schematic of LNA is shown in Fig 4. After the schematic had been optimized, the circuit had been fabricated on a FR4 PCB for measurement.

#### 5. LNA Circuit and Prototype

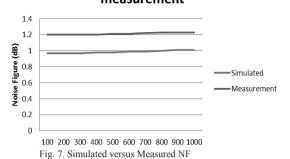

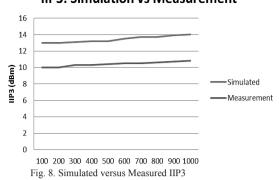

The fabricated wideband LNA is shown in Fig. 5. The layout of the board was designed using the Advance Design System (ADS). The circuit is supplied with a 1.8V DC through the DC pins at the top of the board. The drain current is measured to be around 8 mA, thus it is consistent with the simulated circuit. SMA connectors are attached at both RF input and output. The fabricated board is measured using standard RF equipment (Network Analyzers, Signal Generators, Spectrum Analyzer and Noise Figure Analyzer) for the parameters performance of Table II. The simulated and measured S-Parameter performances are shown in Fig. 6, while the simulated and measured NF performances are shown in Fig. 7. Finally, the simulated and measured IIP3 performances are shown in Fig. 8.

By referring to the result, it can be observed that the simulated and measured results are quite different. The simulated and measured return losses  $S_{11}$  are below -10dB which indicates that the board is well match at the input. The good matching at the input ensures a good noise figure performance. The output return loss,  $S_{22}$  seems to resonate at 0.3GHz compared to the flat response of the simulation.

The measured and simulated gain has the difference of 0.8 dB at lower frequency and the difference gets smaller at higher frequency. This shows that there is a good correlation between the simulated and actual board at higher frequency. The difference in gain is due to the parasitic effect of the components. In the simulation, parasitic effect of the component and RF traces are not taken into account. Thus, it contributes to the inaccuracy of the simulation result.

The LNA show a good reverse isolation which will prevent the signal from the output feed into input and become an oscillator. There are almost 3.5 dB different between measurement and simulated result. This is due to the miller effect if BJT transistor and the parasitic effect of the component.

There are also differences of around 0.2 dB in terms of noise figure. This small difference is considered good as the noise figure of the RF board can easily be affected due to imperfect soldering, RF traces and addition of the SMA connector.

The IIP3 performance also not so well correlated because at lower power, the circuit is more affected by the environmental temperature and equipment uncertainties.

Fig. 4. The simulated LNA schematic

Fig. 5. The fabricated LNA circuit

Fig. 6. Simulated versus measured S-Parameter Performance

## Noise Figure: Simulation vs measurement

#### **IIP3: Simulation vs Measurement**

#### 6. Conclusions

The LNA for SDR two-way radio operating from 100 MHz to 1 GHz had been designed. The design specification deduced from the TIA standard requires challenging design skills as the design is focused on low power consumption. This is quite impossible to achieve those requirements with the conventional LNA design. Therefore, feedback technique has been employed in the LNA design in order to meet the design specification over the wide frequency ranges.

The RLC feedback technique has the benefit of providing consistency of performances throughout the wide frequency range. Output resistive loading was also implemented in the circuit to stabilize the active device which is initially unstable. The matching and biasing circuits are also carefully designed so that the design specifications are met with lowest count parts. Tuning and optimization of the circuit is very crucial to make sure that the LNA gives the best performance. From the design of the schematic until the generation of layout, troubleshooting and improvement need to be made in order to get the final fabricated LNA that meeting the design specifications.

For further study and future work, the performance of feedback LNA may be compared with the compact branch line coupler balance amplifier, since this type of amplifier is proven to exhibit higher linearity and better matching while expected will reduce the RF trace by at least 30%. Hence, it is smaller size compared to conventional balanced amplifier design at < 400 MHz application.

#### Acknowledgement

The author would like to thank Universiti Teknikal Malaysia Melaka (UTeM) for the grant number PJP/2011/FKEKK (35C)/S00933.

#### References

- [1] Motorola Solutions, "Motorbo™ Digital Two-Way Radio Repeaters Product Spec Sheet, Motorola Solutions, pp. 3-7, 2011.

- [2] Guillermo Gonzalez, "Microwave Transistor Amplifiers Analysis and Design," Prentice-Hall, Inc., 2<sup>nd</sup> ed., 1996.

- [3] D. M. Pozar, "Microwave and RF Design of Wireless Systems" 3rd Edition: John Wiley & Sons Inc, 2001.

- [4] Dale D. Henkes, "LNA Design Uses Series Feedback to Achieve Simultaneous Low Input VSWR and Low Noise," *Applied Microwave & Wireless*, pp. 26, October 1998.

- [5] M. Cimino, H. Lapuyade, Y. Deval, T. Taris and J.B. Bégueret, "Design of a 0.9 V, 2.45 GHz Self-testable and Reliability-enhanced CMOS LNA," IEEE Journal of Solid-State Circuits, Vol. 43, No. 5, May 2008, pp. 1187-1194.

- [6] J.Y. Hsieh, T. Wang and S.S. Lu, "Wideband Low Noise Amplifier by LC Load Reusing Technique," *Electronics Letters*, Vol. 45, No. 25, December 2009, pp. 1278-1280.

- [7] T.Y. Chang, J.H. Chen, L. Rigge and J.S. Lin, "A Packaged and ESD Protected Inductorless 0.1 to 8 GHz Wideband CMOS LNA," *IEEE Microwave and Wireless Components Letters*, Vol. 18, No. 6, June 2008, pp. 416-418.

- [8] Gramegna, G, "A sub-1-dB NF±2.3-kV ESD-protected 900-MHz CMOS LNA," IEEE Journal of Solid State Circuits, Vol. 36. P.1010 1017, July 2001.

- [9] Guochi Huang, "Post linearization of CMOS LNA using double cascade FETs", Circuits and Systems, 2006. ISCAS 2006. IEEE Proceedings May 2006

- [10] Wei Guo "Noise and linearity analysis for a 1.9 GHz CMOS LNA," Circuits and Systems, 2002. APCCAS 2002 Asia Pacific conference on Vol. 2, P.409 – 414, Oct. 2002.

- [11] S.W. Ellingson, "Requirements for an Experimental Public Safety Multiband/Multimode Radio: Analog FM Modes," Virginia Tech University, pp. 8-12, 2006.