#### **W&M ScholarWorks**

Dissertations, Theses, and Masters Projects

Theses, Dissertations, & Master Projects

2011

## Effective Large Scale Computing Software for Parallel Mesh Generation

andriy Kot College of William & Mary - Arts & Sciences

Follow this and additional works at: https://scholarworks.wm.edu/etd

Part of the Computer Sciences Commons

#### **Recommended Citation**

Kot, andriy, "Effective Large Scale Computing Software for Parallel Mesh Generation" (2011). Dissertations, Theses, and Masters Projects. Paper 1539623585. https://dx.doi.org/doi:10.21220/s2-hsxy-8829

This Dissertation is brought to you for free and open access by the Theses, Dissertations, & Master Projects at W&M ScholarWorks. It has been accepted for inclusion in Dissertations, Theses, and Masters Projects by an authorized administrator of W&M ScholarWorks. For more information, please contact scholarworks@wm.edu.

# Effective Large Scale Computing Software for Parallel Mesh Generation

#### Andriy Kot Ternopil, Ukraine

Master of Science, The College of William and Mary, 2004 Master of Science, Ternopil Academy of National Economy, 2003

A Dissertation presented to the Graduate Faculty of the College of William and Mary in Candidacy for the Degree of Doctor of Philosophy

Department of Computer Science

The College of William and Mary  ${\rm May}~2011$

#### APPROVAL PAGE

This Dissertation is submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Andriy Kot

Approved by the Committee, May 2011

Committee Chair

Professor Nikos Chrisochoides, Computer Science Old Dominion University Adjunct Professor, Computer Science The College of William and Mary

Weizhen Mao

Associate Professor Weizhen Mao, Computer Science The College of William and Mary

Associate Professor Qun Li, Computer Science The College of William and Mary

Assistant Professor Xipeng Shen, Computer Science

The College of William and Mary

Professor Henry Krakauer, Physics The College of William and Mary

#### ABSTRACT PAGE

Scientists commonly turn to supercomputers or Clusters of Workstations with hundreds (even thousands) of nodes to generate meshes for large-scale simulations. Parallel mesh generation software is then used to decompose the original mesh generation problem into smaller sub-problems that can be solved (meshed) in parallel. The size of the final mesh is limited by the amount of aggregate memory of the parallel machine. Also, requesting many compute nodes on a shared computing resource may result in a long waiting, far surpassing the time it takes to solve the problem.

These two problems (i.e., insufficient memory when computing on a small number of nodes, and long waiting times when using many nodes from a shared computing resource) can be addressed by using out-of-core algorithms. These are algorithms that keep most of the dataset out-of-core (i.e., outside of memory, on disk) and load only a portion in-core (i.e., into memory) at a time.

We explored two approaches to out-of-core computing. First, we presented a traditional approach, which is to modify the existing in-core algorithms to enable out-of-core computing. While we achieved good performance with this approach the task is complex and labor intensive. An alternative approach, we presented a runtime system designed to support out-of-core applications. It requires little modification of the existing in-core application code and still produces acceptable results. Evaluation of the runtime system showed little performance degradation while simplifying and shortening the development cycle of out-of-core applications. The overhead from using the runtime system for small problem sizes is between 12% and 41% while the overlap of computation, communication and disk I/O is above 50% and as high as 61% for large problems.

The main contribution of our work is the ability to utilize computing resources more effectively. The user has a choice of either solving larger problems, that otherwise would not be possible, or solving problems of the same size but using fewer computing nodes, thus reducing the waiting time on shared clusters and supercomputers. We demonstrated that the latter could potentially lead to substantially shorter wall-clock time.

# **Table of Contents**

| A  | ckno  | wledgments                                           | iii       |

|----|-------|------------------------------------------------------|-----------|

| Li | st of | Table                                                | iv        |

| Li | st of | Figures                                              | vi        |

| 1  | Intr  | roduction                                            | 2         |

|    | 1.1   | Related work                                         | 6         |

|    |       | 1.1.1 Out-of-core computing                          | 6         |

|    |       | 1.1.2 Run-time systems                               | 8         |

| 2  | Out   | -of-core Parallel Delaunay Refinement                | 11        |

|    | 2.1   | 0                                                    | 11        |

|    |       | 5 1                                                  | 15        |

|    | 2.2   |                                                      | 17        |

|    |       | <b>U</b>                                             | 18        |

|    |       | · · · · · · · · · · · · · · · · · · ·                | 22        |

|    |       | 2.2.3 Out-of-core Hybrid Memory PDR                  | 27        |

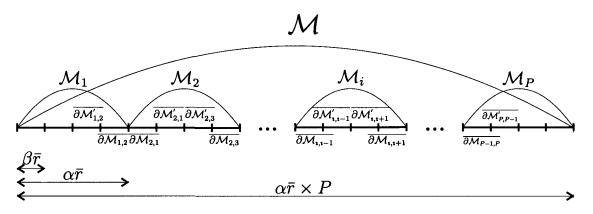

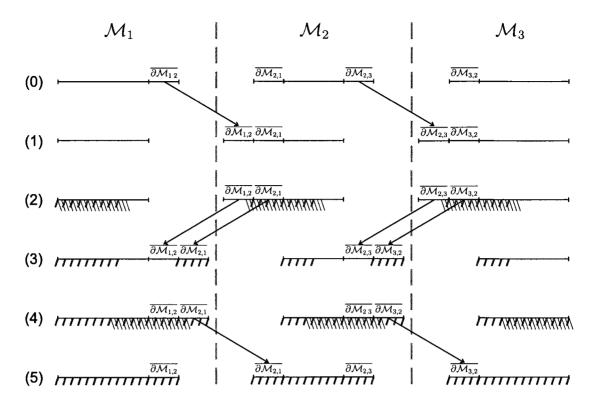

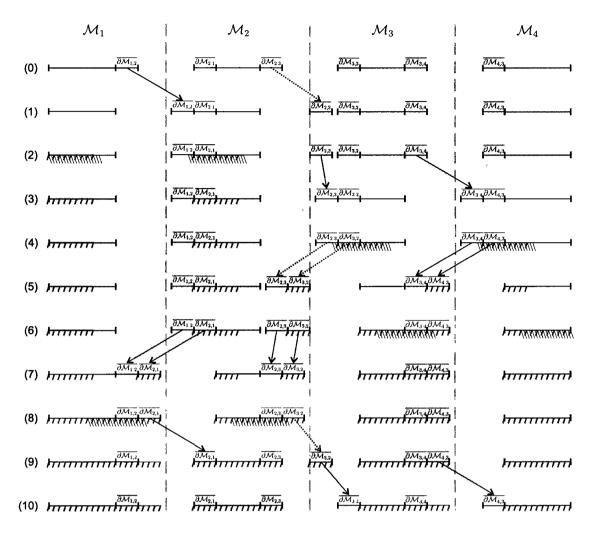

| 3  | Out   | -of-core Parallel Constraint Delaunay Meshing        | 33        |

|    | 3.1   | Parallel Constrained Delaunay Meshing                | 33        |

|    | 3.2   | Programming model                                    | 36        |

|    | 3.3   | Out-of-core subsystem for the PCDM                   | 37        |

|    | 3.4   | Implementation                                       | 38        |

| 4  | Mu    | lti-layered Run-Time System                          | <b>12</b> |

|    | 4.1   | Requirements                                         | 42        |

|    | 4.2   | Background                                           | 43        |

|    | 4.3   | Programming Model                                    | 44        |

|    | 4.4   | Organization                                         | 46        |

|    | 4.5   | Implementation                                       | 48        |

|    |       | 4.5.1 Software layers                                | 48        |

|    |       | 4.5.2 Mobile Objects and Threads                     | 50        |

|    |       | 4.5.3 Message Passing                                | 51        |

|    |       | 4.5.4 Object Migration                               | 52        |

|    | 4.6   | Out-of-core Non-Uniform Parallel Delaunay Refinement | 54        |

|   | Vita                                                  | 85 |

|---|-------------------------------------------------------|----|

|   | Bibliography                                          | 80 |

| 6 | Conclusion and Future work                            | 76 |

|   | 5.4 Multi-layered Run-Time System                     | 66 |

|   | 5.3 Out-of-Core Parallel Constrained Delaunay Meshing | 62 |

|   | 5.2 Out-of-core Parallel Delaunay Refinement          | 57 |

|   | 5.1 Experimental Setup                                | 56 |

| 5 | Performance Evaluation                                | 56 |

|   | 4.6.3 Findings                                        | 54 |

|   | 4.6.2 Optimization                                    | 53 |

|   | 4.6.1 Implementation                                  | 51 |

#### **ACKNOWLEDGMENTS**

I am grateful to my adviser Nikos Chrisochoides for everything he has done.

I thank Andrey Chernikov for his collaboration on numerous projects.

I very much appreciate feedback and support from my committee: Henry Krakauer, Weizhen Mao, Qun Li and Xipeng Shen.

Last but not least, I thank the people who suggested and helped me to get into graduate school, Allen Tucker and his wife Meg.

This work was performed using computational facilities at the College of William and Mary which were enabled by grants from Sun Microsystems, the National Science Foundation, and Virginia's Commonwealth Technology Research Fund.

This work was supported in part by NSF grants: CCF-0916526, CCF-0833081, and CSI-719929 and by the John Simon Guggenheim Foundation and Richard T. Cheng Endowment.

## List of Tables

| 5.1 | Parallel Delaunay refinement for a mesh of a unit square using the IBM                                |    |

|-----|-------------------------------------------------------------------------------------------------------|----|

|     | cluster. The OSPDR, the ODPDR and the OHPDR use 4 processors; the PDR uses 4, 9, 16 and 25 processors | 59 |

| 5.2 | Parallel Delaunay refinement for a mesh of a unit square using the IBM                                | J  |

| 0.2 | cluster. The OSPDR, the ODPDR and the OHPDR use 4 processors; the                                     |    |

|     | PDR uses 4, 9, 16 and 25 processors                                                                   | 59 |

| 5.3 | Parallel Delaunay refinement for the unit square. The ODPDR and the                                   | 00 |

| 0.0 | OHPDR1 use 16 processors (4 nodes, 4 CPU per node); the OHPDR2                                        |    |

|     | uses 16 processors (2 nodes, 8 CPUs per node) of the IBM cluster; the                                 |    |

|     | PDR uses up to 121 processors of the SciClone cluster. In parentheses on                              |    |

|     | the PDR column are the corresponding values from running the in-core                                  |    |

|     | PDR on up to 32 processors of the IBM cluster. Wait-in-queue time is                                  |    |

|     | included when computing normalized speed for the in-core algorithm                                    | 60 |

| 5.4 | Parallel Delaunay refinement for a mesh of the pipe model. The ODPDR                                  |    |

|     | and the OHPDR use 16 processors (4 nodes, 4 CPUs per node); the                                       |    |

|     | PDR uses varying number of processors (16-121). Wait-in-queue time is                                 |    |

|     | included when computing normalized speed for the in-core algorithm                                    | 61 |

| 5.5 | Average sustained speed of local disks for nodes 1 through 4                                          | 63 |

| 5.6 | Normalized speed of the PCDM and the OPCDM for problems that                                          |    |

|     | fit completely in-core. OPCDM(d) and OPCDM(b) denote respectively                                     |    |

|     | OPCDM with disk and database OoC subsystems. Pipe geometry                                            | 63 |

| 5.7 | Normalized speed of the PCDM with virtual memory and the OPCDM for                                    |    |

|     | problems that have memory footprint twice as large as the available phys-                             |    |

|     | ical memory. OPCDM(d) and OPCDM(b) denote respectively OPCDM                                          |    |

|     | with disk and database OoC subsystems. Pipe geometry                                                  | 64 |

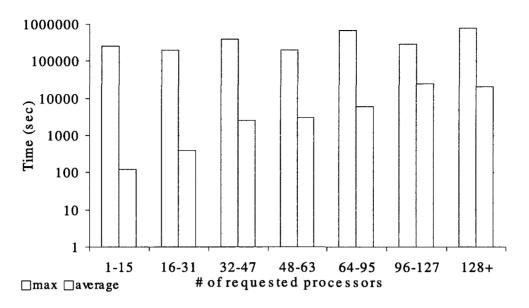

| 5.8 | Normalized speed of the PCDM(estimated) and the OPCDM for large                                       |    |

|     | problem sizes. The normalized speed for the PCDM is estimated using                                   |    |

|     | statistical data for wait-in-queue time and average per processor perfor-                             |    |

|     | mance demonstrated on smaller in-core problems. The normalized speed                                  |    |

|     | for the OPCDM is computed from the actual total execution time using                                  |    |

|     | 16 PE (2 nodes) with total physical memory of 16 GB on varying problem                                |    |

|     | sizes (there is no wait-in-queue time for the OPCDM). OPCDM(d) and                                    |    |

|     | OPCDM(b) denote respectively OPCDM with disk and database OoC                                         | ٥. |

|     | subsystems. Pipe geometry.                                                                            | 65 |

| 5.9         | OPCDM disk utilization and I/O overlap using disk OoC subsystem. Utilization is all associations of calcium of calcium and Openham is all associations of calcium of calcium and openham is all associations of calcium of calcium and openham is all associations of calcium of ca |            |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|             | lization is shown as a fraction of achievable speed. Overlap is shown as a fraction of total time. Pipe geometry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 65         |

| 5 10        | Normalized speed of the PCDM(estimated) and the OPCDM for large                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00         |

| 0.10        | problem sizes. The normalized speed for the PCDM is estimated using                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

|             | statistical data for wait-in-queue time and average per processor perfor-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |

|             | mance demonstrated on smaller in-core problems. The normalized speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

|             | for the OPCDM is computed from the actual total execution time using                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

|             | 16 PE (2 nodes) with total physical memory of 16 GB on varying problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

|             | sizes (there is no wait-in-queue time for the OPCDM). OPCDM(d) and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

|             | OPCDM(b) denote respectively OPCDM with disk and database OoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |

|             | subsystems. Brain geometry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 66         |

| 5.11        | OPCDM disk utilization and I/O overlap using disk OoC subsystem. Uti-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

|             | lization is shown as a fraction of achievable speed. Overlap is shown as a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |

|             | fraction of total time. Brain geometry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 66         |

| 5.12        | Normalized speed of the PCDM(estimated) and the OPCDM for large                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

|             | problem sizes. The normalized speed for the PCDM is estimated using                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

|             | statistical data for wait-in-queue time and average per processor perfor-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |

|             | mance demonstrated on smaller in-core problems. The normalized speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

|             | for the OPCDM is computed from the actual total execution time using                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

|             | 16 PE (2 nodes) with total physical memory of 16 GB on varying problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

|             | sizes (there is no wait-in-queue time for the OPCDM). OPCDM(d) and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

|             | OPCDM(b) denote respectively OPCDM with disk and database OoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |

|             | subsystems. Letter "A" geometry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 67         |

| 5.13        | OPCDM disk utilization and I/O overlap using disk OoC subsystem. Uti-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

|             | lization is shown as a fraction of achievable speed. Overlap is shown as a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |

|             | fraction of total time. Letter "A" geometry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 67         |

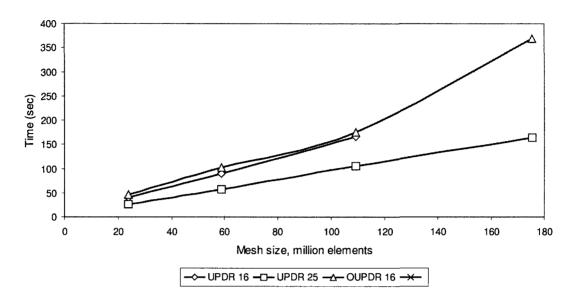

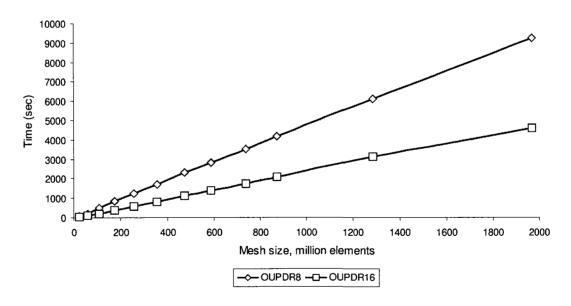

|             | Single PE performance of UPDR and OUPDR methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68         |

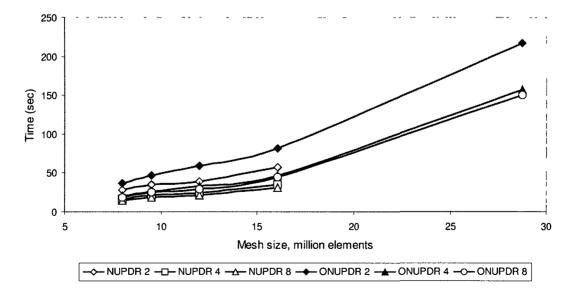

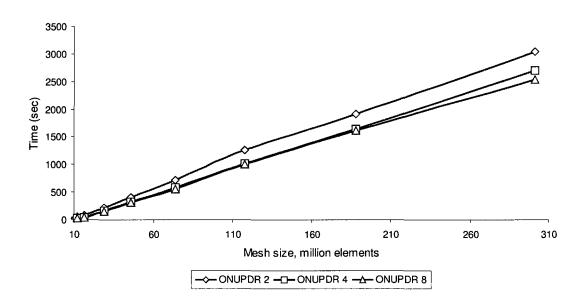

|             | Single PE performance of NUPDR and ONUPDR methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 72         |

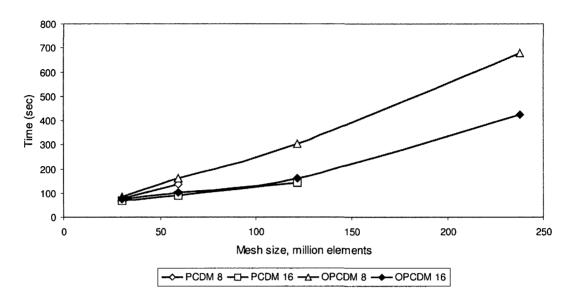

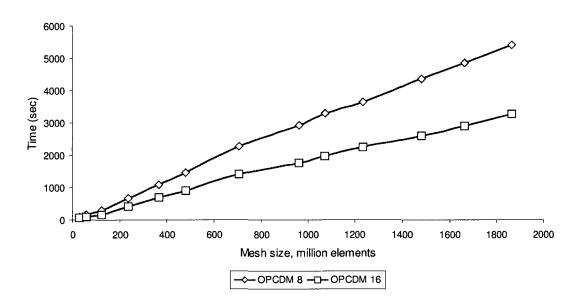

|             | Single PE performance of PCDM and OPCDM methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 72         |

| 5.17        | Overlap of computation, communication and out-of-core disk I/O in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

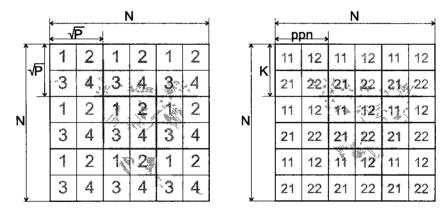

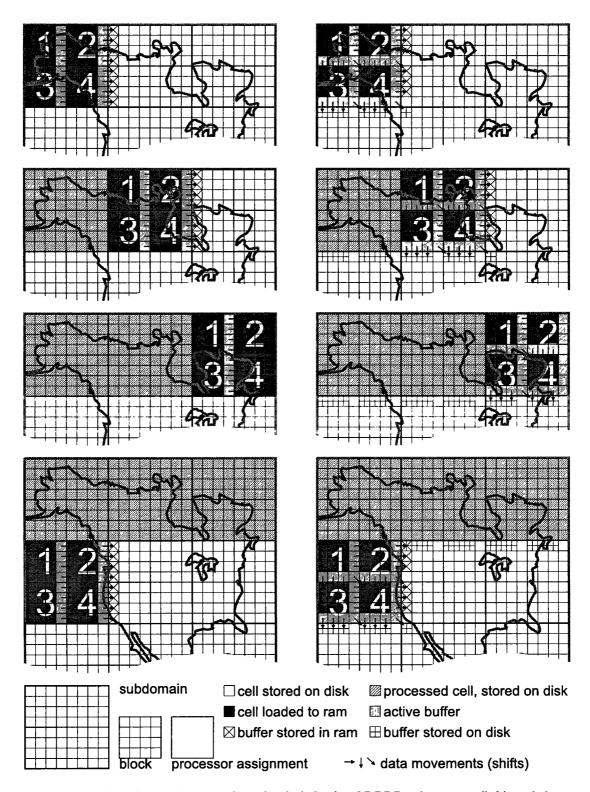

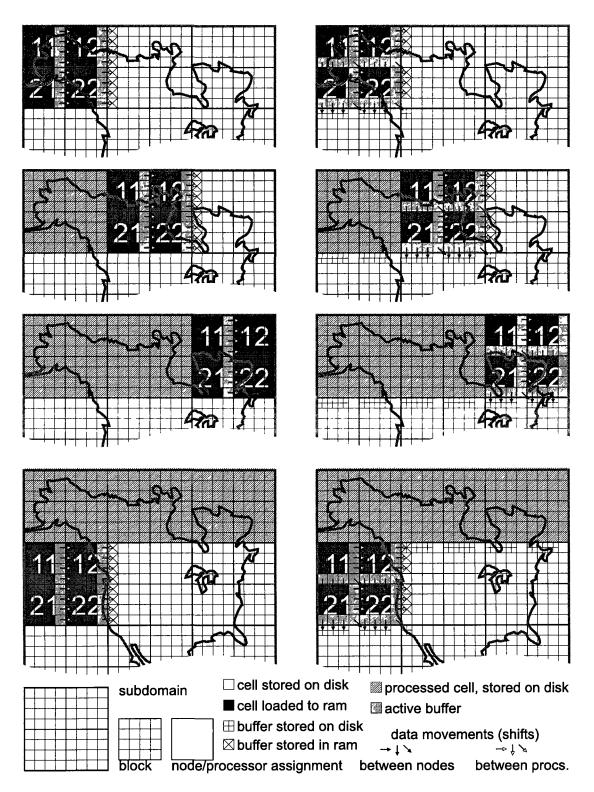

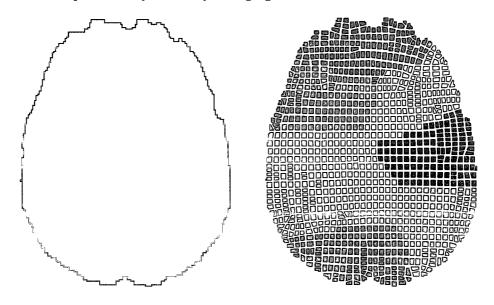

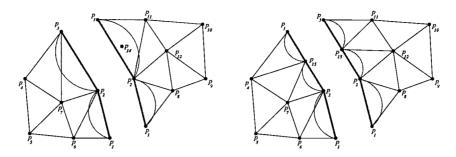

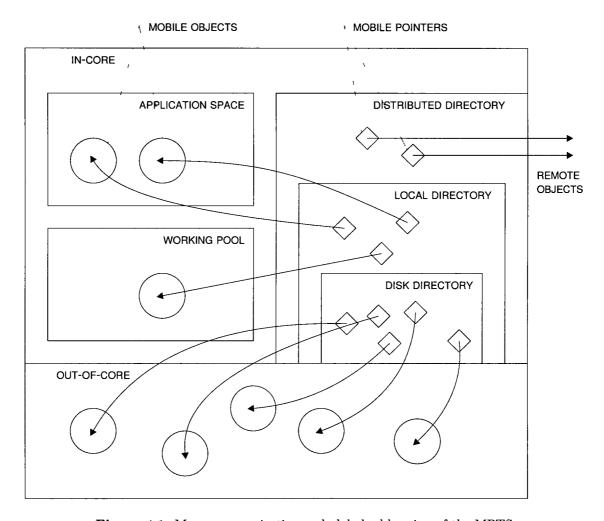

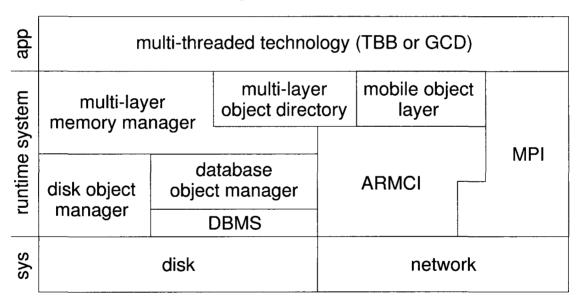

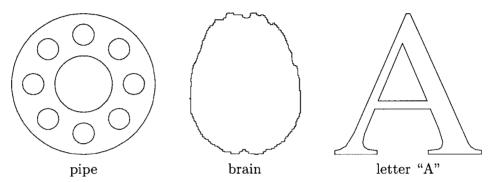

| <b>-</b> 10 | OUPDR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 73         |